Page 1

CONTENTS

Safety Information ............................................................................................................................2

Electrostatic Discharge Sensitive (ESDS) Device Handling .........................................................2

Warranty.............................................................................................................................................2

Specifications ....................................................................................................................................3

Speaker EQ Curves ..........................................................................................................................4

Theory of Operation ................................................................................................................... 5-21

Disassembly/Assembly Procedures ....................................................................................... 21-22

Test Procedures ........................................................................................................................ 23-30

Part List Notes .................................................................................................................................31

Main Part List, Digital BUILT-INvisible

Figure 1. Input/Output PCB, DSP PCB and Chassis Exploded View .............................................32

Figure 2. Amplifier PCB Assembly with Heatsink Exploded View .................................................. 33

Figure 3. Assembled Amplifier with Heatsink Open ........................................................................34

Electrical Part Lists ................................................................................................................... 35-55

I/O PCB Electrical Part List ...................................................................................................... 35-41

DSP PCB Electrical Part List ................................................................................................... 42-48

Amplifier PCB Electrical Part List ........................................................................................... 49-55

Packaging Part List, Digital BUILT-INvisible System (see Figure 4) ...........................................56

Figure 4. Digital BUILT-INvisible System Packaging View ..............................................................56

Integrated Circuit Diagrams..................................................................................................... 57-61

Appendix.................................................................................................................................... 62-80

Accessories used with the TA-1 Amplifier.............................................................................. 62-63

CD-50 System Assembly Part List ................................................................................................63

BUILT-INvisible Series II Bass Module .........................................................................................64

SE-1 Audio/Video Switcher ............................................................................................................65

Figure 5. SE-1 Audio/Video Switcher Packing Diagram .................................................................65

CI-1 Control Integrator ...................................................................................................................66

Figure 6. CI-1 Control Integrator Packing Diagram .........................................................................66

Figure 7. TA-1 Amplifier Test Setup Diagram ...................................................................................67

Figure 8. TA-1 Amplifier Connection Diagram .................................................................................68

Table 1. Satellite Speaker EQ DIP Switch Settings ........................................................................71

Computer Setup Procedure ..................................................................................................... 72-73

Amplifier Firmware Upgrade Procedure.......................................................................................74

TA-1 Amplifier TAP Command Tables ..................................................................................... 75-78

System Troubleshooting Information ..................................................................................... 79-80

Figure 9. TS-200 System Connection Details .................................................................................81

Figure 10. TS-400 System Connection Details ...............................................................................82

Figure 11. TS-600 System Connection Details ...............................................................................83

®

Amplifier (see Figures 1, 2 and 3) ................................31

CAUTION: The Bose® BUILT-INvisible® TA-1 amplifier contains

no user-serviceable parts. To prevent warranty infractions,

refer servicing to warranty service stations or factory service.

PROPRIETARY INFORMATION

THIS DOCUMENT CONTAINS PROPRIETARY INFORMATION OF

BOSE CORPORATION WHICH IS BEING FURNISHED ONLY FOR THE

PURPOSE OF SERVICING THE IDENTIFIED BOSE PRODUCT BY AN

AUTHORIZED BOSE SERVICE CENTER OR OWNER OF THE BOSE

PRODUCT, AND SHALL NOT BE REPRODUCED OR USED FOR ANY

OTHER PURPOSE.

1

Page 2

SAFETY INFORMATION

1. Parts that have special safety characteristics are identified by the symbol on schematics

or by special notes on the parts list. Use only replacement parts that have critical characteristics

recommended by the manufacturer.

2. Make leakage current or resistance measurements to determine that exposed parts are

acceptably insulated from the supply circuit before returning the unit to the customer.

Use the following checks to perform these measurements:

A. Leakage Current Hot Check-With the unit completely reassembled, plug the AC line cord

directly into a 120V AC outlet. Do not use an isolation transformer during this test. Use a leakage

current tester or a metering system that complies with American National Standards Institute

(ANSI) C101.1 "Leakage Current for Appliances" and Underwriters Laboratories (UL) 6500 / IEC

60056 paragraph 9.1.1. With the unit AC switch first in the ON position and then in OFF position,

measure from a known earth ground (metal waterpipe, conduit, etc.) to all exposed metal parts

of the unit (antennas, handle bracket, metal cabinet, screwheads, metallic overlays, control

shafts, etc.), especially any exposed metal parts that offer an electrical return path to the chassis. Any current measured must not exceed 0.5 milliamp. Reverse the unit power cord plug in the

outlet and repeat test. ANY MEASUREMENTS NOT WITHIN THE LIMITS SPECIFIED HEREIN

INDICATE A POTENTIAL SHOCK HAZARD THAT MUST BE ELIMINATED BEFORE RETURNING THE UNIT TO THE CUSTOMER.

B. Insulation Resistance Test Cold Check-(1) Unplug the power supply and connect a jumper

wire between the two prongs of the plug. (2) Turn on the power switch of the unit. (3) Measure the

resistance with an ohmmeter between the jumpered AC plug and each exposed metallic cabinet

part on the unit. When testing 3 wire products, the resistance measured to the product enclosure

should be between 2 and infinite MOhms. Also, the resistance measured to exposed input/output

connectors should be between 4 and infinite MOhms. When testing 2 wire products, the resistance measured to exposed input/output connectors should be between 4 and infinite MOhms.

If it is not within the limits specified, there is the possibility of a shock hazard, and the unit must

be repaired and rechecked before it is returned to the customer.

ELECTROSTATIC DISCHARGE SENSITIVE (ESDS)

DEVICE HANDLING

This unit contains ESDS devices. We recommend the following precautions when repairing,

replacing or transporting ESDS devices:

• Perform work at an electrically grounded work station.

• Wear wrist straps that connect to the station or heel straps that connect to conductive

floor mats.

• Avoid touching the leads or contacts of ESDS devices or PC boards even if properly

grounded. Handle boards by the edges only.

• Transport or store ESDS devices in ESD protective bags, bins, or totes. Do not insert

unprotected devices into materials such as plastic, polystyrene foam, clear plastic bags,

bubble wrap or plastic trays.

WARRANTY

The Bose® BUILT-INvisible® TA-1 Theater Amplifier is covered by a 1-year transferable

limited warranty

2

Page 3

SPECIFICATIONS

Power Output (all channels loaded): Bass Channel: 140 Watts at 100 Hz into 4 Ohms

Satellite Channels: 35 Watts at 1 kHz into 8 Ohms

Distortion: Bass Channel: < 0.4% THD at 0.5W

Satellite Channels: < 0.1% THD at 0.5W

Output Noise: Bass Channel: < 2 mVrms, unweighted

Satellite Channels: < 400 uVrms, A weighted

Signal to Noise Ratio: 96 dB

DC Offset: < 50 mVdc, all channels

Satellite Balance:

Satellite Separation: > 40 dB at 1 kHz, > 30 dB at 10 kHz, stereo mode

Standby Line Power: < 5 W at rated line voltage (plugged in, music center off)

Idle Line Power: < 15 W at rated line voltage (plugged in, music center

Analog Input Impedance: 5.0k Ohms + 10% at 1 kHz

S/PDIF Input Impedance: 75 Ohms + 10% at 100 kHz

Analog Input Sensitivity: 0.5 Vrms input at 100 Hz/1 kHz for rated power in

Analog Input CMRR: > 40 dB at 60 Hz, within + 12V common mode

Compressor: > 20 dB compression from 200-10 kHz with distortion

Turn On Delay: 1.5 Seconds maximum

Turn Off Delay: < 200 mS

+ 1.5 dB for volume settings 0 to -79 dB

on and muted)

bass/satellite channels

throughout the compression range < 3% at 1 kHz and

< 4% at 50 Hz

Volume Control Attenuation Range: 0 dB to -80 dB

Center Volume Control Range: -6 dB to 0 dB in 1 dB steps, 0 dB to 9 dB in 1.5 dB steps

Surround Volume Control Range: -6 dB to 0 dB in 1 dB steps, 0 dB to 9 dB in 1.5 dB steps

Audio Inputs: Audio and audio for video

Control Inputs: IR, Serial (RS-232), Speaker Data (Music Center), and

TV Sense (logic level)

Indicators: Power, Standby/Command, Setup/Analog Input, Fault/

Digital Input

Power Supply: 110-120 Vac, 60 Hz, 400W, 3.63 Amps

Dimensions: 15.75"H x 10.75"W x 3.38"D (40cm x 27.3cm x 8.6cm)

Unit Weight: 16 lbs (7.25 kg)

3

Page 4

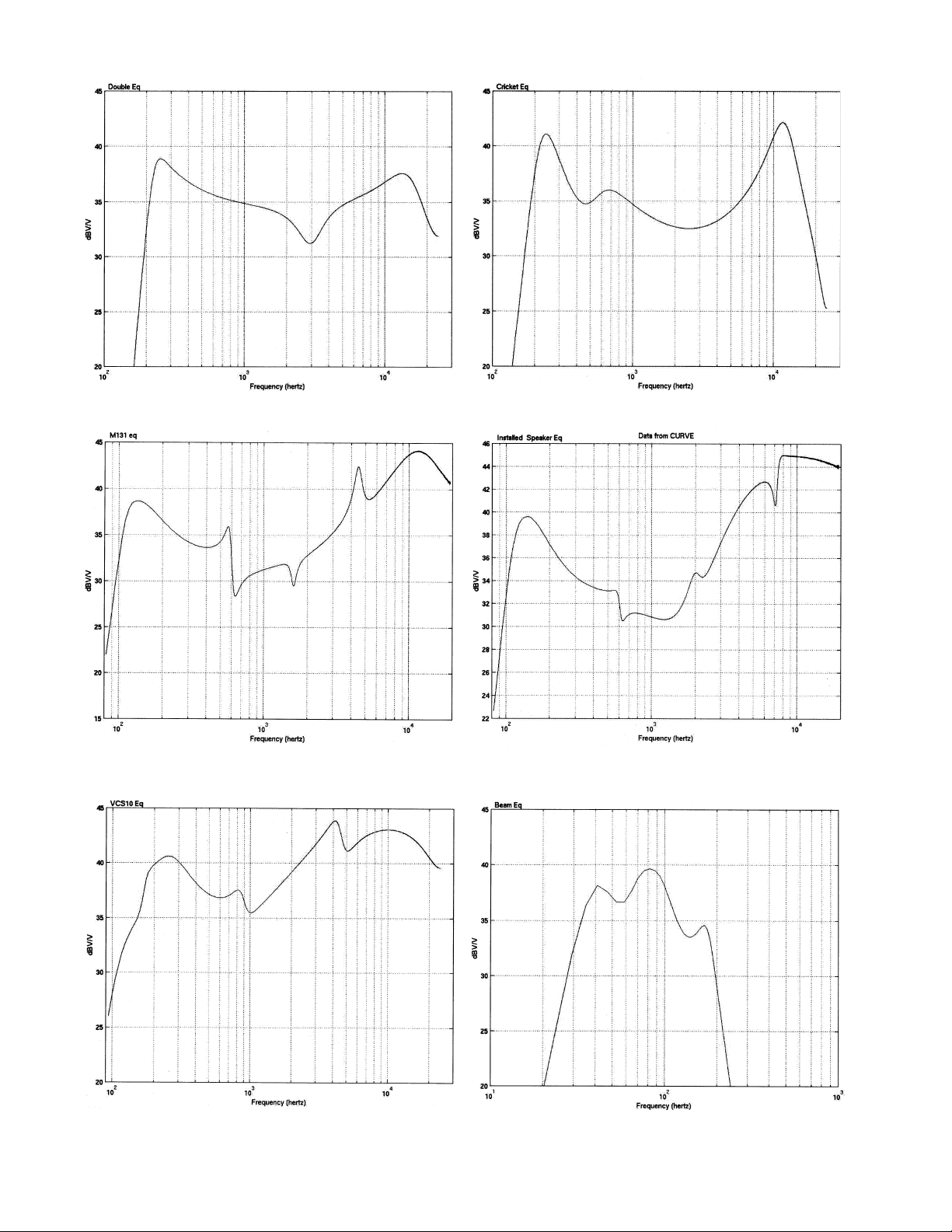

SPEAKER EQ CURVES

CS-2 Satellite Speaker EQ Curve Jewel Cube® Satellite Speaker EQ Curve

Residential 131® Satellite Speaker EQ Curve

VCS-10® Center Channel Speaker EQ Curve

Residential 1.2 Ohm Speakers

EQ Curve

Acoustimass® Series II Bass Module

EQ Curve

4

Page 5

General Overview

THEORY OF OPERATION

The Bose® Digital BUILT-INvisible® amplifier is a six-channel system with DSP-based Dolby

®

Digital 5.1 decoding and Videostage® II signal processing. It is intended for built in installations in

Bose residential sound systems. Its six channels will normally be presenting sound for home

theater, in 5.1 format.

The Digital BUILT-Invisible amplifier has a total of six audio inputs:

- stereo analog audio for a music source

- stereo analog audio for a video source

- four digital audio for stereo or multi-channel Dolby Digital 5.1 audio (SPDIF coax)

Furthermore, the Digital BUILT-Invisible amplifier has a number of control ports:

- Lifestyle® music center compatible input

- RS-232C serial bi-directional port

- TV Sensor input

- Remote IR sensor input

- IR diode

The amplifier responds to the various SmartSpeaker commands issued from the various Bose

Lifestyle

®

head-end units, such as the CD-5, CD-20 and the PMC/MRI used with the Lifestyle

®

40 and 50 systems. The amplifier can also be controlled via an external master remote control

(Philips) used in conjunction with either the CI-1 Control Integrator or the SE-1 Expander.

The Digital BUILT-Invisible amplifier is packaged in a metal enclosure, consisting of a steel base

and an aluminum extrusion cover. Internally, the electronics consist of:

- Input/Output (I/O) PCB

- Power Amplifier PCB

- DSP (Digital Signal Processor) PCB

- Toroidal power transformer

Input/Output (I/O) PCB

Note: Unless otherwise noted, refer to the schematic diagram for the Input/Output board for the

following information. The references in brackets [ ] are the grid coordinates for the component.

Analog audio inputs

The audio signals are applied at J6 [A4] and J21 [A3]. J6 is used for Music Audio Inputs and J21

is used for Video Audio Inputs. U1, 2, 7, & 8 [A2-4], dual op amps, comprise the four differential

amplifiers for these inputs. Each differential amplifier uses two op amp sections. The non-inverting (+) input passes through two inverting sections, while the inverting (–) input passes through

only the second inverting section. In this way, the amplifier responds to the difference between

the non-inverting (+) input and the inverting (–) input. External signals appearing in common on

the two input pins (capacitively or inductively coupled noise) are subtracted and are largely

eliminated. To improve common mode rejection, the critical resistances are packaged in a precision thin film network RN1 [A4] with a high degree of matching. To protect the differential amplifier

against ESD and the presence of higher than normal audio signals with or without power

present, series resistors R105 and R106 [A4] and D25 and D26 [A4] provide clamps. Further

ESD protection comes from the spark gap PCB patterns. C3 and C5 [A4] provide low pass

filtering to remove RF that could be picked up by input wiring.

5

Page 6

THEORY OF OPERATION

Input/Output (I/O) PCB (continued)

S1 [A3] section 1, a user accessible switch, is used to connect the left and right inverting (–)

pins of the Music Inputs together. S1-section 2 is used to connect the left and right – pins of the

Video Inputs together. This is sometimes desirable for certain installation wiring situations, such

as where the source wiring presented to the TA-1 amplifier is left non-inverting (+), right +, and a

common ground (unbalanced). One might choose to close S1 and connect left + to left +, right +

to right +, and common ground to left – (S1 will tie left – to right – in this case).

Analog audio input selector

The two stereo inputs, Music Audio and Video Audio, after passing through their differential

amplifiers, are presented to U3 [B4], an analog multiplexer at pins 4, 5, 12 and 13. When the

Set_Audio (U3 pin 1) input is high, the Video Audio input is selected and passes through. When

the Set_Audio line is low, the Music Audio input is selected. From U3’s outputs at pins 8 and 9,

the analog audio signals pass to J4-12 and 14, which carries them onto the DSP PCB, where

they enter the codec U100, [DSP schematic sheet 1, C4] and are converted to digital audio

signals.

Digital audio inputs

The four S/PDIF digital audio signals are delivered via J7 [C3], each in differential form. A typical

S/PDIF source, Source 1, is presented on J7-4 and J7-5 and passes through a DC blocking

capacitor (to keep the small transformer free of a DC bias) and into T1 [D3]. At the secondary,

the transformer is terminated in 75 Ohms to match the source impedance for best pulse fidelity.

Also at the secondary, the signal is referenced to ground and clamped to about +/-0.65 volts by

diode D8. The clamp is only active for higher than normal S/PDIF sources, but also protect the

inputs of U9 [D3], especially if signals are present while the power is off.

Digital audio input selector

The four single-ended digital sources are presented to U9 [D3], an analog multiplexer. Signals

DIG_SEL_A and DIG_SEL_B from the microcontroller U5 [C4] select one of the four inputs for

passage through U9. Signal DIG_EN can be used to disable the output regardless of the source

selection. From U9’s output, the selected SPDIF signal passes to J4-8 [E4], which carries it onto

the DSP PCB, where it enters a codec U100, [DSP schematic sheet 1, C4] and is unpacked to

yield the embedded digital audio signals.

Power amplifier outputs

The power amplifier output devices U700, U701, U703, U704, U705 and U707 (and associated

power transistors) [amplifier PCB schematic sheet 1] are located on the power amplifier PCB

which is attached to the extruded top cover. The amplifier output signals and their ground returns

are carried via a wire harness from J701 [power amp schematic sheet 2, A-C7] on the amplifier

PCB to J22 [D2] on the I/O PCB. The six amplifier outputs are directly wired to the appropriate

loudspeaker connectors along the right hand edge of the PCB. The RC networks [E2] contribute

to amplifier stability and reduce EMC and ESD events.

Power supplies, +8V and +5V

The I/O PCB receives the AC mains power via J5 [C2] and S9, and through fuses F3 and F4.

The +8V and +5V supplies provide keep-alive voltages to the I/O PCB control circuitry that

enable the amplifier to remain in standby mode, but also allow it to wake up and go into operate

mode when it receives commands to do so. When main power switch S9 is on, the +8V and +5V

supplies are energized. At first, the amplifier will be in standby mode, characterized by the

presence of +8V and +5V, but with the triac Q6 [C1] off.

6

Page 7

THEORY OF OPERATION

Input/Output (I/O) PCB (continued)

Power supplies, +8V and +5V (continued)

Until Q6 is turned on, the rest of the amplifier (the Power Amplifier and DSP PCBs) is off.

The AC mains is applied to T5 [C1], rectified by D22 (full wave bridge), and filtered by C31.

The +5V supply is created by U12 [C1] in a standard 3 terminal regulator application; so too is

+8V, created by U14. These supplies only deliver very low power outputs, capable of no more

than two to three watts total.

Power supply, main transformer control

The amplifier’s main power supply is created from the secondaries of a large toroidal transformer

that is turned on and off by the triac Q6. This is the transformer mounted in the center of the I/O

PCB. The secondary leads of this transformer connect via J702 to the Power Amplifier PCB,

where various power supply voltages are created, including the +/-12V supplies returned to the

I/O PCB to power the op amps and signal selectors. The +/-12V leave the amplifier PCB at J701

pins 13 and 15 and enter the I/O PCB at J22 pins 13 and 15.

A logic signal (AMP_POWER) from the microcontroller U5 [C4] at pin 11, goes high to turn on

the main power supply. AMP_POWER high causes base current in Q7 [C1], which in turn

causes the LED in Q5 to turn on. The opto-coupled LED turns on the internal triac in Q5 which,

finally, turns on the gate of triac Q6 and energizes the transformer.

Pulse Width Modulated tone control low pass filters, U15

The I/O PCB interprets user commands to change the bass and/or treble levels by delivering an

analog voltage between 0V (cut), +2.5V (flat), and +5V (boost) to the DSP PCB. The microcontroller U5 develops this analog voltage by controlling two of its output pins in pulse width

modulation mode. The inherent switching activity in PWM outputs requires a low pass filter, in

this case a 2

Clamp diodes D36 and D38 on the op amp outputs keep the filter output within bounds for its

destination, the DSP microcontroller U202 on the DSP PCB. The signals TREBLE and BASS

are passed to the DSP microcontroller U202 via J4-1 and J4-2 [E4].

TV Sensor input

J11 [A1], a three pin connector, provides ground and +8V (via resetable fuse F2 [A1]) for use by

a small TV sensor that must be attached to the TV monitor in the home theater. The TV sensor

circuitry returns a DC signal via J11-1 which, when high, indicates that the TV set is on. This will

cause the amplifier to turn on (if it is not already on). The TV sensor input is monitored by

microcontroller U5 [C4] at pin 8.

IR input

J10 [A1] acts as the gateway for incoming demodulated IR signals used by remote controls.

These signals are ultimately monitored by the microcontroller U5 [C4] and are sent to the DSP

PCB at J4 [E4]. One form of IR delivery is the electrical signal (logic level) from an externally

mounted IR receiver chip. This would typically be located in the home theater room, where it

would pick up IR radiation from a user remote control, decode it, and send it by wire to J10-3.

This signal is clamped and sent to AND gate U16 [B1], which acts as an OR selector for low

levels coming from this IR input and from the internal IR sensor. The second form of IR delivery

is via an electrical signal sent to J10-1 and –2. When this signal is asserted, the internal IR

emitter D3 [A1] is turned on and emits IR within the amplifier. This optically couples to IR sensor

U11 [A1] which toggles low and high, decoding the IR signal. This signal passes to U16’s second

input, where it is OR’d with the IR source discussed above. Finally, the IR signal is sent to the

microcontroller U5 [C4] as the signal IR_IN on U5 pin 7.

nd

order filter consisting of passive components and the dual op amp U15 [C2].

7

Page 8

THEORY OF OPERATION

Input/Output (I/O) PCB (continued)

Music Center input

®

J8 [A1], a four pin connector, provides a connection from a Bose

Lifestyle® music center to the

amplifier. This connector serve two functions. It can be used for connection to a Bose Lifestyle

music center or alternately for remote terminal access by means of an IBM compatible PC.

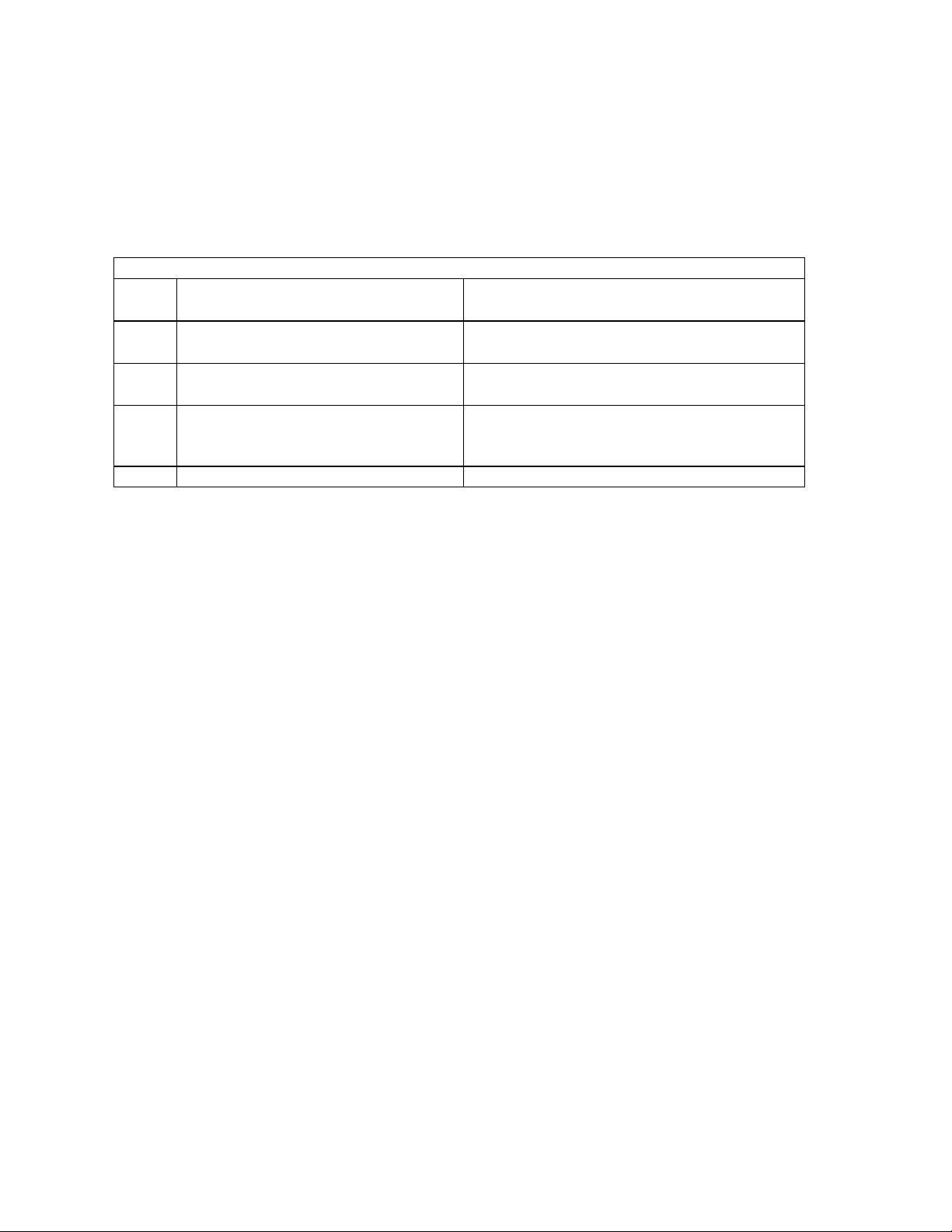

A table will help explain this.

J8 Functions

J8

pin

1

2

Mode: Normal Lifestyle

connection

Turn_on signal from Lifestyle

the amplifier

Speaker data sent from Lifestyle

to the amplifier

to

Mode: Remote terminal access

RS-232 RX line, data sent from RS-232C

terminal or PC to the amplifier

RS-232C TX line, data sent from the

amplifier to RS-232C terminal or PC

3 Antenna signal DTR: RS-232C terminal or PC sets this

high to tell the amplifier to operate in the

Remote Terminal Access mode

4 ground reference ground reference

In the Remote Terminal Access mode, a system installer can set up a notebook PC in the home

theater room and run InstallerTM software to custom equalize and balance the amplifier system

for the customer’s particular home theater room. The installer would connect the PC’s RS-232C

serial output to the Lifestyle® connector on the Bose wall panel, temporarily disconnecting the

Lifestyle® music center. Switching between the two modes is accomplished via the DPDT relay

K1 [A1]. K1, shown in the deenergized state (Normal Lifestyle® mode), is controlled by the logic

level signal provided to pin 3 when the remote terminal is present and has activated DTR.

®

RS-232C input/output

The amplifier in some installations may work entirely under RS-232C control. Such installations

may have Crestron or AMX remote control devices. J9 [A2] provides for RX, TX, and ground

connections to such a terminal. Since RS-232 sources can present electrical waveforms swinging between up to +/-12V, the RX signal is passed through a special RS-232C to TTL translator,

part of IC U10. In the same fashion, to permit the amplifier to transmit a bipolar TX signal, the TX

source is buffered on the way out through the output section of U10.

S4, Speaker EQ switch, and J1, Header to Test Accessory

The four signals controlled by S4 [B3] are read by the microcontroller U5 [C4] during initial

power-up of the amplifier. Refer to the Appendix of this manual for the EQ settings of S4.

J1 connects the I/O PCB with the test accessory. This connector is not used on production

amplifiers.

8

Page 9

THEORY OF OPERATION

Input/Output (I/O) PCB (continued)

Power supply failure monitor level translator

There are four power supplies on the power amplifier PCB, derived as two pairs of symmetrical

bipolar supplies. By tying each of these supplies into a node by appropriate resistor values, we

have a node that sits at zero volts when all supplies are normal. If one or more supplies deviates

sufficiently, we want to detect this as an error. The node PROTECT is brought out of the amplifier

PCB at J701 pin 11 [amplifier sheet 2, A7] and onto the I/O PCB at J22 pin 11 [D2] and connects

to Q1 and Q2 [D2]. Q2 turns on when PROTECT exceeds about 0.5V, while Q1 turns on when

PROTECT exceeds about –0.5V. This dual transistor’s output (Q1 collector) is normally high,

reflecting the state where all six power supplies on the power amplifier PCB are within normal

limits. When either transistor turns on, the output signal BUF_PROTECT_N out of Q1 goes low,

indicating a failure. The PROTECT signal also becomes active when there is a DC offset failure

in the bass speaker amplifier.

When the PROTECT signal becomes active, the microcontroller (U5) [C4] on the I/O PCB

responds by placing the unit into the Standby state, where the main power transformer is deenergized. The Fault LED D29 [D4] flashes on and off when this occurs. The next time a user

command is issued, it attempts to turn on, and will stay on if the fault has been cleared; otherwise, it will again switch to the Standby state.

Microcontroller U5 and related circuits

The I/O PCB requires its own microcontroller to monitor the serial interfaces, the installer DIP

switches, the TV sensor, etc. It is responsible for passing along control commands to the

microcontroller U202 [DSP schematic sheet 2, C5] on the DSP PCB. The I/O PCB’s microcontroller U5 is clocked internally by an oscillator using the crystal Y1 [C3]. The microcontroller

can write and read to the optional (not installed) EEPROM U6 [C3]. A reset generator U4 [C4]

ensures that the microcontroller wakes up and executes its reset routine when power is turned

on or momentarily interrupted. The microcontroller handles the 3 LEDs [D4] Command (D28),

Fault (D29), and Setup (D30). It also reads the configuration DIP switches contained in S7 [D4],

as well as the speaker EQ switches S4 [B3]. Other functions (bass and treble PWM outputs,

etc.) have been mentioned elsewhere in this presentation.

Digital Signal Processor (DSP) PCB

Signal Processing

Note: Unless otherwise noted, refer to the schematic diagrams for the DSP board for the follow-

ing information. The references in brackets [ ] are the schematic sheet and grid coordinates for

the component.

The Digital BUILT-INvisible

PCM (digitized 2-channel audio) or the AC-3 output from up to four separate digital sources.

AC-3, also known as Dolby® Digital, is a perceptual coding and data compression technique that

allows 5 wideband channels and one low frequency bass channel (5.1) to be compressed into

less bandwidth than would be required for 2-channel PCM.

®

amplifier has the ability to receive a digital S/PDIF bitstream, either

The Videostage® 5 processing used in the amplifier expands a L, R input pair into L, C, R, S

and bass, but adds a few new features over previous versions of Videostage, such as stereo

surround channels and a mono to 5 channel mode. The mono to 5 channel mode is a way of

processing a mono soundtrack such that all 5 speakers receive parts of the signal. The amplifier

will also accept two analog inputs directly at the input jacks.

9

Page 10

THEORY OF OPERATION

Digital Signal Processor (DSP) PCB (continued)

Power Supplies

There are several sets of internal power supply voltage rails. These voltages originate with the

main power transformer located in the center of the Input/Output (I/O) PCB. There is also a small

keep-alive transformer T5 [I/O PCB schematic, C1] located on the I/O board itself that allows the

amplifier to be turned on by SmartSpeaker commands.

The power amplifiers are supplied with both +40 and +20 VDC unregulated rails, as determined

by the Class G circuitry. These rails are developed from the transformer secondaries diode

bridges B700 and B701 [amplifier schematic sheet 2, A/B 3/4] and their associated capacitor

banks.

The digital circuitry on the DSP PCB requires two different regulated voltages, +5V and +3.3V.

The +5V regulator U1 [sheet 1, A5] is a standard 3 terminal linear regulator in a surface mount

package and is located on the DSP PCB. It’s powered from the +20V rail via fusing resistor

R704 [amplifier schematic sheet 2, C6] on the amplifier PCB, and supplies about 120mA to the

DSP PCB, most of which is consumed by the microcontroller and codec.

The +3.3V regulator U500 [sheet 4, D4] is a switch-mode regulator and must be located under

the shield to avoid EMI problems (harmonics of the 100 kHz switching frequency will stray into

the AM broadcast band if left unshielded). This regulator is also powered from the +20V rail and

supplies about 350mA to the DSPs.

Operation of the 5V linear regulator is very simple. Current is supplied to the regulator via surface-mount power resistors R10 and R11 [sheet1 A5], which drop the voltage supplied to the

regulator to avoid excessive power dissipation. The regulator needs a minimum of about 7V at its

input terminal to stay in regulation and it should be able to do this even as the +20V rail sags to

+10V or so.

Operation of the +3.3V switch-mode regulator is more complicated. In its simplest terms, the

unregulated input is “chopped” at about 100 kHz, and the resulting pulse train is low-pass filtered

to extract the DC. This DC output is compared to a +3.3V reference, and the duty cycle of the

switching waveform is adjusted accordingly. The high-side switch (the switch that connects

+20V to the output filter) is integrated into the controller, while the low-side switch (the switch that

connects ground to the output filter) is an external diode D500. When the controller is running,

you should be able to observe the switching waveform at L500.

Microcontroller

The microcontroller U202 on the DSP PCB is used for the following housekeeping and

control functions:

to interpret SmartSpeaker commands from the head-end.

to interpret special test mode commands from the functional tester.

to store and retrieve data from nonvolatile memory (U201).

to boot and reprogram the codec (U100) as required by the operating mode of the system.

- to monitor for bass and treble PWM voltage level from U15 on the I/O board.

- DC offset on the amplifier outputs.

- PCB over-temperature.

- presence/absence of a digital S/PDIF signal.

10

Page 11

THEORY OF OPERATION

Digital Signal Processor (DSP) PCB (continued)

Microcontroller (continued)

to sequence the amplifier and codec mute lines as required.

to boot and monitor the performance of the DSPs.

and relay information to/from DSPs.

In detail:

1. SmartSpeaker commands are interpreted by watching for digital activity on the serial data

input line (J5, pin 12 [sheet 1, C8]). This serial input can be either the “standard” SmartSpeaker

protocol, compatible with the outputs of CD-5, CD-20, etc., or it can be 4800 baud RS232 with

5V logic levels. The microcontroller decides which protocol to use based on the voltage level

present on the serial data input at boot time. If the line is low, it assumes RS232; if the line is

high, it assumes SmartSpeaker. It checks only once, at boot time, so switching from one protocol to the other requires a power cycle to reboot the system.

2. Test mode commands are special commands to facilitate testing, or to retrieve stored information from the nonvolatile memory. Test mode commands are RS232 only, e.g., the revision of the

firmware can be queried by sending the command “tv”, the answer “2200/2000” might come

back on the serial data output line. This would indicate version 22.00 for the microcontroller and

version 20.00 for the DSPs.

3. The nonvolatile memory is used to store the following information:

choice of equalization curve.

system, center, and surround volume settings at power-down.

US or Euro bass tone control preference.

system usage statistics.

number of times system was powered off.

minutes spent powered on.

4. The codec U100 [sheet 1, C4] has a fair number of internal registers, all of which must be set

up properly for correct operation, e.g., to switch between the ADC inputs and the S/PDIF input

(both functions are integrated into the codec), the codec must be reprogrammed. In addition,

there are a number of error status bits which are periodically sampled by the microcontroller, the

codec can be rebooted if problems are discovered.

5. The tone control potentiometers are not used on the Digital BUILT-INvisible

bass and treble are adjusted by means of pulse width modulation as acheived with the I/O board

microcontroller and support circuitry. See the I/O board theory of operation for a complete

description. The DSP microcontroller has several ADC inputs, two of which are used to detect

the voltage used to adjust the bass and treble. Everytime this voltage changes it is presented to

the DSPs, which adjust their tone control filter coefficients accordingly.

®

amplifier. The

11

Page 12

THEORY OF OPERATION

Digital Signal Processor (DSP) PCB (continued)

Microcontroller (continued)

6. Other ADC ports are used for the following functions:

• To monitor the gross DC offset on the five satellite speaker channels. Excessive DC offset is

assumed to be an indication of a serious problem and the microcontroller will respond to this

by shutting off the power to the amplifier.

• To detect the presence or absence of a digital S/PDIF signal. The codec cannot be set up for

an analog input and a digital S/PDIF input simultaneously and it cannot be reprogrammed

from analog to digital (or vice versa) without interrupting the audio signal.

• To sequence the mute line. As with the Series I, there are three so-called “speaker modes”,

2-channel (bass, left, right); 3-channel (bass, left, right and center) and 5-channel (bass, plus

all 5 satellites). Unused output channels are muted, not only at the DSP but also at the power

amplifier. The mute inputs to the power amplifiers are 5V logic-level outputs from the

microcontroller.

• The microcontroller is in charge of booting the DSPs at power-up in the following

sequence:

- Boots the codec and establishes the correct output signals from the codec (bit_clock,

frame_clock, and data).

- Enables the 3.3V power supply, and verifies the correct voltage from it.

- Releases the DSP reset line and waits for the DSPs to boot and acknowledge.

The microcontroller is always engaged in dialogue with both DSPs. If the DSPs should fail to

respond within a certain time-out, it is assumed that the DSPs have “crashed” and the DSPs are

rebooted. The microcontroller must pass some of the nonvolatile information in the EEPROM

over to the DSPs at boot time, e.g.: speaker eq, system volume (all volume control in is done in

the DSPs), center and surround volume and bass and treble pot position. The microcontroller

itself can be reset in two ways, by a hardware reset signal, which is generated by U200 when

the 5V supply drops below 4.75V and by the microcontoller itself, once it has already booted

successfully (it can pull its own reset line if the 8 MHz clock is running).

Codec

The codec U100 [sheet 1, C4] is a highly integrated device which includes the following

functions:

•An I 2 C interface for control and status information.

• Three channels of 20-bit ACD; only two are used, one for the left analog input and one for

the right. The ADCs will input signal levels in excess of 1 Vrms.

• Six channels of output DAC; all six are used. Maximum output signal level is 1 Vrms.

• A crystal oscillator which establishes the ADC/DAC sampling rate, in this case, it is

11.2896 MHz / 256 = 44.1 kHz.

• A S/PDIF receiver. “S/PDIF” stands for Sony/Philips Digital Interface Format. Essentially, for

every pair of 20-bit audio samples, another 24 bits of status, parity-checking and general

housekeeping bits are sent along for the ride. The data is encoded in such a way that:

a) there is no net DC content to the bit steam, allowing transformer or AC coupling and

b) the bit clock can be recovered from the bit steam.

12

Page 13

THEORY OF OPERATION

Digital Signal Processor (DSP) PCB (continued)

Codec (continued)

The codec generates three output signals, either from the 11.2896 MHz crystal, or from the input

S/PDIF bitstream;

• a serial bit stream containing the 20-bit audio data.

• a bit_clock, which indicates when to sample the serial bit stream.

• and a frame_clock, which indicates the start of an audio sample.

In addition, there is a serial data input (6 20-bit audio samples) to the codec, with timing that

corresponds exactly to the timing of the serial data output. These four signals (data out, data in,

bit_clock, and frame_clock) are used by the serial ports on the DSPs. The timing of the data flow

into and out of the DSP subsystem is driven entirely by the codec; the serial ports on the DSP

run asynchronously to the 40 MHz clock which drives the DSPs.

DSPs

The DSPs [DSP1, sheet 3 C/D7; DSP2, A/B7] are Analog Devices 21061L general purpose

floating point digital signal processors, each capable of about 40 MIPs of performance.

Two are required to provide enough MIPs for:

• AC-3 decoding.

• Videostage®.

• bass management.

• six channels of speaker equalization.

• tone controls.

The DSPs have no internal ROM; at boot time they load themselves from the external PROM

U401 [sheet 3, C2]. This boot process is more or less automatic; i.e., no intervention from the

microcontroller is required (although the microcontroller has control of the DSP reset line).

The 21061L processors are designed to be bussed together, which accounts for the relatively

large number of pins found on each DSP (240).

For instance, the signals required to connect the DSPs to each other and to the boot PROM

include:

• an external data address buss (32 bits, of which 24 are used).

• an external data buss (48 bits, of which 16 are used).

• buss control signals (buss priority, address and r/w strobes, etc).

Also, there are 30 power and 30 ground pins on each DSP, and a 40 MHz clock oscillator (U400,

crystal CR400, and associated components) which drives both processors.

13

Page 14

THEORY OF OPERATION

Digital Signal Processor (DSP) PCB (continued)

Signal Path

The signal path through the system takes the following route(s):

For analog signals, the L/R stereo pair is introduced from the source via the input cable from the

Input/Output board and the 14-pin connector J9 [schematic sheet 1, A-D8]. Each signal is

received pseudo-differentially by op-amp U105 [B/C6] and associated components and -6 dB of

gain is applied to match with the maximum in/out signal level of the codec (1Vrms).

Digital S/PDIF input signals enter the DSP board at J9 pin 10 [B8] (which come directly from a

S/PDIF signal source selected from one of four possible inputs on the I/O board), the signal is

routed directly to the codec U100 [C4] via a network of components (D1 [B5] and surrounding)

designed to clamp and filter ESD transients.

The codec takes in either the pair of analog inputs, or the single S/PDIF digital input, and outputs

three digital signals (data, bit_clock, and frame_clock, as described earlier). Since the codec

runs on 5V and the DSPs run on 3.3V, any signals passing between them must be level-shifted

via the buffers U101 [D5] and U102 [D3].

Without going into a lot of detail, DSP1 handles (mostly) Dolby® Digital (AC-3) decoding and

Videostage® 5 processing and DSP2 handles (mostly) equalization. With the signal processing

complete, DSP2 formats the six output channels into a single serial bitstream and sends this

back to the output side of the codec U100. The analog buffers following the codec (U103, U104

and associated components) do three things:

• Remove the 2.3VDC reference voltage from the codec’s outputs. The codec is a

single supply (+5V) device and references any of its internal analog signals to a

reference voltage at approximately 2.3V, about one-half the +5V supply voltage.

• Reference the signal to the amplifier ground, not the local ground. The power amps are single

ended and are referenced to their own local ground on the amp PCB, which is not the same

as the local ground at the codec on the DSP PCB. Amplifying the differences between the

two grounds will produce audible hum in the output speakers.

• Provide enough gain to increase the output signal for output to the amplifier board.

The signals leave the codec itself at about 1Vrms full-scale, this is amplified up to about

6Vrms full-scale by the output buffers.

Power-Up Sequence

At power-up, all of the microcontroller ports are in a high impedance state, which means that:

• The amplifier mute lines are held low, muting the power amps.

• The 3.3V regulated supply is disabled, reducing the demand on the +20V supply until

things have stabilized.

• The DSP reset line is held low, holding the DSPs in reset.

14

Page 15

THEORY OF OPERATION

Digital Signal Processor (DSP) PCB (continued)

Power-Up Sequence (continued)

The microcontroller proceeds to:

• Set up its I/O ports.

• Print out a “reset” message on the TTY output.

• Program the codec and verify that it responds.

• Retrieve system variables from nonvolatile memory and print out the “power_cycle” and

“eq” variables.

• Boot the DSPs, and wait for them to respond.

• Pass over system variables to the DSPs.

• Print out any appropriate error messages.

• Unmutes the power amplifiers, then unmutes the DSPs.

At this point, normal signal processing commences. It should take no more than 1.5 seconds

from the time power is applied until the time audio appears at the speaker outputs.

Power-Down Sequence

Upon receiving the “off” command from the head-end, the microcontroller;

• Mutes the DSPs.

• Mutes the power amplifiers.

• Powers down the codec and the DSPs.

• Stores system variables in EEPROM.

And then monitors the voltage level at the turn-on input. When it sees a low to high transition, it

resets itself as if the power had just come on.

Detailed Theory of Operation (see schematic diagram SD256431)

Digital Signal Processor (DSP) Board, Sheet 1 of 4

Sheet 1 of 4 shows the analog input buffers, codec’s power supply, analog output buffers and

some “glue logic” around the codec. The analog input buffers consist of op-amp U105 [B/C6] and

associated components. The ratio of R102 (and R107) to R100 sets the gain; -6 dB from J9 to

the input of the codec. The dual-diodes D100 [D7], D102 [C7], and D104 [B7] are there to clamp

ESD discharges into J9. The filter capacitors C100 [D7], C105 [C7], etc., are present to filter off

RF picked up by the input cable.

The output signal from the buffer is ground referenced, but the codec’s analog inputs are biased

at about 2.3V. C104 [C6] is required to AC-couple the signal from the buffer into the codec. R103

and D103 are present to prevent transients from the op-amp (±12V rails) from overdriving and

perhaps damaging the codec (5V rail). R104 and C102 [C6] are an EMI filter to prevent any RF

leaking from the codec from getting outside the metal EMI shield. The codec is located under the

shield, while the input buffer is not.

15

Page 16

THEORY OF OPERATION

Detailed Theory of Operation (see schematic diagram SD256431)

Digital Signal Processor (DSP) Board, Sheet 1 of 4 (continued)

The S/PDIF input enters the DSP board at J9 pin 10 [B8] and is routed to the codec by means of

C151, R1, R2, D1, C1, C7 and R5 [B5]. C151 AC couples the digital S/PDIF signal, and R1

terminates the input with 75 Ohms. R2 and D1 clamp the input (a typical S/PDIF input is about

500 mVpp into a 75 Ohm load). C1 AC couples the signal at D1 (which is ground referenced) to

the codec input (which will be biased at about 2.3V when the S/PDIF receiver is working). R5

and C7 are an EMI filter designed to prevent RF from leaking outside the shield.

The codec’s power supply consists of U1 [A5] and associated components. R10 and R11 are

power resistors designed to drop the voltage at the voltage regulator’s input, for reducing the

power dissipation of the voltage regulator itself.

D2, D3, and R4 [A5/6] are used to draw a little current from the +12V regulated supply when the

power supplies start to sag severely, as they will at low AC line and heavy amplifier load. The

+12V regulator is fed from the +40V unregulated supply and has considerably more headroom

than the +5V regulator fed from the +20V supply. Also fed from the +20V supply is the 3.3V

switching regulator, which tends to draw more current as its input voltage drops (it delivers a

fixed amount of power, at a fixed conversion efficiency). So, as the +20V supply starts to sag,

the current load on it actually starts to increase, which tends to make it sag more.

The +5 volts supplied by the regulator is sent to two different components; the codec U100 [C4]

and the microcontroller U202 [sheet 2, C5] and associated components. Since the regulator is

located outside the EMI shield and the +5V supply line might be carrying EMI (Electro Magnetic

Interference), ferrite beads L1 and L2 [A4] were placed in series with each of the supply lines.

L1 and R3 [A4] serve to isolate the two different power supply pins on the codec (the “analog”

+5VA from the “digital” +5VD). C5 and C6 are bypass capacitors placed directly under the

codec.

Codec glue logic

U101 [D5] is a 74LCX244, a 3.3V IC that can tolerate 5 volts on its inputs. It’s used to convert

5V to 3.3V logic signals.

U102 [D3] is a 74ACT244, a 5V part that understands the logic levels used by the 3.3V IC. It’s

used to convert the 3.3V logic signals to 5V logic signals.

U106 [A7] is a flip-flop, used to convert a falling edge (from the codec) to a narrow pulse (to the

DSP). This removes a potential timing ambiguity.

R192 [D6] (and others) is a 75 Ohm series resistor used to series-terminate some of the high

speed logic signals, to preserve edge fidelity at the receiving end.

R6 and R7 [C3] comprise a low performance 5V to 3.3V shifter. Using such large series resistances in the presence of even moderate amounts of stray and input gate capacitance slows

down the signal’s edge, but this particular signal is very low bandwidth.

16

Page 17

THEORY OF OPERATION

Detailed Theory of Operation (see schematic diagram SD256431)

Digital Signal Processor (DSP) Board, Sheet 1 of 4 (continued)

Analog output buffers consists of U103, U104 [B-D2], and associated components. Gain is set

by the ratio of R132 to R131 [D2]; to about 6x. Note that the ratio of R189 to R188 [D2] must

match. Gain of the output buffers = (codec_out - codec_reference) - amp_ground_sense).

Sheet 2 of 4 (microcontroller and associated components)

The bass and treble control signal enters the DSP board at J9 pins 1 and 2 [D8]. This signal is

generated on the Input/Output board and connected to a pair of microcontroller ADC inputs at

U202 [C5] pins 19 and 20. All of these connections are EMI filtered.

Thermistor R207 [C8] is mounted on the topside of the DSP PCB. When the DSP PCB temperature rises to about 70 degrees C, the microcontroller starts turning down the output volume by

programming the codec, effectively controlling the maximum temperature inside the amplifier

enclosure and preventing damage.

R211 [D7] connects the signal “CMOUT” to one of the microcontroller’s ADC ports. CMOUT is

the codec’s 2.3V reference voltage. This voltage is monitored as one of the codec’s “vital signs”,

if out-of-bounds, the microcontroller reboots the codec.

R208 [C8] connects the 3.3V power supply to one of the microcontroller’s ADC ports. The

microcontroller has the ability to turn the 3.3V regulator on and off, thus having the ability to

check that the 3.3V supply is within limits. The microcontroller needs to be able to turn the 3.3V

off at power down to avoid draining the +20V supply faster than the -20V supply. If the upper rails

sag faster than the lower rails, the bass amp will unmute causing a “thump” to be heard (about 5

seconds after power down).

R44 throught R48 [I/O schematic sheet, E2] sum together all the satellite outputs and feeds them

out through J4-5 [I/O sheet, E4] to DSP J9-5 [A7] to one of the microcontroller’s ADC ports at

U202 pin 25. The microcontroller watches for grossly excessive DC offset at any of the speaker

outputs. If DC is detected the microcontroller will shut down the AC power.

U201 [B6] is the non-volatile memory. Read/write access is via the 2-wire serial I2C buss.

U200 [D6] generates a 250msec reset pulse for the microcontroller whenever the +5V supply

drops below 4.75V.

D200 [A5] forms a simple level translator. The CLIP signal is generated on the amp PCB whenever one of the satellite power amplifiers starts to clip. It’s an open-collector output that pulls

down to -12V. D200 level shifts this signal from -12V through +12V, to 0V through 5V. This levelshifted signal goes to both the microcontroller and DSP2 (via a 5V to 3.3V buffer). As it turns out,

the microcontroller ignores this signal, but DSP2 turns down the system volume until the CLIP

signal disappears, then lets the volume drift back up to the original setpoint.

Q204 and Q201 [B3] form a simple S/PDIF detector. Q204 sets the bias for Q201 such that it is

just barely off. An S/PDIF signal arriving at Q201 will cause C216 to be discharged, causing the

voltage at C216 to drop from 5V to something closer to ground. This voltage is connected to one

of the microcontroller’s ADC ports and is sampled periodically by the microcontroller.

17

Page 18

THEORY OF OPERATION

Detailed Theory of Operation (see schematic diagram SD256431)

Digital Signal Processor (DSP) Board, Sheet 2 of 4 (continued)

Q200 [C2] allows the microcontroller to pull down on the DSP’s reset line. When the

microcontroller first boots, all of its output ports are set to a high impedance state. Q200 remains

turned on by R252, which holds the DSPs in reset, until the microcontroller is ready to boot the

DSPs.

R246, R248, [C/D2] etc. connect several of the microcontroller output ports to the MUTE inputs

on the power amplifiers. The mute signals are organized into three groups; (bass, left, right),

(center) and (left_surround, right_surround), corresponding to the three speaker modes the

product supports. Each line is EMI filtered. Pulldown resistors R813, R814 and R815 [amplifier

schematic sheet 2, [D5] guarantee that the signals will assume a LOW state i.e., muted) at

power-up.

Sheet 3 of 4 (DSPs)

There are only two DSPs, but since they each have 240 pins, they’ve been broken into several

different schematic symbols so as not to clutter the page:

- address and data busses.

- buss control, and miscellaneous.

- link ports (sheet 4).

- power and ground (sheet 4).

Without going into any detail, the DSPs are connected to each other and to the boot PROM

U401 [C2], as follows:

- address buss connected to address buss.

- data buss connected to data buss.

- buss control signals connected to buss control signals.

- power pins connected to 3.3V power plane.

- ground pins connected to ground plane.

The large number of interconnects and the fact that each signal has extremely fast rise times

(2 nsec), required the use of a four layer PCB. One of the inner layers is a (more or less) solid

ground plane; the other is used for a power plane, plus additional signal interconnect where

required.

U400 [B2] and associated components form a third-overtone 40 MHz oscillator. There are two

buffered outputs; one drives both DSPs and one is connected to the test connector J401 [B1],

which was used to help debug the prototype PCBs but is no longer loaded.

Sheet 4 of 4

U500 [C/D4] and associated components form a 3.3V regulated supply. C500 and L500 [C5] are

the regulator’s output filter. R500 and C501 [D4] set the regulator’s switching frequency (about

100 kHz). C503 [C4] is the “bootstrap” capacitor required for establishing an internal bias voltage

higher than the supply voltage (for turning on the internal N-channel MOSFET switch). C515,

L501, and C505 [C4] prevent switching harmonics from leaking back out onto the raw DC input

voltage. R501, C507, C508 [C3], etc., are feedback and compensation components.

18

Page 19

THEORY OF OPERATION

Detailed Theory of Operation (see schematic diagram SD256431)

Digital Signal Processor (DSP) Board, Sheet 4 of 4 (continued)

C506 [D3] is the “soft-start” capacitor, which forces the regulator to start up slowly when power

is first applied, thus limiting the inrush current. R510 and Q500 [D3] allow the “soft-start” pin to be

pulled low, shutting off the regulator. The 3.3V supply is turned off as part of the normal power

down sequence.

Detailed Theory of Operation (see schematic diagram SD256421)

Power Amplifier Board

Note: Unless otherwise noted, refer to the schematic diagrams for the power amplifier board for

the following information. The references in brackets [ ] are the schematic sheet and grid coordinates for the component.

Sheet 1 of 2

The satellite channel power amplifiers are a discrete high efficiency Class-G design. Maximum

power is 35 W per channel into 4 Ohms at less than 0.1% THD. In Class-G operation the amplifiers are powered by two different power supplies depending on the amplitude of the signal input.

When the audio amplitude is low, the amplifiers run off of the lower supply rails, but during musical peaks they switch to the higher supply rails. Efficiency is typically increased from 20% to

40% and power dissipation is reduced by a factor of 2.5.

Bass Channel Power Amplifier

Audio input is applied to the amplifier PCB at pin 12 of connector J700 [amplifier schematic sheet

2, D7] and is AC coupled through C727 [D8]. The amplifier is controlled by negative feedback to

op-amp U707 [C6], which is configured as an inverting amplifier with a voltage gain of 12 (21.6

dB). With no signal applied to the input, all output power devices are biased off. For a negative

input signal, pin 1 goes high and conducts driver transistor Q713 [D6]. Collector current is pulled

through R707 and R774 [D6] until the voltage drop across R774 reaches about 1 Volt, at which

time the high gain darlington transistor Q718 [D6] begins to conduct emitter current through

power diode D711 [D5/6], which connects to the +20VDC supply.

Collector current from Q718 [D6] flows through the speaker load and the voltage at this node is

regulated by feedback to the op-amp via resistor R789 [D7].

When the audio output voltage approaches the 20VDC power supply rail, output transistor Q718

begins to saturate and conducts much more base current than the normal maximum of 5mA. At

approximately 8mA the voltage drop across 75 Ohm resistor R707 [D6] exceeds 0.6V and small

signal transistor Q714 [D6] begins to conduct. This in turn conducts Class-G Darlington transistor Q715 [D6], which turns on the 40VDC power supply and reverse biases power diode D711

[D6], effectively turning off the 20VDC supply. During this period, the waveform at the collector of

Q715 resembles the audio output signal plus the saturation drop of Q718 and Q715 is operated

in the active region (not as a switch), thus sharing the power dissipation.

Crossover distortion and switching transients are not an issue due to the relatively low bandwidth of the amplifier (less than 250 Hz) and the ability of the bass module to roll off high frequency distortion products. Crossover distortion is less than 0.5% at 200 Hz, 1 Watt.

19

Page 20

THEORY OF OPERATION

Detailed Theory of Operation (see schematic diagram SD256421)

Power Amplifier Board, Bass Channel Power Amplifier (continued)

Short circuit protection is provided through current sense resistor R822. At greater than 16A,

Q726 conducts and triggers the one-shot op-amp circuit U707, pins 5, 6 and 7, and mutes the

amp for several seconds. The amp will cycle in and out of mute until the short circuit is removed.

Satellite Power Amplifiers

Each of the five satellite amplifiers are operated in Class-G configuration and consist of a 50W,

Class AB monolithic integrated circuit (in a multiwatt-15 package, TDA7294). The amplifier is

short circuit and thermally protected. External to this IC is a pair of TO-220 Darlington transistors

(the same as used in the discrete bass amplifier) to perform the Class-G power supply switching. The following detailed operation is described for the left surround channel, however the other

four channels would be the same.

The surround signal enters the amplifier board at J700 pin 11 [sheet 2, D7] and is applied to

capacitor C717 [C5] and couples to the non-inverting input of the TDA7294 amplifier IC. It is

configured as a non-inverting amplifier with a voltage gain of 4 (12 dB). The output stage consists of a pair of MOSFET transistors and the positive FET must develop gate drive well above

the supply voltage and hence there is a bootstrap cap, C716 [C3], between pin 6 and 14.

With low amplitude signal, the amplifier runs off of the 20VDC rails through power diodes D704

[D3] and D710 [C3]. The power supply voltage at pin 13 is subtracted by 5.6V zener diode D703

[D3] and divided down by the ratio of 1 + R731/R732 [D3/4]. This bias voltage sets the threshold

at which transistor Q703 [D4] turns on. When the audio or the input to the amplifier exceeds the

voltage at the emitter of Q703 by two diode drops, D716 [C4] and Q703 conduct. In turn this

conducts small signal transistor Q704 [D4] which in turn conducts output transistor Q705 [D3].

A negative feedback loop is established that prevents Q705 from turning completely on and the

voltage at the collector of Q705 resembles the audio output wave form plus several volts of

saturation headroom. Q705 operating in the active region (instead of as an on/off switch), results

in shared power dissipation between the transistor and the power amplifier IC. The phase lag

created by the input network R753 and C745 [C4] allows the power circuit to switch on slightly

ahead of the power amplifier at high frequencies (above 8 kHz) to minimize turn-on glitch.

Power Amplifier Board, Sheet 2 of 2

Power Supplies and Connectors

AC power is sent to the amplifier board at J702 [A/B5] from the secondary of the power transformer [I/O schematic sheet, D1] located in the center cutout of the Input/Output board. The raw

AC is recitified by bridge rectifiers B700 and B701 [A/B4]. The filtered DC from B701 is passed

through fusible resistors R713 and R714 [B3] and output as +40V fused. These 40V rails are

used as the higher rail voltage for the Class G amplifier output devices as shown on amplifier

schematic sheet 1. The +40Vdc fused outputs are also are regulated down to +12Vdc by regulators U708 and U709 [B/C2]. This +12Vdc is fed to both the DSP board through J700 pins 2 and 6

and to the Input/Output board at J701 pins 13 and 15 [A7]. The filtered DC from B700 provides

+20Vdc and is used as the lower rail voltage for the amplifier Class G output devices.

20

Page 21

THEORY OF OPERATION

Power Amplifier Board, Sheet 2 of 2 (continued)

Outputs to the DSP board from the amplifier board at J700 also include the +20Vdc at pin 4

through fusible resistor R704 [C6] to create +20 fused. The mute and standby signals for the

power amplifiers are brought into the amplifier board at J700 on pins 15, 16 and 18.

The audio inputs to the power amplifier board are applied at J700 [C/D7] pins 8-12 and 14 via a

cable running from J8 of the DSP board. These inputs are then applied to the inputs of the

individual amplifier channels as shown on amplifier schematic sheet 1.

The outputs of all six of the amplifier channels are brought out of the amplifier board at J701 pins

2, 3, 4, 6, 8 and 10. These outputs are fed back to the Input/Output board at J22 by a cable. The

bass channel output is also monitored and output to the Input/Output board as the PROTECT

signal at J701 pin 11. This PROTECT signal is applied to the Input/Output board at J22 pin 11

[Input/Output board schematic, D2]. It is passed to a window comparitor made up of transistors

Q1 and Q2. The output of this comparitor is the signal BUF_PROTECT. This signal is sent to the

microcontroller U5 [C4] at pin 3. In the event of a failure, this BUF_PROTECT signal will cause

the microcontroller to send out a shutdown command on the Amp_Power pin 11 of the

microcontroller to shut down power to the amplifier.

DISASSEMBLY/ASSEMBLY PROCEDURES

Note: Refer to figures 1, 2 and 3 for the

following procedures.

1. Heatsink Removal

1.1 Using a Phillips-head screwdriver,

remove the four screws (20) that secure the

heatsink (16) to the chassis (8).

1.2 Lift the heatsink straight up just far

enough to be able to reach the amplifier

board (9 & 10) cables. Disconnect these two

cables. The amplifier board is mounted to the

underside of the heatsink. Lift the heatsink

clear of the chassis.

2. Heatsink Replacement

2.1 Align the heatsink (16) with the chassis

base (8). Reconnect the two cables removed

in step 1.2. Slide the heatsink down over the

chassis until it is flush with the chassis end

plates.

3. Input/Output Board Removal

3.1 Perform procedure 1.

3.2 Disconnect the two cables that run to the

power transformer (4).

3.3 Using a nut driver, remove the one hex

head bolt (2) that secures the power transformer to the chassis (8). Lift the power

transformer out of the chassis. Lift the power

transformer gasket out of the chassis.

3.4 Using a Phillips-head screwdriver,

remove the four screws (1) that secure the

input/output board (6) to the chassis. Lift the

input/output board straight out of the chassis.

4. Input/Output Board Replacement

4.1 Align the input/output board (6) with the

chassis (8) and secure it in place using the

four screws (1) removed in step 3.4.

2.2 Secure the heatsink to the chassis using

the four screws (20) removed in step 1.1.

4.2 Place the power transformer gasket into

the chassis.

21

Page 22

DISASSEMBLY/ASSEMBLY PROCEDURES

4.3 Align the power transformer (4) with the

chassis and secure it in place using the hex

head bolt (2) removed in step 3.3.

4.4 Perform procedure 2.

5. DSP Board Removal

5.1 Perform procedure 1.

5.2 Disconnect the cable that runs from the

Input/Output board (6) to the DSP board (5).

Disconnect the cable that runs from the

amplifier board (14) to the DSP board.

5.3 Using a Phillips-head screwdriver,

remove the four screws (1) that secure the

DSP board to the chassis (8). Lift the DSP

board out of the chassis.

6. DSP Board Replacement

8. Amplifier Board Replacement

8.1 Place the thermal conducting insulating

tape strips (15) onto the heatsink (16) where

the amplifier board (14) output devices will

be located.

8.2 Align the amplifier board with the

heatsink and secure it in place using the two

standoffs (13) removed in step 7.3.

8.3 Align the tension clamp (12) with the

amplifier board and secure it in place using

the two screws (11) removed in step 7.2.

8.4 Perform procedure 2.

6.1 Align the DSP board (5) with the

chassis (8) and secure it in place using

the four screws (1) removed in step 5.3.

6.2 Connect the cable that runs from the

DSP board to the input/output board (6).

Connect the cable that runs from the DSP

board to the amplifier board (14).

6.3 Perform procedure 2.

7. Amplifier Board Removal

7.1 Perform procedure 1.

7.2 Using a Phillips-head screwdriver,

remove the two screws (11) that secure the

tension clamp (12) to the amplifier board

(14). Lift the tension clamp off of the amplifier

board.

7.3 Using a nut driver, remove the two

standoffs (13) that secure the amplifier

board to the heatsink. Lift the amplifier board

out of the heatsink (16).

22

Page 23

TEST PROCEDURES

Test Setup

Note: The commands used in the following

tests can either be issued by an IR remote

control or PC generated (using hyperterminal) through the RS-232 (TAP) interface

at J9. Refer to the IR commands table in the

appendix of this manual. There is a built-in

remote receiver located on the Input/Output

PCB behind the IR sensor input connector

(J10). If you aim the IR remote at this connector, the IR command will be received by

IR sensor U11. Refer to the Input/Output

PCB schematic sheet for more information.

The following test procedures use TAP

commands issued by an IBM compatible PC.

The TAP commands are used to emulate

commands that would normally be sent by

an IR remote control, with the exception of

the max volume command (S31101), which

is a Lifestyle® Smart Speaker command. To

set the amplifier to full volume using an IR

remote, hold the volume up button for 10

seconds.

Setup instructions for the PC and fabrication

instructions for the TAP cable are located in

the appendix.

Equipment Required:

Audio Signal Generator

S/PDIF Analog to Digital Converter

CAT-5 Cable with RJ-45 connectors

75 Ohm RCA to RCA S/PDIF video cable

Bose® Digital Source plate

IBM Compatible PC w/Windows

TAP Cable

Digital Multimeter

Audio Distortion Analyzer

5 - 8 Ohm, 50 Watt load resistors

1 - 4 Ohm, 150 Watt load resistor

Note: Refer to figures 7 and 8 for the following test setup information.

®

1. Connect the signal generator inputs to the

left and right Music Audio inputs at J6 pins

1, 2, 4 and 5.

2. Place the balanced/unbalanced switches

(S1) to the unbalanced (single-ended)

position. Use a piece of wire to jumper

the negative inputs (J6 pins 2 and 5) to

ground at J6 pin 3.

3. Connect the TAP cable to the amplifiier at

the RS-232 Serial Data Input jack at J9.

Connect the other end to the IBM compat ible PC comm port. TAP cable fabrication

and IBM PC setup are outlined in the

appendix of this manual.

4. Connect an 8 Ohm load resistor to the

satellite speaker channels at J12, J13 and

J14. Connect the 4 Ohm load resistor to

the bass channel speaker output at J15.

5. Set the speaker selector DIP switch (S4)

position 1 to the UP position. Set positions

2, 3 and 4 to the DOWN position. Cycle

the AC mains power to allow this change

to go into effect. This will select the Jewel

Cube® satellite EQ for the following tests.

6. Issue the following commands to the

amplifier under test via hyperterminal.

These commands will put the TA-1 ampli fier into the proper mode for testing.

Note: These commands are case

sensitive.

- ICA (selects music audio inputs)

- I78 (DRC off)

- IF4 (film EQ off)

- IA0 (1-to-5 off)

- IDA (bass boost to mid)

- IB2 (treble boost to mid)

- ID0 (surround mode)

- IF7 (center channel level to mid)

- IF9 (surround channel level to mid)

- S31101 (sets amplifier volume to max)

23

Page 24

TEST PROCEDURES

Music Audio Tests

1. Front Channel Audio Tests

1.1 Set up the amplifier under test as outlined

in the test setup.

1.2 Apply a 100 mV, 1 kHz signal to the left

music audio input at J6 pins 1 and 2.

1.3 Reference a dB meter to the input level.

1.4 Measure the output level at the left front

speaker output at J12 pins 3 and 4. It should

be +34.6 dB + 1.5 dB.

1.5 Apply a 100 mV, 200 Hz signal to the left

music audio input at J6 pins 1 and 2.

1.6 Reference a dB meter to the input level.

1.7 Measure the output level at the left front

speaker output at J12 pins 3 and 4. It should

be +37.1 dB + 1.5 dB.

1.8 Apply a 100 mV, 12 kHz signal to the left

music audio input at J6 pins 1 and 2.

1.15 Apply a 1.8 Vrms, 1 kHz signal to the

left music audio input at J6 pins 1 and 2.

1.16 Measure the compressor signal distortion level at the left front speaker output at

J12 pins 3 and 4. It should be < 2.0%

THD+N.

1.17 Repeat steps 1.2 to 1.16 for the right

music audio input, applying the signal at J6

pins 4 and 5 and measuring the output at

the right front speaker output at J12 pins

1 and 2.

2. Center Channel Audio Tests

2.1 Set up the amplifier under test as out-

lined in the test setup.

2.2 Apply an in-phase, 100 mV, 1 kHz signal

to the left and right music audio inputs at J6.

2.3 Reference a dB meter to the input level.

2.4 Measure the output level at the center

channel speaker output at J13 pins 1 and 2.

It should be +33.7 dB + 1.5 dB.

1.9 Reference a dB meter to the input level.

1.10 Measure the output level at the left front

speaker output at J12 pins 3 and 4. It should

be +39.0 dB + 1.5 dB.

1.11 Apply a 50 mV, 1 kHz signal to the left

music audio input at J6 pins 1 and 2.

1.12 Measure the small signal distortion

level at the left front speaker output at J12

pins 3 and 4. It should be < 0.5% THD+N.

1.13 Apply a 600 mV, 1 kHz signal to the left

music audio input at J6 pins 1 and 2.

1.14 Measure the large signal distortion

level at the left front speaker output at J12

pins 3 and 4. It should be < 0.2% THD+N.

2.5 Apply an in-phase, 100 mV, 200 Hz

signal to the left and right music audio

inputs at J6.

2.6 Reference a dB meter to the input level.

2.7 Measure the output level at the center

channel speaker output at J13 pins 1 and 2.

It should be +37.7 dB + 1.5 dB.

2.8 Apply an in-phase, 100 mV, 12 kHz

signal to the left and right music audio

inputs at J6.

2.9 Reference a dB meter to the input level.

2.10 Measure the output level at the center

channel speaker output at J13 pins 1 and 2.

It should be +39.8 dB + 1.5 dB.

24

Page 25

TEST PROCEDURES

2.11 Apply an in-phase, 50 mV, 1 kHz signal

to the left and right music audio inputs at J6.

2.12 Measure the small signal distortion

level at the center channel speaker output

at J13 pins 1 and 2. It should be < 0.5%

THD+N.

2.13 Apply an in-phase, 600 mV, 1 kHz

signal to the left and right music audio

inputs at J6.

2.14 Measure the large signal distortion

level at the center channel speaker output

at J13 pins 1 and 2. It should be < 0.2%

THD+N.

2.15 Apply an in-phase, 1.8 Vrms, 1 kHz

signal to the left and right music audio

inputs at J6.

2.16 Measure the compressor signal distor-

tion level at the center channel speaker

output at J13 pins 1 and 2. It should be

< 2.0% THD+N.

3. Surround Channel Audio Tests

3.1 Set up the amplifier under test as out-

lined in the test setup.

3.2 Apply a L= -R, 100 mV, 1 kHz signal to

the left and right music audio inputs at J6.

You can do this by inverting the phase of the

right channel input signal from the signal

generator.

3.7 Measure the output level at the left and

right surround channel speaker outputs at

J14. It should be +36.9 dB + 1.5 dB.

3.8 Apply a L= -R, 100 mV, 12 kHz signal to

the left and right music audio inputs at J6.

3.9 Reference a dB meter to the input level.

3.10 Measure the output level at the left and

right surround channel speaker outputs at

J14. It should be +39.2 dB + 1.5 dB.

3.11 Apply a L= -R, 50 mV, 1 kHz signal to

the left and right music audio inputs at J6.

3.12 Measure the small signal distortion

level at the left and right surround channel

speaker outputs at J14. It should be

< 0.5% THD+N.

3.13 Apply a L= -R, 600 mV, 1 kHz signal to

the left and right music audio inputs at J6.

3.14 Measure the large signal distortion

level at the left and right surround channel

speaker output at J14. It should be < 0.2%

THD+N.

3.15 Apply a L= -R, 1.8 Vrms, 1 kHz signal

to the left and right music audio inputs at J6.

3.16 Measure the compressor signal distortion level at the left and right surround channel speaker output at J14. It should be

< 2.0% THD+N.

3.3 Reference a dB meter to the input level.

3.4 Measure the output level at the left and

right surround channel speaker outputs at

J14. It should be +34.5 dB + 1.5 dB.

3.5 Apply a L= -R, 100 mV, 200 Hz signal to

the left and right music audio inputs at J6.

3.6 Reference a dB meter to the input level.

4. Bass Channel Audio Tests

4.1 Set up the amplifier under test as out-

lined in the test setup.

4.2 Apply an in-phase, 100 mV, 100 Hz

signal to the left and right music audio inputs

at J6.

4.3 Reference a dB meter to the input level.

25

Page 26

TEST PROCEDURES

4.4 Measure the output level at the bass

channel speaker output at J15 pins 1 and 2.

It should be +38.4 dB + 1.5 dB.

4.5 Apply an in-phase, 100 mV, 20 Hz signal

to the left and right music audio inputs at J6.

4.6 Reference a dB meter to the input level.

4.7 Measure the output level at the bass

channel speaker output at J15 pins 1 and 2.

It should be +19.1 dB + 1.5 dB.

4.8 Apply an in-phase, 100 mV, 200 Hz

signal to the left and right music audio inputs

at J6.

4.9 Reference a dB meter to the input level.

4.10 Measure the output level at the bass

channel speaker output at J15 pins 1 and 2.

It should be +29.9 dB + 1.5 dB.

4.16 Measure the compressor signal distortion level at the bass channel speaker output

at J15 pins 1 and 2. It should be < 4.0%

THD+N.

5. DC Offset Test

5.1 Set up the amplifier under test as out-

lined in the test setup.

5.2 With no input signal applied, measure the

DC offset level at the front, center, surround

and bass channel speaker outputs at J12,

J13, J14 and J15. It should be < 10 mVdc.

6. Output Noise Test

6.1 Set up the amplifier under test as out-

lined in the test setup.

6.2 Short out the left and right music audio

inputs at J6.

4.11 Apply an in-phase, 50 mV, 100 Hz

signal to the left and right music audio inputs

at J6.

4.12 Measure the small signal distortion

level at the bass channel speaker output

at J15 pins 1 and 2. It should be < 0.5%

THD+N.

4.13 Apply an in-phase, 230 mV, 100 Hz

signal to the left and right music audio inputs

at J6.

4.14 Measure the large signal distortion

level at the bass channel speaker output

at J15 pins 1 and 2. It should be < 0.2%

THD+N.