Page 1

5 4 3 2 1

A

CZC Confidential

D

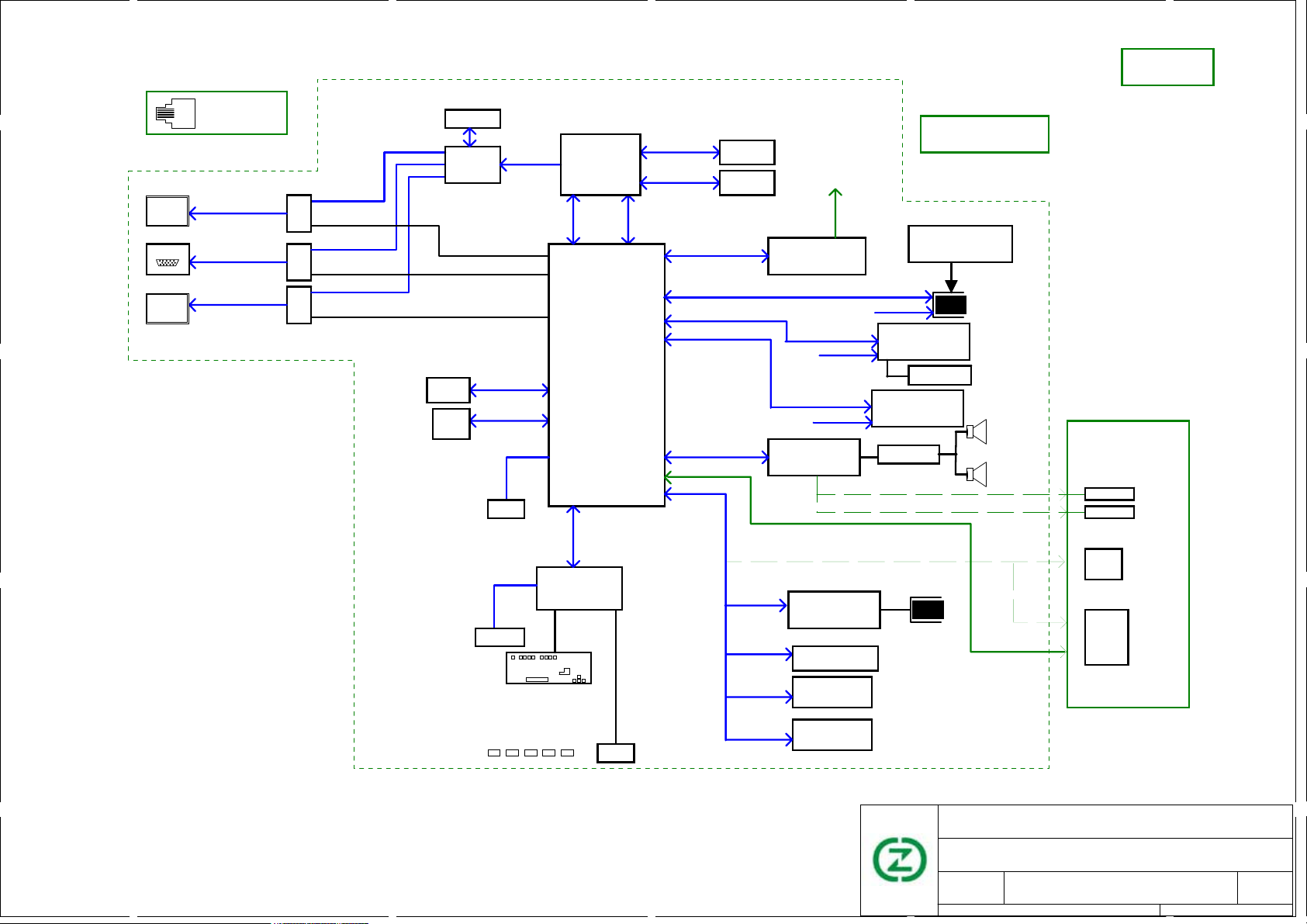

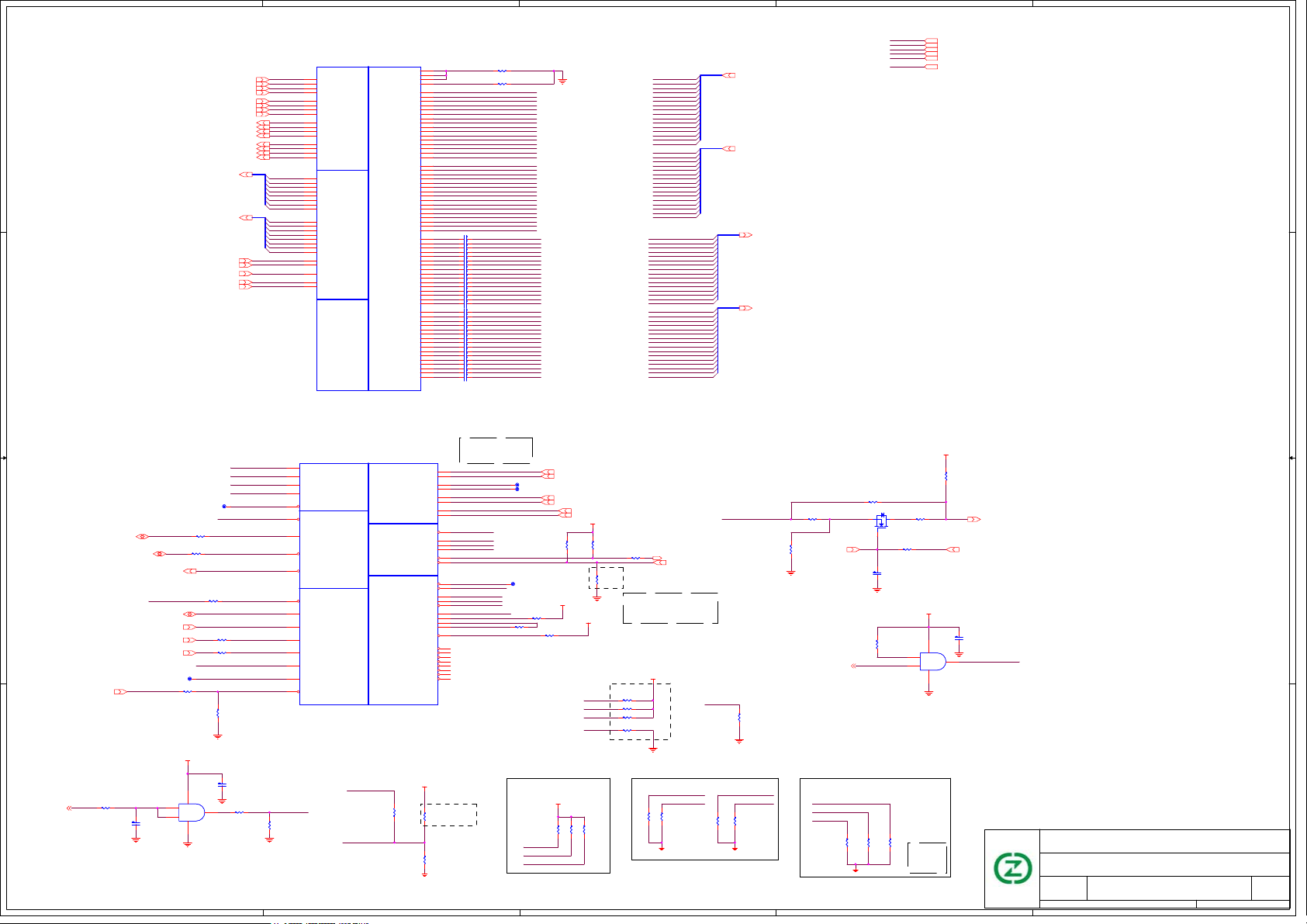

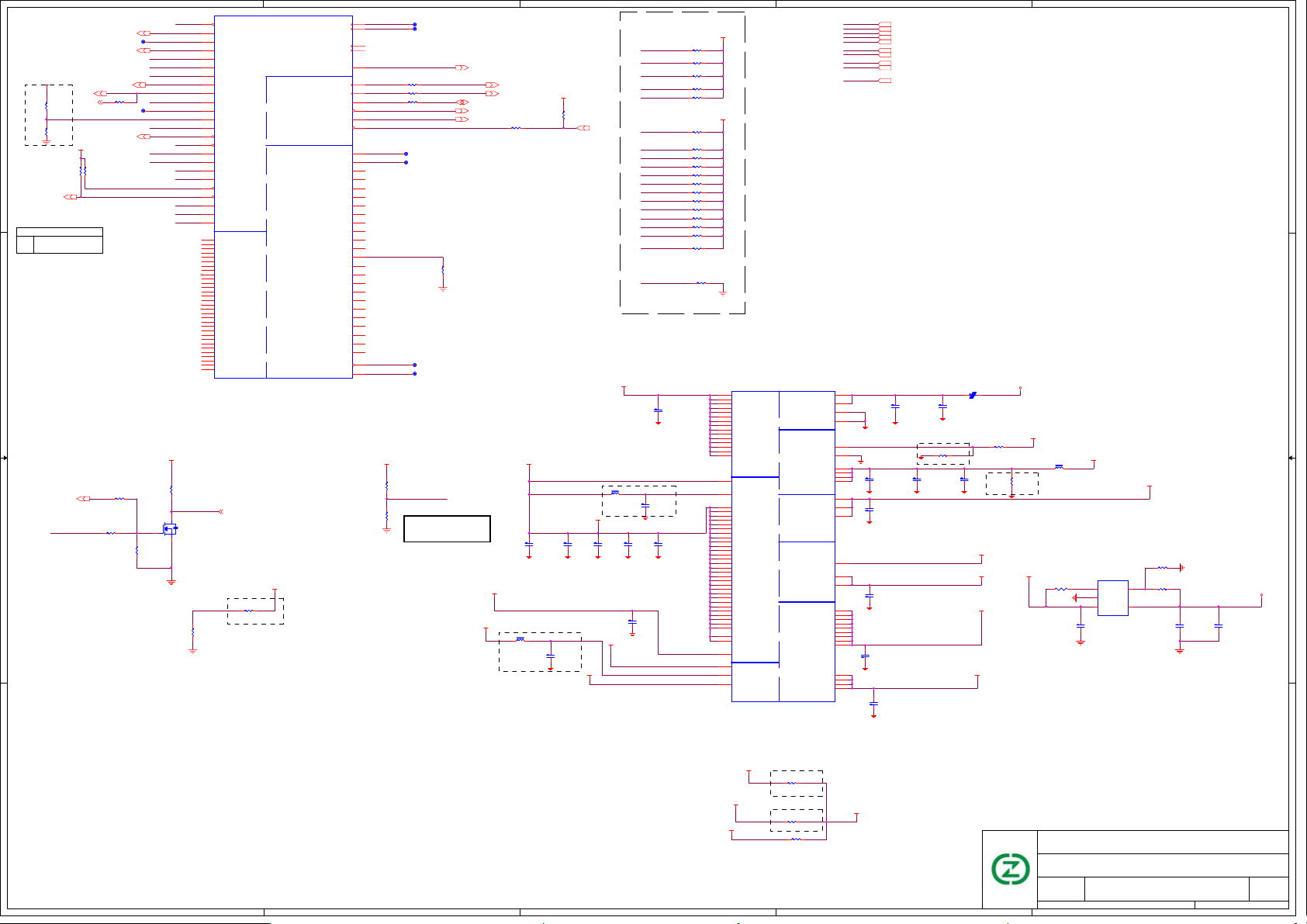

Board name: Mother Board Schematic

Project name:

CPL S01 (R48)

CZC Digital technologies Co.,LTD

1. System Block Diagram & Schematic page description;

2. Power Block Diagram & Discription;

3. Annotations & information;

Version: VerC

Start Date:JAN 6,2010

C

VerA Release Data:

4. Schematic modify Item and history;

5. Power on & off Sequence;

6. ACPI Mode Switch Timings;

7. Power On Sequence Map;

8. CLOCK Distribution;

B

Hardware drawing by:

Power drawing by:

A

Manager Sign by:

Hardware check by:

Power check by:

EMI Check by:

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A4

A4

A4

Date: Sheet

Date: Sheet

Date: Sheet

zw

zw

zw

R48 C

R48 C

R48 C

156Thursday, April 22, 2010

156Thursday, April 22, 2010

156Thursday, April 22, 2010

of

of

of

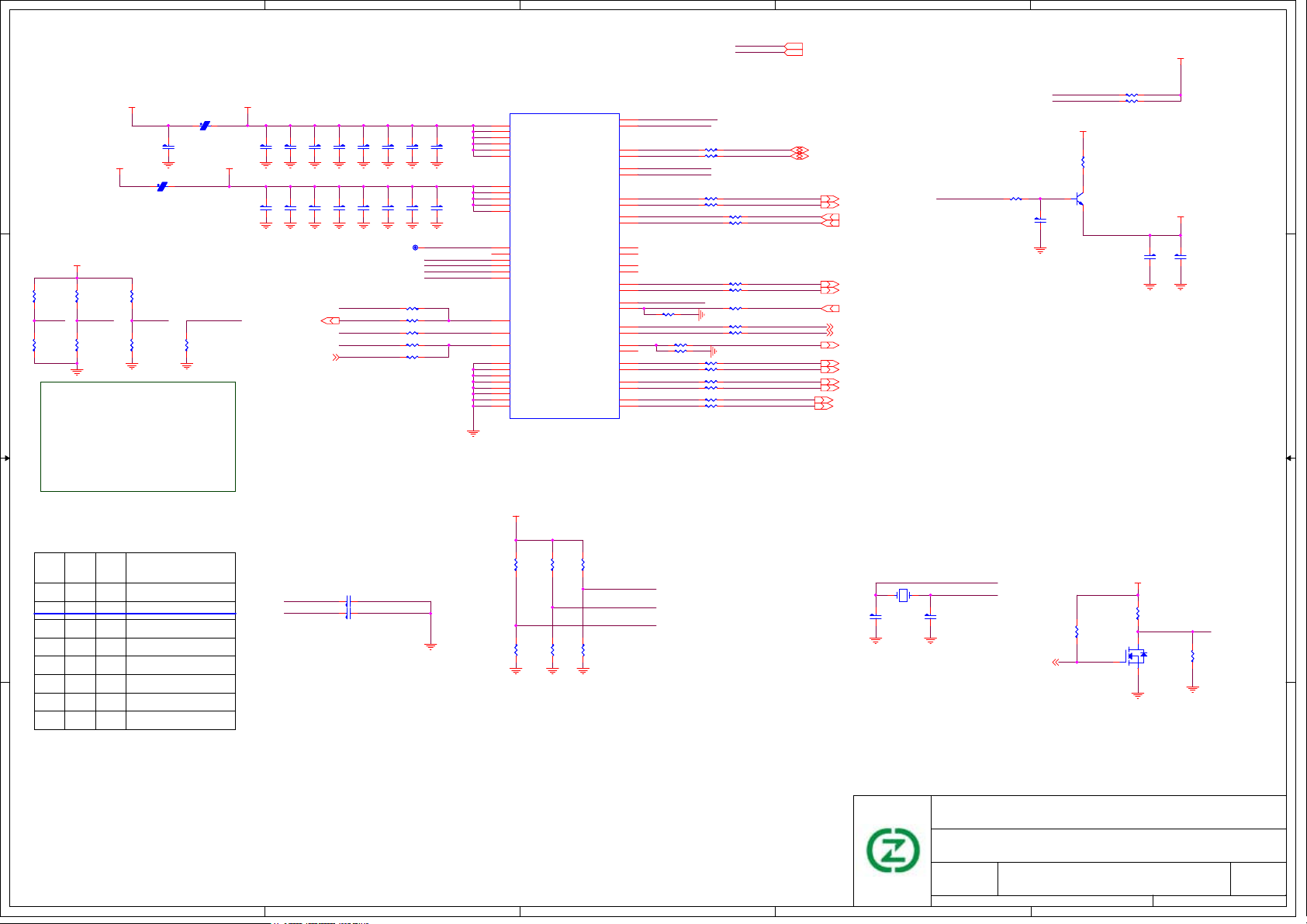

Page 2

5

A

4

3

2

1

S45 System Block Ver:A

PWR_BTN Board

D D

TFT

VGA

HDMI

RJ45 Board

MUX

MUX

MUX

LVDS

VGA

HDMI

DDR3 1GB/512M

Madison/Park

PCIE X16

LVDS

VGA

HDMI

C C

ODD

HDD

2.5"

SATA

SATA

SPI

MB

Arrandale

FDI

PCH

HM55/HM57

DMI X4

DDRIII

DDRIII

SO-DIMM 0

+V1.5,+V0.75S

SO-DIMM 1

+V1.5,+V0.75S

PCIE X1

PCIE X1

PCIE X1

PCIE X1

AZALIA LINK

SATA

To RJ45

LAN Controller

AR8131M

USB2.0

USB2.0

Azalia Codec

ALC662

QKey & LID Board

PWR Switch

R5538/TPS2231/OZ2709

USB2.0

mini PCIE Card

3G

SIM SLOT

mini PCIE

Card

AN12948A

Express Card

R

L

USB AUDIO Board

HP Out

BIOS

LPC BUS

USB2.0

SPI

B B

KB Ctrl & EC

WPC8763L

USB2.0

Cardreader

UB6238N

SD/MS/MS Pro CARD

EC Code

USB2.0

KB Matrix

USB2.0

USB Port

Camera

Mic In

USB

Port

USB

Port

+

eSATA

LED

USB2.0

BT

TP

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A4

A4

A4

Date: Sheet

Date: Sheet

Date: Sheet

R48 C

R48 C

R48 C

zw

zw

zw

of

of

of

256Thursday, April 22, 2010

256Thursday, April 22, 2010

256Thursday, April 22, 2010

A

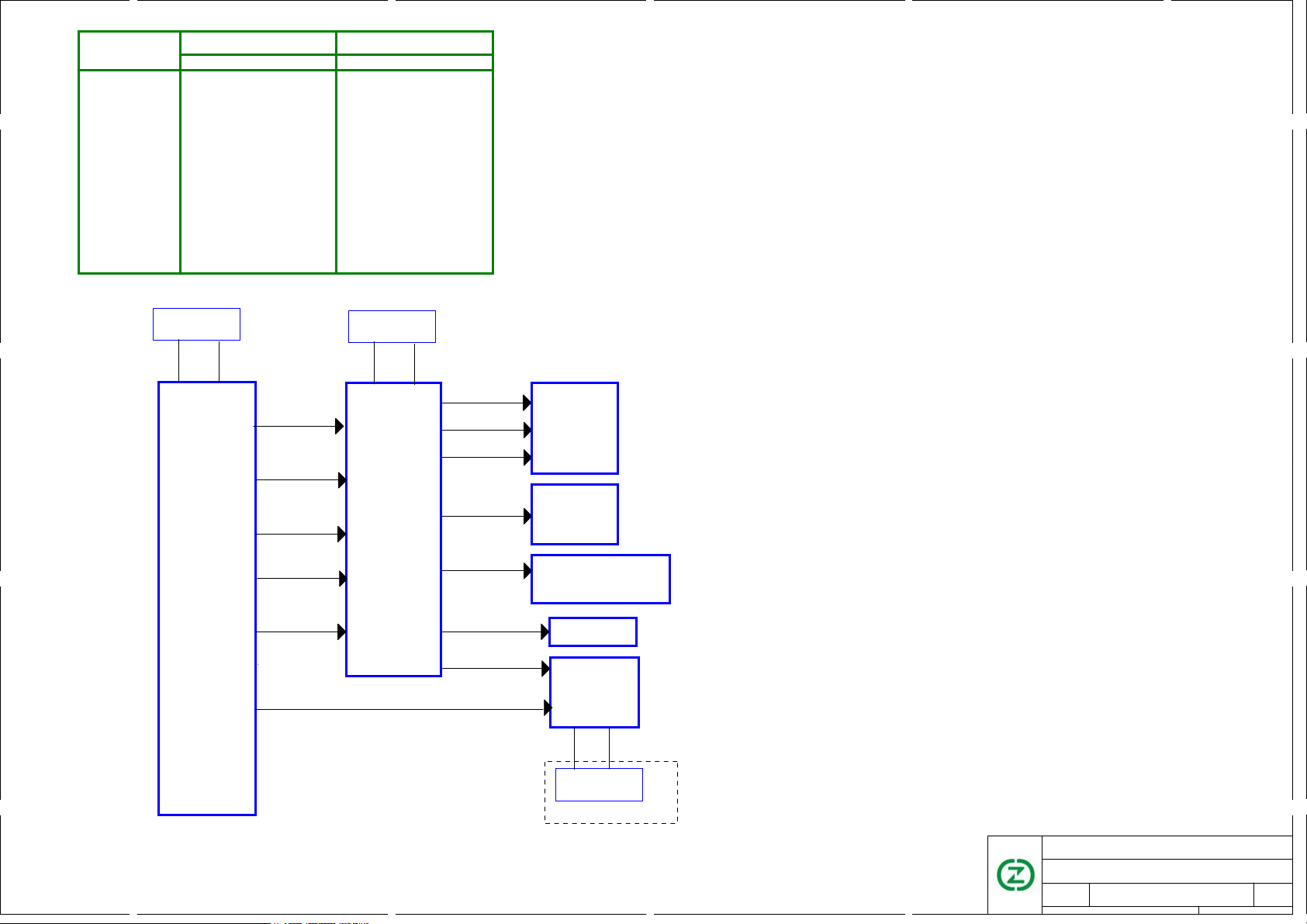

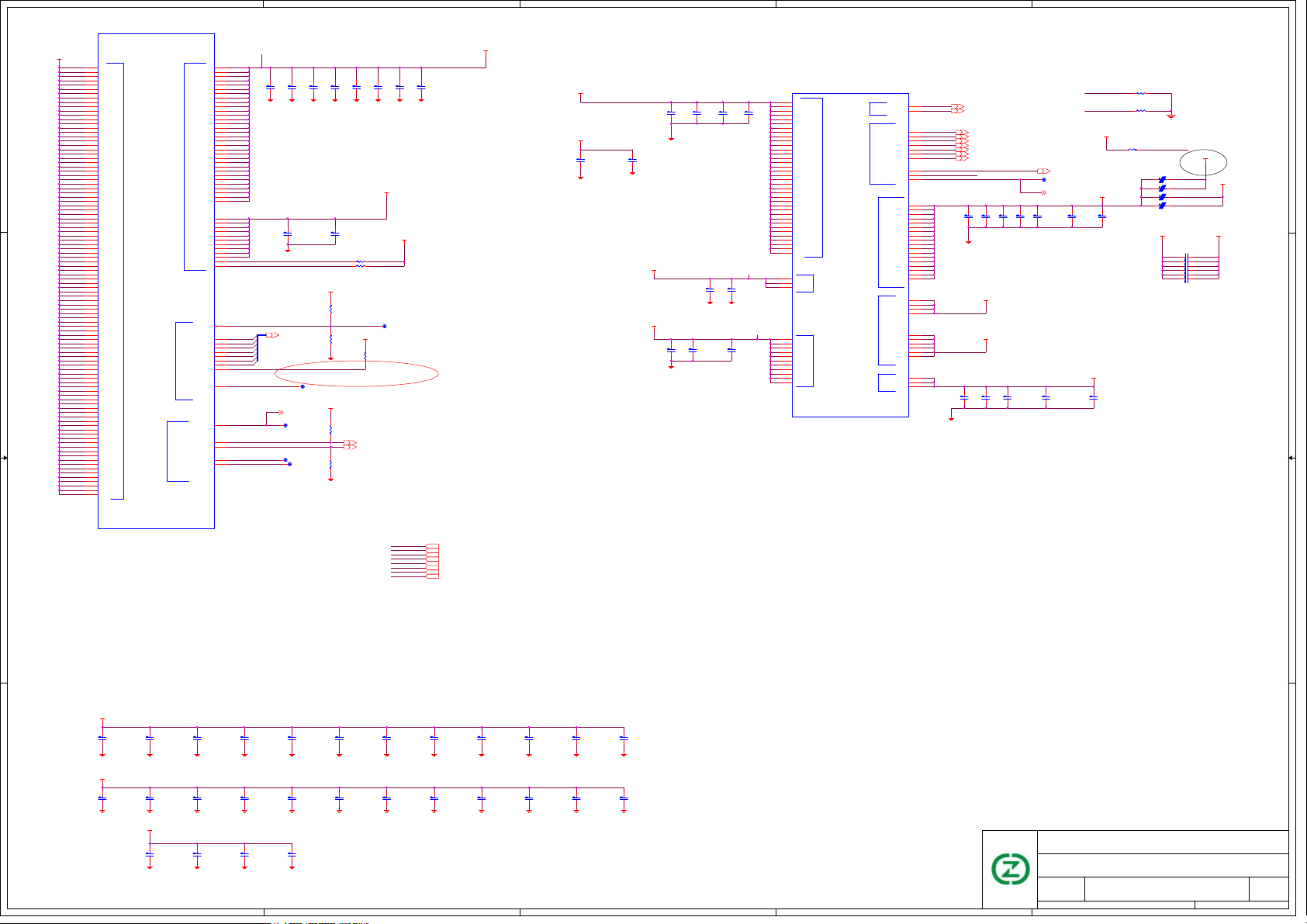

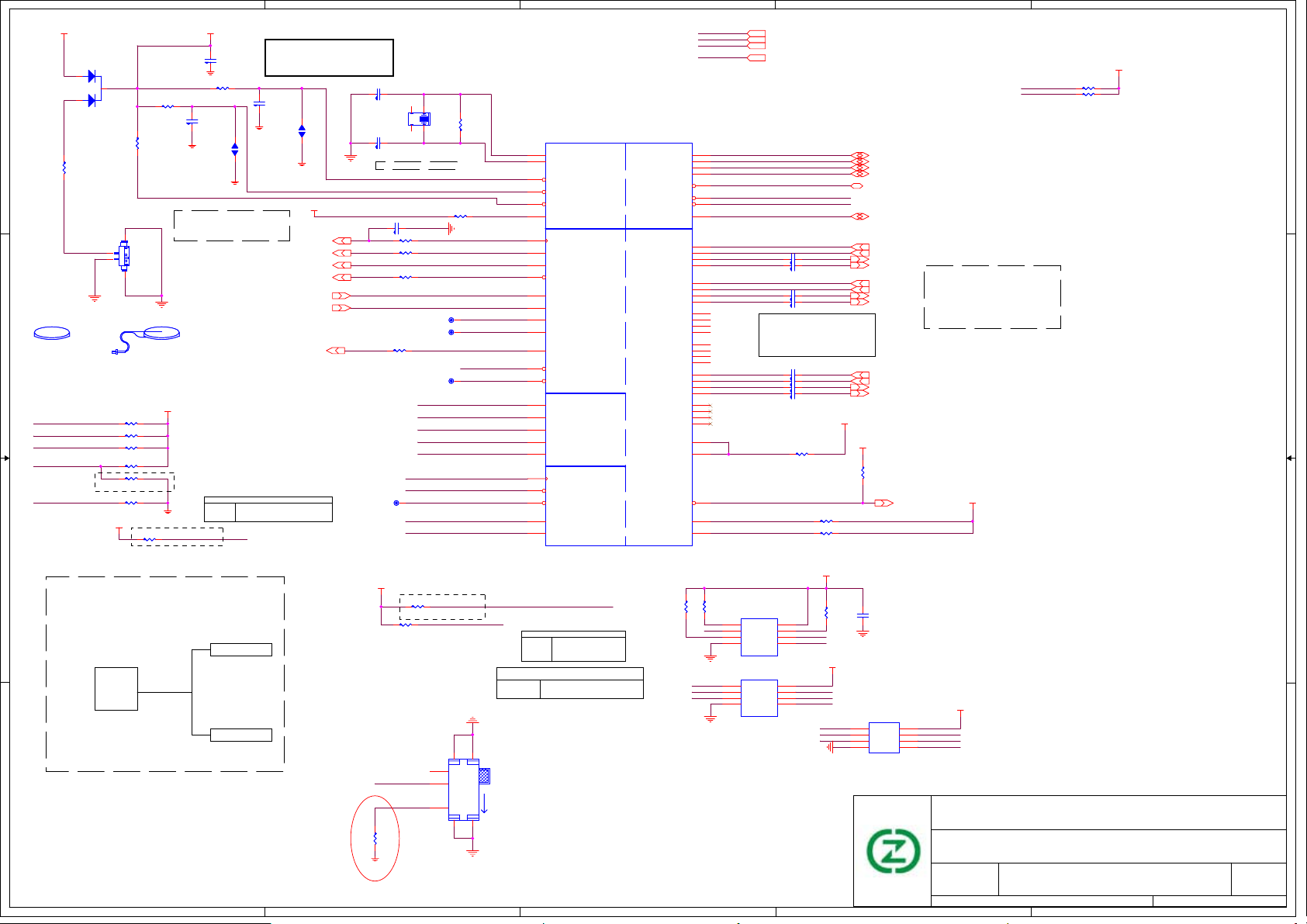

Page 3

5

A

4

3

2

1

POWER RAIL

+V3.3AUX

+V5AUX

D D

+V1.5

+V0.75S

+V5S

+V3.3S

+V1.5S

+V1.8S

+V1.5S

+V1.1S

+Vcore

GFXCORE

14.31818MHz

XTAL

AC Mode Battery Mode

S0 S1 S3 S4 S5

ON ONONON ON

ON ON

ON

ON

OFF OFF

ON

ONON

ONON

OFF

OFFON ON

OFF

ON OFFON

OFF OFF OFFON ON

OFF OFF OFFON ON

S0 S1 S3 S4 S5

ON ON ON

ON

ON

OFFOFF

OFF

OFFOFF

OFFOFFOFFONON

OFFOFFOFFONON

OFFOFFOFFONON

OFFOFFOFFONON OFFOFFOFFONON

25MHz

XTAL

ON

ONON

ON OFFON

ON

ONONON

OFF

OFF

OFF OFF OFFON ON

OFF OFF OFFON ON

OFF OFF

OFF OFF

OFF OFF

OFFOFF

OFF

OFFON ON

OFFOFF

OFFOFFOFFONON

OFFOFFOFFONON

OFFOFFOFFONON

C C

133MHz

133MHz

BCLK

100MHz

CK505

DMI

100MHz

SATA

PCH

Buffered

Mode

96MHz

B B

DOT

BCLK

100MHz

DMI

120MHz

DP

100MHz

PEG A

100MHz

PCIE

CPU

GPU

NEW CARD

Mini PCIE SLOT X2

14.31818MHz

REF

33MHz

PCI

KBC

100MHz

PCIE

48MHz

LAN

25MHz

XTAL

No stuff

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

R48 C

R48 C

R48 C

zw

zw

zw

356Thursday, April 22, 2010

356Thursday, April 22, 2010

356Thursday, April 22, 2010

A

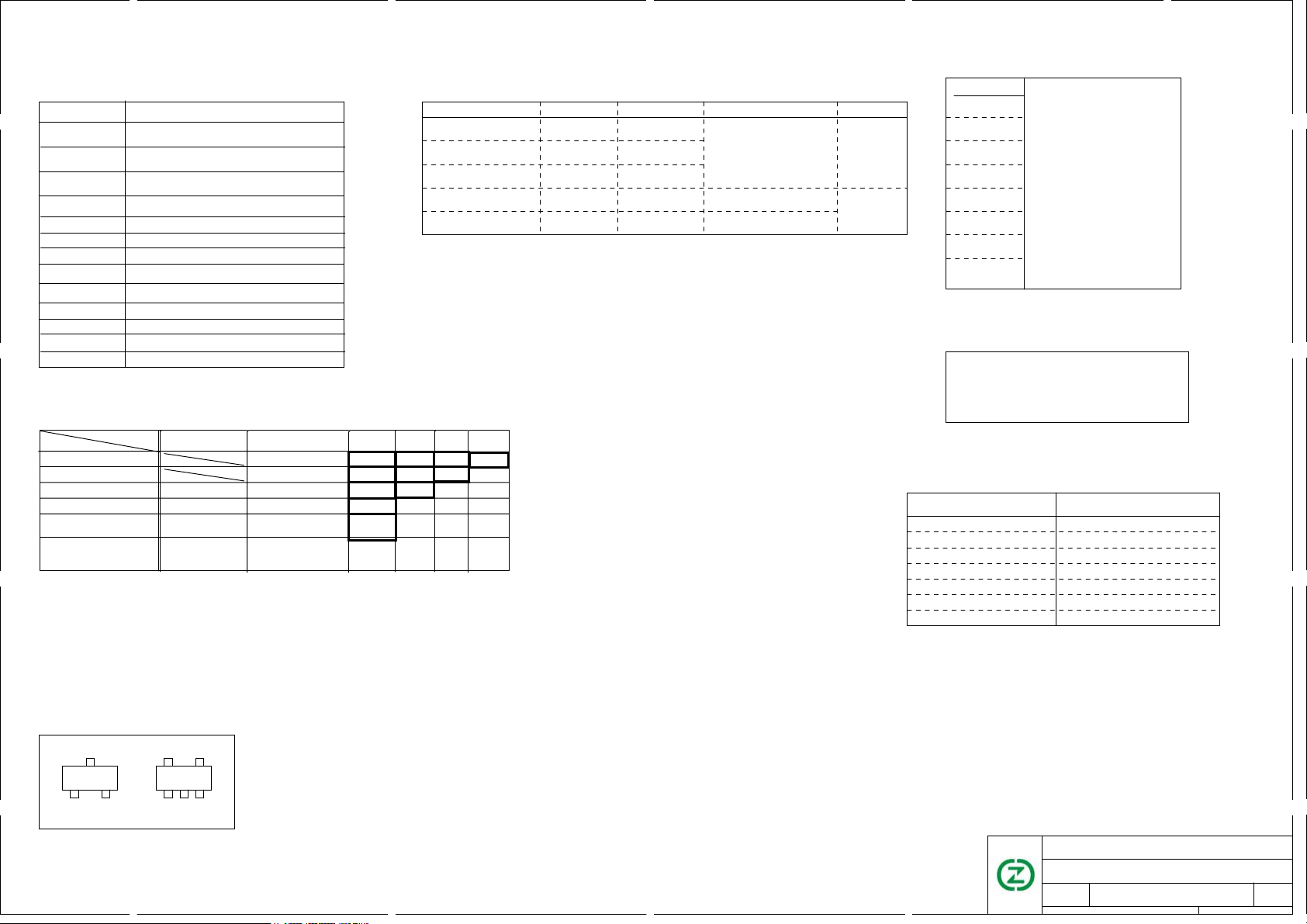

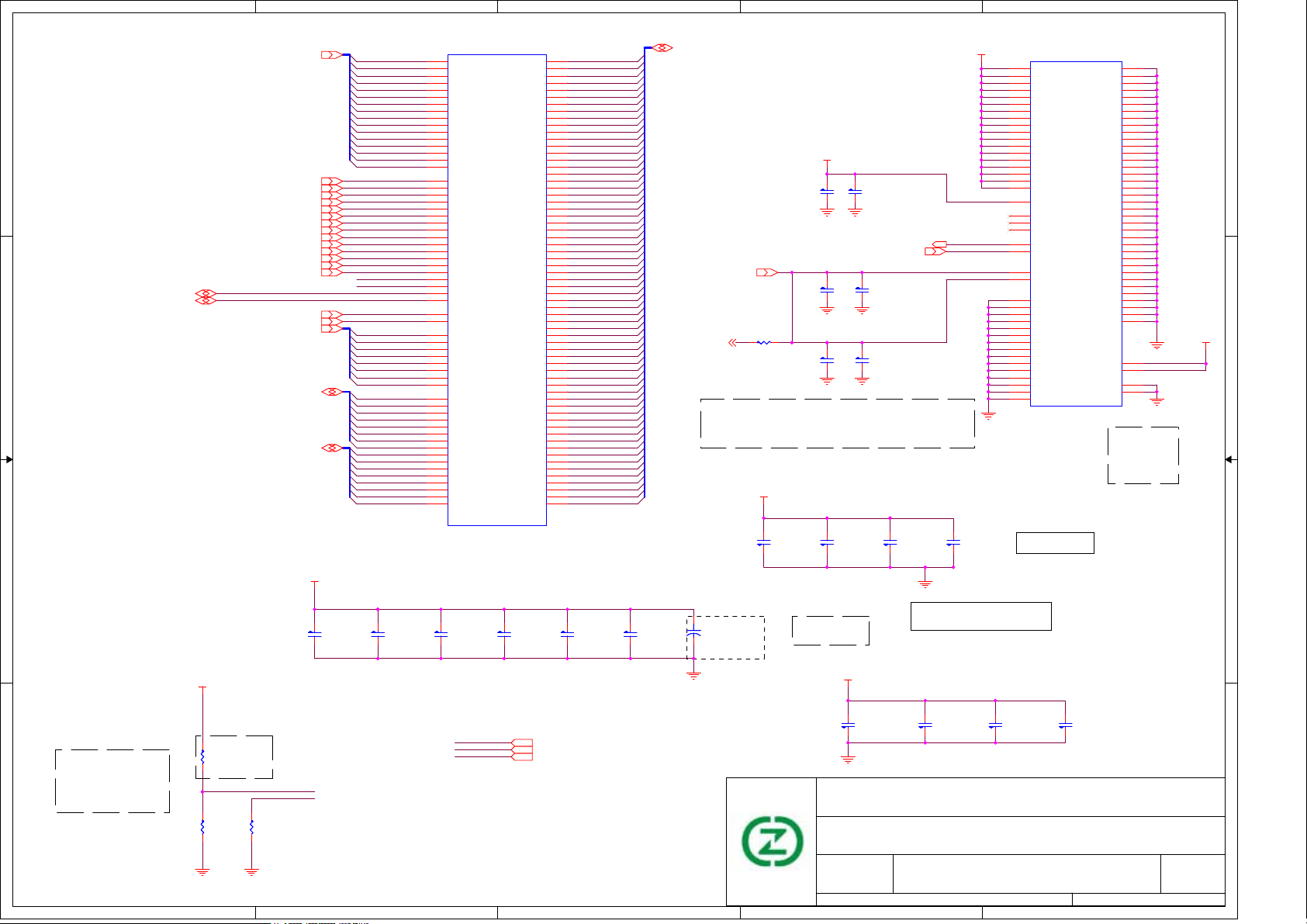

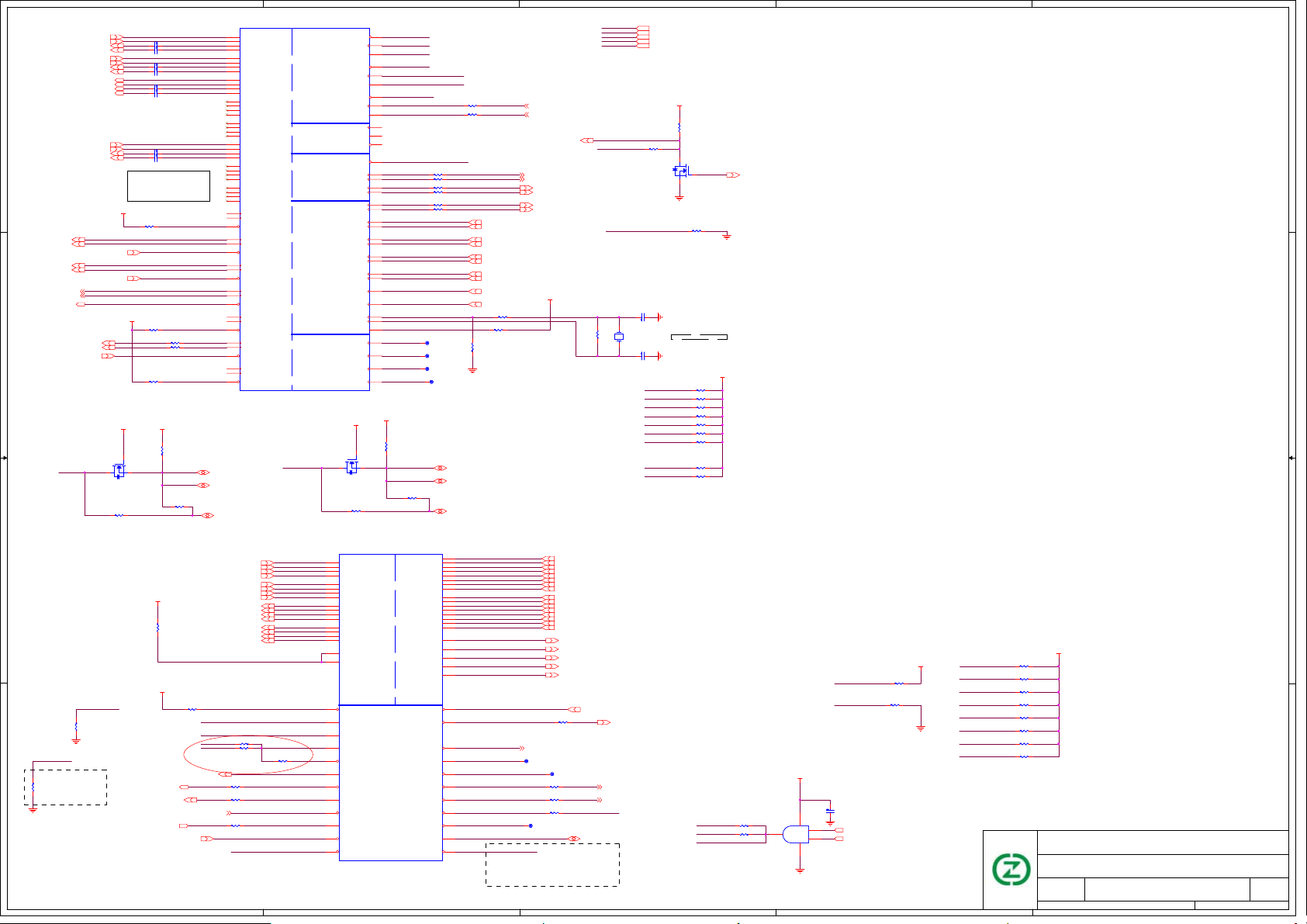

Page 4

5

A

4

3

2

1

Board stack up description

Voltage Rails

D D

C C

+VDC

+VCC_core

+V1.1S

+V0.75S

+V1.5S

+V1.5

+V3.3AUX

+V3.3S

+V5AUX

+V5S

Primary DC system power supply(9V-12V)

Core/VTT voltage for processor

1.8V For PCH CPU+V1.8S

1.05V /1.1V For PCH CPU GPU

0.75V DDRIII Termination voltage

1.5V for system power

1.5V power rail for DDRIII

3.3V always on power rail

3.3V main power rail

5V always on power rail

5V main power rail

+Vcore:0.75V-1.1V

I2C SMB Address

Device

Clock Generator

SO-DIMM0

SO-DIMM1

OZ8805LN

Thermal Diode G781

Address

1101 001x

1010 000x

1010 010x

0001 011x

1001 100x

Hex(W/R)

D2H/D3H

0xA0

0xA4

16H/17H

98H/99H

Bus

SMB_CLK/DATA

EC_I2C_CLK2/DATA2

EC_I2C_CLK/DATA

Master

PCH

EC

Power States

state

Full ON

S1M(Power On Suspend)

S3(Suspend to RAM)

S4(Suspend to DISK)

S5/Soft Off

With AC IN

G3

With Battery

signal

PM_SLP_S4#

HIGH

LOW

LOW

LOW

PM_SLP_S3#

HIGH

HIGH

LOW

LOW

LOW

LOW

+V*AUX

ON

ON

ON

ON

ON

OFF

+V*

ON

ON

OFF

OFF

OFF

+V*S

ON

ON

OFF

OFF

OFF

OFF

CLOCKS

ON

LOW

OFF

OFF

OFF

OFF

Wake up Events

B B

PCB Layers

Top(Signal1)

Ground

Signal2

Signal3

Power

Signal4

Ground

Bottom(Signal5)

Trace Impedence:50ohm +/-15%

PCB Layer Difference signal Impedence list

USB signal difference impedence 85ohm

LVDS signal difference impedence 85ohm

DDRIII signal difference impedence 85ohm

DDRIII CLK signal difference impedence 68ohm

Wake Events

LID switch from EC

Power Button from EC

Keyboard from EC

USB device

State Supported(AC)

S3 support

S3,S4,S5 support

No

No

[Option]:ns -- Component marked "ns" is not stuff

[Use State]:new --Component Marked "new" is new Materiel.

PCB Footprints

SOT23

1

3

5

4

SOT23_5

2

3

2ON1

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

R48 C

R48 C

R48 C

zw

zw

zw

456Thursday, April 22, 2010

456Thursday, April 22, 2010

456Thursday, April 22, 2010

A

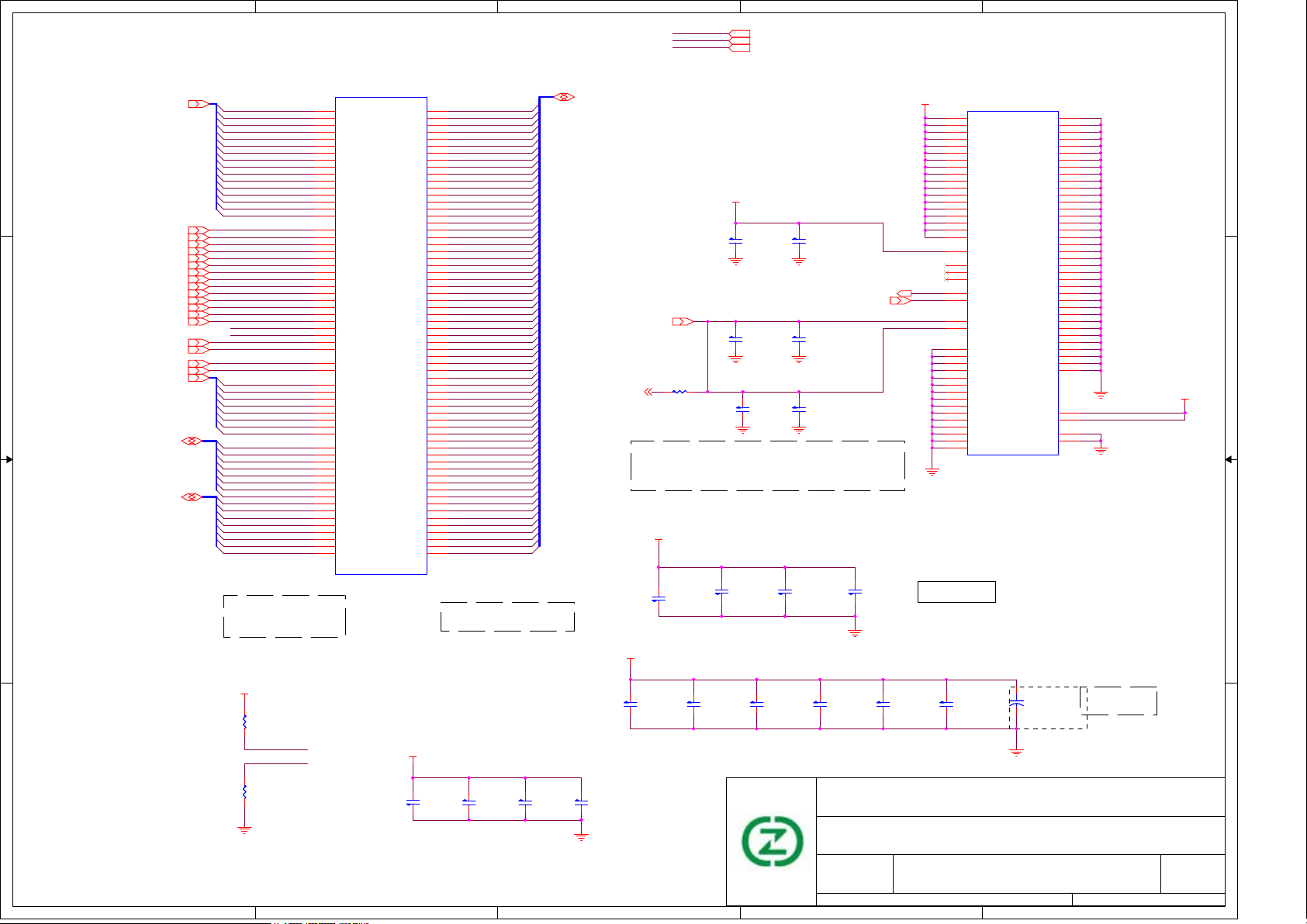

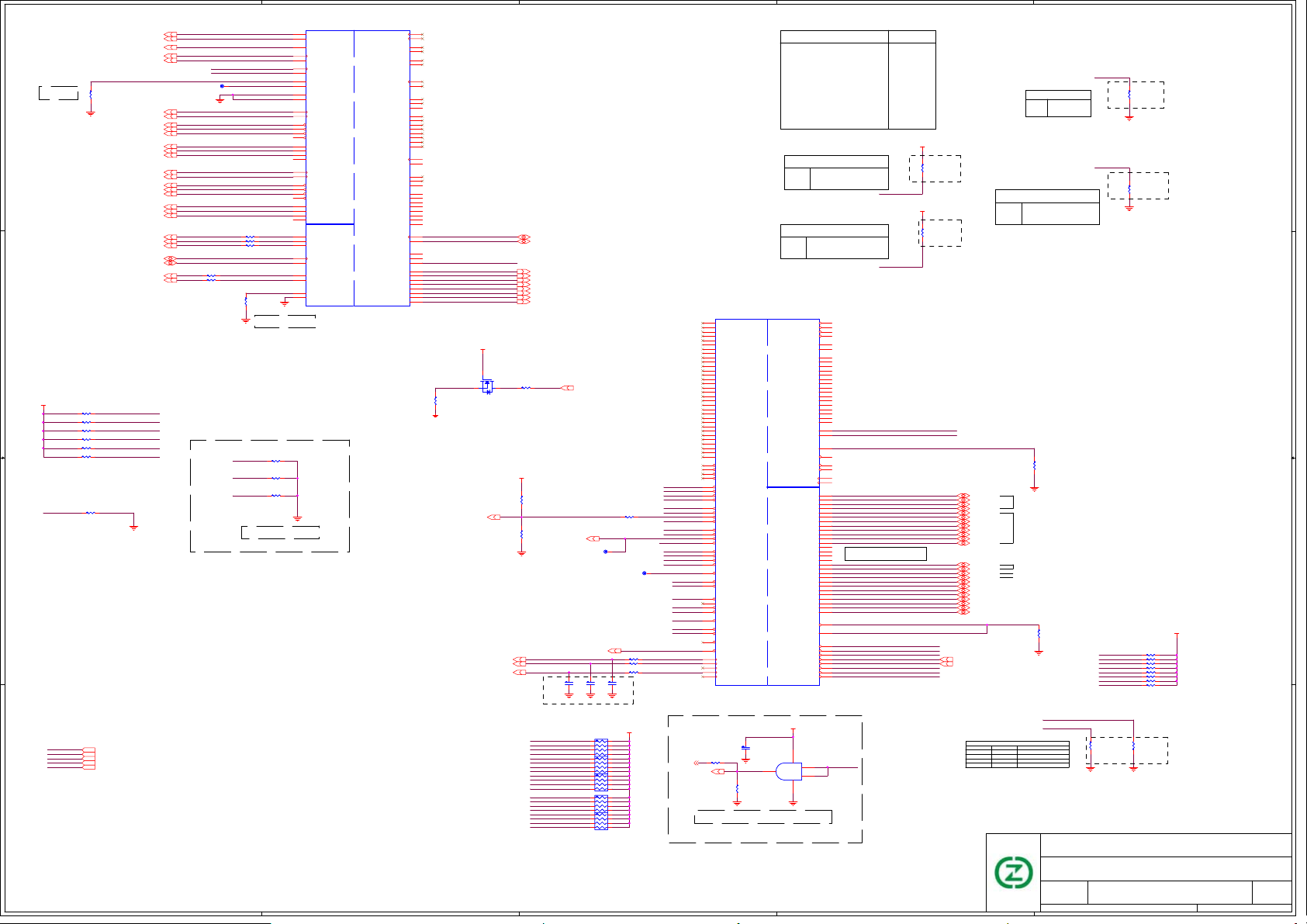

Page 5

5

U1A

U1A

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

DMI_TXN014

DMI_TXN114

DMI_TXN214

DMI_TXN314

DMI_TXP014

DMI_TXP114

DMI_TXP214

D D

DMI_TXP314

DMI_RXN014

DMI_RXN114

DMI_RXN214

DMI_RXN314

DMI_RXP014

DMI_RXP114

DMI_RXP214

DMI_RXP314

FDI_TXN[7:0]14

FDI_TXP[7:0]14

FDI_FSYNC014

FDI_FSYNC114

FDI_INT14

FDI_LSYNC014

FDI_LSYNC114

C C

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

U1B

PECI_PCH

PLT_RSTL_R

U1B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP_SKTOCC_L

TP1TP1

H_CATERR_L

R6 0

PM_DRAM_PWRGD14

H_THRMTRIP_L16

H_PM_SYNC14

H_CPUPWRGD16

H_CPUPWRGD16

BUF_PLT_RST_L

TP13TP13

R12

R12

R6 0

R319 0

R319 0

1.5K,1%

1.5K,1%

R0402_0

R0402_0

R0402_0

R0402_0

H_THRMTRIP_L

R489 0 nsR489 0 ns

R10 0

R10 0

R318 0

R318 0

H_VTTPWRGD

R0402_0

R0402_0

R0402_0

R0402_0

R18

R18

750

750

H_PROCHOT_L

H_CPURST_L

VCCPWRGOOD_R

VDDPWRGOOD_R

H_PECI16

H_PROCHOT#38

B B

BUF_PLT_RST_L15,41

4

PEG_IRCOMP_R

B26

PEG_ICOMPI

A26

PEG_ICOMPO

B27

PEG_RCOMPO

A25

PEG_RBIAS

K35

PEG_RX#[0]

J34

PEG_RX#[1]

J33

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

MISC THERMAL

MISC THERMAL

PWR MANAGEMENT

PWR MANAGEMENT

G35

PEG_RX#[3]

G32

PEG_RX#[4]

F34

PEG_RX#[5]

F31

PEG_RX#[6]

D35

PEG_RX#[7]

E33

PEG_RX#[8]

C33

PEG_RX#[9]

D32

PEG_RX#[10]

B32

PEG_RX#[11]

C31

PEG_RX#[12]

B28

PEG_RX#[13]

B30

PEG_RX#[14]

A31

PEG_RX#[15]

J35

PEG_RX[0]

H34

PEG_RX[1]

H33

PEG_RX[2]

F35

PEG_RX[3]

G33

PEG_RX[4]

E34

PEG_RX[5]

F32

PEG_RX[6]

D34

PEG_RX[7]

F33

PEG_RX[8]

B33

PEG_RX[9]

D31

PEG_RX[10]

A32

PEG_RX[11]

C30

PEG_RX[12]

A28

PEG_RX[13]

B29

PEG_RX[14]

A30

PEG_RX[15]

L33

PEG_TX#[0]

M35

PEG_TX#[1]

M33

PEG_TX#[2]

M30

PEG_TX#[3]

L31

PEG_TX#[4]

K32

PEG_TX#[5]

M29

PEG_TX#[6]

J31

PEG_TX#[7]

K29

PEG_TX#[8]

H30

PEG_TX#[9]

H29

PEG_TX#[10]

F29

PEG_TX#[11]

E28

PEG_TX#[12]

D29

PEG_TX#[13]

D27

PEG_TX#[14]

C26

PEG_TX#[15]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

L34

PEG_TX[0]

M34

PEG_TX[1]

M32

PEG_TX[2]

L30

PEG_TX[3]

M31

PEG_TX[4]

K31

PEG_TX[5]

M28

PEG_TX[6]

H31

PEG_TX[7]

K28

PEG_TX[8]

G30

PEG_TX[9]

G29

PEG_TX[10]

F28

PEG_TX[11]

E27

PEG_TX[12]

D28

PEG_TX[13]

C27

PEG_TX[14]

C25

PEG_TX[15]

A16

BCLK

B16

BCLK#

AR30

BCLK_ITP

AT30

BCLK_ITP#

E16

PEG_CLK

D16

PEG_CLK#

A18

DPLL_REF_SSCLK

A17

DPLL_REF_SSCLK#

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

JTAG & BPM

JTAG & BPM

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

TCK

AP28

TMS

AT27

AT29

TDI

AR27

TDO

AR29

AP29

AN25

DBR#

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

EXP_RBIAS

R2 750R2 750

C1 0.1uF/16V,X7R DGPUC1 0.1uF/16V,X7R DGPU

C2 0.1uF/16V,X7R DGPUC2 0.1uF/16V,X7R DGPU

C3 0.1uF/16V,X7R DGPUC3 0.1uF/16V,X7R DGPU

C4 0.1uF/16V,X7R DGPUC4 0.1uF/16V,X7R DGPU

C5 0.1uF/16V,X7R DGPUC5 0.1uF/16V,X7R DGPU

C6 0.1uF/16V,X7R DGPUC6 0.1uF/16V,X7R DGPU

C7 0.1uF/16V,X7R DGPUC7 0.1uF/16V,X7R DGPU

C8 0.1uF/16V,X7R DGPUC8 0.1uF/16V,X7R DGPU

C9 0.1uF/16V,X7R DGPUC9 0.1uF/16V,X7R DGPU

C10 0.1uF/16V,X7R DGPUC10 0.1uF/16V,X7R DGPU

C11 0.1uF/16V,X7R DGPUC11 0.1uF/16V,X7R DGPU

C12 0.1uF/16V,X7R DGPUC12 0.1uF/16V,X7R DGPU

C13 0.1uF/16V,X7R DGPUC13 0.1uF/16V,X7R DGPU

C14 0.1uF/16V,X7R DGPUC14 0.1uF/16V,X7R DGPU

C15 0.1uF/16V,X7R DGPUC15 0.1uF/16V,X7R DGPU

C16 0.1uF/16V,X7R DGPUC16 0.1uF/16V,X7R DGPU

C17 0.1uF/16V,X7R DGPUC17 0.1uF/16V,X7R DGPU

C18 0.1uF/16V,X7R DGPUC18 0.1uF/16V,X7R DGPU

C19 0.1uF/16V,X7R DGPUC19 0.1uF/16V,X7R DGPU

C20 0.1uF/16V,X7R DGPUC20 0.1uF/16V,X7R DGPU

C21 0.1uF/16V,X7R DGPUC21 0.1uF/16V,X7R DGPU

C22 0.1uF/16V,X7R DGPUC22 0.1uF/16V,X7R DGPU

C23 0.1uF/16V,X7R DGPUC23 0.1uF/16V,X7R DGPU

C24 0.1uF/16V,X7R DGPUC24 0.1uF/16V,X7R DGPU

C25 0.1uF/16V,X7R DGPUC25 0.1uF/16V,X7R DGPU

C26 0.1uF/16V,X7R DGPUC26 0.1uF/16V,X7R DGPU

C27 0.1uF/16V,X7R DGPUC27 0.1uF/16V,X7R DGPU

C28 0.1uF/16V,X7R DGPUC28 0.1uF/16V,X7R DGPU

C29 0.1uF/16V,X7R DGPUC29 0.1uF/16V,X7R DGPU

C30 0.1uF/16V,X7R DGPUC30 0.1uF/16V,X7R DGPU

C31 0.1uF/16V,X7R DGPUC31 0.1uF/16V,X7R DGPU

C32 0.1uF/16V,X7R DGPUC32 0.1uF/16V,X7R DGPU

Layout Note: All

resistors need to be

close to Processor

(ARD/CFD) to avoid stubs

CK_BCK1

CK_BCK1_L

CPU_DRAMRST_L

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

PM_EXTTS_L0

PM_EXTTS_L1

XDP_PREQ_L

XDP_TCLK

XDP_TMS

XDP_TRST_L

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

PEG_RXN15

PEG_RXN14

PEG_RXN13

PEG_RXN12

PEG_RXN11

PEG_RXN10

PEG_RXN9

PEG_RXN8

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP15

PEG_RXP14

PEG_RXP13

PEG_RXP12

PEG_RXP11

PEG_RXP10

PEG_RXP9

PEG_RXP8

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

R22 0

R22 0

49.9,1%R1 49.9,1%R1

PEG_TXN15

PEG_TXN14

PEG_TXN13

PEG_TXN12

PEG_TXN11

PEG_TXN10

PEG_TXN9

PEG_TXN8

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP15

PEG_TXP14

PEG_TXP13

PEG_TXP12

PEG_TXP11

PEG_TXP10

PEG_TXP9

PEG_TXP8

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

TP64TP64

TP53TP53

TP54TP54

R161 51.1,1%R161 51.1,1%

R0402_0

R0402_0

R21 1KR21 1K

lane reversal

CLK_MCP_BCLK 12,16

CLK_MCP_BCLK_L 12,16

CLK_MCH_PEG 12,14

CLK_MCH_PEG_L 12,14

CLK_DP_P 14

CLK_DP_N 14

+V1.1S_VTT

R7

10K,1%R710K,1%

+V1.1S_VTT

+V3.3S

XDP_TMS

XDP_TDI_R

XDP_PREQ_L

XDP_TCLK

3

R8

10K,1%R810K,1%

R1054 0 nsR1054 0 ns

NO_STUFF

R9

R9

12.4K,1%

12.4K,1%

ns

ns

CAD Note:

TCLK: Provide a scope test point at the

Processor socket breakout via to verify

signal integrity of the first

platforms.

+V1.1S_VTT

NO_STUFF

R11 51.1,1% nsR11 51.1,1% ns

R13 51.1,1% nsR13 51.1,1% ns

R15 51.1,1% nsR15 51.1,1% ns

R19 51.1,1% nsR19 51.1,1% ns

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3PEG_TXN3

PEG_TXN4PEG_TXN4

PEG_TXN5PEG_TXN5

PEG_TXN6PEG_TXN6

PEG_TXN7PEG_TXN7

PEG_TXN8PEG_TXN8

PEG_TXN9PEG_TXN9

PEG_TXN10PEG_TXN10

PEG_TXN11PEG_TXN11

PEG_TXN12PEG_TXN12

PEG_TXN13PEG_TXN13

PEG_TXN14PEG_TXN14

PEG_TXN15PEG_TXN15

PEG_TXP0

PEG_TXP1PEG_TXP1

PEG_TXP2PEG_TXP2

PEG_TXP3PEG_TXP3

PEG_TXP4PEG_TXP4

PEG_TXP5PEG_TXP5

PEG_TXP6PEG_TXP6

PEG_TXP7PEG_TXP7

PEG_TXP8PEG_TXP8

PEG_TXP9PEG_TXP9

PEG_TXP10PEG_TXP10

PEG_TXP11PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

PM_EXTTS#0_EC 9,27

PM_EXTTS_L1 9

XDP_TRST_L

PEG_RXN[15:0] 41

PEG_RXP[15:0] 41

CPU_DRAMRST_L

R17

R17

51.1,1%

51.1,1%

ns

ns

PEG_TXN[15:0] 41

PEG_TXP[15:0] 41

R874

R874

100K

100K

R873 0 R0402_0R873 0 R0402_0

V1_1S1_5S_PWROK33,36

R872 0 nsR872 0 ns

R927

R927

10K

10K

312

BSS138Q6BSS138

Q6

R876 0

R876 0

C1043

C1043

470pF/50V,X7R

470pF/50V,X7R

2

+V3.3AUX 13,14,15,16,17,19,21,22,24,25,27,28,29,30,31,32,34,35

+V1.5S 7,16,21,22,28,35,36

+V1.5 7,8,10,11,33,35

+V1.1S_VTT 7,12,16,17,35,36

+V3.3S 9,10,11,12,13,14,15,16,17,18,19,20,21,22,24,25,27,28,29,34,35,36,37,38,48

+V1.5S_CPU 7

+V1.5

R8771KR877

1K

R875 0

R875 0

R0402_0

R0402_0

1

2

+V3.3AUX

VCC

VCC

GND

GND

R0402_0

R0402_0

53

DRAMRST_CNTRL_PCH 16DRAMRST_CNTRL8,27

C314

C314

0.1uF/16V,X7R

0.1uF/16V,X7R

4

SOT23_5

SOT23_5

SN74AHC1G08DBV

SN74AHC1G08DBV

U34

U34

DDR3_DRAMRST_L 10,11

DRAMPWRGD_CPU

1

+V3.3S

Processor Compensation Signals

H_COMP2

R25

R25

R24

R24

20,1%

20,1%

20,1%

20,1%

3

49.9,1%

49.9,1%

H_COMP1H_COMP3

H_COMP0

R26

R26

R27

R27

49.9,1%

49.9,1%

DDR3 Compensation Signals

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

R32

R32

24.9,1%

24.9,1%

R31

R31

100,1%

100,1%

R33

R33

130,1%

130,1%

Layout Note:

Place these

resistors near

Processor

2

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Panel &VGA connect

Panel &VGA connect

Panel &VGA connect

R48 C

R48 C

R48 C

1

zw

zw

zw

of

of

of

556Thursday, April 22, 2010

556Thursday, April 22, 2010

556Thursday, April 22, 2010

R16

R16

1.5K,1%

1.5K,1%

+V1.5S_CPU

R23

R23

1.1K,1%

1.1K,1%

R34

R34

750

750

ns

ns

NO_STUFF

Processor Pullups

+V1.1S_VTT

R28

R28

49.9,1%

49.9,1%

H_CATERR_L

H_PROCHOT_L

H_CPURST_L

R2968R29

R30

R30

68

68

ns

ns

68

4

C235

C235

0.1uF/16V,X7R

A A

V1_1S1_5S_PWROK33,36

R490 1KR490 1K

C312

C312

0.1uF/16V,X7R

0.1uF/16V,X7R

1

2

0.1uF/16V,X7R

53

VCC

VCC

R14 1.5K,1%R14 1.5K,1%

4

GND

GND

SOT23_5

SOT23_5

SN74AHC1G08DBV

SN74AHC1G08DBV

U33

U33

H_VTTPWRGD

R20

R20

750

750

DRAMPWRGD_CPU

VDDPWRGOOD_R

5

Page 6

5

U1C

U1C

D D

C C

B B

M_A_DQ[63:0]10

M_A_BS010

M_A_BS110

M_A_BS210

M_A_CAS_L10

M_A_RAS_L10

M_A_WE_L10

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_CAS_L

M_A_RAS_L

M_A_WE_L

AJ10

AL10

AK12

AK11

AM10

AR11

AL11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

A10

C10

B10

D10

E10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AK8

AL7

AL8

AN8

AM9

AN9

AC3

AB2

AE1

AB3

AE9

SA_DQ[0]

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

U7

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

4

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_CKE0

M_CKE1M_A_DQ5

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS_L0

M_A_DQS_L1

M_A_DQS_L2

M_A_DQS_L3

M_A_DQS_L4

M_A_DQS_L5

M_A_DQS_L6

M_A_DQS_L7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 10

M_CLK_DDR0_L 10

M_CKE0 10

M_CLK_DDR1 10

M_CLK_DDR1_L 10

M_CKE1 10

M_CS_L0 10

M_CS_L1 10

M_ODT0 10

M_ODT1 10

M_A_DM[7:0] 10

M_A_DQS_L[7:0] 10

M_A_DQS[7:0] 10

M_A_A[15:0] 10

3

U1D

U1D

M_B_DQ[63:0]11

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS011

M_B_BS111

M_B_BS211

M_B_CAS_L11

M_B_RAS_L11

M_B_WE_L11

M_B_CAS_L

M_B_RAS_L

M_B_WE_L

AM6

AM4

AM3

AR10

AT10

AF3

AG1

AJ3

AK1

AG4

AG3

AJ4

AH4

AK3

AK4

AN2

AK5

AK2

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AB1

AC5

AC6

M1

M4

W5

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

K5

K4

N5

R7

Y7

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

2

W8

SB_CK[0]

W9

SB_CK#[0]

M3

SB_CKE[0]

V7

SB_CK[1]

V6

SB_CK#[1]

M2

SB_CKE[1]

AB8

SB_CS#[0]

AD6

SB_CS#[1]

AC7

SB_ODT[0]

AD1

SB_ODT[1]

D4

SB_DM[0]

E1

SB_DM[1]

H3

SB_DM[2]

K1

SB_DM[3]

AH1

SB_DM[4]

AL2

SB_DM[5]

AR4

SB_DM[6]

AT8

SB_DM[7]

D5

SB_DQS#[0]

F4

SB_DQS#[1]

J4

SB_DQS#[2]

L4

SB_DQS#[3]

AH2

SB_DQS#[4]

AL4

SB_DQS#[5]

AR5

SB_DQS#[6]

AR8

SB_DQS#[7]

C5

SB_DQS[0]

E3

SB_DQS[1]

H4

SB_DQS[2]

M5

SB_DQS[3]

AG2

SB_DQS[4]

AL5

SB_DQS[5]

AP5

SB_DQS[6]

AR7

SB_DQS[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS_L0

M_B_DQS_L1

M_B_DQS_L2

M_B_DQS_L3

M_B_DQS_L4

M_B_DQS_L5

M_B_DQS_L6

M_B_DQS_L7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

1

M_CLK_DDR2 11

M_CLK_DDR2_L 11

M_CKE2 11

M_CLK_DDR3 11

M_CLK_DDR3_L 11

M_CKE3 11

M_CS_L2 11

M_CS_L3 11

M_ODT2 11

M_ODT3 11

M_B_DM[7:0] 11

M_B_DQS_L[7:0] 11

M_B_DQS[7:0] 11

M_B_A[15:0] 11

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

OCD_CPU

OCD_CPU

A A

5

4

3

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

OCD_CPU

OCD_CPU

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

Panel &VGA connect

Panel &VGA connect

Panel &VGA connect

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

R48 C

R48 C

R48 C

zw

zw

zw

656Thursday, April 22, 2010

656Thursday, April 22, 2010

656Thursday, April 22, 2010

1

of

of

of

Page 7

5

U1F

U1F

+VCORE

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

D D

C C

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

CPU VIDS

CPU VIDS

SENSE LINES

SENSE LINES

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

1.1V RAIL POWER

1.1V RAIL POWER

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

PSI#

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

PROC_DPRSLPVR

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

AN35

AJ34

AJ35

B15

A15

PSI_L

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

PM_DPRSLPVR_R

H_VTTVID1

TP_VTT_SENSE

TP_VSS_SENSE_VTT

C33

C33

10uF/10V X5R

10uF/10V X5R

H_VID[0:6] 38

CORE_IMON 38

C34

C34

10uF/10V X5R

10uF/10V X5R

C52

C52

22uF/6.3V,X5R

22uF/6.3V,X5R

TP5TP5

TP2TP2

TP3TP3

+VTT_43

+VTT_44

TP4TP4

C35

C35

10uF/10V X5R

10uF/10V X5R

+V1.1S

+VCORE

R1166

R1166

1K

1K

ns

ns

R11671KR1167

1K

R41

R41

100

100

R42

R42

100

100

C36

C36

10uF/10V X5R

10uF/10V X5R

C53

C53

22uF/6.3V,X5R

22uF/6.3V,X5R

R38 0R38 0

R39 0R39 0

C37

C37

10uF/10V X5R

10uF/10V X5R

+V1.1S

R11681KR1168

1K

VCC_SENSE 38

VSS_SENSE 38

4

C38

C38

10uF/10V X5R

10uF/10V X5R

+V1.1S_VTT

TP14TP14

C39

C39

10uF/10V X5R

10uF/10V X5R

+V1.1S_VTT

C40

C40

10uF/10V X5R

10uF/10V X5R

ns

ns

+V1.1S_VTT

+VCC_GFXCORE

+VCC_GFXCORE

C64

C64

10uF/10V X5R

10uF/10V X5R

3

C65

C65

10uF/10V X5R

10uF/10V X5R

+V1.1S_VTT

+V1.1S_VTT

C41

C41

22uF/6.3V,X5R

22uF/6.3V,X5R

C56

C56

22uF/6.3V,X5R

22uF/6.3V,X5R

C43

C43

22uF/6.3V,X5R

22uF/6.3V,X5R

C57

C57

22uF/6.3V,X5R

22uF/6.3V,X5R

C42

C42

10uF/10V X5R

10uF/10V X5R

C54

C54

22uF/6.3V,X5R

22uF/6.3V,X5R

C55

C55

22uF/6.3V,X5R

22uF/6.3V,X5R

C58

C58

22uF/6.3V,X5R

22uF/6.3V,X5R

C44

C44

10uF/10V X5R

10uF/10V X5R

U1G

U1G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

GRAPHICS

GRAPHICS

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

2

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

GRAPHICS VIDs

GRAPHICS VIDs

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

1.1V1.8V

1.1V1.8V

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

GFXVR_DPRSLPVR_R

VCC_AXG_SENSE 37

VSS_AXG_SENSE 37

1uF/10V,X5R

1uF/10V,X5R

C59

C59

1uF/10V,X5R

1uF/10V,X5R

GFXVR_VID_0 37

GFXVR_VID_1 37

GFXVR_VID_2 37

GFXVR_VID_3 37

GFXVR_VID_4 37

GFXVR_VID_5 37

GFXVR_VID_6 37

GFXVR_EN

GFXVR_IMON

C46

C46

C45

C45

1uF/10V,X5R

1uF/10V,X5R

+V1.1S_VTT

+V1.1S_VTT

C60

C60

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

C47

C47

C61

C61

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

C48

C48

GFX_IMON 37

C49

C49

1uF/10V,X5R

1uF/10V,X5R

GFXVR_EN 37

TP23TP23

C62

C62

4.7uF/10V,X5R

4.7uF/10V,X5R

GFXVR_DPRSLPVR_R

GFXVR_EN

+V1.1S_VTT

+V1.5S_CPU

C50

C50

22uF/6.3V,X5R

22uF/6.3V,X5R

+V1.8S

C63

C63

22uF/6.3V,X5R

22uF/6.3V,X5R

R36 1K nsR36 1K ns

C51

C51

22uF/6.3V,X5R

22uF/6.3V,X5R

1

10KR128ns10KR128

ns

470R35 470R35

GFXVR_EN

FB92 120ohm/100MHz,2.5A nsFB92 120ohm/100MHz,2.5Ans

FB93 120ohm/100MHz,2.5A nsFB93 120ohm/100MHz,2.5Ans

FB90 120ohm/100MHz,2.5AFB90 120ohm/100MHz,2.5A

FB91 120ohm/100MHz,2.5AFB91 120ohm/100MHz,2.5A

C136 0.1uF/16V,X7RC136 0.1uF/16V,X7R

C137 0.1uF/16V,X7RC137 0.1uF/16V,X7R

C138 0.1uF/16V,X7RC138 0.1uF/16V,X7R

C139 0.1uF/16V,X7RC139 0.1uF/16V,X7R

C143 0.1uF/16V,X7RC143 0.1uF/16V,X7R

C144 0.1uF/16V,X7RC144 0.1uF/16V,X7R

+V1.5

+V1.5S

+V1.5+V1.5S_CPU

DIMM0

DIMM1

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

B B

C68

C68

22uF/6.3V,X5R

22uF/6.3V,X5R

C80

C80

10uF/10V X5R

10uF/10V X5R

C91

C91

10uF/10V X5R

10uF/10V X5R

22u*12

C69

C69

22uF/6.3V,X5R

22uF/6.3V,X5R

C81

C81

10uF/10V X5R

10uF/10V X5R

C92

C92

10uF/10V X5R

10uF/10V X5R

C70

C70

22uF/6.3V,X5R

22uF/6.3V,X5R

C82

C82

10uF/10V X5R

10uF/10V X5R

C93

C93

10uF/10V X5R

10uF/10V X5R

C71

C71

22uF/6.3V,X5R

22uF/6.3V,X5R

10u*16

C83

C83

10uF/10V X5R

10uF/10V X5R

4

+VCORE

C66

C66

22uF/6.3V,X5R

22uF/6.3V,X5R

+VCORE

C78

A A

C78

10uF/10V X5R

10uF/10V X5R

+VCORE

C67

C67

22uF/6.3V,X5R

22uF/6.3V,X5R

C79

C79

10uF/10V X5R

10uF/10V X5R

C90

C90

10uF/10V X5R

10uF/10V X5R

5

C72

C72

22uF/6.3V,X5R

22uF/6.3V,X5R

C84

C84

10uF/10V X5R

10uF/10V X5R

+V1.1S 13,14,16,17,34,35,36

+VCC_GFXCORE 37

+V1.8S 15,16,28,34,36

+V1.1S_VTT 5,12,16,17,35,36

+VCORE 28,38

+V1.5 5,8,10,11,33,35

+V1.5S 16,21,22,28,35,36

+V1.5S_CPU 5

C73

C73

22uF/6.3V,X5R

22uF/6.3V,X5R

C85

C85

10uF/10V X5R

10uF/10V X5R

C74

C74

22uF/6.3V,X5R

22uF/6.3V,X5R

C86

C86

10uF/10V X5R

10uF/10V X5R

C75

C75

22uF/6.3V,X5R

22uF/6.3V,X5R

C87

C87

10uF/10V X5R

10uF/10V X5R

C76

C76

22uF/6.3V,X5R

22uF/6.3V,X5R

C88

C88

10uF/10V X5R

10uF/10V X5R

C77

C77

22uF/6.3V,X5R

22uF/6.3V,X5R

C89

C89

10uF/10V X5R

10uF/10V X5R

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

3

2

Date: Sheet

Panel &VGA connect

Panel &VGA connect

Panel &VGA connect

R48 C

R48 C

R48 C

1

zw

zw

zw

of

of

of

756Thursday, April 22, 2010

756Thursday, April 22, 2010

756Thursday, April 22, 2010

Page 8

5

U1H

U1H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

VSS8

AR17

VSS9

AR15

VSS10

AR12

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

AP20

VSS15

AP17

VSS16

AP13

VSS17

AP10

VSS18

AP7

VSS19

D D

C C

AP4

VSS20

AP2

VSS21

AN34

VSS22

AN31

VSS23

AN23

VSS24

AN20

VSS25

AN17

VSS26

AM29

VSS27

AM27

VSS28

AM25

VSS29

AM20

VSS30

AM17

VSS31

AM14

VSS32

AM11

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

AL34

VSS37

AL31

VSS38

AL23

VSS39

AL20

VSS40

AL17

VSS41

AL12

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

AK29

VSS46

AK27

VSS47

AK25

VSS48

AK20

VSS49

AK17

VSS50

AJ31

VSS51

AJ23

VSS52

AJ20

VSS53

AJ17

VSS54

AJ14

VSS55

AJ11

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

AH35

VSS60

AH34

VSS61

AH33

VSS62

AH32

VSS63

AH31

VSS64

AH30

VSS65

AH29

VSS66

AH28

VSS67

AH27

VSS68

AH26

VSS69

AH20

VSS70

AH17

VSS71

AH13

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

AG10

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

AE35

VSS80

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

VSS

VSS

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

VSS81

AE33

VSS82

AE32

VSS83

AE31

VSS84

AE30

VSS85

AE29

VSS86

AE28

VSS87

AE27

VSS88

AE26

VSS89

AE6

VSS90

AD10

VSS91

AC8

VSS92

AC4

VSS93

AC2

VSS94

AB35

VSS95

AB34

VSS96

AB33

VSS97

AB32

VSS98

AB31

VSS99

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

4

U1I

U1I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

E24

E21

E18

E13

E11

D33

D30

D26

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

A29

A27

A23

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

VSS205

VSS206

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

VSS230

VSS231

VSS232

A9

VSS233

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

VSS

VSS

NCTF

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

3

2

1

+V1.5 5,7,10,11,33,35

U1E

U1E

AP25

RSVD1

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

J17

SA_DIMM_VREFDQ

H17

SB_DIMM_VREFDQ

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

CFG0

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

CFG3

AL32

CFG[3]

CFG4

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

CFG7

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]

AN30

CFG[12]

AN32

CFG[13]

AJ32

CFG[14]

AJ29

CFG[15]

AJ30

CFG[16]

AK30

CFG[17]

H16

RSVD_TP_86

B19

RSVD15

A19

RSVD16

A20

RSVD17

B20

RSVD18

U9

RSVD19

T9

RSVD20

AC9

RSVD21

AB9

RSVD22

C1

RSVD_NCTF_23

A3

RSVD_NCTF_24

J29

RSVD26

J28

RSVD27

A34

RSVD_NCTF_28

A33

RSVD_NCTF_29

C35

RSVD_NCTF_30

B35

RSVD_NCTF_31

IC,ARD_CFD_rPGA,R1P5

IC,ARD_CFD_rPGA,R1P5

RESERVED

RESERVED

R50 0 nsR50 0 ns

R51 0 nsR51 0 ns

ns

ns

VREF_CH_A_DIMM

VREF_CH_B_DIMM

R1046

R1046

R1047

R1047

100K

100K

100K

100K

H_RSVD17_R

H_RSVD18_R

M_VREF_DQ_DIMM0C10

M_VREF_DQ_DIMM1C11

B B

DRAMRST_CNTRL5,27

Close to DIMM

+V1.5

R1042

R1042

1K,1%

1K,1%

R1043

R1043

1K,1%

1K,1%

+V1.5

R1044

R1044

1K,1%

1K,1%

R1045

R1045

1K,1%

1K,1%

R71 0

R71 0

R91 0

R91 0

R0402_0

R0402_0

R0402_0

R0402_0

M_VREF_DQ_DIMM0C

M_VREF_DQ_DIMM1C

R43 0 nsR43 0 ns

R44 0 nsR44 0 ns

312

2N7002KQ72N7002K

Q7

2N7002KQ82N7002K

312

Q8

CFG7

R46 3.01K,1%

R46 3.01K,1%

NO_STUFF

A A

5

4

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD_NCTF_37

RSVD38

RSVD39

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD58

RSVD_TP_59

RSVD_TP_60

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

KEY

D15

C15

RSVD64_R

AJ15

RSVD65_R

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

TP_RSVD86

AP34

VSS

R61 0 nsR61 0 ns

R48 0 nsR48 0 ns

R49 0 nsR49 0 ns

3

PCI-Express Configuration Select

CFG0 1:Single PEG

0:Bifurcation enabled

CFG3 - PCI-Express Static Lane Reversal

1 :Normal Operation

0 :Lane Numbers Reversed

CFG3

15 -> 0, 14 -> 1, ...

CFG4 - Display Port Presence

1:Disabled; No Physical Display Port

attached to Embedded Display Port

CFG4

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

2

CFG0

NO_STUFF

R45

R45

3.01K,1%

3.01K,1%

ns

ns

CFG3

R47

R47

3.01K,1%

3.01K,1%

CFG4

R52

R52

3.01K,1%

3.01K,1%

ns

ns

NO_STUFF

Title

Title

Title

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Date: Sheet

Date: Sheet

Date: Sheet

Layout Note:

Location of all CFG strap resistors needs

to be close to trace to minimize stub

CZC Technology

CZC Technology

CZC Technology

Panel &VGA connect

Panel &VGA connect

Panel &VGA connect

A3

A3

A3

zw

zw

zw

R48 C

R48 C

R48 C

1

of

of

of

856Thursday, April 22, 2010

856Thursday, April 22, 2010

856Thursday, April 22, 2010

Page 9

5

A

4

3

2

1

D D

C C

+V3.3S

R1053

R1053

R1050

R1050

10K

10K

10K

10K

ns

ns

ns

ns

Input To EC

PM_EXTTS_DIMM27

PM_EXTTS_L15

R1051 0 nsR1051 0 ns

R1052 0 nsR1052 0 ns

TS#_DIMM0_110,11

PM_EXTTS#0_EC5,27

TO EC output

TS#_DIMM0_1

R1048 0 nsR1048 0 ns

R1049 0 nsR1049 0 ns

+V3.3S

+V3.3S

EC_SMB1_CLK14,22,27

EC_SMB1_DAT14,22,27

PM_THRM_DN#

G781_PULLHIGH

+V3.3S 5,10,11,12,13,14,15,16,17,18,19,20,21,22,24,25,27,28,29,34,35,36,37,38,48

R320 ns

R320 ns

100

100

0.1uF/16V,X7R

0.1uF/16V,X7R

ns

ns

8

7

6

4

SOIC8_1P27_3P9

SOIC8_1P27_3P9

ns

ns

C141

C141

SMBCLK

SMBDATA

ALERT#

THERM#

12

vdd

1

VCC

G781

G781

ADM1032AR

ADM1032AR

LM86CIM

LM86CIM

MAX6657MSA

MAX6657MSA

SOIC-8

SOIC-8

GND

5

U2

U2

2

DXP

2200pF/25V,X7R ns

2200pF/25V,X7R ns

3

DXN

W83L771ASG

W83L771ASG

EC_SMB1_CLK14,22,27

EC_SMB1_DAT14,22,27

G781_PULLHIGH

C140

C140

PM_THRM_DN#

TSSOP8_P65_3P0

TSSOP8_P65_3P0

12

THERMDA

THERMDC

8

SMBCLK

7

SMBDATA

6

ALERT#

4

THERM#

vdd

5

1

1

DXP

VCC

DXN

G781

G781

ADM1032AR

ADM1032AR

LM86CIM

LM86CIM

MAX6657MSA

MAX6657MSA

SOIC-8

SOIC-8

GND

W83L771 TSSOP8

W83L771 TSSOP8

ns

ns

U28

U28

2 3

Q155

Q155

MMBT3904-F

MMBT3904-F

ns

ns

2

3

Under DIMM

THERMDA

THERMDC

B B

A

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet of

R48 C

R48 C

R48 C

zw

zw

zw

956Thursday, April 22, 2010

956Thursday, April 22, 2010

956Thursday, April 22, 2010

of

of

Page 10

5

4

3

2

1

Channel A High :9.2mm

DIMM1A

M_A_A[15:0]6

D D

M_A_BS06

M_A_BS16

M_A_BS26

M_CS_L06

M_CS_L16

M_CLK_DDR06

M_CLK_DDR0_L6

M_CLK_DDR16

M_CLK_DDR1_L6

M_CKE06

M_CKE16

M_A_CAS_L6

M_A_RAS_L6

M_A_WE_L6

M_ODT06

M_ODT16

SODIMM0_1_SMB_CLK_R

SODIMM0_1_SMB_DATA_R

SMB_CLK_S211,12,14

SMB_DATA_S211,12,14

M_A_DM[7:0]6

C C

M_A_DQS[7:0]6

M_A_DQS_L[7:0]6

B B

+V1.5

M_CS_L0

M_CS_L1

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

SA0_DIM0

SA1_DIM0

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS_L0

M_A_DQS_L1

M_A_DQS_L2

M_A_DQS_L3

M_A_DQS_L4

M_A_DQS_L5

M_A_DQS_L6

M_A_DQS_L7

DIMM1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDRIIISODIMM-204PS_BLACK-RH-1

DDRIIISODIMM-204PS_BLACK-RH-1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_A_DQ0

5

M_A_DQ1

7

M_A_DQ2

15

M_A_DQ3

17

M_A_DQ4

4

M_A_DQ5

6

M_A_DQ6

16

M_A_DQ7

18

M_A_DQ8

21

M_A_DQ9

23

M_A_DQ10

33

M_A_DQ11

35

M_A_DQ12

22

M_A_DQ13

24

M_A_DQ14

34

M_A_DQ15

36

M_A_DQ16

39

M_A_DQ17

41

M_A_DQ18

51

M_A_DQ19

53

M_A_DQ20

40

M_A_DQ21

42

M_A_DQ22

50

M_A_DQ23

52

M_A_DQ24

57

M_A_DQ25

59

M_A_DQ26

67

M_A_DQ27

69

M_A_DQ28

56

M_A_DQ29

58

M_A_DQ30

68

M_A_DQ31

70

M_A_DQ32

129

M_A_DQ33

131

M_A_DQ34

141

M_A_DQ35

143

M_A_DQ36

130

M_A_DQ37

132

M_A_DQ38

140

M_A_DQ39

142

M_A_DQ40

147

M_A_DQ41

149

M_A_DQ42

157

M_A_DQ43

159

M_A_DQ44

146

M_A_DQ45

148

M_A_DQ46

158

M_A_DQ47

160

M_A_DQ48

163

M_A_DQ49

165

M_A_DQ50

175

M_A_DQ51

177

M_A_DQ52

164

M_A_DQ53

166

M_A_DQ54

174

M_A_DQ55

176

M_A_DQ56

181

M_A_DQ57

183

M_A_DQ58

191

M_A_DQ59

193

M_A_DQ60

180

M_A_DQ61

182

M_A_DQ62

192

M_A_DQ63

194

M_A_DQ[63:0] 6

+V3.3S

C95

C95

C94

C94

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

0.1uF/16V,X7R

0.1uF/16V,X7R

TS#_DIMM0_19,11

DDR3_DRAMRST_L5,11

M_VREF_DQ_DIMM0C8

R1157 0 nsR1157 0 ns

M_VREF11,33

VRefCA on both SO-DIMMs can be connected by a single M_VREF_MCH trace

VRefDQ on both SO-DIMMs can be shared by a second separate M_VREF_MCH trace

+V0.75S

C100

C100

1uF/10V,X5R

1uF/10V,X5R

M_VREF_DQ_DIMM0C

C97

C97

C96

C96

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

0.1uF/16V,X7R

0.1uF/16V,X7R

M_VREF_DQ_DIMM0

C98

C98

C99

C99

0.1uF/16V,X7R

0.1uF/16V,X7R

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

C101

C101

1uF/10V,X5R

1uF/10V,X5R

C102

C102

1uF/10V,X5R

1uF/10V,X5R

+V1.5

C103

C103

1uF/10V,X5R

1uF/10V,X5R

DIMM1B

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS

3

VSS

8

VSS

9

VSS

13

VSS

14

VSS

19

VSS

20

VSS

25

VSS

26

VSS

31

VSS

32

VSS

37

VSS

38

VSS

43

VSS

DDRIIISODIMM-204PS_BLACK-RH-1

DDRIIISODIMM-204PS_BLACK-RH-1

Place near Vtt pins

DIMM1B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

VTT

204

VTT

205

205

206

206

Place these caps

close to VTT1 and

VTT2. Place C21

on common path

for both DIMM's

+V0.75S

Place two capacitors close to the VR

Layout Note: Place

C110

C110

+

C107

C106

C105

C104

C104

10UF/6.3V,X5R

10UF/6.3V,X5R

+V3.3S

Note:

If SA0_DIM0 = 0, SA1_DIM0 = 0

SO-DIMM0 SPD Address is 0xA0

SO-DIMM0 TS Address is 0x30

If SA0_DIM0 = 1, SA1_DIM0 = 0

A A

SO-DIMM0 SPD Address is 0xA2

SO-DIMM0 TS Address is 0x32

NO_STUFF

R53

R53

10K

10K

ns

ns

R54

R54

10K

10K

R55

R55

10K

10K

SA0_DIM0

SA1_DIM0

5

C105

10UF/6.3V,X5R

10UF/6.3V,X5R

4

C106

10UF/6.3V,X5R

10UF/6.3V,X5R

C107

10UF/6.3V,X5R

10UF/6.3V,X5R

C108

C108

10UF/6.3V,X5R

10UF/6.3V,X5R

+V1.5 5,7,8,11,33,35

+V3.3S 5,9,11,12,13,14,15,16,17,18,19,20,21,22,24,25,27,28,29,34,35,36,37,38,48

+V0.75S 11,28,33

C109

C109

10UF/6.3V,X5R

10UF/6.3V,X5R

3

+

220uF/6.3V,POSCAP

220uF/6.3V,POSCAP

ns

ns

NO_STUFF

these Caps near

SO-DIMM1.

+V1.5

C111

C111

1uF/10V,X5R

1uF/10V,X5R

Title

Title

Title

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

2

and one between the two DIMMs

C112

C112

1uF/10V,X5R

1uF/10V,X5R

CZC Technology

CZC Technology

CZC Technology

C113

C113

1uF/10V,X5R

1uF/10V,X5R

Panel &VGA connect

Panel &VGA connect

Panel &VGA connect

R48 C

R48 C

R48 C

C114

C114

1uF/10V,X5R

1uF/10V,X5R

zw

zw

zw

of

of

of

10 56Thursday, April 22, 2010

10 56Thursday, April 22, 2010

10 56Thursday, April 22, 2010

1

Page 11

5

4

3

2

1

Channel B High :5.2mm

DIMM2A

M_B_A[15:0]6

D D

M_B_BS06

M_B_BS16

M_B_BS26

M_CS_L26

M_CS_L36

M_CLK_DDR26

M_CLK_DDR2_L6

M_CLK_DDR36

M_CLK_DDR3_L6

M_CKE26

M_CKE36

M_B_CAS_L6

M_B_RAS_L6

M_B_WE_L6

SMB_CLK_S210,12,14

C C

SMB_DATA_S210,12,14

M_ODT26

M_ODT36

M_B_DM[7:0]6

M_B_DQS[7:0]6

M_B_DQS_L[7:0]6

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

SA0_DIM1

SA1_DIM1

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS_L0

M_B_DQS_L1

M_B_DQS_L2

M_B_DQS_L3

M_B_DQS_L4

M_B_DQS_L5

M_B_DQS_L6

M_B_DQS_L7

B B

Note:

SO-DIMM1 SPD Address is 0xA4

SO-DIMM1 TS Address is 0x34

DIMM2A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDRIIISODIMM-204PS_BLACK-RH

DDRIIISODIMM-204PS_BLACK-RH

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_B_DQ1

7

M_B_DQ2

15

M_B_DQ3

17

M_B_DQ4

4

M_B_DQ5

6

M_B_DQ6

16

M_B_DQ7

18

M_B_DQ8

21

M_B_DQ9

23

M_B_DQ10

33

M_B_DQ11

35

M_B_DQ12

22

M_B_DQ13

24

M_B_DQ14

34

M_B_DQ15

36

M_B_DQ16

39

M_B_DQ17

41

M_B_DQ18

51

M_B_DQ19

53

M_B_DQ20

40

M_B_DQ21

42

M_B_DQ22

50

M_B_DQ23

52

M_B_DQ24

57

M_B_DQ25

59

M_B_DQ26

67

M_B_DQ27

69

M_B_DQ28

56

M_B_DQ29

58

M_B_DQ30

68

M_B_DQ31

70

M_B_DQ32

129

M_B_DQ33

131

M_B_DQ34

141

M_B_DQ35

143

M_B_DQ36

130

M_B_DQ37

132

M_B_DQ38

140

M_B_DQ39

142

M_B_DQ40

147

M_B_DQ41

149

M_B_DQ42

157

M_B_DQ43

159

M_B_DQ44

146

M_B_DQ45

148

M_B_DQ46

158

M_B_DQ47

160

M_B_DQ48

163

M_B_DQ49

165

M_B_DQ50

175

M_B_DQ51

177

M_B_DQ52

164

M_B_DQ53

166

M_B_DQ54

174

M_B_DQ55

176

M_B_DQ56

181

M_B_DQ57

183

M_B_DQ58

191

M_B_DQ59

193

M_B_DQ60

180

M_B_DQ61

182

M_B_DQ62

192

M_B_DQ63

194

SO-DIMM1 is placed farther from

the Processor than SO-DIMM0

M_B_DQ0

5

M_B_DQ[63:0] 6

M_VREF_DQ_DIMM1C8

R1158 0 nsR1158 0 ns

M_VREF10,33

VRefCA on both SO-DIMMs can be connected by a single M_VREF_MCH trace

VRefDQ on both SO-DIMMs can be shared by a second separate M_VREF_MCH trace

+V0.75S

C121

C121

1uF/10V,X5R

1uF/10V,X5R

+V1.5 5,7,8,10,33,35

+V3.3S 5,9,10,12,13,14,15,16,17,18,19,20,21,22,24,25,27,28,29,34,35,36,37,38,48

+V0.75S 10,28,33

+V1.5

+V3.3S

C115

C115

0.1uF/16V,X7R

0.1uF/16V,X7R

M_VREF_DQ_DIMM1C

C117

C117

0.1uF/16V,X7R

0.1uF/16V,X7R

M_VREF_DQ_DIMM1

C119

C119

0.1uF/16V,X7R

0.1uF/16V,X7R

C122

C122

1uF/10V,X5R

1uF/10V,X5R

C116

C116

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

DDR3_DRAMRST_L5,10

C118

C118

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

C120

C120

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

C123

C123

1uF/10V,X5R

1uF/10V,X5R

TS#_DIMM0_19,10

C124

C124

1uF/10V,X5R

1uF/10V,X5R

75

VDD

76

VDD

81

VDD

82

VDD

87

VDD

88

VDD

93

VDD

94

VDD

99

VDD

100

VDD

105

VDD

106

VDD

111

VDD

112

VDD

117

VDD

118

VDD

123

VDD

124

VDD

199