AVER AL440B-24, AL440B-12 Datasheet

AL440B Data Sheets

Version 1.0

AVERLOGIC TECHNOLOGIES, INC. TEL: 1 408 361-0400 e-mail: sales@averlogic.com URL: www.averlogic.com

November 28, 2001

AL440B

Amendments

11-28-01 AL440B version 1.0 release data sheets.

AL440B November 28, 2001 2

AL440B

AL440B 4MBits FIFO Field Memory

Contents:

1.0 Description _________________________________________________________________ 4

2.0 Features____________________________________________________________________ 4

3.0 Applications_________________________________________________________________ 4

4.0 Ordering Information_________________________________________________________ 4

5.0 Pin-out Diagram _____________________________________________________________ 5

6.0 Block Diagram ______________________________________________________________ 5

7.0 Pin Definition and Description__________________________________________________ 6

8.0 Register Definition ___________________________________________________________ 8

8.1 Register Set ____________________________________________________________________________ 8

9.0 Multiple Devices Bus Expansion and Cascading ___________________________________ 9

10.0 Serial Bus Interface _________________________________________________________ 9

11.0 Memory Operation _________________________________________________________ 11

11.1 Power-On-Reset & Initialization __________________________________________________________ 11

11.2 WRST, RRST Reset Operation ___________________________________________________________ 11

11.3 Control Signals Polarity Select ___________________________________________________________ 11

11.4 FIFO Write Operation __________________________________________________________________ 12

11.5 FIFO Read Operation___________________________________________________________________ 12

11.6 IRDY, ORDY Flags____________________________________________________________________ 13

11.7 Window Write Register Programming _____________________________________________________ 14

11.8 Window Read Register Programming ______________________________________________________ 17

12.0 Electrical Characteristics ____________________________________________________ 19

12.1 Absolute Maximum Ratings _____________________________________________________________ 19

12.2 Recommended Operating Conditions ______________________________________________________ 19

12.3 DC Characteristics_____________________________________________________________________ 19

12.4 AC Characteristics_____________________________________________________________________ 20

13.0 Timing Diagrams __________________________________________________________ 22

14.0 Mechanical Drawing – 44 PIN PLASTIC TSOP (II) ______________________________ 30

15.0 Application Notes __________________________________________________________ 32

15.1 Chip Global Reset Recommend Circuit _____________________________________________________ 32

15.2 The AL440B Reference Schematic ________________________________________________________ 32

AL440B November 28, 2001 3

AL440B

1.0 Description

The AL440B 4Mbits (512k x 8-bit) FIFO memory provides completely independent 8bit input and

output ports that can operate at a maximum speed of 80 MHz. The built-in address and pointer

control circuits provide a very easy-to-use memory interface that greatly reduces design time and

effort. Manufactured using state-of-the-art embedded high density memory cell array, the AL440B

uses high performance process technologies with extended controller functions (write mask, read

skip.. etc.), allowing easy operation of non-linearity and regional read/write FIFO for PIP, Digital

TV, security system and video camera applications. The status flags can be used to indicate

Fullness/Emptiness of the FIFO and also allow multiple cascading AL440Bs to expand the storage

depth or provide a longer delay, which cannot be achieved with only a single device. Expanding

AL440B data bus width is also possible by using multiple AL440B chips in parallel. To get better

design flexibility, the polarities of the AL440B control signals are selectable. The read and write

control signals, such as Read/Write Enable, Input/Output Enable.., can be either active low or high

by pulling /PLRTY signal to high or low respectively. In AL440B, Window data write/read and

data mirroring functions can offer better control assistance in the application design. The built-in

registers set can be easily programmed via serial bus (I2C like control bus) to perform various

useful functions such as multi-freeze, P-in-P in the digital TV, VCR, and video camera application.

Available as a 44-pin TSOP (II), the small footprint allows product designers to keep real estate to a

minimum.

2.0 Features

• 4Mbits (512k x 8 bits) organization FIFO

• Independent 8bit read/write port operations

(different read/write data rates acceptable)

• Maximum Read/write cycle time: 80Mhz

and 40Mhz (2 speed grades)

• Input Enable (write mask) / Output Enable

(data skipping) control

• Window read/write with Mirroring capable

• Selectable control signal polarity

• Input Ready / Output Ready flags

• Direct cascade connection

• Self refresh

• 3.3V ± 10% power supply

• Standard 44-pin TSOP (II) package

3.0 Applications

• Multimedia systems

• Video capture or editing systems for

NTSC/PAL or SVGA resolution

• Security systems

• Scan rate converters

• PIP (Picture-In-Picture) video display

• TBC (Time Base Correction)

• Frame synchronizer

• Digital video camera

• Hard disk cache memory

• Buffer for communication systems

** 8800MMHHzz HHiigghh--SSppeeeedd vveerrssiioon

• DTV/HDTV video stream buffer

n

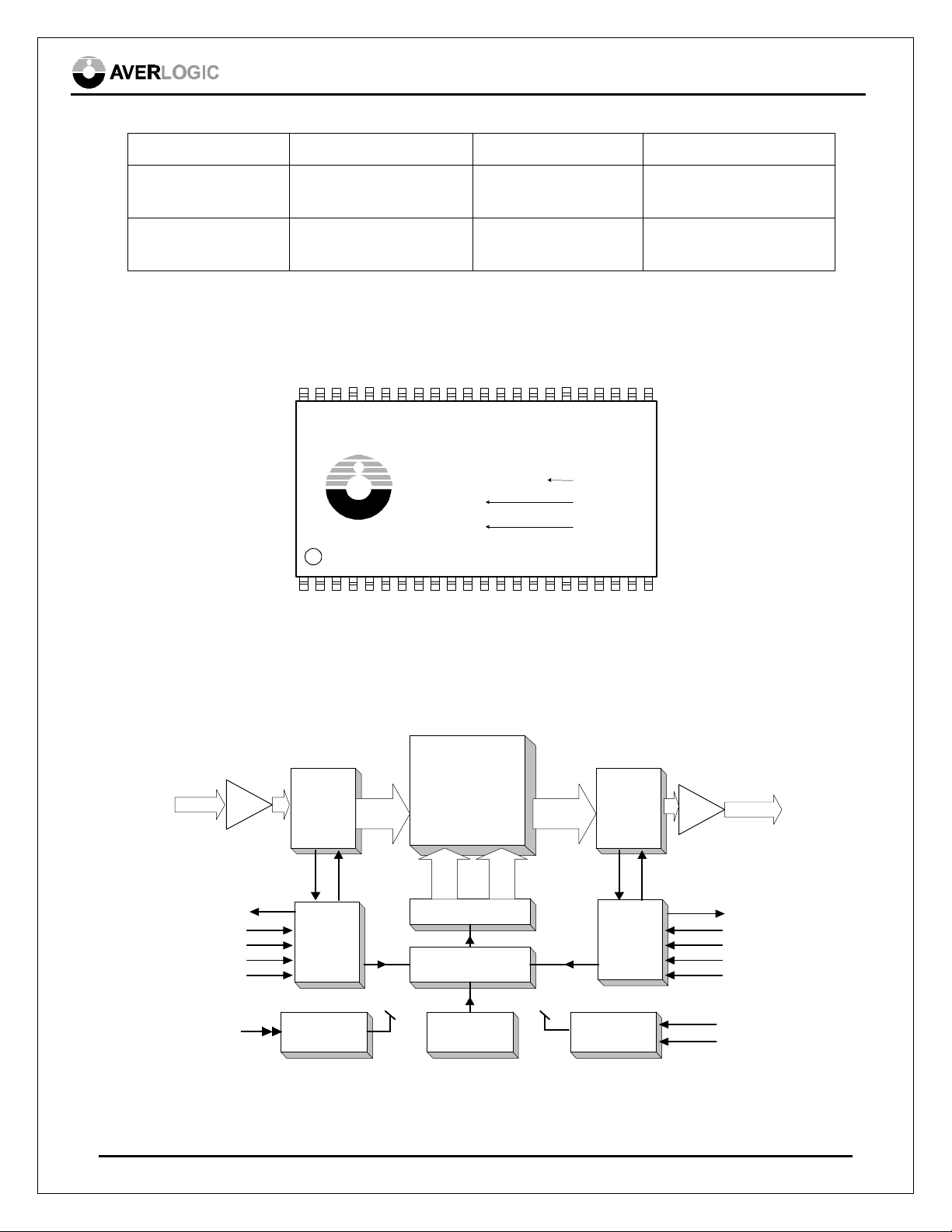

4.0 Ordering Information

The AL440B has two speed grades, AL440B-24 and AL440B-12, which can operate at frequencies

of 40MHz and 80MHz respectively. Both speed grades are powered by 3.3V and are available in a

44-pin standard TSOP-II package.

AL440B November 28, 2001 4

AL440B

Part number Package Power Supply Status

AL440B-24

(40MHz)

AL440B-12

(80MHz)

44-pin plastic

TSOP(II)

44-pin plastic

TSOP(II)

5.0 Pin-out Diagram

The AL440B pin-out diagram is following.

DO5

DO4

VDD

DO3

DO2

DO1

DO0

AVERLOGIC

1

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 202122

DI0

DI1

DI2

DI3

DI4

DI5

VDD

+3.3V±10%

+3.3V±10%

DO6

DO7

RE

OE

GND

RCK

RRST

AL440B-XX

XXXXX

XXXX

DI6

IE

DI7

WE

GND

WCK

WRST

ORDY

IRDY

VDD

/PLRTY

NC

TEST

/RESET

GND

Speed

Lot Number

Date Code

NCNCNC

AVDD

SDA

Sample Dec., 2001

Sample Dec.., 2001

SCL

23242526272829303132333435363738394041424344

AGND /SDAEN

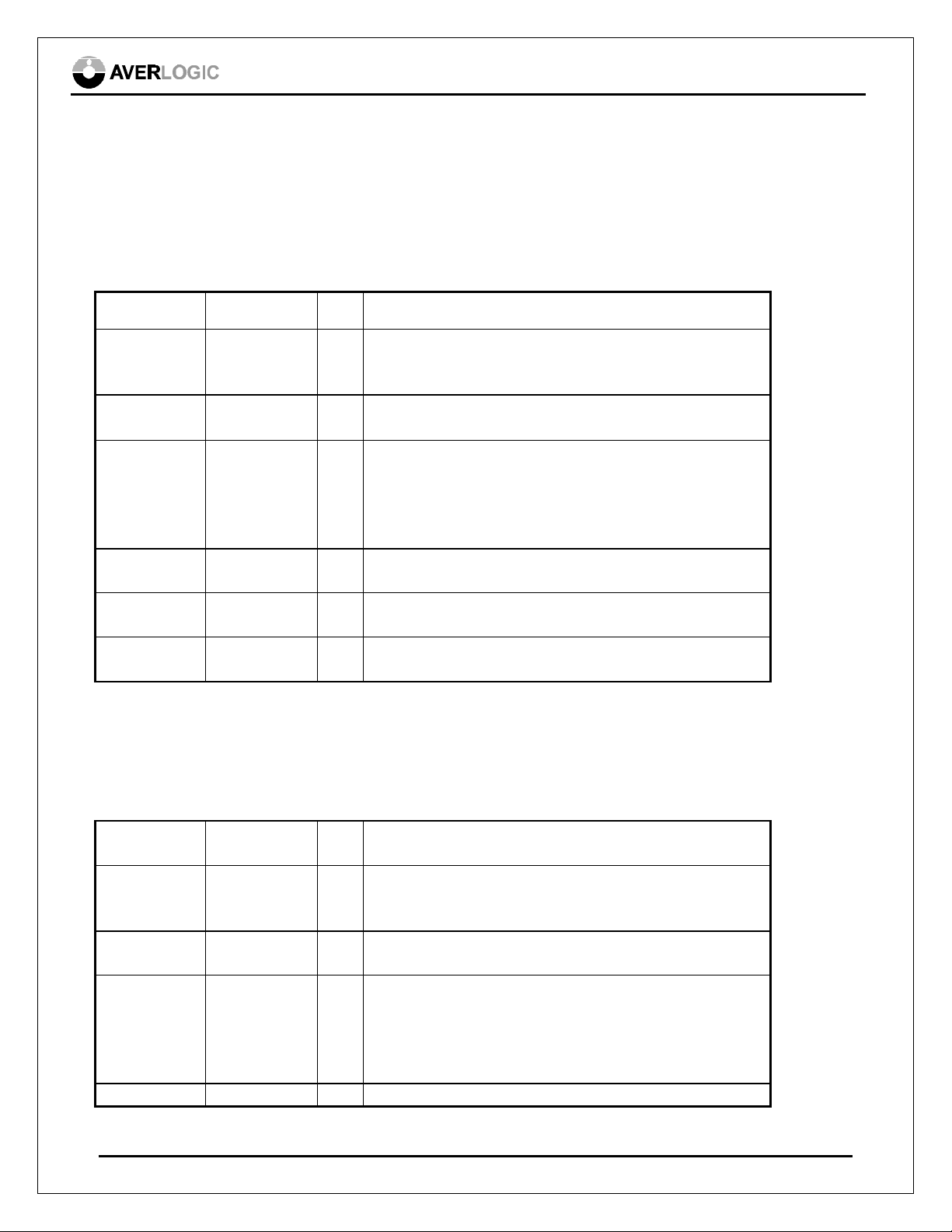

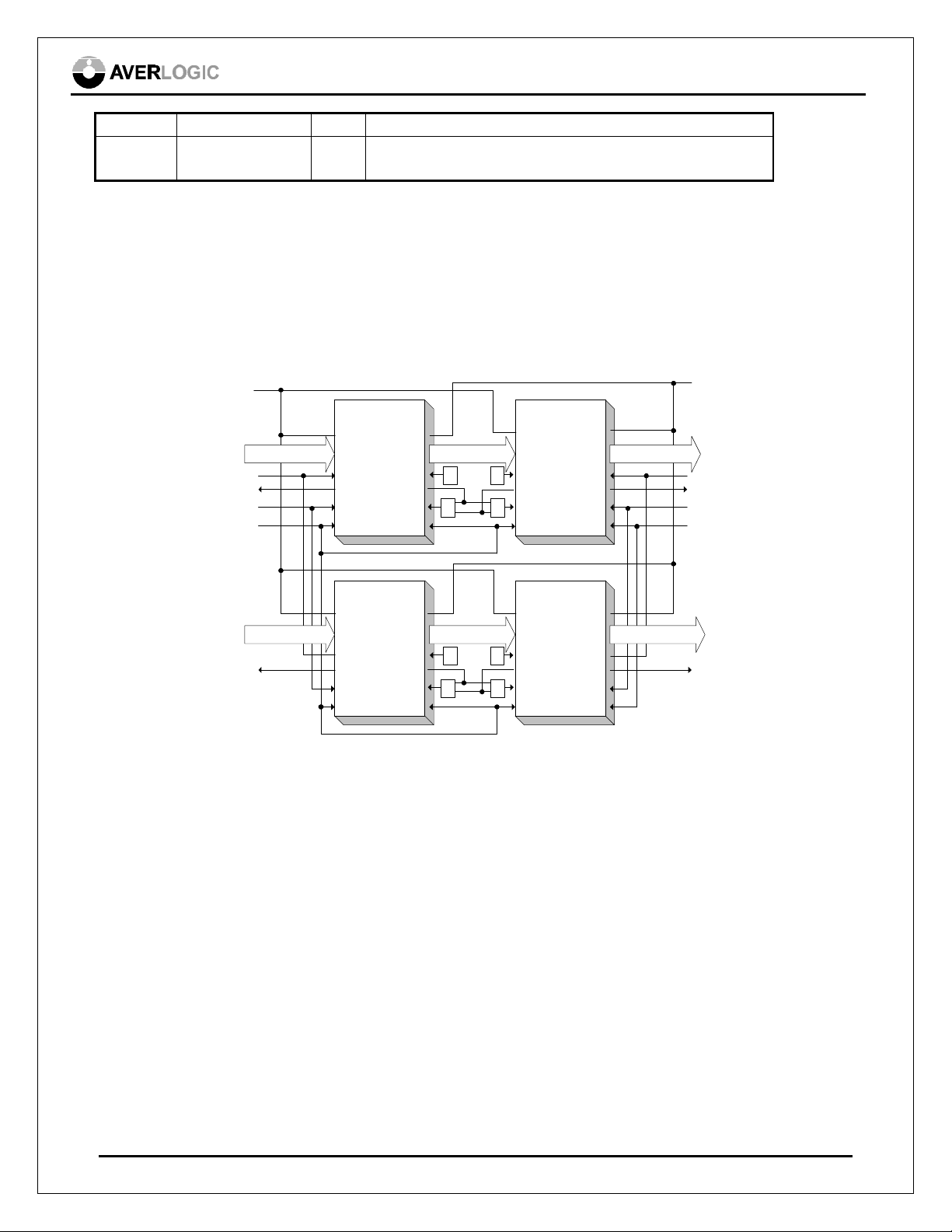

6.0 Block Diagram

DI[7:0]

WRST

/SDAEN

SCL &

SDA

IRDY

WCK

WE

Input

Buffer

IE

Write

Data

Register

Iutput

Control

Control

Registers

AL440B-12/24 TSOP (II) pinout diagram (Top view)

512kx8 memory

Internal

Bus

cell array

Bus

Control

Memory Control

Timing Generator

& Arbiter

To all

Modules

Refresh

Counter

AL440B Block Diagram

Bus

Address

Internal

Bus

To all

Modules

Read

Data

Register

Output

Control

Timing &

Logic Control

Output

Buffer

DO[7:0]

ORDY

RCK

RRST

OE

RE

/PLRTY

/RESET

AL440B November 28, 2001 5

AL440B

IRDY is a status output flag that reports the FIFO

RCK is the read clock input pin. The read data

The internal structure of the AL440B consists of an Input/Output buffers, Write Data Registers, Read

Data Registers and main 512k x8 memory cell array and the state-of-the-art logic design that takes

care of addressing and controlling the read/write data.

7.0 Pin Definition and Description

The pin definitions and descriptions are as follows:

Write Bus Signals

Pin name Pin number I/O

type

DI[7:0] 9,8,7,6,4,3,2,1 I The DI pins input 8bits of data. Data input is

synchronized with the WCK clock. Data is acquired

at the rising edge of WCK clock.

WE 10 I WE is an input signal that controls the 8bit input

data write and write pointer operation.

IE 11 I IE is an input signal that controls the enabling/

disabling of the 8bit data input pins. The internal

write address pointer is always incremented at rising

edge of WCK by enabling WE regardless of the IE

level.

WCK 13 I WCK is the write clock input pin. The write data

input is synchronized with this clock.

WRST 14 I The WRST is a reset input signal that resets the

write address pointer to 0.

IRDY 15 O

space availability.

Description

*Note: For the polarity definition of all write control signals (WE, IE, WRST and IRDY), please refer

to /PLRTY pin definition and “Memory Operation” section for details.

Read Bus Signals

Pin name Pin number I/O

type

DO[7:0] 36,37,38,39,

41,42,43,44

O The DO pins output 8bit of data. Data output is

synchronized with the RCK clock. Data is output at

the rising edge of the RCK clock.

RE 35 I RE is an input signal that controls the 8bit output

data read and read pointer operation.

OE 34 I OE is an input signal that controls the enabling/

disabling of the 8bit data output pins. The internal

read address pointer is always incremented at rising

edge of RCK by enabling RE regardless of the OE

level.

RCK 32 I

AL440B November 28, 2001 6

Description

AL440B

ORDY is a status output flag that reports the FIFO

output is synchronized with this clock.

RRST 31 I The RRST is a reset input signal that resets the read

address pointer to 0.

ORDY 30 O

data availability.

*Note: For the polarity definition of all read control signals (RE, OE, RRST and ORDY), please refer

to /PLRTY pin definition and “Memory Operation” section for details.

Serial Port Bus Signals

Pin name Pin number I/O

type

SDA 25 I/O SDA carries the serial bus read/write data bits. The

SDA data bit is valid when the SCL is high after

start up sequence.

SCL 24 I SCL supplies the serial bus clock signal to FIFO.

The serial data bit is valid when the SCL is high

after start up sequence.

/SDAEN 23 I /SDAEN controls the enabling/disabling of serial

bus interface. When /SDAEN is high, the serial

interface is disabled and SDA pin is high

impedance. When /SDAEN is low, the serial

interface is enabled and data can be written to or

read from the FIFO registers.

Description

Power/Ground Signals

Pin name Pin number I/O

type

VDD 5, 29, 40 -

3.3V ± 10%.

GND 12, 26, 33 - Ground.

AVDD 18 - Dedicated power pin for the internal oscillator. 3.3V

± 10%.

AGND 22 - Dedicated ground pin for the internal oscillator.

Description

Miscellaneous Signals

Pin name Pin number I/O

type

/RESET 27 I The global reset pin /RESET will automatically

initialize chip logic. For the recommended circuit

for the global reset signal, please refer to the

Application Notes.

Description

AL440B November 28, 2001 7

AL440B

/PLRTY 16 I Select active polarity of the control signals including

WE, RE, WRST, RRST, IE, OE, IRDY and ORDY

totally 8 signals

/PLRTY = VDD, active low.

/PLRTY = GND, active high.

Note: during memory operation, the pin must be

permanently connected to VDD or GND. If

/PLRTY level is changed during memory operation,

memory data is not guaranteed.

TEST 17 I For testing purpose only. No connect or connect to

Ground.

NC 19,20,21,28 - No connect or connect to Ground

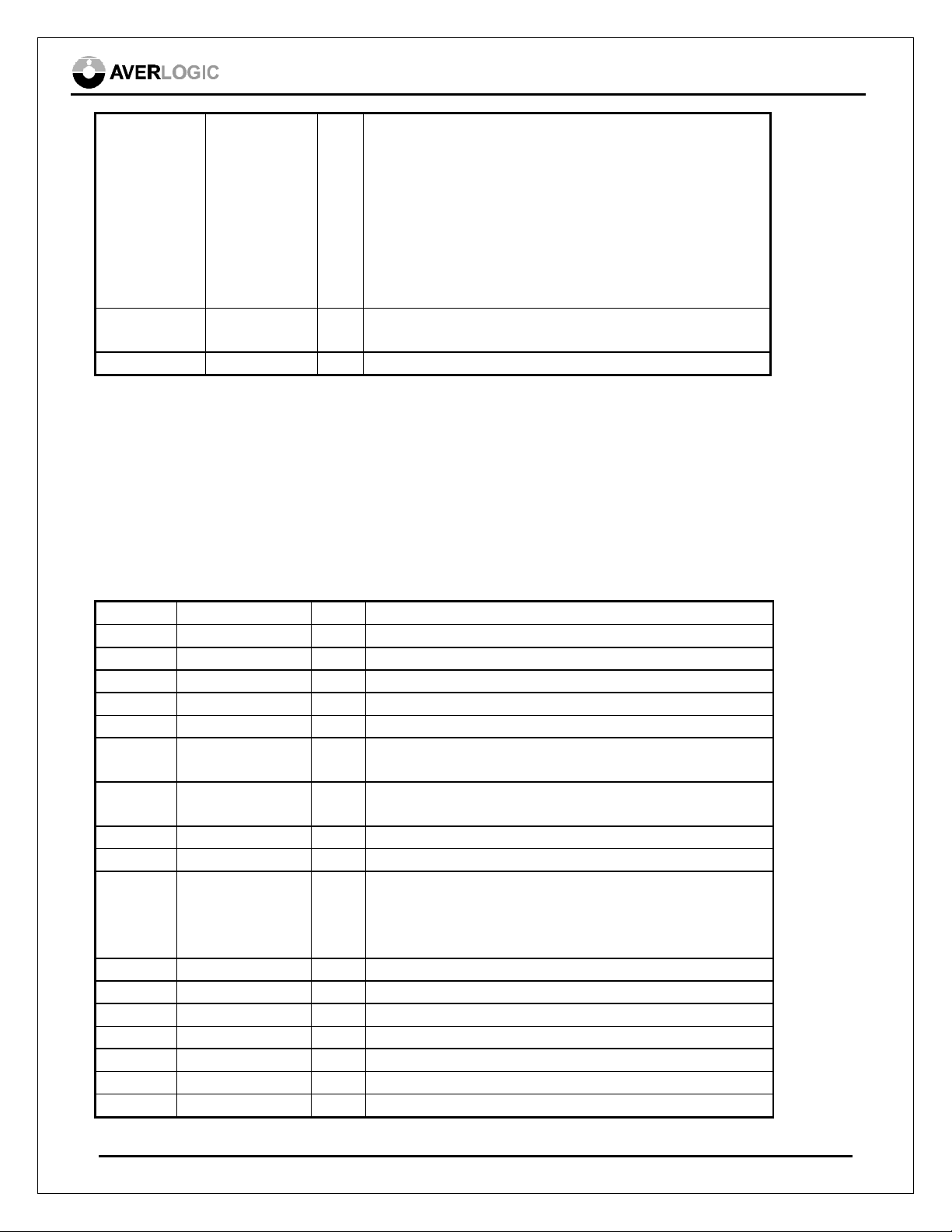

8.0 Register Definition

There are some built-in registers in the AL440B that allows performing some optional functions such

as window read/write access. These registers can be programmed via serial bus (SDA, SCL and

/SDAEN). The serial bus interface protocol is illustrated in “Serial Bus Interface” chapter. The

serial bus control software code or tool is available at Averlogic Technologies, Inc. upon request.

8.1 Register Set

Address

00h COMPANYID R Company ID (46h)

02h WSTART_L R/W Window write starting address (Low byte)

03h WSTART_H R/W Window write starting address (High byte)

04h WXSIZE_L R/W Window write horizontal size (Low byte)

05h WXSIZE_H R/W Window write horizontal size (High byte)

06h WSTRIDE_L R/W Window write strike size (Low byte)

07h WSTRIDE_H R/W Window write strike size (High byte)

08h WYSIZE_L R/W Window write vertical size (Low byte)

09h WYSIZE_H R/W Window write vertical size (High byte)

0Ah WWCTRL R/W Window write control register

0Bh RSTART_L R/W Window read starting address (Low byte)

0Ch RSTART_H R/W Window read starting address (High byte)

0Dh RXSIZE_L R/W Window read horizontal size (Low byte)

0Eh RXSIZE_H R/W Window read horizontal size (High byte)

0Fh RSTRIDE_L R/W Window read strike size (Low byte)

10h RSTRIDE_H R/W Window read strike size (High byte)

11h RYSIZE_L R/W Window read vertical size (Low byte)

Register R/W

Description

2’s complement (for Y-mirror)

2’s complement (for Y-mirror)

[7]: enable window write function

[6]: X mirror

[5]: freeze

AL440B November 28, 2001 8

AL440B

12h RYSIZE_H R/W Window read vertical size (High byte)

13h RWCTRL R/W Window read control register

[7]: enable window read function

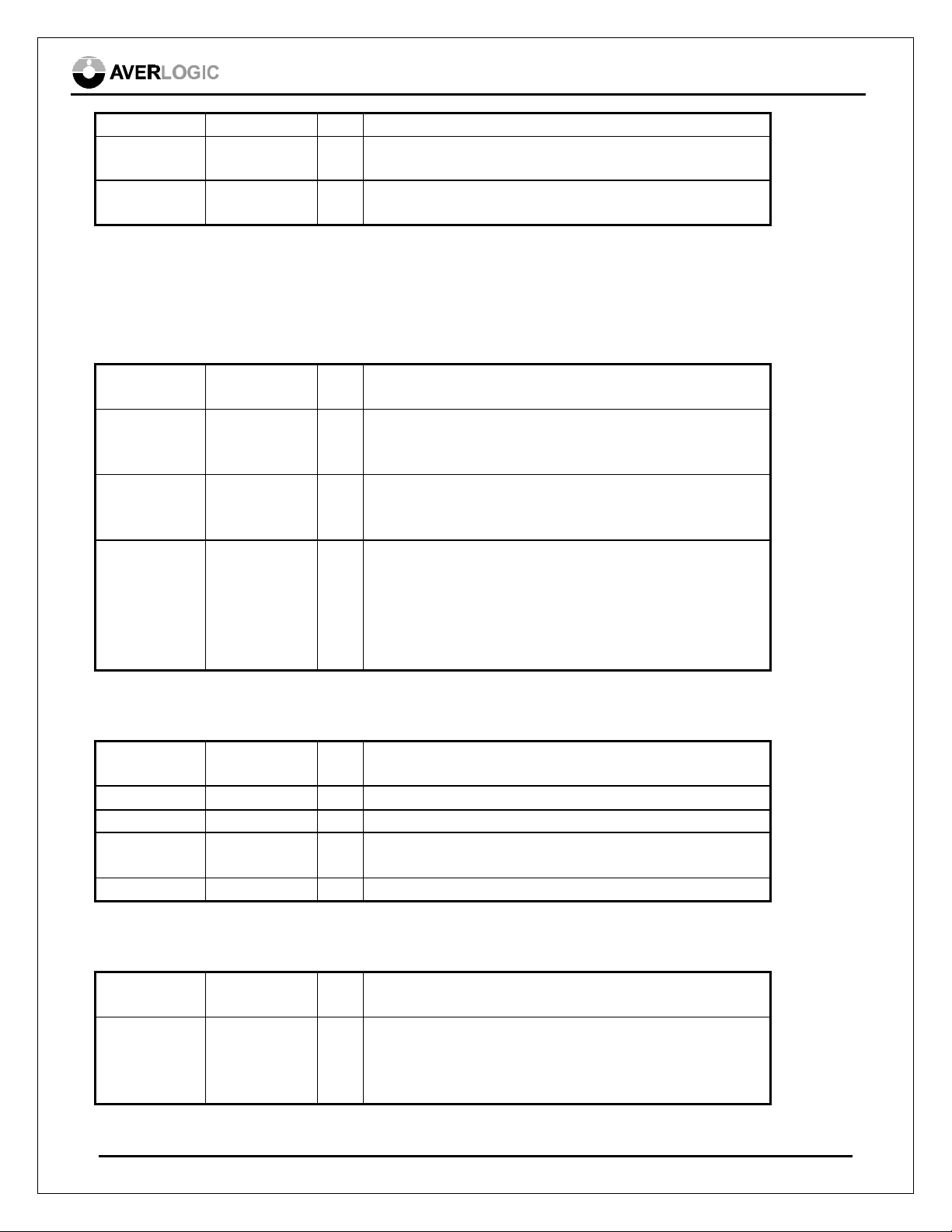

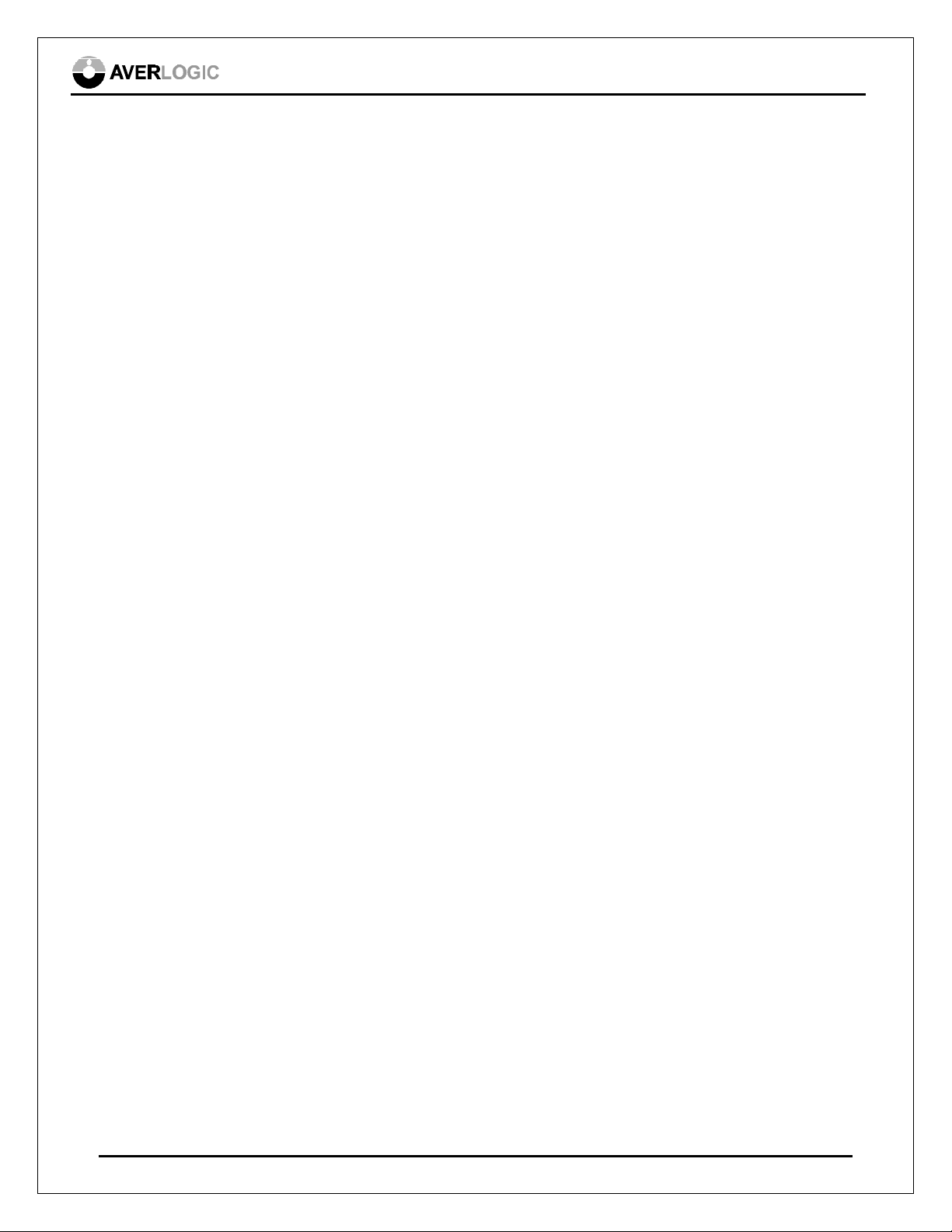

9.0 Multiple Devices Bus Expansion and Cascading

The AL440B FIFO memory can be applied to very wide range of media applications. A parallel

connect or cascade of multiple AL440B FIFOs provides FIFO bus width or memory depth expansion

for some applications; eg. accommodating HDTV resolution.. etc.

Write Reset

Read Reset

AL440

DI[7:0]

DO[7:0]

FIFO Empty

Write Enable

Write Clock

8-bit Input

FIFO Empty

(1) Logic Block: "OR" Gate if /PLTY = HIGH, "AND" Gate if /PLTY = HIGH

(2) Always Enabled : Tie to LOW if /PLTY = HIGH, Tie to High if /PLTY = LOW

IE OEInput Enable

IRDY

WE

WCK

AL440

WRST

DO[7:0]

IE IE

IRDY

WE

WCK

10.0 Serial Bus Interface

AL440

RRSTWRST

8-bit Output

ORDY

RCK

RRST

ORDY

RCK

(2)

(1) (1)

RE

8-bit OutputDI[7:0]

OE OE

(2) (2)

RE

AL440B Expanding & Cascading

WRST

DI[7:0]

IE

(2)

IRDY

WE

WCK

AL440

WRST

DI[7:0]

IRDY

(1)(1)

WE

WCK

RRST

DO[7:0]

OE

ORDY

RE

RCK

RRST

DO[7:0]

ORDY

RE

RCK

8-bit Output8-bit Input

Output Enable

FIFO Full

Read Enable

Read Clock

8-bit Output

FIFO Full

The serial bus interface consists of the SCL (serial clock), SDA (serial data) and /SDAEN (serial

interface enable) signals. There are pull up circuit internally for both SCL and SDA pins. When

/SDAEN is high, the serial bus interface is disabled and both SCL and SDA pins are pulled high.

When /SDAEN is low, the serial bus interface is enabled and data can be written into or read from the

AL440B register set. For both read and write, each byte is transferred MSB first and LSB last, and

the SDA data bit is valid when the SCL is pulled high. The serial bus control sample C code is

available in Averlogic Technologies, Inc. upon request.

The read/write command format is as follows:

Write: <S> <Write SA> <A> <Register Index> <A> <Data> <A> <P>

AL440B November 28, 2001 9

AL440B

Read: <S> <Write SA> <A> <Register Index> <A> <S> <Read SA> <A> <Data> <NA> <P>

Following are the details:

<S>:

Start signal

SCL SDA

High High

High Low

The Start signal is HIGH to LOW transition on the SDA line when SCL is HIGH.

<WRITE SA>:

Write Slave Address: 0h

<READ SA>:

Read Slave Address: 1h

<REGISTER INDEX>:

Value of the AL440B register index.

<A>:

Acknowledge stage

The acknowledge-related clock pulse is generated by the host (master). The host releases the SDA

line (HIGH) for the AL440B (slave) to pull down the SDA line during the acknowledge clock

pulse.

<NA>:

Not Acknowledged stage

The acknowledge-related clock pulse is generated by the host (master). The host releases the SDA

line (HIGH) during the acknowledge clock pulse, but the AL440B does not pull it down during

this stage.

<DATA>:

Data byte write to or read from the register index.

In read operation, the host must release the SDA line (high) before the first clock pulse is

transmitted to the AL440B.

<P>:

Stop signal

SCL SDA

High Low

High High

The Stop signal is LOW to HIGH transition on the SDA line when SCL is HIGH.

Suppose data F0h is to be written to register 0Fh using write slave address 0h, the timing is as

follows:

AL440B November 28, 2001 10

Loading...

Loading...