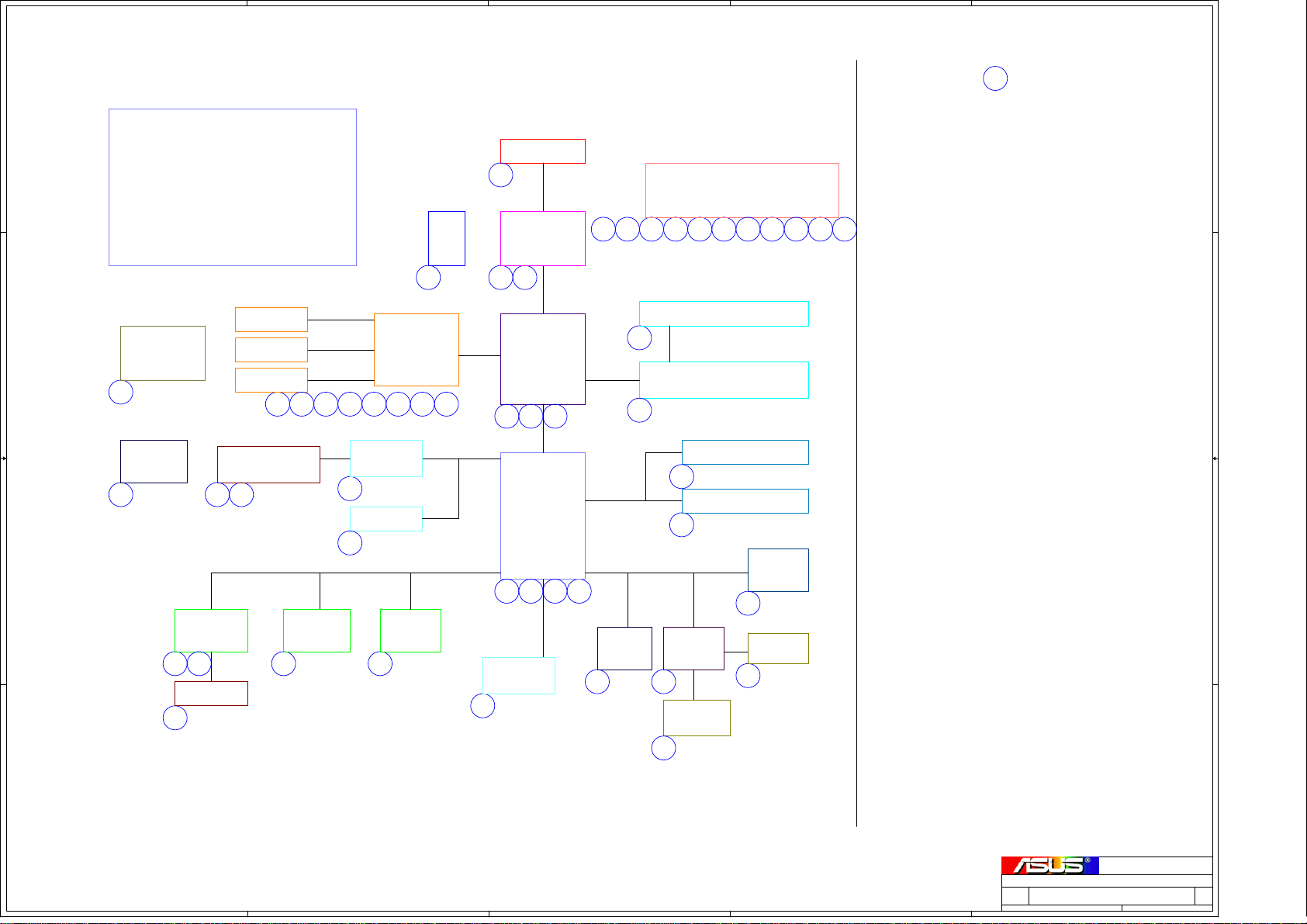

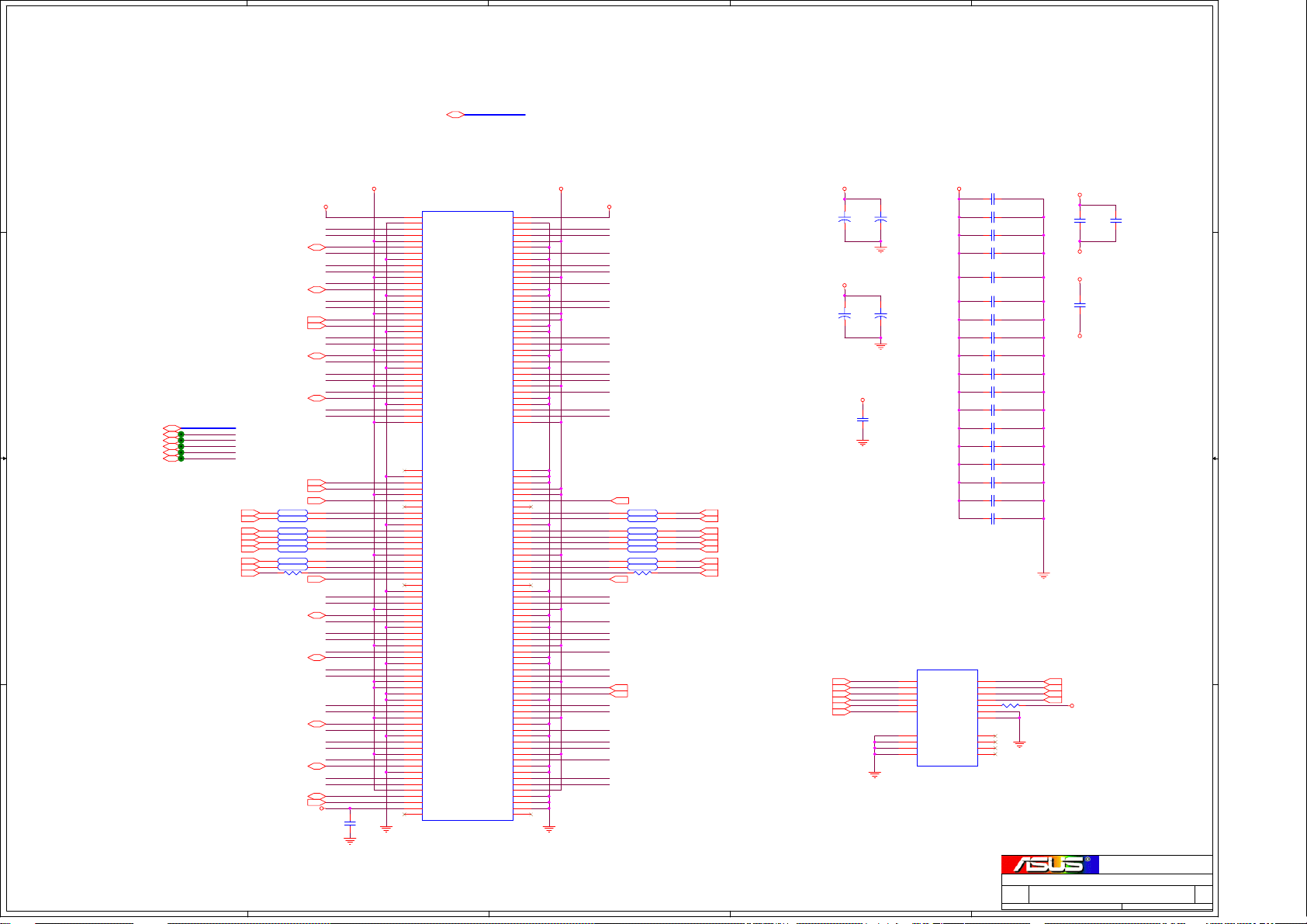

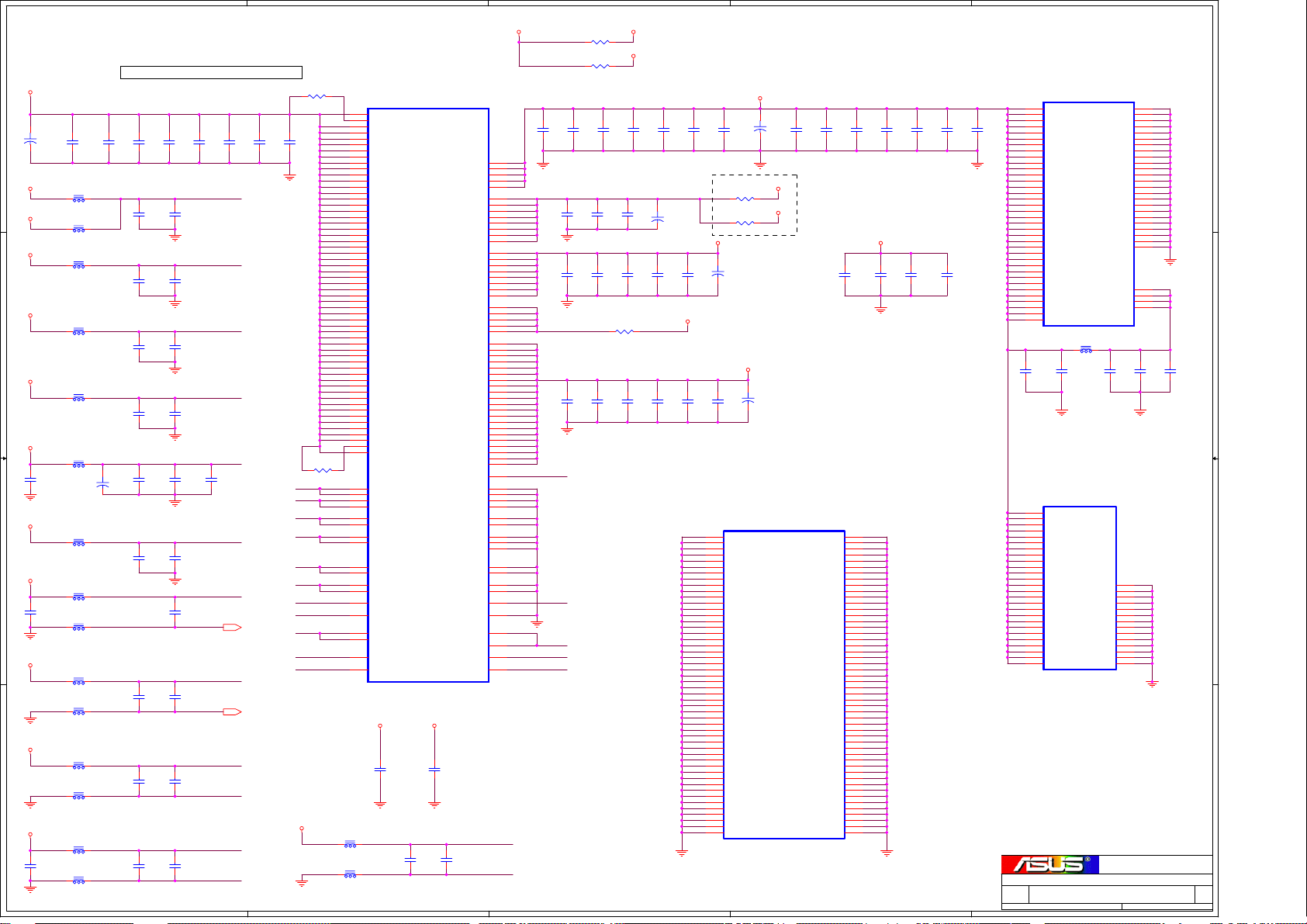

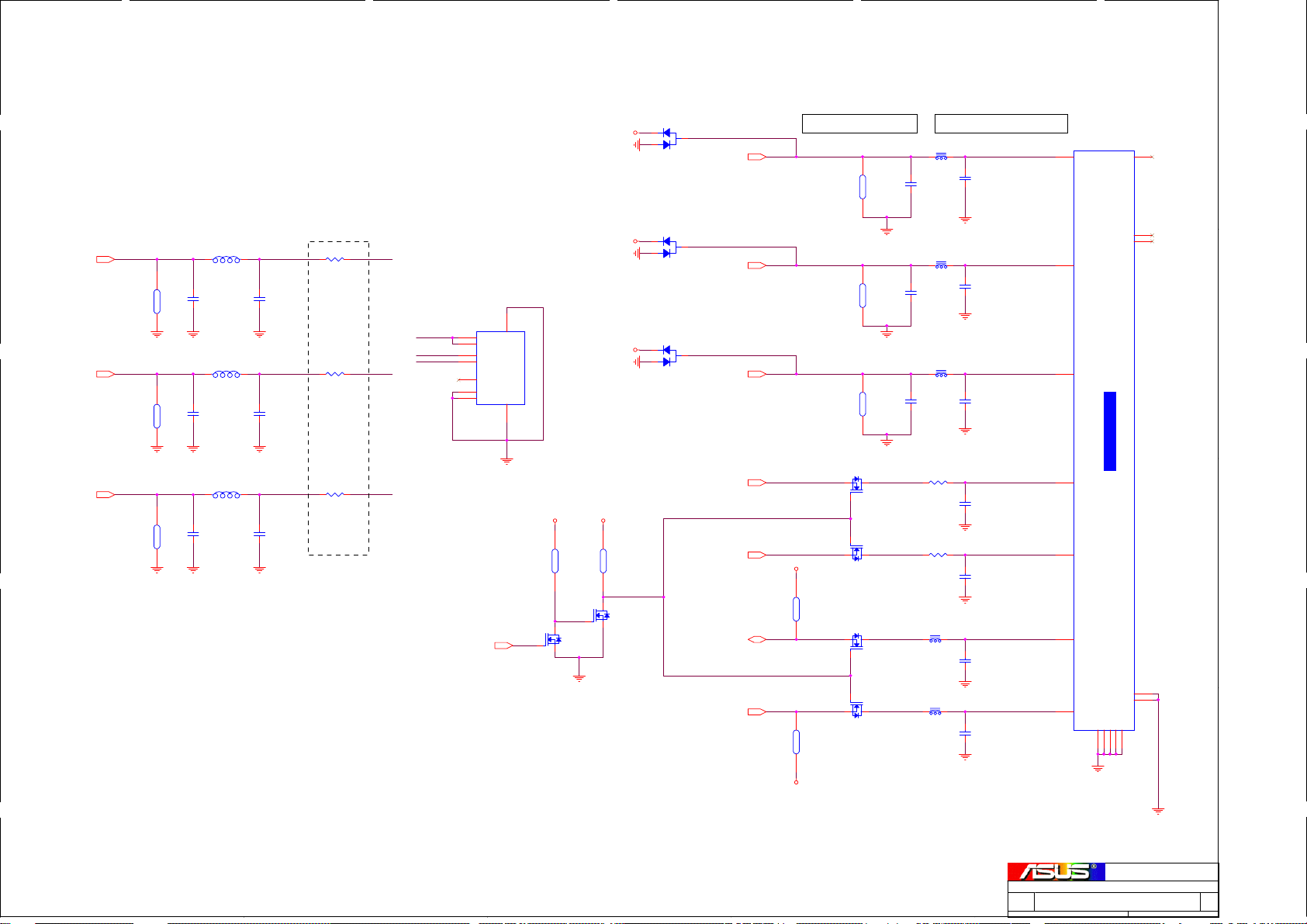

Asus A3G Schematics

5

4

3

2

01

1

FILE LIST

D D

A3G

BLOCK

DIAGRAM

FAN

39

THERMAL

05

DOTHAN

21W

03

04

POWER

(IMVP4)

41

42

44

43

46

45

47

49

48

50

PSB

LCD

C C

B B

CLOCK

GEN

22

Function

Key

40

1394

CARDBUS

26

25

AUDIO AMP

& MIC

36

35

TV

CRT

11

24

PCMCIA

27

A A

LVDS

C/Y/COMP

RGB

12 14

13

MINIPCI

34

37

VGA(M11)

9W

15

16

AC'97

CODEC

MDC

23

LAN

MCHM

AGP

MONTARA

-PM

DDR

11W

52

17

AC97

06

08

07

HUB

IDE

Ultra

ICH4

ATA100

2.9W

PCI

18

USB 2.0

USB X6

38

20

19

21

KBC

30

DDR TERMINATION

10

DUAL DDR SODIMM

09

SECONDARY IDE

29

PRIMARY IDE

28

LPC

SIO

31

PRINTER

PORT

32

DEBUG

PORT

33

IR&LPT

32

01_BLOCK DIAGRAM

02_POWER DIAGRAM

03_CPU-DOTHAN(HOST)

04_CPU-DOTHAN(PWR)

05_THERMAL

06_NB-MCHM1

07_NB-MCHM2

08_NB-MCHM3

09_DUAL_DDR

10_DDR_TERMINATION

51

11_VGA_M11-Disp Sys

12_VGA_M11-Mem IF

13_VGA_M11-PWR/GND

14_VGA_M11-VM TERMINATION

15_VGA_M11-Video RAM

16_BACKLIGHT&LCD CON

17_TV-OUT & CRT CON

18_ICH4-M(HUB_PCI)

19_ICH4-M(IDE_AC97)

20_ICH4-M(USB_PM)

21_ICH4-M(POWER)

22_CLOCK-ICS950815

23_LAN-RTL8100CL

24_MINIPCI

25_CB1394-R5C593(1)

26_CB1394-R5C593(2)

27_PCMCIA SOCKET

28_IDE-HD

29_IDE-ODD

30_KBC-M38857

31_SuperI/O&FWH

32_IR&LPT_PORT

33_DEBUG PORT

34_CODEC-ALC650

35_AUDIO AMP

36_MIC

37_MDC&RJ45&RJ11

38_USB

39_FAN&Audio DJ

40_FUNCTION KEY

41_PWR & RESET SEQ

42_VCORE

43_VGACORE

44_SYSTEM

45_2.5V&1.5V&1.35V&1.05V

46_1.25V&1.8V

47_PIC16C54C

48_CHARGER

49_AC_BAT_SYS

50_BATLOW/SD#

51_LOAD SWITCH

52_SCREW_HOLES

53_Clock Map

54_Platform Power Delivery Map

55_System Power Sequence(1)

56_System Power Sequence(2)

57_Revision History

Title :

BLOCK DIAGRAM

ASUSTECH CO.,LTD.

Size Project Name

C

5

4

3

2

Date: Sheet

Engineer:

A3G

1

HD_NB TEAM

of

153Thursday, August 19, 2004

Rev

1.2

5

D D

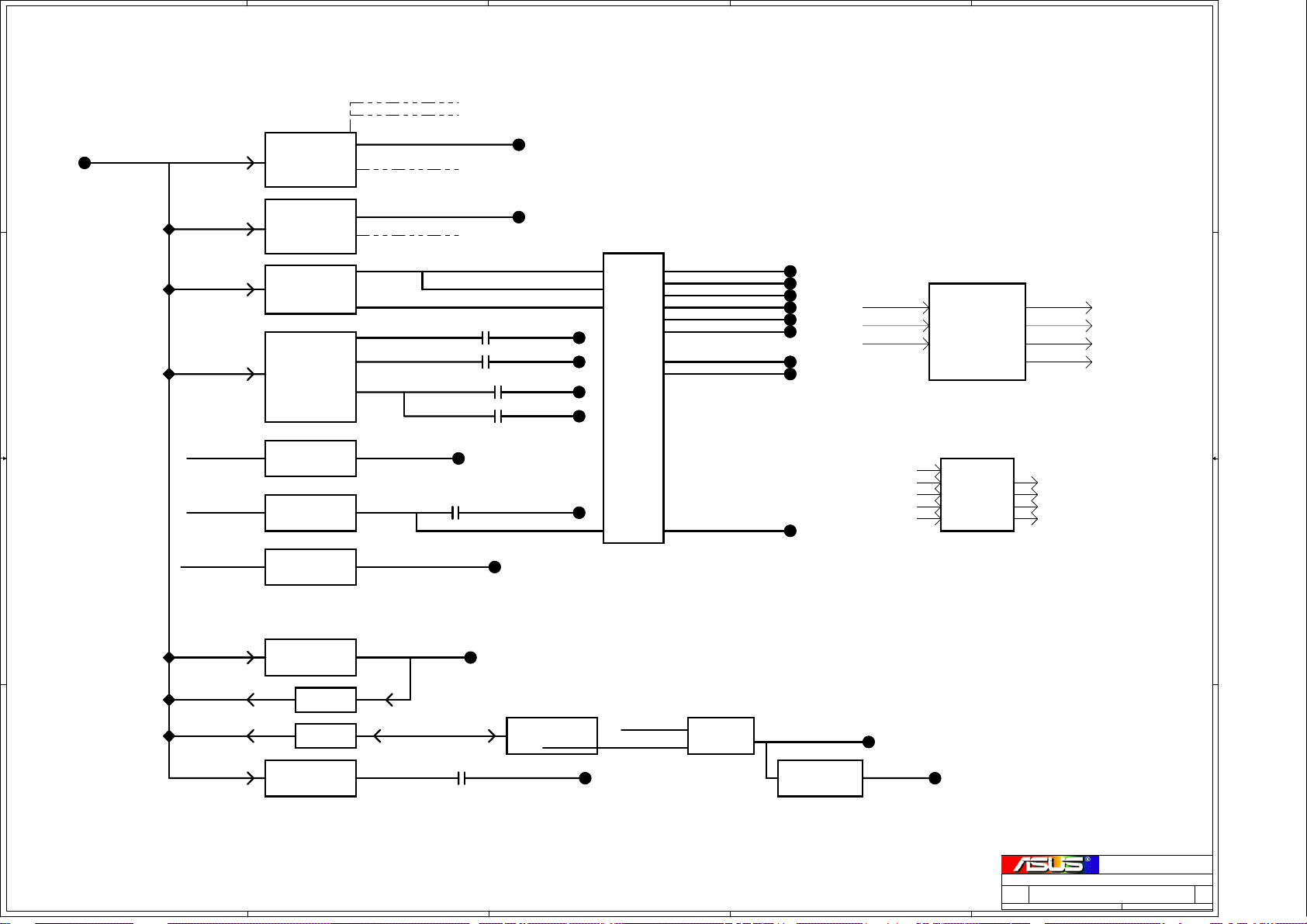

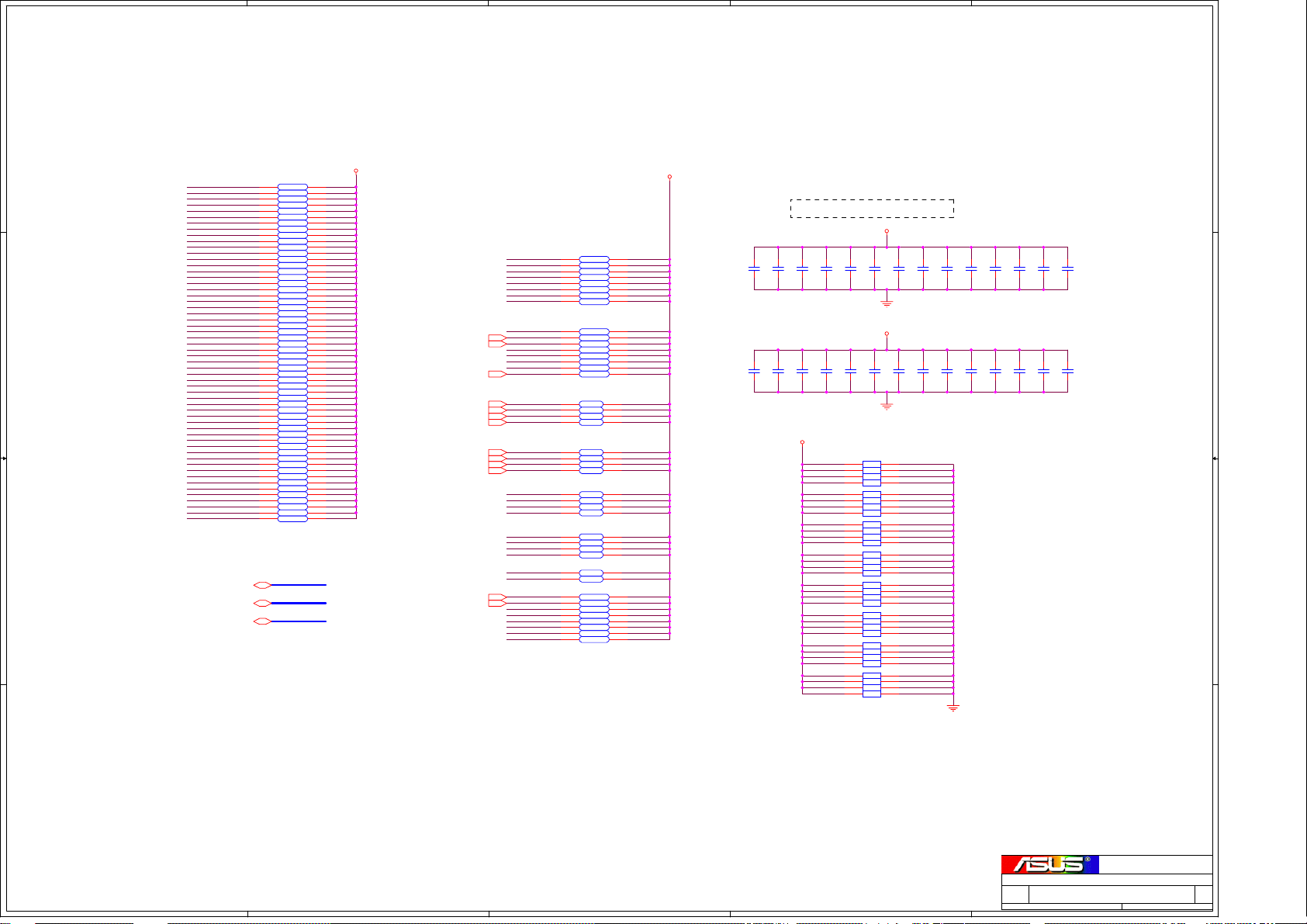

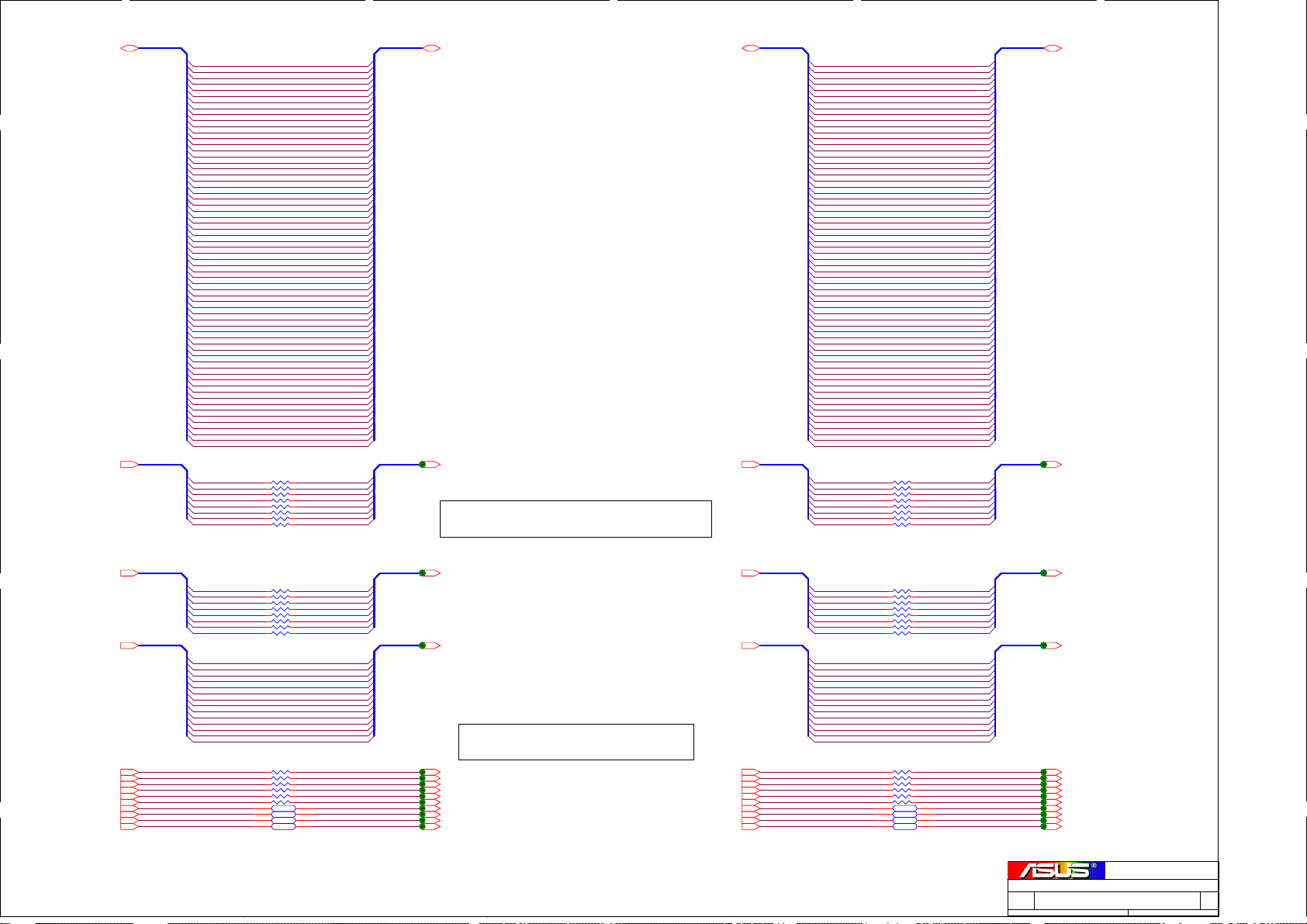

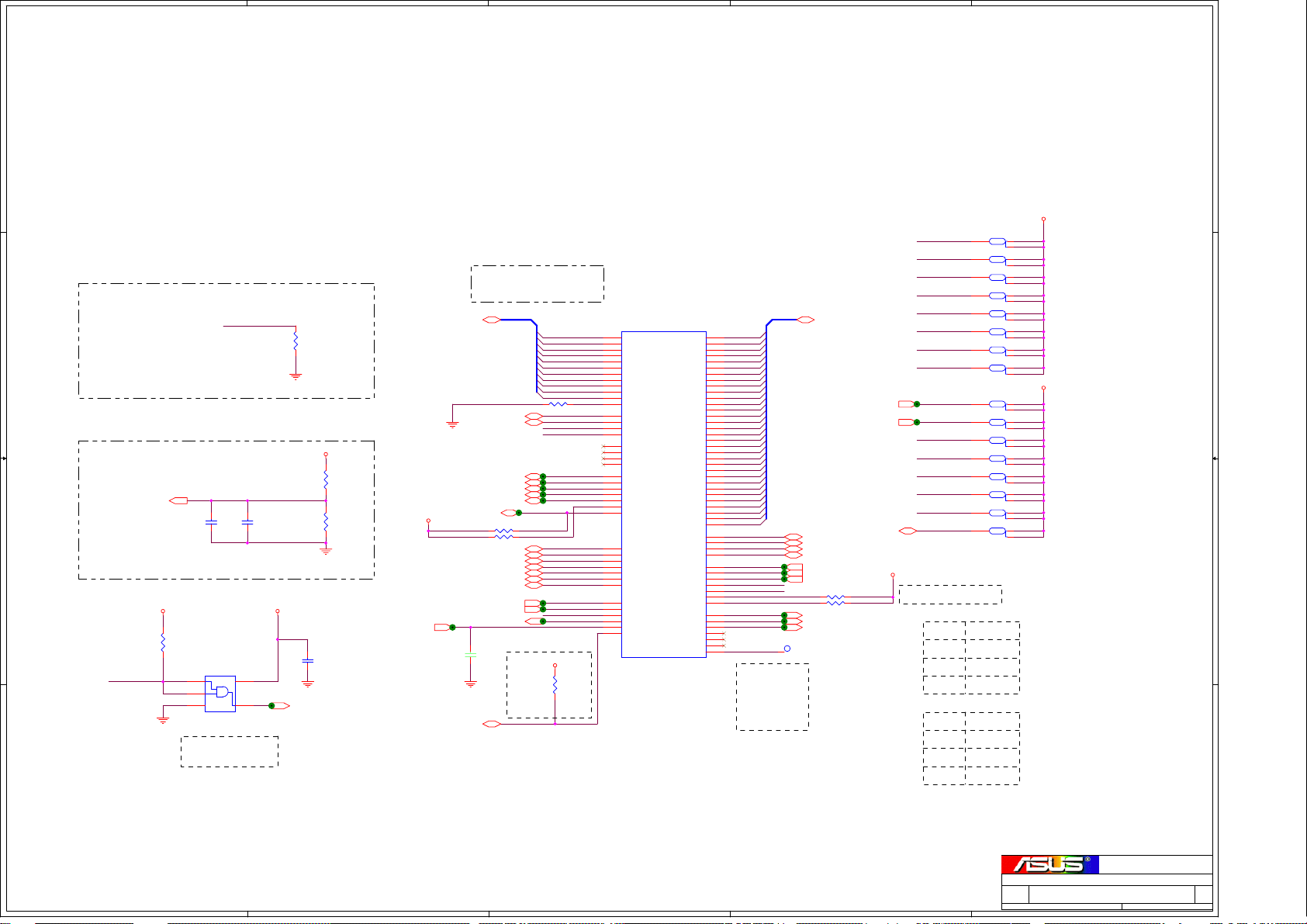

AC_BAT_SYS

(2A)

CPU_VRON

MAX1987

4

+VCORE

3

VR_VID0-VR_VID5

PM_STPCPU#.,PM_DPRSLPVR.,PCI#.,MCH_OK.,CLK_EN#

(25A)

VRM_PWRGD

2

1

(1A)

(2.5A)

C C

(2A)

MAX1844

SUSC#.

LTC3728

(Regulator)

+5VAO

TPS5130

SUSC#

SUSC#

SUSB#

(6A)

+V3.3SUS

+1.5VO

+2.5VO

(4.2A)

CPU_VRON

(8.625A)+VGACORE

(5A)

(1.35A)

(8.2A)

+1.2VO

+1.05VO

VGA_PWRGD

+5VO

+12VO

(1.9A) (1.9A)

(2.8A)

(5.5A)

(0.2A)

+V1.5

+V2.5

+V1.2S

+VCCP

(1.35A)

(8.2A)

(2.8A)

SUSB#

SUSB#

SUSB#

SUSB#

+V5S

+V3.3S

+V5

+V3

+V12S

+V12

+V1.5S

+V2.5S

(5.5A)

(5A)

(5.5A)

(5A)

(0.2A)

(0.2A)

(1.35A)

(8.2A)

A/D_VIN

BAT_S

TS

Power

Signal

Circuit

SHUT_DOWN#

BAT_IN#_OC

ACIN_OC

AC_APR_UC

SUSB#

+V2.5

+2.5VO

B B

+V3.3SUS +V1.5SUSSI9183DT

(0.5A)

(0.6A)

(2.25A)

CM8562

(Regulator)

SUSC#

MIC37101-1.8

LDO

(LDO)

PIC + TL494

(Charge)

+V1.25S

(0.8A)

(1A)

+1.8VO

(1.35A)(0.7A)

BAT

(2.5A) (10.5A)

+V1.8

(0.8A)

(0.8A)

SUSB#

SWITCH

+V1.8S

(0.8A)

SUSB#

AC_APR_UC

SMC_BAT

SMD_BAT

TS#

PIC16C54B/C

CHG EN

CHG LED

PWR LED

BAT_LLOW

FDS6679

FD6JK3TP

MIC5223MB

A A

5

(Regulator)

(10.5A)(10.5A)

(6.4A) (10mA)(6.4A)

+3VAO

A/D_VIN

(10mA)(2mA) (10mA)

4

+3VALWAYS

L78L05ACUTR

(Regulator)

+5VO

+5VCHG

3

(20mA)

(100mA)

SWITCH

(F02JK2E)

+5VLCM

(120mA)

LM4040BIM3X

(Regulator)

+2.5VREF

(500uA)

2

Title :

ASUSTECH CO.,LTD.

Size Project Name

C

Date: Sheet

Engineer:

A3G

1

POWER DIAGRAM

EDDY ZHAO

of

257Thursday, August 19, 2004

Rev

1.2

5

4

3

2

1

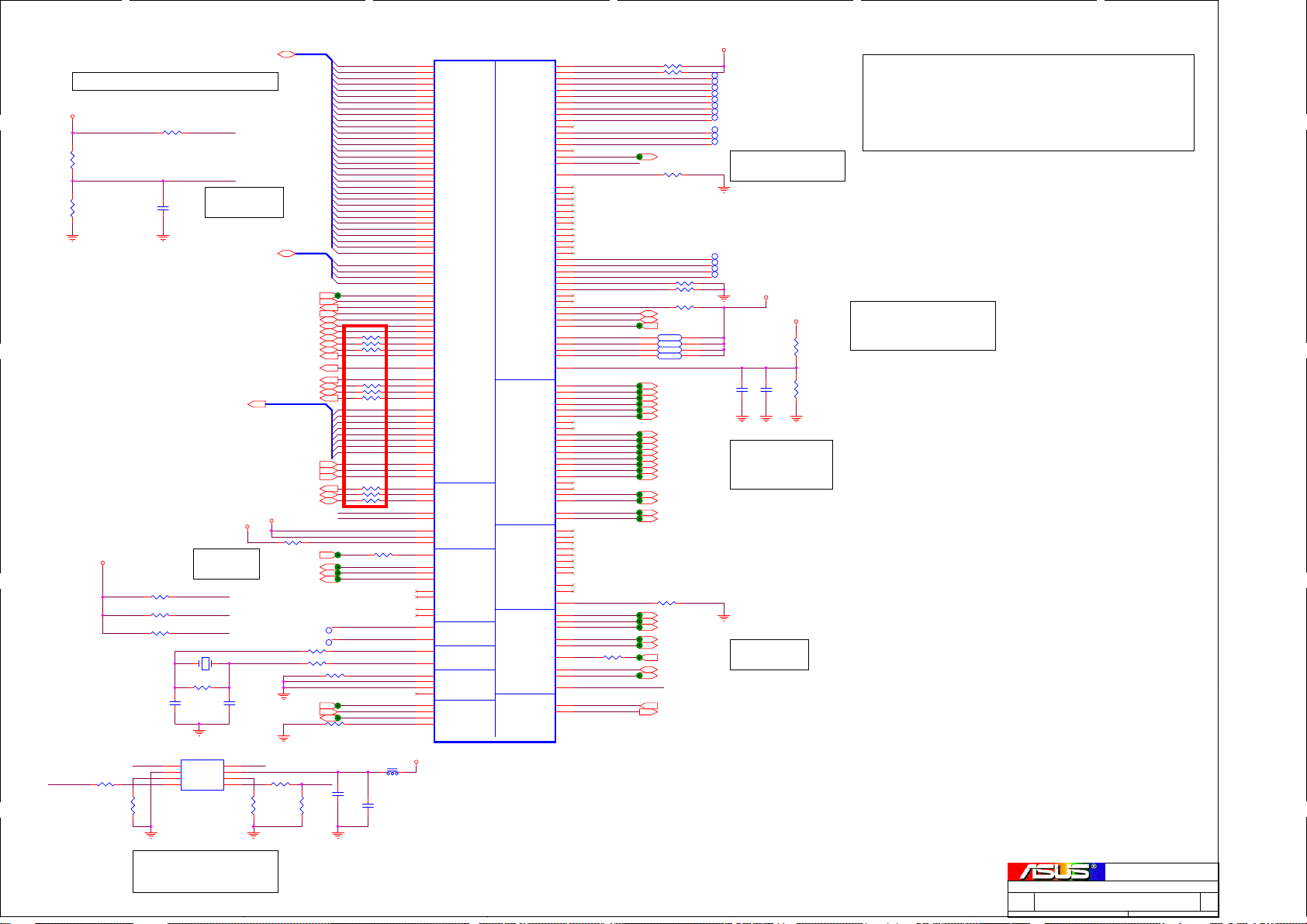

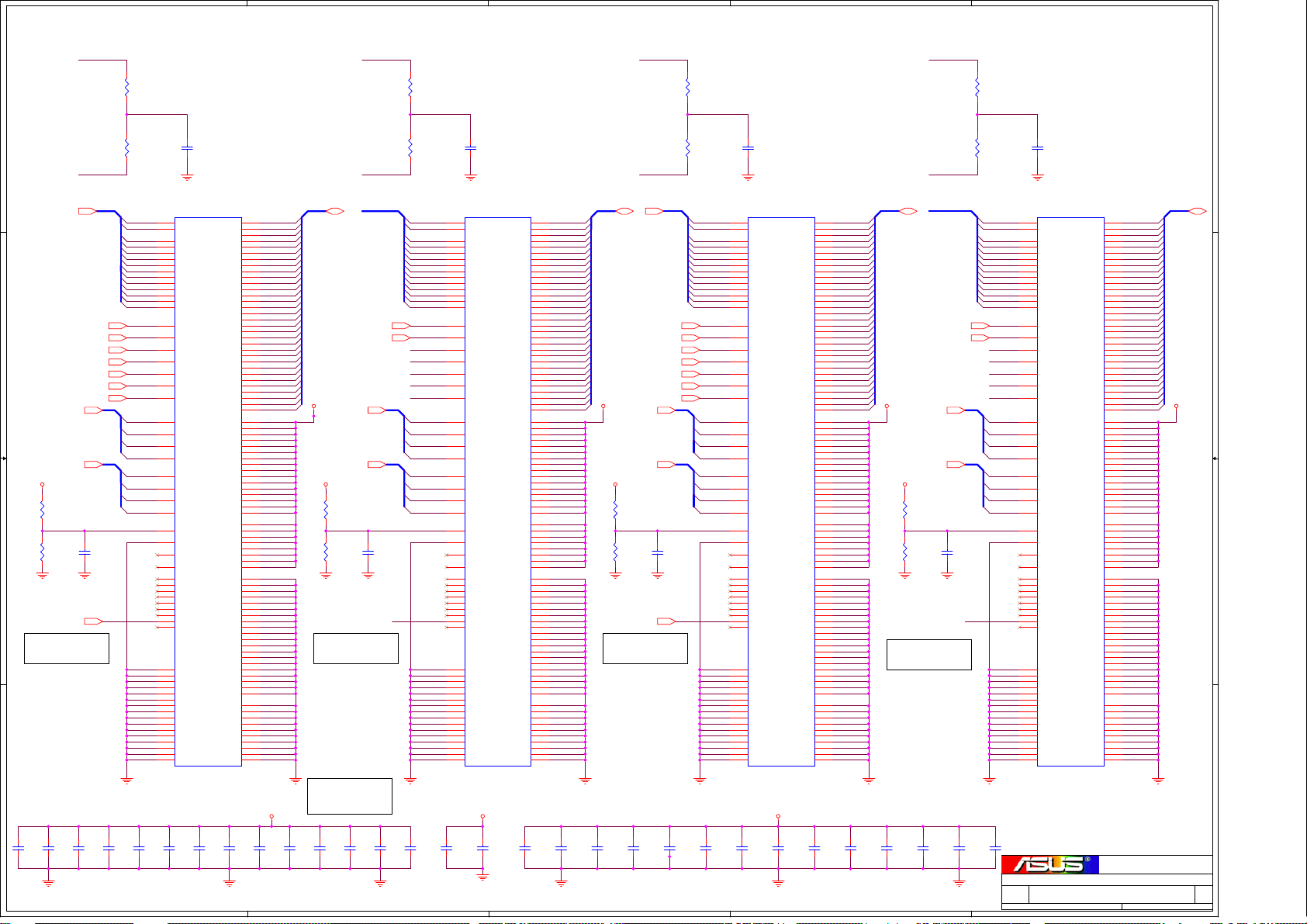

CPU Pin A1 need to be enlarged(M)

D D

WIDTH:4mils

SPACE >= 1:2

STROBE SPACE >=1:3

GROUP SPACE >=1:5

C C

LENGTH: 0.5" - 6.5"

(#0012)

H_A#[16:3]<8>

H_ADSTB#0<8>

H_REQ#[4:0]<8>

H_A#[31:17]<8>

H_ADSTB#1<8>

H_DPWR#<6>

H_A#16

H_A#15

H_A#14

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

H_A#6

H_A#5

H_A#4

H_A#3

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

1"-6.5"

AA2

Y3

AA3

U1

Y1

Y4

W2

T4

W1

V2

R3

V3

U4

P4

U3

T1

P1

T2

P3

R2

AF1

AE1

AF3

AD6

AE2

AD5

AC6

AB4

AD2

AE4

AD3

AC3

AC7

AC4

AF4

AE5

C19

U42B

A[16]#

A[15]#

A[14]#

A[13]#

A[12]#

A[11]#

A[10]#

A[9]#

A[8]#

A[7]#

A[6]#

A[5]#

A[4]#

A[3]#

ADSTB[0]#

REQ[4]#

REQ[3]#

REQ[2]#

REQ[1]#

REQ[0]#

A[31]#

A[30]#

A[29]#

A[28]#

A[27]#

A[26]#

A[25]#

A[24]#

A[23]#

A[22]#

A[21]#

A[20]#

A[19]#

A[18]#

A[17]#

ADSTB[1]#

DPWR#

SOCKET479P

ADS#

PRDY#

PREQ#

BNR#

BPRI#

DBR#

ADDRESS GROUP 0ADDRESS GROUP 1

DEFER#

DRDY#

DBSY#

BR0#

CONTROL

IERR#

INIT#

LOCK#

RESET#

RS[2]#

RS[1]#

RS[0]#

TRDY#

HIT#

HITM#

N2

H_PRDY#

A10

H_PREQ#

B10

L1

J3

A7

L4

H2

M2

H_BR0#

N4

H_IERR#

A4

0.5"-12"

B5

<=10"

J2

<=10"

B11

<=3"

H_RS#2

L2

H_RS#1

K1

H_RS#0

H1

M3

K3

K4

R362

1 2

56Ohm

H_ADS# <7>

H_BNR# <7>

H_BPRI# <7>

H_DEFER# <7>

H_DRDY# <7>

H_DBSY# <7>

H_BR0# <7>

H_INIT# <20,31>

H_LOCK# <7>

H_CPURST# <8>

H_RS#[2:0] <7>

H_TRDY# <7>

H_HIT# <7>

H_HITM# <7>

WIDTH: 5 mils

SPACE >= 1:2

GROUP SPACE >=1:5

Breakout Length:<=200 mil

LENGTH: 1" - 6.5"(OPT: 4"+/-0.5")

(#0011)

+VCCP

Here IERR# is not routed as

a test point or to any

optional system receiver

RESET# Signal Routing with

NO ITP700FLEX Connector

H_D#[63:0] <8>

H_DINV2# <8>

H_DSTBN#2 <8>

H_DSTBP#2 <8>

H_DINV3# <8>

H_DSTBN#3 <8>

H_DSTBP#3 <8>

WIDTH:4mils

SPACE >= 1:3

GROUP SPACE >=1:5

LENGTH: 0.5" - 5.5"

(#0012)

C25

E23

B23

C26

E24

D24

B24

C20

B20

A21

B26

A24

B21

A22

A25

A19

D25

C23

C22

K25

N25

H26

M25

N24

L26

J25

M23

J23

G24

F25

H24

M26

L23

G25

H23

J26

K24

L24

U42A

D[15]#

D[14]#

D[13]#

D[12]#

D[11]#

D[10]#

D[9]#

D[8]#

D[7]#

D[6]#

D[5]#

D[4]#

D[3]#

D[2]#

D[1]#

D[0]#

DINV[0]#

DSTBN[0]#

DSTBP[0]#

D[31]#

D[30]#

D[29]#

D[28]#

D[27]#

D[26]#

D[25]#

D[24]#

D[23]#

D[22]#

D[21]#

D[20]#

D[19]#

D[18]#

D[17]#

D[16]#

DINV[1]#

DSTBN[1]#

DSTBP[1]#

SOCKET479P

D[47]#

D[46]#

D[45]#

D[44]#

D[43]#

D[42]#

D[41]#

D[40]#

D[39]#

D[38]#

D[37]#

DATA GROUP 0DATA GROUP 1

D[36]#

DATA GROUP 2DATA GROUP 3

D[35]#

D[34]#

D[33]#

D[32]#

DINV[2]#

DSTBN[2]#

DSTBP[2]#

D[63]#

D[62]#

D[61]#

D[60]#

D[59]#

D[58]#

D[57]#

D[56]#

D[55]#

D[54]#

D[53]#

D[52]#

D[51]#

D[50]#

D[49]#

D[48]#

DINV[3]#

DSTBN[3]#

DSTBP[3]#

Y25

AA26

Y23

V26

U25

V24

U26

AA23

R23

R26

R24

V23

U23

T25

AA24

Y26

T24

W25

W24

AF26

AF22

AF25

AD21

AE21

AF20

AD24

AF23

AE22

AD23

AC25

AC22

AC20

AB24

AC23

AB25

AD20

AE24

AE25

H_D#47

H_D#46

H_D#45

H_D#44

H_D#43

H_D#42

H_D#41

H_D#40

H_D#39

H_D#38

H_D#37

H_D#36

H_D#35

H_D#34

H_D#33

H_D#32

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_D#53

H_D#52

H_D#51

H_D#50

H_D#49

H_D#48

H_D#15

H_D#14

H_D#13

H_D#12

H_D#11

H_D#10

H_D#9

H_D#8

H_D#7

H_D#6

H_D#5

H_D#4

H_D#3

H_D#2

H_D#1

H_DINV0#<8>

H_DSTBN#0<8>

H_DSTBP#0<8>

H_DINV1#<8>

H_DSTBN#1<8>

H_DSTBP#1<8>

H_D#0

H_D#31

H_D#30

H_D#29

H_D#28

H_D#27

H_D#26

H_D#25

H_D#24

H_D#23

H_D#22

H_D#21

H_D#20

H_D#19

H_D#18

H_D#17

H_D#16

CPU PLL

CIRCUITS

+V1.8S

12

12

12

B B

12

12

A A

C426

0.01uF/25V

GND

+V1.8S_AC26

C420

0.01uF/25V

GND

+V1.8S_N1

C166

0.01uF/25V

GND

+V1.8S_B1

C167

0.01uF/25V

GND

C425

10uF

U42C

B15

CLK_CPU100<22>

T12TPC28t

12

C423

10uF

12

C170

10uF

12

C171

Close to Pin

VCCA[3..1] of CPU

10uF

5

T13TPC28t

CLK_CPU100#<22>

1

1

/X

/X

H_A20M#<20>

H_FERR#<20>

H_IGNNE#<20>

H_DPSLP#<6,20>

H_CPUSLP#<20>

H_INTR<20>

H_NMI<20>

H_SMI#<20>

H_STPCLK#<20>

H_PWRGD<20>

+V1.8S_AC26

+V1.8S_N1

+V1.8S_B1

+V1.8S

H_THERMDA<5>

H_THERMDC<5,11>

H_THRMTRIP_S#<5,20>

PM_PSI#<42>

2"-8"

B14

2"-8"

ITP_CLK

A16

ITP_CLK#

A15

<=10"

C2

D3

0.5"-12"

A3

<=10"

B7

<=10"

A6

<=10"

D1

<=10"

D4

<=10"

B4

<=10"

<=10"

C6

E4

<=10"

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

H_PROCHOT#

T26TPC28t

1

T1TPC28t

1

T21TPC28t

1

T27TPC28t

1

H_RSVD3

H_RSVD2

H_RSVD1

H_RSVD0

H4

G4

G3

F3

F2

E2

AC26

N1

B1

F26

B18

A18

C17

B17

E1

C16

C3

C14

AF7

B2

SOCKET479P

4

BCLK[0]

BCLK[1]

ITP_CLK[0]

ITP_CLK[1]

A20M#

FERR#

IGNNE#

DPSLP#

SLP#

LINT0

LINT1

SMI#

STPCLK#

PWRGOOD

VID[5]

VID[4]

VID[3]

VID[2]

VID[1]

VID[0]

VCCA[3]

VCCA[2]

VCCA[1]

VCCA[0]

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

RSVD5

RSVD4

RSVD3

RSVD2

RSVD1

RSVD0

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

COMP[3]

COMP[2]

HOSTCLKLEGACY CPU

COMP[1]

COMP[0]

BPM[3]#

BPM[2]#

BPM[1]#

BPM[0]#

GTLREF[3]

GTLREF[2]

GTLREF[1]

GTLREF[0]

TEST1

TEST2

MISC

TRST#

VCCSENSE

VSSSENSE

VR_VID5 <42>

VR_VID4 <42>

VR_VID3 <42>

VR_VID2 <42>

VR_VID1 <42>

VR_VID0 <42>

CPU_COMP3

AB1

CPU_COMP2

AB2

CPU_COMP1

P26

CPU_COMP0

P25

H_BPM#3

C9

H_BPM#2

A9

H_BPM#1

B8

H_BPM#0

C8

AC1

G1

E26

H_GTLREF0

AD26

C5

F23

H_TCK

A13

TCK

H_TDI

C12

TDI

H_TDO

A12

TDO

H_TMS

C11

TMS

H_TRST#

B13

AE7

AF6

T2 TPC28t

1

T15 TPC28t

1

T19 TPC28t

1

T3 TPC28t

1

TOPOLOGY 2C:

CMOS Signals:

LINT0/INTR,LINT1/NMI,A20M#,

IGNNE#,SLP#,SMI#,and STPCLK#

CPU-ICH:0.5" - 12"

3

TOPOLOGY 2A:

Open Drain (OD) Signal

R-CPU-ICH Y-FORK

CPU-ICH: 0.5" - 12"

R - CPU <= 3"

(#0013)

H_PWRGD

TOPOLOGY 2B:

CMOS Signals

MCH-CPU-ICH4

MCH-CPU:0.5"-6.5"

CPU-ICH4:0.5"-12"

(#0013)

H_DPSLP#

TOPOLOGY 3:

CMOS Signals

CPU-ICH-R-LSC-FWH

CPU-ICH:0.5" - 12"

R - LSC <= 3"

LSC-FWH:0.5"-6"(#0013)

H_INIT#

Close to Pin A12 of CPU

Width= 5 mils

Length <= 2"

+VCCP

TOPOLOGY 1B:

Open Drain (OD) Signal

12

CPU-ICH-R

CPU-ICH: 0.5" - 12"

R78

ICH-R <= 3"

332Ohm

(#0013)

TOPOLOGY 1C:

Open Drain (OD) Signal

CPU-R-LSC-ICH

CPU-R: 0.5" - 12"

R - LSC<= 3"

LSC-ICH:0.5"-12"

TOPOLOGY 1B:

Open Drain (OD) Signal

CPU-ICH-R

CPU-ICH: 0.5" - 12"

ICH-R <= 3"

(#0013)

CPU DEBUG PORT

R341 200Ohm /ITP

H_PREQ#

R336 56Ohm /ITP

H_PRDY#

Close to Pin A8 of CPU

CPU JTAG

R333

H_TMS

R330

H_TDO

R328

H_TDI

R327

H_TCK

R325

H_TRST#

1 2

1 2

1 2

1 2

1 2

1 2

1 2

H_FERR#

H_PROCHOT#

H_THRMTRIP_S#

39Ohm

56Ohm

150Ohm

27.4Ohm

680Ohm

2

+VCCP

/ITP

+VCCP

GND

+VCCP

+VCCP

+VCCP

12

R192

56Ohm

12

R320

56Ohm

12

R194

56Ohm

H_GTLREF0

LENGTH <=0.5"

WIDTH = 5 mils

SPACE >= 25 mils

X BPSB(#0004)

CPU_COMP2 :

Analog

Length <= 0.5"

Width = 20 mils(L1/L4)

Space>= 25 mils

X BPSB(#0001)

CPU_COMP2

1 2

Pin AD1,AC2 of BANIAS

CPU_COMP3 :

Analog

Length <= 0.5"

Width = 5 mils

Space>= 25 mils

X BPSB(#0001)

CPU_COMP3

1 2

Pin AD1,AC2 of BANIAS

+VCCP

Close to

12

Pin AD26

R308

of CPU

1KOhm

H_GTLREF0

12

Same Side w/ CPU

R307

2KOhm

GND

CPU_COMP0 :

Analog

Length <= 0.5"

Width = 20 mils(L1/L4)

Space>= 25 mils

X BPSB(#0001)

R95

27.4Ohm

56Ohm

CPU_COMP0

GND

R96

CPU_COMP1

GND

ASUSTECH CO.,LTD.

Size Project Name

C

Date: Sheet

1 2

27.4Ohm

CPU_COMP1 :

Analog

Length <= 0.5"

Width = 5 mils

Space>= 25 mils

X BPSB(#0001)

1 2

56Ohm

A3G

R309

R310

Engineer:

1

GND

GND

Title :

CPU-DOTHAN(HOST)

EDDY ZHAO

Rev

1.2

357Thursday, August 19, 2004

of

5

4

3

2

1

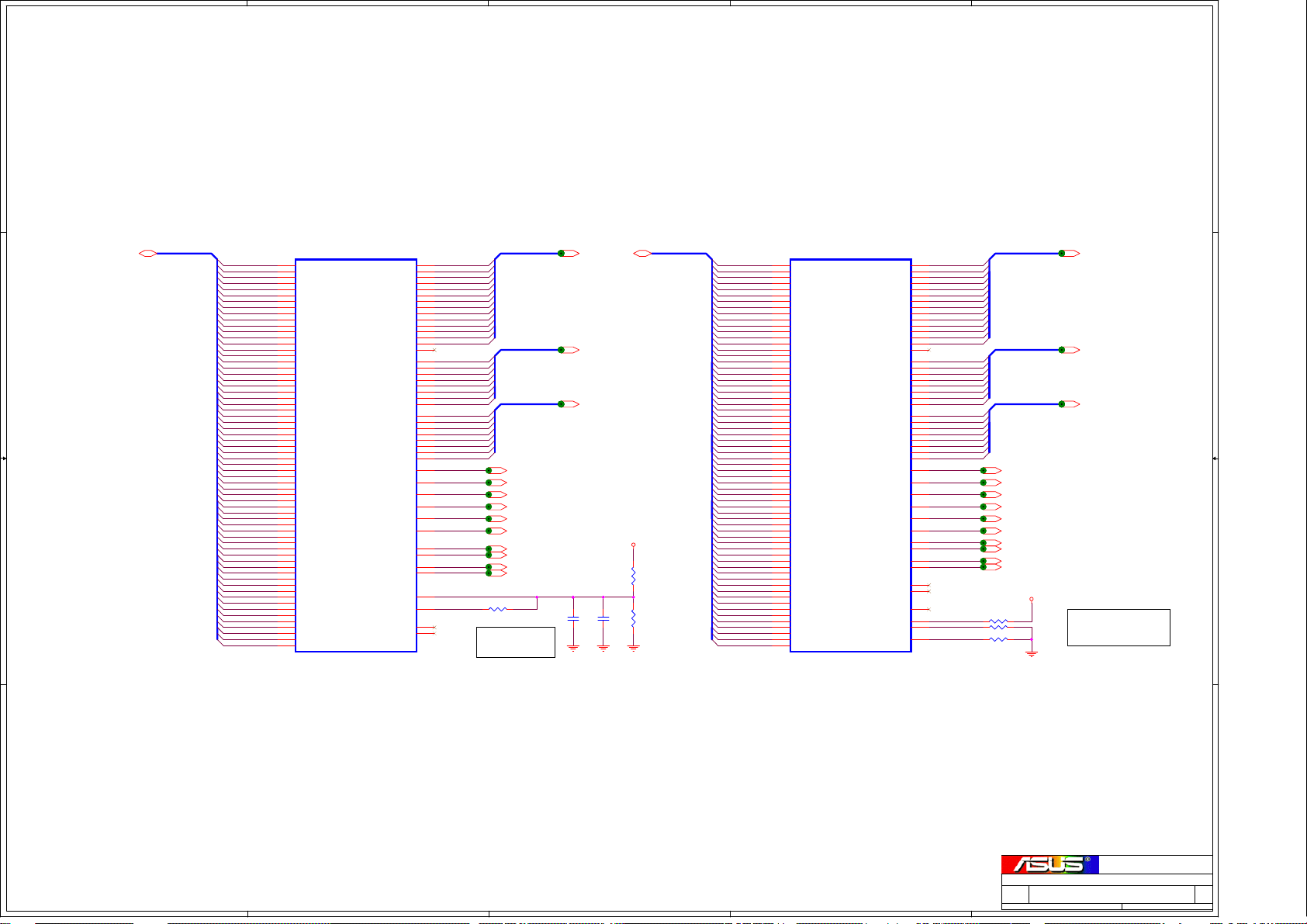

Target VCC (Std Voltage) :

HFM: 1.308V

LFM: 0.956V

Target Deeper Sleep Vcc =

D D

0.745 V

+VCORE

D6

VCC2D8VCC1

E17

D22

D20

D18

VCC4

VCC3

F20

F18

E21

E19

VCC9

VCC8E9VCC7E7VCC6E5VCC5

VCC14

VCC13F8VCC12F6VCC11

VCC10

VCC15

K22

J21

H22

G21

F22

VCC22

VCC21J5VCC20

VCC19H6VCC18

VCC17G5VCC16

VCC

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12K6VCCP13L5VCCP14

VCCQ[1]W4VCCQ[0]

E11

E13

P23

+VCCP

C C

12

12

C150

0.1uF/10V

GND

+VCORE

12

C439

10uF

12

B B

C69

10uF

12

C168

10uF

12

C147

10uF

E15

D10

D12

D14

D16

C61

0.1uF/10V

These pins should be connected to VCCP on the

motherboard. However, these connections should enable

addition of decoupling on the VCCQ lines if

necessary.

12

12

C107

10uF

12

12

C68

10uF

12

12

C165

10uF

12

12

C75

10uF

VCCP15M6VCCP16

L21

F10

F12

F14

F16

M22

12

C70

C468

10uF

10uF

12

C456

C108

10uF

10uF

12

C445

C136

10uF

10uF

12

C76

C77

10uF

10uF

V22

VCC27W5VCC26

VCC25V6VCC24U5VCC23

VCCP17N5VCCP18

VCCP19P6VCCP20

N21

12

12

12

12

TDP:

21W (Std Voltage)

10W (Low Voltage)

5W (Ultra Low

Voltage)

AA7

AA5

Y22

W21

VCC32

VCC31

VCC30

VCC29Y6VCC28

VCCP21R5VCCP22

VCCP23T6VCCP24

T22

P22

R21

C469

10uF

C463

10uF

C460

10uF

C78

10uF

U42E

AC24

AC21

AC18

AC16

AC14

AC12

AC10

AC8

AC5

AC2

AB26

AB23

AB21

AB19

AB17

AB15

AB13

AB11

AB9

AB7

AB5

AB3

AA25

AA22

AA20

AA18

AA16

AA14

AA12

AA10

AA8

AA6

AA4

AA1

Y24

Y21

W26

W23

W22

V25

V21

U24

U22

T26

T23

T21

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124Y5VSS123Y2VSS122

VSS121

VSS120

VSS119W6VSS118W3VSS117

VSS116

VSS115V5VSS114V4VSS113V1VSS112

VSS111

VSS110U6VSS109U2VSS108

VSS107

VSS106

VSS49

VSS50F1VSS51F4VSS52F5VSS53F7VSS54F9VSS55

E25

12

C474

0.1uF/10V

F11

12

VSS105T5VSS104T3VSS103

VSS56

F13

F15

C473

0.1uF/10V

AD1

VSS161

AD4

VSS162

AD7

VSS163

AA9

VCC55

VCC54

VCC53

VCC52

VCC51

VCC50

VCC49

VCC48

VCC47

VCC46

VCC45

VCC44

VCC43

VCC42

VCC41

VCC40

VCC39

VCC38

VCC37

VCC36

VCC35

VCC34

VCC33

VCCP25

+VCCP

U21

12

12

12

C442

C448

10uF

10uF

12

12

C106

C135

10uF

10uF

12

12

C436

C475

10uF

10uF

12

C137

10uF

12

C441

C467

10uF

10uF

12

12

C132

C71

10uF

10uF

12

C146

10uF

VCC56

VCC57

VCC58

VCC59

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC60

SOCKET479P

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

Mid Frequency

Decoupling (Place

around Processor)

High Frequency

Decoupling (Place

underneath

Processor) using

10uF/6.3V X5R

+VCORE

Bulk

Decoupling

U42D

AD18

AD16

AD14

AD12

AD10

AD8

AC19

AC17

AC15

AC13

AC11

AC9

AB22

AB20

AB18

AB16

AB14

AB12

AB10

AB8

AB6

AA21

AA19

AA17

AA15

AA13

AA11

AD9

VSS164

AD11

VSS165

AD13

VSS166

AD15

VSS167

AD17

VSS168

AD19

VSS169

AD22

VSS170

AD25

VSS171

AE3

VSS172

AE6

VSS173

AE8

VSS174

AE10

VSS175

AE12

VSS176

AE14

VSS177

AE16

VSS178

AE18

VSS179

AE20

VSS180

AE23

VSS181

AE26

VSS182

AF2

VSS183

AF5

VSS184

AF9

VSS185

AF11

VSS186

AF13

VSS187

AF15

VSS188

AF17

VSS189

AF19

VSS190

AF21

VSS191

AF24

VSS192

VSS1A2VSS2A5VSS3A8VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10B3VSS11B6VSS12B9VSS13

VSS14

VSS15

VSS16

VSS17

VSS18C1VSS19C4VSS20C7VSS21

A11

A14

A17

A20

A23

A26

B12

B16

B19

B22

B25

C10

GND

+VCCP

+VCCP (CPU) Decoupling Capacitor

GND

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27D2VSS28D5VSS29D7VSS30D9VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39E3VSS40E6VSS41E8VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

E10

E12

E14

E16

E18

E20

C13

C15

C18

C21

C24

D11

D13

D15

D17

D19

D21

D23

D26

E22

(Place near CPU)

12

C440

0.1uF/10V

12

C438

0.1uF/10V

12

C437

0.1uF/10V

12

12

+

+

GND

CE15

CE11

150U/4.0V

150U/4.0V

Two 150-UF POSCAPs with an ESR of 36 mOhm(typ) should be used for bulk decoupling. One

capacitor should be placed next to the processor socket and one capacitor in close

proximity to the MCH package.

Ten 0.1-UF X7R capacitors in a 0603 form factor should be placed on the secondary side

of the motherboard under the processor socket cavity next to the VCCP pins of the

processor. Five capacitors should be spread out near the Data signal side and five

capacitors near the Address signal side of the processor socket's pin-map.

12

C472

0.1uF/10V

12

C458

0.1uF/10V

12

C449

0.1uF/10V

SOCKET479P

R25

R22

R4

P24

P21

VSS99R1VSS98

VSS97

VSS102

VSS101R6VSS100

P5

VSS96

P2

VSS95

N26

VSS94

N23

VSS93

N22

VSS92

N6

VSS91

N3

VSS90

M24

VSS89

M21

VSS88

M5

VSS87

M4

VSS86

M1

VSS85

L25

VSS84

L22

VSS83

L6

VSS82

L3

VSS81

K26

VSS80

K23

VSS79

K21

VSS78

K5

VSS77

K2

VSS76

J24

VSS75

J22

VSS74

J6

VSS73

J4

VSS72

J1

VSS71

H25

VSS70

H21

VSS69

H5

VSS68

H3

VSS67

G26

VSS66

G23

VSS65

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62G2VSS63G6VSS64

F17

F19

F21

F24

G22

12

12

C471

C470

0.1uF/10V

0.1uF/10V

12

12

C105

10uF

Four 200 uF are located in IMVP4

A A

C134

12

C133

10uF

10uF

GND

Title :

CPU-DOTHAN(PWR)

ASUSTECH CO.,LTD.

Size Project Name

C

5

4

3

2

Date: Sheet

Engineer:

A3G

1

EDDY ZHAO

of

457Thursday, August 19, 2004

Rev

1.2

5

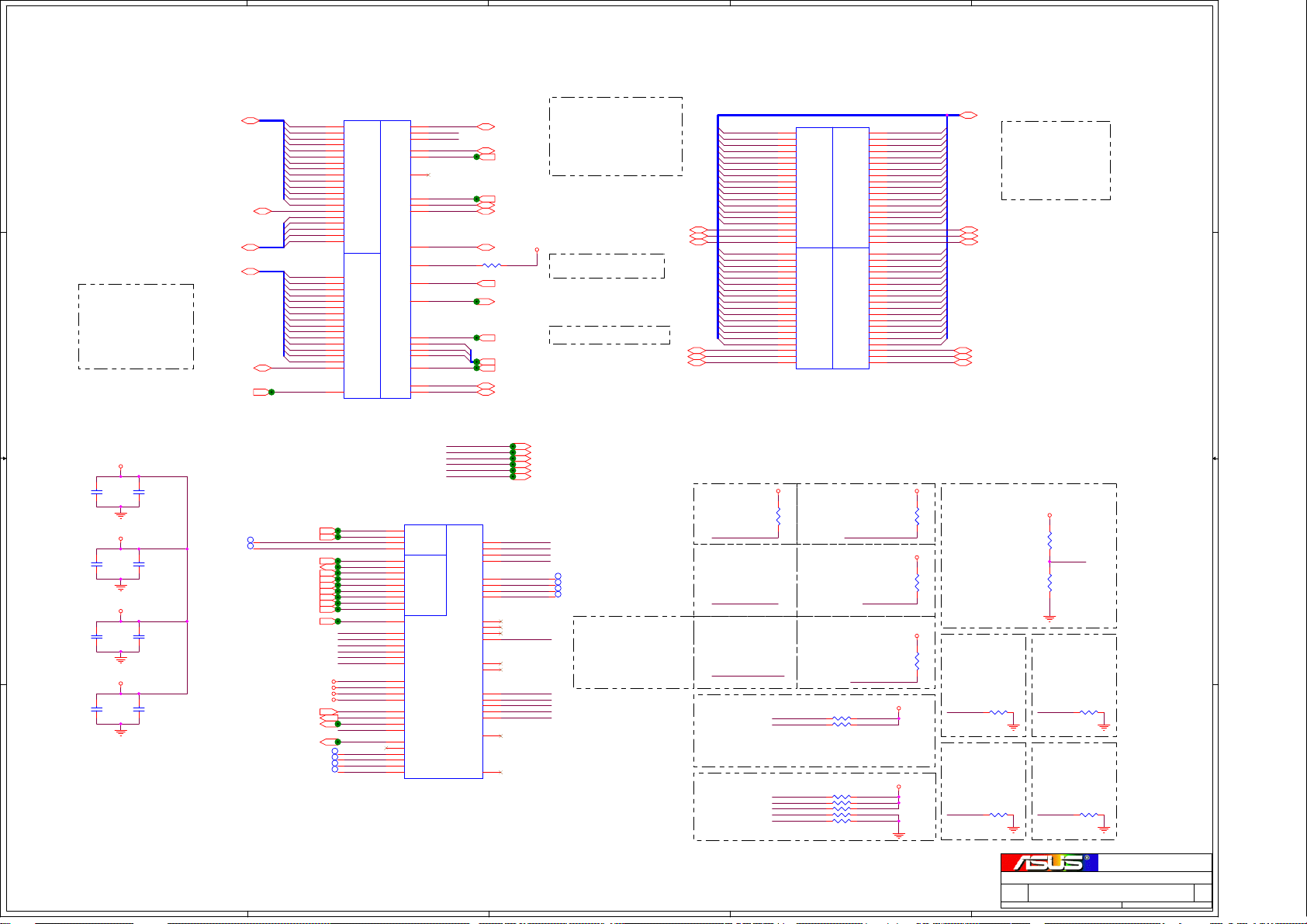

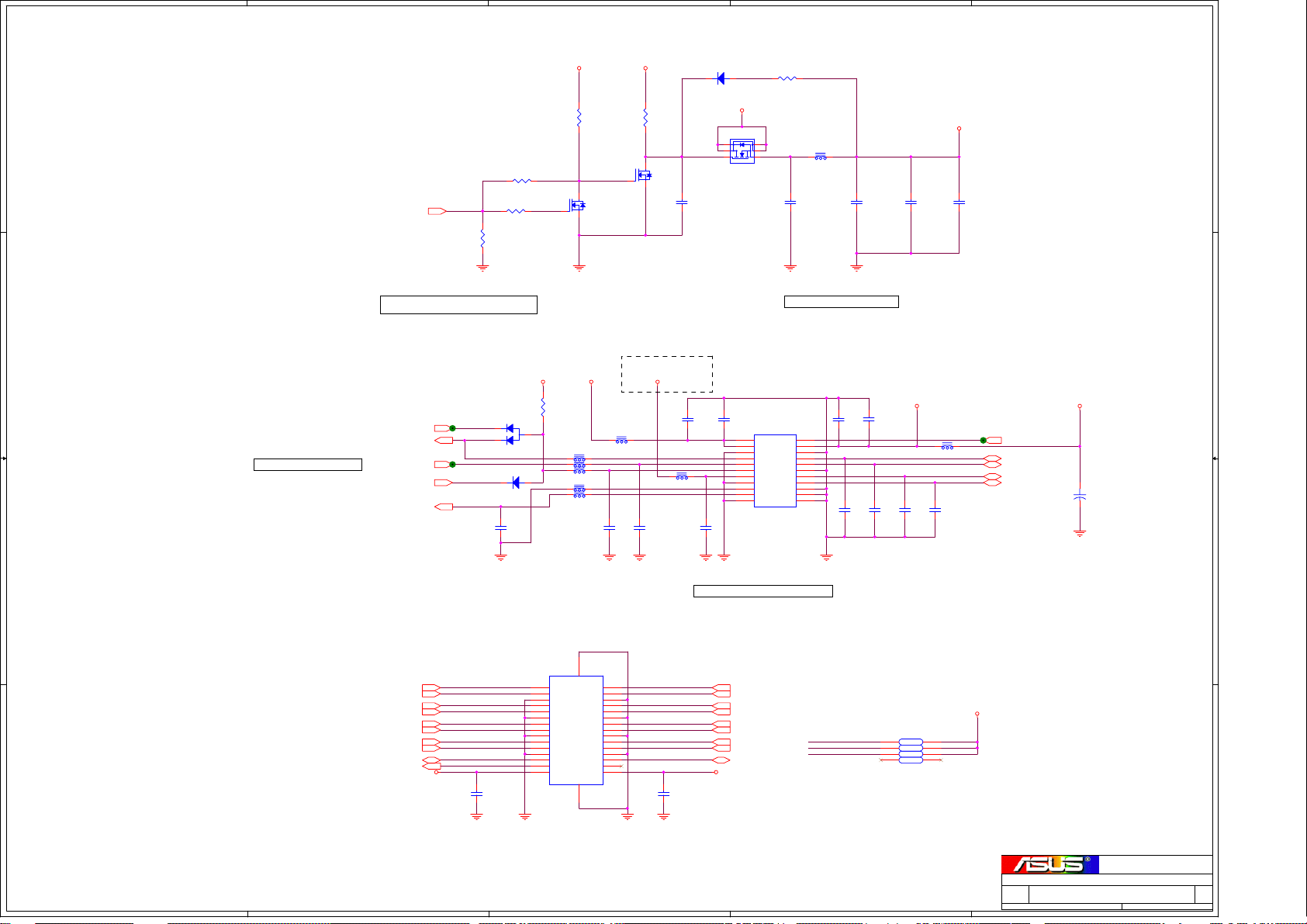

D D

C C

4

Route H_THERMDA and H_THERMDC on the same layer

Route VGA_THEM_DP and VGA_THEM_DN on the same layer

------------------------------------OTHER SIGNALS

12 mils

==============================GND

10 mils

==================H_THERMDA(10 mils)

10 mils

==================H_THERMDC(10 mils)

10 mils

==================GND

12 mils

-----------------------------------------OTHER SIGNALS

3

2

1

Avoid BPSB,Power

+V3.3S +V3.3S_THM

R375

1 2

OS#_OC

47Ohm

12

C509

2200P

C503

2200P

1 2

VGA_THEM_DP<11>

B B

VGA_THEM_DN<3,11>

H_THERMDC<3,11>

H_THERMDA<3>

OS#_OC<39>

Different from A3N Thermal Control

A3N use Max6657

G3N use Max6695

12

C502

0.1uF/10V

GND

U44

1

VCC

2

DXP1

3

DXN

4

DXP2

5

OT1#

Standby Mode: 3uA(Max. 10uA)

Full Active: 0.5 mA(Max. 1mA)

10

OT2#

SMBDATA

ALERT#

SMBCLK

SDA_3S

9

8

SCL_3S

7

6

GND

SCL_3S&SDA_3S(PULL_UP 10K

IN PAGE19)

H_THRMTRIP_S# <3,20>

SDA_3S <9,19,22>

PM_THRM# <20,39>

SCL_3S <9,19,22>

H_THRMTRIP_S##(PULL_UP 56Ohm IN PAGE3)

PM_THRM#(PULL_UP 10K IN PAGE39)

OS#_OC(PULL_UP 10K IN PAGE 39)

GND

A A

Title :

THERMAL

ASUSTECH CO.,LTD.

Size Project Name

C

5

4

3

2

Date: Sheet

Engineer:

A3G

1

EDDY ZHAO

of

557Thursday, August 19, 2004

Rev

1.2

5

AGP_AD[31:0]<11>

D D

AGP_C/BE#[3:0]<11>

12

+V1.8S

R334

<0.5"

36.5Ohm

CLK_MCH66<22>

AGP_SBA[7:0]<11>

AGP_SB_STB<11>

AGP_SB_STB#<11>

PCI_RST#<11,18,28,33>

R90

1 2

30.1Ohm

AGP_FRAME#<11>

AGP_DEVSEL#<11>

AGP_IRDY#<11>

AGP_TRDY#<11>

AGP_STOP#<11>

AGP_REQ#<11>

AGP_GNT#<11>

AGP_AD_STB0<11>

AGP_AD_STB0#<11>

AGP_AD_STB1<11>

AGP_AD_STB1#<11>

AGP_RBF#<11>

AGP_WBF#<11>

AGP_ST0

AGP_ST1

AGP_ST2

HUB_PD[10:0]<18>

AGP_PAR<11>

HUB_PSTRB<18>

HUB_PSTRB#<18>

M_RCOMP

H_DPSLP#<3,20>

NOTE:

GRCOMP SHUOULD BE

C C

B B

A A

10 MILS WIDE LESS

THEN 0.5'' FROM 855PM

R49

1 2

36.5Ohm

R601 USE 36.5 OHM

FOR 55 OHM BOARD

IMPEDANCE AGP

ROUTING

AGP_ST[2:0]<11>

+V1.5S

12

R91

4.7KOhm

+V1.25S

12

C156

The length of C603 to

0.1uF/10V

SMRCOMP pin should <1''

C603 decouping capacitor

should be placed near to

SMRCOMP pin

DDR_CKE0<9,10>

DDR_CKE1<9,10>

DDR_CKE2<9,10>

DDR_CKE3<9,10>

DDR_BS0#<9>

DDR_BS1#<9>

DDR_CS0#<9,10>

DDR_CS1#<9,10>

DDR_CS2#<9,10>

DDR_CS3#<9,10>

T10TPC28t /X

H_DPWR#<3>

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_RCOMP

AGP_VREF

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

HUB_PSTRB

HUB_PSTRB#

MCH_HLZCOMP

HUB_VREF_MCH

MCH_TEST#

MCH_RCVEN

1

AA28

AB25

AB27

AA27

AB26

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

AA23

AG24

AH25

AD25

AA21

AC27

AC28

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AF27

AF26

AE22

AE23

AF22

AG25

AF24

AG26

AD26

AD27

R27

R28

T25

R25

T26

T27

U27

U28

V26

V27

T23

U23

T24

U24

U25

V24

Y27

Y26

Y23

V25

V23

Y25

Y24

W28

W27

W24

W23

W25

P22

R24

R23

P25

P24

N27

P23

M26

M25

L28

L27

M27

N28

M24

N25

N24

P27

P26

J27

H27

H26

G23

E22

H23

F23

G12

G13

E9

F7

F9

E7

J28

G15

G14

V8

Y8

U43A

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GCBE0#

GCBE1#

GCBE2#

GCBE3#

GFRAME#

GDEVSEL#

GIRDY#

GTRDY#

GSTOP#

GPAR

GREQ#

GGNT#

GRCOMP

AGPREF

66IN

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SB_STB

SB_STB#

RBF#

WBF#

PIPE#

ST0

ST1

ST2

HI_0

HI_1

HI_2

HI_3

HI_4

HI_5

HI_6

HI_7

HI_8

HI_9

HI_10

HI_STB

HI_STB#

HLRCOMP

HI_REF

RSTIN#

RSVD1

TESTIN#

SCKE0

SCKE1

SCKE2

SCKE3

SBS0

SBS1

SCS0#

SCS1#

SCS2#

SCS3#

SMRCOMP

RCVENIN#

RCVENOUT#

NC0

NC1

DPSLP#

DPWR#

AGP

HUB

MCH_M

4

MEOMERY

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

RSVD2

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

MEOMERY

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SWE#

SCAS#

SRAS#

SCK0

SCK0#

SCK1

SCK1#

SCK2

SCK2#

SCK3

SCK3#

SCK4

SCK4#

SCK5

SCK5#

SMVREF0

SMVREF1

E12

F17

E16

G17

G18

E18

F19

G20

G19

F21

F13

E20

G21

G22

G28

F27

C28

E28

H25

G27

F25

B28

E27

C27

B25

C25

B27

D27

D26

E25

D24

E23

C22

E21

C24

B23

D22

B21

C21

D20

C19

D18

C20

E19

C18

E17

E13

C12

B11

C10

B13

C13

C11

D10

E10

C9

D8

E8

E11

B9

B7

C7

C6

D6

D4

B3

E6

B5

C4

E4

C3

D3

F4

F3

B2

C2

E2

G4

C16

D16

B15

C14

B17

C17

C15

D14

F26

C26

C23

B19

D12

C8

C5

E3

E15

G11

G8

F11

J25

K25

G5

F5

G24

E24

G25

J24

G6

G7

K23

J23

J9

J21

_DDR_AA0

_DDR_AA1

_DDR_AA2

_DDR_AA3

_DDR_AA4

_DDR_AA5

_DDR_AA6

_DDR_AA7

_DDR_AA8

_DDR_AA9

_DDR_AA10

_DDR_AA11

_DDR_AA12

DDR_DATA0

DDR_DATA1

DDR_DATA2

DDR_DATA3

DDR_DATA4

DDR_DATA5

DDR_DATA6

DDR_DATA7

DDR_DATA8

DDR_DATA9

DDR_DATA10

DDR_DATA11

DDR_DATA12

DDR_DATA13

DDR_DATA14

DDR_DATA15

DDR_DATA16

DDR_DATA17

DDR_DATA18

DDR_DATA19

DDR_DATA20

DDR_DATA21

DDR_DATA22

DDR_DATA23

DDR_DATA24

DDR_DATA25

DDR_DATA26

DDR_DATA27

DDR_DATA28

DDR_DATA29

DDR_DATA30

DDR_DATA31

DDR_DATA32

DDR_DATA33

DDR_DATA34

DDR_DATA35

DDR_DATA36

DDR_DATA37

DDR_DATA38

DDR_DATA39

DDR_DATA40

DDR_DATA41

DDR_DATA42

DDR_DATA43

DDR_DATA44

DDR_DATA45

DDR_DATA46

DDR_DATA47

DDR_DATA48

DDR_DATA49

DDR_DATA50

DDR_DATA51

DDR_DATA52

DDR_DATA53

DDR_DATA54

DDR_DATA55

DDR_DATA56

DDR_DATA57

DDR_DATA58

DDR_DATA59

DDR_DATA60

DDR_DATA61

DDR_DATA62

DDR_DATA63

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_AA0 <9>

DDR_AA1 <9>

DDR_AA2 <9>

DDR_AA3 <9>

DDR_AA4 <9>

DDR_AA5 <9>

DDR_AA6 <9>

DDR_AA7 <9>

DDR_AA8 <9>

DDR_AA9 <9>

DDR_AA10 <9>

DDR_AA11 <9>

DDR_AA12 <9>

DDR_WE# <9>

DDR_CAS# <9>

DDR_RAS# <9>

CLK_DDR0 <9>

CLK_DDR0# <9>

CLK_DDR1 <9>

CLK_DDR1# <9>

CLK_DDR2 <9>

CLK_DDR2# <9>

CLK_DDR3 <9>

CLK_DDR3# <9>

CLK_DDR4 <9>

CLK_DDR4# <9>

CLK_DDR5 <9>

CLK_DDR5# <9>

DDR_VREF

3

_DDR_DATA[63:0] <9,10>

_DDR_DQS[7:0] <9,10>

Close to MCH

_DDR_DATA3

_DDR_DATA6

_DDR_DATA7

_DDR_DATA2

_DDR_DATA4

_DDR_DATA5

_DDR_DATA0

_DDR_DATA1

_DDR_DQS0

_DDR_DATA15

_DDR_DATA11

_DDR_DATA10

_DDR_DATA14

_DDR_DATA9

_DDR_DATA8

_DDR_DATA12

_DDR_DQS1

_DDR_DATA19

_DDR_DATA23

_DDR_DATA22

_DDR_DATA18

_DDR_DATA17

_DDR_DATA21

_DDR_DATA20

_DDR_DQS2

_DDR_DATA31

_DDR_DATA27

_DDR_DATA26

_DDR_DATA30

_DDR_DATA29

_DDR_DATA28

_DDR_DATA25

_DDR_DQS3

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

DDR_DATA3

RN23A10Ohm

DDR_DATA6

RN23B10Ohm

DDR_DATA7

RN23C10Ohm

DDR_DATA2

RN23D10Ohm

DDR_DATA4

RN23E10Ohm

DDR_DATA5

RN23F10Ohm

DDR_DATA0

RN23G10Ohm

DDR_DATA1

RN23H10Ohm

DDR_DQS0

R17810Ohm

DDR_DATA15

RN22A10Ohm

DDR_DATA11

RN22B10Ohm

DDR_DATA10

RN22C10Ohm

DDR_DATA14

RN22D10Ohm

DDR_DATA9

RN22E10Ohm

DDR_DATA13_DDR_DATA13

RN22F10Ohm

DDR_DATA8

RN22G10Ohm

DDR_DATA12

RN22H10Ohm

DDR_DQS1

R17510Ohm

DDR_DATA19

RN21A10Ohm

DDR_DATA23

RN21B10Ohm

DDR_DATA22

RN21C10Ohm

DDR_DATA18

RN21D10Ohm

DDR_DATA17

RN21E10Ohm

DDR_DATA16_DDR_DATA16

RN21F10Ohm

DDR_DATA21

RN21G10Ohm

DDR_DATA20

RN21H10Ohm

DDR_DQS2

R17910Ohm

DDR_DATA31

RN20A10Ohm

DDR_DATA27

RN20B10Ohm

DDR_DATA26

RN20C10Ohm

DDR_DATA30

RN20D10Ohm

DDR_DATA29

RN20E10Ohm

DDR_DATA24_DDR_DATA24

RN20F10Ohm

DDR_DATA28

RN20G10Ohm

DDR_DATA25

RN20H10Ohm

DDR_DQS3

R18010Ohm

_DDR_DATA39

_DDR_DATA34

_DDR_DATA35

_DDR_DATA37

_DDR_DATA36

_DDR_DATA33

_DDR_DATA32

_DDR_DQS4

_DDR_DATA47

_DDR_DATA46

_DDR_DATA43

_DDR_DATA42

_DDR_DATA44

_DDR_DATA41

_DDR_DATA40

_DDR_DQS5

_DDR_DATA55

_DDR_DATA50

_DDR_DATA51

_DDR_DATA54

_DDR_DATA53

_DDR_DATA48

_DDR_DATA49

_DDR_DQS6

_DDR_DATA61

_DDR_DATA63

_DDR_DATA62

_DDR_DATA58

_DDR_DATA60

_DDR_DATA57

_DDR_DATA56

_DDR_DQS7

Intel suggested that DDR_VREF should

be turned off in S3-S5. But measure the

leakage because there is no +V2.5S.

+V2.5

12

R171

10KOhm

1

12

C232

0.1uF/10V

12

3

R170

10KOhm

Place C605,R619,R620 close to U601.P26

+V5

12

C223

U13

DDR_VREF

4

0.1uF/10V

1.225V-1.275V

S0-S1M:10 mA(Max.

50 mA)

52

V+

+

V-

LMV321

MCH--------R619&R620 <=3"

HUB_VREF_MCH

12

C139

0.01uF/25V

2

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

+V1.8S_MCH

12

R79

12

R80

150Ohm

GND

150Ohm

1

DDR_DATA39

RN17A10Ohm

DDR_DATA34

RN17B10Ohm

DDR_DATA35

RN17C10Ohm

DDR_DATA37

RN17D10Ohm

DDR_DATA36

RN17E10Ohm

DDR_DATA38_DDR_DATA38

RN17F10Ohm

DDR_DATA33

RN17G10Ohm

DDR_DATA32

RN17H10Ohm

DDR_DQS4

R18110Ohm

DDR_DATA47

RN16A10Ohm

DDR_DATA46

RN16B10Ohm

DDR_DATA43

RN16C10Ohm

DDR_DATA42

RN16D10Ohm

DDR_DATA44

RN16E10Ohm

DDR_DATA45_DDR_DATA45

RN16F10Ohm

DDR_DATA41

RN16G10Ohm

DDR_DATA40

RN16H10Ohm

DDR_DQS5

R17410Ohm

DDR_DATA55

RN15A10Ohm

DDR_DATA50

RN15B10Ohm

DDR_DATA51

RN15C10Ohm

DDR_DATA54

RN15D10Ohm

DDR_DATA53

RN15E10Ohm

DDR_DATA52_DDR_DATA52

RN15F10Ohm

DDR_DATA48

RN15G10Ohm

DDR_DATA49

RN15H10Ohm

DDR_DQS6

R17310Ohm

DDR_DATA61

RN14A10Ohm

DDR_DATA63

RN14B10Ohm

DDR_DATA62

RN14C10Ohm

DDR_DATA58

RN14D10Ohm

DDR_DATA60

RN14E10Ohm

DDR_DATA59_DDR_DATA59

RN14F10Ohm

DDR_DATA57

RN14G10Ohm

DDR_DATA56

RN14H10Ohm

DDR_DQS7

R17210Ohm

+V1.5S

12

R48

1KOhm

AGP_VREF

12

R52

1KOhm

12

C91

0.1uF/10V

Title :

NB-MCHM1

ASUSTECH CO.,LTD.

Size Project Name

C

5

4

3

2

Date: Sheet

Engineer:

A3G

1

Benny Liang

of

657Thursday, August 19, 2004

Rev

1.2

5

4

3

2

1

D D

C C

B B

All decoupling capacitances should Be

placed near to the associated pins.

+V1.5S

12

+

12

12

150U/4.0V

+V1.2S

+V1.8S

+V1.8S

CE18

12

150U/4.0V

C128

12

+

CE9

150U/4.0V

0.01UF/10V

12

2.2UF/6.3V

C464

C141

0.01UF/10V

+

CE16

0.01UF/10V

12

C115

0.01UF/10V

C462

12

0.01UF/10V

12

12

C116

0.1U

12

C118

10uF

C73

C142

0.01UF/10V

12

0.01UF/10V

12

C144

0.22UF/10V

12

C145

U43B

AA22

VCC1_5_0

12

12

C143

C138

0.01UF/10V

+V1.8S_MCH

C112

12

C103

C92

0.01UF/10V

12

12

C125

0.022U

0.047UF/10V

0.1U

12

C149

10uF

12

0.01UF/10V

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

VCC1_5_1

R22

VCC1_5_2

R29

VCC1_5_3

U22

VCC1_5_4

U26

VCC1_5_5

W22

VCC1_5_6

W29

VCC1_5_7

VCC1_5_8

VCC1_5_9

VCC1_5_10

VCC1_5_11

VCC1_5_12

VCC1_5_13

VCC1_5_14

AJ25

VCC1_5_15

N14

VCC0

N16

VCC1

P13

VCC2

P15

VCC3

P17

VCC4

R14

VCC5

R16

VCC6

T15

VCC7

U14

VCC8

U16

VCC9

L25

VCC1_8_0

L29

VCC1_8_1

M22

VCC1_8_2

N23

VCC1_8_3

N26

VCC1_8_4

G16

RSVD3

G10

RSVD4

G9

RSVD5

H7

RSVD6

H4

ETS#

H3

RSVD7

G3

RSVD8

G2

RSVD9

T17

VCCGA

T13

VCCHA

MCH_M

HOST

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HLOCK#

BNR#

BPR#

DBSY#

RS0#

RS1#

RS2#

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

U7

V4

W2

Y4

Y3

Y5

HIT#

W3

V7

BR0

V3

Y7

V5

H_RS#0

W7

H_RS#1

W5

H_RS#2

W6

AB10

AB14

AB18

AB20

AB8

AC19

AD18

AD20

AE19

AE21

AF18

AF20

AG19

AG21

AG23

AJ19

AJ21

AJ23

M8

T8

A13

A17

A21

A25

A5

A9

C1

C29

D11

D15

D19

D23

D25

D7

E5

F10

F14

F16

F18

F22

G1

G29

H10

H12

H14

H16

H18

H20

H22

H24

H5

H8

J6

K22

K24

K26

K7

L23

H_ADS# <3>

H_TRDY# <3>

H_DRDY# <3>

H_DEFER# <3>

H_HITM# <3>

H_HIT# <3>

H_LOCK# <3>

H_BR0# <3>

H_BNR# <3>

H_BPRI# <3>

H_DBSY# <3>

H_RS#[2:0] <3>

12

C148

0.1uF/10V

12

C172

0.1uF/10V

12

C179

0.1uF/10V

12

C180

0.1uF/10V

12

C174

1UF/10V

/EMI

12

C59

0.1uF/10V

12

12

12

12

C224

1UF/10V

/EMI

C177

0.1uF/10V

C158

0.1uF/10V

C157

0.1uF/10V

12

C90

0.1uF/10V

12

12

C163

0.1uF/10V

12

12

C215

1UF/10V

/EMI

C178

0.1uF/10V

C154

0.1uF/10V

12

12

C169

1UF/10V

/EMI

12

C114

0.1uF/10V

C164

0.1uF/10V

12

C161

0.1uF/10V

12

+

CE13

150U/4.0V

+VCCP

12

+

CE17

150U/4.0V

12

C153

0.1uF/10V

+V2.5

AA29

AB11

AB13

AB15

AB17

AB19

AB22

AC18

AC20

AC21

AC23

AC26

AD10

AD12

AD14

AD16

AD19

AD22

AE18

AE20

AE29

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG18

AG20

AG22

AH19

AH21

AH23

AJ11

AJ13

AJ15

AJ17

AJ27

U43D

A11

VSS0

A15

VSS1

A19

VSS2

A23

VSS3

A27

VSS4

A3

VSS5

A7

VSS6

AA1

VSS7

VSS8

AA4

VSS9

AA8

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

AB6

VSS17

AB9

VSS18

AC1

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

AC4

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

AD6

VSS32

AD8

VSS33

AE1

VSS34

VSS35

VSS36

VSS37

AE4

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

AF5

VSS46

AF7

VSS47

AF9

VSS48

AG1

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

AJ3

VSS61

AJ5

VSS62

AJ7

VSS63

AJ9

VSS64

D13

VSS65

D17

VSS66

D21

VSS67

D5

VSS68

D9

VSS69

E1

VSS70

MCH_M

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

E14

E26

E29

F12

F15

F20

F24

F6

F8

G26

H11

H13

H15

H17

H19

H21

H6

H9

J1

J22

J26

J29

J4

J7

K27

K6

L1

L22

L24

L26

L4

L8

M23

M6

N1

N13

N15

N17

N22

N29

N4

N8

P14

P16

P6

R1

R13

R15

R17

R26

R4

R8

T14

T16

T22

T6

U1

U13

U15

U17

U29

U4

U8

V22

V6

W1

W26

W4

W8

Y22

Y6

A A

Title :

NB-MCHM2

ASUSTECH CO.,LTD.

Size Project Name

C

5

4

3

2

Date: Sheet

Engineer:

A3G

1

Benny Liang

of

757Thursday, August 19, 2004

Rev

1.2

5

D D

C C

B B

R61

301Ohm

+VCCP

12

12

R57

150Ohm

12

C95

0.01UF/10V

4

HSWING [1:0]

18 MIL TRACE

10 MIL SPACE

MCH_HSWNG0

R68

27.4Ohm

12

R315 27.4Ohm

12

R64

301Ohm

MCH_HRCOMP1

MCH_HRCOMP0

+VCCP

12

12

R63

150Ohm

12

C93

0.01UF/10V

CLK_MCH100#<22>

CLK_MCH100<22>

H_CPURST#<3>

LAYOUT NOTE:

H_CPURST# FORKS

AT 855PM PIN

MCH_HSWNG1

3

H_A#[31:3]<3> H_D#[63:0] <3>

H_REQ#[4:0]<3>

H_ADSTB#0<3>

H_ADSTB#1<3>

C801 should be placed closer to de HSWNG0 than R805

and R807

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

MCH_HRCOMP1

MCH_HSWNG1

MCH_HRCOMP0

MCH_HSWNG0

H_DSTBN#0<3>

H_DSTBN#1<3>

H_DSTBN#2<3>

H_DSTBN#3<3>

H_DSTBP#0<3>

H_DSTBP#1<3>

H_DSTBP#2<3>

H_DSTBP#3<3>

H_DINV0#<3>

H_DINV1#<3>

H_DINV2#<3>

H_DINV3#<3>

MCH_GTLREF

AC13

AD13

AD11

AC15

AE11

AC16

AD15

AE17

AB12

AB16

AC2

AA7

AD4

AF6

AD3

AG6

AD5

AG5

AH9

AA9

U6

R2

U3

R3

R6

N2

N5

N3

M3

M4

M5

N6

U2

R7

U5

R5

N7

M7

T5

P7

T3

P4

P3

P5

J3

L5

K3

J2

L6

L2

K5

L3

L7

K4

J5

T7

T4

K8

J8

P8

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADSTB0#

HADSTB1#

BCLK#

BCLK

HRCOMP1

HSWNG1

HRCOMP0

HSWNG0

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

DBI0#

DBI1#

DBI2#

DBI3#

CPURST#

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

U43C

HOST

MCH_M

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AE5

AF3

AC6

AC3

AF4

AE2

AG4

AG2

AE7

AE8

AH2

AC7

AG3

AD7

AH7

AE6

AC8

AG8

AG7

AH3

AF8

AH5

AC11

AC12

AE9

AC10

AE10

AD9

AG9

AC9

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

2

C802 should be placed closer to de HSWNG1 than R806 and R808

1

+VCCP

12

R71

49.9Ohm

12

12

R62

100Ohm

1 2

A A

5

C102

0.22UF/10V

C83

0.22UF/10V

4

12

MCH_GTLREF

C127

1UF/10V

Place R809 close to HVREF4 and R810 close to

HVREF1

3

Title :

NB-MCHM3

ASUSTECH CO.,LTD.

Size Project Name

C

2

Date: Sheet

Engineer:

A3G

1

Benny Liang

of

857Thursday, August 19, 2004

Rev

1.2

5

4

3

2

1

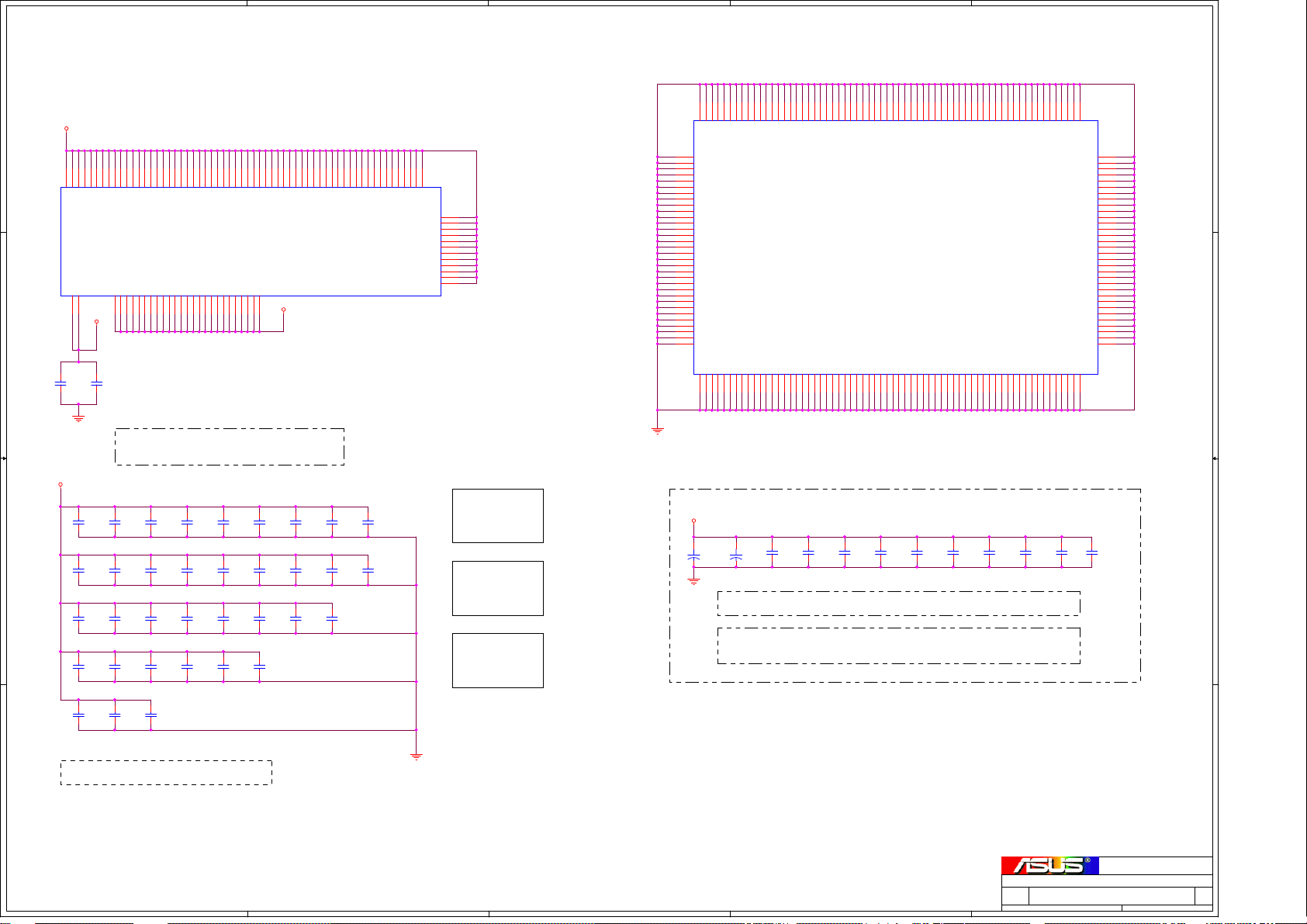

D D

_DDR_DATA[63:0]<6,10>

All decoupling capacitances should Be

placed near to the associated pins.

FOR +V2.5 DECOUPLING

+V2.5 +V2.5

JP29A

1

VREF0

3

_DDR_DATA0

+V3.3S

RN19A10Ohm

RN19B10Ohm

RN19C10Ohm

RN19D10Ohm

RN19E10Ohm

RN19F10Ohm

RN19G10Ohm

RN19H10Ohm

_DDR_DATA1

_DDR_DATA2

_DDR_DATA3

_DDR_DATA8

_DDR_DATA9

_DDR_DATA10

_DDR_DATA11

_DDR_DATA16

_DDR_DATA17

_DDR_DATA18

_DDR_DATA19

_DDR_DATA24

_DDR_DATA25

_DDR_DATA26

_DDR_DATA27

_DDR_AA12

_DDR_AA9

_DDR_AA7

_DDR_AA5

_DDR_AA3

_DDR_AA1

_DDR_AA10

_DDR_BS0#

_DDR_WE#

_DDR_DATA32

_DDR_DATA33

_DDR_DATA34

_DDR_DATA35

_DDR_DATA40

_DDR_DATA41

_DDR_DATA42

_DDR_DATA43

_DDR_DATA48

_DDR_DATA49

_DDR_DATA50

_DDR_DATA51

_DDR_DATA56

_DDR_DATA57

_DDR_DATA58

_DDR_DATA59

12

C550

0.1uF/10V

GND

4

_DDR_DQS0<6,10>

_DDR_DQS1<6,10>

CLK_DDR0<6>

CLK_DDR0#<6>

C C

_DDR_AA[12:0]<10>

_DDR_BS0#<10>

_DDR_WE#<10>

_DDR_BS1#<10>

_DDR_RAS#<10>

_DDR_CAS#<10>

DDR_AA12<6>

DDR_AA9<6>

DDR_AA7<6>

DDR_AA5<6>

DDR_AA3<6>

DDR_AA1<6>

DDR_AA10<6>

DDR_BS0#<6>

B B

DDR_WE#<6>

_DDR_DQS2<6,10>

_DDR_DQS3<6,10>

CLK_DDR2<6>

CLK_DDR2#<6>

DDR_CKE1<6,10>

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

R177 10Ohm

1 2

DDR_CS0#<6,10>

Rn902 and R902 should be placed close to MCH

_DDR_DQS4<6,10>

_DDR_DQS5<6,10>

_DDR_DQS6<6,10>

_DDR_DQS7<6,10>

A A

5

SDA_3S<5,19,22>

SCL_3S<5,19,22>

VSS0

5

DQ0

7

DQ1

9

VDD0

11

DQS0

13

DQ2

15

VSS2

17

DQ3

19

DQ8

21

VDD2

23

DQ9

25

DQS1

27

VSS4

29

DQ10

31

DQ11

33

VDD4

35A

A: CK0

37A

A: CK0#

39

VSS7

41

DQ16

43

DQ17

45

VDD7

47

DQS2

49

DQ18

51

VSS9

53

DQ19

55

DQ24

57

VDD9

59

DQ25

61

DQS3

63

VSS11

65

DQ26

67

DQ27

69

VDD11

85

DU_0

87

VSS13

89A

A: CK2

91A

A: CK2#

93

VDD14

95A

A: CKE1

97

DU/A13

99

A12

101

A9

103

VSS16

105

A7

107

A5

109

A3

111

A1

113

VDD16

115

A10/AP

117

BA0

119

WE#

121A

A: S0#

123

DU_1

125

VSS18

127

DQ32

129

DQ33

131

VDD18

133

DQS4

135

DQ34

137

VSS20

139

DQ35

141

DQ40

143

VDD20

145

DQ41

147

DQS5

149

VSS22

151

DQ42

153

DQ43

155

VDD22

157

VDD24

159

VSS24

161

VSS25

163

DQ48

165

DQ49

167

VDD25

169

DQS6

171

DQ50

173

VSS27

175

DQ51

177

DQ56

179

VDD27

181

DQ57

183

DQS7

185

VSS29

187

DQ58

189

DQ59

191

VDD29

193

SDA

195

SCL

197

VDDSPD

199

VDDID

GND GND

VREF1

VSS1

VDD1

VSS3

DQ12

VDD3

DQ13

VSS5

DQ14

DQ15

VDD5

VDD6

VSS6

VSS8

DQ20

DQ21

VDD8

DQ22

VSS10

DQ23

DQ28

VDD10

DQ29

VSS12

DQ30

DQ31

VDD12

DU/RESET#

VSS14

VSS15

VDD13

VDD15

A: CKE0

DU/BA2

VSS17

VDD17

RAS#

CAS#

A: S1#

DU_3

VSS19

DQ36

DQ37

VDD19

DQ38

VSS21

DQ39

DQ44

VDD21

DQ45

VSS23

DQ46

DQ47

VDD23

A: CK1#

A: CK1

VSS26

DQ52

DQ53

VDD26

DQ54

VSS28

DQ55

DQ60

VDD28

DQ61

VSS30

DQ62

DQ63

VDD30

A: SA0

A: SA1

A: SA2

DU_2

DQ4

DQ5

DM0

DQ6

DQ7

DM1

DM2

DM3

A11

A8

A6

A4

A2

A0

BA1

DM4

DM5

DM6

DM7

+V2.5

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DDR_VREFDDR_VREF

_DDR_DATA4

_DDR_DATA5

_DDR_DATA6

_DDR_DATA7

_DDR_DATA12

_DDR_DATA13

_DDR_DATA14

_DDR_DATA15

_DDR_DATA20

_DDR_DATA21

_DDR_DATA22

_DDR_DATA23

_DDR_DATA28

_DDR_DATA29

_DDR_DATA30

_DDR_DATA31

_DDR_AA11

_DDR_AA8

_DDR_AA6

_DDR_AA4

_DDR_AA2

_DDR_AA0

_DDR_BS1#

_DDR_RAS#

_DDR_CAS#

_DDR_DATA36

_DDR_DATA37

_DDR_DATA38

_DDR_DATA39

_DDR_DATA44

_DDR_DATA45

_DDR_DATA46

_DDR_DATA47

_DDR_DATA52

_DDR_DATA53

_DDR_DATA54

_DDR_DATA55

_DDR_DATA60

_DDR_DATA61

_DDR_DATA62

_DDR_DATA63

DDR_CKE0 <6,10>

3 14

6 11

7 10

4 13

5 12

2 15

8 9

1 16

R176 10Ohm

1 2

DDR_CS1# <6,10>

CLK_DDR1# <6>

CLK_DDR1 <6>

3

RN18C10Ohm

RN18F10Ohm

RN18G10Ohm

RN18D10Ohm

RN18E10Ohm

RN18B10Ohm

RN18H10Ohm

RN18A10Ohm

DDR_AA11 <6>

DDR_AA8 <6>

DDR_AA6 <6>

DDR_AA4 <6>

DDR_AA2 <6>

DDR_AA0 <6>

DDR_BS1# <6>

DDR_RAS# <6>

DDR_CAS# <6>

Rn901 and R901 should be placed close to MCH

CLK_DDR3<6>

CLK_DDR3#<6>

CLK_DDR5<6>

CLK_DDR5#<6>

DDR_CKE3<6,10>

DDR_CS2#<6,10>

2.375V - 2.625V(+/- 5%)

S0-S3: 8.12 A

12

+

CE21

150U/4.0V

+V2.5

12

+

CE22

150U/4.0V

DDR_VREF

12

GND

GND

2

12

+

CE19

150U/4.0V

12

+

150U/4.0V

C560

0.1uF/10V

CE20

35

37

89

91

95

121

201

202

203

204

JP29B

B: CK0

B: CK0#

B: CK2

B: CK2#

B: CKE1

B: S0#

NC0

NC1

NC2

NC3

+V2.5

B: CKE0

B: S1#

B: CK1#

B: CK1

B: SA0

B: SA1

B: SA2

NP_NC7

NP_NC6

NP_NC5

NP_NC4

C551 0.1uF/10V

1 2

C557 0.1uF/10V

1 2

C531 0.1uF/10V

1 2

C530 0.1uF/10V

1 2

C554 0.1uF/10V

1 2

C553 0.1uF/10V

1 2

C552 0.1uF/10V

1 2

C555 0.1uF/10V

1 2

C556 0.1uF/10V

1 2

C529 0.1uF/10V

1 2

C532 0.1uF/10V

1 2

C535 0.1uF/10V

1 2

C559 0.1uF/10V

1 2

C536 0.1uF/10V

1 2

C534 0.1uF/10V

1 2

C533 0.1uF/10V

1 2

C558 0.1uF/10V

1 2

C263

1 2

1UF/10V

/EMI

96B

122B

158B

160B

194B

1 2

R196 10KOhm

196B

198B

208

207

206

205

GND

ASUSTECH CO.,LTD.

Size Project Name

C

Date: Sheet

+V2.5

12

+V5s

+V2.5

12

+V1.5s

DDR_CKE2 <6,10>

DDR_CS3# <6,10>

CLK_DDR4# <6>

CLK_DDR4 <6>

+V3.3S

A3G

C275

1UF/10V

/EMI

C291

1UF/10V

/EMI

1

12

Title :

Engineer:

C240

1UF/10V

/EMI

DUAL_DDR

Benny Liang

of

957Thursday, August 19, 2004

Rev

1.2

5

4

3

2

1

D D

C C

B B

All termination registers

should Be placed near to

the associated pins of

SO-DIMM1

_DDR_DATA2

_DDR_DQS0

_DDR_DATA6

_DDR_DATA7

_DDR_DATA4

_DDR_DATA5

_DDR_DATA1

_DDR_DATA0

_DDR_DATA17

_DDR_DATA16

_DDR_DATA23

_DDR_DATA22

_DDR_DATA21

_DDR_DATA20

_DDR_DATA11

_DDR_DATA10

_DDR_DQS1

_DDR_DATA9

_DDR_DATA15

_DDR_DATA13

_DDR_DATA14

_DDR_DATA12

_DDR_DATA8

_DDR_DATA3

_DDR_DQS5

_DDR_DATA41

_DDR_DATA40

_DDR_DATA35

_DDR_DATA38

_DDR_DATA39

_DDR_DATA37

_DDR_DATA36

_DDR_DATA49

_DDR_DATA48

_DDR_DATA46

_DDR_DATA47

_DDR_DATA44

_DDR_DATA45

_DDR_DATA43

_DDR_DATA42

_DDR_DATA56

_DDR_DATA51

_DDR_DATA50

_DDR_DATA54

_DDR_DATA55

_DDR_DATA52

_DDR_DATA53

_DDR_DQS6

_DDR_DATA62

_DDR_DATA63

_DDR_DATA60

_DDR_DATA61

_DDR_DATA59

_DDR_DATA58

_DDR_DQS7

_DDR_DATA57

_DDR_AA[12:0]<9>

_DDR_DATA[63:0]<6,9>

_DDR_DQS[7:0]<6,9>

1 16

56Ohm

2 15

56Ohm

3 14

56Ohm

4 13

56Ohm

5 12

56Ohm

6 11

56Ohm

7 10

56Ohm

8 9

56Ohm

1 16

56Ohm

2 15

56Ohm

3 14

56Ohm

4 13

56Ohm

5 12

56Ohm

6 11

56Ohm

7 10

56Ohm

8 9

56Ohm

1 16

56Ohm

2 15

56Ohm

3 14

56Ohm

4 13

56Ohm

5 12

56Ohm

6 11

56Ohm

7 10

56Ohm

8 9

56Ohm

1 16

56Ohm

2 15

56Ohm

3 14

56Ohm

4 13

56Ohm

6 11

56Ohm

5 12

56Ohm

8 9

56Ohm

7 10

56Ohm

1 16

56Ohm

2 15

56Ohm

4 13

56Ohm

3 14

56Ohm

6 11

56Ohm

5 12

56Ohm

7 10

56Ohm

8 9

56Ohm

1 16

56Ohm

2 15

56Ohm

3 14

56Ohm

5 12

56Ohm

4 13

56Ohm

6 11

56Ohm

7 10

56Ohm

8 9

56Ohm

1 16

56Ohm

2 15

56Ohm

4 13

56Ohm

3 14

56Ohm

5 12

56Ohm

6 11

56Ohm

7 10

56Ohm

8 9

56Ohm

RN64A

RN64B

RN64C

RN64D

RN64E

RN64F

RN64G

RN64H

RN62A

RN62B

RN62C

RN62D

RN62E

RN62F

RN62G

RN62H

RN63A

RN63B

RN63C

RN63D

RN63E

RN63F

RN63G

RN63H

RN56A

RN56B

RN56C

RN56D

RN56F

RN56E

RN56H

RN56G

RN55A

RN55B

RN55D

RN55C

RN55F

RN55E

RN55G

RN55H

RN54A

RN54B

RN54C

RN54E

RN54D

RN54F

RN54G

RN54H

RN53A

RN53B

RN53D

RN53C

RN53E

RN53F

RN53G

RN53H

+V1.25S

+V1.25S

FOR +V1.25S DECOUPLING

Place one cap between every 2 pullup resistors to +V1.25S

+V1.25S

_DDR_DATA24

_DDR_DATA19

_DDR_DATA18

_DDR_DQS2

_DDR_DATA30

_DDR_DATA31

_DDR_DATA28

_DDR_DATA29

_DDR_AA12

_DDR_CAS#<9>

_DDR_RAS#<9>

_DDR_BS1#<9>

DDR_CS2#<6,9>

DDR_CS0#<6,9>

DDR_CS3#<6,9>

DDR_CS1#<6,9>

DDR_CKE3<6,9>

DDR_CKE0<6,9>

DDR_CKE2<6,9>

DDR_CKE1<6,9>

_DDR_WE#<9>

_DDR_BS0#<9>

_DDR_CAS#

_DDR_RAS#

_DDR_AA4

_DDR_AA0

_DDR_AA2

_DDR_AA11

_DDR_BS1#

DDR_CS2#

DDR_CS0#

DDR_CS3#

DDR_CS1#

DDR_CKE3

DDR_CKE0

DDR_CKE2

DDR_CKE1

_DDR_DATA27

_DDR_DATA26

_DDR_DQS3

_DDR_DATA25

_DDR_DATA34

_DDR_DQS4

_DDR_DATA33

_DDR_DATA32

_DDR_AA6

_DDR_AA8

_DDR_WE#

_DDR_BS0#

_DDR_AA10

_DDR_AA1

_DDR_AA3

_DDR_AA5

_DDR_AA7

_DDR_AA9

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

RN58A

RN58B

RN58C

RN58D

RN66A

RN66B

RN66C

RN66D

RN67A

RN67B

RN67C

RN67D

RN57A

RN57B

RN57C

RN57D

RN65A

RN65B

RN61A

RN61B

RN61C

RN61D

RN61E

RN61F

RN61G

RN61H

RN60A

RN60B

RN60C

RN60D

RN60E

RN60F

RN60G

RN60H

RN59A

RN59B

RN59C

RN59D

RN59E

RN59F

RN59G

RN59H

12

C578

0.1uF/10V

12

C576

0.1uF/10V

12

C579

0.1uF/10V

12

C577

0.1uF/10V

12

12

+V1.25S

C582

0.1uF/10V

C580

0.1uF/10V

12

12

C584

0.1uF/10V

C581

0.1uF/10V

12

C586

0.1uF/10V

12

C583

0.1uF/10V

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

C587

0.1uF/10V

+V1.25S

C585

0.1uF/10V

CN13A

CN13B

CN13C

CN13D

CN15A

CN15B

CN15C

CN15D

CN11A

CN11B

CN11C

CN11D

CN8A

CN8B

CN8C

CN8D

CN12A

CN12B

CN12C

CN12D

CN14A

CN14B

CN14C

CN14D

CN10A

CN10B

CN10C

CN10D

CN9A

CN9B

CN9C

CN9D

12

C591

0.1uF/10V

12

C588

0.1uF/10V

12

C590

0.1uF/10V

12

C589

0.1uF/10V

12

12

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

All decoupling capacitances should Be

placed near to the associated pins.

12

12

12

12

C595

C594

0.1uF/10V

0.1uF/10V

12

12

C593

C592

0.1uF/10V

0.1uF/10V

These chip capacitors should be

placed equationally near the

termination resistors

GND

C265

0.1uF/10V

C597

0.1uF/10V

12

C575

0.1uF/10V

12

C596

0.1uF/10V

12

12

C266

0.1uF/10V

C267

0.1uF/10V

12

C268

0.1uF/10V

12

C264

0.1uF/10V

A A

Title :

DDR_TERMINATION

ASUSTECH CO.,LTD.

Size Project Name

C

5

4

3

2

Date: Sheet

Engineer:

A3G

1

Benny Liang

of

10 57Thursday, August 19, 2004

Rev

1.2

5

A

4

3

2

1

+V3.3_VGA

T16 TPC28t

1

T17 TPC28t

1

T14 TPC28t

1

T8 TPC28t

1

T20 TPC28t

1

T18 TPC28t

1

T24 TPC28t

1

T22 TPC28t

1

T23 TPC28t

1

T7 TPC28t

1

T25 TPC28t

1

PWR_PLY = H, VGACORE=1.0V

PWR_PLY = L, VGACORE=1.2V

GND

T6 TPC28t

1

T9 TPC28t

1

T5 TPC28t

1

T4 TPC28t

1

GND

RN49D

RN49C

RN49B

RN49A

C483

0.001uF/50V

/M11-P

GND

Place R313 close

to VGA

M11-P: Pull-up to [1,1]

M9+X: not stuff [0,0]

+V3.3_VGA

+V3.3_VGA

R353

4.7KOhm

/M11-P

1 2

12

12

R352

C482

4.7KOhm

0.1uF/10V

/M11-P

/M11-P

1 2

GND

GNDGND

M11-P: need GPIO_VREF

M9+X: not stuff

Place C483 & C482

close to VGA

M11-P Strap-pin

GPIO[1:0] = 11 (iPD) ; refclk 2 taps earlier than feedback clk (recommended)

GPIO[3:2] = 00 (iPD) ; 0 tap delay between x1clk and x2clk (recommended)

GPIO[6:4] = 000 (iPD) ; AGP8X_DETb = 1, AGP4X, 1.5V, AD16

GPIO[8] = 0 (iPD) ; ID Enable

GPIO[13:11,9] = 0000 (iPD) ; No ROM, CHG_ID=0 (default setting)