Evaluation Board User Guide

One Technology Way • P. O . Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel : 781.329.4700 • Fax : 781.461.3113 • www.analog.com

UG-016

Evaluating the AD9276 and AD9277 Octal LNA/VGA/AAF/12-/14-Bit ADCs

and CW I/Q Demodulators

FEATURES

Full featured evaluation board for the AD9276 and the

AD9277

SPI and alternate clock options

Internal and external reference options

VisualAnalog and SPI Controller software interfaces

EQUIPMENT NEEDED

Analog signal source and antialiasing filter

2 switching power supplies (6.0 V, 2.5 A) CUI EPS060250UH-

PHP-SZ, provided

Linear bench top dc voltage source (0 V to 1.6 V), not

required for CW Doppler mode

PC running Windows® 98 (2nd edition), Windows 2000,

Windows ME, or Windows XP

USB 2.0 port, recommended (USB 1.1 compatible)

AD9276 and AD9277 evaluation board

HSC-ADC-EVALCZ FPGA-based data capture kit

For CW Doppler mode: spectrum analyzer

DOCUMENTS NEEDED

AD9276 and AD9277 data sheets

TYPICAL MEASUREMENT SETUP

HSC-ADC-EVALCZ data sheet, High Speed Converter

Evaluation Platform (FPGA-based data capture kit)

AN-905 Application Note, VisualAnalog Converter Evaluation

Tool Version 1.0 User Manual

AN-878 Application Note, High Speed ADC SPI Control Software

AN-877 Application Note, Interface to High Speed ADCs via SPI

SOFTWARE NEEDED

VisualAnalog

SPI Controller

GENERAL DESCRIPTION

This document describes the evaluation board for the AD9276

and AD9277, which provides all of the support circuitry required

to operate the AD9276 and AD9277 in their various modes and

configurations. The application software used to interface with

the devices is also described.

The AD9276 and AD9277 data sheets, available at

www.analog.com, provide additional information and should be

consulted when using the evaluation board. All documents and

software tools are available at http://www.analog.com/fifo. For

any questions, send an email to highspeed.converters@analog.com.

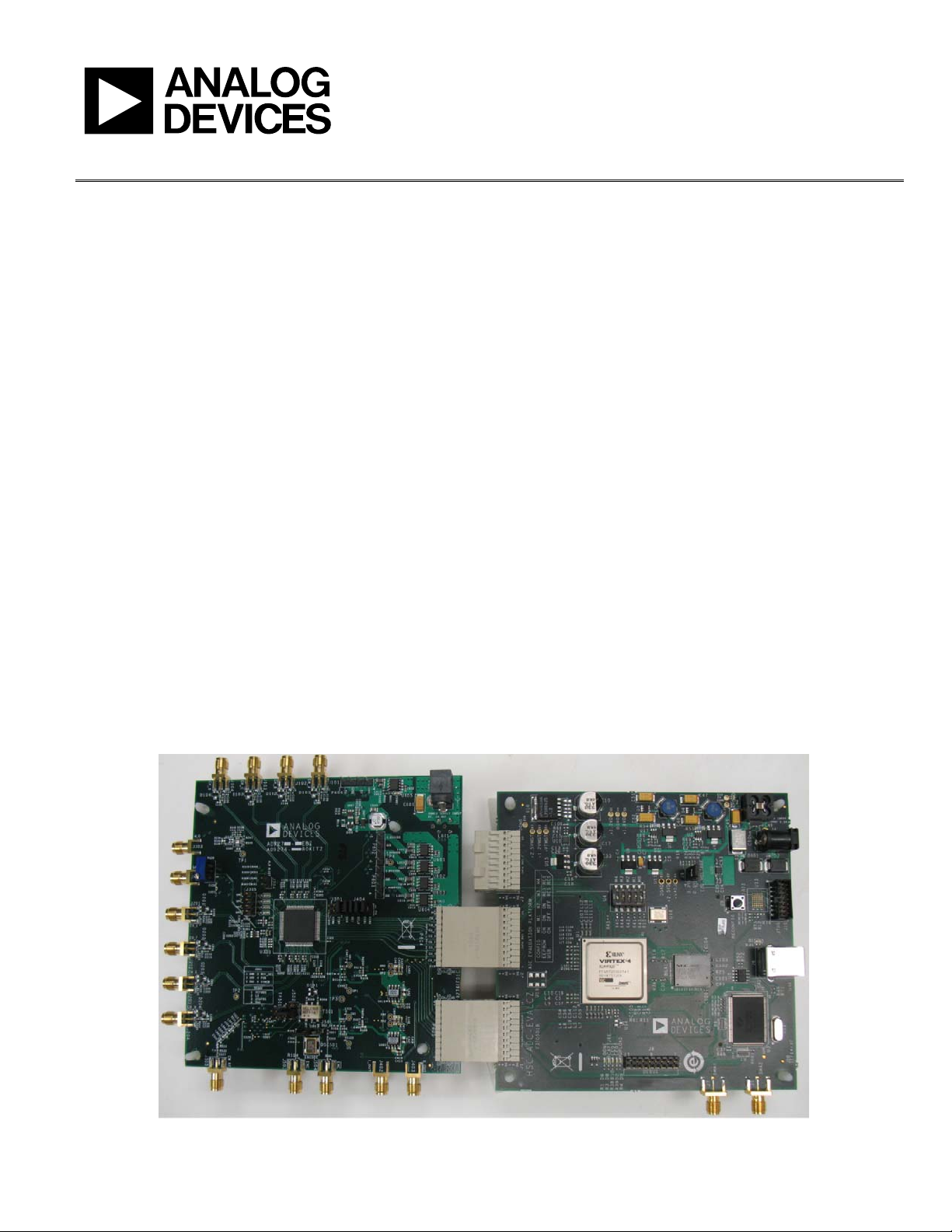

Figure 1. AD9276-65EBZ/AD9276-80KITZ/AD9277-50EBZ Evaluation Board and HSC-ADC-EVALCZ Data Capture Board

See the last page for an important warning and disclaimers. Rev. 0 | Page 1 of 28

08282-001

UG-016 Evaluation Board User Guide

TABLE OF CONTENTS

Features .............................................................................................. 1

Equipment Needed ........................................................................... 1

Documents Needed .......................................................................... 1

Software Needed ............................................................................... 1

General Description ......................................................................... 1

Typical Measurement Setup ............................................................ 1

Evaluation Board Hardware ............................................................ 3

Power Supplies .............................................................................. 3

Input Signals .................................................................................. 3

Output Signals ............................................................................... 3

10/09—Revision 0: Initial Version

Default Operation and Jumper Selection Settings ....................5

Evaluation Board Software Quick Start Procedures .....................6

Configuring the Board For TGC MODE ...................................6

Using the Software for Testing .....................................................6

Using the Integrated I/Q Demodulator

(CW Doppler Mode) ....................................................................9

Evaluation Board Schematics and Artwork ................................ 11

Ordering Information .................................................................... 23

Bill of Materials ........................................................................... 23

ESD Caution................................................................................ 28

Rev. 0 | Page 2 of 28

Evaluation Board User Guide UG-016

EVALUATION BOARD HARDWARE

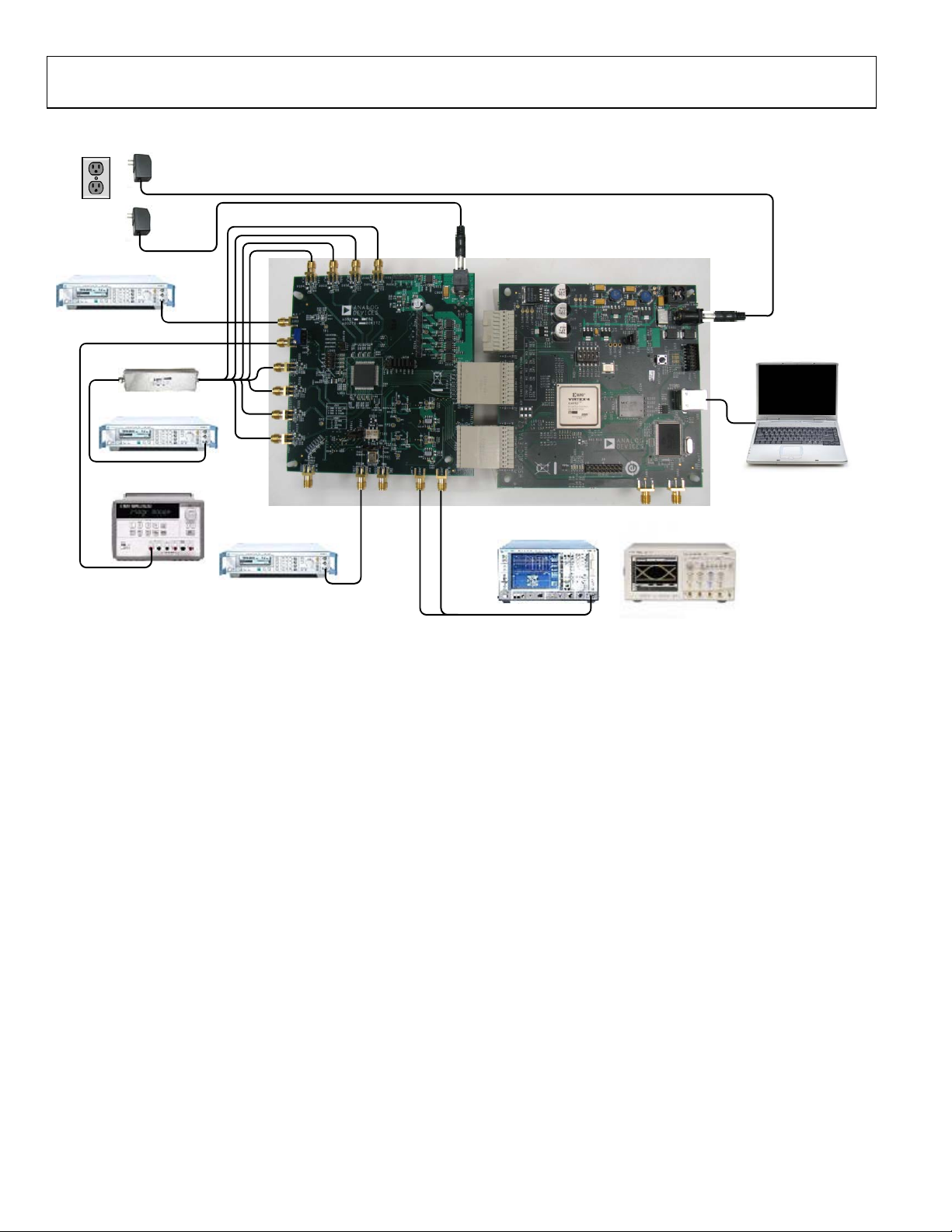

The evaluation board for the AD9276 and AD9277 provides all of

the support circuitry required to operate the AD9276 and

AD9277 in their various modes and configurations. Figure 2

shows the typical bench characterization setup used to evaluate

the performance of the AD9276 and AD9277. It is critical that

the signal sources used for the analog input and clock have very low

phase noise (<1 ps rms jitter) to realize the optimum performance

of the signal chain. Proper filtering of the analog input signal to

remove harmonics and lower the integrated or broadband noise at

the input is necessary to achieve the specified noise performance

(see the AD9276 or AD9277 data sheet).

See the Evaluation Board Software Quick Start Procedures

section to get started and Figure 21 to Figure 32 for the

complete schematics and layout diagrams that demonstrate the

routing and grounding techniques that should be applied at the

system level.

POWER SUPPLIES

This evaluation board comes with a wall-mountable switching

power supply that provides a 6 V, 2.5 A maximum output. Connect

the supply to the rated 100 V ac to 240 V ac wall outlet at 47 Hz

to 63 Hz. The other end is a 2.1 mm inner diameter jack that

connects to the PCB at P601. Once on the PC board, the 6 V

supply is fused and conditioned before connecting to low dropout

linear regulators that supply the proper bias to each of the various

sections on the board.

When operating the evaluation board in a nondefault condition,

L602, L603, L604, L605, L606, L607, L608, and L609 can be

removed to disconnect the switching power supply. This enables

the user to bias each section of the board individually. Use P602,

P603, and P606 to connect a different supply for each section. At

least one 1.8 V supply is needed with a 1 A current capability for

1.8 V AVDD and 1.8 V DRVDD; however, it is recommended that

separate supplies be used for both analog and digital domains.

An additional supply is also required to supply 3.0 V to the DUT,

3.0 V AVDD2. This should also have a 1 A current capability. To

operate the evaluation board using the SPI and alternate clock

options, a separate 3.3 V analog supply is needed in addition to

the other supplies. The 3.3 V supply, or 3.3 V AVDD, should have a

1 A current capability. To bias the CW I/Q demodulator section

and differential gain drive circuitry, separate +5 V and −5 V

supplies are required at P606. These should each have 1 A current

capability.

INPUT SIGNALS

When connecting the TGC (time gain compensation) ADC

clock, 4LO and analog source, use clean signal generators with

low phase noise, such as Rohde and Schwarz SMA or HP8644B

signal generators or the equivalent. Use a 1 meter shielded, RG-58,

50 Ω coaxial cable for making connections to the evaluation

board. Enter the desired frequency and amplitude (refer to the

specifications in the AD9276 or AD9277 data sheet). In the

default condition, the evaluation board is set up to clock the ADC

from the crystal oscillator, OSC501, when in the TGC mode.

If a different or external ADC clock source is desired, follow the

instructions in the Clock section. Typically, most Analog Devices,

Inc., evaluation boards can accept ~2.8 V p-p or 13 dBm sine

wave input for the clock. When connecting the analog input

source, it is recommended to use a multipole, narrow-band

band-pass filter with 50 Ω terminations. Analog Devices uses

TTE and K&L Microwave, Inc., band-pass filters. The filter

should be connected directly to the evaluation board.

OUTPUT SIGNALS

The default TGC setup uses the FIFO5 high speed, dual-channel

FIFO data capture board (HSC-ADC-EVALCZ). Two of the

eight TGC channels can then be evaluated at the same time. For

more information on channel settings on these boards and their

optional settings, visit http://www.analog.com/fifo.

The default I/Q demodulator setup uses two AD8021 amplifiers

for I-V conversion and two ADA4841 amplifiers for gain and

filtering. The analog outputs can be evaluated using an oscilloscope

or spectrum analyzer.

Rev. 0 | Page 3 of 28

UG-016 Evaluation Board User Guide

W

ALL OUTLET

100V TO 240V AC

47Hz TO 63Hz

SWITCHING

POWER

SUPPLY

SWITCHING

SIGNAL

SYNTHESIZER

ANALOG I N P UT

SYNTHESIZER

SIGNAL

POWER

SUPPLY

4LO INPUT

6V DC

2A MAX

6V DC

2A MAX

AGILENT

POWER SUPPLY

GAIN CONTROL

INPUT

SIGNAL

SYNTHESIZER

OPTIONAL

CLOCK

INPUT

CW I/Q

OUTPUTS

SPECTRUM

ANALYZER

Figure 2. Evaluation Board Connection

OR

OSCILLOSCOPE

PC

RUNNING ADC

ANALYZER

OR VISUAL ANALOG

USER SOFTWARE

08282-002

Rev. 0 | Page 4 of 28

Evaluation Board User Guide UG-016

DEFAULT OPERATION AND JUMPER SELECTION SETTINGS

This section explains the default and optional settings or modes

allowed on the evaluation board for the AD9276 and AD9277.

Power Circuitry

Connect the switching power supply that is supplied in the

evaluation kit between a rated 100 V ac to 240 V ac wall outlet

at 47 Hz to 63 Hz and P601.

Analog Input Front-End Circuit

The evaluation board is set up for single-ended Kelvin

connection analog input with an optimum 50 Ω impedance

match of 18 MHz of bandwidth. For a different bandwidth

response, use the manual tune feature and antialiasing filter

settings.

VREF

VREF is set to 1.0 V. This causes the ADC to operate with the

internal reference in the 2.0 V p-p full-scale range. A separate

external reference option using the ADR130 is also included on

the evaluation board. Populate R320 with a 0 Ω resistor and remove

C301. Note that ADC full-scale ranges less than 2.0 V p-p are

not supported by the AD9276 and AD9277.

RBIAS

RBIAS has a default setting of 10 kΩ (R304) to ground and is used

to set the ADC core bias current. However, note that using other

than a 10 kΩ, 1% resistor for RBIAS may degrade the performance

of the device, depending on the resistor chosen.

Clock Circuitry

The default clock input circuitry is derived from a simple

transformer-coupled circuit using a high bandwidth 1:1

impedance ratio transformer (T501) that adds a very low amount

of jitter to the clock path. The clock input is 50 Ω terminated

and ac-coupled to handle single-ended sine wave types of inputs.

The transformer converts the single-ended input to a differential

signal that is clipped before entering the ADC clock inputs.

The evaluation board is already set up to be clocked from the

crystal oscillator, OSC501. This oscillator is a low phase noise

oscillator from Valpey Fisher (VFAC3HL-40MHz). If a different

clock source is desired, remove R503, set Jumper J501 to disable

the oscillator from running, and connect the external clock

source to the SMA connector, J503.

A differential LVPECL clock driver can also be used to clock the

ADC input using the AD9516 (U501). Populate C528 and C529

with 0.1 µF capacitors and remove C506 and C507 to disconnect

the default clock path inputs. In addition, populate C511 and C512

with a 0.1 F capacitor. The AD9516 has many SPI-selectable

options that are set to a default mode of operation. Consult the

AD9516 data sheet for more information about these and other

options.

PDWN

To enable the power-down feature, short P301 (Pin 3 to Pin 4)

to the on position (AVDD) on the PDWN pin.

STBY

To enable the standby feature, short P301 (Pin 1 to Pin 2) to the

on position (AVDD) on the STBY pin.

GAIN+, GAIN−

To change the VGA attenuation, drive the GAIN+ pin from 0 V

to 1.6 V on J401 using a linear supply. This uses the single-ended

method to change the VGA gain from 0 dB to 42 dB. U411 is

available for users who wish to drive the gain pins (GAIN±)

differentially. Install R426, R435, and R436 and remove C456,

C457, and R440 to connect the amplifier correctly. In differential

mode, a linear supply from −0.8 V to +0.8 V on J401 is required

to change the VGA gain from 0 dB to 42 dB.

If an external source is not available, remove R425, and install

R438 to use the on-board resistive divider (R439) for gain

adjustment in the single-ended case.

CWI/Q+, CWI/Q−

To view the CWI+/CWI− and/or CWQ+/CWQ− outputs,

configure the AD9276 and AD9277 to be in CW mode and

enable each channel via the SPI Controller program. Apply a

13 dBm, 20 MHz reference clock (4LO) on J303. Each enabled

channel is summed and is available through J402/J403.

DOUTx+, DOUTx−

If an alternative data capture method to the setup described in

Figure 2 is used, optional receiver terminations, R604 to R613, can

be installed next to the high-speed backplane connector, P604.

Rev. 0 | Page 5 of 28

UG-016 Evaluation Board User Guide

EVALUATION BOARD SOFTWARE QUICK START PROCEDURES

This section provides quick start procedures for using the AD9276

and AD9277, either on the evaluation board or at the system

level design. Both the default and optional settings are described.

CONFIGURING THE BOARD FOR TGC MODE

Before using the software for testing, configure the evaluation

board as follows:

1. Connect the evaluation board and the HSC-ADC-EVALCZ

as shown in Figure 1 and Figure 2.

2. Connect one 6 V, 2.5 A switching power supply (such as

the CUI, Inc., EPS060250UH-PHP-SZ supplied) to the

evaluation board.

3. Connect one 6 V, 2.5 A switching power supply (such as

the CUI EPS060250UH-PHP-SZ supplied) to the HSCADC-EVALCZ board.

4. Connect the USB cable to J6 on the HSC-ADC-EVALCZ

board to the PC.

5. On the evaluation board, place jumpers on all five pin pairs

of J404 to connect the SPI bus.

6. On the evaluation board, ensure that J501 (OSC_EN) is

jumpered to the OFF setting to use the on-board 40 MHz

Valpey Fisher VFAC3 oscillator.

7. On the evaluation board, use a clean signal generator with

low phase noise to provide an input signal to the desired

channel. Use a 1 meter, shielded, RG-58, 50 Ω coaxial cable

to connect the signal generator. For best results, use a

narrow-band band-pass filter with 50 Ω terminations and

an appropriate center frequency (Analog Devices uses

TTE, Allen Avionics, and K&L band-pass filters).

USING THE SOFTWARE FOR TESTING

Set Up the ADC Data Capture Block

After configuring the evaluation board, set up the ADC data

capture block using the following steps:

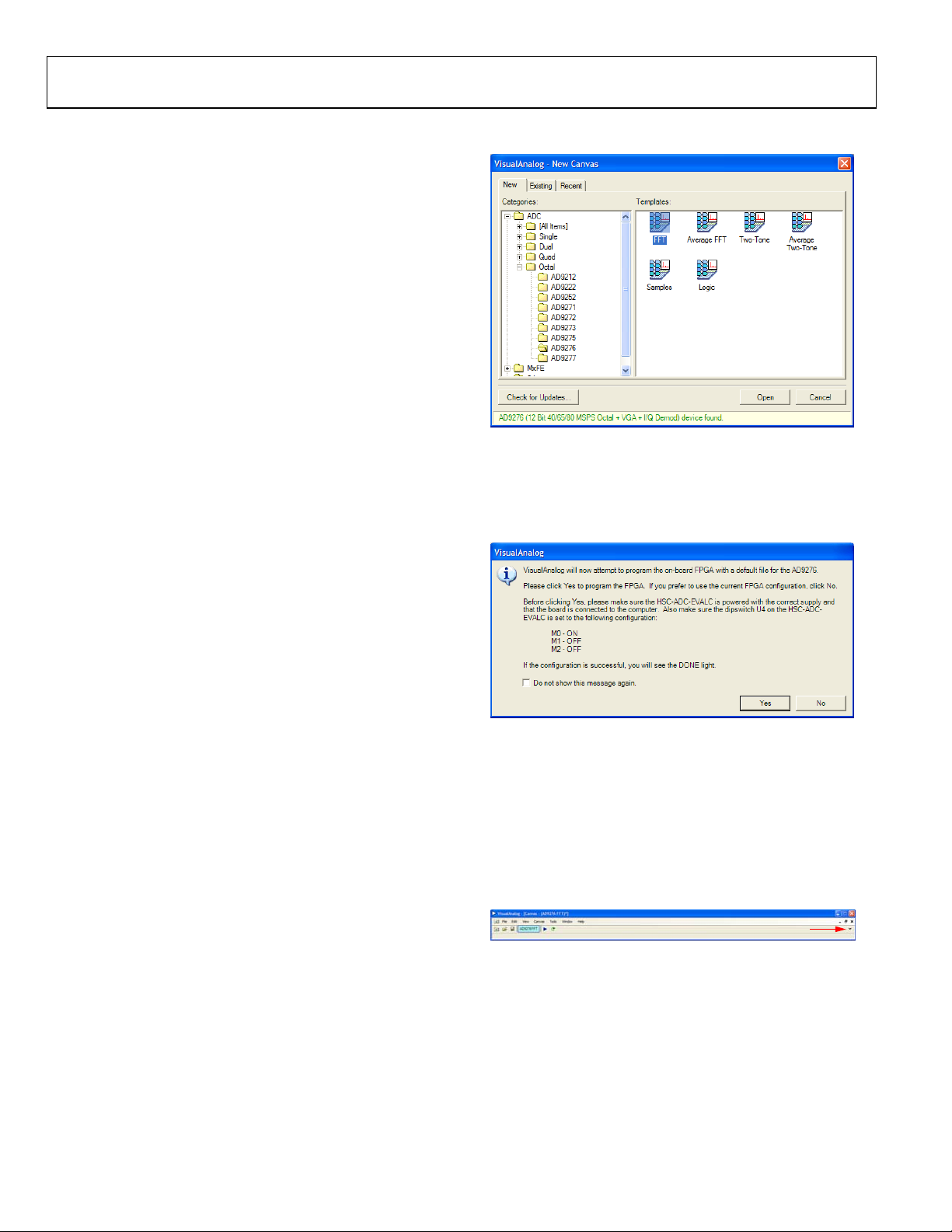

1. Open VisualAnalog™ on a PC. AD9276 or AD9277 should

be listed in the status bar of the New Canvas window.

Select the template that corresponds to the type of testing

to be performed (see Figure 3).

2. After the template is selected, a message box opens, asking

3. To view different channels or change features to settings

Figure 3. VisualAnalog, New Canvas Dialog Box

if the default configuration can be used to program the

FPGA (see Figure 4). Click Ye s , and the window closes.

If a different program is desired, follow Step 3.

Figure 4. VisualAnalog, New Canvas Message Box

other than the default settings, click the Expand Display

button located on the top right corner of the VisualAnalog

window, as shown in Figure 5 and Figure 6.

This process is described in the AN-905 Application Note,

VisualAnalog Converter Evaluation Tool Version 1.0 User

Manual. After you are finished, click the Collapse Display

button.

EXPAND DISPLAY BUTTON

Figure 5. VisualAnalog Window Toolbar, Expand Display Button

08282-003

08282-004

8282-005

Rev. 0 | Page 6 of 28

Evaluation Board User Guide UG-016

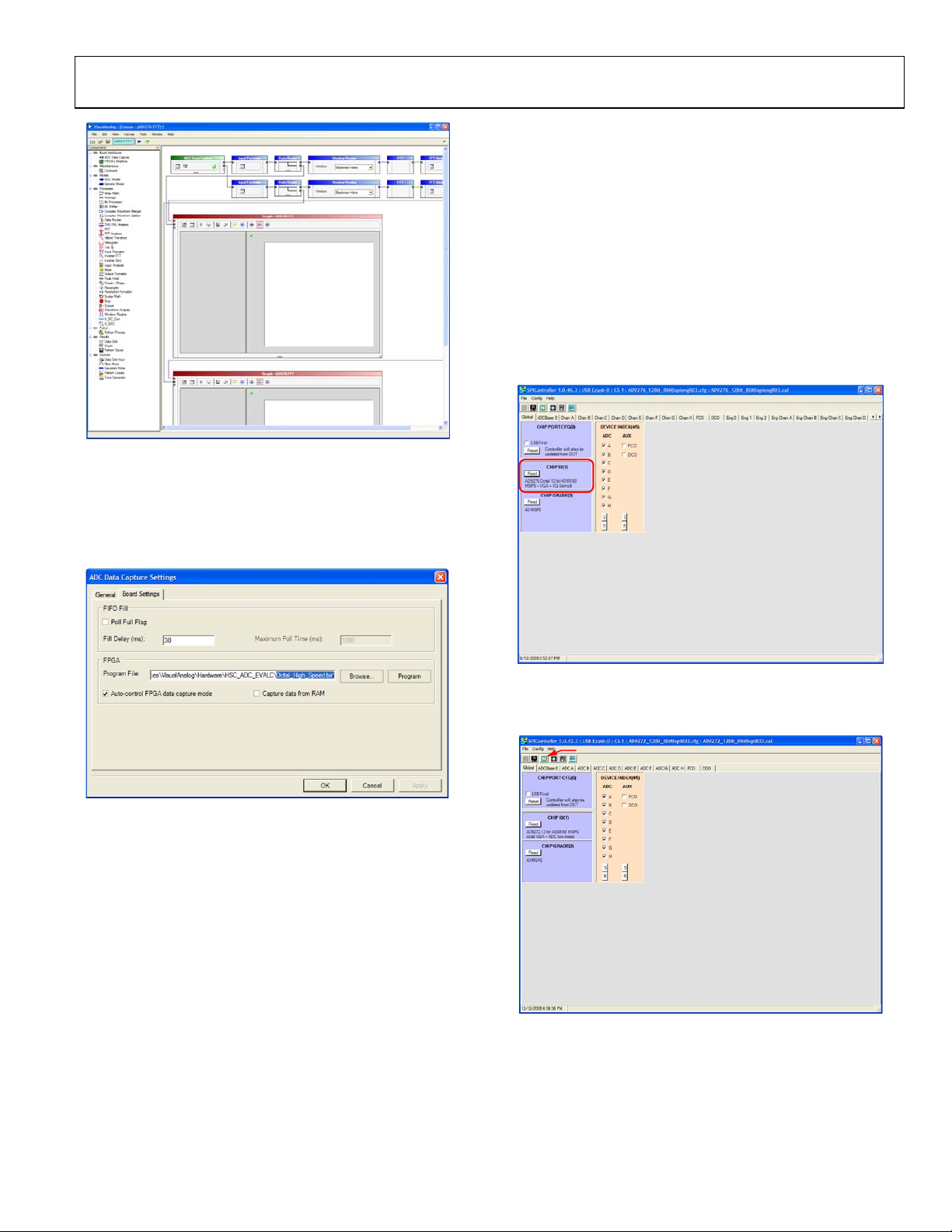

Set Up the SPI Controller

After the ADC data capture board setup has been completed,

set up the SPI Controller:

1. Open the SPI Controller software by going to the Start

menu or double-clicking the SPI Controller software

desktop icon. If prompted for a configuration file, select

the appropriate one. If not, check the title bar at the top of

the SPI Controller window to determine which configuration

is loaded. If necessary, choose Cfg Open from the File

menu and select the appropriate configuration Note that

the CHIP ID(1) field should be filled to indicate whether

the correct SPI Controller configuration file is loaded (see

Figure 8).

08282-006

Figure 6. VisualAnalog, Main Window Expanded Display

4. Program the FPGA of the HSC-ADC-EVALCZ board to a

setting other than the default setting as described in Step 3.

Then expand the VisualAnalog display and click the Settings

button in the ADC Data Capture block (see Figure 6). The

ADC Data Capture Settings box opens (see Figure 7).

Figure 7. ADC Data Capture Settings, Board Settings Tab

5. Select the Board Settings tab and browse to the appropriate

programming file. If you are using an encode rate <28 MSPS,

select Octal_Low_Speed.bin. If you are using an encode

rate >28 MSPS, select Octal_High_Speed.bin. Next, click

Program; the DONE LED in the HSC-ADC-EVALCZ board

should then turn on. If more than two channels are required

to be displayed, select High_Speed_Octal_synchronous_

capture.bin. This canvas allows the user to display all the

channels at once. The drawback is that each FFT display is

only 8k points.

Exit the ADC Data Capture Settings box by clicking OK.

08282-008

Figure 8. SPI Controller, CHIP ID(1) Box

2. Click the New DUT button in the SPI Controller (see

Figure 9).

NEW DUT BUT TON

08282-007

08282-009

Figure 9. SPI Controller, New DUT Button

Rev. 0 | Page 7 of 28

UG-016 Evaluation Board User Guide

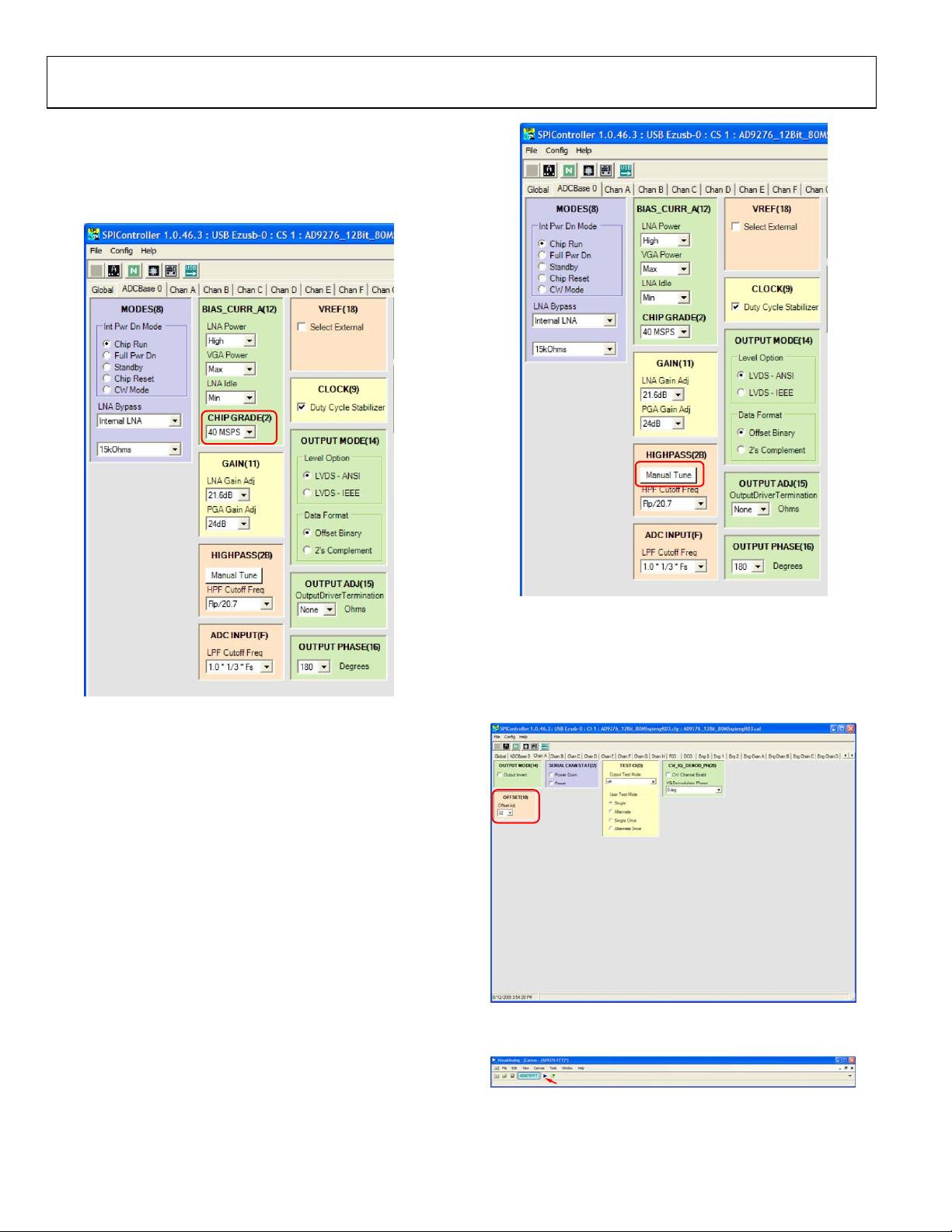

3. In the ADCBase 0 tab of the SPI Controller, find the CHIP

GRADE(2) box. Use the drop-down list box to select the

correct speed mode, if necessary. See the AD9276 or AD9277

data sheet, the AN-878 Application Note, and the AN-877

Application Note for reference.

Figure 10. SPI Controller, CHIP GRADE(2)

4. In the ADCBase 0 tab of the SPI Controller, find the

HIGHPASS(2B) box. Click the Manual Tune button to

calibrate the antialiasing filter. See the AD9276 or AD9277

data sheet, the AN-878 Application Note, and the AN-877

Application Note for reference.

Figure 11. SPI Controller, HIGHPASS(2B)

08282-011

5. In the Chan A tab of SPI Controller, find the OFFSET(10)

box. Use the drop-down list box labeled Offset Adj to

perform an offset correction to the LNA if the LNA power

08282-010

setting BIAS_CURR_A(12) is set low. The default value

is 32.

08282-012

Figure 12. SPI Controller, OFFSET(10)

6. Click the Run button in the VisualAnalog toolbar.

Rev. 0 | Page 8 of 28

RUN BUTTON

Figure 13. VisualAnalog Window Toolbar, Run Button

08282-013

Evaluation Board User Guide UG-016

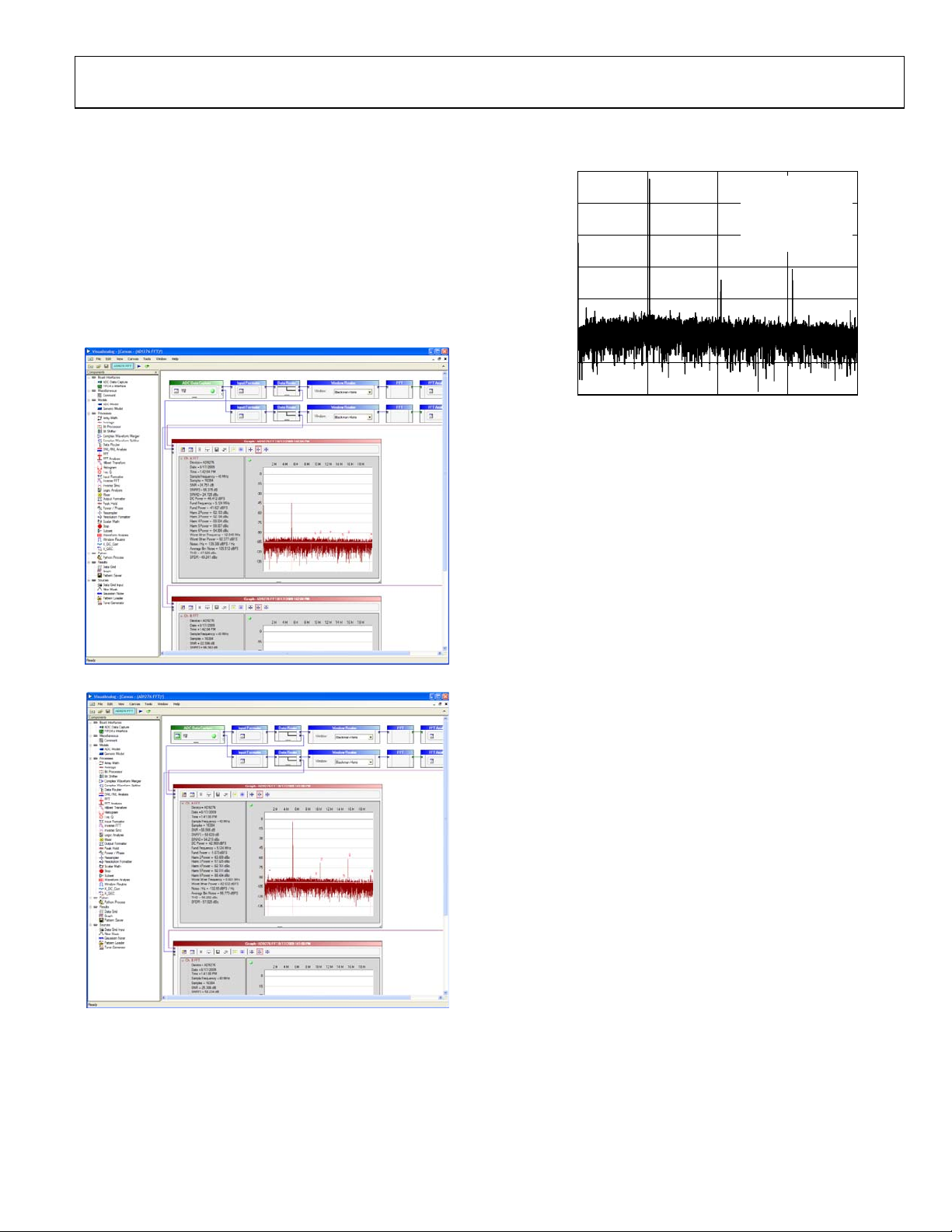

Adjust the Amplitude of the Input Signal

Next, adjust the amplitude of the input signal for each channel

as follows:

1. Adjust the amplitude of the input signal so that the

fundamental is at the desired level (examine the Fund

Power reading in the left panel of the VisualAnalog FFT

window). If the gain pin voltage is too low, it is not possible

to reach full scale without distortion. Use a higher gain setting

or a lower input level to avoid distortion. This also depends

on the PGA gain setting, which can be 30 dB, 27 dB, 24 dB

(default), or 21 dB. See Figure 14 and Figure 15.

Figure 14. VisualAnalog, FFT Graph, Gain = 0 V

08282-014

3. Click the disk icon within the Graph box to save the

performance plot. See Figure 16.

0

–20

–40

–60

–80

AMPLITUDE ( d BF S)

–100

–120

–140

0 5 10 15 20

Figure 16. Typical FFT, AD9276 and AD9277

FREQUENCY (MHz )

fIN = 5MHz @ –1dBFS

LNA = 21.6dB

PGA = 24dB

V

= 1.6V

GAIN

LPF = 1 × 1/3 × F

HPF = FLP ÷ 20.7

SAMPLE

08282-016

USING THE INTEGRATED I/Q DEMODULATOR (CW DOPPLER MODE)

To examine the spectrum of the CW Doppler integrated I/Q

demodulator output, use the following procedure:

1. Complete the steps in the Configuring the Board and

Using the Software for Testing sections to ensure that the

evaluation board is set up correctly.

2. Optionally, remove the voltage source from the gain pin,

J401. It does not affect the CW Doppler output.

3. Use a 1 meter, shielded, RG-58, 50 Ω coaxial cable to

connect the spectrum analyzer to J402 and/or J403.

8. Connect a 20 MHz signal source to J303, 4LO input. Use a

clean signal generator with low phase noise to provide an

input clock signal. Use a 1 meter, shielded, RG-58, 50 Ω

coaxial cable to connect the signal generator.

9. Connect an analog input signal, 5.0123 MHz for example,

to ChA, J101. Use a clean signal generator with low phase

noise to provide an input signal to the desired channel. Use

a 1 meter, shielded, RG-58, 50 Ω coaxial cable to connect

the signal generator. For best results, use a narrow-band

band-pass filter with 50 Ω terminations and an appropriate

center frequency (Analog Devices uses TTE, Allen

Avionics, and K&L band-pass filters).

4. In the ADCBase 0 tab of the SPI Controller, find the

MODES(8) box. Select the CW Mode option (see

Figure 17).

Figure 15. VisualAnalog, FFT Graph, Gain = 1.6 V

2. If another channel needs to be evaluated, change the

channel setting within the ADC Data Capture block.

Channels A and B are the default displayed channels ADC

Data Capture Settings box under the General tab. Clock

Frequency and the number of samples can also be changed.

8282-015

Rev. 0 | Page 9 of 28

Loading...

Loading...