ANALOG DEVICES OP07 Service Manual

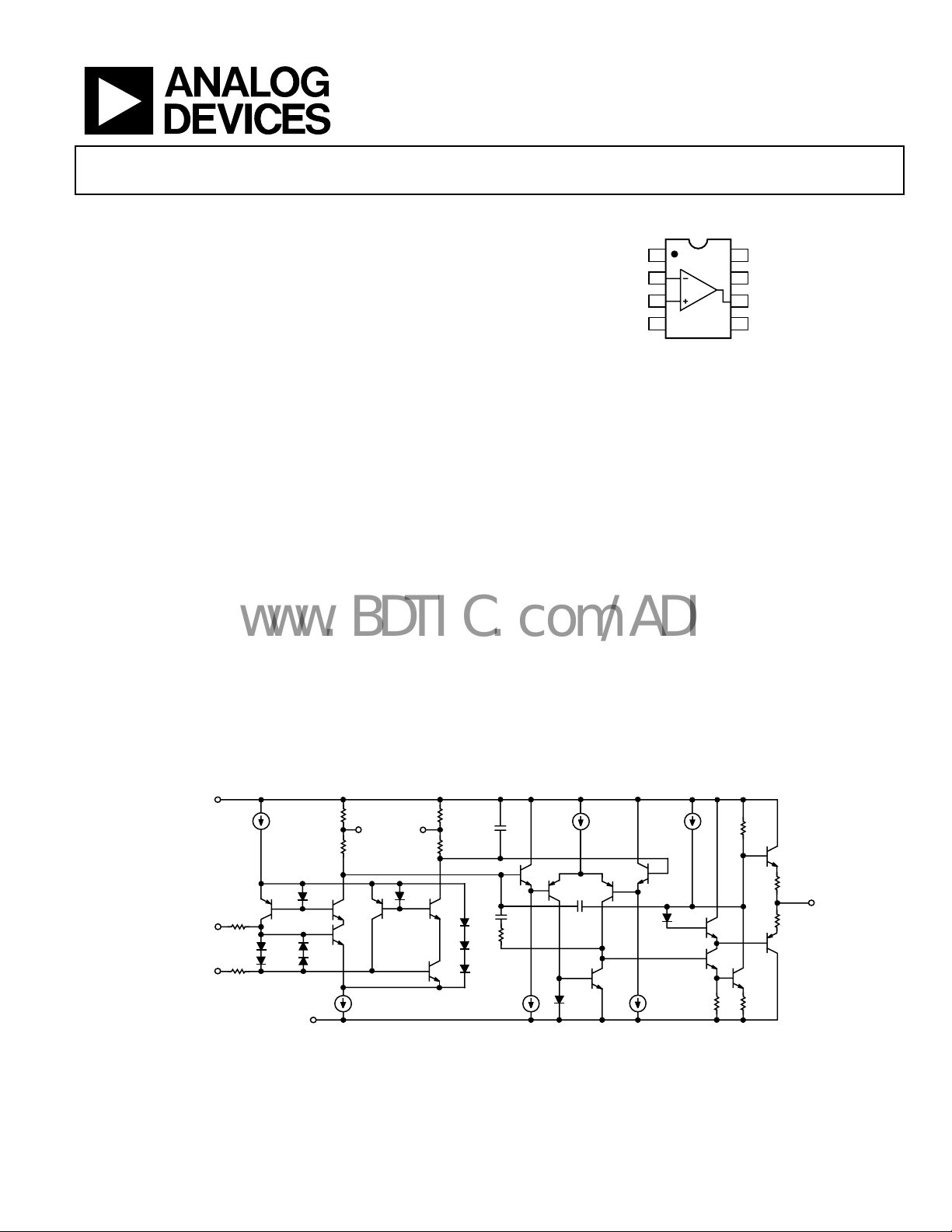

Ultralow Offset Voltage

V

V

G

www.BDTIC.com/ADI

FEATURES

Low VOS: 75 μV maximum

Low V

Ultrastable vs. time: 1.5 μV per month maximum

Low noise: 0.6 μV p-p maximum

Wide input voltage range: ±14 V typical

Wide supply voltage range: 3 V to 18 V

125°C temperature-tested dice

APPLICATIONS

Wireless base station control circuits

Optical network control circuits

Instrumentation

Sensors and controls

Precision filters

GENERAL DESCRIPTION

The OP07 has very low input offset voltage (75 μV maximum for

OP07E) that is obtained by trimming at the wafer stage. These

low offset voltages generally eliminate any need for external

nulling. The OP07 also features low input bias current (±4 nA for

the OP07E) and high open-loop gain (200 V/mV for the OP07E).

The low offset and high open-loop gain make the OP07

particularly useful for high gain instrumentation applications.

drift: 1.3 μV/°C maximum

OS

Thermocouples

Resistor thermal detectors (RTDs)

Strain bridges

Shunt current measurements

Operational Amplifier

OP07

PIN CONFIGURATION

OS

–IN

+IN

V–

OP07

2

3

4

NC = NO CONNECT

1

TRIM

Figure 1.

The wide input voltage range of ±13 V minimum combined

with a high CMRR of 106 dB (OP07E) and high input

impedance provide high accuracy in the noninverting circuit

configuration. Excellent linearity and gain accuracy can be

maintained even at high closed-loop gains. Stability of offsets

and gain with time or variations in temperature is excellent. The

accuracy and stability of the OP07, even at high gain, combined

with the freedom from external nulling have made the OP07 an

industry standard for instrumentation applications.

The OP07 is available in two standard performance grades. The

OP07E is sp

ecified for operation over the 0°C to 70°C range,

and the OP07C is specified over the −40°C to +85°C

temperature range.

The OP07 is available in epoxy 8-lead PDIP and 8-lead narrow

SOI

C packages. For CERDIP and TO-99 packages and standard

microcircuit drawing (SMD) versions, see the OP77.

8

VOS TRIM

7

V+

6

OUT

5

NC

0316-001

+

7

Q5

NONINVERTI N

INPUT

INVERTING

INPUT

1

R2A AND R2B ARE ELECTRONICALLY ADJUST ED ON CHIP AT FACTORY FOR MINIMUM INPUT OF FSET VO LTAGE.

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

R3

3

2

Q21

Q22

R4

1

R2A

R1A

Q7

Q23

Q24

4

V–

1

Q3 Q6

Q1

(OPTIONAL

NULL)

Q8

R2B

8

R1B

Q4

Q2

Figure 2. Simplified Schematic

1

Q16

Q15

R7

Q19

R9

OUT

6

R10

Q20

Q18

R8

R6

00316-002

C1

Q9

Q11

C3

Q27

R5

Q26

Q25

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

C2

Q13

Q10

Q12

Q17

Q14

OP07

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Absolute Maximum Ratings ............................................................6

Applications....................................................................................... 1

General Description ......................................................................... 1

Pin Configuration............................................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

OP07E Electrical Characteristics ............................................... 3

OP07C Electrical Characteristics ............................................... 4

REVISION HISTORY

7/06—Rev. C. to Rev D

Changes to Features.......................................................................... 1

Changes to General Description .................................................... 1

Changes to Specifications Section.................................................. 3

Changes to Table 4............................................................................ 6

Changes to Figure 6 and Figure 8................................................... 7

Changes to Figure 13 and Figure 14............................................... 8

Changes to Figure 20........................................................................ 9

Changes to Figure 21 to Figure 25................................................ 10

Changes to Figure 26 and Figure 30............................................. 11

Replaced Figure 28 .........................................................................11

Changes to Applications Information Section............................ 12

Updated Outline Dimensions....................................................... 13

Changes to Ordering Guide.......................................................... 14

8/03—Rev. B to Rev. C

hanges to OP07E Electrical Specifications................................. 2

C

Changes to OP07C Electrical Specifications................................. 3

Edits to Ordering Guide .................................................................. 5

Edits to Figure 6................................................................................ 9

Updated Outline Dimensions....................................................... 11

Thermal Resistance.......................................................................6

ESD Caution...................................................................................6

Typical Performance Characteristics..............................................7

Typical Applications....................................................................... 11

Applications Information.......................................................... 12

Outline Dimensions....................................................................... 13

Ordering Guide .......................................................................... 14

3/03—Rev. A to Rev. B

pdated Package Titles......................................................Universal

U

Updated Outline Dimensions....................................................... 11

2/02—Rev. 0 to Rev. A

dits to Features.................................................................................1

E

Edits to Ordering Guide...................................................................1

Edits to Pin Connection Drawings .................................................1

Edits to Absolute Maximum Ratings..............................................2

Deleted Electrical Characteristics .............................................. 2–3

Deleted OP07D Column from Electrical Characteristics....... 4–5

Edits to TPCs ................................................................................ 7–9

Edits to High-Speed, Low V

Composite Amplifier ...................9

OS

Rev. D | Page 2 of 16

OP07

www.BDTIC.com/ADI

SPECIFICATIONS

OP07E ELECTRICAL CHARACTERISTICS

VS = ±15 V, unless otherwise noted.

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

TA = 25°C

Input Offset Voltage

Long-Term VOS Stability

1

2

Input Offset Current IOS 0.5 3.8 nA

Input Bias Current IB ±1.2 ±4.0 nA

Input Noise Voltage en p-p 0.1 Hz to 10 Hz

Input Noise Voltage Density en fO = 10 Hz 10.3 18.0 nV/√Hz

f

f

Input Noise Current In p-p 14 30 pA p-p

Input Noise Current Density In fO = 10 Hz 0.32 0.80 pA/√Hz

f

f

Input Resistance, Differential Mode

4

Input Resistance, Common Mode R

Input Voltage Range IVR ±13 ±14 V

Common-Mode Rejection Ratio CMRR VCM = ±13 V 106 123 dB

Power Supply Rejection Ratio PSRR VS = ±3 V to ±18 V 5 20 μV/V

Large Signal Voltage Gain AVO RL ≥ 2 kΩ, VO = ±10 V 200 500 V/mV

R

0°C ≤ TA ≤ 70°C

Input Offset Voltage

Voltage Drift Without External Trim

Voltage Drift with External Trim

1

4

3

Input Offset Current IOS 0.9 5.3 nA

Input Offset Current Drift TCIOS 8 35 pA/°C

Input Bias Current IB ±1.5 ±5.5 nA

Input Bias Current Drift TCIB 13 35 pA/°C

Input Voltage Range IVR ±13 ±13.5 V

Common-Mode Rejection Ratio CMRR VCM = ±13 V 103 123 dB

Power Supply Rejection Ratio PSRR VS = ±3 V to ±18 V 7 32 μV/V

Large Signal Voltage Gain AVO RL ≥ 2 kΩ, VO = ±10 V 180 450 V/mV

OUTPUT CHARACTERISTICS

TA = 25°C

Output Voltage Swing VO RL ≥ 10 kΩ ±12.5 ±13.0 V

R

R

0°C ≤ TA ≤ 70°C

Output Voltage Swing VO RL ≥ 2 kΩ ±12 ±12.6 V

VOS 30 75 μV

VOS/Time 0.3 1.5 μV/Month

3

= 100 Hz

O

= 1 kHz 9.6 11.0 nV/√Hz

O

= 100 Hz

O

= 1 kHz 0.12 0.17 pA/√Hz

O

3

3

0.35 0.6 μV p-p

10.0 13.0 nV/√Hz

0.14 0.23 pA/√Hz

RIN 15 50 MΩ

160 GΩ

INCM

≥ 500 Ω, VO = ±0.5 V, VS = ±3 V

L

4

150 400 V/mV

VOS 45 130 μV

TCVOS 0.3 1.3 μV/°C

TCV

RP = 20 kΩ 0.3 1.3 μV/°C

OSN

≥ 2 kΩ ±12.0 ±12.8 V

L

≥ 1 kΩ ±10.5 ±12.0 V

L

Rev. D | Page 3 of 16

OP07

www.BDTIC.com/ADI

Parameter Symbol Conditions Min Typ Max Unit

DYNAMIC PERFORMANCE

TA = 25°C

Slew Rate SR RL ≥ 2 kΩ

Closed-Loop Bandwidth BW A

Open-Loop Output Resistance RO VO = 0, IO = 0 60 Ω

Power Consumption Pd VS = ±15 V, No load 75 120 mW

V

Offset Adjustment Range RP = 20 kΩ ±4 mV

1

Input offset voltage measurements are performed by automated test equipment approximately 0.5 seconds after application of power.

2

Long-term input offset voltage stability refers to the averaged trend time of VOS vs. the time over extended periods after the first 30 days of operation. Excluding the

initial hour of operation, changes in VOS during the first 30 operating days are typically 2.5 μV. Refer to the Typical Performance Characteristics section. Parameter is

sample tested.

3

Sample tested.

4

Guaranteed by design.

5

Guaranteed but not tested.

OP07C ELECTRICAL CHARACTERISTICS

VS = ±15 V, unless otherwise noted.

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

TA = 25°C

Input Offset Voltage1 VOS 60 150 μV

Long-Term VOS Stability2 VOS/Time 0.4 2.0 μV/Month

Input Offset Current IOS 0.8 6.0 nA

Input Bias Current IB ±1.8 ±7.0 nA

Input Noise Voltage en p-p 0.1 Hz to 10 Hz3 0.38 0.65 μV p-p

Input Noise Voltage Density en fO = 10 Hz 10.5 20.0 nV/√Hz

f

f

Input Noise Current In p-p 15 35 pA p-p

Input Noise Current Density In fO = 10 Hz 0.35 0.90 pA/√Hz

f

f

Input Resistance, Differential Mode4 RIN 8 33 MΩ

Input Resistance, Common Mode R

Input Voltage Range IVR ±13 ±14 V

Common-Mode Rejection Ratio CMRR VCM = ±13 V 100 120 dB

Power Supply Rejection Ratio PSRR VS = ±3 V to ±18 V 7 32 μV/V

Large Signal Voltage Gain AVO RL ≥ 2 kΩ, VO = ±10 V 120 400 V/mV

R

−40°C ≤ TA ≤ +85°C

Input Offset Voltage

Voltage Drift Without External Trim

Voltage Drift with External Trim

Input Offset Current IOS 1.6 8.0 nA

Input Offset Current Drift TCIOS 12 50 pA/°C

Input Bias Current IB ±2.2 ±9.0 nA

Input Bias Current Drift TCIB 18 50 pA/°C

Input Voltage Range IVR ±13 ±13.5 V

Common-Mode Rejection Ratio CMRR VCM = ±13 V 97 120 dB

Power Supply Rejection Ratio PSRR VS = ±3 V to ±18 V 10 51 μV/V

Large Signal Voltage Gain AVO RL ≥ 2 kΩ, VO = ±10 V 100 400 V/mV

1

4

3

3

5

= 1

VOL

= ±3 V, No load 4 6 mW

S

0.1 0.3 V/μs

0.4 0.6 MHz

= 100 Hz3 10.2 13.5 nV/√Hz

O

= 1 kHz 9.8 11.5 nV/√Hz

O

= 100 Hz3 0.15 0.27 pA/√Hz

O

= 1 kHz 0.13 0.18 pA/√Hz

O

120 GΩ

INCM

≥ 500 Ω, VO = ±0.5 V, VS = ±3 V4100 400 V/mV

L

VOS 85 250 μV

TCVOS 0.5 1.8 μV/°C

TCV

RP = 20 kΩ 0.4 1.6 μV/°C

OSN

Rev. D | Page 4 of 16

OP07

www.BDTIC.com/ADI

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT CHARACTERISTICS

TA = 25°C

Output Voltage Swing VO RL ≥ 10 kΩ ±12.0 ±13.0 V

R

R

−40°C ≤ TA ≤ +85°C

Output Voltage Swing VO RL ≥ 2 kΩ ±12 ±12.6 V

DYNAMIC PERFORMANCE

TA = 25°C

Slew Rate SR RL ≥ 2 kΩ3 0.1 0.3 V/μs

Closed-Loop Bandwidth BW A

Open-Loop Output Resistance RO VO = 0, IO = 0 60 Ω

Power Consumption Pd VS = ±15 V, No load 80 150 mW

V

Offset Adjustment Range RP = 20 kΩ ±4 mV

1

Input offset voltage measurements are performed by automated test equipment approximately 0.5 seconds after application of power.

2

Long-term input offset voltage stability refers to the averaged trend time of VOS vs. the time over extended periods after the first 30 days of operation. Excluding the

initial hour of operation, changes in VOS during the first 30 operating days are typically 2.5 μV. Refer to the Typical Performance Characteristics section. Parameter is

sample tested.

3

Sample tested.

4

Guaranteed by design.

5

Guaranteed but not tested.

≥ 2 kΩ ±11.5 ±12.8 V

L

≥ 1 kΩ ±12.0 V

L

= 15 0.4 0.6 MHz

VOL

= ±3 V, No load 4 8 mW

S

Rev. D | Page 5 of 16

Loading...

Loading...