CN-0248

An IQ Demodulator-Based IF-to-Baseband Receiver with IF and Baseband Variable

Rev. 0

Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices

engineers. Standard engineering practices have been employed in the design and construction of

room temperature. However, you are solely responsible for testing the circuit and determining its

suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices

or direct, indirect, special, incidental, consequential or punitive damages due to any cause

whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)

Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved.

ADRF6510

I

Q

RF

DIV BY 2

ADL5387

2xLO

0°

90°

ADF4350

ADL5336

AD9248

BITS

BITS

10285-001

VCO

CORE

Circuits from the Lab™ reference circuits are engineered and

tested for quick and easy system integration to help solve today’s

analog, mixed-signal, and RF design challenges. For more

information and/or support, visit www.analog.com/CN0248.

Gain and Programmable Baseband Filtering

EVALUATION AND DESIGN SUPPORT

Circuit Evaluation Boards

ADRF6510 Evaluation Board (ADRF6510-EVALZ)

ADL5387 Evaluation Board (ADL5387-EVALZ)

ADL5336 Evaluation Board (ADL5336-EVALZ)

AD8130 Evaluation Board (AD8130-EBZ) two required

Design and Integration Files

Schematics, Layout Files, Bill of Materials

CIRCUIT FUNCTION AND BENEFITS

This circuit is a flexible, frequency agile IF-to-baseband receiver.

Variable gain at both IF and baseband is used to adjust the signal

level. The ADRF6510 baseband ADC driver also includes a

programmable low-pass filter that eliminates out-of-channel

blockers and noise.

Circuit Note

Devices Connected/Referenced

ADRF6510

ADL5387

ADL5336

The bandwidth of this filter can be dynamically adjusted as the

bandwidth of the input signal changes. This ensures that the available

dynamic range of the ADC that this circuit drives is fully used.

The core of the circuit is an IQ demodulator. The 2×LO based

phase-splitting architecture of the ADL5387 allows for operation

over a wide frequency range. Precise quadrature balance and

low output dc offsets ensure that there is minimal degradation

of the error vector magnitude (EVM).

The interfaces between all of the components in this circuit are

fully differential. Where dc coupling is required between stages,

the bias levels of the adjacent stages are compatible with each other.

30 MHz Dual Programmable Filters and

Variable Gain Amplifiers

50 MHz to 2 GHz Quadrature

Demodulator

LF to 1 GHz VGA with 48 dB Gain Control

Range and Programmable RMS Detectors

each circuit, and their function and performance have been tested and verified in a lab environment at

be liable f

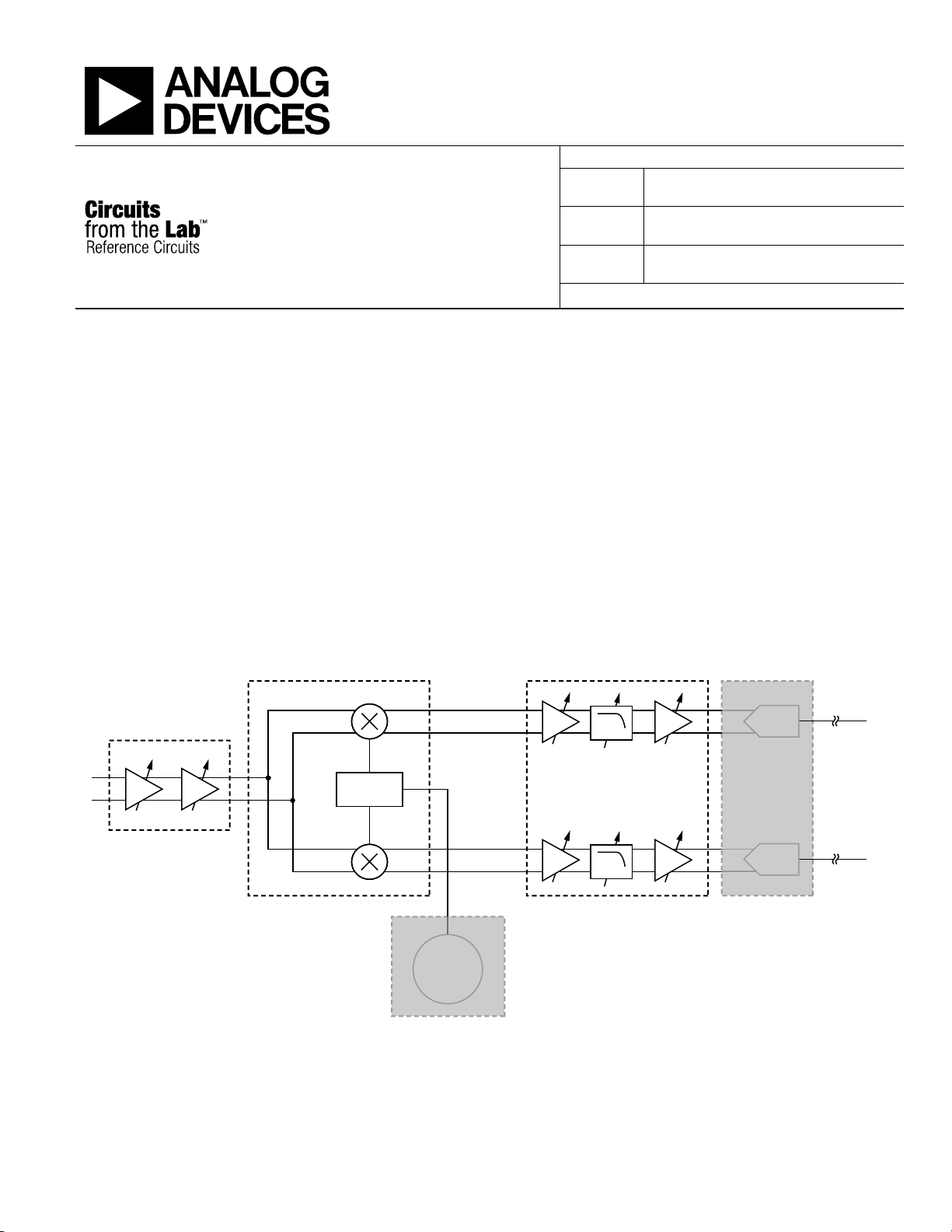

Figure 1. Direct Conversion Receiver Simplified Schematic (All Connections and Decoupling Not Shown)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

CN-0248 Circuit Note

CIRCUIT DESCRIPTION

Receiver Architecture

A direct conversion (also known as a homodyne or zero IF)

architecture for a receiver is presented in this circuit note. Direct

conversion radios perform just one frequency translation

compared to a superheterodyne receiver that can perform

several frequency translations. One frequency translation is

advantageous because it

• Reduces receiver complexity and the number of stages needed;

increasing performance and reducing power consumption

• Avoids image rejection issues and unwanted mixing

products; one LPF at baseband is all that is needed

• Has high selectivity (adjacent-channel rejection ratio [ACRR])

Figure 1 shows the basic simplified schematic of the system that

consists of cascaded IF variable gain amplifiers (VGAs) with

integrated automatic gain control (AGC) loops, followed by a

quadrature demodulator and by programmable low-pass filters

with variable baseband gain. The grayed out components shown in

Figure 1 (ADF4350 and AD9248) are included for clarity but were

not included during system-level measurements (see the Common

Var i ati ons section for more information on these devices).

Ideally, the input of the first stage and the output of the last stage

should set the dynamic range (signal-to-noise ratio) of the

system. Practically, this may not be the case. Having a cascaded

VGA before the quadrature demodulator not only adds more

gain to the system, but it also helps with overall system noise

performance if the noise figure of the VGA is less than that of

the quadrature demodulator, and if the VGA still has gain, and

it is not attenuating. The noise figures of the subsequent stages

are divided by the gain of the initial VGA. Another benefit of

having a VGA (vs. just having a fixed gain amplifier) is that an

AGC loop can be designed to level the incoming signal to the

quadrature demodulator. It is important to have this ability to

limit the signal levels applied to the quadrature demodulator

and any subsequent stages.

IF VGAs and AGC Loops

The IF VGA and AGC loop functions are accomplished with

the ADL5336. It has two cascadable VGAs, each with 24 dB of

analog dynamic range and the ability to digitally change the

maximum gain on each VGA via a SPI port.

To achieve the signal leveling AGC function, each ADL5336

VGA has a square law detector connected to its output through

a programmable attenuator. The detector compares the output

of the attenuator to an internal reference of 63 mV rms. If there

is a difference between the output of the attenuator and the

63 mV rms reference, an error current is produced and is

integrated onto a C

connecting the DTO1/DTO2 pin to the GAIN1/GAIN2 pin. For

the AGC loop to function properly, pull the MODE pin low,

causing a negative VGA gain slope.

capacitor. The AGC loop is closed by

AGC

Rev. 0 | Page 2 of 6

Each ADL5336 VGA has an allowable range of input power over

which the AGC will level to a particular setpoint. Outside that

range, the VGA output either increases or decreases dB-for-dB

with the input (assuming the VGA is not in compression or that

the signal is not in the noise floor).

IQ Demodulator

From the ADL5336, the signal is routed to the ADL5387, where

it is demodulated and the frequency is translated to a zero IF. The

ADF4350 synthesizer can provide the required 2×LO signal to the

ADL5387 (see the Common Variations section); however, a signal

generator was used instead of the ADF4350 for actual testing.

The ADL5387 uses two double-balanced mixers, one for the I

channel and one for the Q channel. The LO provided to the

mixers is generated using a divide-by-two quadrature phase

splitter. This provides the 0° and 90° signals for the I and Q

channels. There is about 4.5 dB of conversion gain provided by

the ADL5387 from the RF input to the baseband I and Q outputs.

Low-Pass Filter, Baseband VGA, and ADC Driver

The low-pass filtering, baseband gain, and ADC driver functions

are all achieved using the ADRF6510. The signal, now in its

separate I and Q paths, is applied to the ADRF6510 where the

signal is first amplified by the preamplifier, then low-pass

filtered to suppress any unwanted out-of-band signals and/or

noise, and finally amplified by the VGA.

Each channel of the ADRF6510 can be broken up into three stages:

• Preamplifier

• Programmable low-pass filter

• VGA and output driver

The preamplifier has a user-selectable gain, via the GNSW pin,

of either 6 dB or 12 dB. The low-pass filter can be programmed

for a corner frequency of 1 MHz to 30 MHz in 1 MHz steps via

the SPI port. The VGA has a 50 dB gain range with a gain slope

of 30 mV/dB. The gain of the VGA is controlled via the GAIN

pin, and it can range from −5 dB to +45 dB when the GNSW

pin is pulled low to +1 dB to +51 dB when the GNSW pin is

pulled high. The output driver has the ability to drive 1.5 V p-p

differential into a 1 kΩ load while maintaining a HD2 and a

HD3 of better than 60 dBc.

The maximum CW signal that can be applied to the low-pass

filters, while still maintaining acceptable HD levels in the

ADRF6510, is 2 V p-p. In applications where a large out-of-band

interferer is present that could overload the input of either the

ADL5387 and/or the ADRF6510, the out-of-band interferer

(and the in-band desired signal) can be attenuated by the

ADL5336 VGA. Once the out of-band interferer is rejected by

the low-pass filter of the ADRF6510, the wanted signal can then

be amplified with the X-AMP VGAs that follow the filters of the

ADRF6510.

From the ADRF6510, the IQ signal can be applied to an

appropriate analog-to-digital converter (ADC), such as the

AD9248.

Loading...

Loading...