Complete 12-Bit 5 MSPS

a

FEATURES

Monolithic 12-Bit 5 MSPS A/D Converter

Low Noise: 0.17 LSB RMS Referred to Input

No Missing Codes Guaranteed

Differential Nonlinearity Error: 0.5 LSB

Signal-to-Noise and Distortion Ratio: 68 dB

Spurious-Free Dynamic Range: 73 dB

Power Dissipation: 1.03 W

Complete: On-Chip Track-and-Hold Amplifier and

Voltage Reference

Pin Compatible with the AD872

Twos Complement Binary Output Data

Out of Range Indicator

28-Lead Side Brazed Ceramic DIP or 44-Terminal

Surface Mount Package

PRODUCT DESCRIPTION

The AD871 is a monolithic 12-bit, 5 MSPS analog-to-digital

converter with an on-chip, high performance track-and-hold

amplifier and voltage reference. The AD871 uses a multistage

differential pipelined architecture with error correction logic to

provide 12-bit accuracy at 5 MSPS data rates and guarantees no

missing codes over the full operating temperature range. The

AD871 is a redesigned variation of the AD872 12-bit, 10 MSPS

ADC, optimized for lower noise in applications requiring sampling rates of 5 MSPS or less. The AD871 is pin compatible

with the AD872, allowing the parts to be used interchangeably

as system requirements change.

The low-noise input track-and-hold (T/H) of the AD871 is ideally suited for high-end imaging applications. In addition, the

T/H’s high input impedance and fast settling characteristics

allow the AD871 to easily interface with multiplexed systems

that switch multiple signals through a single A/D converter. The

dynamic performance of the input T/H also renders the AD871

suitable for sampling single channel inputs at frequencies up to

and beyond the Nyquist rate. The AD871 provides both reference output and reference input pins, allowing the onboard reference to serve as a system reference. An external reference can

also be chosen to suit the dc accuracy and temperature drift

requirements of the application. A single clock input is used to

control all internal conversion cycles. The digital output data is

presented in twos complement binary output format. An out-ofrange signal indicates an overflow condition, and can be used

with the most significant bit to determine low or high overflow.

Monolithic A/D Converter

AD871

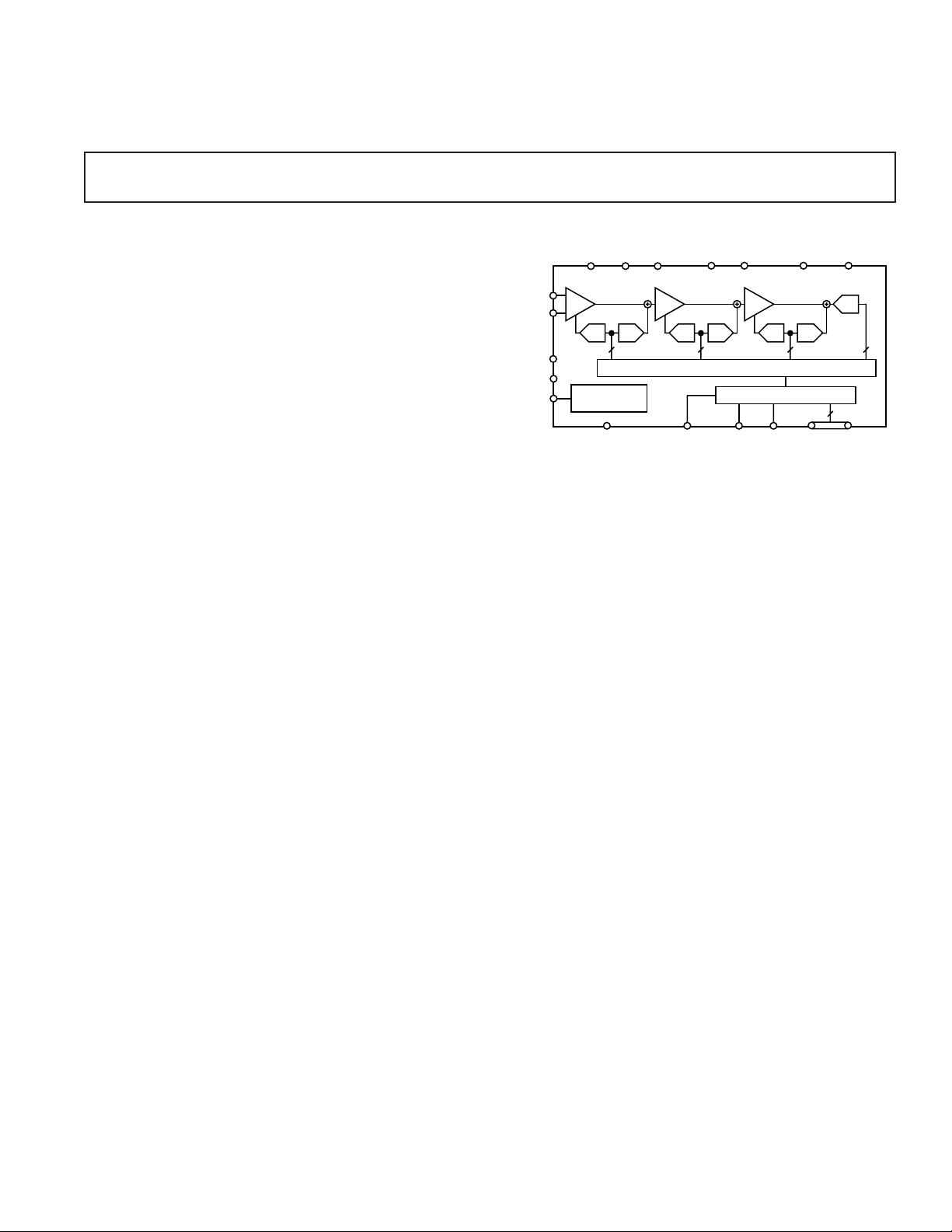

FUNCTIONAL BLOCK DIAGRAM

DV

SS

T/H

A/D4D/A

CORRECTION LOGIC

*

OUTPUT

ENABLE

DGND

DD

T/H

OUTPUT BUFFERS

OTR *MSB

*

DRV

AD871

A/D3D/A

MSB–BIT 12

(LSB)

*

DRGND

DD

A/D

4

12

V

INA

V

INB

CLOCK

REF IN

REF OUT

AV

DD

T/H

A/D4D/A

+2.5V

REFERENCE

REF OUT

*ONLY AVAILABLE ON 44-TERMINAL SURFACE MOUNT PACKAGE

AGND

AV

The AD871 is fabricated on Analog Devices’ ABCMOS-1 process, which uses high speed bipolar and CMOS transistors on a

single chip. High speed, precision analog circuits are now combined with high density logic circuits.

The AD871 is packaged in a 28-lead ceramic DIP and a

44-terminal leadless ceramic surface mount package and is

specified for operation from 0°C to +70°C and –55°C to

+125°C.

PRODUCT HIGHLIGHTS

The AD871 offers a complete single-chip sampling 12-bit,

5 MSPS analog-to-digital conversion function in a 28-lead DIP

or 44-terminal leadless ceramic surface mount package (LCC).

Low Noise—The AD871 features 0.17 LSB referred-to-input

noise, producing essentially a “1 code wide” histogram for a

code-centered dc input.

Low Power—The AD871 at 1.03 W consumes a fraction of the

power of presently available hybrids.

On-Chip Track-and-Hold (T/H)—The low noise, high impedance T/H input eliminates the need for external buffers and can

be configured for single ended or differential inputs.

Ease of Use—The AD871 is complete with T/H and voltage reference and is pin-compatible with the AD872 (12-bit, 10 MSPS

monolithic ADC).

Out of Range (OTR)—The OTR output bit indicates when the

input signal is beyond the AD871’s input range.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1997

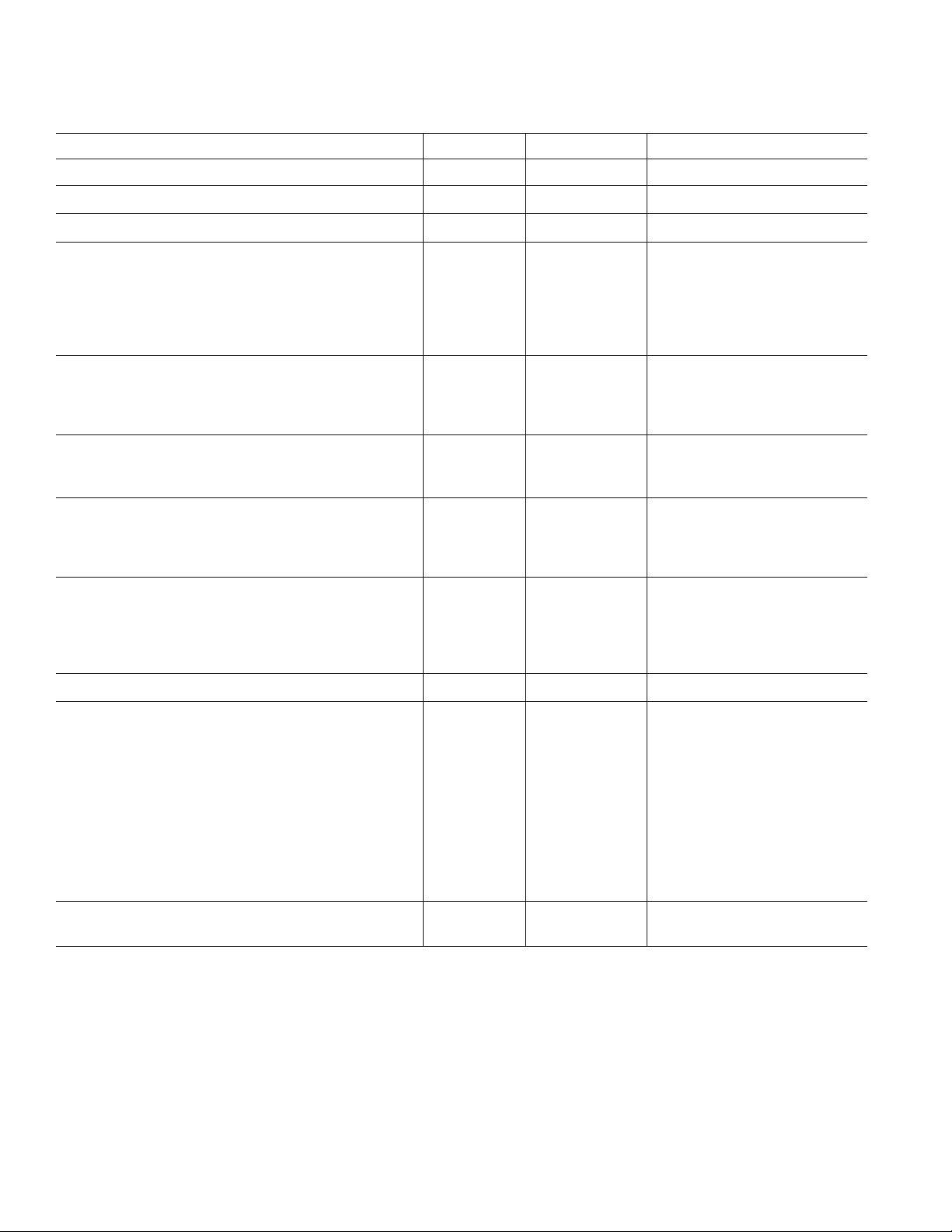

AD871–SPECIFICATIONS

AD871

(T

to T

with AVDD = +5 V, DVDD = +5 V, DRVDD = +5 V, AVSS = –5 V, f

MAX

DC SPECIFICATIONS

MIN

noted)

Parameter J Grade

1

S Grade

l

= 5 MHz, unless otherwise

SAMPLE

Units

RESOLUTION 12 12 Bits min

MAX CONVERSION RATE 5 5 MHz min

INPUT REFERRED NOISE 0.17 0.17 LSB rms typ

ACCURACY

Integral Nonlinearity (INL) ± 1.5 ±1.5 LSB typ

Differential Nonlinearity (DNL) ±0.5 ± 0.5 LSB typ

No Missing Codes 12 12 Bits Guaranteed

Zero Error (@ +25°C)

Gain Error (@ +25°C)

TEMPERATURE DRIFT

Zero Error ±0.15 ±0.3 % FSR max

Gain Error

Gain Error

3, 4

3, 5

POWER SUPPLY REJECTION

AVDD, DV

AV

(–5 V ± 0.25 V) ±0.125 ±0.125 % FSR max

SS

(+5 V ± 0.25 V) ±0.125 ±0.125 % FSR max

DD

2

2

3

±0.75 ±0.75 % FSR max

±1.25 ±1.25 % FSR max

±0.80 ±1.75 % FSR max

±0.25 ±0.50 % FSR max

6

ANALOG INPUT

Input Range ±1 ±1 Volts max

Input Resistance 50 50 kΩ typ

Input Capacitance 10 10 pF typ

INTERNAL VOLTAGE REFERENCE

Output Voltage 2.5 2.5 Volts typ

Output Voltage Tolerance ±20 ±40 mV max

Output Current (Available for External Loads) 2.0 2.0 mA typ

(External load should not change during conversion.)

REFERENCE INPUT RESISTANCE 5 5 kΩ typ

POWER SUPPLIES

Supply Voltages

AV

DD

AV

SS

DV

DD

DRV

DD

7

+5 +5 V (±5% AV

–5 –5 V (±5% AV

+5 +5 V (±5% DV

+5 +5 V (±5% DRV

Supply Current

IAV

DD

IAV

SS

IDV

DD

IDRV

DD

7

87 88 mA max (82 mA typ)

147 150 mA max (115 mA typ)

20 21 mA max (7 mA typ)

2 2 mA max

POWER CONSUMPTION 1.03 1.03 W typ

1.25 1.3 W max

NOTES

1

Temperature ranges are as follows: J Grade: 0°C to +70°C, S Grade: –55°C to +125°C.

2

Adjustable to zero with external potentiometers (see Zero and Gain Error Calibration section).

3

+25°C to T

4

Includes internal voltage reference error.

5

Excludes internal reference drift.

6

Change in Gain Error as a function of the dc supply voltage (V

7

LCC package only.

Specifications subject to change without notice.

and +25°C to T

MIN

MAX

.

to V

NOMINAL

MIN

, V

NOMINAL

to V

MAX

).

Operating)

DD

Operating)

SS

Operating)

DD

Operating)

DD

–2–

REV. A

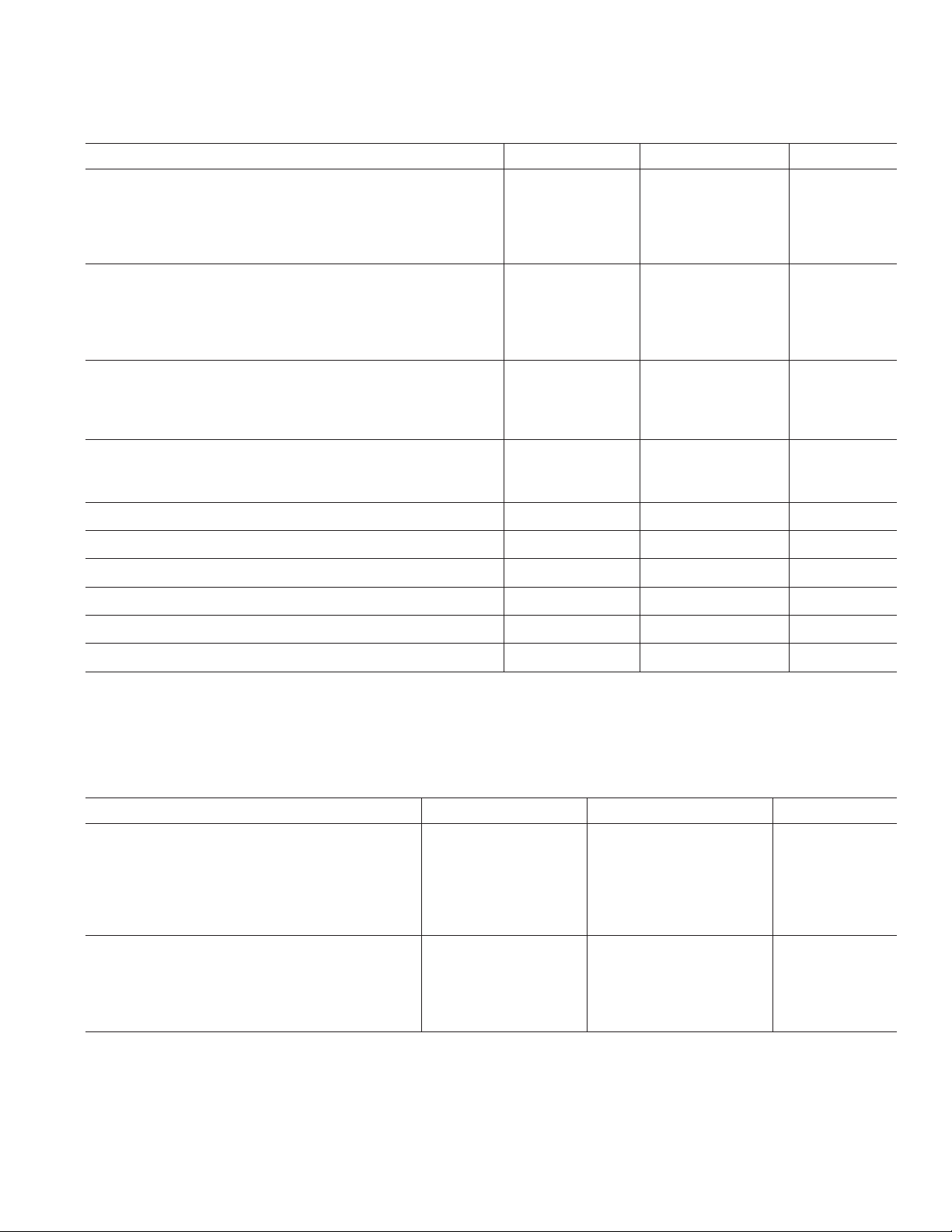

AD871

(T

to T

with AVDD = +5 V, DVDD = +5 V, DRVDD = +5 V, AVSS = –5 V, f

MAX

1

AC SPECIFICATIONS

MIN

noted)

J Grade S Grade Units

SIGNAL-TO-NOISE AND DISTORTION RATIO (S/N+D)

f

= 750 kHz 68 68 dB typ

INPUT

f

= 1 MHz 66 66 dB typ

INPUT

63 62 dB min

f

= 2.49 MHz 60 60 dB typ

INPUT

TOTAL HARMONIC DISTORTION (THD)

f

= 750 kHz –72 –72 dB typ

INPUT

f

= 1 MHz –69 –69 dB typ

INPUT

–64 –63 dB max

f

= 2.49 MHz –62 –62 dB typ

INPUT

SPURIOUS FREE DYNAMIC RANGE (SFDR)

f

= 750 kHz 73 73 dB typ

INPUT

f

= 1 MHz 70 70 dB typ

INPUT

f

= 2.49 MHz 62 62 dB typ

INPUT

INTERMODULATION DISTORTION (IMD)

2

Second Order Products –80 –80 dB typ

Third Order Products –73 –73 dB typ

FULL POWER BANDWIDTH 15 15 MHz typ

= 5 MSPS, unless otherwise

SAMPLE

SMALL SIGNAL BANDWIDTH 15 15 MHz typ

APERTURE DELAY 6 6 ns typ

APERTURE JITTER 16 16 ps rms typ

ACQUISITION TO FULL-SCALE STEP 80 80 ns typ

OVERVOLTAGE RECOVERY TIME 80 80 ns typ

NOTES

1

fIN amplitude = –0.5 dB full scale unless otherwise indicated. All measurements referred to a 0 dB (1 V pk) input signal unless otherwise indicated.

2

fa = 1.0 MHz, fb = 0.95 MHz with f

Specifications subject to change without notice.

DIGITAL SPECIFICATIONS

SAMPLE

= 5 MHz.

(T

MIN

to T

with AVDD = +5 V, DVDD = +5 V, AVSS = –5 V unless otherwise noted)

MAX

Parameter Symbol J, S Grades Units

LOGIC INPUTS

High Level Input Voltage V

Low Level Input Voltage V

High Level Input Current (V

Low Level Input Current (V

= DVDD)I

IN

= 0 V) I

IN

Input Capacitance C

IH

IL

IH

IL

IN

+2.0 V min

+0.8 V max

±115 µA max

±115 µA max

5 pF typ

LOGIC OUTPUTS

High Level Output Voltage (I

Low Level Output Voltage (I

Output Capacitance C

= 0.5 mA) V

OH

= 1.6 mA) V

OL

OH

OL

OUT

+2.4 V min

+0.4 V max

5 pF typ

Leakage (Three-State, LCC Only) IZ ±10 µA max

Specifications subject to change without notice.

REV. A

–3–

AD871

WARNING!

ESD SENSITIVE DEVICE

(T

to T

MIN

SWITCHING SPECIFICATIONS

VIH = 2.0 V, VOL = 0.4 V and VOH = 2.4 V)

Parameter Symbol J, S Grades Units

Clock Period

l

CLOCK Pulsewidth High t

CLOCK Pulsewidth Low t

Clock Duty Cycle

2

Output Delay t

Pipeline Delay (Latency) 3 Clock Cycles

Data Access Time (LCC Package Only)

Output Float Delay (LCC Package Only)

NOTES

1

Conversion rate is operational down to 10 kHz without degradation in specified performance.

2

For clock periods of 200 ns or greater, see Clock Input section.

3

See section on Three-State Outputs for timing diagrams and application information.

Specifications subject to change without notice.

VIN

CLOCK

BIT 2–12

MSB, OTR

N

3

t

tCHt

3

N+1

C

N+1N

CL

with AVDD = +5 V, DVDD = +5 V, DRVDD = +5 V, AVSS = –5 V; VIL = 0.8 V,

MAX

t

C

CH

CL

200 ns min

95 ns min

95 ns min

40 % min (50% typ)

60 % max

OD

t

DD

t

HL

DATA

N

10 ns min (20 ns typ)

50 ns typ (100 pF Load)

50 ns typ (10 pF Load)

t

OD

DATA

N+1

Figure 1. Timing Diagram

ABSOLUTE MAXIMUM RATINGS

1

Parameter With Respect to Min Max Units

AV

DD

AV

SS

DV

, DRV

DD

DD

2

DRV

DRGND

DD

2

AGND –0.5 +6.5 Volts

AGND –6.5 +0.5 Volts

DGND, DRGND –0.5 +6.5 Volts

DV

DD

–6.5 +6.5 Volts

DGND –0.3 +0.3 Volts

AGND DGND –1.0 +1.0 Volts

AV

DD

Clock Input, OEN DGND –0.5 DV

Digital Outputs DGND –0.5 DV

V

, V

INA

REF IN AGND –6.5 +6.5 Volts

INB

REF IN AGND AV

DV

DD

–6.5 +6.5 Volts

+ 0.5 Volts

DD

+ 0.3 Volts

DD

SS

AV

DD

Volts

Junction Temperature +150 °C

Storage Temperature –65 +150 °C

Lead Temperature (10 sec) +300 °C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of

the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum

ratings for extended periods may affect device reliability.

2

LCC Package Only.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD871 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–4–

REV. A

PIN FUNCTION DESCRIPTIONS

DIP LCC

Symbol Pin No. Pin No. Type Name and Function

AD871

V

V

AV

AV

INA

INB

SS

DD

1 1 AI (+) Analog Input Signal on the differential input amplifier.

2 2 AI (–) Analog Input Signal on the differential input amplifier.

3, 25 5, 40 P –5 V Analog Supply.

4 6, 38 P +5 V Analog Supply.

AGND 5, 24 9, 36 P Analog Ground.

DGND 6, 23 10 P Digital Ground.

DV

DD

7, 22 33 P +5 V Digital Supply.

BIT 12 (LSB) 8 16 DO Least Significant Bit.

BIT 2–BIT 11 18–9 26–17 DO Data Bits 2 through 11.

MSB 19 29 DO Inverted Most Significant Bit. Provides twos complement output

data format.

OTR 20 30 DO Out of Range is Active HIGH on the leading edge of code 0 or

the trailing edge of code 4096. See Output Data Format Table III.

CLK 21 31 DI Clock Input. The AD871 will initiate a conversion on the rising

edge of the clock input. See the Timing Diagram for details.

REF OUT 26 41 AO +2.5 V Reference Output. Tie to REF IN for normal operation.

REF GND 27 42 AI Reference Ground.

REF IN 28 43 AI Reference Input. +2.5 V input gives ±1 V full-scale range.

BIT 1 (MSB) N/A 27 DO Most Significant Bit.

DRV

DD

N/A 12, 32 P +5 V Digital Supply for the output drivers.

DRGND N/A 11, 34 P Digital Ground for the output drivers.

(See section on Power Supply Decoupling for details on

DRV

and DRGND.)

DD

OEN N/A 13 DI Output Enable. See the Three State Output Timing Diagram for details.

NC N/A 3, 4, 7, 8, 14, 15, No Connect.

28, 35, 37, 39, 44

TYPE: AI = Analog Input; AO = Analog Output; DI = Digital Input; DO = Digital Output; P = Power; N/A = Not Available on 28-lead DIP, available only on

44-terminal surface mount package.

PIN CONFIGURATIONS

28-Lead Side Brazed Ceramic DIP

V

INA

V

INB

AV

AV

AGND

DGND

DV

BIT 12 (LSB)

BIT 11

BIT 10

BIT 9

BIT 8

BIT 7

BIT 6

SS

DD

DD

AD871

TOP VIEW

(Not to Scale)

REF IN

REF GND

REF OUT

AV

SS

AGND

DGND

DV

DD

CLK

OTR

MSB

BIT 2

BIT 3

BIT 4

BIT 5

AGND

DGND

DRGND

DRV

OEN

BIT 12 (LSB)

BIT 11

44-Terminal LCC

(Not to Scale)

BIT 9

BIT 8

INBVINA

AD871

TOP VIEW

BIT 7

BIT 6

AVDDAVSSNCNCV

6 5 4 3 2 1 44 43 42 41 40

7

NC

8

NC

9

10

11

12

DD

13

NC

14

NC

15

16

17

18 19 20 21 22 23 24 25 26 27 28

BIT 10

NC = NO CONNECT

BIT 5

NC

BIT 4

REF IN

REF GND

PIN 1

IDENTIFIER

BIT 3

BIT 2

SS

REF OUT

AV

39

NC

38

AV

37

NC

36

AGND

35

NC

34

DRGND

33

DV

DRV

32

31

CLK

OTR

30

29

MSB

NC

BIT 1 (MSB)

DD

DD

DD

REV. A

–5–

Loading...

Loading...