ANALOG DEVICES AD8465 Service Manual

Rail-to-Rail, Very Fast, 2.5 V to 5.5 V,

V

V

Data Sheet

FEATURES

Fully specified rail to rail at V

Input common-mode voltage from −0.2 V to V

Low glitch LVDS-compatible output stage

Propagation delay: 1.6 ns

Power dissipation: 37 mW at 2.5 V

Shutdown pin

Single-pin control for programmable hysteresis and latch

Power supply rejection > 60 dB

−40°C to +125°C operation

APPLICATIONS

High speed instrumentation

Clock and data signal restoration

Logic level shifting or translation

Pulse spectroscopy

High speed line receivers

Threshold detection

Peak and zero-crossing detectors

High speed trigger circuitry

Pulse-width modulators

Current-/voltage-controlled oscillators

Automatic test equipment (ATE)

Automotive

= 2.5 V to 5.5 V

CCI

+ 0.2 V

CCI

Single-Supply LVDS Comparator

AD8465

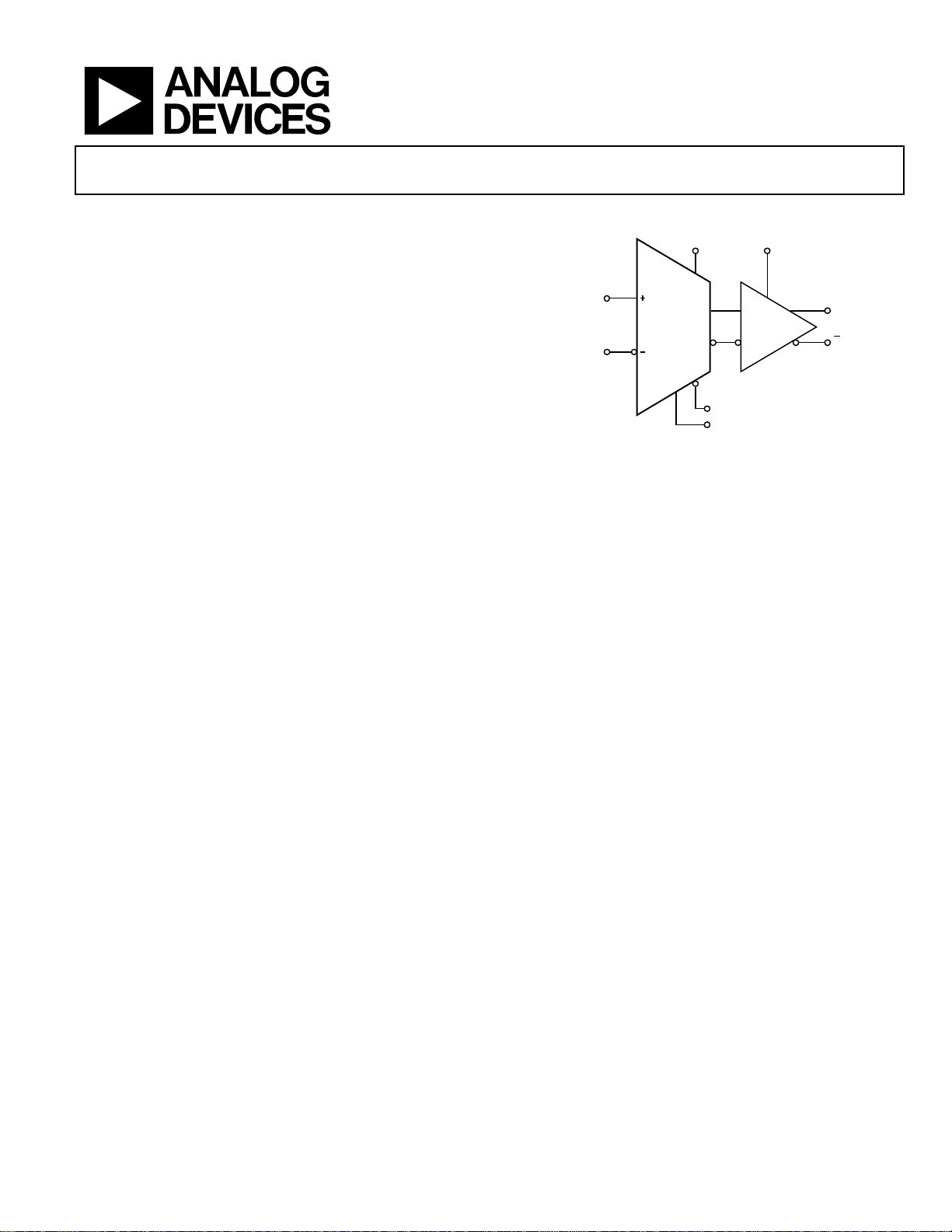

FUNCTIONAL BLOCK DIAGRAM

NONINVERTI NG

P

INVERTING

V

N

INPUT

INPUT

AD8465

V

CCI

Figure 1.

CCO

LVDS

LE/HYS INPUT

INPUT

S

DN

Q OUTPUT

Q OUTPUT

07958-001

GENERAL DESCRIPTION

The AD8465 is a very fast comparator fabricated on the Analog

Devices, Inc., proprietary XFCB2 process. This comparator is

exceptionally versatile and easy to use. Features include an

input range from V

compatible output drivers, and TTL/CMOS latch inputs with

adjustable hysteresis and/or shutdown inputs.

The device offers 1.6 ns propagation delay with 1 ps rms

random jitter (RJ). Overdrive and slew rate dispersion are

typically less than 50 ps.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

− 0.5 V to V

EE

+ 0.2 V, low noise, LVDS-

CCI

A flexible power supply scheme allows the devices to operate

with a single 2.5 V positive supply and a −0.5 V to +2.7 V input

signal range up to a 5.5 V positive supply with a −0.5 V to +5.7 V

input signal range. Split input/output supplies, with no sequencing

restrictions, support a wide input signal range with greatly

reduced power consumption.

The LVDS-compatible output stage is designed to drive any

standard LVDS input. The comparator input stage offers robust

protection against large input overdrive, and the outputs do not

phase reverse when the valid input signal range is exceeded. High

speed latch and programmable hysteresis features are also provided

in a unique single-pin control option.

The AD8465 is available in a 12-lead LFCSP.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009–2011 Analog Devices, Inc. All rights reserved.

AD8465 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Electrical Characteristics ............................................................. 3

Timing Information......................................................................... 5

Absolute Maximum Ratings............................................................ 6

Thermal Resistance ...................................................................... 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Typical Performance Characteristics ............................................. 8

REVISION HISTORY

11/11—Rev. 0 to Rev. A

Changed V

Table 1 ................................................................................................ 3

4/09—Revision 0: Initial Version

= 0.4 V to VIL = 0.8 V in Conditions of IIL,

IL

Application Information................................................................ 10

Power/Ground Layout and Bypassing..................................... 10

LVDS-Compatible Output Stage.............................................. 10

Using/Disabling the Latch Feature........................................... 10

Optimizing Performance........................................................... 10

Comparator Propagation Delay Dispersion ........................... 11

Comparator Hysteresis .............................................................. 11

Crossover Bias Points................................................................. 12

Minimum Input Slew Rate Requirement ................................ 12

Typical Application Circuits ......................................................... 13

Outline Dimensions....................................................................... 14

Ordering Guide .......................................................................... 14

Rev. A | Page 2 of 16

Data Sheet AD8465

SPECIFICATIONS

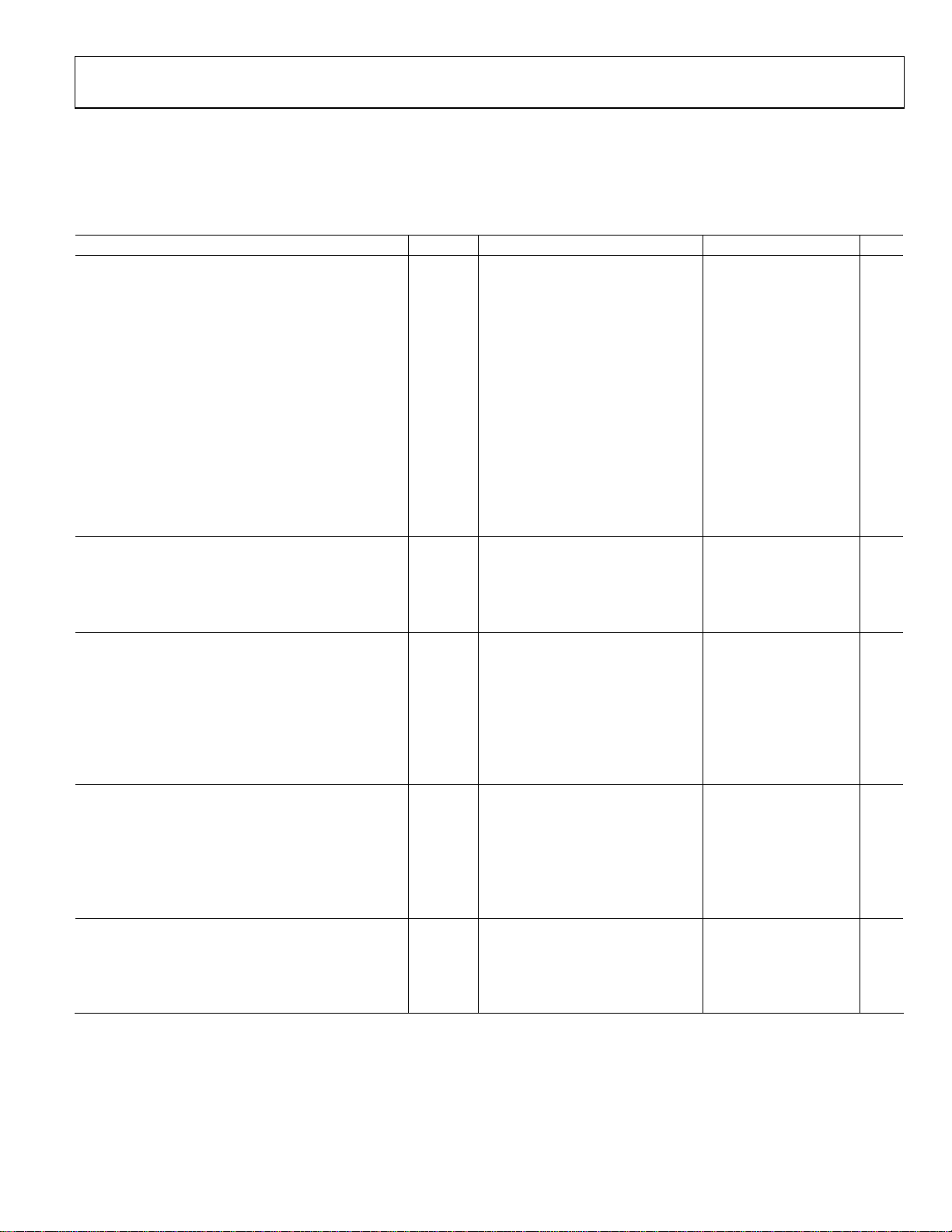

ELECTRICAL CHARACTERISTICS

V

= V

CCI

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

DC INPUT CHARACTERISTICS

Voltage Range VP, VN V

Common-Mode Range V

Differential Voltage V

Offset Voltage VOS −5.0 +5.0 mV

Bias Current IP, IN −5.0 ±2 +5.0 μA

Offset Current −2.0 +2.0 μA

Capacitance CP, CN 1 pF

Resistance, Differential Mode −0.1 V to V

Resistance, Common Mode −0.5 V to V

Active Gain AV 62 dB

Common-Mode Rejection Ratio CMRR

V

Hysteresis R

LATCH ENABLE PIN CHARACTERISTICS

VIH Hysteresis is shut off 2.0 V

VIL Latch mode guaranteed −0.2 +0.4 +0.8 V

IIH V

IIL V

HYSTERESIS MODE AND TIMING

Hysteresis Mode Bias Voltage Current sink −1 μA 1.145 1.25 1.40 V

Minimum Resistor Value Hysteresis = 120 mV 30 110 kΩ

Hysteresis Current Hysteresis = 120 mV −25 −8 μA

Latch Setup Time tS V

Latch Hold Time tH V

Latch-to-Output Delay t

Latch Minimum Pulse Width tPL V

SHUTDOWN PIN CHARACTERISTICS

VIH Comparator is operating 2.0 V

VIL Shutdown guaranteed −0.2 +0.4 +0.6 V

IIH V

IIL V

Sleep Time tSD 10% output swing 1.4 ns

Wake-Up Time tH V

DC OUTPUT CHARACTERISTICS V

Differential Output Voltage Level VOD R

ΔVOD R

Common-Mode Voltage V

Peak-to-Peak Common-Mode Output V

= 2.5 V, TA = −40°C to +125°C, typical at TA = 25 °C, unless otherwise noted.

CCO

= 2.5 V to 5.5 V −0.5 V

CCI

= 2.5 V to 5.5 V −0.2 V

CCI

= 2.5 V to 5.5 V V

CCI

200 750 7500 kΩ

CCI

+ 0.5 V 100 370 4000 kΩ

CCI

= 2.5 V, V

V

CCI

V

= −0.2 V to +2.7 V

CM

= 2.5 V, V

CCI

= ∞ <0.1 mV

HYS

= V

IH

= 0.8 V −0.1 +0.1 mA

IL

= 50 mV −2 ns

OD

= 50 mV 2.7 ns

OD

, t

VOD = 50 mV 20 ns

PLOH

PLOL

= 50 mV 24 ns

OD

= V

IH

= 0 V −0.1 mA

IL

= 50 mV, output valid 25 ns

OD

= 2.5 V to 5.0 V

CCO

LOAD

LOAD

R

OCI

OC (p-p)

LOAD

R

LOAD

CCO

CCO

+ 0.2 V −6 +6 μA

CCO

−6 +6 μA

CCO

= 100 Ω 245 350 445 mV

= 100 Ω 50 mV

= 100 Ω 1.125 1.375 V

= 100 Ω 50 mV

+ 0.2 V

CCI

+ 0.2 V

CCI

V

CCI

= 2.5 V,

50 dB

= 5.0 V 50 dB

V

CCO

V

CCO

Rev. A | Page 3 of 16

AD8465 Data Sheet

Parameter Symbol Conditions Min Typ Max Unit

AC PERFORMANCE1

Rise Time/Fall Time tR, tF 10% to 90% 600 ps

Propagation Delay tPD

V

Propagation Delay Skew—Rising to Falling Transition t

Propagation Delay Skew—Q to Q

V

PINSKEW

V

= V

V

CCI

= 50 mV

V

OD

= V

CCI

= V

CCI

= V

CCI

= 2.5 V to 5.0 V,

CCO

= 2.5 V, VOD = 10 mV 3.0 ns

CCO

= 2.5 V to 5.0 V 70 ps

CCO

= 2.5 V to 5.0 V 70 ps

CCO

Overdrive Dispersion 10 mV < VOD < 125 mV 1.6 ns

Common-Mode Dispersion VCM = −0.2 V to V

+ 0.2 V 250 ps

CCI

Input Bandwidth 500 MHz

Minimum Pulse Width PW

MIN

= V

V

CCI

= 90% of PWIN

PW

OUT

= 2.5 V to 5.0 V,

CCO

POWER SUPPLY

Input Supply Voltage Range V

Output Supply Voltage Range V

Positive Supply Differential V

V

Input Section Supply Current I

Output Section Supply Current I

Power Dissipation PD V

V

Power Supply Rejection Ratio PSRR V

Shutdown Mode I

Shutdown Mode I

1

VIN = 100 mV square input at 50 MHz, VOD = 50 mV, VCM = 1.25 V, V

V

CCI

V

CCO

2.5 5.5 V

CCI

2.5 5.0 V

CCO

− V

Operating −3 +3 V

CCI

CCO

− V

Nonoperating −5.0 +5.0 V

CCI

CCO

V

VCCI

V

VCCO

= V

= 2.5 V, unless otherwise noted.

CCI

CCO

= 2.5 V to 5.5 V 1.6 3.0 mA

CCI

= 2.5 V to 5.0 V 15 23 mA

CCO

= V

CCI

CCI

CCI

CCI

CCI

= 2.5 V 37 55 mW

CCO

= V

= 5.0 V 95 120 mW

CCO

= V

= 2.5 V to 5.0 V −50 −60 dB

CCO

= V

= 2.5 V to 5.0 V 0.92 1.1 mA

CCO

= V

= 2.5 V to 5.0 V −30 +30 μA

CCO

1.6 ns

1.3 ns

Rev. A | Page 4 of 16

Data Sheet AD8465

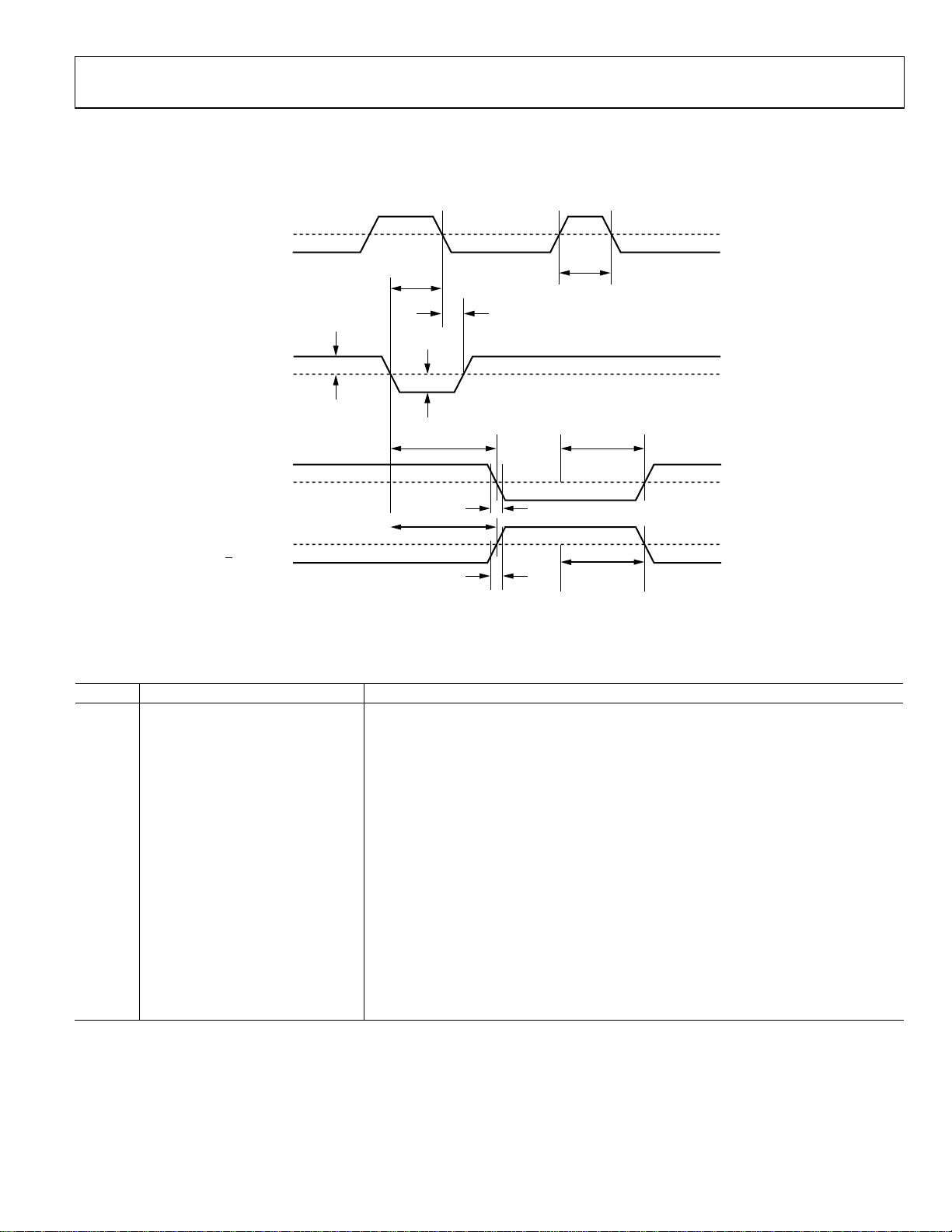

TIMING INFORMATION

Figure 2 illustrates the AD8465 latch timing relationships. Tabl e 2 provides definitions of the terms shown in Figure 2.

1.1V

LATCH ENABLE

DIFFERENTIAL

INPUT VOLTAGE

Q OUTPUT

Q OUTPUT

t

S

t

H

V

IN

V

OD

t

PDL

t

PDH

t

t

R

t

PL

± V

V

N

OS

t

PLOH

50%

F

50%

t

PLOL

7958-002

Figure 2. System Timing Diagram

Table 2. Timing Descriptions

Symbol Timing Description

t

Input-to-Output High Delay

PDH

Propagation delay measured from the time the input signal crosses the reference (± the

input offset voltage) to the 50% point of an output low-to-high transition.

t

Input-to-Output Low Delay

PDL

Propagation delay measured from the time the input signal crosses the reference (± the

input offset voltage) to the 50% point of an output high-to-low transition.

t

Latch Enable-to-Output High Delay

PLOH

Propagation delay measured from the 50% point of the latch enable signal low-to-high

transition to the 50% point of an output low-to-high transition.

t

Latch Enable-to-Output Low Delay

PLOL

Propagation delay measured from the 50% point of the latch enable signal high-to-low

transition to the 50% point of an output high-to-low transition.

tH Minimum Hold Time

Minimum time after the negative transition of the latch enable signal that the input

signal must remain unchanged to be acquired and held at the outputs.

tPL Minimum Latch Enable Pulse Width Minimum time that the latch enable signal must be high to acquire an input signal change.

tS Minimum Setup Time

Minimum time before the negative transition of the latch enable signal occurs that an

input signal change must be present to be acquired and held at the outputs.

tR Output Rise Time

Amount of time required to transition from a low-to-high output as measured at the

20% and 80% points.

tF Output Fall Time

Amount of time required to transition from a high-to-low output as measured at the

20% and 80% points.

VOD Voltage Overdrive Difference between the input voltages, VP and VN.

Rev. A | Page 5 of 16

Loading...

Loading...