Dual Output

GSM PA Controller

AD8316

FEATURES

Complete RF Detector/Controller Function

Selectable Dual Outputs

49 dB Range at 0.9 GHz (–47.6 dBm to +1.5 dBm re 50 )

Accurate Scaling from 0.1 GHz to 2.5 GHz

Temperature-Stable Linear-in-dB Response

Log Slope of 22 mV/dB

True Integration Function in Control Loop

Low Power: 23 mW at 2.7 V

Power-Down to 11 W

APPLICATIONS

Single-Band, Dual-Band, and Triband Mobile Handsets

(GSM, DCS, PCS, EDGE)

Wireless Terminal Devices

Transmitter Power Control

GENERAL DESCRIPTION

The AD8316 is a complete, low cost subsystem for the precise

control of dual RF power amplifiers (PAs) operating in the

frequency range 0.1 GHz to 2.5 GHz and over a typical dynamic

range of 50 dB. The device is a dual-output version of the AD8315

and intended for use in dual-band or triband cellular handsets

and other battery-operated wireless devices where a separate

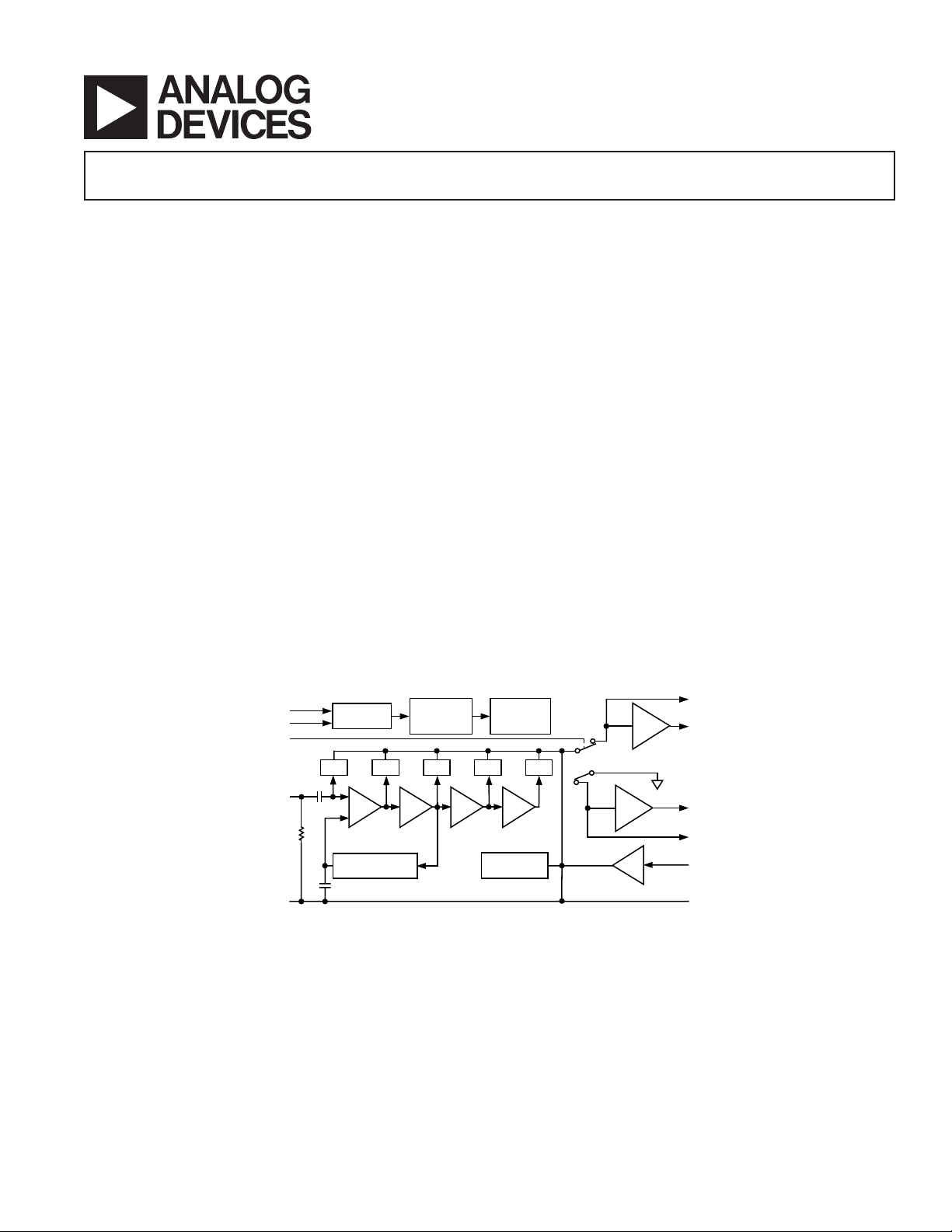

FUNCTIONAL BLOCK DIAGRAM

power control signal is required for each band. The logarithmic

amplifier technique provides a much wider measurement range

and better accuracy than is possible using controllers based on

diode detectors. In particular, multiband and multimode cellular designs can benefit from the temperature-stable (–30°C to

+85°C) operation over all cellular telephony frequencies.

Its high sensitivity allows control at low input signal levels, thus

reducing the amount of power that needs to be coupled to the

detector. The selected output, OUT1 or OUT2, has the voltage

range and current drive to directly connect to the gain control

pin of most handset power amplifiers; the deselected output is

pulled low to ensure that the inactive PA remains off. Each

output has a dedicated integrating filter capacitor that allows

separate control loop settings for each PA. OUT1 and OUT2 can

swing from 125 mV above ground to within 100 mV below the

supply voltage. Load currents of up to 12 mA can be supported.

The setpoint control input applied to pin VSET has an operating

range of 0.25 V to 1.4 V. The input resistance of the setpoint

interface is over 100 MΩ, and the bias current is typically 0.5 µA.

The AD8316 is available in 10-lead MSOP and 16-lead LFCSP

packages and consumes 8.5 mA from a 2.7 V to 5.5 V supply.

When it is powered down, the sleep current is 4 µA.

VPOS

ENBL

BSEL

RFIN

COMM

LOW NOISE

GAIN BIAS

DET DET DET DET

10dB

OFFSET

COMPENSATION

LOW NOISE

BAND GAP

REFERENCE

DET

10dB 10dB 10dB

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

OUTPUT

ENABLE

DELAY

INTERCEPT

POSITIONING

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

HI-Z

HI-Z

1.35

1.35

V–I

FLT1

OUT1

OUT2

FLT2

VSET

AD8316–SPECIFICATIONS

(V

= 2.7 V, TA = 25C, 52.3 on RFIN, unless otherwise noted.)

POS

Parameter Conditions Min Typ Max Unit

OVERALL FUNCTION

Frequency Range

1

To Meet All Specifications 0.1 2.5 GHz

Input Voltage Range ±1 dB Log Conformance, 0.1 GHz –58.6 –10 dBV

Equivalent dBm Range –45.6 +3 dBm

Logarithmic Slope

Logarithmic Intercept

2, 3

2, 3

0.1 GHz 20.5 22.1 24.5 mV/dB

0.1 GHz –68 –74 –78 dBV

Equivalent dBm Level –55 –61 –65 dBm

RF INPUT INTERFACE Pin RFIN

Input Resistance

Input Capacitance

4

4

0.1 GHz 2.9 kΩ

0.1 GHz 1.0 pF

OUTPUTS Pins OUT1 and OUT2

Minimum Output Voltage VSET ≤ 200 mV, ENBL High, RF Input ≤ –60 dBm 0.1 0.15 0.25 V

ENBL Low 0.025 V

Maximum Output Voltage R

General Limit 2.7 V ≤ V

> 800 Ω 2.45 2.6 V

L

≤ 5.5 V V

POS

– 0.1 V

POS

Output Current Drive Source 12 mA

Output Buffer Noise 25 nV/√Hz

Output Noise RF Input = 2 GHz, 0 dBm, 100 nV/√Hz

= 220 pF, f

C

FLT

Small Signal Bandwidth 0.2 V to 2.6 V Swing 30 MHz

Slew Rate 10%–90%, 250 mV Step (V

= 400 kHz

NOISE

), Open Loop

SET

5

20 V/µs

Full-Scale Response Time FLTR = Open; Refer to TPC 28 50 ns

SETPOINT INTERFACE Pin VSET

Nominal Input Range Corresponding to Central 50 dB 0.25 1.5 V

Logarithmic Scale Factor 43.5 dB/V

Input Resistance 100 kΩ

Slew Rate 16 V/µs

ENABLE INTERFACE Pin ENBL

Logic Level to Enable Power 1.8 V

POS

V

Input Current when Enable High 20 µA

Logic Level to Disable Power 0.8 V

Enable Time Time from ENBL High to V

Final Value, C

= 68 pF; Refer to TPC 20

FLT

Disable Time Time from ENBL Low to V

Final Value, C

= 68 pF; Refer to TPC 20

FLT

Power-On/Enable Time Time from VPOS/ENBL Low to V

1% of Final Value, C

FLT

Power-Off/Disable Time Time from VPOS/ENBL High to V

1% of Final Value, C

FLT

within 1% of 7 µs

APC

within 1% of 3 µs

APC

within 3 µs

APC

= 68 pF; Refer to TPC 25

within 4 µs

APC

= 68 pF; Refer to TPC 25

BAND SELECT INTERFACE Pin BSEL

Logic Level to Enable OUT1 1.8 V

POS

V

Input Current when BSEL High 50 µA

Logic Level to Enable OUT2 0.0 1.7 V

POWER INTERFACE Pin VPOS

Supply Voltage 2.7 5.5 V

Quiescent Current ENBL High 8.5 10.7 mA

Over Temperature –30°C ≤ TA ≤ +85°C12mA

Disable Current

6

ENBL Low 3 10 µA

Over Temperature –30°C ≤ TA ≤ +85°C13µA

NOTES

1

Operation down to 0.02 GHz is possible.

2

Calculated over the input range of –40 dBm to –10 dBm.

3

Mean and standard deviation specifications are in Table I.

4

See TPC 9 for plot of Input Impedance vs. Frequency.

5

Response time in a closed-loop system will depend upon the filter capacitor (C

6

This parameter is guaranteed but not tested in production. The maximum specified limit on this parameter is the +6 sigma value from characterization.

Specifications subject to change without notice.

) used and the response of the variable gain element.

FLT

REV. C–2–

AD8316

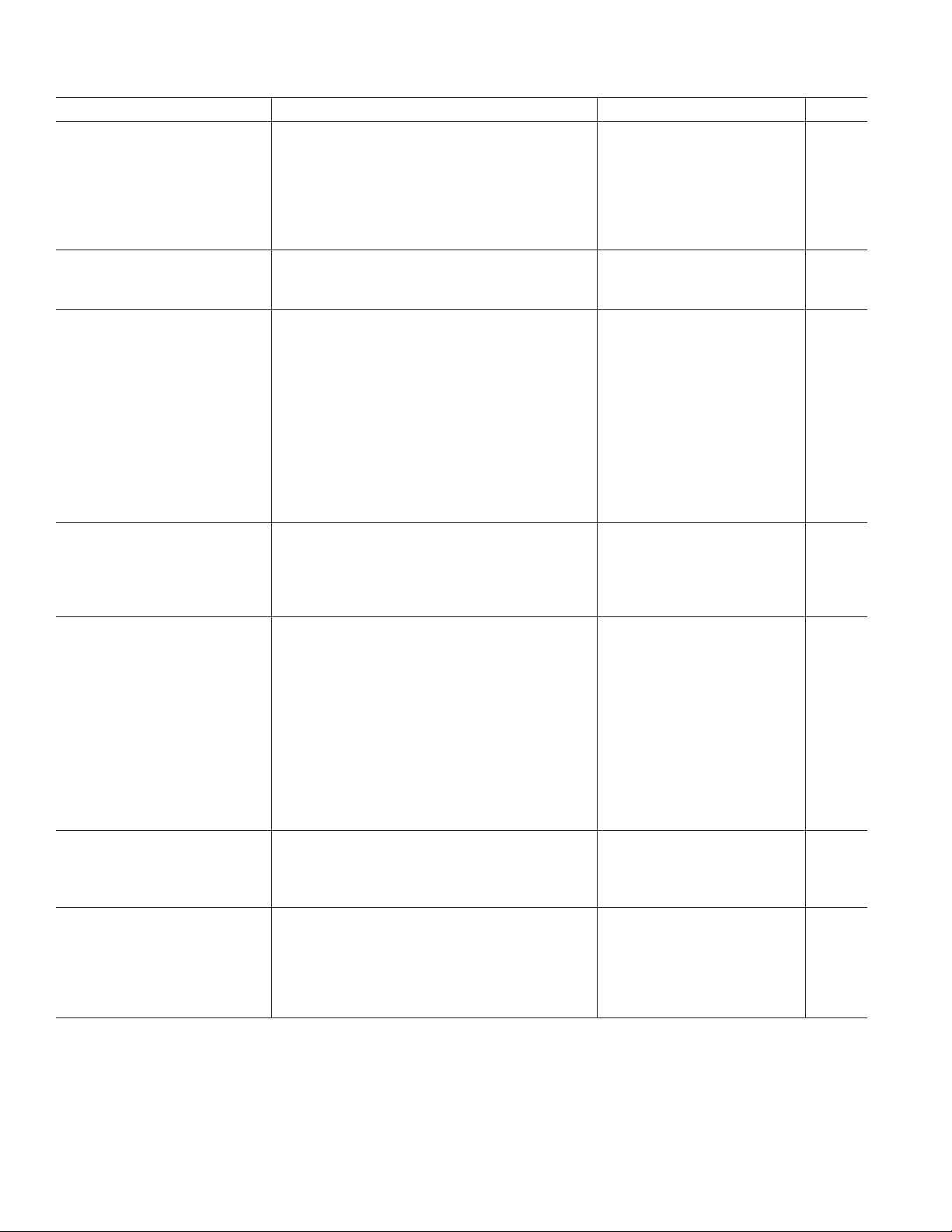

Table I. Typical Specifications at Selected Frequencies at 25°C

Dynamic Range Dynamic Range

Slope (mV/dB) Intercept (dBm) Low Point (dBm) High Point (dBm)

Frequency Standard Standard Standard Standard

(GHz) Mean Deviation Mean Deviation Mean Deviation Mean Deviation

0.1 22.1 0.3 –61.0 1.5 –45.6 0.7 3.0 0.7

0.9 22.2 0.3 –62.2 1.5 –47.6 0.6 1.5 0.6

1.9 21.6 0.3 –63.1 1.5 –49.2 0.8 –4.5 0.8

2.5 21.3 0.3 –66.0 1.6 –51.5 1.1 –3.0 1.1

Slope and intercept calculated over the input amplitude range of –40 dBm to –10 dBm.

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage VPOS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5 V

OUT1, OUT2, VSET, ENBL . . . . . . . . . . . . . . . . . . . 0 V, VPOS

RFIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 dBm

Equivalent Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.6 V

Internal Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . 100 mW

JA (MSOP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200°C/W

(LFCSP, Paddle soldered) . . . . . . . . . . . . . . . . . . . . . 80°C/W

JA

(LFCSP, Paddle not soldered) . . . . . . . . . . . . . . . . . 130°C/W

JA

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . 125°C

Operating Temperature Range . . . . . . . . . . . . . . –40°C to +85°C

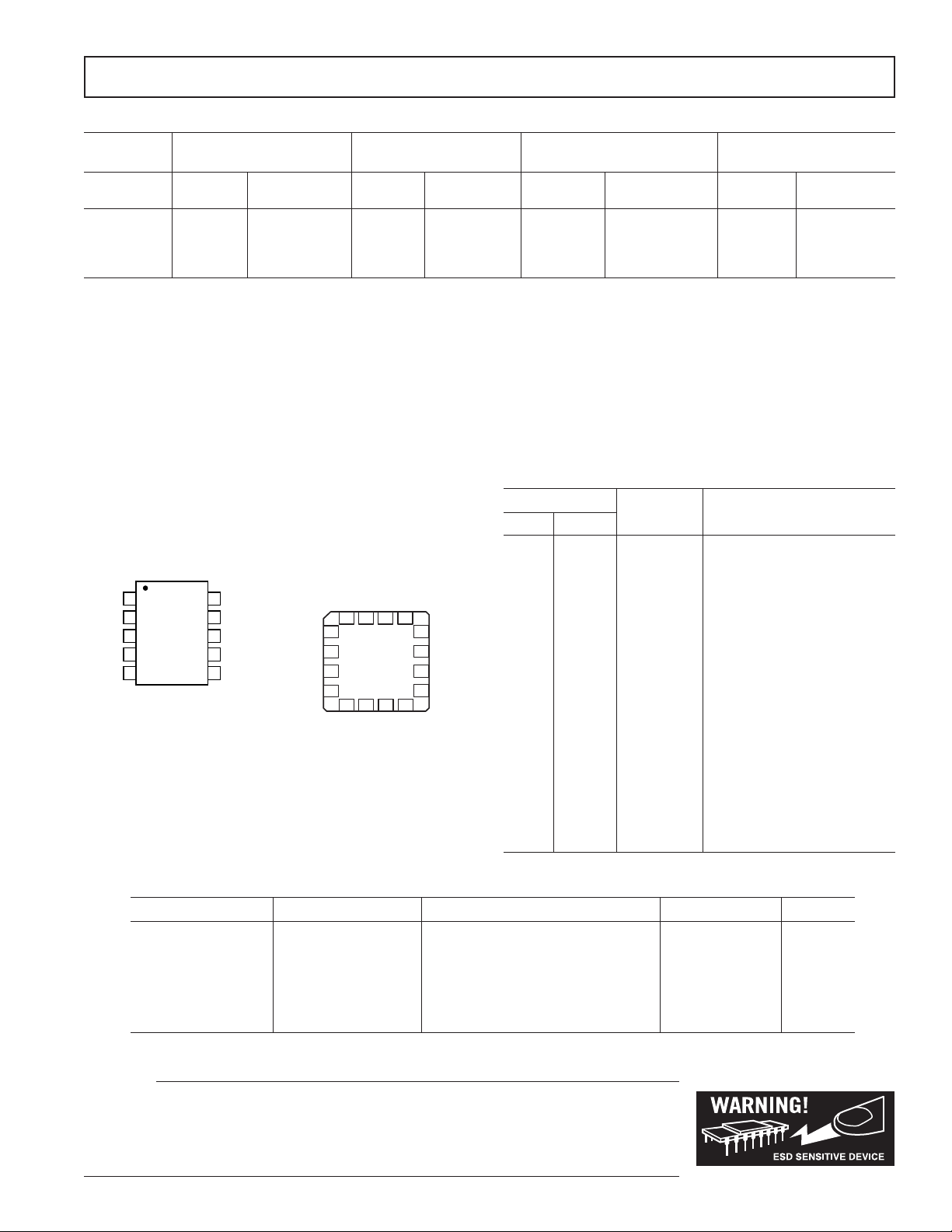

PIN CONFIGURATION

10-Lead MSOP

1

RFIN

ENBL

2

AD8316

TOP VIEW

3

VSET

(NOT TO SCALE)

4

FLT1

BSEL

5

10

9

8

7

6

VPOS

OUT1

COMM

OUT2

FLT2

16-Lead LFCSP

NCNCCOMM

161514

1

RFIN

2

3

4

AD8316

TOP VIEW

(Not to Scale)

5

NC

BSEL

ENBL

VSET

FLT1

NC = NO CONNECT

NC

13

12

VPOS

11

OUT1

10

COMM

9

6

OUT2

7

8

NC

FLT2

Storage Temperature Range . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering 60 sec)

MSOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300°C

LFCSP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

PIN FUNCTION DESCRIPTIONS

Pin No.

MSOP LFCSP Mnemonic Function

11 RFIN RF Input.

22 ENBL Connect to VPOS for Normal

Operation. Connect pin to

ground for disable mode.

33 VSET Setpoint Input.

44 FLT1 Integrator Capacitor for OUT1.

Connect between FLT1 and

COMM.

56 BSEL Band Select. LO = OUT2,

HI = OUT1.

67 FLT2 Integrator Capacitor for OUT2.

Connect between FLT2 and

COMM.

79 OUT2 Band 2 Output.

8 10, 14 COMM Device Common (Ground).

911OUT1 Band 1 Output.

10 12 VPOS Positive Supply Voltage: 2.7 V

to 5.5 V.

5, 8, 13, NC No Connection.

15, 16

ORDERING GUIDE

Model Temperature Range Package Description Package Option Branding

AD8316ARM –30°C to +85°C 10-Lead MSOP, Tube RM-10 J8A

AD8316ARM-REEL7 –30°C to +85°CMSOP, 7" Tape and Reel RM-10 J8A

AD8316-EVAL MSOP Evaluation Board

AD8316ACP-REEL –30°C to +85°C 16-Lead LFCSP, 13" Tape and Reel CP-16-3 J8A

AD8316ACP-REEL7 –30°C to +85°CLFCSP, 7" Tape and Reel CP-16-3 J8A

AD8316ACP-EVAL LFCSP Evaluation Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD8316 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

REV. C

–3–

AD8316

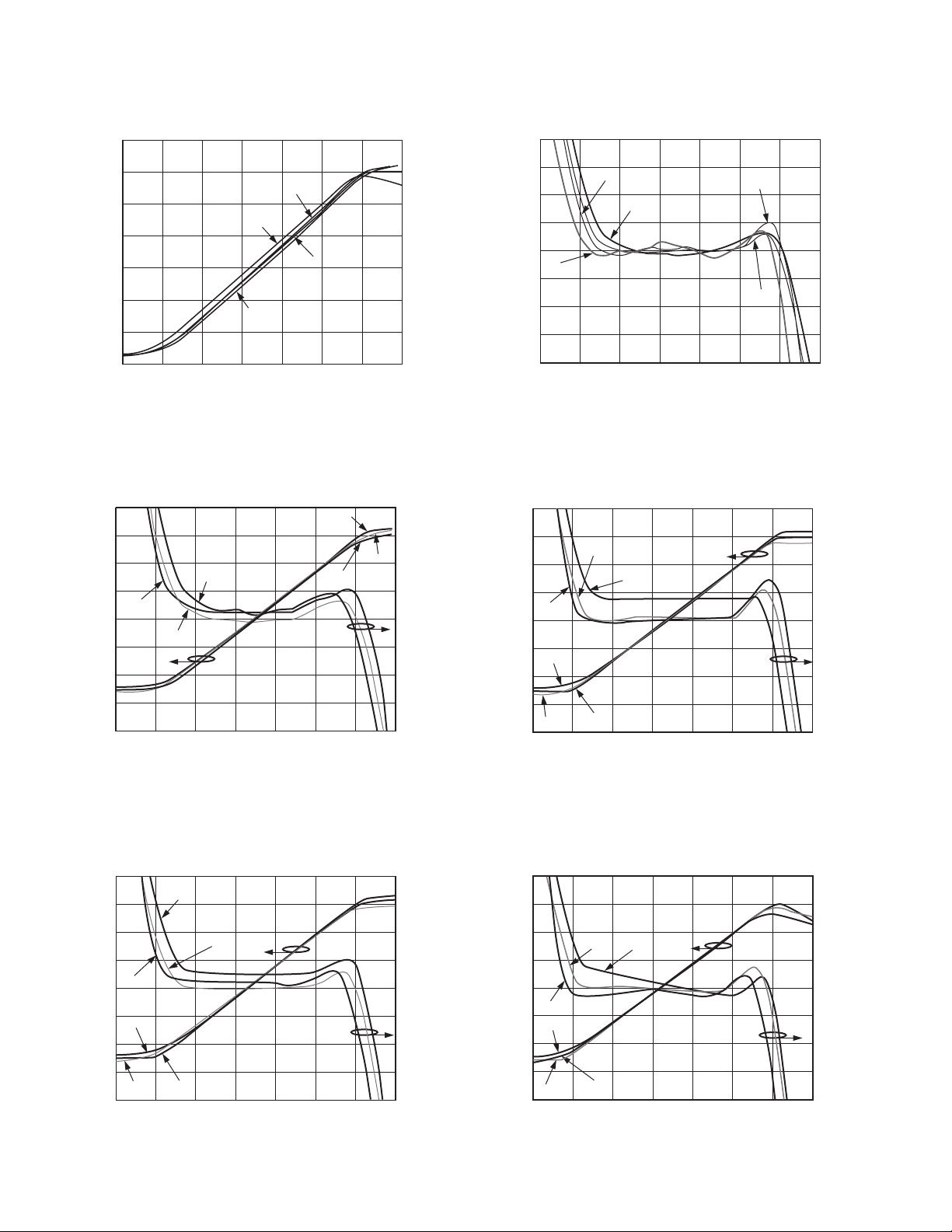

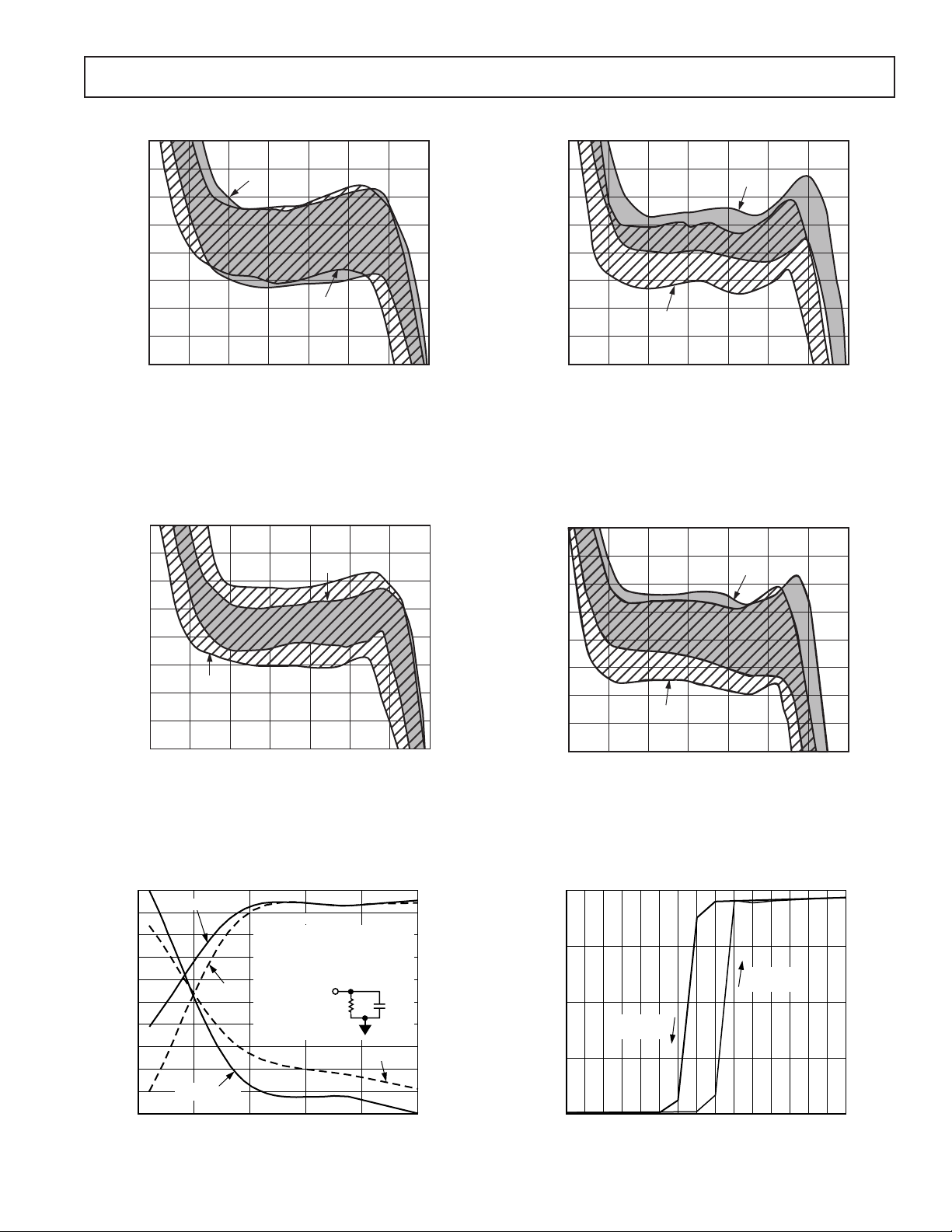

–Typical Performance Characteristics

–73 –53 –43 –33 –13–23 –3–63

1.6

1.4

1.2

1.0

– V

SET

V

0.8

0.6

0.4

0.2

–60

–73 –53 –43 –33 –13–23 –3–63

1.6

1.4

1.2

1.0

– V

0.8

SET

V

0.6

0.4

TPC 1. V

–30C

INPUT AMPLITUDE – dBV

2.5GHz

0.1GHz

–40 –30 –20 0

–50

INPUT AMPLITUDE – dBm

vs. Input Amplitude

SET

INPUT AMPLITUDE – dBV

+85C

+25C

0.9GHz

1.9GHz

–10

–30C

+85C

+25C

10

4

3

2

1

0

–1

–2

ERROR – dB

–73 –53 –43 –33 –13–23 –3–63

4

3

2

1

0

2.5GHz

ERROR – dB

–1

–2

–3

–4

–60

–50

INPUT AMPLITUDE – dBV

1.9GHz

0.1GHz

–40 –30 –20 0

INPUT AMPLITUDE – dBm

–10

1.9GHz

0.9GHz

10

TPC 4. Log Conformance vs. Input Amplitude at

Selected Frequencies

–73 –53 –43 –33 –13–23 –3–63

1.6

1.4

1.2

1.0

–30C

– V

0.8

SET

V

0.6

+85C

0.4

INPUT AMPLITUDE – dBV

4

3

+25C

2

+85C

1

0

–1

–2

ERROR – dB

0.2

0

–60

TPC 2. V

–40 –30 –20 0

–50

INPUT AMPLITUDE – dBm

and Log Conformance vs. Input

SET

Amplitude at 0.1 GHz

–73 –53 –43 –33 –13–23 –3–63

1.6

1.4

1.2

1.0

–30C

– V

0.8

SET

V

0.6

0.4

0.2

0

–60

TPC 3. V

+85C

+25C

–50

INPUT AMPLITUDE – dBV

+85C

+25C

–30C

–40 –30 –20 0

INPUT AMPLITUDE – dBm

and Log Conformance vs. Input

SET

Amplitude at 0.9 GHz

–10

–10

–3

–4

10

4

3

2

1

0

–1

–2

–3

–4

10

ERROR – dB

0.2

0

–60

TPC 5. V

+25C

–30C

–40 –30 –20 0

–50

INPUT AMPLITUDE – dBm

and Log Conformance vs. Input

SET

Amplitude at 1.9 GHz

–73 –53 –43 –33 –13–23 –3–63

1.6

1.4

1.2

1.0

– V

0.8

SET

V

0.6

0.4

0.2

+25C

0

–60

TPC 6. V

–30C

+85C

–50

INPUT AMPLITUDE – dBV

+25C

+85C

–30C

–40 –30 –20 0

INPUT AMPLITUDE – dBm

and Log Conformance vs. Input

SET

Amplitude at 2.5 GHz

–10

–10

–3

–4

10

4

3

2

1

0

–1

–2

–3

–4

10

REV. C–4–

ERROR – dB

AD8316

–73 –53 –43 –33 –13–23 –3–63

4

3

2

1

0

ERROR – dB

–1

–2

–3

–4

–60

–50

INPUT AMPLITUDE – dBV

+85C

–30C

–40 –30 –20 0

INPUT AMPLITUDE – dBm

–10

10

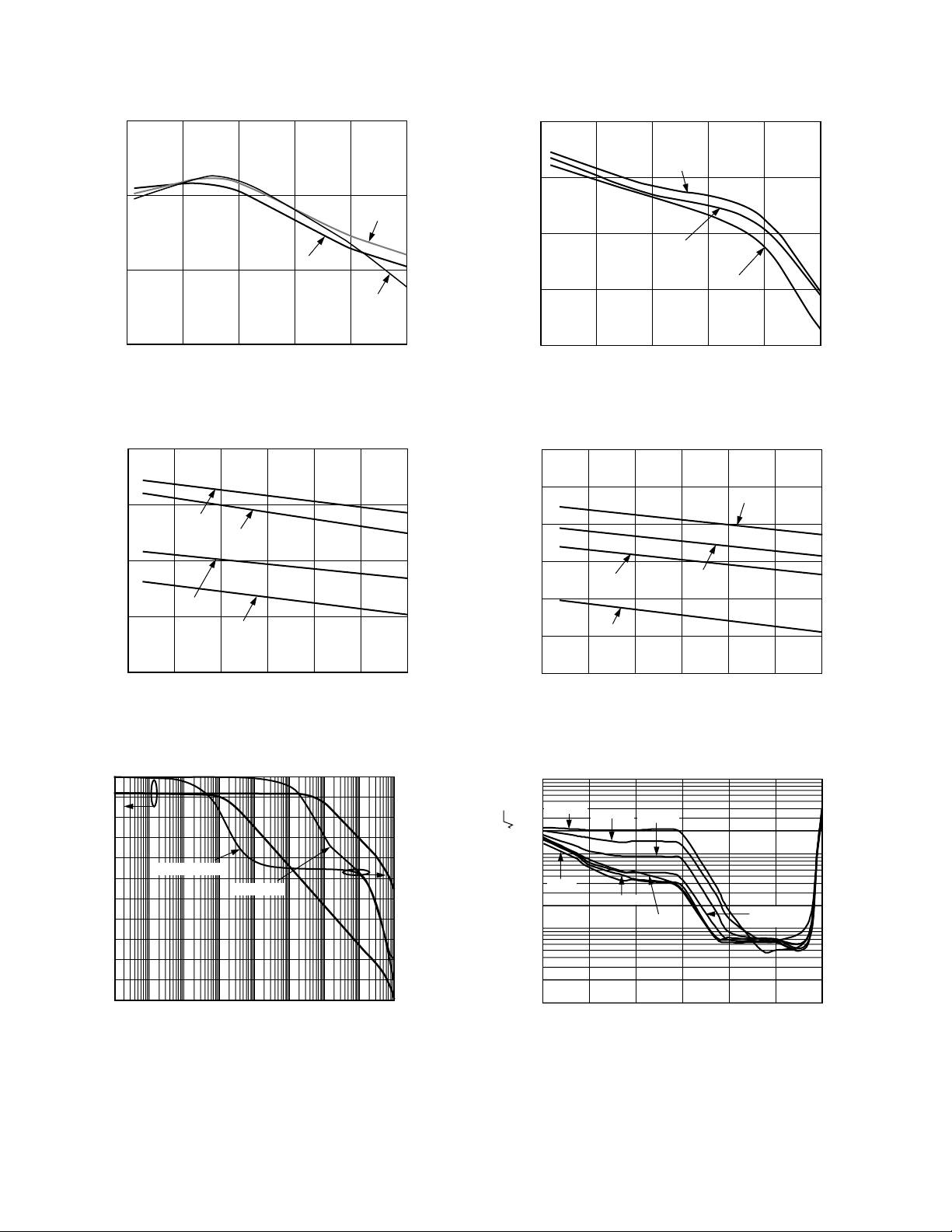

TPC 7. Distribution of Error at Temperature after Ambient

Normalization vs. Input Amplitude, 3 Sigma to Either Side

of Mean, 0.1 GHz

–73 –53 –43 –33 –13–23 –3–63

4

3

2

1

0

ERROR – dB

–1

–2

–3

–4

–60

–50

INPUT AMPLITUDE – dBV

+85C

–30C

–40 –30 –20 0

INPUT AMPLITUDE – dBm

–10

10

TPC 8. Distribution of Error at Temperature after Ambient

Normalization vs. Input Amplitude, 3 Sigma to Either Side

of Mean, 0.9 GHz

–73 –53 –43 –33 –13–23 –3–63

4

3

2

1

0

ERROR – dB

–1

–2

–3

–4

–60

–50

INPUT AMPLITUDE – dBV

+85C

–30C

–40 –30 –20 0

INPUT AMPLITUDE – dBm

–10

10

TPC 10. Distribution of Error at Temperature after Ambient

Normalization vs. Input Amplitude, 3 Sigma to Either Side

of Mean, 1.9 GHz

–73 –53 –43 –33 –13–23 –3–63

4

3

2

1

0

ERROR – dB

–1

–2

–3

–4

–60

–50

INPUT AMPLITUDE – dBV

+85C

–30C

–40 –30 –20 0

INPUT AMPLITUDE – dBm

–10

10

TPC 11. Distribution of Error at Temperature after Ambient

Normalization vs. Input Amplitude, 3 Sigma to Either Side

of Mean, 2.5 GHz

3100

2800

2500

2200

1900

1600

1300

RESISTANCE –

1000

700

400

100

REV. C

X (MSOP)

FREQ MSOP CHIP-SCALE (LFCSP)

(GHz)

R –

jX

R –

0.1

3100 –

600 –

320 –

110 –

j1220

j194

j134

j86

0.9

1.9

X (LFCSP)

R (MSOP)

0

0.5 1.5 2.0

2.5

1.0

FREQUENCY – GHz

2630 –

1000 –

620 –

435 –

R

jX

j1800

j270

j130

j110

R (CSP)

TPC 9. Input Impedance vs. Frequency

0

–200

–400

–600

–800

–1000

X

–1200

REACTANCE –

–1400

–1600

–1800

–2000

2.5

8

6

4

DECREASING

V

ENBL

SUPPLY CURRENT – mA

2

0

0.8

1.0 1.1 1.2 1.41.3 1.5

0.9

V

TPC 12. Supply Current vs. V

INCREASING

V

ENBL

1.6 1.7 1.8 1.9 2.0 2.1 2.2 2.3

– V

ENBL

ENBL

–5–

AD8316

23

22

+25C

SLOPE – mV/dB

21

20

0

0.5 1.0

FREQUENCY – GHz

–30C

+85C

1.5 2.0 2.5

TPC 13. Slope vs. Frequency at Selected Temperatures

22.5

22.0

21.5

SLOPE – mV/dB

21.0

0.9GHz

0.1GHz

1.9GHz

2.5GHz

–60

–62

–64

INTERCEPT – dBm

–66

–68

0

0.5 1.0 2.01.5

+25C

–30C

+85C

2.5

FREQUENCY – GHz

TPC 16. Intercept vs. Frequency at Selected Temperatures

–58

–60

–62

–64

–66

INTERCEPT – dBm

–68

1.9GHz

2.5GHz

0.1GHz

0.9GHz

20.5

2.5

3.0 3.5

4.0 4.5 5.0

VS – V

5.5

TPC 14. Slope vs. Supply Voltage

0

40

30

20

10

0

–10

–20

AMPLITUDE – dB

–30

–40

–50

–60

1

10 100501k 10k 100k 1M

C

FLT

= 220pF

C

= 0pF

FLT

FREQUENCY – Hz

10M 100M

–20

–40

–60

–80

–100

–120

–140

–160

–180

–200

–210

TPC 15. AC Response from VSET to OUT1 and OUT2

PHASE – Degrees

–70

2.5

3.0 3.5 5.04.5

4.0

V

– V

TPC 17. Intercept vs. Supply Voltage

10000

–50dBm

Hz

NOISE SPECTRAL DENSITY – nV/

1000

100

10

100

–40dBm

–25dBm

0dBm

–20dBm

–10dBm

1k 10k 10M1M

FREQUENCY – Hz

100k

RF INPUT

28dBm

TPC 18. Output Noise Spectral Density, RL = ,

= 220 pF, by RF Input Amplitude

C

FLT

5.5

100M

REV. C–6–

Loading...

Loading...