5 MHz–500 MHz 100 dB Demodulating

a

Logarithmic Amplifier with Limiter Output

FEATURES

Complete Multistage Log-Limiting IF Amplifier

100 dB Dynamic Range: –78 dBm to +22 dBm (Re 50 ⍀)

Stable RSSI Scaling Over Temperature and Supplies:

20 mV/dB Slope, –95 dBm Intercept

ⴞ0.4 dB RSSI Linearity up to 200 MHz

Programmable Limiter Gain and Output Current

Differential Outputs to 10 mA, 2.4 V p-p

Overall Gain 100 dB, Bandwidth 500 MHz

Constant Phase (Typical ⴞ80 ps Delay Skew)

Single Supply of +2.7 V to +6.5 V at 16 mA Typical

Fully Differential Inputs, R

= 1 k⍀, C

IN

= 2.5 pF

IN

500 ns Power-Up Time, <1 A Sleep Current

APPLICATIONS

Receivers for Frequency and Phase Modulation

Very Wide Range IF and RF Power Measurement

Receiver Signal Strength Indication (RSSI)

Low Cost Radar and Sonar Signal Processing

Instrumentation: Network and Spectrum Analyzers

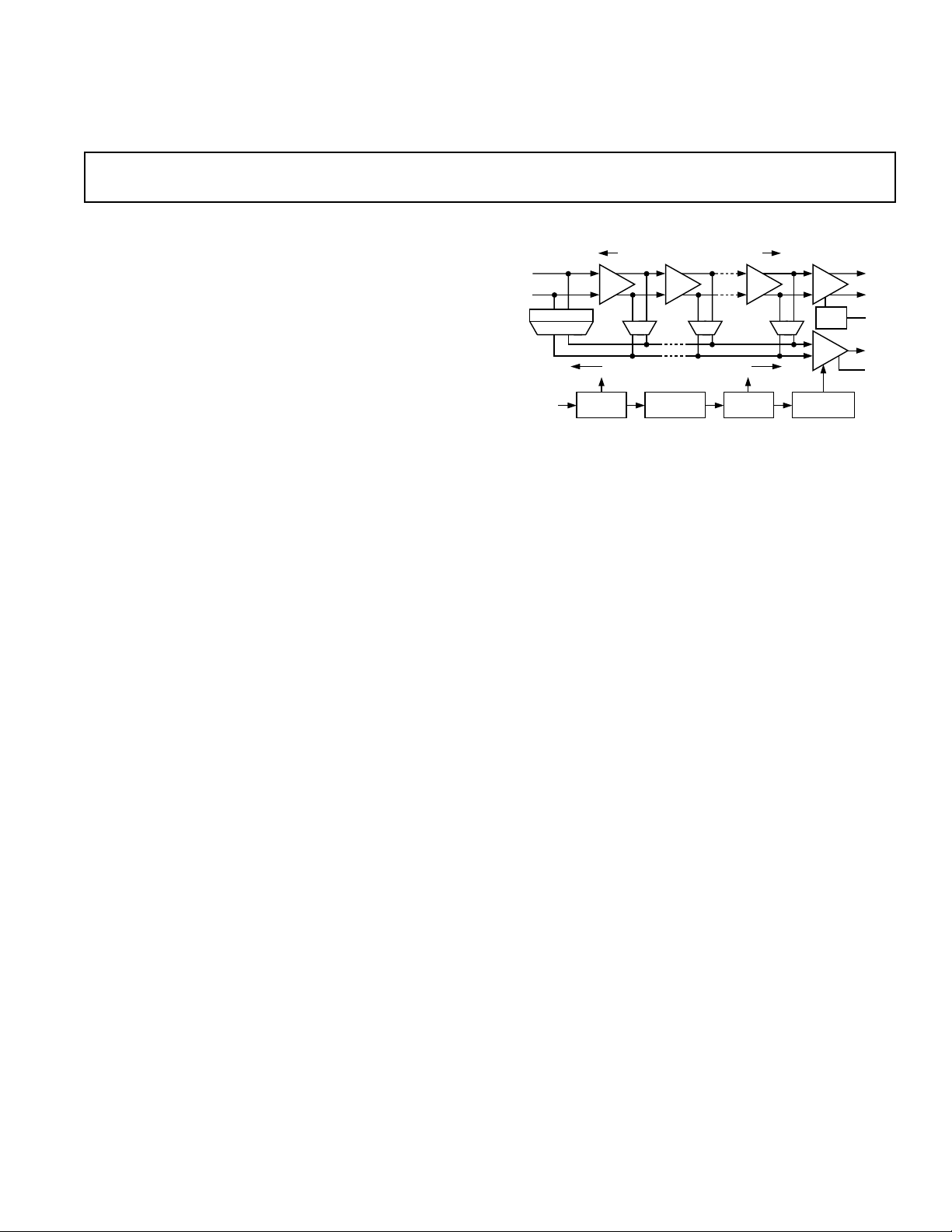

INHI

INLO

LADR ATTEN

ENBL

AD8309

FUNCTIONAL BLOCK DIAGRAM

SIX STAGES TOTAL GAIN 72dB TYP GAIN 18dB

12dB

TEN DETECTORS SPACED 12dB

GAIN

BIAS

DET DET4 3 DET

BAND-GAP

REFERENCE

12dB

12dB LIM

DET

SLOPE

BIAS

INTERCEPT

TEMP COMP

BIAS

CTRL

I-V

LMHI

LMLO

LMDR

VLOG

FLTR

PRODUCT DESCRIPTION

The AD8309 is a complete IF limiting amplifier, providing both

an accurate logarithmic (decibel) measure of the input signal

(the RSSI function) over a dynamic range of 100 dB, and a

programmable limiter output, useful from 5 MHz to 500 MHz.

It is easy to use, requiring few external components. A single

supply voltage of +2.7 V to +6.5 V at 16 mA is needed, corresponding to a power consumption of under 50 mW at 3 V, plus

the limiter bias current, determined by the application and

typically 2 mA, providing a limiter gain of 100 dB when using

200 Ω loads. A CMOS-compatible control interface can enable

the AD8309 within about 500 ns and disable it to a standby

current of under 1 µA.

The six cascaded amplifier/limiter cells in the main path have a

small signal gain of 12.04 dB (×4), with a –3 dB bandwidth of

850 MHz, providing a total gain of 72 dB. The programmable

output stage provides a further 18 dB of gain. The input is fully

differential and presents a moderately high impedance (1 kΩ in

parallel with 2.5 pF). The input-referred noise-spectral-density,

when driven from a terminated 50 Ω, source is 1.28 nV/√Hz,

equivalent to a noise figure of 3 dB. The sensitivity of the

AD8309 can be raised by using an input matching network.

Each of the main gain cells includes a full-wave detector. An

additional four detectors, driven by a broadband attenuator, are

used to extend the top end of the dynamic range by over 48 dB.

The overall dynamic range for this combination extends from

–91 dBV (–78 dBm at the 50 Ω level) to a maximum permissible

value of +9 dBV, using a balanced drive of antiphase inputs each

of 2 V in amplitude, which would correspond to a sine wave

power of +22 dBm if the differential input were terminated in

50 Ω. The slope of the RSSI output is closely controlled to

20 mV/dB, while the intercept is set to –108 dBV (–95 dBm

re 50 Ω). These scaling parameters are determined by a band-

gap voltage reference and are substantially independent of temperature and supply. The logarithmic law conformance is typically

within ±0.4 dB over the central 80 dB of this range at any fre-

quency between 10 MHz and 200 MHz, and is degraded only

slightly at 500 MHz.

The RSSI response time is nominally 67 ns (10%–90%). The

averaging time may be increased without limit by the addition of

an external capacitor. The full output of 2.34 V at the maximum

input of +9 dBV can drive any resistive load down to 50 Ω and

this interface remains stable with any value of capacitance on

the output.

The AD8309 is fabricated on an advanced complementary

bipolar process using silicon-on-insulator isolation techniques

and is available in the industrial temperature range of –40°C to

+85°C, in a 16-lead TSSOP package.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

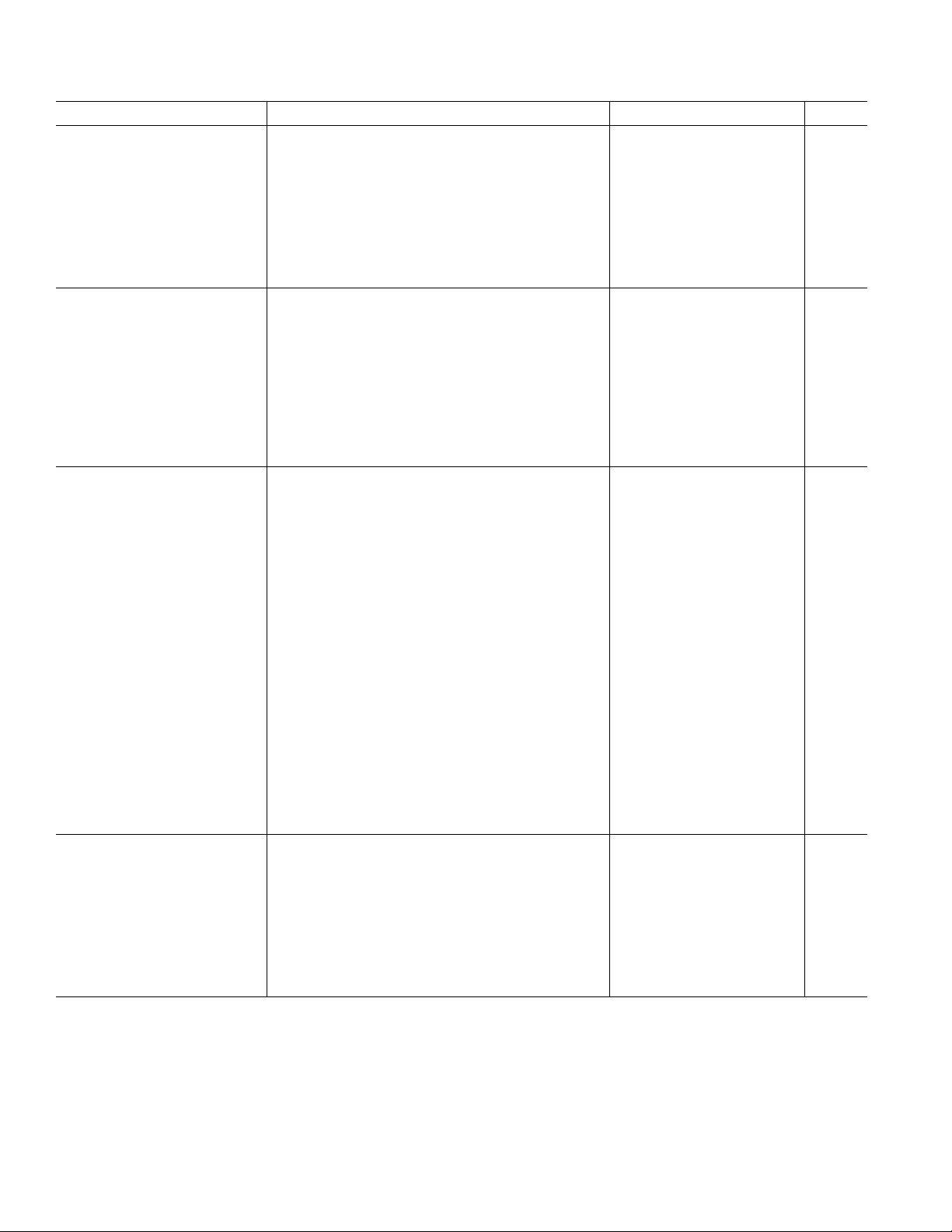

AD8309–SPECIFICATIONS

Parameter Conditions Min

INPUT STAGE (Inputs INHI, INLO)

Maximum Input

2

Differential Drive, p-p ±3.5 ±4V

(VS = +5 V, TA = +25ⴗC, unless otherwise noted)

1

Typ Max1Units

+9 dBV

Equivalent Power in 50 Ω Terminated in 52.3 Ω +22 dBm

Noise Floor Terminated 50 Ω Source 1.28 nV/√Hz

Equivalent Power in 50 Ω 500 MHz Bandwidth –78 dBm

Input Resistance From INHI to INLO 800 1000 1200 Ω

Input Capacitance From INHI to INLO 2.5 pF

DC Bias Voltage Either Input 1.725 V

LIMITING AMPLIFIER (Outputs LMHI, LMLO)

Usable Frequency Range 5 500 MHz

= R

At Limiter Output R

LOAD

= 50 Ω to –10 dB Point 875 MHz

LIM

Phase Variation at 100 MHz Over Input Range –60 dBm to +10 dBm ±3 Degrees

Limiter Output Current Nominally 400 mV/R

Versus Temperature –40°C ≤ T

Input Range

3

LIM

≤ +85°C –0.008 %/°C

A

0110mA

–78 +9 dBV

Equivalent dBm –65 +22 dBm

Maximum Output Voltage At Either LMHI or LMLO, wrt VPS2 1 1.25 V

Rise/Fall Time (10%–90%) R

≤ 50 Ω, 40 Ω ≤ R

LOAD

≤ 400 Ω 0.4 ns

LIM

LOGARITHMIC AMPLIFIER (Output VLOG)

±3 dB Error Dynamic Range From Noise Floor to Maximum Input 100 dB

Transfer Slope 5 MHz ≤ f ≤ 200 MHz 18 20 22 mV/dB

Over Temperature –40°C < T

< +85°C 17 20 23 mV/dB

A

Intercept (Log Offset) 5 MHz ≤ f ≤ 200 MHz –116 –108 –100 dBV

Equivalent dBm (re 50 Ω) –103 –95 –87 dBm

Over Temperature –40°C ≤ T

≤ +85°C –117 –108 –99 dBV

A

Equivalent dBm (re 50 Ω) –104 –95 –86 dBm

Temperature Sensitivity –0.009 dB/°C

Linearity Error (Ripple) Input from –83 dBV (–70 dBm) to +7 dBV (+20 dBm) ±0.4 dB

Output Voltage Input = –91 dBV (–78 dBm) V

Input = +9 dBV (+22 dBm) V

Input = +9 dBV (+22 dBm) V

Minimum Load Resistance, R

L

= +5 V, +2.7 V 0.34 V

S

= +5 V 2.34 2.75 V

S

= +2.75 V 2.10 V

S

40 50 Ω

Maximum Sink Current To Ground 0.75 1.0 1.25 mA

Output Resistance 0.3 Ω

Small-Signal Bandwidth 3.5 MHz

Output Settling Time to 1% Large Scale Input, +3 dBV (+16 dBm),

≥␣ 50 Ω, CL ≤␣ 100 pF 120 220 ns

R

L

Rise/Fall Time (10%–90%) Large Scale Input, +3 dBV (+16 dBm),

R

≥␣ 50 Ω, CL ≤␣ 100 pF 67 100 ns

L

POWER INTERFACES

Supply Voltage, V

POS

2.7 5 6.5 V

Quiescent Current Zero-Signal, LMDR Open 13 16 20 mA

Over Temperature –40°C < T

Disable Current –40°C < T

Additional Bias for Limiter R

LIM

Logic Level to Enable Power HI Condition, –40°C < T

Input Current when HI 3 V at ENBL, –40°C < T

< +85°C 111623mA

A

< +85°C 0.01 4 µA

A

= 400 Ω (See Text) 1.4 1.6 mA

< +85°C 1.8 V

A

< +85°C4060µA

A

POS

V

Logic Level to Disable Power LO Condition, –40°C < TA < +85°C –0.5 1 V

NOTES

1

Minimum and maximum specified limits on parameters that are guaranteed but not tested are six sigma values.

2

The input level is specified in “dBV” since logarithmic amplifiers respond strictly to voltage, not power. 0 dBV corresponds to a sinusoidal single-frequency input of

1 V rms. A power level of 0 dBm (1 mW) in a 50 Ω termination corresponds to an input of 0.2236 V rms. Hence, the relationship between dBV and dBm is a fixed

offset of +13 dBm in the special case of a 50 Ω termination.

3

Due to the extremely high Gain Bandwidth Product of the AD8309, the output of either LMHI or LMLO will be unstable for levels below –78 dBV (–65 dBm, re 50 Ω).

Specifications subject to change without notice.

–2–

REV. B

AD8309

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage VS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7.5 V

Input Level, Differential (re 50 Ω) . . . . . . . . . . . . . . . +26 dBm

Input Level, Single-Ended (re 50 Ω) . . . . . . . . . . . . . +20 dBm

Internal Power Dissipation . . . . . . . . . . . . . . . . . . . . . 500 mW

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C/W

θ

JA

θ

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27.6°C/W

JC

Maximum Junction Temperature . . . . . . . . . . . . . . . . +125°C

Operating Temperature Range . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering 60 sec) . . . . . . . . +300°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may effect device reliability.

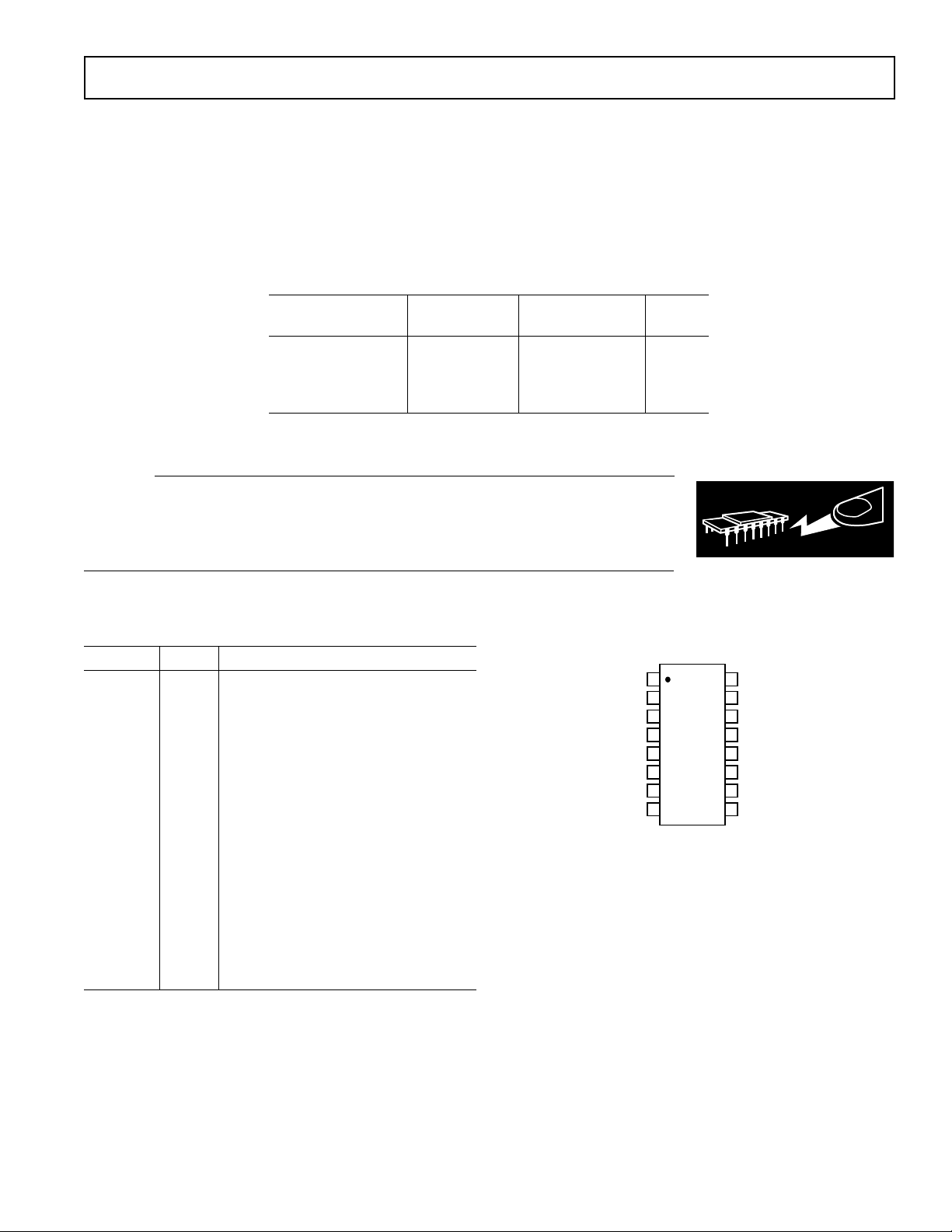

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD8309ARU –40°C to +85°C 16-Lead TSSOP RU-16

AD8309ARU-REEL –40°C to +85°C 13" Tape and Reel RU-16

AD8309ARU-REEL7 –40°C to +85°C 7" Tape and Reel RU-16

AD8309-EVAL Evaluation Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD8309 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

PIN FUNCTION DESCRIPTIONS

Pin Name Function

1 COM2 Special Common Pin for RSSI Output.

2 VPS1 Supply Pin for First Five Amplifier Stages

and the Main Biasing System.

3, 6, 11, 14 PADL Four Tie-Downs to the Paddle on Which

the IC Is Mounted; Grounded.

4 INHI Signal Input, HI or Plus Polarity.

5 INLO Signal Input, LO or Minus Polarity.

7 COM1 Main Common Connection.

8 ENBL Chip Enable; Active When HI.

9 LMDR Limiter Drive Programming Pin.

10 FLTR RSSI Bandwidth-Reduction Pin.

12 LMLO Limiter Output, LO or Minus Polarity.

13 LMHI Limiter Output, HI or Plus Polarity.

15 VPS2 Supply Pin for Sixth Gain Stage, Limiter

and RSSI Output Stage Load Current.

16 VLOG Logarithmic (RSSI) Output.

PIN CONFIGURATION

COM2

VPS1

PADL

INHI

INLO

PADL

COM1

ENBL

1

2

3

AD8309

4

TOP VIEW

5

(Not to Scale)

6

7

8

16

VLOG

VPS2

15

PADL

14

LMHI

13

LMLO

12

PADL

11

FLTR

10

LMDR

9

REV. B

–3–

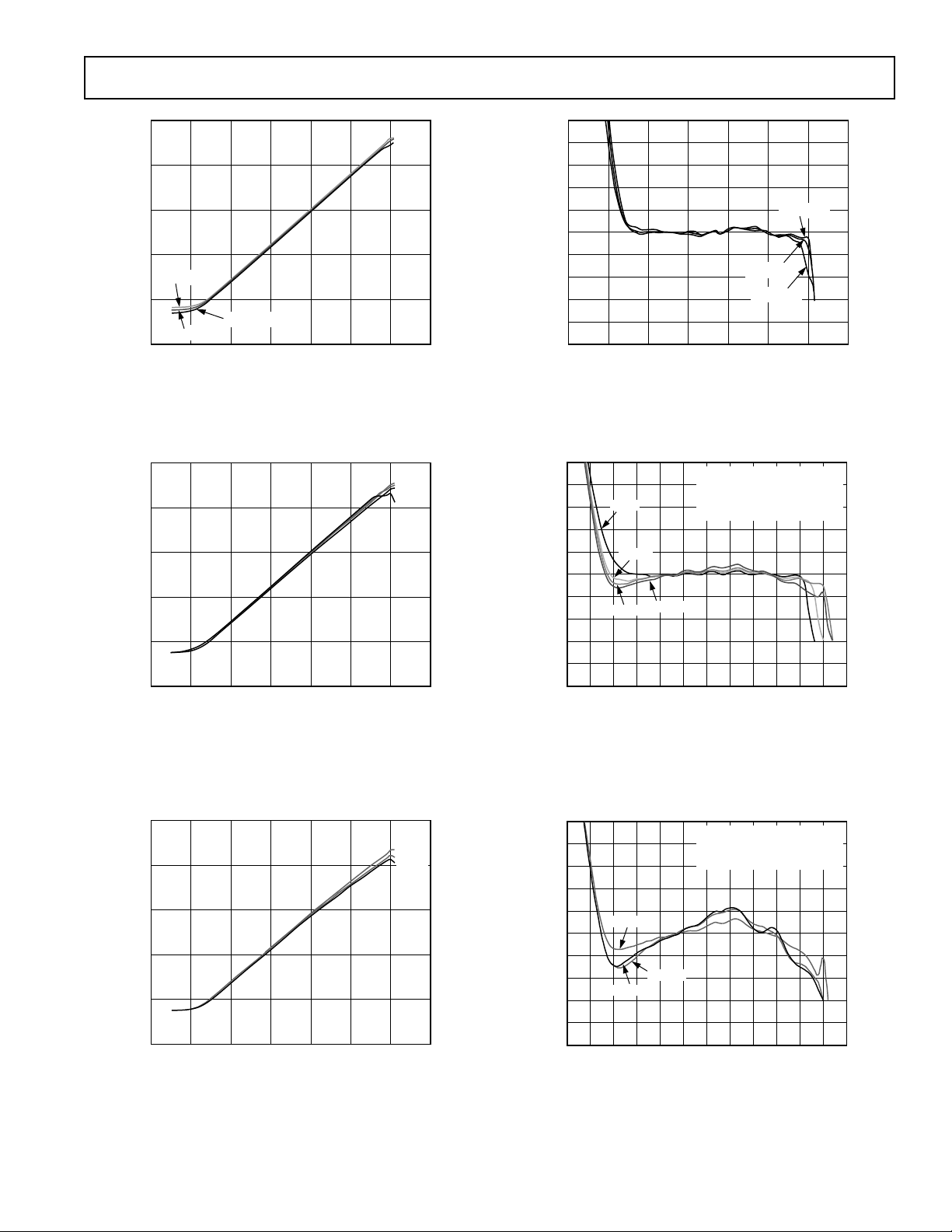

AD8309–Typical Performance Characteristics

100

10

1

0.1

0.01

0.001

SUPPLY CURRENT – mA

0.0001

0.00001

0.5 2.50.7

+258C

+858C

–408C

0.9 1.1 1.3 1.5 1.7 1.9 2.1 2.3

ENABLE VOLTAGE – V

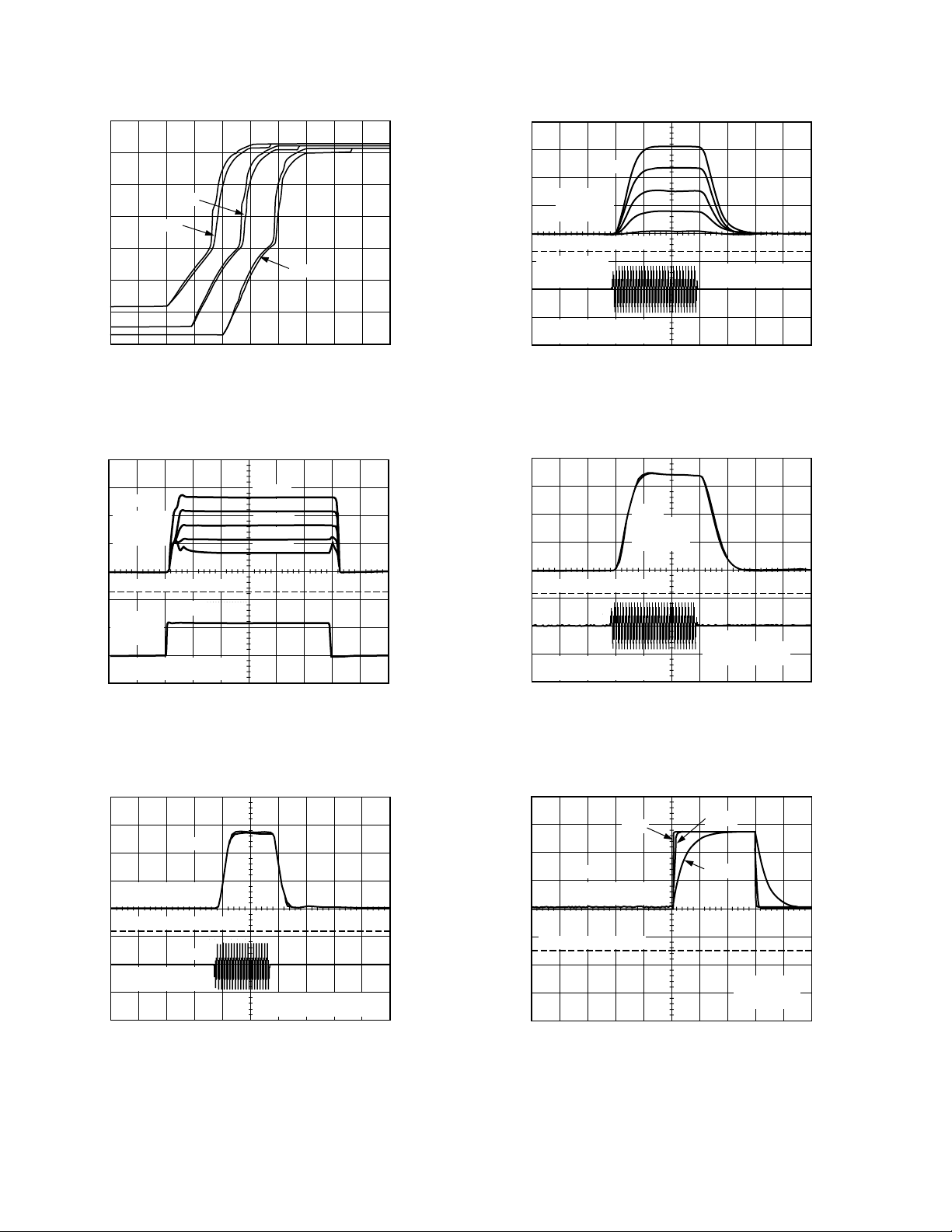

Figure 1. Supply Current vs. Enable Voltage @

T

= –40°C, +25°C and +85°C

A

–13dBV

–33dBV

–53dBV

–73dBV

–93dBV

VLOG

500mV PER

VERTICAL

DIVISION

GROUND REFERENCE

5V PER

VERTICAL

DIVISION

ENBL

500ns PER HORIZONTAL

DIVISION

VLOG

500mV PER

VERTICAL

DIVISION

GROUND REFERENCE

+10dBm INPUT

LEVEL SHOWN

HERE

100ns PER HORIZONTAL

DIVISION

500mV PER

VERTICAL DIVISION

Figure 4. RSSI Pulse Response for Inputs Stepped from

Zero to –63 dBV, –43 dBV, –23 dBV, –3 dBV

VLOG

500mV PER

VERTICAL

DIVISION

GROUND REFERENCE

INPUT

1V PER VERTICAL

100ns PER HORIZONTAL

DIVISION

DIVISION

Figure 2. Power On/Off Response Time with RF Input of

–93 dBV to –13 dBV

VLOG

500mV PER

VERTICAL DIVISION

GROUND REFERENCE

INPUT

500mV PER

VERTICAL DIVISION

200ns PER HORIZONTAL

DIVISION

Figure 3. Large Signal RSSI Pulse Response with

C

= 100 pF and RL = 50Ω and 75Ω (Curves Overlap)

L

Figure 5. Large Signal RSSI Pulse Response with RL = 100

and CL = 33 pF, 100 pF and 330 pF (Curves Overlap)

27pF

VLOG

200mV PER

VERTICAL DIVISION

GROUND REFERENCE

270pF

3300pF

100ms PER

HORIZONTAL

DIVISION

Figure 6. Small Signal AC Response of RSSI Output with

External Filter Capacitance of 27 pF, 270 pF and 3300 pF

Ω

–4–

REV. B

AD8309

2.5

2.0

1.5

1.0

RSSI OUTPUT – V

TA = +858C

0.5

TA = –408C

–80 –60 –40 –20 0 20 40

INPUT LEVEL – dBm Re 50V

0

–100

TA = +258C

Figure 7. RSSI Output vs. Input Level, 100 MHz Sine Input,

= –40°C, +25°C and +85°C, Single-Ended Input

at T

A

2.5

2.0

1.5

1.0

RSSI OUTPUT – V

0.5

0

–80 –60 –40 –20 0 20 40

–100

INPUT LEVEL – dBm Re 50V

100MHz

50MHz

200MHz

5MHz

Figure 8. RSSI Output vs. Input Level, at TA = +25°C, for

Frequencies of 5 MHz, 50 MHz, 100 MHz and 200 MHz

5

4

3

2

TA = +258C

TA = –408C

0

TA = +858C

20 40

1

0

–1

ERROR – dB

–2

–3

–4

–5

–100

–80 –60 –40 –20

INPUT LEVEL – dBm Re 50V

Figure 10. Log Linearity of RSSI Output vs. Input Level,

100 MHz Sine Input, at T

5

4

3

2

1

0

–1

ERROR – dB

–2

–3

–4

–5

–90

5MHz

50MHz

100MHz

–80 –70 –60 –50

= –40°C, +25°C, and +85°C

A

DYNAMIC RANGE

5MHz

50MHz

100MHz

200MHz

200MHz

–40 –30 –20 –10 0 10 20 30

INPUT LEVEL – dBm Re 50V

61dB

85

91

97

96

63dB

93

99

103

102

Figure 11. Log Linearity of RSSI Output vs. Input Level, at

T

= +25°C, for Frequencies of 5 MHz, 50 MHz, 100 MHz

A

and 200 MHz

2.5

300MHz

400MHz

2.0

1.5

1.0

RSSI OUTPUT – V

0.5

0

–80 –60 –40 –20 0 20 40

–100

INPUT LEVEL – dBm Re 50V

500MHz

Figure 9. RSSI Output vs. Input Level, at TA = +25°C, for

Frequencies of 300 MHz, 400 MHz and 500 MHz

REV. B

5

4

3

2

1

0

–1

ERROR – dB

–2

–3

–4

–5

–90

300MHz

400MHz

500MHz

–80 –70 –60 –50 –40 –30 –20 –10 0 10 20 30

INPUT LEVEL – dBm Re 50V

DYNAMIC RANGE

300MHz

400MHz

500MHz

61dB

90

65

66

63dB

102

100

100

Figure 12. Log Linearity of RSSI Output vs. Input Level,

at T

= +25°C, for Frequencies of 300 MHz, 400 MHz and

A

500 MHz

–5–

AD8309

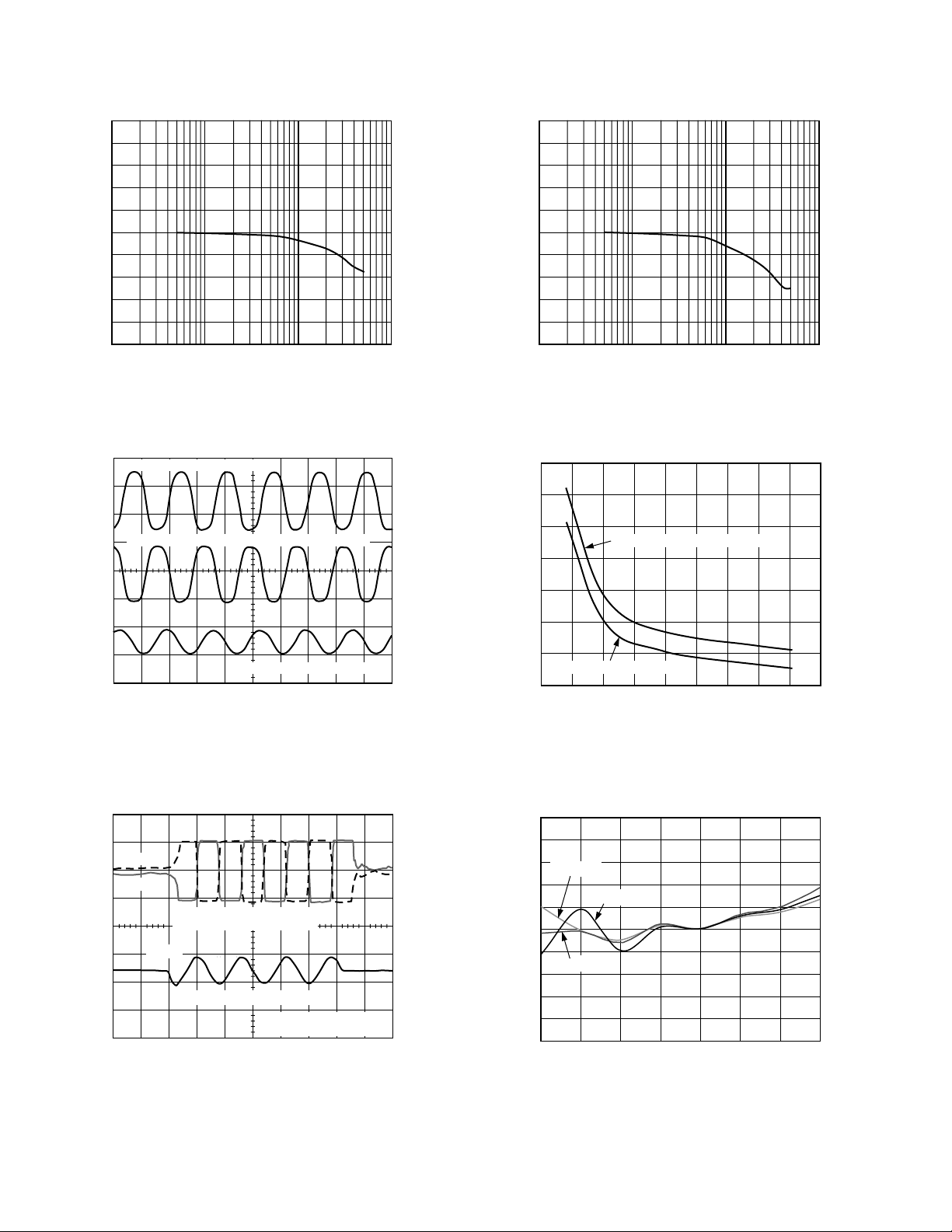

25

24

23

22

21

20

19

RSSI SLOPE – mV/dB

18

17

16

15

1

10 100 1000

FREQUENCY – MHz

Figure 13. RSSI Slope vs. Frequency Using Termination of

Ω

in Series with 4.7 nH

52.3

2ns PER HORIZONTAL DIVISION

LIMITER OUTPUTS 100mV PER VERTICAL DIVISION

–103

–104

–105

–106

–107

–108

–109

–110

RSSI INTERCEPT – dBV

–111

–112

–113

1

10 100 1000

FREQUENCY – MHz

Figure 16. RSSI Intercept vs. Frequency Using Termina-

Ω

tion of 52.3

in Series with 4.7 nH

14

12

10

ADDITIONAL SUPPLY CURRENT

8

2mV PER VERTICAL DIVISION

Figure 14. Limiter Output at 300 MHz for a Sine Wave

Input of –60 dBV (–47 dBm), Using an R

R

LIM

of 100

Ω

LMLO

LMHI

LIMITER OUTPUTS

50mV PER VERTICAL DIVISION

INPUT

1mV PER VERTICAL DIVISION

12.5ns PER HORIZONTAL

of 50 Ω and an

LOAD

DIVISION

Figure 15. Limiter Response at LMHI, LMLO with Pulsed

Sine Input of –70 dBV (–57 dBm) at 50 MHz; R

= 200

R

LIM

Ω

LOAD

= 50 Ω,

6

CURRENT – mA

4

2

LIMITER OUTPUT CURRENT

0

0

100 200 300 400 450

150 250 35050

R

– V

LIM

Figure 17. Additional Supply Current and Limiter Output Current vs. R

10

8

6

TA = +858C

4

2

0

–2

NORMALIZED

TA = +258C

–4

–6

LIMITER PHASE RESPONSE – Degrees

–8

–10

–60

LIM

TA = –408C

–50 –30 –20 –10 10

–40 0

INPUT LEVEL – dBm Re 50V

Figure 18. Normalized Limiter Phase Response vs. Input

Level. Frequency = 100 MHz; T

= –40°C, +25°C and +85°C

A

–6–

REV. B

Loading...

Loading...