ANALOG DEVICES AD8139 Service Manual

Low Noise, Rail-to-Rail,

+OUT

FEATURES

Fully differential

Low noise

2.25 nV/√Hz

2.1 pA/√Hz

Low harmonic distortion

98 dBc SFDR @ 1 MHz

85 dBc SFDR @ 5 MHz

72 dBc SFDR @ 20 MHz

High speed

410 MHz, 3 dB BW (G = 1)

800 V/μs slew rate

45 ns settling time to 0.01%

69 dB output balance @ 1 MHz

80 dB dc CMRR

Low offset: ±0.5 mV maximum

Low input offset current: 0.5 μA maximum

Differential input and output

Differential-to-differential or single-ended-to-differential

operation

Rail-to-rail output

Adjustable output common-mode voltage

Wide supply voltage range: 5 V to 12 V

Available in a small SOIC package and an 8-lead LFCSP

GENERAL DESCRIPTION

The AD8139 is an ultralow noise, high performance differential

amplifier with rail-to-rail output. With its low noise, high

SFDR, and wide bandwidth, it is an ideal choice for driving

ADCs with resolutions to 18 bits. The AD8139 is easy to apply,

and its internal common-mode feedback architecture allows its

output common-mode voltage to be controlled by the voltage

applied to one pin. The internal feedback loop also provides

outstanding output balance as well as suppression of even-order

harmonic distortion products. Fully differential and singleended-to-differential gain configurations are easily realized by

the AD8139. Simple external feedback networks consisting of

four resistors determine the closed-loop gain of the amplifier.

The AD8139 is manufactured on the Analog Devices, Inc.

proprietary, second-generation XFCB process, enabling it to

achieve low levels of distortion with input voltage noise of only

2.25 nV/√Hz.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

Differential ADC Driver

AD8139

APPLICATIONS

ADC drivers to 18 bits

Single-ended-to-differential converters

Differential filters

Level shifters

Differential PCB drivers

Differential cable drivers

FUNCTIONAL BLOCK DIAGRAMS

AD8139

–IN

1

2

V

OCM

V+

3

+OUT

4

NC = NO CONNECT

Figure 1. 8-Lead SOIC

AD8139

TOP VIEW

(Not to Scale)

1–IN

2V

OCM

3V+

4

NC = NO CONNECT

Figure 2. 8-Lead LFCSP

The AD8139 is available in an 8-lead SOIC package with an

exposed paddle (EP) on the underside of its body and a 3 mm ×

3 mm LFCSP. It is rated to operate over the temperature range

of −40°C to +125°C.

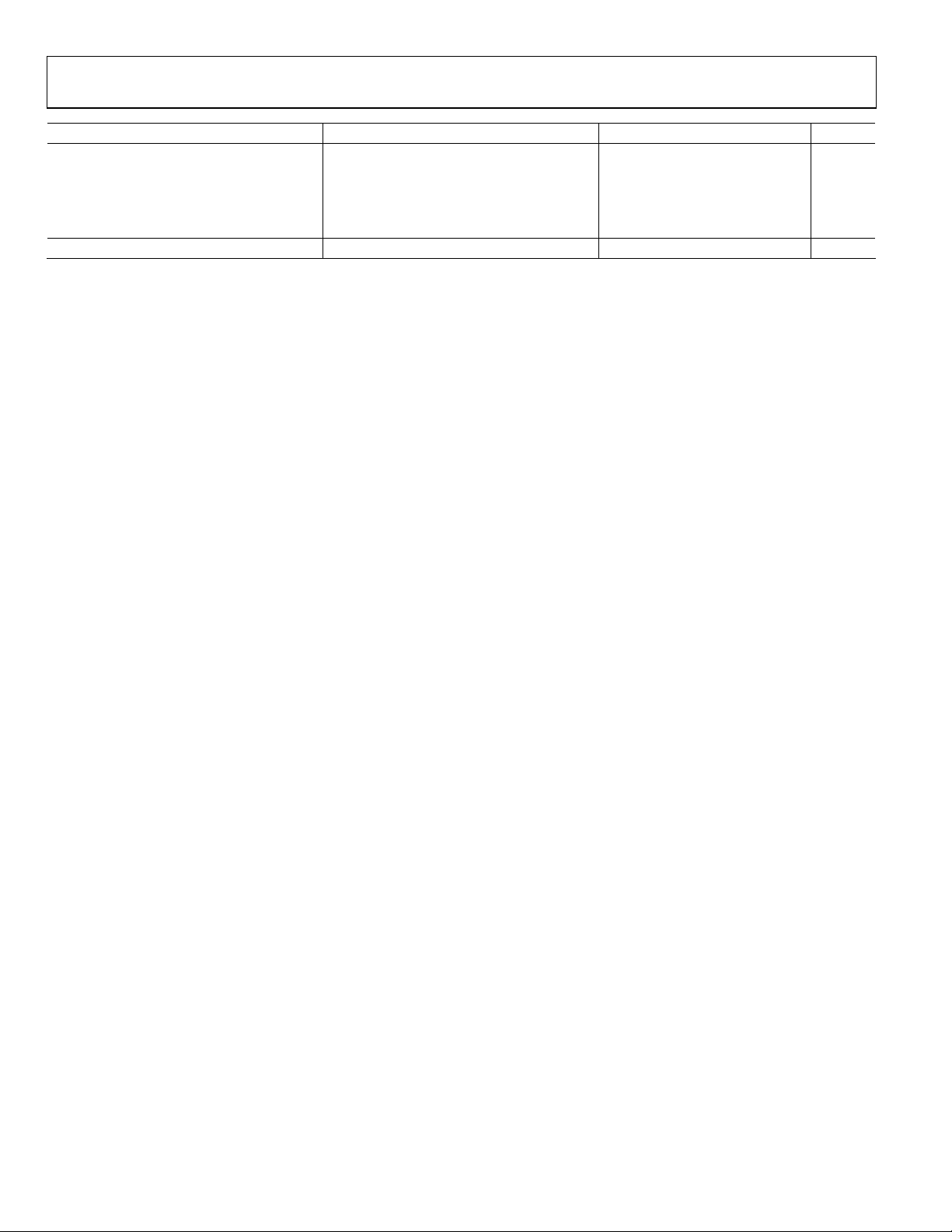

100

10

INPUT VOLTAGE NOISE (nV/ Hz)

1

10 100 1k 10k 100k 1M 10M 1G100M

Figure 3. Input Voltage Noise vs. Frequency

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

FREQUENCY (Hz)

8

7

6

5

+IN

NC

V–

–OUT

8+IN

7NC

6V–

5–OUT

04679-001

04679-102

4679-078

AD8139

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagrams............................................................. 1

General Description......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

VS = ±5 V, V

VS = 5 V, V

= 0 V.................................................................. 3

OCM

= 2.5 V ................................................................. 5

OCM

Absolute Maximum Ratings............................................................ 7

Thermal Resistance ...................................................................... 7

ESD Caution.................................................................................. 7

REVISION HISTORY

10/07—Rev. A to Rev. B.

Changes to General Description .................................................... 1

Inserted Figure 2; Renumbered Sequentially................................ 1

Changes to Table 1............................................................................ 3

Changes to Table 2............................................................................ 5

Changes to Table 6 and Layout....................................................... 8

Inserted Figure 6; Renumbered Sequentially................................ 8

Changes to Figure 30...................................................................... 12

Changes to Layout.......................................................................... 17

Changes to Figure 63...................................................................... 22

Changes to Exposed Paddle (EP) Section ...................................23

Updated Outline Dimensions....................................................... 24

Pin Configurations and Function Descriptions............................8

Typical Performance Characteristics ..............................................9

Test Circ uit s ................................................................................ 17

Theory of Operation ...................................................................... 18

Typical Connection and Definition of Terms ........................ 18

Applications..................................................................................... 19

Estimating Noise, Gain, and Bandwidth with Matched

Feedback Networks.................................................................... 19

Outline Dimensions .......................................................................24

Ordering Guide .......................................................................... 24

8/04—Rev. 0 to Rev. A.

Added 8-Lead LFCSP.........................................................Universal

Changes to General Description .....................................................1

Changes to Figure 2...........................................................................1

Changes to V

Changes to V

= ±5 V, V

S

= 5 V, V

S

= 0 V Specifications.........................3

OCM

= 2.5 V Specifications.........................5

OCM

Changes to Table 4.............................................................................7

Changes to Maximum Power Dissipation Section........................7

Changes to Figure 26 and Figure 29............................................. 12

Inserted Figure 39 and Figure 42.................................................. 14

Changes to Figure 45 to Figure 47................................................ 15

Inserted Figure 48........................................................................... 15

Changes to Figure 52 and Figure 53............................................. 16

Changes to Figure 55 and Figure 56............................................. 17

Changes to Table 6.......................................................................... 19

Changes to Voltage Gain Section ................................................. 19

Changes to Driving a Capacitive Load Section.......................... 22

Changes to Ordering Guide.......................................................... 24

Updated Outline Dimensions....................................................... 24

5/04—Revision 0: Initial Version

Rev. B | Page 2 of 24

AD8139

SPECIFICATIONS

VS = ±5 V, V

TA = 25°C, differential gain = 1, R

Table 1.

Parameter Conditions Min Typ Max Unit

DIFFERENTIAL INPUT PERFORMANCE

Dynamic Performance

−3 dB Small Signal Bandwidth V

−3 dB Large Signal Bandwidth V

Bandwidth for 0.1 dB Flatness V

Slew Rate V

Settling Time to 0.01% V

Overdrive Recovery Time G = 2, V

Noise/Harmonic Performance

SFDR V

V

V

Third-Order IMD V

Input Voltage Noise f = 100 kHz 2.25 nV/√Hz

Input Current Noise f = 100 kHz 2.1 pA/√Hz

DC Performance

Input Offset Voltage VIP = VIN = V

Input Offset Voltage Drift T

Input Bias Current T

Input Offset Current 0.12 0.5 μA

Open-Loop Gain 114 dB

Input Characteristics

Input Common-Mode Voltage Range −4 +4 V

Input Resistance Differential 600 kΩ

Common mode 1.5 MΩ

Input Capacitance Common mode 1.2 pF

CMRR ∆V

Output Characteristics

Output Voltage Swing Each single-ended output, RF = RG = 10 kΩ −VS + 0.20 +VS – 0.20 V

Output Current Each single-ended output 100 mA

Output Balance Error f = 1 MHz −69 dB

V

TO V

OCM

O, cm

V

Dynamic Performance

OCM

−3 dB Bandwidth V

Slew Rate V

Gain 0.999 1.000 1.001 V/V

V

Input Characteristics

OCM

Input Voltage Range −3.8 +3.8 V

Input Resistance 3.5 MΩ

Input Offset Voltage V

Input Voltage Noise f = 100 kHz 3.5 nV/√Hz

Input Bias Current 1.3 4.5 μA

CMRR ∆V

= 0 V

OCM

= 1 kΩ, RF = RG = 200 Ω, unless otherwise noted. T

L, dm

= 0.1 V p-p 340 410 MHz

O, dm

= 2 V p-p 210 240 MHz

O, dm

= 0.1 V p-p 45 MHz

O, dm

= 2 V step 800 V/μs

O, dm

= 2 V step, CF = 2 pF 45 ns

O, dm

= 12 V p-p triangle wave 30 ns

IN, dm

= 2 V p-p, fC = 1 MHz 98 dBc

O, dm

= 2 V p-p, fC = 5 MHz 85 dBc

O, dm

= 2 V p-p, fC = 20 MHz 72 dBc

O, dm

= 2 V p-p, fC = 10.05 MHz ± 0.05 MHz −90 dBc

O, dm

= 0 V

OCM

to T

MIN

MAX

to T

MIN

MAX

= ±1 V dc, RF = RG = 10 kΩ 80 84 dB

ICM

Each single-ended output,

= open circuit, RF = RG = 10 kΩ

R

L, dm

MIN

to T

= −40°C to +125°C.

MAX

−500 ±150 +500 μV

1.25 μV/°C

2.25 8.0 μA

+ 0.15 +VS − 0.15 V

−V

S

PERFORMANCE

= 0.1 V p-p 515 MHz

O, cm

= 2 V p-p 250 V/μs

O, cm

= V

− V

OS, cm

OCM

/∆V

O, cm

O, dm

; VIP = VIN = V

OCM

, ∆V

= ±1 V 74 88 dB

OCM

= 0 V −900 ±300 +900 μV

OCM

Rev. B | Page 3 of 24

AD8139

Parameter Conditions Min Typ Max Unit

POWER SUPPLY

Operating Range +4.5 ±6 V

Quiescent Current 24.5 25.5 mA

+PSRR Change in +VS = ±1 V 95 112 dB

−PSRR Change in −VS = ±1 V 95 109 dB

OPERATING TEMPERATURE RANGE −40 +125 °C

Rev. B | Page 4 of 24

AD8139

VS = 5 V, V

TA = 25°C, differential gain = 1, R

Table 2.

Parameter Conditions Min Typ Max Unit

DIFFERENTIAL INPUT PERFORMANCE

Dynamic Performance

−3 dB Small Signal Bandwidth V

−3 dB Large Signal Bandwidth V

Bandwidth for 0.1 dB Flatness V

Slew Rate V

Settling Time to 0.01% V

Overdrive Recovery Time G = 2, V

Noise/Harmonic Performance

SFDR V

V

V

Third-Order IMD V

Input Voltage Noise f = 100 kHz 2.25 nV/√Hz

Input Current Noise f = 100 kHz 2.1 pA/√Hz

DC Performance

Input Offset Voltage VIP = VIN = V

Input Offset Voltage Drift T

Input Bias Current T

Input Offset Current 0.13 0.5 μA

Open-Loop Gain 112 dB

Input Characteristics

Input Common-Mode Voltage Range 1 4 V

Input Resistance Differential 600 kΩ

Common mode 1.5 MΩ

Input Capacitance Common mode 1.2 pF

CMRR ΔV

Output Characteristics

Output Voltage Swing Each single-ended output, RF = RG = 10 kΩ −VS + 0.15 +VS − 0.15 V

Output Current Each single-ended output 80 mA

Output Balance Error f = 1 MHz −70 dB

V

TO V

OCM

V

Dynamic Performance

OCM

−3 dB Bandwidth V

Slew Rate V

Gain 0.999 1.000 1.001 V/V

V

Input Characteristics

OCM

Input Voltage Range 1.0 3.8 V

Input Resistance 3.5 MΩ

Input Offset Voltage V

Input Voltage Noise f = 100 kHz 3.5 nV/√Hz

Input Bias Current 1.3 4.2 μA

CMRR ΔV

= 2.5 V

OCM

= 1 kΩ, RF = RG = 200 Ω, unless otherwise noted. T

L, dm

= 0.1 V p-p 330 385 MHz

O, dm

= 2 V p-p 135 165 MHz

O, dm

= 0.1 V p-p 34 MHz

O, dm

= 2 V step 540 V/μs

O, dm

= 2 V step 55 ns

O, dm

= 7 V p-p triangle wave 35 ns

IN, dm

= 2 V p-p, fC = 1 MHz 99 dBc

O, dm

= 2 V p-p, fC = 5 MHz, RL = 800 Ω 87 dBc

O, dm

= 2 V p-p, fC = 20 MHz, RL = 800 Ω 75 dBc

O, dm

= 2 V p-p, fC = 10.05 MHz ± 0.05 MHz −87 dBc

O, dm

= 2.5 V

OCM

to T

MIN

MAX

to T

MIN

MAX

= ±1 V dc, RF = RG = 10 kΩ 75 79 dB

ICM

Each single-ended output,

= open circuit, RF = RG = 10 kΩ

R

L, dm

PERFORMANCE

O, cm

= 0.1 V p-p 440 MHz

O, cm

= 2 V p-p 150 V/μs

O, cm

= V

− V

OS, cm

OCM

/ΔV

O, cm

O, dm

; VIP = VIN = V

OCM

, ΔV

= ±1 V 67 79 dB

OCM

= 2.5 V −1.0 ±0.45 +1.0 mV

OCM

MIN

to T

= −40°C to +125°C.

MAX

−500 ±150 +500 μV

1.25 μV/°C

2.2 7.5 μA

+ 0.10 +VS − 0.10 V

−V

S

Rev. B | Page 5 of 24

AD8139

Parameter Conditions Min Typ Max Unit

POWER SUPPLY

Operating Range +4.5 ±6 V

Quiescent Current 21.5 22.5 mA

+PSRR Change in +VS = ±1 V 86 97 dB

−PSRR Change in −VS = ±1 V 92 105 dB

OPERATING TEMPERATURE RANGE −40 +125 °C

Rev. B | Page 6 of 24

AD8139

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage 12 V

V

OCM

±V

S

Power Dissipation See Figure 4

Input Common-Mode Voltage ±V

S

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +125°C

Lead Temperature (Soldering 10 sec) 300°C

Junction Temperature 150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

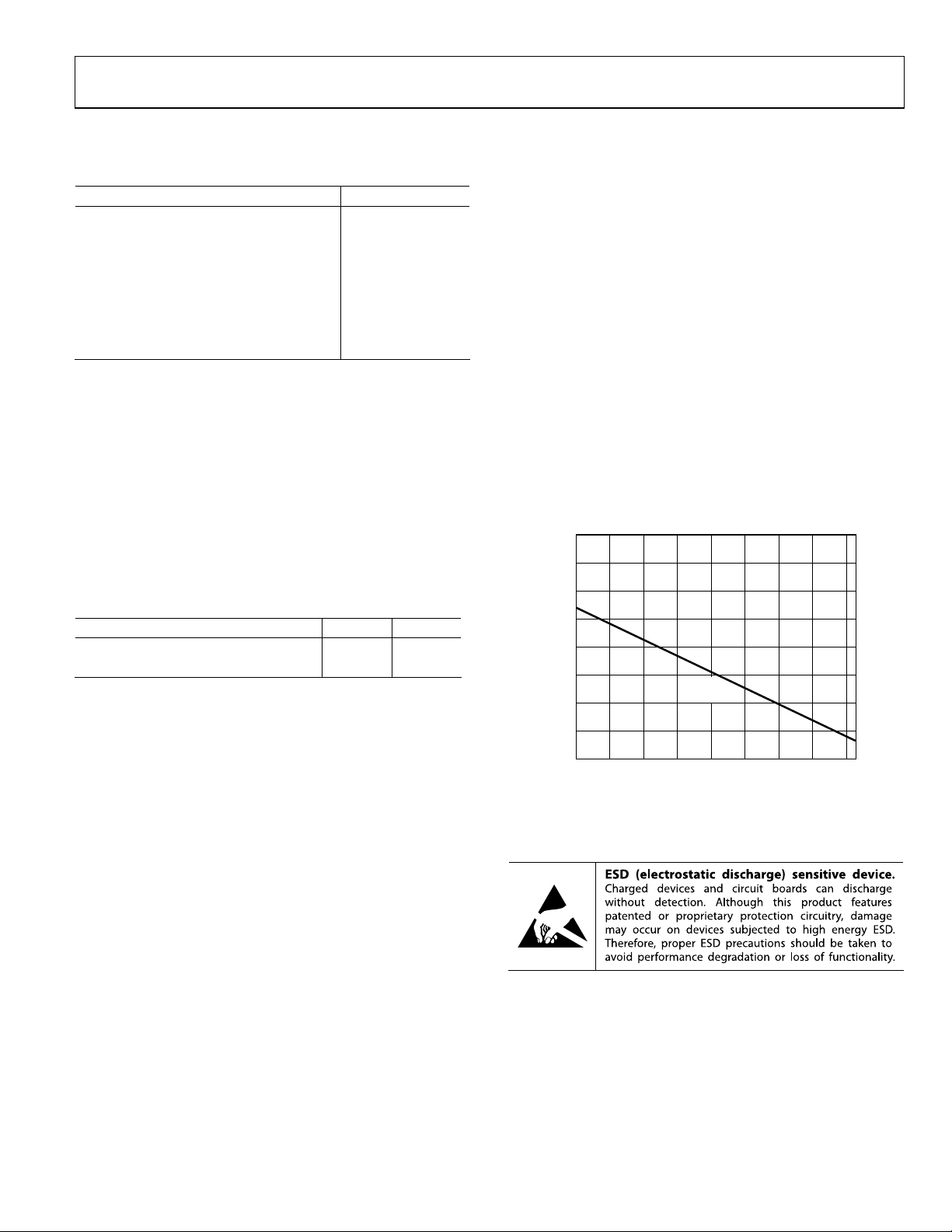

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, θJA is

specified for device soldered in circuit board for surface-mount

The power dissipated in the package (P

quiescent power dissipation and the power dissipated in the

package due to the load drive for all outputs. The quiescent

power is the voltage between the supply pins (V

quiescent current (I

and common-mode currents flowing to the load, as well as

currents flowing through the external feedback networks and

the internal common-mode feedback loop. The internal resistor

tap used in the common-mode feedback loop places a 1 kΩ

differential load on the output. RMS output voltages should be

considered when dealing with ac signals.

Airflow reduces θ

with the package leads from metal traces, through holes,

ground, and power planes reduce the θ

Figure 4 shows the maximum safe power dissipation in the

package vs. the ambient temperature for the exposed paddle

(EP) 8-lead SOIC (θ

(θ

= 70°C/W) on a JEDEC standard 4-layer board. θJA values

JA

are approximations.

4.0

3.5

packages.

3.0

Table 4.

Package Type θ

JA

Unit

8-Lead SOIC with EP/4-Layer 70 °C/W

8-Lead LFCSP/4-Layer 70 °C/W

Maximum Power Dissipation

The maximum safe power dissipation in the AD8139 package

is limited by the associated rise in junction temperature (T

) on

J

the die. At approximately 150°C, which is the glass transition

2.5

2.0

1.5

1.0

MAXIMUM POWER DISSIPATION (W )

0.5

0

–40 –20 0 20 40 60 80 100 120

temperature, the plastic will change its properties. Even

temporarily exceeding this temperature limit can change the

stresses that the package exerts on the die, permanently shifting

the parametric performance of the AD8139. Exceeding a junction

temperature of 175°C for an extended period can result in

Figure 4. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

ESD CAUTION

changes in the silicon devices potentially causing failure.

). The load current consists of differential

S

. In addition, more metal directly in contact

JA

= 70°C/W) and the 8-lead LFCSP

JA

SOIC

AND LFCSP

AMBIENT TEMPERATURE (°C)

) is the sum of the

D

) times the

S

.

JA

4679-055

Rev. B | Page 7 of 24

AD8139

+OUT

A

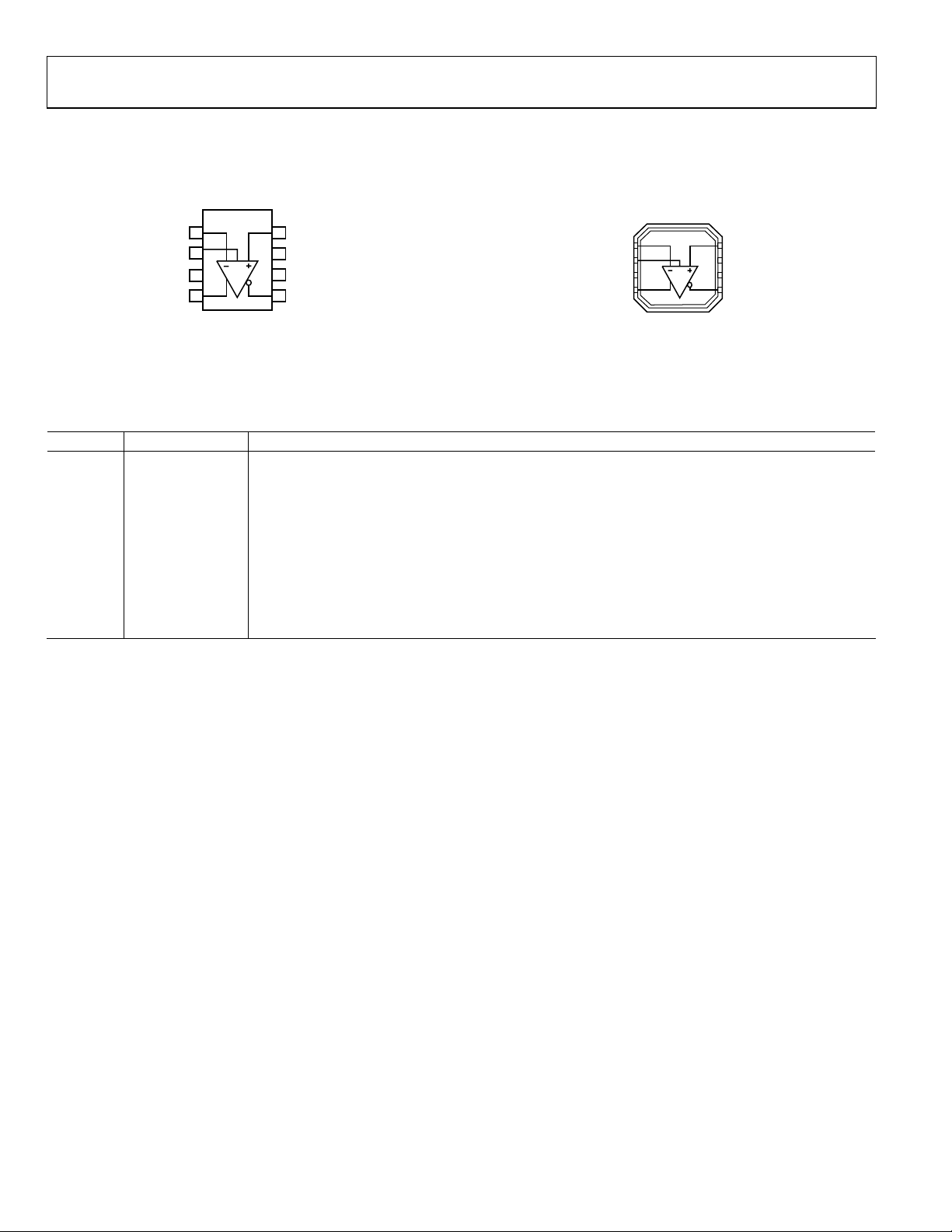

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

D8139

TOP VIEW

AD8139

–IN

1

2

V

OCM

V+

3

+OUT

4

NC = NO CONNECT

Figure 5. 8-Lead SOIC Pin Configuration

+IN

8

NC

7

V–

6

–OUT

5

04679-003

OCM

Figure 6. 8-Lead LFCSP Pin Configuration

Table 5. Pin Function Descriptions

Pin No. Mnemonic Description

1 −IN Inverting Input.

2 V

OCM

An internal feedback loop drives the output common-mode voltage to be equal to the voltage applied to

the V

pin, provided the operation of the amplifier remains linear.

OCM

3 V+ Positive Power Supply Voltage.

4 +OUT Positive Side of the Differential Output.

5 −OUT Negative Side of the Differential Output.

6 V− Negative Power Supply Voltage.

7 NC No Internal Connection.

8 +IN Noninverting Input.

9 Exposed Paddle Solder exposed paddle on back of package to ground plane or to a power plane.

(Not to Scale)

1–IN

2V

3V+

4

NC = NO CONNECT

8+IN

7NC

6V–

5–OUT

04679-103

Rev. B | Page 8 of 24

Loading...

Loading...