ANALOG DEVICES AD7870, AD7875, AD7876 Service Manual

LC2MOS Complete,

V

V

FEATURES

Complete monolithic 12-bit ADCs with

2 μs track-and-hold amplifier

8 μs ADC

On-chip reference

Laser-trimmed clock

Parallel, byte, and serial digital interface

72 dB SNR at 10 kHz input frequency

(AD7870, AD7875)

57 ns data access time

Low power: −60 mW typical

Variety of input ranges

±3 V for AD7870

0 V to +5 V for AD7875

±10 V for AD7876

12-Bit, 100 kHz, Sampling ADCs

AD7870/AD7875/AD7876

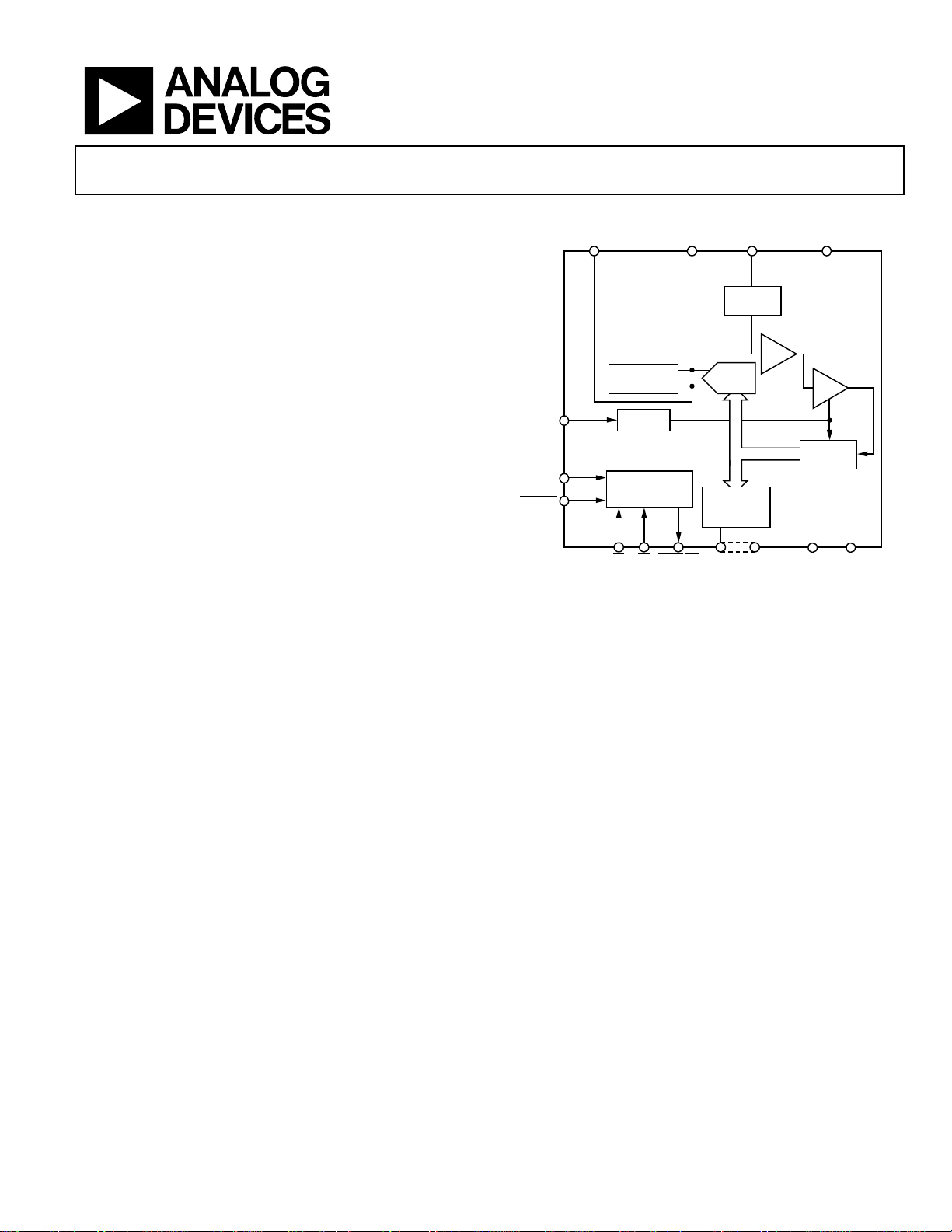

FUNCTIONAL BLOCK DIAGRAM

3V

CLOCK

REF OUT

Figure 1.

IN

INPUT

SCALING

12-BIT

DAC

PARALLEL

AND SERIAL

INTERFACE

DB11 DB0CS RD BUSY/INT

DD

AD7870/AD7875/

AD7876

TRACK-AND-HOLD

COMP

SAR +

COUNTER

DGND

V

SS

07730-001

CLK

12/8/CLK

CONVST

AGND

REFERENCE

CONTROL LO GIC

GENERAL DESCRIPTION

The AD7870/AD7875/AD7876 are fast, complete, 12-bit

analog-to-digital converters (ADCs). These converters consist

of a track-and-hold amplifier, an 8 μs successive approximation

ADC, a 3 V buried Zener reference, and versatile interface logic.

The ADCs feature a self-contained internal clock which is laser

trimmed to guarantee accurate control of conversion time. No

external clock timing components are required; the on-chip

clock may be overridden by an external clock if required.

The parts offer a choice of three data output formats: a single,

parallel, 12-bit word; two 8-bit bytes or serial data. Fast bus

access times and standard control inputs ensure easy interfacing

to modern microprocessors and digital signal processors.

All parts operate from ±5 V power supplies. The AD7870 and

AD7876 accept input signal ranges of ±3 V and ±10 V, respectively, while the AD7875 accepts a unipolar 0 V to +5 V input

range. The parts can convert full power signals up to 50 kHz.

The AD7870/AD7875/AD7876 feature dc accuracy specifications, such as linearity, full-scale and offset error. In addition,

the AD7870 and AD7875 are fully specified for dynamic

performance parameters including distortion and signal-tonoise ratio.

The parts are available in a 24-pin, 0.3 inch-wide, plastic or

hermetic dual-in-line package (DIP). The AD7870 and AD7875

are available in a 28-pin plastic leaded chip carrier (PLCC),

while the AD7876 is available and in a 24-pin small outline

(SOIC) package.

PRODUCT HIGHLIGHTS

1. Complete 12-bit ADC on a chip.

The AD7870/AD7875/AD7876 provide all the functions

necessary for analog-to-digital conversion and combine a

12-bit ADC with internal clock, track-and-hold amplifier

and reference on a single chip.

2. Dynamic specifications for DSP users.

The AD7870 and AD7875 are fully specified and tested for

ac parameters, including signal-to-noise ratio, harmonic

distortion and intermodulation distortion.

3. Fast microprocessor interface.

Data access times of 57 ns make the parts compatible with

modern 8-bit and 16-bit microprocessors and digital signal

processors. Key digital timing parameters are tested and

guaranteed over the full operating temperature range.

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©1997–2009 Analog Devices, Inc. All rights reserved.

AD7870/AD7875/AD7876

TABLE OF CONTENTS

Features .............................................................................................. 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

AD7870 Specifications ................................................................. 3

AD7875/AD7876 Specifications ................................................. 4

Timing Characteristics ................................................................ 6

Absolute Maximum Ratings ............................................................ 7

ESD Caution .................................................................................. 7

Pin Configurations and Function Descriptions ........................... 8

Load Circuits ................................................................................... 10

Converter Details ............................................................................ 11

Internal Reference ...................................................................... 11

Track-and-Hold Amplifier ........................................................ 11

Analog Input ............................................................................... 11

Offset And Full-Scale Adjustment—AD7870 ........................ 12

Offset And Full-Scale Adjustment—AD7876 ........................ 13

Offset And Full-Scale Adjustment—AD7875 ........................ 13

Timing and Control ....................................................................... 14

Data Output Formats ................................................................. 14

Mode 1 Interface ......................................................................... 14

Mode 2 Interface ......................................................................... 15

Dynamic Specifications ............................................................. 16

Microprocessor Interface ............................................................... 19

Parallel Read Interfacing ........................................................... 19

Two-Byte Read Interfacing ....................................................... 19

Serial Interfacing ........................................................................ 20

Standalone Operation ................................................................ 21

Applications Information .............................................................. 22

Layout Hints ................................................................................ 22

Noise ............................................................................................ 22

Outline Dimensions ....................................................................... 23

Ordering Guide .......................................................................... 25

REVISION HISTORY

2/09—Rev. B to Rev. C

Updated Format .................................................................. Universal

Reorganized Layout ............................................................ Universal

Deleted S Version ................................................................ Universal

Changes to Internal Clock Parameter, Table 1 and

Added Endnote to Table 1 ............................................................... 4

Changes to Internal Clock Parameter, Table 2 .............................. 5

Changes to Mode 1 Interface Section .......................................... 14

Deleted Data Acquisition Board and Interface Connections

Sections and Figure 26 ................................................................... 15

Deleted Figure 27 and Power Supply Connections, Shorting

Plug Options and Components List Sections ............................. 16

Deleted Figure 28 and Figure 29 ................................................... 17

Deleted Figure 30 and Figure 31 ................................................... 18

Updated Outline Dimensions ....................................................... 23

Changes to Ordering Guide .......................................................... 25

Rev. C | Page 2 of 28

AD7870/AD7875/AD7876

SPECIFICATIONS

VDD = +5 V ± 5%, VSS = −5 V ± 5%, AGND = DGND = 0 V, f

T

, unless otherwise noted.

max

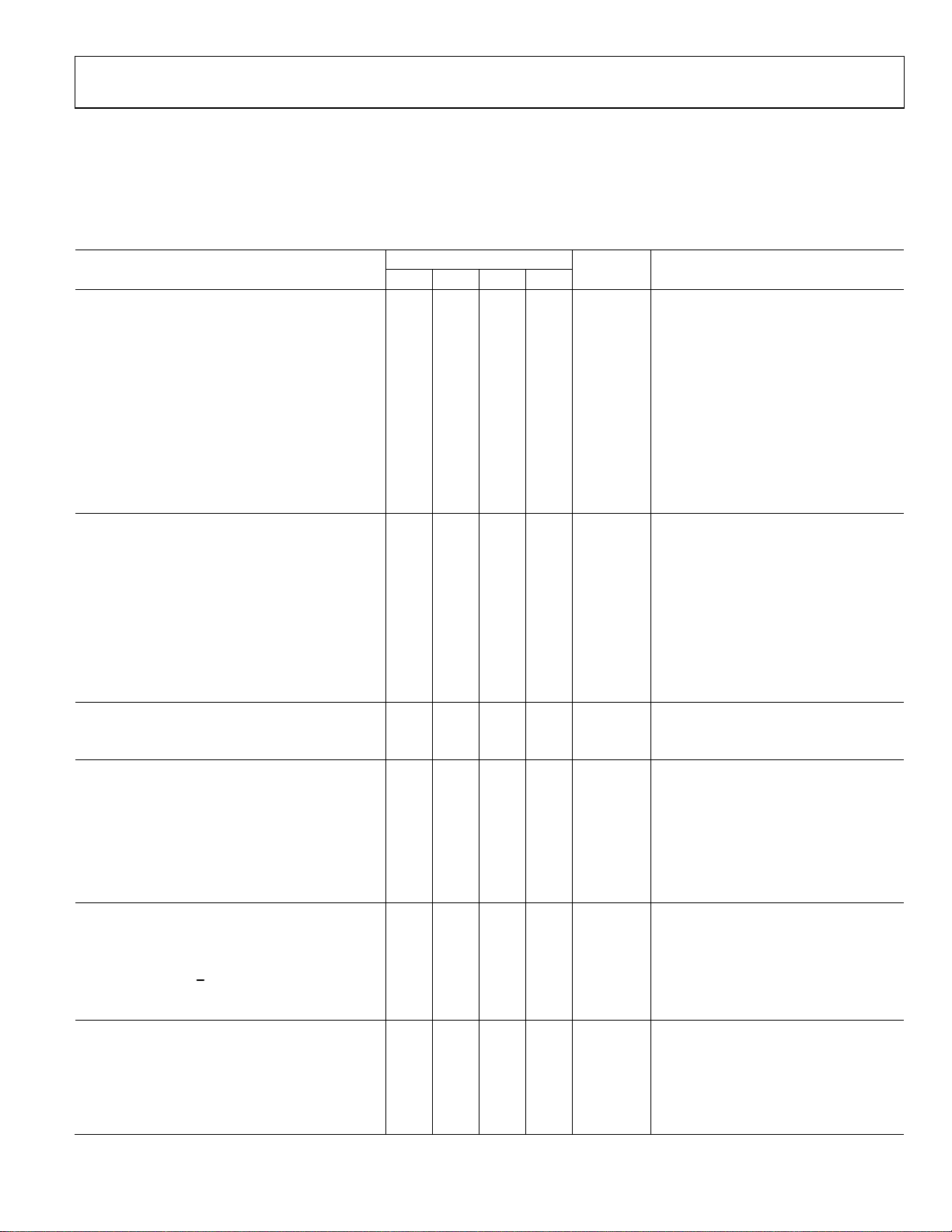

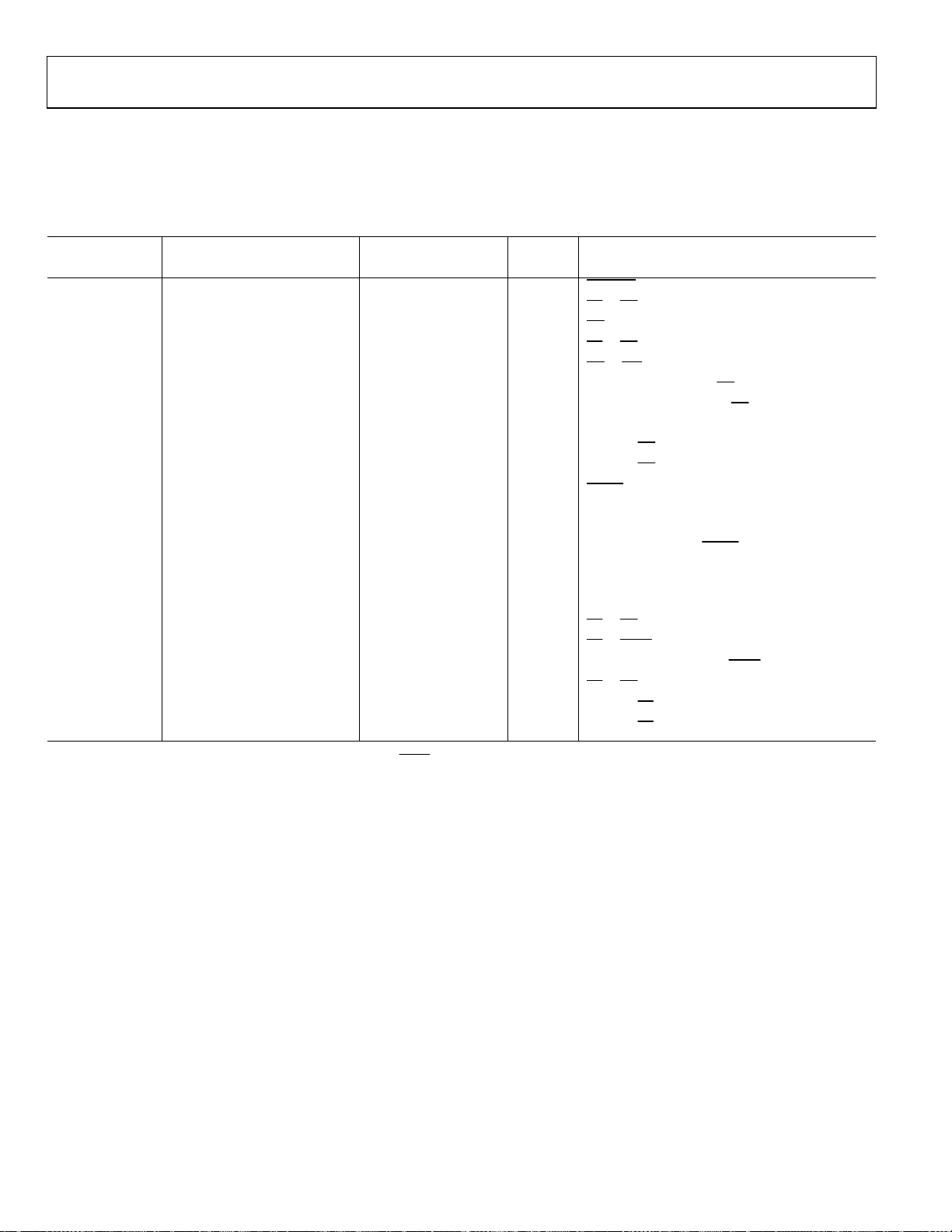

AD7870 SPECIFICATIONS

= 2.5 MHz external, unless otherwise stated. All Specifications T

CLK

min

to

Table 1.

ADN7870

1

Parameter J, A K, B L, C T Units Test Conditions/Comments

DYNAMIC PERFORMANCE2

Signal-to-Noise Ratio3 (SNR)

@ +25°C 70 70 72 69 dB min VIN = 10 kHz sine wave, f

T

to T

MIN

Total Harmonic Distortion (THD) −80 −80 −80 −78 dB max

70 70 71 69 dB min Typically 71.5 dB for 0 < VIN < 50 kHz

MAX

= 10 kHz sine wave, f

V

IN

Typically −86 dB for 0 < V

Peak Harmonic or Spurious Noise −80 −80 −80 −78 dB max

= 10 kHz, f

V

IN

SAMPLE

Typically −86 dB for 0 < V

SAMPLE

SAMPLE

< 50 kHz

IN

= 100 kHz

< 50 kHz

IN

Intermodulation Distortion (IMD)

Second Order Terms −80 −80 −80 −78 dB max fa = 9 kHz, fb = 9.5 kHz, f

Third Order Terms −80 −80 −80 −78 dB max fa = 9 kHz, fb = 9.5 kHz, f

SAMPLE

SAMPLE

Track-and-Hold Acquisition Time 2 2 2 2 μs max

DC ACCURACY

Resolution 12 12 12 12 Bits

Minimum Resolution for which No Missing Codes

12 12 12 12 Bits

are Guaranteed

Integral Nonlinearity ±1/2 ±1/2 ±1/4 ±1/2 LSB typ

Integral Nonlinearity ±1 ±1/2 ±1 LSB max

Differential Nonlinearity ±1 ±1 ±1 LSB max

Bipolar Zero Error ±5 ±5 ±5 ±5 LSB max

Positive Full-Scale Error4 ±5 ±5 ±5 ±5 LSB max

Negative Full-Scale Error4 ±5 ±5 ±5 ±5 LSB max

ANALOG INPUT

Input Voltage Range ±3 ±3 ±3 ±3 V

Input Current ±500 ±500 ±500 ±500 μA max

REFERENCE OUTPUT

REF OUT @ +25°C 2.99 2.99 2.99 2.99 V min

3.01 3.01 3.01 3.01 V max

REF OUT Tempco ±60 ±60 ±35 ±35

ppm/°C

max

Reference Load Sensitivity

(ΔREF OUT/ΔI)

±1 ±1 ±1 ±1 mV max

Reference load current change (0 μA to

500 μA). Reference load should not be

changed during conversion.

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

2.4 2.4 2.4 2.4 V min VDD = 5 V ± 5%

INH

0.8 0.8 0.8 0.8 V max VDD = 5 V ± 5%

INL

Input Current, IIN ±10 ±10 ±10 ±10 μA max VIN = 0 V to VDD

Input Current (12/8/CLK Input Only)

Input Capacitance, C

5

IN

±10 ±10 ±10 ±10 μA max V

10 10 10 10 pF max

= VSS to VDD

IN

LOGIC OUTPUTS

Output High Voltage, VOH 4.0 4.0 4.0 4.0 V min I

Output Low Voltage, VOL 0.4 0.4 0.4 0.4 V max I

= 40 μA

SOURCE

= 1.6 mA

SINK

DB11 to DB0

Floating-State Leakage Current ±10 ±10 ±10 ±10 μA max

Floating-State Output Capacitance

5

15 15 15 15 pF max

= 100 kHz

= 100 kHz

= 50 kHz

= 50 kHz

Rev. C | Page 3 of 28

AD7870/AD7875/AD7876

ADN7870

1

Parameter J, A K, B L, C T Units Test Conditions/Comments

CONVERSION TIME

External Clock (f

Internal Clock

= 2.5 MHz) 8 8 8 8 μs max

CLK

6

6.5/9 6.5/9 6.5/9 6.5/9

μs min/

μs max

POWER REQUIREMENTS

VDD +5 +5 +5 +5 V nom ±5% for specified performance

VSS −5 −5 −5 −5 V nom ±5% for specified performance

IDD 13 13 13 13 mA max Typically 8 mA

ISS 6 6 6 6 mA max Typically 4 mA

Power Dissipation 95 95 95 95 mW max Typically 60 mW

1

The temperature range for the J, K, and L versions is from 0°C to +70°C; for the A, B, and C versions is−40°C to +85°C; and for the T version is −55°C to +125°C.

2

VIN (p-p) = ±3 V.

3

SNR calculation includes distortion and noise components.

4

Measured with respect to internal reference and includes bipolar offset error.

5

Sample tested @ +25°C to ensure compliance.

6

Conversion time specification for the AD7870A device with internal clock used is 8 μs/10 μs minimum/maximum.

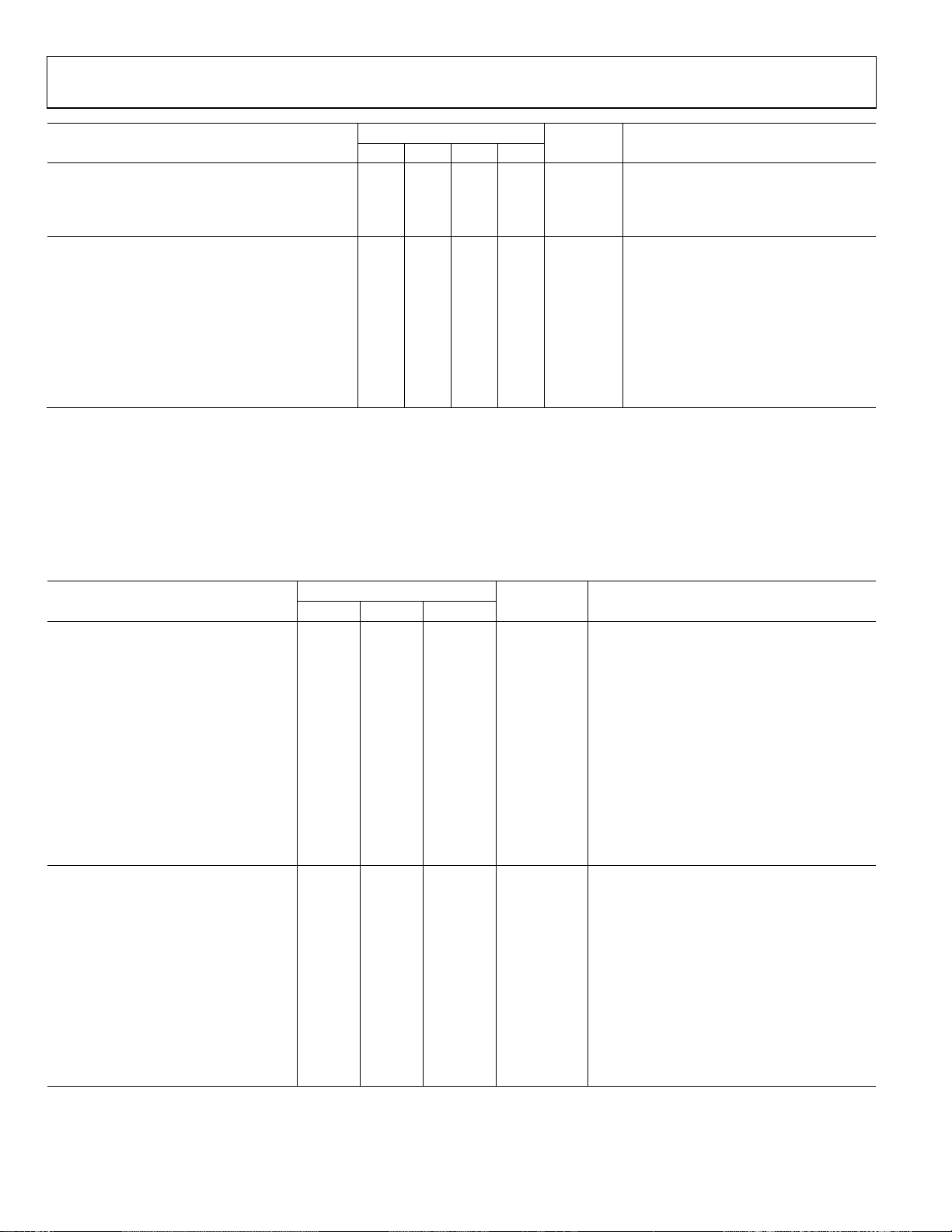

AD7875/AD7876 SPECIFICATIONS

Table 2.

AD7875/AD7876

Parameter

1

Units Test Conditions/Comments K, B L, C T

DC ACCURACY

Resolution 12 12 12 Bits

Min Resolution for which No Missing

12 12 12 Bits

Codes Are Guaranteed

Integral Nonlinearity @ +25°C ±1 ±1/2 ±1 LSB max

T

to T

MIN

T

MIN

(AD7875 Only) ±1 ±1 ±1 LSB max

MAX

to T

(AD7876 Only) ±1 ±1/2 ±1 LSB max

MAX

Differential Nonlinearity ±1 ±1 ±1.5/−1.0 LSB max

Unipolar Offset Error (AD7875 Only) ±5 ±5 ±5 LSB max

Bipolar Zero Error (AD7876 Only) ±6 ±2 ±6 LSB max

Full-Scale Error at +25°C2 ±8 ±8 ±8 LSB max Typical full-scale error is ±1 LSB

Full-Scale TC2 ±60 ±35 ±60 ppm/°C max Typical TC is ±20 ppm/°C

Track-and-Hold Acquisition Time 2 2 2 μs max

DYNAMIC PERFORMANCE3 (AD7875

ONLY)

Signal-to-Noise Ratio4 (SNR)

@ +25°C 70 72 69 dB min VIN = 10 kHz sine wave, f

T

to T

MIN

Total Harmonic Distortion (THD) −80 −80 −78 dB max

70 71 69 dB min Typically 71.5 dB for 0 < VIN < 50 kHz

MAX

= 10 kHz sine wave, f

V

IN

Typically −86 dB for 0 < V

Peak Harmonic or Spurious Noise −80 −80 −78 dB max

= 10 kHz, f

V

IN

SAMPLE

Typically −86 dB for 0 < V

SAMPLE

SAMPLE

IN

= 100 kHz

IN

Intermodulation Distortion (IMD)

Second Order Terms −80 −80 −78 dB max fa = 9 kHz, fb = 9.5 kHz, f

Third Order Terms −80 −80 −78 dB max fa = 9 kHz, fb = 9.5 kHz, f

SAMPLE

SAMPLE

= 100 kHz

= 100 kHz

< 50 kHz

< 50 kHz

= 50 kHz

= 50 kHz

Rev. C | Page 4 of 28

AD7870/AD7875/AD7876

AD7875/AD7876

Parameter

1

Units Test Conditions/Comments K, B L, C T

ANALOG INPUT

AD7875 Input Voltage Range 0 to +5 0 to +5 0 to +5 V

AD7875 Input Current 500 500 500 μA max

AD7876 Input Voltage Range ±10 ±10 ±10 V

AD7876 Input Current

±600 ±600 ±600 μA max

REFERENCE OUTPUT

REF OUT @ +25°C 2.99 2.99 2.99 V min

3.01 3.01 3.01 V max

REF OUT Tempco ±60 ±35 ±60 ppm/°C max Typical tempco Is ±20 ppm/°C

Reference Load Sensitivity

(ΔREF OUT/ΔI)

−1 −1 −1 mV max

Reference load current change (0 μA to 500 μA).

Reference load should not be changed during

conversion.

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

2.4 2.4 2.4 V min VDD = 5 V ± 5%

INH

0.8 0.8 0.8 V max VDD = 5 V ± 5%

INL

Input Current, IIN ±10 ±10 ±10 μA max VIN = 0 V to VDD

Input Current (12/8/CLK Input Only)

Input Capacitance, C

5

IN

±10 ±10 ±10 μA max V

10 10 10 pF max

= VSS to VDD

IN

LOGIC OUTPUTS

Output High Voltage, VOH 4.0 4.0 4.0 V min I

Output Low Voltage, VOL 0.4 0.4 0.4 V max I

= 40 mA

SOURCE

= 1.6 mA

SINK

DB11–DB0

Floating-State Leakage Current 10 10 10 μA max

Floating-State Output

Capacitance

5

15 15 15 pF max

CONVERSION TIME

External Clock (f

Internal Clock 6.5/9 6.5/9 6.5/9

= 2.5 MHz) 8 8 8 μs max

CLK

μs min/μs

max

POWER REQUIREMENTS As per AD7870

1

For the AD7875, the temperature range for the K and L versions is from 0°C to +70°C; for the B and C versions is−40°C to +85°C; and for the T version is −55°C to

+125°C. For the AD7876, the temperature range for the B and C versions is from −40°C to +85°C and for the T version is−55°C to +125°C.

2

Includes internal reference error and is calculated after unipolar offset error (AD7875) or bipolar zero error (AD7876) has been adjusted out. Full-scale error refers to

both positive and negative full-scale error for the AD7876.

3

Dynamic performance parameters are not tested on the AD7876, but these are typically the same as for the AD7875.

4

SNR calculation includes distortion and noise components.

5

Sample tested @ +25°C to ensure compliance.

Refer to the power requirements in Table 1.

Rev. C | Page 5 of 28

AD7870/AD7875/AD7876

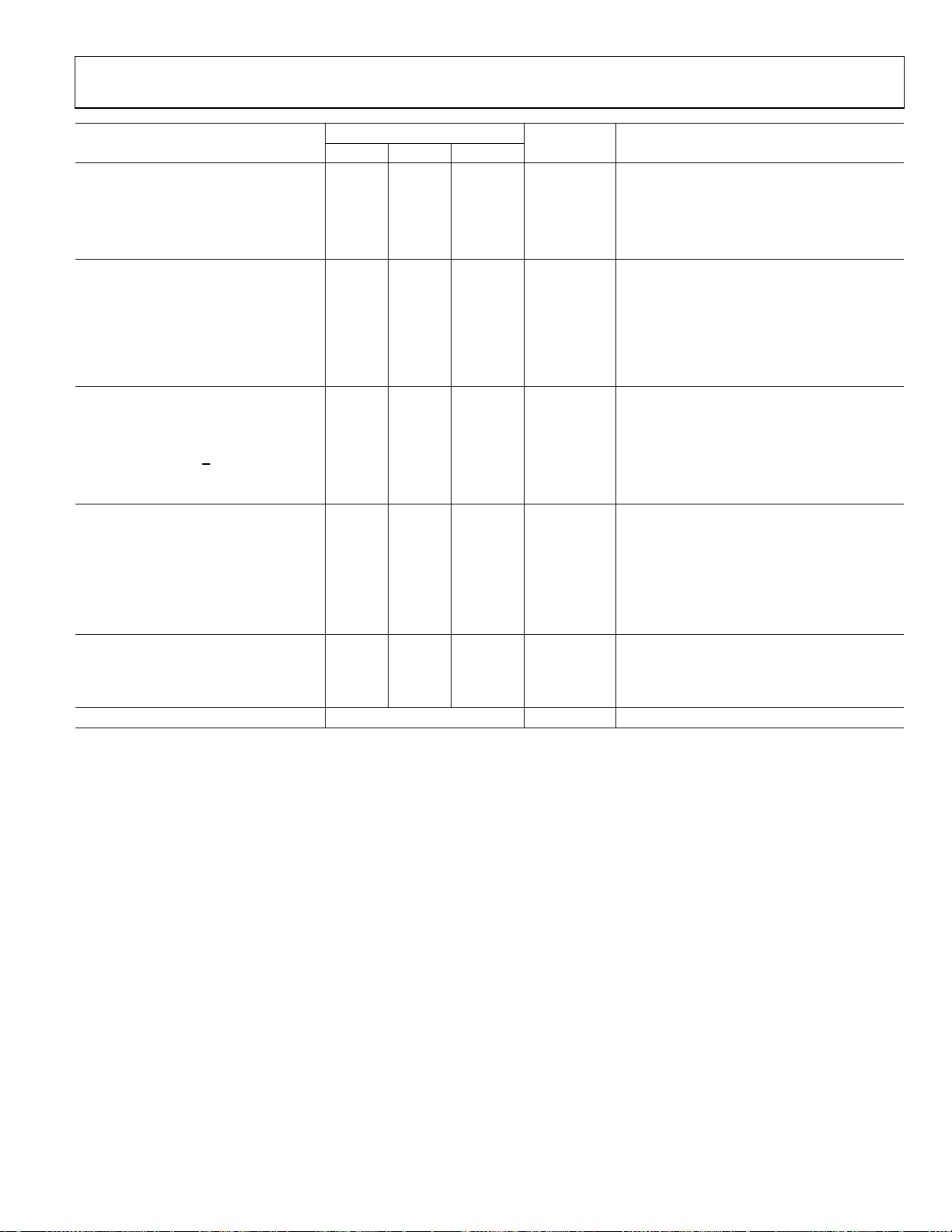

TIMING CHARACTERISTICS

VDD = +5 V ± 5%, VSS = −5 V ± 5%, AGND = DGND = 0 V. See Figure 14, Figure 15, Figure 16, and Figure 17. Timing specifications are

sample tested at 25°C to ensure compliance, unless otherwise noted. All input signals are specified with t

and timed from a voltage level of 1.6 V.

Table 3.

Parameter

t1

t2

2

t

3

t4

t5

2, 3

t

6

4

t

72,

t8

t9

t10

5

t

11

6

t

12

t13

1

Limit at T

(J, K, L, A, B, C Versions)

50 50 ns min

0 0 ns min

60 75 ns min

0 0 ns min

70 70

57 70 ns max

5 5 ns min

50 50

0 0 ns min

0 0 ns min

100 100 ns min

370 370 ns min SCLK cycle time

135 150 ns max SCLK to valid data delay. CL = 35 pF

20 20 ns min

MIN

, T

MAX

Limit at T

MIN

, T

MAX

(T Version) Units Conditions/Comments

CONVST

to RD setup time (Mode 1)

CS

pulse width

RD

to RD hold time (Mode 1)

CS

to INT delay

ns max

RD

Data access time after RD

Bus relinquish time after RD

ns max

HBEN to RD setup time

HBEN to RD

to SCLK falling edge setup time

SSTRB

SCLK rising edge to SSTRB

100 100 ns max

t14 10 10 ns min Bus relinquish time after SCLK

100 100 ns max

to RD setup time (Mode 2)

t15

t16

t17

t18

t19

t20

1

Serial timing is measured with a 4.7 kΩ pull-up resistor on SDATA and

2

Timing specifications for t3, t6, and for the maximum limit at t7 are 100% production tested.

3

t6 is measured with the load circuits of Figure 4 and defined as the time required for an output to cross 0.8 V or 2.4 V.

4

t7 is defined as the time required for the data lines to change 0.5 V when loaded with the circuits of Figure 5.

5

SCLK mark/space ratio (measured from a voltage level of 1.6 V) is 40/60 to 60/40.

6

SDATA will drive higher capacitive loads but this will add to t12 since it increases the external RC time constant (4.7 kΩ||CL) and thus the time to reach 2.4 V.

60 60 ns min

120 120

ns max

200 200 ns min

0 0 ns min

0 0 ns min

0 0 ns min

SSTRB

and a 2 kΩ pull-up on SCLK. The capacitance on all three outputs is 35 pF.

CS

CS

to BUSY propagation delay

Data setup time prior to BUSY

to RD hold time (Mode 2)

CS

HBEN to CS

HBEN to CS

= tf = 5 ns (10% to 90% of 5 V)

r

pulse width

hold time

setup time

hold time

Rev. C | Page 6 of 28

AD7870/AD7875/AD7876

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

VDD to AGND −0.3 V to +7 V

VSS to AGND +0.3 V to −7 V

AGND to DGND −0.3 V to VDD +0.3 V

VIN to AGND −15 V to +15 V

REF OUT to AGND 0 V to VDD

Digital Inputs to DGND −0.3 V to VDD +0.3 V

Digital Outputs to DGND −0.3 V to VDD +0.3 V

Operating Temperature Range

Commercial (J, K, L Versions–AD7870) 0°C to +70°C

Commercial (K, L Versions–AD7875) 0°C to +70°C

Industrial (A, B, C Versions–AD7870) −25°C to +85°C

Industrial (B, C Versions–AD7875/

AD7876)

Extended (T Version) −55°C to +125°C

Storage Temperature Range −65°C to +150°C

Lead Temperature (Soldering, 10 sec) +300°C

Power Dissipation (Any Package) to +75°C 450 mW

Derates above +75°C by 10 mW/°C

−40°C to +85°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. C | Page 7 of 28

AD7870/AD7875/AD7876

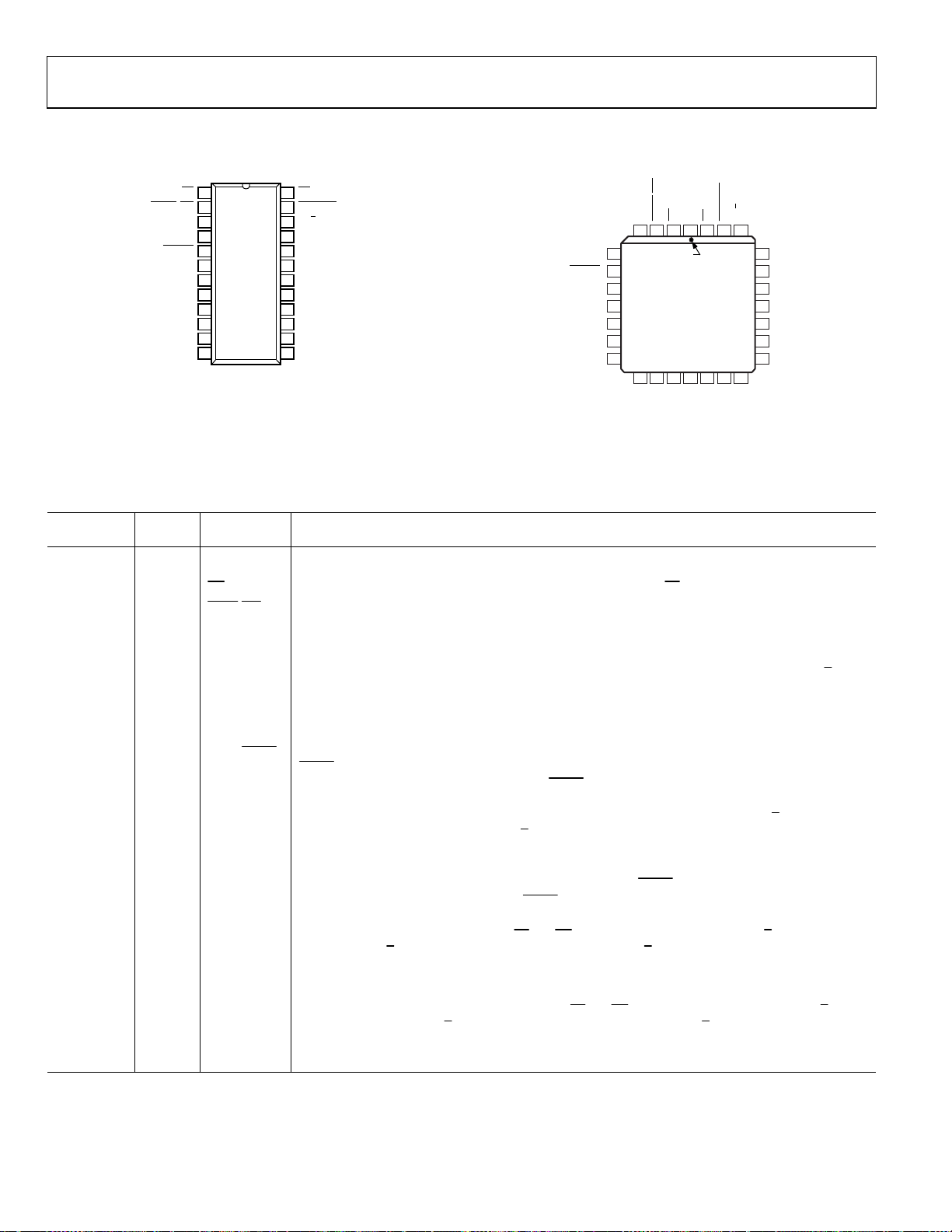

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

RD

1

CLK

DGND

2

AD7870/

3

AD7875/

4

AD7876

5

6

TOP VIEW

7

(Not to Scale)

8

9

10

11

12

BUSY/INT

DB11/HBEN

DB10/SSTRB

DB9/SCLK

DB8/SDATA

DB7/LOW

DB6/LOW

DB5/LOW

DB4/LOW

Figure 2. DIP and SOIC Pin Configuration

Table 5. Pin Function Descriptions

DIP and SOIC

Pin No.

N/A 1, 8, 15,

1 2

2 3

3 4 CLK

4 5 DB11/HBEN

5 6

6 7 DB9/SCLK

7 9 DB8/SDATA

8 to11 10 to 13 DB7/LOW–

12 14 DGND Digital Ground. Ground reference for digital circuitry.

13 to 16 16 to 19 DB3/DB11–

17 20 VDD Positive Supply, +5 V ± 5%.

PLCC

Pin No. Mnemonic Function

NC No Connect.

22

RD

Read. Active low logic input. This input is used in conjunction with CS low to enable the data outputs.

BUSY

INT

/

SSTRB

DB10/

DB4/LOW

DB0/DB8

CS

24

23

CONVST

12/8/CLK

22

V

21

20

V

REF OUT

19

AGND

18

17

V

DB0/DB8

16

DB1/DB9

15

14

DB2/DB10

DB3/DB11

13

SS

IN

DD

07730-004

DB11/HBEN

DB10/SSTRB

DB9/SCLK

NC

DB8/SDATA

DB7/LO W

DB6/LO W

CLK

BUSY/INTRDNCCSCONVST

5

6

7

8

9

10

11

PIN 1

INDENTFIER

AD7870/AD7875/

AD7876

TOP VIEW

(Not to Scale)

12 13 14 15 16 17 18

DGND

DB5/LOW

DB4/LOW

NC = NO CONNECT

1282726234

NC

12/8/CLK

25

V

24

V

23

REF OUT

22

NC

21

AGND

20

V

DB0/DB8

19

DB1/DB9

DB3/DB 11

DB2/DB10

Figure 3. PLCC Pin Configuration

Busy/Interrupt. Active low logic output indicating converter status. See Figure 14, Figure 15, Figure 16,

and Figure 17.

Clock Input. An external TTL-compatible clock may be applied to this input pin. Alternatively, tying this

pin to V

enables the internal laser-trimmed clock oscillator.

SS

Data Bit 11 (MSB)/High Byte Enable. The function of this pin is dependent on the state of the 12/

input. When 12-bit parallel data is selected, this pin provides the DB11 output. When byte data is

selected, this pin becomes the HBEN logic input. HBEN is used for 8-bit bus interfacing. When HBEN is

low, DB7/LOW to DB0/DB8 become DB7 to DB0. With HBEN high, DB7/LOW to DB0/DB8 are used for

the upper byte of data (see ). Table 6

Data Bit 10/Serial Strobe. When 12-bit parallel data is selected, this pin provides the DB10 output.

SSTRB

is an active low open-drain output that provides a strobe or framing pulse for serial data. An

external 4.7 kΩ pull-up resistor is required on

SSTRB

.

Data Bit 9/Serial Clock. When 12-bit parallel data is selected, this pin provides the DB9 output. SCLK is

the gated serial clock output derived from the internal or external ADC clock. If the 12/

−5 V, then SCLK runs continuously. If 12/

8

/CLK is at 0 V, then SCLK is gated off after serial transmission is

8

complete. SCLK is an open-drain output and requires an external 2 kΩ pull-up resistor.

Data Bit 8/Serial Data. When 12-bit parallel data is selected, this pin provides the DB8 output. SDATA is

SSTRB

an open-drain serial data output which is used with SCLK and

is valid on the falling edge of SCLK while

SSTRB

is low. An external 4.7 kΩ pull-up resistor is required on

for serial data transfer. Serial data

SDATA.

Three-state data outputs controlled by

inputs. With 12/

8

/CLK high, they are always DB7–DB4. With 12/8/CLK low or −5 V, their function is

CS

and RD. Their function depends on the 12/8/CLK and HBEN

controlled by HBEN (see ). Table 6

Three-state data outputs which are controlled by

and HBEN inputs. With 12/

8

/CLK high, they are always DB3–DB0. With 12/8/CLK low or −5 V, their

CS

and RD. Their function depends on the 12/8/CLK

function is controlled by HBEN (see ). Table 6

SS

IN

DD

07730-005

8

/CLK

/CLK input is at

Rev. C | Page 8 of 28

AD7870/AD7875/AD7876

DIP and SOIC

Pin No.

18 21 AGND Analog Ground. Ground reference for track-and-hold, reference and DAC.

19 23 REF OUT Voltage Reference Output. The internal 3 V reference is provided at this pin. The external load capability is

20 24 VIN Analog Input. The analog input range is ±3 V for the AD7870, ±10 V for the AD7876, and 0 V to +5 V for the

21 25 VSS Negative Supply, −5 V ± 5%.

22 26

23 27

24 28

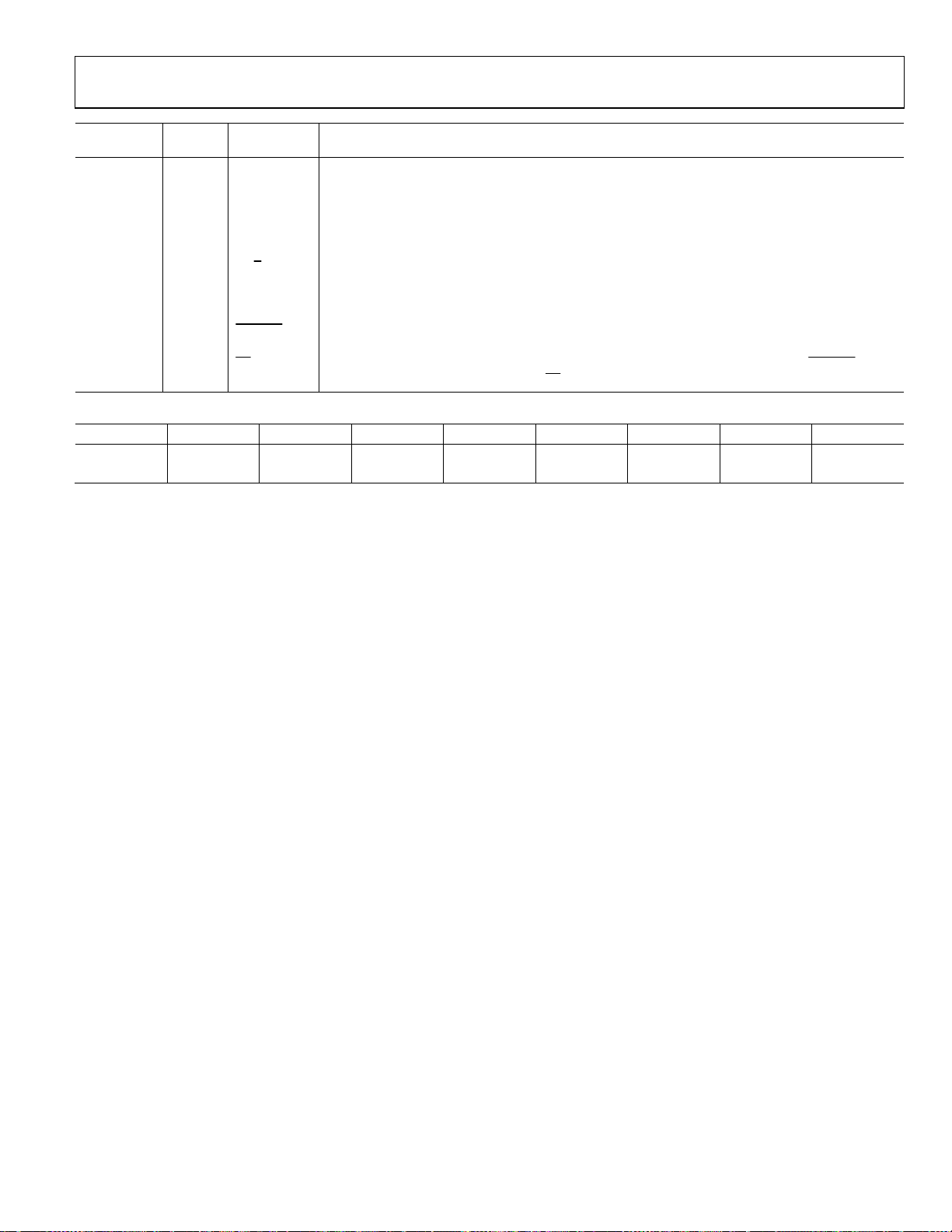

Table 6. Output Data for Byte Interfacing

HBEN DB7/Low DB6/Low DB5/Low DB4/Low DB3/DB11 DB2/DB10 DB1/DB9 DB0/DB8

High Low Low Low Low DB11(MSB) DB10 DB9 DB8

Low DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 (LSB)

PLCC

Pin No. Mnemonic Function

500 μA.

AD7875.

8

12/

/CLK

CONVST

CS

Chip Select. Active low logic input. The device is selected when this input is active. With

Three Function Input. Defines the data format and serial clock format. With this pin at +5 V, the output

data for-mat is 12-bit parallel only. With this pin at 0 V, either byte or serial data is available and SCLK is

not continuous. With this pin at −5 V, either byte or serial data is again available but SCLK is now

continuous.

Convert Start. A low to high transition on this input puts the track-and-hold into its hold mode and

starts conversion. This input is asynchronous to the CLK input.

low, a new conversion is initiated when

CS

goes low.

CONVST

tied

Rev. C | Page 9 of 28

Loading...

Loading...