Analog Devices AD7740 Datasheet

3 V/5 V Low Power, Synchronous

a

FEATURES

Synchronous Operation

Full-Scale Frequency Set by External System Clock

8-Lead SOT-23 and 8-Lead microSOIC Packages

3 V or 5 V Operation

Low Power: 3 mW (Typ)

Nominal Input Range: 0 to V

True –150 mV Capability Without Charge Pump

V

Range: 2.5 V to VDD

REF

Internal 2.5 V Reference

1 MHz Max Input Frequency

Selectable High Impedance Buffered Input

Minimal External Components Required

APPLICATIONS

Isolation of High Common-Mode Voltages

Low-Cost Analog-to-Digital Conversion

Battery Monitoring

Automotive Sensing

GENERAL DESCRIPTION

The AD7740 is a low-cost, ultrasmall synchronous Voltage-toFrequency Converter (VFC). It works from a single 3.0 V to

3.6 V or 4.75 V to 5.25 V supply consuming 0.9 mA. The AD7740

is available in an 8-lead SOT-23 and also in an 8-lead microSOIC

package. Small package, low cost and ease of use were major

design goals for this product. The part contains an on-chip 2.5 V

bandgap reference but the user may overdrive this using an

external reference. This external reference range includes VDD.

The full-scale output frequency is synchronous with the clock

signal on the CLKIN pin. This clock can be generated with the

addition of an external crystal (or resonator) or supplied from a

CMOS-compatible clock source. The part has a maximum

input frequency of 1 MHz.

For an analog input signal that goes from 0 V to V

put frequency goes from 10% to 90% of f

the part provides a very high input impedance and accepts a

range of 0.1 V to VDD – 0.2 V on the VIN pin. There is also

an unbuffered mode of operation that allows VIN to go from

–0.15 V to VDD + 0.15 V. The modes are interchangeable using

the BUF pin.

The AD7740 (Y Grade) is guaranteed over the automotive

temperature range of –40°C to +105°C. The AD7740 (K Grade)

is guaranteed from 0°C to 85°C.

REF

REF

In buffered mode,

CLKIN.

, the out-

Voltage-to-Frequency Converter

AD7740*

FUNCTIONAL BLOCK DIAGRAM

REFIN/OUT

AD7740

VIN

PRODUCT HIGHLIGHTS

X1

BUF

VOLTAGE-TO-

GND

REFERENCE

FREQUENCY

MODULATOR

GENERATION

CLKOUT

1. The AD7740 is a single channel, single-ended VFC. It is

available in 8-lead SOT-23 and 8-lead microSOIC packages,

and is intended for low-cost applications. The AD7740 offers

considerable space saving over alternative solutions.

2. The AD7740 operates from a single 3.0 V to 3.6 V or 4.75 V

to 5.25 V supply and consumes typically 0.9 mA when the

input is unbuffered. It also contains an automatic power-down

function.

3. The AD7740 does not require external resistors and capacitors to set the output frequency. The maximum output

frequency is set by a crystal or a clock. No trimming or calibration is required.

4. The analog input can be taken to 150 mV below GND for

true bipolar operation.

5. The specified voltage reference range on REFIN is from

2.5 V to the supply voltage, VDD.

VDD

2.5V

FOUT

CLOCK

CLKIN

*Patents pending.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

(VDD = 3.0 V to 3.6 V, 4.75 V to 5.25 V, GND = 0 V, REFIN = 2.5 V; CLKIN = 1 MHz; All

AD7740 SPECIFICATIONS

Parameter

2

DC PERFORMANCE

Integral Nonlinearity

CLKIN = 32 kHz

CLKIN = 1 MHz ± 0.012 % of Span Unbuffered Mode, Crystal at CLKIN

CLKIN = 32 kHz

3

3

CLKIN = 1 MHz ± 0.018 % of Span Buffered Mode, Crystal at CLKIN

Offset Error ± 7 ± 35 mV Unbuffered Mode, VIN = 0 V

Gain Error ± 0.1 ± 0.7 % of Span

Offset Error Drift

Gain Error Drift

Power Supply Rejection Ratio

3

3

3

ANALOG INPUT, VIN

Nominal Input Span 0 – V

Input Current 8 10 µA Unbuffered Mode, VIN = 5.4 V, REFIN = 5.25 V

REFERENCE VOLTAGE

REFIN

5

Nominal Input Voltage 2.5 VDD V

REFOUT

Output Voltage 2.3 2.5 2.7 V

Output Impedance

Reference Drift

Line Rejection

Line Rejection

3

3

3

3

Reference Noise (0.1 Hz to 10 Hz)

FOUT OUTPUT

Nominal Frequency Span 0.1 f

LOGIC INPUTS (CLKIN, BUF)

3

CLKIN

Input frequency 32 1000 kHz For Specified Performance

Input High Voltage, V

Input High Voltage, V

Input Low Voltage, V

Input Low Voltage, V

Input Current ± 2 µA VIN = 0 V to V

IH

IH

IL

IL

Pin Capacitance 3 10 pF

BUF

Input High Voltage, V

Input High Voltage, V

Input Low Voltage, V

Input Low Voltage, V

Input Current ± 100 nA

IH

IH

IL

IL

Pin Capacitance 3 10 pF

LOGIC OUTPUTS (FOUT, CLKOUT)

Output High Voltage, V

Output High Voltage, V

Output Low Voltage, V

POWER REQUIREMENTS

7

V

DD

I

(Normal Mode)

DD

I

(Normal Mode)

DD

I

(Power-Down) 30 100 µA

DD

Power-Up Time

NOTES

1

Temperature range: K Version, 0°C to +85°C; Y Version, –40°C to +105°C; typical specifications are at 25°C.

2

See Terminology.

3

Guaranteed by design and characterization, not production tested.

4

Span = Max output frequency–Min output frequency.

5

Because this pin is bidirectional, any external reference must be capable of sinking/sourcing 400 µA in order to overdrive the internal reference.

6

These logic levels apply to CLKOUT only when it is loaded with one CMOS load.

7

Operation at VDD = 2.7 V is also possible with degraded specifications.

8

Outputs unloaded. IDD increases by CL × V

type (see Clock Generation section).

Specifications subject to change without notice.

OH

OH

OL

8

8

3

OUT

K, Y Versions

Min Typ Max Unit Test Conditions/Comments

0.1 VDD – 0.2 V Buffered Mode

3

3.5 V VDD = 5 V ± 5%

2.5 V VDD = 3.3 V ± 10%

2.4 V VDD = 5 V ± 5%

2.1 V VDD = 3.3 V ± 10%

3

4.0 V Output Sourcing 200 µA6. VDD = 5 V ± 5%

2.1 V Output Sourcing 200 µA6. VDD = 3.3 V ± 10%

3.0 5.25 V

× f

when FOUT is loaded. If using a crystal/resonator as the clock source, IDD will vary depending on the crystal/resonator

FOUT

specifications T

1

± 0.012 % of Span

MIN

to T

unless otherwise noted.)

MAX

4

Unbuffered Mode, External Clock at CLKIN

± 0.018 % of Span Buffered Mode, External Clock at CLKIN

± 7 ± 35 mV Buffered Mode, VIN = 0.1 V

± 20 µV/°C

± 4 ppm of Span/°C

–55 dB ∆VDD = ± 5% (5 V)

–65 dB ∆VDD = ± 10% (3.3 V)

REF

V ± 150 mV Overrange Available

5 100 nA Buffered Mode, VIN = 0.1 V, REFIN = 2.5 V

1kΩ See Pin Function Description

± 50 ppm/°C

–75 dB ∆VDD = ± 5% (5 V)

–60 dB ∆VDD = ± 10% (3.3 V)

100 µV p–p

CLKIN

to 0.9 f

CLKIN

Hz VIN = 0 V to V

. See Figure 2

REF

0.8 V VDD = 5 V ± 5%

0.4 V VDD = 3.3 V ± 10%

DD

0.8 V VDD = 5 V ± 5%

0.4 V VDD = 3.3 V ± 10%

0.1 0.4 V Output Sinking 1.6 mA

6

0.9 1.25 mA VIH = VDD, VIL= GND. Unbuffered Mode

1.1 1.5 mA VIH = VDD, VIL= GND. Buffered Mode

30 µs Exiting Power-Down (Ext. Clock at CLKIN)

–2–

REV. 0

AD7740

MAX

1, 2, 3

(VDD = 3.0 V to 3.6 V, 4.75 V to 5.25 V, GND = O V, REFIN = 2.5 V)

Limit at T

MIN

, T

MAX

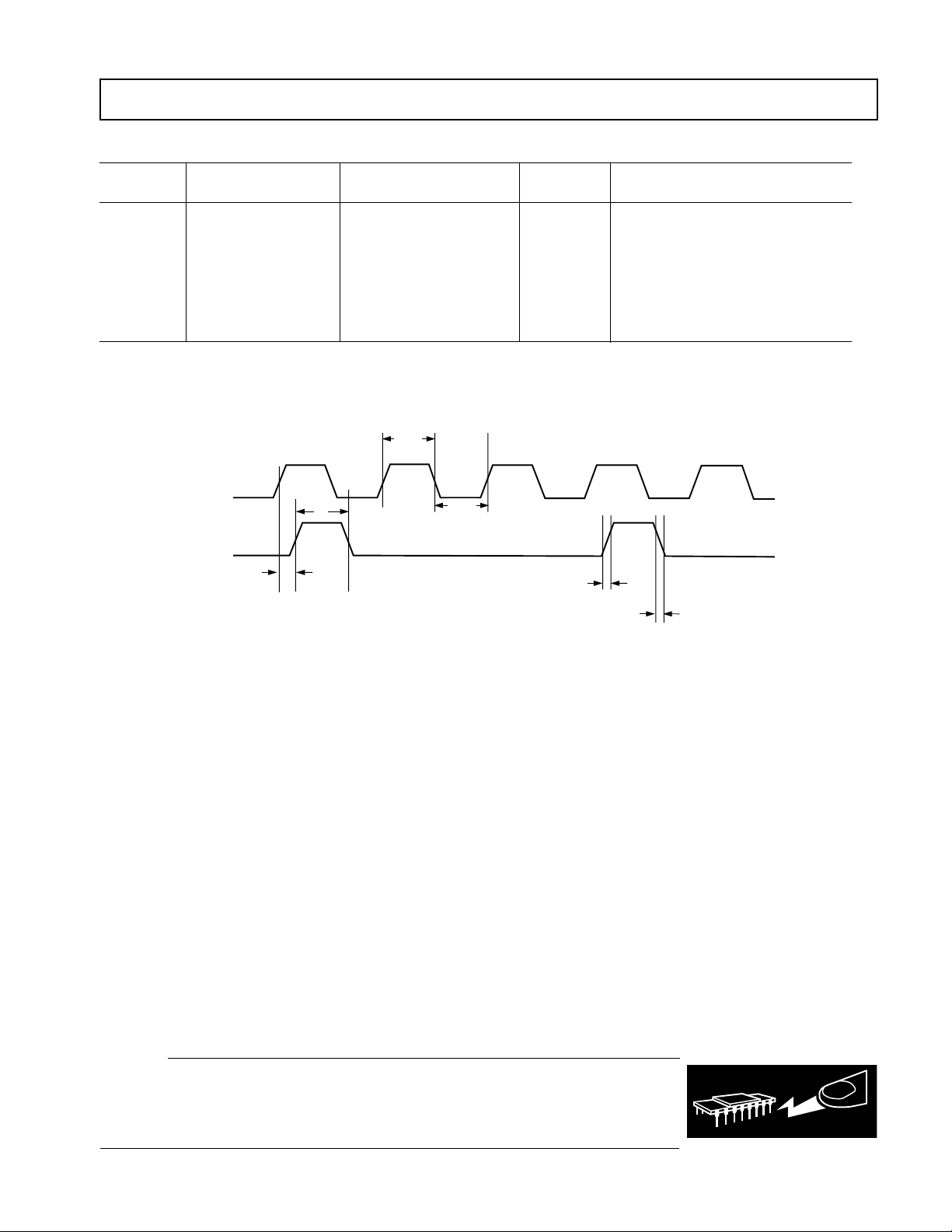

TIMING CHARACTERISTICS

Limit at T

MIN

, T

Parameter VDD = 3.0 V to 3.6 V VDD = 4.75 V to 5.25 V Unit Conditions/Comments

f

CLKIN

32 32 kHz min Clock Frequency

1 1 MHz max

t

HIGH:tLOW

40:60 40:60 min Clock Mark/Space Ratio

60:40 60:40 max

t

1

t

2

t

3

t

4

NOTES

1

Guaranteed by design and characterization, not production tested.

2

All input signals are specified with tr = tf = 5 ns (10% to 90% of VDD) and timed from a voltage level of (V

3

See Figure 1.

Specifications subject to change without notice

50 35 ns typ CLKIN Edge to FOUT Edge Delay

2.3 1.8 ns typ FOUT Rise Time

1.6 1.4 ns typ FOUT Fall Time

t

HIGH

CLKIN

FOUT

± 20

t

t

1

t

± 8

HIGH

t

HIGH

t

4

LOW

ns typ FOUT Pulsewidth

+ VIH)/2.

IL

t

2

t

3

Figure 1. Timing Diagram

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C unless otherwise noted)

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

Analog Input Voltage to GND . . . . . . . . –0.3 V to V

Reference Input Voltage to GND . . . . . –0.3 V to V

+ 0.3 V

DD

+ 0.3 V

DD

Logic Input Voltage to GND . . . . . . . . –0.3 V to VDD + 0.3 V

FOUT Voltage to GND . . . . . . . . . . . –0.3 V to VDD + 0.3 V

Operating Temperature Range

Commercial (K Version) . . . . . . . . . . . . . . . . 0°C to +85°C

Automotive (Y Version) . . . . . . . . . . . . . . –40°C to +105°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature (T

Max) . . . . . . . . . . . . . . . . . . 150°C

J

SOT-23 Package

Power Dissipation . . . . . . . . . . . . . . . . . . (T

Max – TA)/θ

J

microSOIC Package

Power Dissipation . . . . . . . . . . . . . . . . . (T

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 206°C/W

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 44°C/W

θ

JC

Lead Temperature (10 secs) . . . . . . . . . . . . . . . . . . . 300°C

Reflow Soldering

Peak Temperature . . . . . . . . . . . . . . . . . . . . . . 220 +5/0°C

Time at Peak Temperature . . . . . . . . . . . . . 10 sec to 40 sec

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

JA

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 240°C/W

Lead Temperature (10 secs) . . . . . . . . . . . . . . . . . . 300°C

Reflow Soldering

Peak Temperature . . . . . . . . . . . . . . . . . . . . 220 + 5/0°C

Time at Peak Temperature . . . . . . . . . . . . 10 sec to 40 sec

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD7740 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

Max – TA)/θ

J

ESD SENSITIVE DEVICE

JA

REV. 0

–3–

AD7740

PIN CONFIGURATIONS

8-Lead microSOIC

1

CLKOUT

2

CLKIN

REFIN/OUT

GND

microSOIC

TOP VIEW

3

(Not to Scale)

4

AD7740

8

BUF

7

FOUT

6

VDD

5

VIN

8-Lead SOT-23

1

BUF

AD7740

2

FOUT

VDD

VIN

SOT-23

3

TOP VIEW

(Not to Scale)

4

8

CLKOUT

7

CLKIN

6

GND

5

REFIN/OUT

PIN FUNCTION DESCRIPTIONS

8-LEAD microSOIC PIN NUMBERS*

Pin

No. Mnemonic Function

1 CLKOUT The crystal/resonator is tied between this pin and CLKIN. In the case of an external clock driving CLKIN, an

inverted clock signal appears on this pin and can be used to drive other circuitry provided it is buffered first.

2 CLKIN The master clock for the device may be in the form of a crystal/resonator tied between this pin and CLKOUT.

An external CMOS-compatible clock may also be applied to this input as the clock for the device. If CLKIN

is inactive low for 1 ms (typ), the AD7740 automatically enters power-down.

3 GND Ground reference for all the circuitry on-chip.

4 REFIN/OUT Voltage Reference Input. This is the reference input to the core of the VFC and defines the span of the VFC.

If this pin is left unconnected, the internal 2.5 V reference is the default reference. Alternatively, a precision

external reference may be used to overdrive the internal reference. The internal reference has high output

impedance in order to allow it to be overdriven.

5 VIN The analog input to the VFC. It has a nominal input range from 0 V to V

frequency of 10% f

CLKIN

to 90% f

. It has a ± 150 mV overrange. If buffered, it draws virtually no current

CLKIN

which corresponds to an output

REF

from whatever source is driving it.

6 VDD Power Supply Input. These parts can be operated at 3.3 V ± 10% or 5 V ± 5%. The supply should be

adequately decoupled with a 10 µF and a 0.1 µF capacitor to GND.

7 FOUT Frequency Output. FOUT goes from 10% to 90% of f

, depending on VIN.

CLKIN

8 BUF Buffered Mode Select Pin. When BUF is tied low, the VIN input is unbuffered and the range on the VIN

pin is –0.15 V to VDD + 0.15 V. When it is tied high, VIN is buffered and the range on the VIN pin

is restricted to 0.1 V to VDD – 0.2 V.

*Note that the SOT-23 and microSOIC packages have different pinouts.

ORDERING GUIDE

Package Branding

Model Temperature Range Package Description Option Information

AD7740KRM 0°C to 85°C microSOIC Package RM-8 VOK

AD7740YRT –40°C to +105°C SOT-23 Package RT-8 VOY

AD7740YRM –40°C to +105°C microSOIC Package RM-8 VOY

–4–

REV. 0

Loading...

Loading...