Analog Devices AD7734 Datasheet

4-Channel, ±10 V Input Range, High

FEATURES

High resolution ADC

24 bits no missing codes

±0.0025% nonlinearity

Optimized for fast channel switching

18-bit p-p resolution (21 bits effective) at 500 Hz

16-bit p-p resolution (19 bits effective) at 2 kHz

14-bit p-p resolution (18 bits effective) at 15 kHz

On-chip per channel system calibration

4 single-ended analog inputs

Input ranges +5 V, ±5 V, +10 V, ±10 V

Overvoltage tolerant

Up to ±16.5 V not affecting adjacent channel

Up to ±50 V absolute maximum

3-wire serial interface

SPI™, QSPI™, MICROWIRE™, and DSP compatible

Schmitt trigger on logic inputs

Single-supply operation

5 V analog supply

3 V or 5 V digital supply

Package: 28-lead TSSOP

APPLICATIONS

PLCs/DCS

Multiplexing applications

Process control

Industrial instrumentation

GENERAL DESCRIPTION

The AD7734 is a high precision, high throughput analog front

end. True 16-bit p-p resolution is achievable with a total

conversion time of 500 µs (2 kHz channel switching), making it

ideally suitable for high resolution multiplexing applications.

The part can be configured via a simple digital interface, which

allows users to balance the noise performance against data

throughput up to a 15.4 kHz.

The analog front end features four single-ended input channels

with unipolar or true bipolar input ranges to ±10 V while

operating from a single +5 V analog supply. The part has an

overrange and underrange detection capability and accepts an

analog input overvoltage to ±16.5 V without degrading the

performance of the adjacent channels.

Throughput, 24-Bit ∑-∆ ADC

AD7734

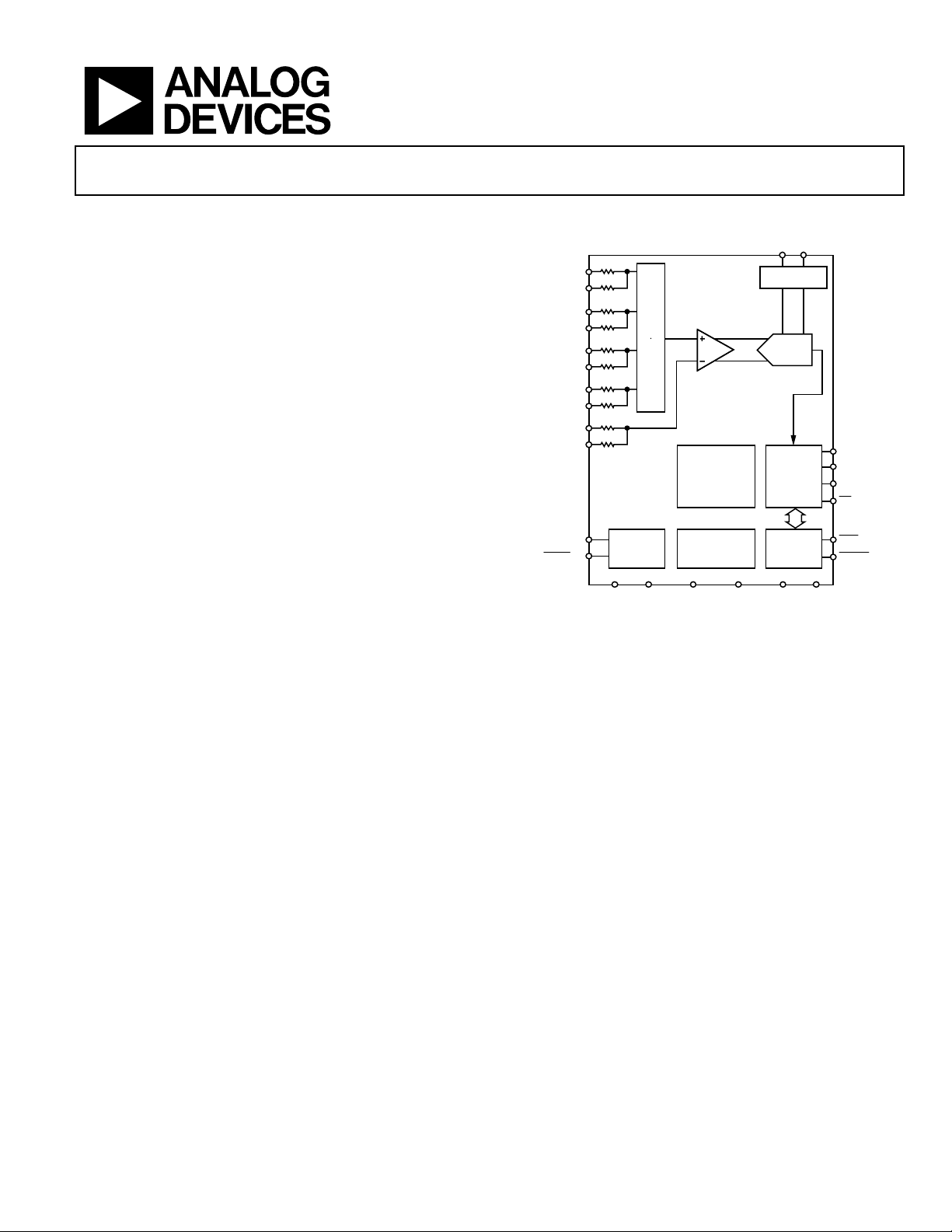

FUNCTIONAL BLOCK DIAGRAM

REFIN(–) REFIN(+)

AIN0

AIN1

AIN2

AIN3

BIASHI

BIASLO

SYNC/P1

MUX

P0

I/O PORT

DD

BUFFER

CALIBRATION

CIRCUITRY

CLOCK

GENERATOR

Figure 1.

The differential reference input features “No-Reference” detect

capability. The ADC also supports per channel system

calibration options. The digital serial interface can be

configured for 3-wire operation and is compatible with

microcontrollers and digital signal processors. All interface

inputs are Schmitt triggered.

The part is specified for operation over the extended industrial

temperature range of –40°C to +105°C.

Other parts in the AD7734 family are the AD7732 and

the AD7738.

The AD7732 is similar to AD7734, but its analog front end

features two fully differential input channels.

The AD7738 analog front end is configurable for four fully

differential or eight single-ended input channels, features

0.625 V to 2.5 V bipolar/unipolar input ranges, and accepts a

common-mode input voltage from 200 mV to AVDD–300 mV.

The AD7738 multiplexer output is pinned out externally,

allowing the user to implement programmable gain or signal

conditioning before being applied to the ADC.

AD7734

REFERENCE

DETECT

24-BIT

Σ−∆ ADC

SERIAL

INTERFACE

CONTROL

LOGIC

DGNDMCLKINMCLKOUTAGND AV

DV

SCLK

DOUT

D

I

N

CS

RDY

RESET

DD

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2003 Analog Devices, Inc. All rights reserved.

AD7734

TABLE OF CONTENTS

AD7734—Specifications.................................................................. 3

Mode Register............................................................................. 20

Timing Specifications....................................................................... 6

Absolute Maximum Ratings............................................................ 8

Typical Performance Characteristics ............................................. 9

Output Noise and Resolution Specification................................ 10

Chopping Enabled...................................................................... 10

Chopping Disabled..................................................................... 11

Pin Configurations and Functional Descriptions...................... 12

Register Description....................................................................... 14

Register Access............................................................................ 15

Communications Register......................................................... 15

I/O Port Register......................................................................... 16

Revision Register ........................................................................16

Test Register ................................................................................ 16

ADC Status Register................................................................... 17

Checksum Register..................................................................... 17

Digital Interface Description ........................................................ 22

Hardware ..................................................................................... 22

Reset ............................................................................................. 23

Access the AD7734 Registers.................................................... 23

Single Conversion and Reading Data...................................... 23

Dump Mode................................................................................ 24

Continuous Conversion Mode ................................................. 24

Continuous Read (Continuous Conversion) Mode .............. 25

Circuit Description......................................................................... 26

Analog Front End....................................................................... 26

Analog Input’s Extended Voltage Range ................................. 27

Chopping..................................................................................... 27

Multiplexer, Conversion, and Data Output Timing............... 28

Sigma-Delta ADC....................................................................... 28

Frequency Response .................................................................. 29

ADC Zero-Scale Calibration Register ..................................... 17

ADC Full-Scale Register............................................................ 17

Channel Data Registers ............................................................. 17

Channel Zero-Scale Calibration Registers.............................. 18

Channel Full-Scale Calibration Registers................................ 18

Channel Status Registers ...........................................................18

Channel Setup Registers............................................................ 19

Channel Conversion Time Registers ....................................... 19

REVISION HISTORY

Revision 0: Initial Version

Voltage Reference Inputs........................................................... 29

Reference Detect......................................................................... 29

I/O Port........................................................................................ 30

Calibration................................................................................... 30

ADC Zero-Scale Self-Calibration ............................................ 30

Per Channel System Calibration .............................................. 30

Outline Dimensions....................................................................... 32

Rev. 0 | Page 2 of 32

AD7734

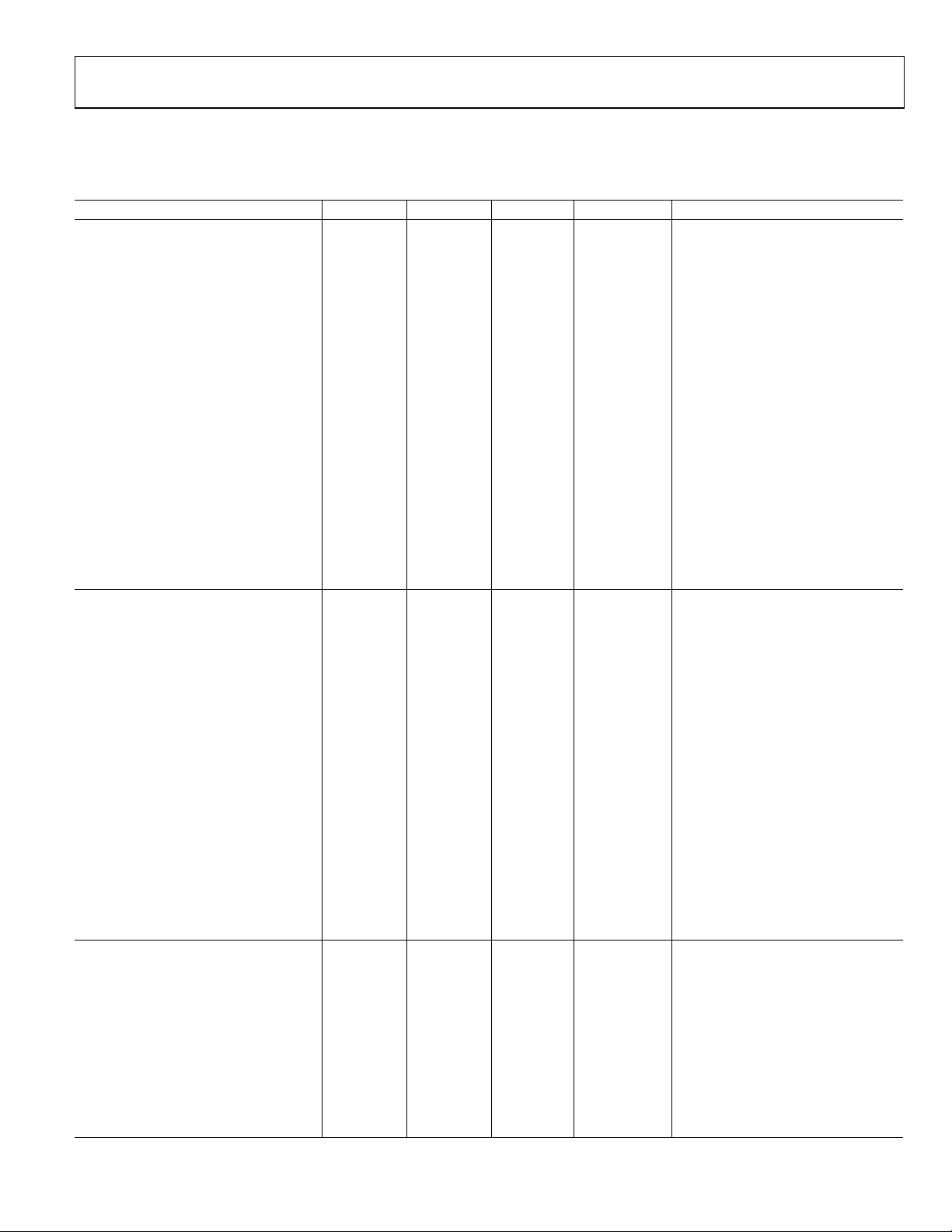

AD7734—SPECIFICATIONS

Table 1. (–40°C to +105°C; AVDD = 5 V ± 5%; DVDD = 2.7 V to 3.6 V, or 5 V ± 5%; BIAS0 to BIAS3, BIASHI, REFIN(+) = 2.5 V;

BIASLO, REFIN(–) = AGND; AIN Range = ±10 V; f

Parameter Min Typ Max Unit Test Conditions/Comments

ADC PERFORMANCE

CHOPPING ENABLED

Conversion Time Rate 372 12190 Hz Configure via Conv. Time Register

No Missing Codes

1, 2

24 Bits FW ≥ 6 (Conversion Time ≥ 165 µs)

Output Noise

Resolution

Integral Nonlinearity (INL)

1, 2

±0.0010 ±0.0030 % of FSR f

Integral Nonlinearity (INL)2 ±0.0025 ±0.0045 % of FSR f

Offset Error (Unipolar, Bipolar)3 ±10 mV Before Calibration

Offset Drift vs. Temperature1 ±2.5 µV/°C

Gain Error3 ±0.35 % Before Calibration

Gain Drift vs. Temperature1 ±3.2 ppm of FS/°C

Positive Full-Scale Error3 ±0.5 % of FSR Before Calibration

Positive Full-Scale Drift vs. Temp.1 ±3 ppm of FS/°C

Bipolar Negative Full-Scale Error4 ±0.0050 % of FSR After Calibration

Power Supply Sensitivity ±4 ±10 LSB16 At DC, AIN = 7 V, AVDD = 5 V ± 5%

Channel-to-Channel Isolation 100 dB At DC, Maximum ±16.5 V AIN Voltage

ADC PERFORMANCE

CHOPPING DISABLED

Conversion Time Rate 737 15437 Hz Configure via Conv. Time Register

No Missing Codes

1, 2

24 Bits FW ≥ 8 (Conversion Time ≥ 117 µs)

Output Noise

Resolution

Integral Nonlinearity (INL)2 ±0.0025 % of FSR

Offset Error (Unipolar, Bipolar)5 ±15 mV Before Calibration

Offset Drift vs. Temperature ±25 µV/°C

Gain Error3 ±0.1 % Before Calibration

Gain Drift vs. Temperature ±5.3 ppm of FS/°C

Positive Full-Scale Error3 ±0.2 % of FSR Before Calibration

Positive Full-Scale Drift vs. Temp. ±4 ppm of FS/°C

Bipolar Negative Full-Scale Error4 ±0.0050 % of FSR After Calibration

Power Supply Sensitivity ±4 LSB16 At DC, AIN = 7 V, AVDD = 5 V ± 5%

Channel-to-Channel Isolation 100 dB At DC, Maximum ±16.5 V AIN Voltage

ANALOG INPUTS

Analog Input Voltage

1, 6, 7

±10 V Range

0 V to +10 V Range 0 to +10 V

±5 V Range

0 V to +5 V Range 0 to +5 V

BIASLO Voltage 0 V

BIAS0 to 3, BIASHI Voltage 2.5 V

AIN Impedance

AIN Pin, BIASLO Pin Impedance

1, 8

100 124

1, 8

87.5 108.5

= 6.144 MHz; unless otherwise noted.)

MCLKIN

See

Table 4

See Table 5

and Table 6

See

Table 7

See Table 8

and Table 9

±10

±5

V

V

kΩ

kΩ

= 2.5 MHz

MCLKIN

= 6.144 MHz

MCLKIN

Rev. 0 | Page 3 of 32

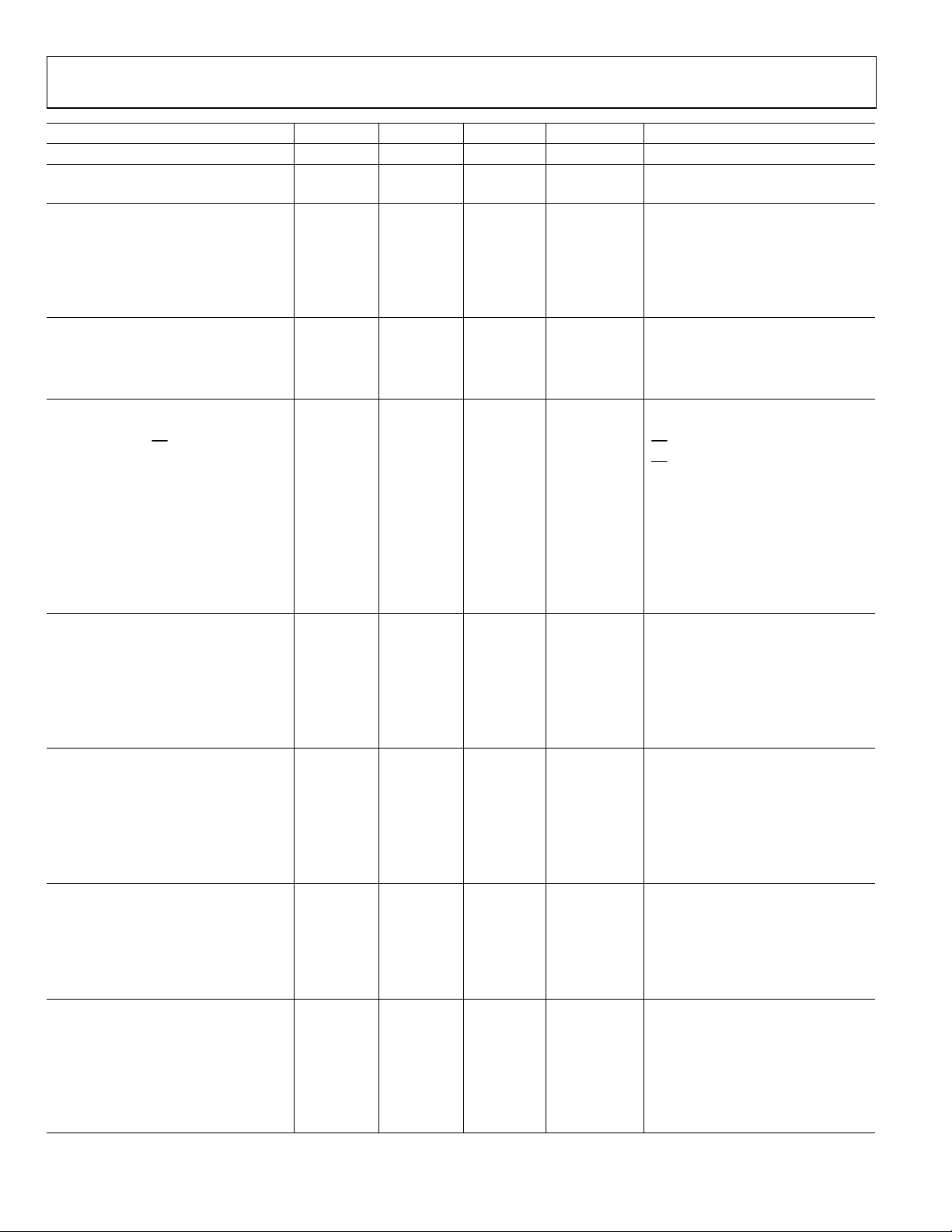

AD7734

Parameter Min Typ Max Unit Test Conditions/Comments

BIAS0 to 3, BIASHI Pin Impedance

Input Resistor Matching 0.2 %

Input Resistor Temp. Coefficient –30 ppm/°C

REFERENCE INPUTS

REFIN(+) to REFIN(–) Voltage

NOREF Trigger Voltage 0.5 V NOREF Bit in Channel Status Register

REFIN(+), REFIN(–)

Common-Mode Voltage1 0 AVDD V

Reference Input DC Current10 400 µA

SYSTEM CALIBRATION

1, 11

Full-Scale Calibration Limit

Zero-Scale Calibration Limit

Input Span

LOGIC INPUTS

Input Current

Input Current CS

–40 µA

Input Capacitance 5 pF

1

V

1.4 2 V DVDD = 5 V

T+

1

V

0.8 1.4 V DVDD = 5 V

T–

VT+ – V

V

1

0.3 0.85 V DVDD = 5 V

T–

1

0.95 2 V DVDD = 3 V

T+

VT– 1 0.4 1.1 V DVDD = 3 V

VT+ – V

1

0.3 0.85 V DVDD = 3 V

T–

MCLK IN ONLY

Input Current

Input Capacitance 5 pF

V

Input Low Voltage 0.8 V DVDD = 5 V

INL

V

Input High Voltage 3.5 V DVDD = 5 V

INH

V

Input Low Voltage 0.4 V DVDD = 3 V

INL

V

Input High Voltage 2.5 V DVDD = 3 V

INH

LOGIC OUTPUTS12

VOL Output Low Voltage 0.4 V I

VOH Output High Voltage 4.0 V I

VOL Output Low Voltage 0.4 V I

VOH Output High Voltage DVDD – 0.6 V I

Floating State Leakage Current

Floating State Leakage Capacitance 3 pF

P0, P1 INPUTS/OUTPUTS Levels Referenced to Analog Supplies

Input Current

V

Input Low Voltage 0.8 V AVDD = 5 V

INL

V

Input High Voltage 3.5 V AVDD = 5 V

INH

VOL Output Low Voltage 0.4 V I

VOH Output High Voltage 4.0 V I

POWER REQUIREMENTS

AVDD–AGND Voltage 4.75 5.25 V

DVDD–DGND Voltage 4.75 5.25 V

2.70 3.60 V

AVDD Current (Normal Mode) 13.5 15.9 mA AVDD = 5 V

DVDD Current (Normal Mode)

DVDD Current (Normal Mode) 13 1.0 1.5 mA DVDD = 3 V

1, 8

12.5 15.5

1, 9

2.475 2.5 2.525 V

+1.05 × FS

–1.05 × FS

0.8 × FS

V

2.1 × FS

±1

±10

±10

±1

±10

13

2.8 3.1 mA DVDD = 5 V

kΩ

V

V

µA

µA

µA

µA

µA

CS = DVDD

= DGND, Internal Pull-Up Resistor

CS

SINK

SOURCE

SINK

SOURCE

SINK

SOURCE

= 800 µA, DVDD = 5 V

= 200 µA, DVDD = 5 V

= 100 µA, DVDD = 3 V

= 100 µA, DVDD = 3 V

= 7 mA, See Abs. Max. Ratings

= 200 µA, AVDD = 5 V

Rev. 0 | Page 4 of 32

AD7734

Parameter Min Typ Max Unit Test Conditions/Comments

Power Dissipation (Normal Mode)

AVDD+DVDD Current (Standby Mode)14 100 µA

Power Dissipation (Standby Mode) 14 525 µW

13

85 100 mW

1

Specifications are not production tested but guaranteed by design and/or characterization data at initial product release.

2

See Typi . cal Performance Characteristics

3

Specifications before calibration. Channel system calibration reduces these errors to the order of the noise.

4

Applies after the zero-scale and full-scale calibration. The negative full-scale error represents the remaining error after removing the offset and gain error.

5

ADC zero-scale self-calibration reduces this error to ±10 mV. Channel zero-scale system calibration reduces this error to the order of the noise.

6

For specified performance. The output data span corresponds to the specified nominal input voltage range. The ADC is functional outside the nominal input voltage

range, but the performance might degrade. Outside the nominal input voltage range, the OVR bit in the channel status register is set and the channel data register

value depends on the CLAMP bit in the mode register. See the register and circuit descriptions for more details.

7

The adjacent channels are not affected by AIN voltage up to ±16.5 V.

8

Pin impedance is from the pin to the internal node. In normal circuit configuration, the analog input total impedance is typically 108.5 kΩ + 15.5 kΩ = 124 kΩ.

9

For specified performance. Part is functional with lower V

10

Dynamic current charging the sigma-delta modulator input switching capacitor.

11

Outside the specified calibration range, calibration is possible but the performance may degrade.

12

These logic output levels apply to the MCLK OUT output when it is loaded with a single CMOS load.

13

With external MCLK, MCLKOUT disabled (CLKDIS bit set in the mode register).

14

External MCLKIN = 0 V or DVDD, digital inputs = 0 V or DVDD, P0 and P1 = 0 V or AVDD.

.

REF

Rev. 0 | Page 5 of 32

AD7734

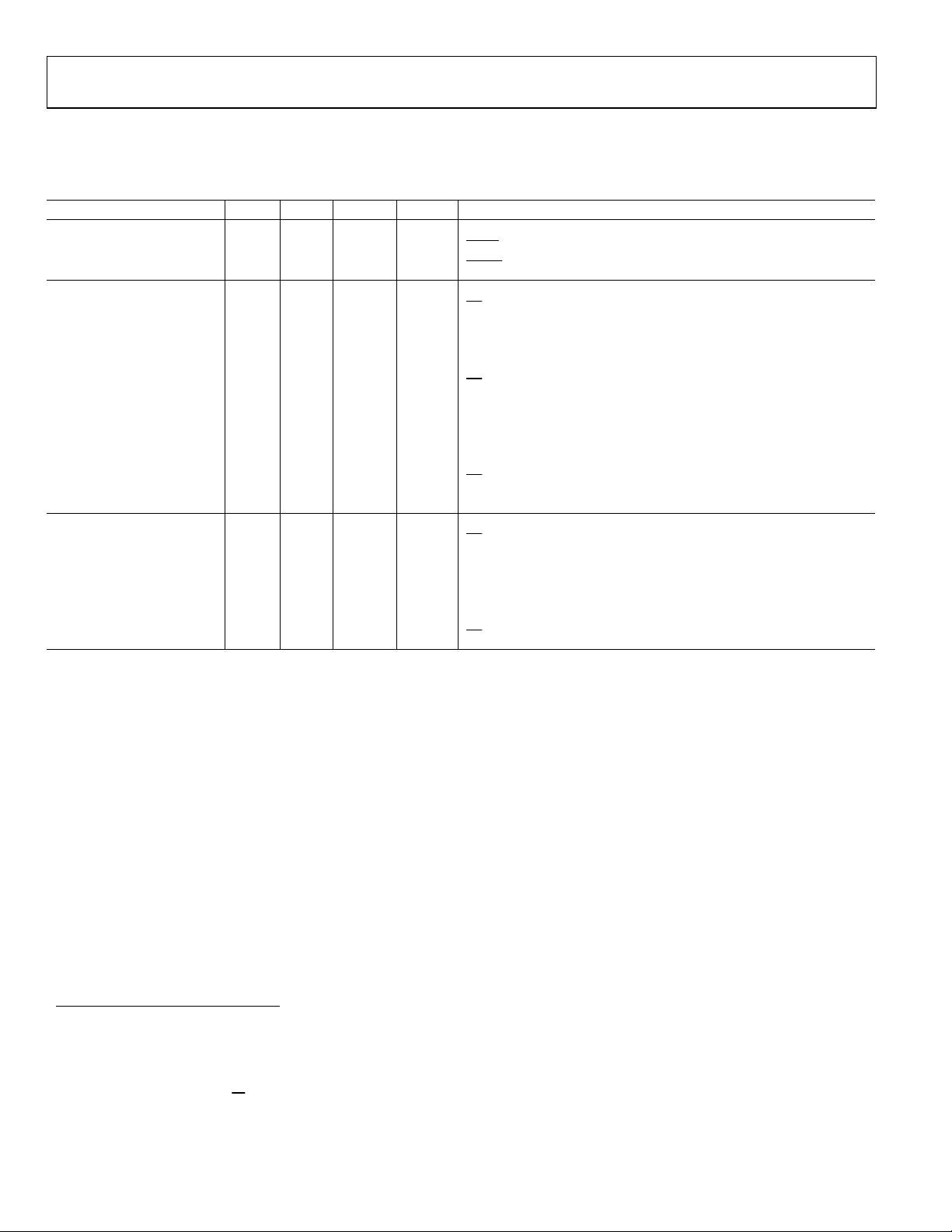

TIMING SPECIFICATIONS

Table 2. (AVDD = 5 V ± 5%; DVDD = 2.7 V to 3.6 V, or 5 V ± 5%; Input Logic 0 = 0 V; Logic 1 = DVDD;

unless otherwise noted.)

Parameter Min Typ Max Unit Test Conditions/Comments

Master Clock Range 1 6.144 MHz

t1 50 ns

t2 500 ns

Read Operation

t4 0 ns

2

t

SCLK Falling Edge to Data Valid Delay

5

0 60 ns DVDD of 4.75 V to 5.25 V

0 80 ns DVDD of 2.7 V to 3.3 V

2, 3

t

5A

0 60 ns DVDD of 4.75 V to 5.25 V

0 80 ns DVDD of 2.7 V to 3.3 V

t6 50 ns SCLK High Pulsewidth

t7 50 ns SCLK Low Pulsewidth

t8 0 ns

4

t

10 80 ns Bus Relinquish Time after SCLK Rising Edge

9

Write Operation

t11 0 ns

t12 30 ns Data Valid to SCLK Rising Edge Setup Time

t13 25 ns Data Valid after SCLK Rising Edge Hold Time

t14 50 ns SCLK High Pulsewidth

t15 50 ns SCLK Low Pulsewidth

t16 0 ns

1

Pulsewidth

SYNC

Pulsewidth

RESET

Falling Edge to SCLK Falling Edge Setup Time

CS

Falling Edge to Data Valid Delay

CS

Rising Edge after SCLK Rising Edge Hold Time

CS

Falling Edge to SCLK Falling Edge Setup

CS

Rising Edge after SCLK Rising Edge Hold Time

CS

1

Sample tested during initial release to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of DVDD) and timed from a voltage level of

1.6 V. See Figure 2 and Figure 3.

2

These numbers are measured with the load circuit of Figure 4 and defined as the time required for the output to cross the VOL or VOH limits.

3

This specification is relevant only if CS goes low while SCLK is low.

4

These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit of Figure 4. The measured number is then

extrapolated back to remove effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the Timing Characteristics are the true bus

relinquish times of the part and as such are independent of external bus loading capacitances.

Rev. 0 | Page 6 of 32

AD7734

SCLK

T

CS

t

4

SCLK

t

5

t

5A

DOUT MSB LSB

t

6

t

7

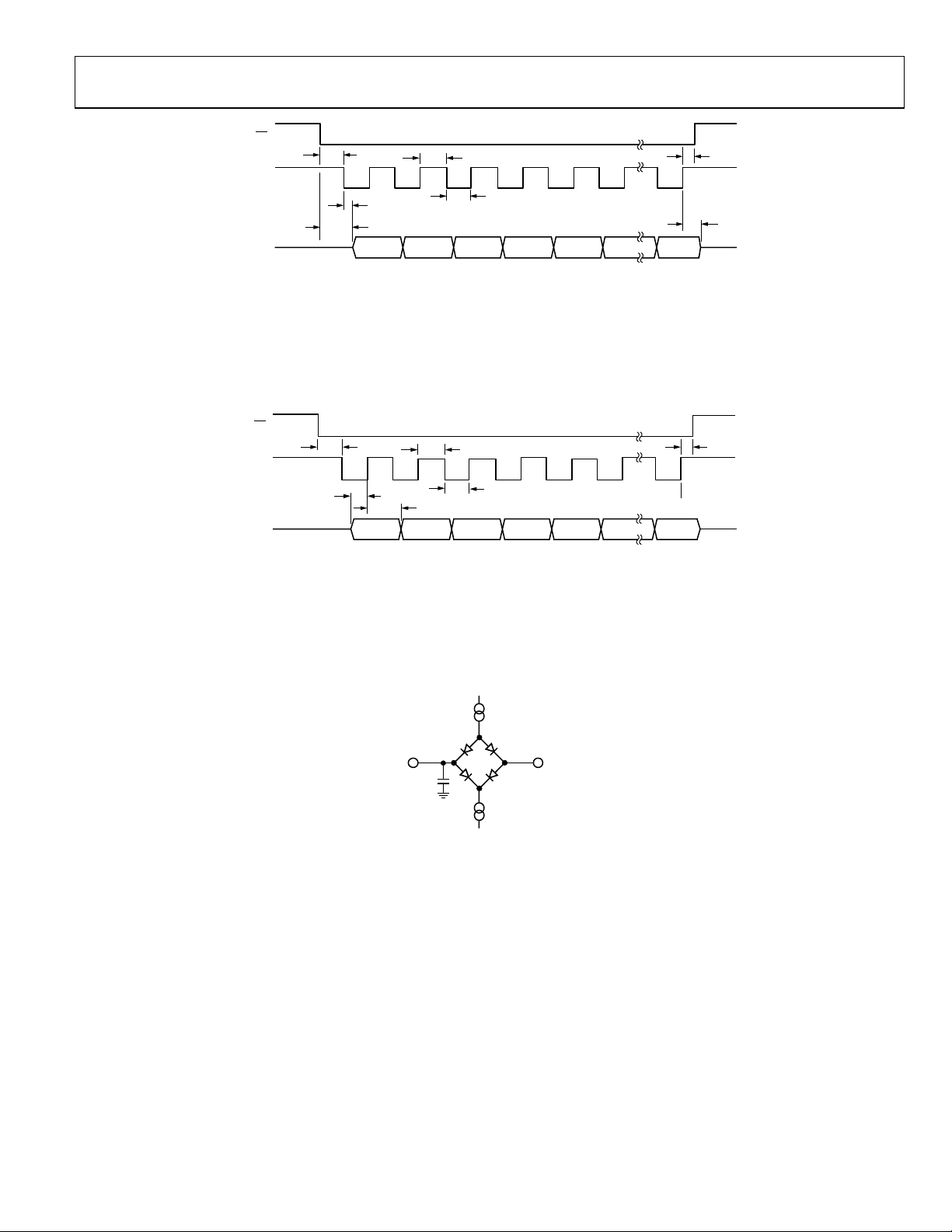

Figure 2. Read Cycle Timing Diagram

CS

t

DIN

11

t

12

MSB

t

14

t

15

t

13

Figure 3. Write Cycle Timing Diagram

LSB

t

8

t

9

t

16

(800µA AT DVDD = 5V

I

SINK

O OUTPUT

PIN

50pF

100µA AT DV

I

(200µA AT DVDD = 5V

SOURCE

100µA AT DV

1.6V

DD

= 3V)

DD

= 3V)

Figure 4. Load Circuit for Access Time and Bus Relinquish Time

Rev. 0 | Page 7 of 32

AD7734

ABSOLUTE MAXIMUM RATINGS

Table 3. TA = 25°C, unless otherwise noted.

Parameter Rating

AVDD to AGND, DVDD to DGND –0.3 V to +7 V

AGND to DGND –0.3 V to +0.3 V

AVDD to DVDD –5 V to +5 V

AIN to AGND –50 V to +50 V

BIAS to AGND –0.3 V to AVDD + 0.3 V

REFIN+, REFIN– to AGND –0.3 V to AVDD + 0.3 V

MUX0, INTBIAS to AGND –0.3 V to AVDD + 0.3 V

P0, P1 Voltage to AGND –0.3 V to AVDD + 0.3 V

P0, P1 Current (T

P0, P1 Current (T

P0, P1 Current (T

Digital Input Voltage to DGND –0.3 V to DVDD + 0.3 V

Digital Output Voltage to DGND –0.3 V to DVDD + 0.3 V

Operating Temperature Range –40°C to +105°C

Storage Temperature Range –65°C to +150°C

Junction Temperature 150°C

TSSOP Package, Power Dissipation 660 mW

θJA Thermal Impedance

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

= 70°C) 8 mA

MAX

= 85°C) 5 mA

MAX

= 105°C) 2.5 mA

MAX

97.9°C/W

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only;

functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is

not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Rev. 0 | Page 8 of 32

AD7734

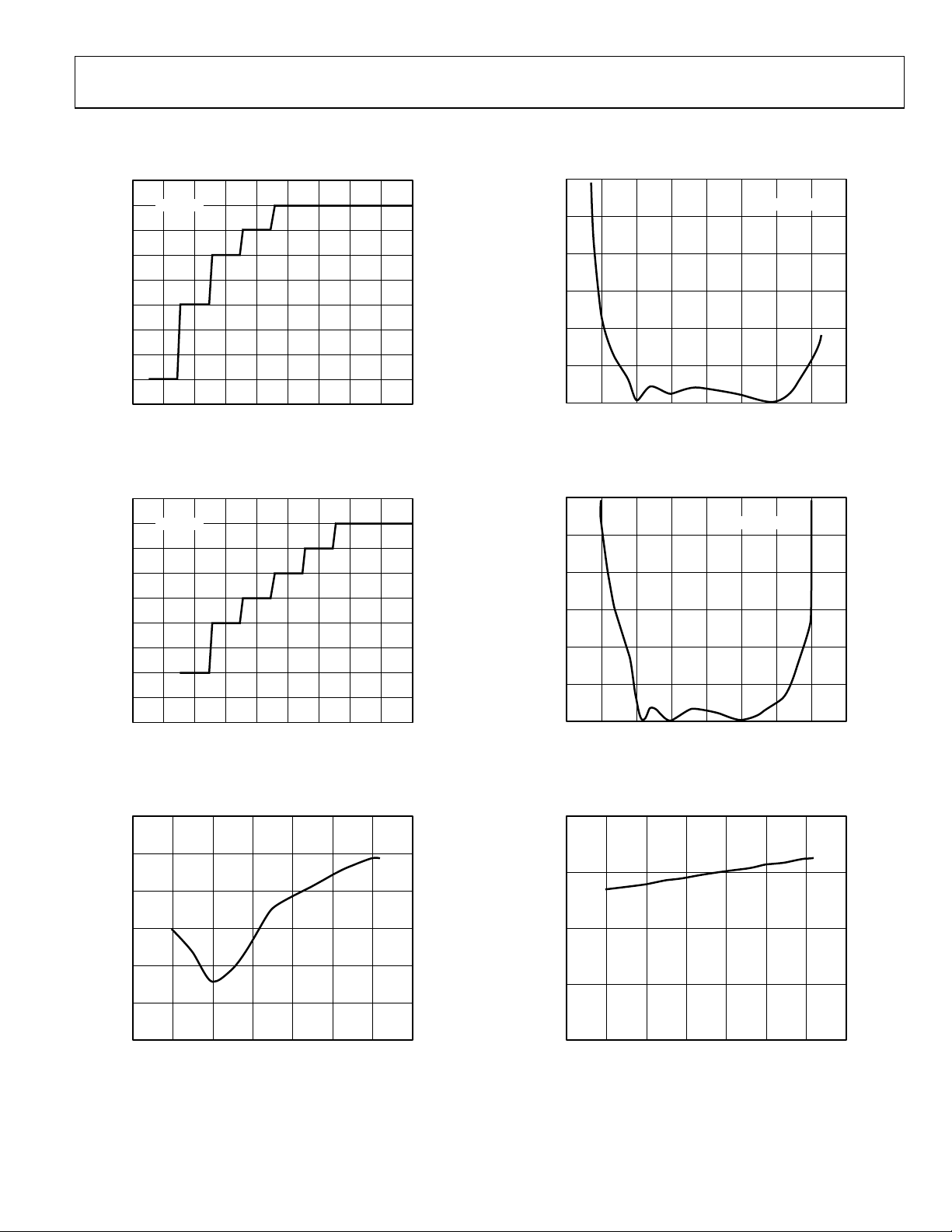

TYPICAL PERFORMANCE CHARACTERISTICS

25

24

CHOP = 1

23

22

21

20

19

NO MISSING CODES

18

17

16

12345678910

FILTER WORD

Figure 5. No Missing Codes Performance, Chopping Enabled

25

24

CHOP = 0

23

22

21

20

19

NO MISSING CODES

18

17

16

12345678910

FILTER WORD

Figure 6. No Missing Codes Performance, Chopping Disabled

30

300

250

200

150

INL – ppm

100

50

0

–20–15–10–50 5101520

AIN DIFFERENTIAL VOLTAGE – V

MCLK = 6.144MHz

Figure 8. Typical INL vs. AIN Voltage, AIN Range =±10 V,

BIAS0 to BIAS3, BIASHI = 2.5 V, BIASLO = O V

300

250

200

150

INL – ppm

100

50

0

–20–15–10–50 5101520

AIN DIFFERENTIAL VOLTAGE – V

MCLK = 6.144MHz

Figure 9. Typical INL vs. AIN Voltage, AIN Range = ±10 V,

BIAS0 to BIAS3, BIASHI = 2.5 V, BIASLO = 0 V

20

25

20

15

INL – ppm

10

5

0

01234567

MCLK FREQUENCY – MHz

Figure 7. Typical INL vs. MCLK Frequency,

AIN = ±10 V, BIAS0 to BIAS3, BIASHI = 2.5 V, BIASLO = 0 V

Rev. 0 | Page 9 of 32

15

10

CURRENT – mA

DD

+ DV

DD

5

AV

0

01234567

MCLK FREQUENCY – MHz

Figure 10. Typical Supply Current vs. MCLK Frequency,

Normal Operation, Converting

AD7734

OUTPUT NOISE AND RESOLUTION SPECIFICATION

The AD7734 can be operated with chopping enabled or

disabled, allowing the ADC to be programmed to either

optimize the throughput rate and channel switching time or to

optimize the offset drift performance. Noise tables for these two

primary modes of operation are outlined below for a selection

of output rates and settling times.

The AD7734 noise performance depends on the selected

chopping mode, the filter word (FW) value, and the selected

analog input range. The AD7734 noise will not vary

significantly with MCLK frequency.

Chopping Enabled

The first mode, in which the AD7734 is configured with

chopping enabled (CHOP = 1), provides very low noise with

lower output rates. Table 4 to Table 6 show the –3 dB

Table 4. Typical Output RMS Noise in µV vs. Conversion Time and Input Range with Chopping Enabled

FW Conversion Time

Register

127 FFh 2686 372 200 9.6

46 AEh 999 1001 520 15.5

22 96h 499 2005 1040 22.7

17 91h 395 2534 1300 26.1

8 88h 207 4826 2500 39.2

6 86h 166 6041 3100 46.0

2 82h 82 12166 6300 120.0

Conversion Time

(µs)

Output Data Rate

(Hz)

frequencies and typical performance versus the channel

conversion time and equivalent output data rate, respectively.

Table 4 shows the typical output rms noise. Table 5 shows the

typical effective resolution based on rms noise. Table 6 shows

the typical output peak-to-peak resolution, representing values

for which there will be no code flicker within a 6-sigma limit.

The peak-to-peak resolutions are not calculated based on rms

noise but on peak-to-peak noise.

These typical numbers are generated from 4096 data samples

acquired in continuous conversion mode with an analog input

voltage set to 0 V and MCLK = 6.144 MHz. The conversion

time is selected via the channel conversion time register.

–3 dB Frequency

(Hz)

RMS Noise

(µV)

Table 5. Typical Effective Resolution in Bits vs. Conversion Time and Input Range with Chopping Enabled

Conversion Time

Register

127 FFh 2686 372 200 21.0 20.0 20.0 19.0

46 AEh 999 1001 520 20.3 19.3 19.3 18.3

22 96h 499 2005 1040 19.7 18.7 18.7 17.7

17 91h 395 2534 1300 19.5 18.5 18.5 17.5

8 88h 207 4826 2500 19.0 18.0 18.0 17.0

6 86h 166 6041 3100 18.7 17.7 17.7 16.7

2 82h 82 12166 6300 17.3 16.3 16.3 15.3

(µs)

Output Data Rate

(Hz)

–3 dB Frequency

(Hz)

Input Range/Effective Resolution (Bits) FW Conversion Time

±10 V 0 V to +10 V ±5 V 0 V to +5 V

Table 6. Typical Peak-to-Peak Resolution in Bits vs. Conversion Time and Input Range with Chopping Enabled

Conversion Time

Register

127 FFh 2686 372 200 18.1 17.1 17.1 16.1

46 AEh 999 1001 520 17.4 16.4 16.4 15.4

22 96h 499 2005 1040 16.9 15.9 15.9 14.9

17 91h 395 2534 1300 16.7 15.7 15.7 14.7

8 88h 207 4826 2500 16.2 15.2 15.2 14.2

6 86h 166 6041 3100 15.8 14.8 14.8 13.8

2 82h 82 12166 6300 15.0 13.4 13.4 12.4

(µs)

Output Data Rate

(Hz)

Rev. 0 | Page 10 of 32

–3 dB Frequency

(Hz)

Input Range/Peak-to-Peak Resolution (Bits) FW Conversion Time

±10 V 0 V to +10 V ±5 V 0 V to +5 V

Loading...

Loading...