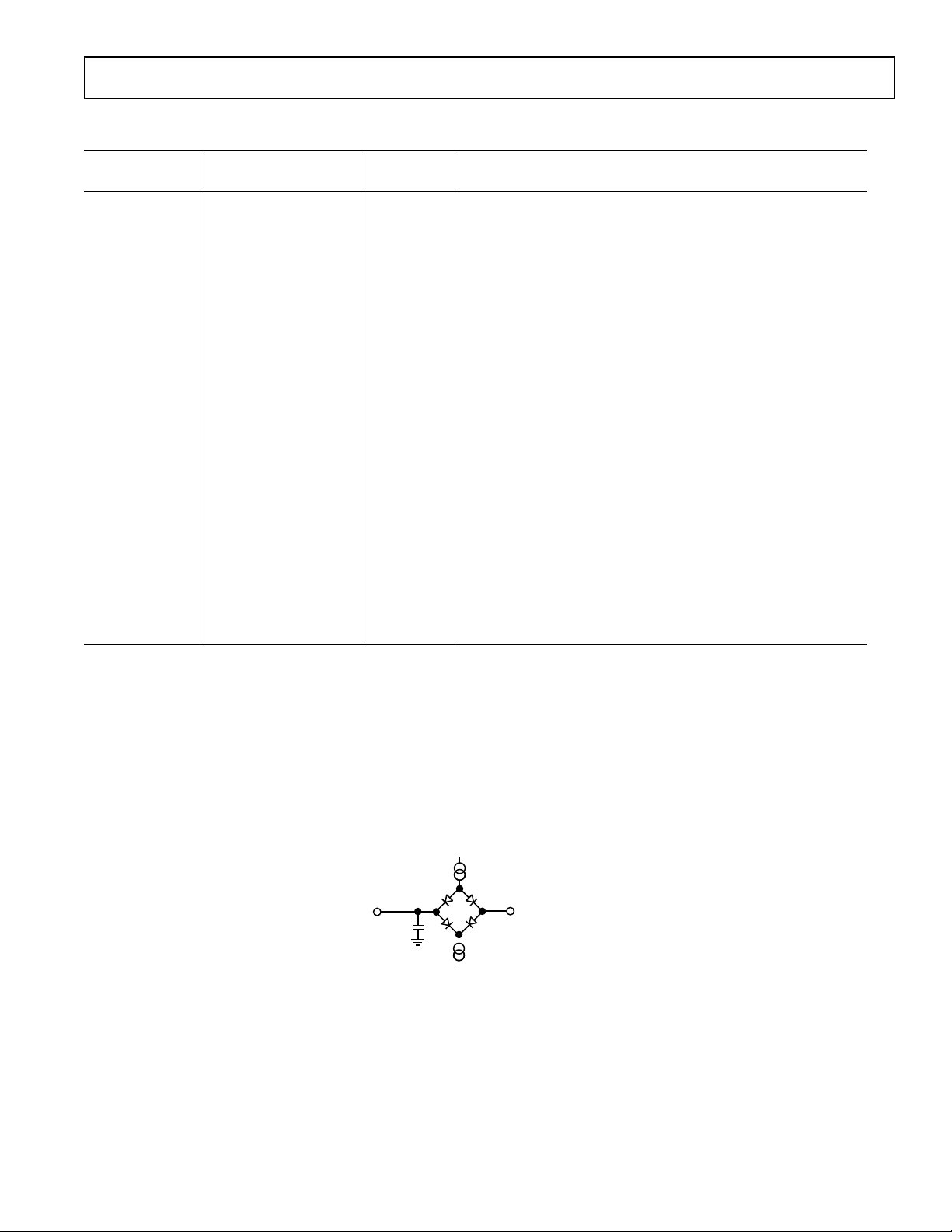

Analog Devices AD7715 c Datasheet

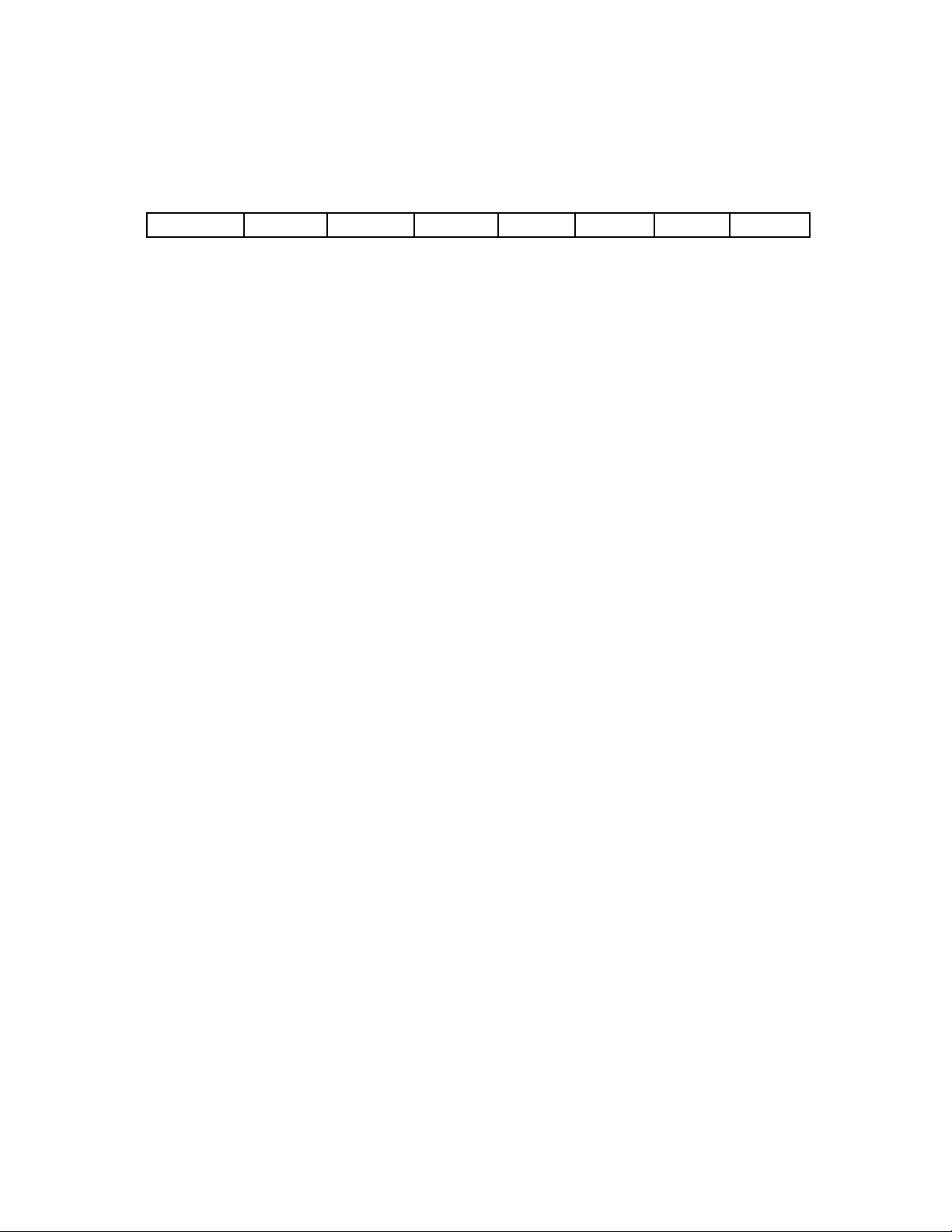

PGABUFFER

CHARGE BALANCING

A/D CONVERTER

SIGMA-DELTA

MODULATOR

DIGITAL

FILTER

REF IN(–) REF IN(+)

AV

DD

DV

DD

A = 1–128

MCLK IN

MCLK OUT

RESET

AIN(+)

AIN(–)

SERIAL

INTERFACE

REGISTER BANK

SCLK

CS

DIN

DOUT

DRDY

CLOCK

GENERATION

AGND

DGND

AD7715

3 V/5 V, 450 A

a

FEATURES

Charge-Balancing ADC

16 Bits No Missing Codes

0.0015% Nonlinearity

Programmable Gain Front End

Gains of 1, 2, 32 and 128

Differential Input Capability

Three-Wire Serial Interface

SPI™, QSPI™, MICROWIRE™ and DSP Compatible

Ability to Buffer the Analog Input

3 V (AD7715-3) or 5 V (AD7715-5) Operation

Low Supply Current: 450␣ A max @ 3␣ V Supplies

Low-Pass Filter with Programmable Output Update

16-Lead SOIC/DIP/TSSOP

GENERAL DESCRIPTION

The AD7715 is a complete analog front end for low frequency

measurement applications. The part can accept low level input

signals directly from a transducer and outputs a serial digital

word. It employs a sigma-delta conversion technique to realize

up to 16 bits of no missing codes performance. The input signal

is applied to a proprietary programmable gain front end based

around an analog modulator. The modulator output is processed by an on-chip digital filter. The first notch of this digital

filter can be programmed via the on-chip control register allowing adjustment of the filter cutoff and output update rate.

The AD7715 features a differential analog input as well as a differential reference input. It operates from a single supply (+3␣ V

or +5␣ V). It can handle unipolar input signal ranges of 0 mV to

+20␣ mV, 0 mV to +80␣ mV, 0 V to +1.25␣ V and 0 V to +2.5␣ V.

It can also handle bipolar input signal ranges of ±20␣ mV, ±80␣ mV,

±1.25␣ V and ±2.5␣ V. These bipolar ranges are referenced to

the negative input of the differential analog input. The AD7715

thus performs all signal conditioning and conversion for a singlechannel system.

The AD7715 is ideal for use in smart, microcontroller or DSP

based systems. It features a serial interface that can be configured for three-wire operation. Gain settings, signal polarity and

update rate selection can be configured in software using the

input serial port. The part contains self-calibration and system

calibration options to eliminate gain and offset errors on the

part itself or in the system.

16-Bit, Sigma-Delta ADC

AD7715*

FUNCTIONAL BLOCK DIAGRAM

CMOS construction ensures very low power dissipation, and the

power-down mode reduces the standby power consumption to

50␣ µW typ. The part is available in a 16-lead, 0.3 inch-wide,

plastic dual-in-line package (DIP) as well as a 16-lead 0.3 inchwide small outline (SOIC) package and a 16-lead TSSOP package.

PRODUCT HIGHLIGHTS

1. The AD7715 consumes less than 450␣ µA in total supply

current at 3 V supplies and 1␣ MHz master clock, making it

ideal for use in low-power systems. Standby current is less

than 10␣ µA.

2. The programmable gain input allows the AD7715 to accept

input signals directly from a strain gage or transducer removing a considerable amount of signal conditioning.

3. The AD7715 is ideal for microcontroller or DSP processor

applications with a three-wire serial interface reducing the

number of interconnect lines and reducing the number of

opto-couplers required in isolated systems. The part contains on-chip registers which allow software control over

output update rate, input gain, signal polarity and calibration

modes.

4. The part features excellent static performance specifications

with 16-bits no missing codes, ±0.0015% accuracy and low

rms noise (<550␣ nV). Endpoint errors and the effects of

temperature drift are eliminated by on-chip calibration options, which remove zero-scale and full-scale errors.

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corporation.

*Protected by U.S. Patent No: 5,134,401.

See page 30 for data sheet index.

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

AD7715-5–SPECIFICATIONS

f

= 2.4576␣ MHz unless otherwise noted. All specifications T

CLK IN

Parameter A Version

(AVDD = +5␣ V, DVDD = +3␣ V or +5␣ V, REF IN(+) = +2.5␣ V; REF␣ IN(–) = AGND;

to T

MIN

1

unless otherwise noted.)

MAX

Unit Conditions/Comments

STATIC PERFORMANCE

No Missing Codes 16 Bits min Guaranteed by Design. Filter Notch ≤ 60␣ Hz

Output Noise See Tables V to VIII Depends on Filter Cutoffs and Selected Gain

Integral Nonlinearity ±0.0015 % of FSR max Filter Notch ≤ 60␣ Hz

Unipolar Offset Error See Note 2

Unipolar Offset Drift

Bipolar Zero Error See Note 2

Bipolar Zero Drift

Positive Full-Scale Error

Full-Scale Drift

Gain Error

Gain Drift

6

3, 7

Bipolar Negative Full-Scale Error

Bipolar Negative Full-Scale Drift

3, 5

3

3

4

0.5 µV/°C typ

0.5 µV/°C typ

See Note 2

0.5 µV/°C typ

See Note 2

2

3

0.5 ppm of FSR/°C typ

±0.0015 % of FSR max Typically ±0.0004%

1 µV/°C typ For Gains of 1 and 2

0.6 µV/°C typ For Gains of 32 and 128

ANALOG INPUTS/REFERENCE INPUTS Specifications for AIN and REF IN Unless Noted

Input Common-Mode Rejection (CMR) 90 dB min at DC. Typically 102 dB

Normal-Mode 50 Hz Rejection

Normal-Mode 60 Hz Rejection

Common-Mode 50 Hz Rejection

Common-Mode 60 Hz Rejection

Common-Mode Voltage Range

Absolute AIN/REF IN Voltage

Absolute/Common-Mode AIN Voltage

AIN DC Input Current

AIN Sampling Capacitance

AIN Differential Voltage Range

AIN Input Sampling Rate, f

8

8

8

8

9

8

8

8

10

S

98 dB min For Filter Notches of 25 Hz, 50 Hz, ±0.02 × f

98 dB min For Filter Notches of 20 Hz, 60 Hz, ±0.02 × f

150 dB min For Filter Notches of 25 Hz, 50 Hz, ±0.02 × f

150 dB min For Filter Notches of 20 Hz, 60 Hz, ±0.02 × f

AGND to AV

V min to V max AIN for BUF Bit of Setup Register = 0 and REF IN

DD

AGND – 30 mV V min AIN for BUF Bit of Setup Register = 0 and REF IN

AV

+ 30␣ mV V max

9

DD

AGND + 50␣ mV V min BUF Bit of Setup Register = 1

AV

– 1.5␣ V V max

DD

1 nA max

10 pF max

0 to +V

±V

GAIN × f

f

CLK␣ IN

/GAIN11nom Unipolar Input Range (B/U Bit of Setup Register = 1)

REF

/GAIN nom Bipolar Input Range (B/U Bit of Setup Register = 0)

REF

/64 For Gains of 1 and 2

CLK␣ IN

/8 For Gains of 32 and 128

NOTCH

NOTCH

NOTCH

NOTCH

REF IN(+) – REF IN(–) Voltage +2.5 V nom ±1% for Specified Performance. Functional with

Lower V

REF IN Input Sampling Rate, f

S

f

CLK IN

/64

REF

LOGIC INPUTS

Input Current ±10 µA max

All Inputs Except MCLK IN

V

, Input Low Voltage 0.8 V max DVDD = +5␣ V

INL

V

, Input Low Voltage 0.4 V max DVDD = +3.3␣ V

INL

V

, Input High Voltage 2.4 V min DVDD = +5 V

INH

V

, Input High Voltage 2.0 V min

INH

MCLK IN Only

V

, Input Low Voltage 0.8 V max DVDD = +5␣ V

INL

V

, Input Low Voltage 0.4 V max DVDD = +3.3␣ V

INL

V

, Input High Voltage 3.5 V min DVDD = +5␣ V

INH

V

, Input High Voltage 2.5 V min DVDD = +3.3␣ V

INH

LOGIC OUTPUTS (Including MCLK OUT)

, Output Low Voltage 0.4 V max I

V

OL

V

, Output Low Voltage 0.4 V max I

OL

V

, Output High Voltage 4.0 V min I

OH

V

, Output High Voltage DVDD – 0.6 V V min I

OH

Floating State Leakage Current ±10 µA max

Floating State Output Capacitance

13

9 pF typ

= 800␣ µA Except for MCLK OUT12. DVDD = +5␣ V

SINK

= 100␣ µA Except for MCLK OUT12. DVDD = +3.3␣ V

SINK

= 200 µA Except for MCLK OUT12. DVDD = +5␣ V

SOURCE

= 100 µA Except for MCLK OUT12. DVDD = +3.3␣ V

SOURCE

Data Output Coding Binary Unipolar Mode

Offset Binary Bipolar Mode

REV. C–2–

AD7715

AD7715-3–SPECIFICATIONS

REF␣ IN(–) = AGND; f

Parameter A Version

STATIC PERFORMANCE

No Missing Codes 16 Bits min Guaranteed by Design. Filter Notch ≤ 60␣ Hz

Output Noise See Tables IX to XII Depends on Filter Cutoffs and Selected Gain

Integral Nonlinearity ±0.0015 % of FSR max Filter Notch ≤ 60␣ Hz

Unipolar Offset Error See Note 2

Unipolar Offset Drift

Bipolar Zero Error See Note 2

Bipolar Zero Drift

Positive Full-Scale Error

Full-Scale Drift

Gain Error

Gain Drift

Bipolar Negative Full-Scale Error

Bipolar Negative Full-Scale Drift

ANALOG INPUTS/REFERENCE INPUTS Specifications for AIN and REF IN Unless Noted

Input Common-Mode Rejection (CMR) 90 dB min at DC. Typically 102 dB

Normal-Mode 50 Hz Rejection

Normal-Mode 60 Hz Rejection

Common-Mode 50 Hz Rejection

Common-Mode 60 Hz Rejection

Common-Mode Voltage Range

Absolute AIN/REF IN Voltage

Absolute/Common-Mode AIN Voltage

AIN DC Input Current

AIN Sampling Capacitance

AIN Differential Voltage Range

AIN Input Sampling Rate, f

REF IN(+) – REF IN(–) Voltage +1.25 V nom ±1% for Specified Performance. Functional with Lower V

REF IN Input Sampling Rate, f

LOGIC INPUTS

Input Current ±10 µA max

All Inputs Except MCLK IN

MCLK IN Only

LOGIC OUTPUTS (Including MCLK OUT)

V

OL

VOH, Output High Voltage DVDD – 0.6 V min I

Floating State Leakage Current ±10 µA max

Floating State Output Capacitance

Data Output Coding Binary Unipolar Mode

6

3, 7

V

, Input Low Voltage 0.8 V max

INL

V

, Input High Voltage 2.0 V min

INH

V

, Input Low Voltage 0.4 V max

INL

V

, Input High Voltage 2.5 V min

INH

, Output Low Voltage 0.4 V max I

= 2.4576␣ MHz unless otherwise noted. All specifications T

CLK IN

3

3

4

3, 5

0.2 µV/°C typ

0.2 µV/°C typ

See Note 2

0.2 µV/°C typ

See Note 2

2

3

0.2 ppm of FSR/°C typ

±0.003 % of FSR max Typically ±0.0004%

1 µV/°C typ For Gains of 1 and 2

0.6 µV/°C typ For Gains of 32 and 128

8

8

8

8

9

8

8

8

10

S

S

13

98 dB min For Filter Notches of 25 Hz, 50 Hz, ±0.02 × f

98 dB min For Filter Notches of 20 Hz, 60 Hz, ±0.02 × f

150 dB min For Filter Notches of 25 Hz, 50 Hz, ±0.02 × f

150 dB min For Filter Notches of 20 Hz, 60 Hz, ±0.02 × f

AGND to AV

AGND – 30 mV V min AIN for BUF Bit of Setup Register = 0 and REF IN

AV

9

DD

AGND + 50␣ mV V min BUF Bit of Setup Register = 1

AV

DD

1 nA max

10 pF max

0 to +V

±V

REF

GAIN × f

f

CLK␣ IN

f

CLK IN

9 pF typ

Offset Binary Bipolar Mode

(AVDD = +3␣ V, DVDD = +3 V, REF IN (+) = +1.25␣ V;

to T

MIN

1

DD

Unit Conditions/Comments

V min to V max AIN for BUF Bit of Setup Register = 0 and REF IN

+ 30␣ mV V max

– 1.5␣ V V max

/GAIN11nom Unipolar Input Range (B/U Bit of Setup Register = 1)

REF

/GAIN nom Bipolar Input Range (B/U Bit of Setup Register = 0)

/64 For Gains of 1 and 2

CLK␣ IN

/8 For Gains of 32 and 128

/64

unless otherwise noted.)

MAX

= 100␣ µA Except for MCLK OUT

SINK

= 100 µA Except for MCLK OUT

SOURCE

NOTCH

NOTCH

NOTCH

NOTCH

12

12

REF

REV. C

–3–

AD7715–SPECIFICATIONS

(AD7715-5); REF␣ IN(–) = AGND; MCLK␣ IN = 1␣ MHz to 2.4576␣ MHz unless otherwise noted. All specifications T

Pa

rameter A Version Unit Conditions/Comments

SYSTEM CALIBRATION

Positive Full-Scale Calibration Limit

Negative Full-Scale Calibration Limit

Offset Calibration Limit

Input Span

15

15

A (AVDD = +3␣ V to +5␣ V, DVDD = +3␣ V to +5␣ V, REF IN(+) = +1.25␣ V (AD7715-3) or +2.5␣ V

to T

unless otherwise noted.)

MAX

14

14

(1.05 × V

–(1.05 × V

–(1.05 × V

0.8 × V

REF

(2.1 × V

REF

MIN

)/GAIN V max GAIN Is the Selected PGA Gain (1, 2, 32 or 128)

REF

)/GAIN V max GAIN Is the Selected PGA Gain (1, 2, 32 or 128)

REF

)/GAIN V max GAIN Is the Selected PGA Gain (1, 2, 32 or 128)

REF

/GAIN V min GAIN Is the Selected PGA Gain (1, 2, 32 or 128)

)/GAIN V max GAIN Is the Selected PGA Gain (1, 2, 32 or 128)

POWER REQUIREMENTS

Power Supply Voltages

AV

Voltage (AD7715-3) +3 to +3.6 V For Specified Performance

DD

AV

Voltage (AD7715-5) +4.75 to +5.25 V For Specified Performance

DD

DV

Voltage +3 to +5.25 V For Specified Performance

DD

Power Supply Currents

AV

Current AVDD = 3.3␣ V or 5␣ V. Gain = 1 to 128 (f

DD

Gain = 1 or 2 (f

= 2.4576␣ MHz)

CLK IN

= 1␣ MHz) or

CLK IN

0.27 mA max Typically 0.2␣ mA. BUF Bit of Setup Register = 0

0.6 mA max Typically 0.4␣ mA. BUF Bit of Setup Register = 1

AV

= 3.3␣ V or 5␣ V. Gain = 32 or 128 (f

DD

= 2.4576␣ MHz)

CLK IN

16

0.5 mA max Typically 0.3␣ mA. BUF Bit of Setup Register = 0

1.1 mA max Typically 0.8␣ mA. BUF Bit of Setup Register = 1

Digital I/Ps = 0␣ V or DVDD. External MCLK IN

0.18 mA max Typically 0.15␣ mA. DV

0.4 mA max Typically 0.3␣ mA. DV

0.5 mA max Typically 0.4␣ mA. DV

0.8 mA max Typically 0.6␣ mA. DV

See Note 19 dB typ

17

AV

DD

= DV

= +3.3␣ V. Digital I/Ps = 0␣ V or DVDD. External MCLK IN

DD

= 3.3␣ V. f

DD

= 5␣ V. f

DD

= 3.3␣ V. f

DD

= 5␣ V. f

DD

CLK IN

= 1␣ MHz

CLK IN

= 2.4576␣ MHz

CLK IN

= 2.4576␣ MHz

CLK IN

= 1␣ MHz

Current

17

18

DV

DD

Power Supply Rejection

Normal-Mode Power Dissipation

1.5 mW max BUF Bit = 0. All Gains 1␣ MHz Clock

2.65 mW max BUF Bit = 1. All Gains 1␣ MHz Clock

Normal-Mode Power Dissipation

17

3.3 mW max BUF Bit = 0. Gain = 32 or 128 @ f

5.3 mW max BUF Bit = 1. Gain = 32 or 128 @ f

AV

= DV

DD

= +5␣ V. Digital I/Ps = 0␣ V or DVDD. External MCLK IN

DD

= 2.4576␣ MHz

CLK IN

= 2.4576␣ MHz

CLK IN

3.25 mW max BUF Bit = 0. All Gains 1␣ MHz Clock

5 mW max BUF Bit = 1. All Gains 1␣ MHz Clock

6.5 mW max BUF Bit = 0. Gain = 32 or 128 @ f

Standby (Power-Down) Current

Standby (Power-Down) Current

NOTES

1

Temperature Range as follows: A Version, –40°C to +85°C.

2

A calibration is effectively a conversion so these errors will be of the order of the conversion noise shown in Tables V to XII. This applies after calibration at the

temperature of interest.

3

Recalibration at any temperature will remove these drift errors.

4

Positive Full-Scale Error includes Zero-Scale Errors (Unipolar Offset Error or Bipolar Zero Error) and applies to both unipolar and bipolar input ranges.

5

Full-Scale Drift includes Zero-Scale Drift (Unipolar Offset Drift or Bipolar Zero Drift) and applies to both unipolar and bipolar input ranges.

6

Gain Error does not include Zero-Scale Errors. It is calculated as Full-Scale Error–Unipolar Offset Error for unipolar ranges and Full-Scale Error–Bipolar Zero Error

for bipolar ranges.

7

Gain Error Drift does not include Unipolar Offset Drift/Bipolar Zero Drift. It is effectively the drift of the part if zero scale calibrations only were performed.

8

These numbers are guaranteed by design and/or characterization.

9

This common-mode voltage range is allowed provided that the input voltage on AIN(+) or AIN(–) does not go more positive than A VDD + 30 mV or go more negative than AGND – 30␣ mV.

10

The analog input voltage range on AIN(+) is given here with respect to the voltage on AIN(–). The absolute voltage on the analog inputs should not go more positive than AVDD + 30␣ mV or go more negative than AGND␣ – 30␣ mV.

11

V

= REF IN(+) – REF IN(–).

REF

12

These logic output levels apply to the MCLK OUT only when it is loaded with one CMOS load.

13

Sample tested at +25°C to ensure compliance.

14

After calibration, if the analog input exceeds positive full scale, the converter will output all 1s. If the analog input is less than negative full scale, then the device will

output all 0s.

15

These calibration and span limits apply provided the absolute voltage on the analog inputs does not exceed AVDD + 30␣ mV or go more negative than AGND –

30␣ mV. The offset calibration limit applies to both the unipolar zero point and the bipolar zero point.

16

Assumes CLK Bit of Setup Register is set to correct status corresponding to the master clock frequency.

17

When using a crystal or ceramic resonator across the MCLK pins as the clock source for the device, the DVDD current and power dissipation will vary depending on

the crystal or resonator type (see Clocking and Oscillator Circuit section).

18

Measured at dc and applies in the selected passband. PSRR at 50␣ Hz will exceed 120␣ dB with filter notches of 25 Hz or 50␣ Hz. PSRR at 60␣ Hz will exceed 120␣ dB

with filter notches of 20 Hz or 60␣ Hz.

19

PSRR depends on gain. Gain of 1: 85 dB typ; Gain of 2: 90 dB typ; Gains of 32 and 128: 95 dB typ.

20

If the external master clock continues to run in standby mode, the standby current increases to 50␣ µA typical. When using a crystal or ceramic resonator across the

20

20

MCLK pins as the clock source for the device, the internal oscillator continues to run in standby mode and the power dissipation depends on the crystal or

resonator type (see Standby Mode section).

Specifications subject to change without notice.

9.5 mW max BUF Bit = 1. Gain = 32 or 128 @ f

20 µA max External MCLK IN = 0␣ V or DVDD. Typically 10␣ µA. VDD = +5␣ V

10 µA max External MCLK IN = 0␣ V or DVDD. Typically 5␣ µA. VDD = +3.3␣ V

–4–

= 2.4576␣ MHz

CLK IN

= 2.4576␣ MHz

CLK IN

REV. C

AD7715

TIMING CHARACTERISTICS

Limit at T

MIN

, T

MAX

(DVDD = +3␣ V to +5.25␣ V; AVDD = +3␣ V to +5.25␣ V; AGND = DGND = 0 V; f

1, 2

Input Logic 0 = 0 V, Logic 1 = DVDD, unless otherwise noted)

= 2.4576␣ MHz;

CLKIN

Parameter (A Version) Unit Conditions/Comments

3, 4

f

CLKIN

400 kHz min Master Clock Frequency: Crystal Oscillator or Externally Supplied

2.5 MHz max for Specified Performance

t

CLK IN LO

t

CLK IN HI

t

1

t

2

0.4 × t

0.4 × t

500 × t

CLK IN

CLK IN

CLK IN

ns min Master Clock Input Low Time. t

ns min Master Clock Input High Time

ns nom DRDY High Time

100 ns min RESET Pulsewidth

CLK IN

= 1/f

CLK IN

Read Operation

t

3

t

4

5

t

5

t

6

t

7

t

8

6

t

9

t

10

0 ns min DRDY to CS Setup Time

120 ns min CS Falling Edge to SCLK Rising Edge Setup Time

0 ns min SCLK Falling Edge to Data Valid Delay

80 ns max DV

100 ns max DV

= +5␣ V

DD

= +3.3␣ V

DD

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0 ns min CS Rising Edge to SCLK Rising Edge Hold Time

10 ns min Bus Relinquish Time after SCLK Rising Edge

60 ns max DV

100 ns max DV

100 ns max SCLK Falling Edge to DRDY High

= +5␣ V

DD

= +3.3␣ V

DD

7

Write Operation

t

11

t

12

t

13

t

14

t

15

t

16

NOTES

1

Sample tested at +25°C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of D VDD) and timed from a voltage level of 1.6 V.

2

See Figures 6 and 7.

3

CLKIN Duty Cycle range is 45% to 55%. CLKIN must be supplied whenever the AD7715 is not in Standby mode. If no clock is present in this case, the

device can draw higher current than specified and possibly become uncalibrated.

4

The AD7715 is production tested with f

5

These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross the VOL or VOH limits.

6

These numbers are derived from the measured time taken by the data output to change 0.5␣ V when loaded with the circuit of Figure 1. The measured number is

then extrapolated back to remove effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the

true bus relinquish times of the part and as such are independent of external bus loading capacitances.

7

DRDY returns high after the first read from the device after an output update. The same data can be read again, if required, while DRDY is high although care

should be taken that subsequent reads do not occur close to the next output update.

Specifications subject to change without notice.

120 ns min CS Falling Edge to SCLK Rising Edge Setup Time

30 ns min Data Valid to SCLK Rising Edge Setup Time

20 ns min Data Valid to SCLK Rising Edge Hold Time

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0 ns min CS Rising Edge to SCLK Rising Edge Hold Time

at 2.4576␣ MHz (1␣ MHz for some IDD tests). It is guaranteed by characterization to operate at 400␣ kHz.

CLKIN

REV. C

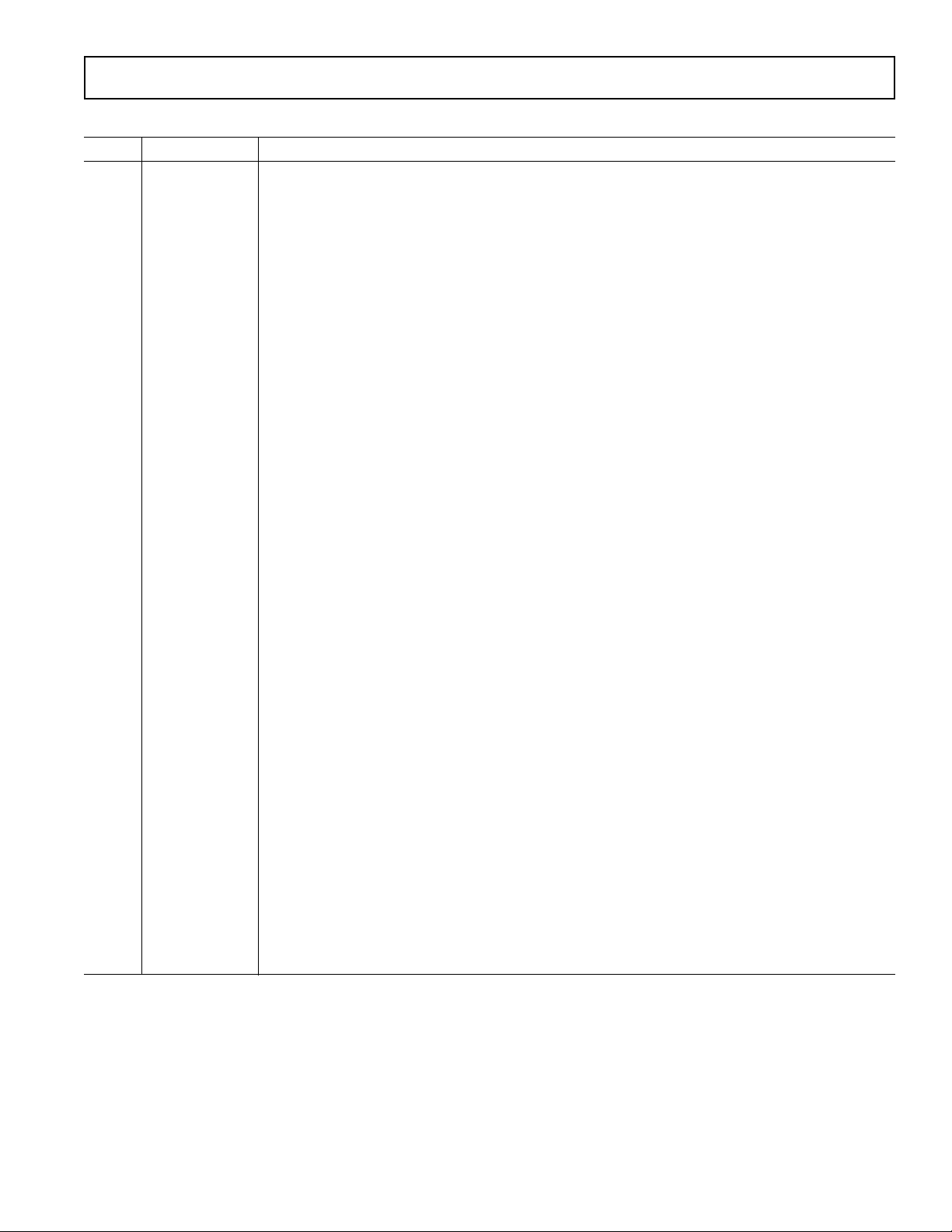

I

(800mA AT DVDD = 5V

OUTPUT

TO

PIN

50pF

SINK

100mA AT DV

+1.6V

I

(200mA AT DVDD = 5V

SOURCE

100mA AT DV

DD

= 3.3V)

= 3.3V)

DD

Figure 1. Load Circuit for Access Time and Bus Relinquish Time

–5–

AD7715

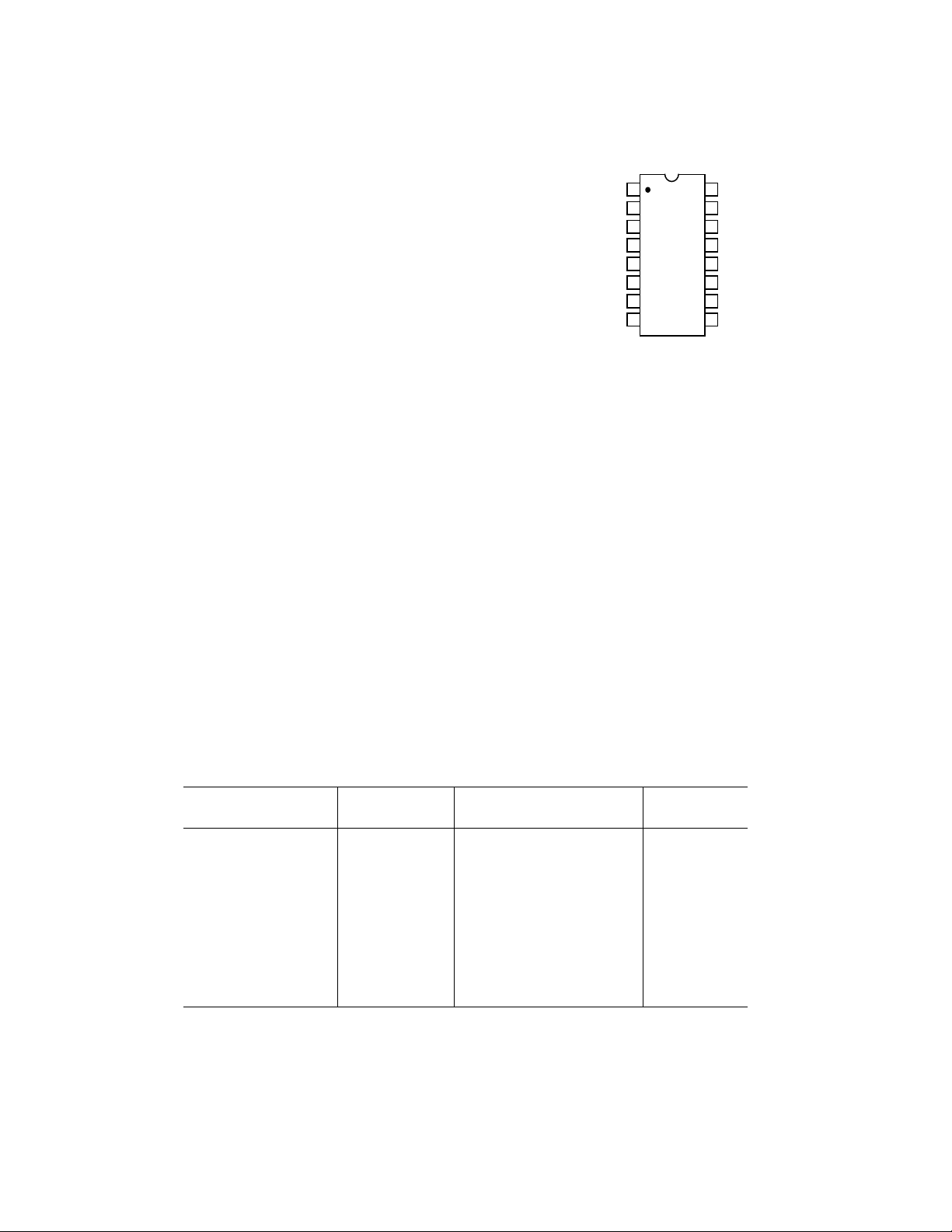

14

13

12

11

16

15

10

9

8

1

2

3

4

7

6

5

TOP VIEW

(Not to Scale)

AD7715

SCLK

DOUT

DIN

DV

DD

DGND

MCLK IN

MCLK OUT

CS

REF IN(+)

AGND

DRDY

RESET

AV

DD

AIN(+)

AIN(–)

REF IN(–)

ABSOLUTE MAXIMUM RATINGS*

(TA = +25°C unless otherwise noted)

AVDD to AGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

to DGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

AV

DD

to DVDD . . . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

AV

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

DV

DD

to DGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

DV

DD

DGND to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

Analog Input Voltage to AGND . . . . . –0.3 V to AV

Reference Input Voltage to AGND . . . –0.3 V to AV

Digital Input Voltage to DGND . . . . . –0.3 V to DV

Digital Output Voltage to DGND . . . . –0.3 V to DV

+ 0.3␣ V

DD

+ 0.3␣ V

DD

+ 0.3 V

DD

+ 0.3 V

DD

Operating Temperature Range

Commercial (A Version) . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . +150°C

Plastic DIP Package, Power Dissipation . . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 105°C/W

θ

JA

Lead Temperature, (Soldering, 10 sec) . . . . . . . . . . +260°C

SOIC Package, Power Dissipation . . . . . . . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 75°C/W

θ

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

TSSOP Package, Power Dissipation . . . . . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 128°C/W

θ

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

Power Dissipation (Any Package) to +75°C . . . . . . . . 450 mW

ESD Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .>4000 V

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

PIN CONFIGURATION

DIP, SOIC and TSSOP

ORDERING GUIDE

AV

DD

Temperature Package

Model Supply Range Options*

AD7715AN-5 5 V –40°C to +85°C N-16

AD7715AR-5 5 V –40°C to +85°C R-16

AD7715ARU-5 5 V –40°C to +85°C RU-16

AD7715AN-3 3 V –40°C to +85°C N-16

AD7715AR-3 3 V –40°C to +85°C R-16

AD7715ARU-3 3 V –40°C to +85°C RU-16

AD7715AChips-5 5 V –40°C to +85°CDie

AD7715AChips-3 3 V –40°C to +85°CDie

EVAL-AD7715-5EB 5 V Evaluation Board

EVAL-AD7715-3EB 3 V Evaluation Board

*N = Plastic DIP; R = SOIC RU = TSSOP.

–6–

REV. C

AD7715

PIN FUNCTION DESCRIPTION

Pin No. Mnemonic Function

1 SCLK Serial Clock. Logic Input. An external serial clock is applied to this input to access serial data from

the AD7715. This serial clock can be a continuous clock with all data transmitted in a continuous

train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to the AD7715 in smaller batches of data.

2 MCLK IN Master Clock signal for the device. This can be provided in the form of a crystal/resonator or exter-

nal clock. A crystal/resonator can be tied across the MCLK IN and MCLK OUT pins. Alternatively, the MCLK IN pin can be driven with a CMOS-compatible clock and MCLK OUT left

unconnected. The part is specified with clock input frequencies of both 1␣ MHz and 2.4576␣ MHz.

3 MCLK OUT When the master clock for the device is a crystal/resonator, the crystal/resonator is connected be-

tween MCLK IN and MCLK␣ OUT. If an external clock is applied to MCLK IN, MCLK␣ OUT

provides an inverted clock signal. This clock can be used to provide a clock source for external

circuitry.

4 CS Chip Select. Active low Logic Input used to select the AD7715. With this input hardwired low, the

AD7715 can operate in its three-wire interface mode with SCLK, DIN and DOUT used to interface to the device. CS can be used to select the device in systems with more than one device on the

serial bus or as a frame synchronization signal in communicating with the AD7715.

5 RESET Logic Input. Active low input which resets the control logic, interface logic, calibration coefficients,

digital filter and analog modulator of the part to power-on status.

6AV

DD

7 AIN(+) Analog Input. Positive input of the programmable gain differential analog input to the AD7715.

8 AIN(–) Analog Input. Negative input of the programmable gain differential analog input to the AD7715.

9 REF IN(+) Reference Input. Positive input of the differential reference input to the AD7715. The reference

10 REF IN(–) Reference Input. Negative input of the differential reference input to the AD7715. The REF␣ IN(–)

11 AGND Ground reference point for analog circuitry. For correct operation of the AD7715, no voltage on

12 DRDY Logic Output. A logic low on this output indicates that a new output word is available from the

13 DOUT Serial Data Output with serial data being read from the output shift register on the part. This output

14 DIN Serial Data Input with serial data being written to the input shift register on the part. Data from this

15 DV

DD

16 DGND Ground reference point for digital circuitry.

Analog Positive Supply Voltage, +3.3␣ V nominal (AD7715-3) or +5␣ V nominal (AD7715-5).

input is differential with the provision that REF IN(+) must be greater than REF IN(–).

REF␣ IN(+) can lie anywhere between AV

can lie anywhere between AV

and AGND provided REF␣ IN(+) is greater than REF␣ IN(–).

DD

and AGND.

DD

any of the other pins should go more than 30 mV negative with respect to AGND.

AD7715 data register. The DRDY pin will return high upon completion of a read operation of a full

output word. If no data read has taken place between output updates, the DRDY line will return

high for 500 × t

cycles prior to the next output update. While DRDY is high, a read operation

CLK␣ IN

should not be attempted or in progress to avoid reading from the data register as it is being updated.

The DRDY line will return low again when the update has taken place. DRDY is also used to indi-

cate when the AD7715 has completed its on-chip calibration sequence.

shift register can contain information from the setup register, communications register or data register depending on the register selection bits of the Communications Register.

input shift register is transferred to the setup register or communications register depending on the

register selection bits of the Communications Register.

Digital Supply Voltage, +3.3␣ V or +5 V nominal.

REV. C

–7–

AD7715

TERMINOLOGY

Integral Nonlinearity

This is the maximum deviation of any code from a straight line

passing through the endpoints of the transfer function. The endpoints of the transfer function are Zero-Scale (not to be confused

with Bipolar Zero), a point 0.5 LSB below the first code transition

(000 . . . 000 to 000 . . . 001) and Full-Scale, a point 0.5␣ LSB

above the last code transition (111 . . . 110 to 111 . . . 111). The

error is expressed as a percentage of full scale.

Positive Full-Scale Error

Positive Full-Scale Error is the deviation of the last code transition (111 . . . 110 to 111 . . . 111) from the ideal AIN(+) voltage

(AIN(–) + V

/GAIN –3/2 LSBs). It applies to both unipolar

REF

and bipolar analog input ranges.

Unipolar Offset Error

Unipolar Offset Error is the deviation of the first code transition

from the ideal AIN(+) voltage (AIN(–) + 0.5 LSB) when operating in the unipolar mode.

Bipolar Zero Error

This is the deviation of the midscale transition (0111 . . . 111

to 1000 . . . 000) from the ideal AIN(+) voltage (AIN(–)

– 0.5␣ LSB) when operating in the bipolar mode.

Gain Error

This is a measure of the span error of the ADC. It includes fullscale errors but not zero-scale errors. For unipolar input ranges

it is defined as (full scale error–unipolar offset error) while for

bipolar input ranges it is defined as (full-scale error–bipolar zero

error).

Bipolar Negative Full-Scale Error

This is the deviation of the first code transition from the ideal

AIN(+) voltage (AIN(–) – V

/GAIN + 0.5␣ LSB), when oper-

REF

ating in the bipolar mode.

Positive Full-Scale Overrange

Positive full-scale overrange is the amount of overhead available

to handle input voltages on AIN(+) input greater than AIN(–) +

/GAIN (for example, noise peaks or excess voltages due to

V

REF

system gain errors in system calibration routines) without introducing errors due to overloading the analog modulator or overflowing the digital filter.

Negative Full-Scale Overrange

This is the amount of overhead available to handle voltages on

AIN(+) below AIN(–) –V

/GAIN without overloading the

REF

analog modulator or overflowing the digital filter. Note that the

analog input will accept negative voltage peaks even in the unipolar mode provided that AIN(+) is greater than AIN(–) and

greater than AGND –␣ 30␣ mV.

Offset Calibration Range

In the system calibration modes, the AD7715 calibrates its

offset with respect to the analog input. The offset calibration

range specification defines the range of voltages that the

AD7715 can accept and still calibrate offset accurately.

Full-Scale Calibration Range

This is the range of voltages that the AD7715 can accept in the

system calibration mode and still calibrate full scale correctly.

Input Span

In system calibration schemes, two voltages applied in sequence

to the AD7715’s analog input define the analog input range.

The input span specification defines the minimum and maximum input voltages from zero to full scale that the AD7715 can

accept and still calibrate gain accurately.

ON-CHIP REGISTERS

The part contains four on-chip registers which can be accessed by via the serial port on the part. The first of these is a Communications Register that decides whether the next operation is a read or write operation and also decides which register the read or write

operation accesses. All communications to the part must start with a write operation to the Communications Register. After poweron or RESET, the device expects a write to its Communications Register. The data written to this register determines whether the

next operation to the part is a write or a read operation and also determines to which register this read or write operation occurs.

Therefore, write access to any of the other registers on the part starts with a write operation to the Communications Register followed by a write to the selected register. A read operation from any register on the part (including the Communications Register itself

and the output data register) starts with a write operation to the Communications Register followed by a read operation from the

selected register. The Communication Register also controls the standby mode and the operating gain of the part. The DRDY status

is also available by reading from the Communications Register. The second register is a Setup Register that determines calibration

modes, filter selection and bipolar/unipolar operation. The third register is the Data Register from which the output data from the

part is accessed. The final register is a Test Register that is accessed when testing the device. It is advised that the user does not

attempt to access or change the contents of the test register as it may lead to unspecified operation of the device. The registers are

discussed in more detail in the following sections.

–8–

REV. C

AD7715

Communications Register (RS1, RS0 = 0, 0)

The Communications Register is an eight-bit register from which data can either be read or to which data can be written. All communications to the part must start with a write operation to the Communications Register. The data written to the Communications

Register determines whether the next operation is a read or write operation and to which register this operation takes place. Once the

subsequent read or write operation to the selected register is complete, the interface returns to where it expects a write operation to

the Communications Register. This is the default state of the interface, and on power-up or after a RESET, the AD7715 is in this

default state waiting for a write operation to the Communications Register. In situations where the interface sequence is lost, if a

write operation to the device of sufficient duration (containing at least 32 serial clock cycles) takes place with DIN high, the AD7715

returns to this default state. Table I outlines the bit designations for the Communications Register.

Table I. Communications Register

0/DRDY ZERO RS1 RS0 R/W STBY G1 G0

0/DRDY For a write operation, a 0 must be written to this bit so that the write operation to the Communications Reg-

ister actually takes place. If a 1 is written to this bit, the part will not clock on to subsequent bits in the register. It will stay at this bit location until a 0 is written to this bit. Once a 0 is written to this bit, the next 7 bits

will be loaded to the Communications Register. For a read operation, this bit provides the status of the

DRDY flag from the part. The status of this bit is the same as the DRDY output pin.

ZERO For a write operation, a 0 must be written to this bit for correct operation of the part. Failure to do this will

result in unspecified operation of the device. For a read operation, a 0 will be read back from this bit location.

RS1– RS0 Register Selection Bits. These bits select to which one of four on-chip registers the next read or write opera-

tion takes place as shown in Table II along with the register size. When the read or write to the selected register is complete, the part returns to where it is waiting for a write operation to the Communications Register.

It does not remain in a state where it will continue to access the selected register.

R/W Read/Write Select. This bit selects whether the next operation is a read or write operation to the selected

register. A 0 indicates a write cycle as the next operation to the appropriate register, while a 1 indicates a read

operation from the appropriate register.

Table II. Register Selection

RS1 RS0 Register Register Size

0 0 Communications Register 8 Bits

0 1 Setup Register 8 Bits

1 0 Test Register 8 Bits

1 1 Data Register 16 Bits

STBY Standby. Writing a 1 to this bit puts the part in its standby or power-down mode. In this mode, the part

consumes only 10␣ µA of power supply current. The part retains its calibration and control word information

when in STANDBY. Writing a 0 to this bit places the part in its normal operating mode. The default value

for this bit after power-on or RESET is 0.

G2 G1 Gain Setting

001

012

1032

1 1 128

REV. C

–9–

AD7715

Setup Register (RS1, RS0 = 0, 1); Power On/Reset Status: 28␣ Hex

The Setup Register is an eight-bit register from which data can either be read or to which data can be written. This register controls

the setup which the device is to operate in such as the calibration mode, output rate, unipolar/bipolar operation etc. Table III outlines the bit designations for the Setup Register.

Table III. Setup Register

MD1 MD0 CLK FS1 FS0 B/U BUF FSYNC

MD1 MD0 Operating Mode

0 0 Normal Mode; this is the normal mode of operation of the device whereby the device is performing normal

conversions. This is the default condition of these bits after Power-On or RESET.

0 1 Self-Calibration; this activates self-calibration on the part. This is a one step calibration sequence and when

complete the part returns to Normal Mode with MD1 and MD0 returning to 0, 0. The DRDY output or bit

goes high when calibration is initiated and returns low when this self-calibration is complete and a new valid

word is available in the data register. The zero-scale calibration is performed at the selected gain on internally

shorted (zeroed) inputs and the full-scale calibration is performed at the selected gain on an internally

generated V

1 0 Zero-Scale System Calibration; this activates zero-scale system calibration on the part. Calibration is per-

formed at the selected gain on the input voltage provided at the analog input during this calibration sequence.

This input voltage should remain stable for the duration of the calibration. The DRDY output or bit goes

high when calibration is initiated and returns low when this zero-scale calibration is complete and a new valid

word is available in the data register. At the end of the calibration, the part returns to Normal Mode with

MD1 and MD0 returning to 0, 0.

1 1 Full-Scale System Calibration; this activates full-scale system calibration on the part. Calibration is per-

formed at the selected gain on the input voltage provided at the analog input during this calibration sequence.

This input voltage should remain stable for the duration of the calibration. Once again, the DRDY output or

bit goes high when calibration is initiated and returns low when this full-scale calibration is complete and a

new valid word is available in the data register. At the end of the calibration, the part returns to Normal

Mode with MD1 and MD0 returning to 0, 0.

CLK Clock Bit. This bit should be set in accordance with the operating frequency of the AD7715. If the device has

a master clock frequency of 2.4576␣ MHz, then this bit should be set to a 1. If the device has a master clock

frequency of 1␣ MHz, then this bit should be set to a 0. This bit sets up the correct scaling currents for a given

master clock and also chooses (along with FS1 and FS0) the output update rate for the device. If this bit is

not set correctly for the master clock frequency of the device, then the device may not operate to specification. The default value for this bit after power-on or RESET is 1.

FS1, FS0 Filter Selection Bits. Along with the CLK bit, FS1 and FS0 determine the output update rate, filter first

notch and –3 dB frequency as outlined in Table IV. The on-chip digital filter provides a Sinc

filter response. In association with the gain selection, it also determines the output noise (and hence the

resolution) of the device. Changing the filter notch frequency, as well as the selected gain, impacts resolution.

Tables V through XII show the effect of the filter notch frequency and gain on the output noise and effective

resolution of the part. The output data rate (or effective conversion time) for the device is equal to the frequency selected for the first notch of the filter. For example, if the first notch of the filter is selected at 50␣ Hz

then a new word is available at a 50 Hz rate or every 20␣ ms. If the first notch is at 500␣ Hz, a new word is

available every 2␣ ms. The default value for these bits is 1, 0.

The settling-time of the filter to a full-scale step input change is worst case 4 × 1/(output data rate). For

example, with the first filter notch at 50␣ Hz, the settling time of the filter to a full-scale step input change is

80␣ ms max. If the first notch is at 500␣ Hz, the settling time of the filter to a full-scale input step is 8␣ ms max.

This settling-time can be reduced to 3 × 1/(output data rate) by synchronizing the step input change to a

reset of the digital filter. In other words, if the step input takes place with the FSYNC bit high, the settlingtime time will be 3 × 1/(output data rate) from when FSYNC returns low.

The –3 dB frequency is determined by the programmed first notch frequency according to the relationship:

/Selected Gain.

REF

filter –3 dB frequency = 0.262 × filter first notch frequency.

3

(or (Sinx/x)3 )

–10–

REV. C

Loading...

Loading...