ANALOG DEVICES AD7366-5 Service Manual

True Bipolar Input, 12-/14-Bit,

V

V

V

AAV

VB1V

2-Channel, Simultaneous Sampling SAR ADCs

FEATURES

Dual 12-bit/14-bit, 2-channel ADCs

True bipolar analog inputs

Programmable input ranges

±10 V, ±5 V, 0 V to +10 V

±12 V with +3 V external reference

Throughput rate: 500 kSPS

Simultaneous conversion with read in less than 2 μs

High analog input impedance

Low current consumption

5.1 mA typical in normal mode

320 nA typical in shutdown mode

AD7366-5

72 dB SNR at 50 kHz input frequency

12-bit no missing codes

AD7367-5

76 dB SNR at 50 kHz input frequency

14-bit no missing codes

Accurate on-chip reference: 2.5 V ± 0.2%

–40°C to +85°C operation

High speed serial interface

SPI-/QSPI-/MICROWIRE-/DSP-compatible

iCMOS process technology

Available in a 24-lead TSSOP

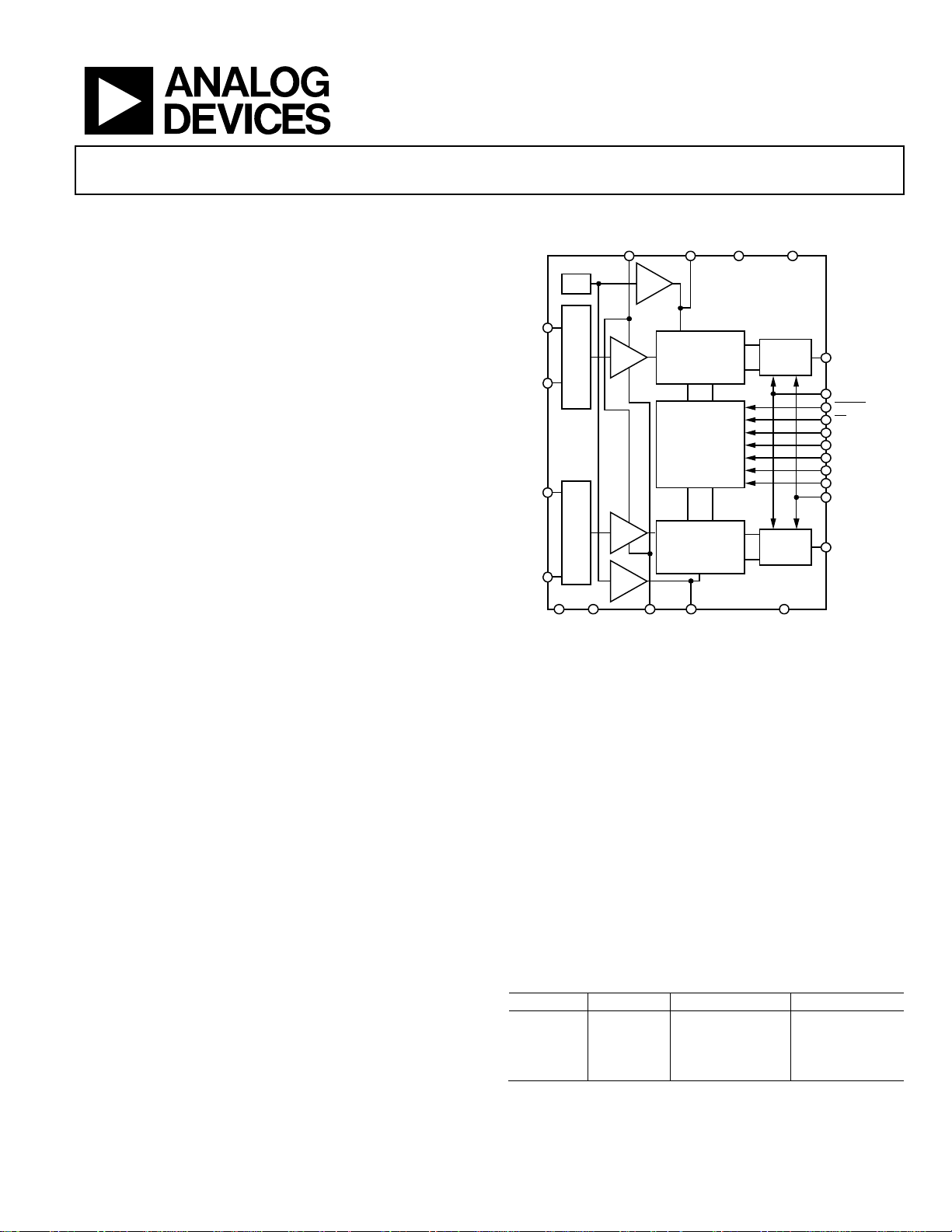

FUNCTIONAL BLOCK DIAGRAM

REF

A1

MUX

A2

MUX

B2

AGND AGND V

AD7366-5/AD7367-5

T/H

T/H

BUF

DD

BUF

SS

D

CAP

AD7366-5/AD7367-5

12-/14-BIT

SUCCESSIVE

APPROXIMATION

ADC

CONTROL

LOGIC

12-/14-BIT

SUCCESSIVE

APPROXIMATION

ADC

B

CAP

Figure 1.

CC

DV

CC

OUTPUT

DRIVERS

OUTPUT

DRIVERS

DGNDD

D

SCLK

CNVST

CS

BUSY

ADDR

RANGE0

RANGE1

REFSEL

V

D

OUT

DRIVE

OUT

A

B

06842-001

GENERAL DESCRIPTION

The AD7366-5/AD7367-51 are dual, 12-/14-bit, low power,

successive approximation analog-to-digital converters (ADCs)

that feature throughput rates up to 500 kSPS. Each device contains

two ADCs, which are both preceded by a 2-channel multiplexer,

and a low noise, wide bandwidth, track-and-hold amplifier.

The AD7366-5/AD7367-5 are fabricated on the Analog

Devices, Inc., industrial CMOS process (iCMOS®)

a technology platform combining the advantages of low and

high voltage CMOS. The process allows the parts to accept

high voltage bipolar signals in addition to reducing power

consumption and package size. The AD7366-5/AD7367-5 can

accept true bipolar analog input signals in the ±10 V range,

±5 V range, and 0 V to +10 V range.

1

Protected by U.S. Patent No. 6,731,232.

2

For analog systems designers within industrial/instrumentation equipment

OEMs who need high performance ICs at higher voltage levels, iCMOS is a

technology platform that enables the development of analog ICs capable of

+30 V and operating at ±15 V supplies while allowing dramatic reductions in

power consumption and package size, and increased ac and dc performance.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

2

, which is

The devices have an on-chip 2.5 V reference that can be disabled to

allow the use of an external reference. If a 3 V reference is applied

to the D

A and D

CAP

B pins, the AD7366-5/AD7367-5 can

CAP

accept a true bipolar ±12 V analog input. Minimum ±12 V V

and V

supplies are required for the ±12 V input range.

SS

PRODUCT HIGHLIGHTS

1. True bipolar analog input signals can be accepted, as well

as ±10 V, ±5 V, ±12 V (with external reference), and 0 V to

+10 V unipolar signals.

2. Two complete ADC functions allow simultaneous

sampling and conversion of two channels.

3. A 500 kSPS serial interface is SPI-/QSPI™-/MICROWIRE™-/

DSP-compatible.

Table 1. Related Products

Device Resolution Throughput Rate No. of Channels

AD7366 12-Bit 1 MSPS Dual, 2-channel

AD7366-5 12-Bit 500 kSPS Dual, 2-channel

AD7367 14-Bit 1 MSPS Dual, 2-channel

AD7367-5 14-Bit 500 kSPS Dual, 2-channel

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007-2009 Analog Devices, Inc. All rights reserved.

DD

AD7366-5/AD7367-5

TABLE OF CONTENTS

Features .............................................................................................. 1

Typical Connection Diagram ................................................... 18

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

AD7366-5 Specifications ............................................................. 3

AD7367-5 Specifications ............................................................. 5

Timing Specifications .................................................................. 7

Absolute Maximum Ratings ............................................................ 8

ESD Caution .................................................................................. 8

Pin Configuration and Function Descriptions ............................. 9

Typical Performance Characteristics ........................................... 11

Terminolog y .................................................................................... 14

Theory of Operation ...................................................................... 16

Circuit Information .................................................................... 16

Driver Amplifier Choice ........................................................... 19

Reference ..................................................................................... 19

Modes of Operation ....................................................................... 20

Normal Mode .............................................................................. 20

Shutdown Mode ......................................................................... 21

Power-Up Times ......................................................................... 21

Serial Interface ................................................................................ 22

Microprocessor Interfacing ........................................................... 24

AD7366-5/AD7367-5 to ADSP-218x ...................................... 24

AD7366-5/AD7367-5 to ADSP-BF53x ................................... 25

AD7366-5/AD7367-5 to TMS320VC5506 ............................. 25

AD7366-5/AD7367-5 to DSP563xx......................................... 26

Application Hints ........................................................................... 27

Layout and Grounding .............................................................. 27

Evaluating the AD7366-5/AD7367-5 ...................................... 27

Converter Operation .................................................................. 16

Analog Inputs .............................................................................. 17

Transfer Function ....................................................................... 17

REVISION HISTORY

8/09—Rev. 0 to Rev. A

Changes to Table 2 ............................................................................ 4

Changes to Table 3 ............................................................................ 6

7/07—Revision 0: Initial Version

Outline Dimensions ....................................................................... 28

Ordering Guide .......................................................................... 28

Rev. A | Page 2 of 28

AD7366-5/AD7367-5

SPECIFICATIONS

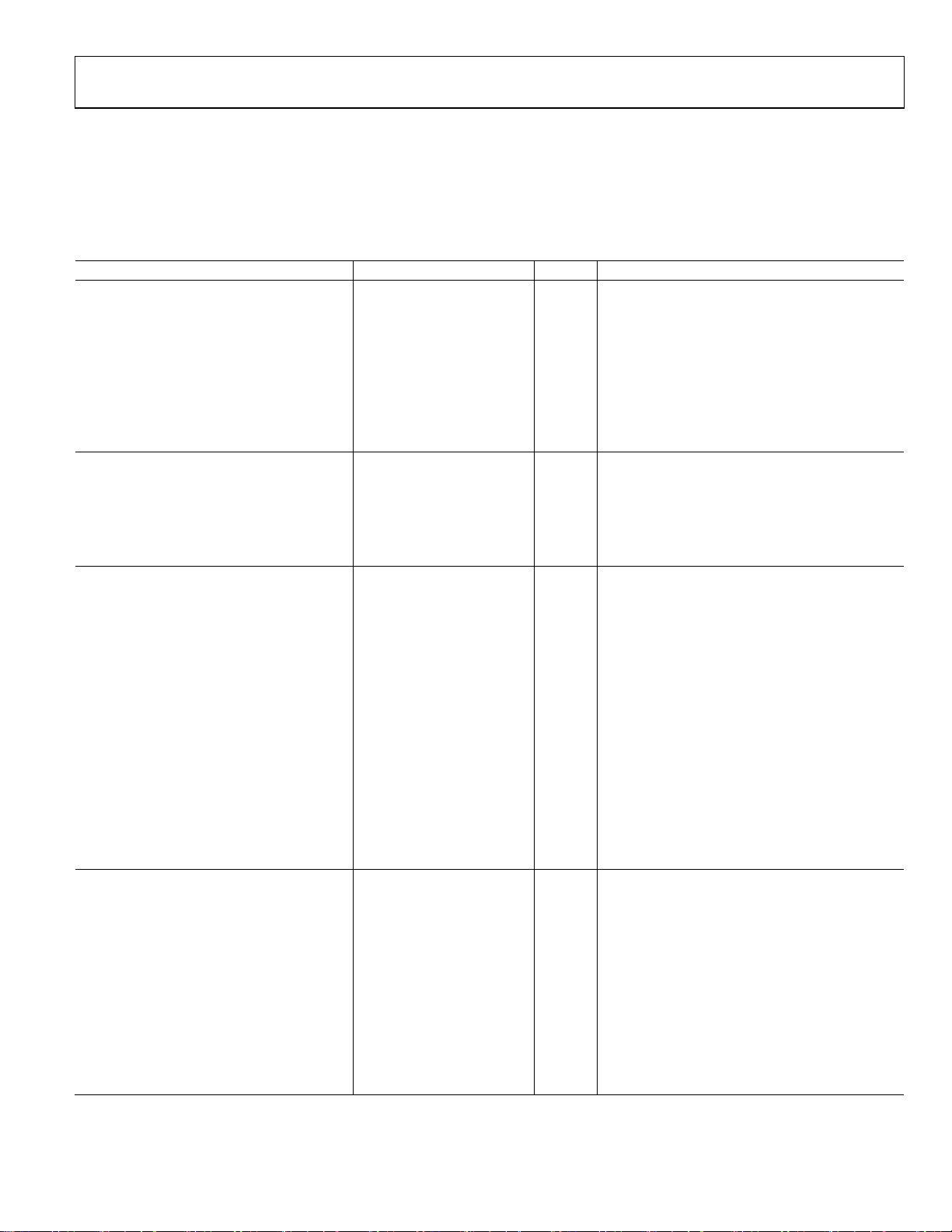

AD7366-5 SPECIFICATIONS

AVCC = DVCC = 4.75 V to 5.25 V; VDD = 5 V to 16.5 V; VSS = −16.5 V to −5 V; V

V

= 2.5 V internal/external; TA = −40°C to +85°C, unless otherwise noted.

REF

Table 2.

Parameter Min Typ Max Unit Test Conditions/Comments

DYNAMIC PERFORMANCE fIN = 50 kHz sine wave

1

Signal-to-Noise Ratio (SNR)

Signal-to-Noise (+ Distortion) Ratio (SINAD)

Total Harmonic Distortion (THD)

Spurious-Free Dynamic Range (SFDR)

Intermodulation Distortion (IMD)

1

1

70 72 dB

1

70 71 dB

−85 −78 dB

1

−87 −78 dB

fa = 49 kHz, fb = 51 kHz

Second-Order Terms −88 dB

Third-Order Terms

Channel-to-Channel Isolation

1

−88 dB

−90 dB

SAMPLE AND HOLD

Aperture Delay

Aperture Jitter

Aperture Delay Matching

2

2

40 ps

2

±100 ps

10 ns

Full Power Bandwidth 35 MHz @ 3 dB, ±10 V range

8 MHz @ 0.1 dB, ±10 V range

DC ACCURACY

Resolution 12 Bits

1

Integral Nonlinearity (INL)

Differential Nonlinearity (DNL)

Positive Full-Scale Error

1

1

±1 ±7 LSB ±5 V and ±10 V analog input range

±0.5 ±1 LSB

±0.25 ±0.5 LSB Guaranteed no missed codes to 12 bits

±1 ±6 LSB 0 V to 10 V analog input range

Positive Full-Scale Error Match

1

±1.5 LSB Matching from ADC A to ADC B

±0.1 LSB Channel-to-channel matching for ADC A and ADC B

Zero Code Error

1

±0.5 ±3 LSB ±5 V and ±10 V analog input range

±1 ±6 LSB 0 V to 10 V analog input range

Zero Code Error Match

1

±1.5 LSB Matching from ADC A to ADC B

±0.1 LSB Channel-to-channel matching for ADC A and ADC B

1

Negative Full-Scale Error

±1 ±7 LSB ±5 V and ±10 V analog input range

±1 ±6 LSB 0 V to 10 V analog input range

Negative Full-Scale Error Match

1

±1.5 LSB Matching from ADC A to ADC B

±0.1 LSB Channel-to-channel matching for ADC A and ADC B

ANALOG INPUT

Input Voltage Ranges

±10 V

(Programmed via RANGE Pins)

±5 V

0 to 10 V

DC Leakage Current ±0.01 ±1 µA

Input Capacitance 9 pF When in track, ±10 V range

13 pF When in track, ±5 V or 0 V to +10 V range

Input Impedance 500 kΩ For ±10 V @ 500 kSPS

2.5 MΩ For ±10 V @ 100 kSPS

250 kΩ For ±5 V/0 V to +10 V @ 500 kSPS

1.2 MΩ For ±5 V/0 V to +10 V @ 100 kSPS

= 2.7 V to 5.25 V; f

DRIVE

= 500 kSPS; f

SAMPLE

= 20 MHz;

SCLK

Rev. A | Page 3 of 28

AD7366-5/AD7367-5

Parameter Min Typ Max Unit Test Conditions/Comments

REFERENCE INPUT/OUTPUT

Reference Output Voltage

Long-Term Stability 150 ppm For 1000 hours

Output Voltage Hysteresis

Reference Input Voltage Range 2.5 3.0 V

DC Leakage Current ±0.01 ±1 µA External reference applied to Pin D

Input Capacitance 25 pF ±5 V and ±10 V analog input range

17 pF 0 V to 10 V analog input range

D

A, D

CAP

B Output Impedance

CAP

Reference Temperature Coefficient 6 25 ppm/°C

V

Noise 20 µV rms Bandwidth = 3 kHz

REF

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, IIN ±0.01 ±1 µA VIN = 0 V or V

Input Capacitance, C

LOGIC OUTPUTS

Output High Voltage, VOH V

Output Low Voltage, VOL 0.4 V

Floating State Leakage Current ±0.01 ±1 µA

Floating State Output Capacitance

CONVERSION RATE

Conversion Time 1.25 s

Track/Hold Acquisition Time

Throughput Rate 500 kSPS For 2.7 V ≤ V

POWER REQUIREMENTS Digital inputs = 0 V or V

V

CC

V

DD

V

SS

V

2.7 5.25 V

DRIVE

Normal Mode (Static)

IDD 370 550 µA VDD = 16.5 V

ISS 40 60 µA VSS = −16.5 V

ICC 1.5 2.25 mA VCC = 5.5 V

Normal Mode (Operational) fS = 500 kSPS

IDD 1 1.2 mA VDD = 16.5 V

ISS 0.7 0.82 mA VSS = −16.5 V

ICC 3.4 4 mA VCC = 5.25 V, internal reference enabled

Shutdown Mode

IDD 0.01 1 µA VDD = 16.5 V

ISS 0.01 1 µA VSS = −16.5 V

ICC 0.3 3 µA VCC = 5.25 V

Power Dissipation

Normal Mode (Operational) 46 54.5 mW

15 mW ±10 V input range, fS = 100 kSPS

20 mW ±5 V and 0 V to +10 V input range, fS = 100 kSPS

Shutdown Mode 1.9 48.75 µW VDD = +16.5 V, VSS = −16.5 V, VCC = +5.25 V

1

See the Terminology section.

2

Sample tested during initial release to ensure compliance.

3

Refers to Pin D

A or Pin D

CAP

3

1

50 ppm

0.7 × V

INH

+0.8 V

INL

2

IN

2

2

2.494 2.5 2.506 V ±0.2% maximum @ 25°C

7 Ω

V

DRIVE

6 pF

− 0.2 V

DRIVE

8 pF

140 ns Full-scale step input

4.75 5.25 V See Tab le 7

5 16.5 V See Table 7

−16.5 −5 V See Table 7

B specified for 25

CAP

o

C.

= +16.5 V, VSS = −16.5 V, VCC = +5.25 V,

V

DD

f

= 500 kSPS

S

DRIVE

≤ 5.25 V, f

DRIVE

SCLK

DRIVE

= 20 MHz

A/Pin D

CAP

CAP

B

Rev. A | Page 4 of 28

AD7366-5/AD7367-5

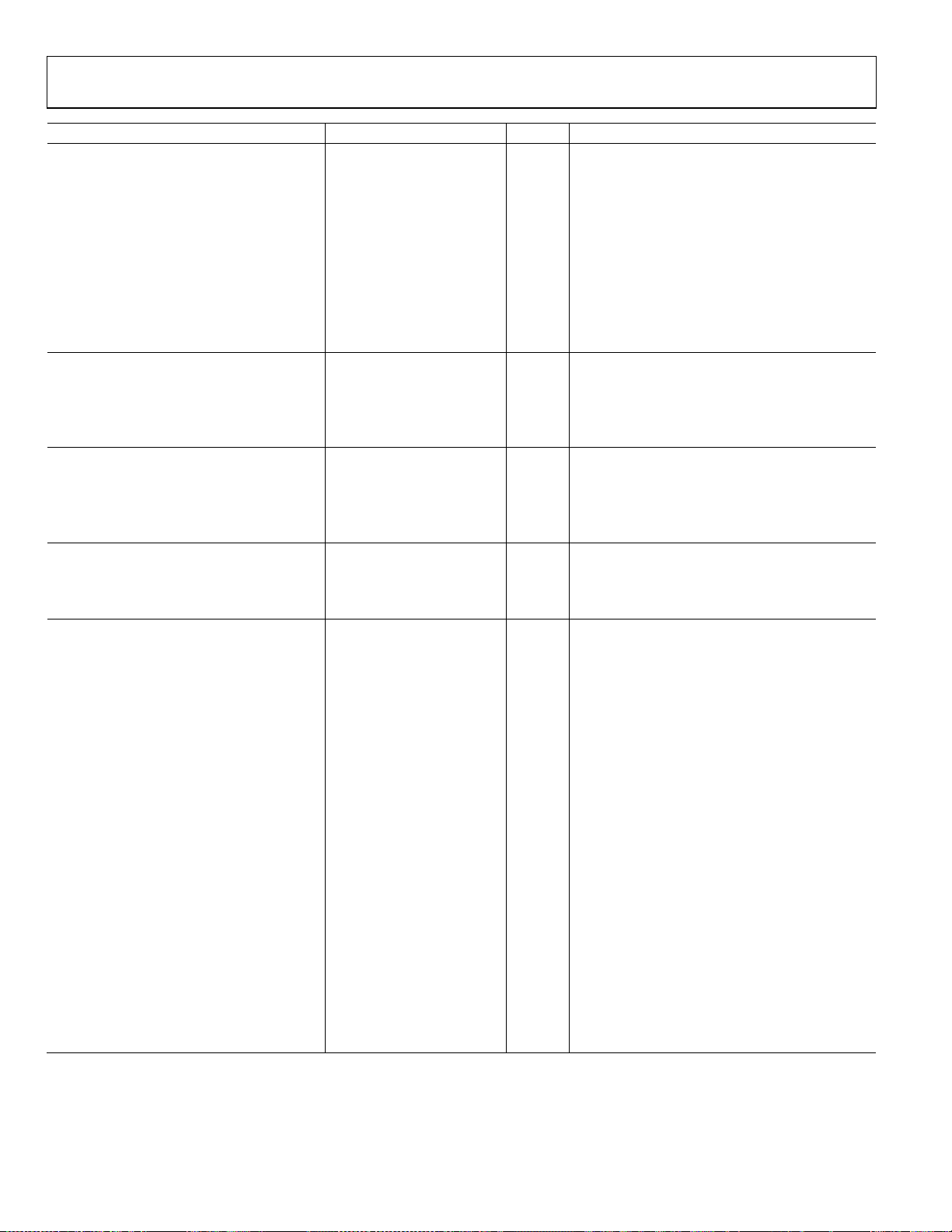

AD7367-5 SPECIFICATIONS

AVCC = DVCC = 4.75 V to 5.25 V; VDD = 5 V to 16.5 V; VSS = −16.5 V to −5 V; V

V

= 2.5 V internal/external; TA = −40°C to +85°C, unless otherwise noted.

REF

Table 3.

Parameter Min Typ Max Unit Test Conditions/Comments

DYNAMIC PERFORMANCE fIN = 50 kHz sine wave

1

Signal-to-Noise Ratio (SNR)

Signal-to-Noise (+ Distortion) Ratio (SINAD)

Total Harmonic Distortion (THD)

Spurious-Free Dynamic Range (SFDR)

Intermodulation Distortion (IMD)

1

1

1

74 76 dB

1

73 75 dB

−84 −78 dB

−87 −79 dB

fa = 49 kHz, fb = 51 kHz

Second-Order Terms −91 dB

Third-Order Terms

Channel-to-Channel Isolation

1

−89 dB

−90 dB

SAMPLE AND HOLD

Aperture Delay

Aperture Jitter

Aperture Delay Matching

2

2

40 ps

2

±100 ps

10 ns

Full Power Bandwidth 35 MHz @ 3 dB, ±10 V range

8 MHz @ 0.1 dB, ±10 V range

DC ACCURACY

Resolution 14 Bits

1

Integral Nonlinearity (INL)

Differential Nonlinearity (DNL)

Positive Full-Scale Error

1

1

±4 ±25 LSB ±5 V and ±10 V analog input range

±2 ±3.5 LSB

±0.5 ±0.90 LSB Guaranteed no missed codes to 14 bits

±5 ±25 LSB 0 V to 10 V analog input range

Positive Full-Scale Error Match

1

±3 LSB Matching from ADC A to ADC B

±0.2 LSB Channel-to-channel matching for ADC A and ADC B

Zero Code Error

1

±1 ±10 LSB ±5 V and ±10 V analog input range

±5 ±25 LSB 0 V to 10 V analog input range

Zero Code Error Match

1

±3 LSB Matching from ADC A to ADC B

±0.2 LSB Channel-to-channel matching for ADC A and ADC B

1

Negative Full-Scale Error

±4 ±25 LSB ±5 V and ±10 V analog input range

±5 ±25 LSB 0 V to 10 V analog input range

Negative Full-Scale Error Match

1

±3 LSB Matching from ADC A to ADC B

±0.2 LSB Channel-to-channel matching for ADC A and ADC B

ANALOG INPUT

Input Voltage Ranges

±10 V

(Programmed via RANGE Pins)

±5 V

0 to 10 V See Table 7

DC Leakage Current ±0.01 ±1 µA

Input Capacitance 9 pF When in track, ±10 V range

13 pF When in track, ±5 V or 0 V to +10 V range

Input Impedance 500 kΩ For ±10 V @ 500 kSPS

2.5 MΩ For ±10 V @ 100 kSPS

250 kΩ For ±5 V/0 V to +10 V @ 500 kSPS

1.2 MΩ For ±5 V/0 V to +10 V @ 100 kSPS

= 2.7 V to 5.25 V; f

DRIVE

= 500 kSPS; f

SAMPLE

= 20 MHz;

SCLK

Rev. A | Page 5 of 28

AD7366-5/AD7367-5

Parameter Min Typ Max Unit Test Conditions/Comments

REFERENCE INPUT/OUTPUT

Reference Output Voltage

Long-Term Stability 150 ppm For 1000 hours

Output Voltage Hysteresis

Reference Input Voltage Range 2.5 3.0 V

DC Leakage Current ±0.01 ±1 µA External reference applied to D

Input Capacitance 25 pF ±5 V and ±10 V analog input range

17 pF 0 V to 10 V analog input range

D

A, D

CAP

B Output Impedance

CAP

Reference Temperature Coefficient 6 25 ppm/°C

V

Noise 20 µV rms Bandwidth = 3 kHz

REF

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, IIN ±0.01 ±1 µA VIN = 0 V or V

Input Capacitance, C

LOGIC OUTPUTS

Output High Voltage, VOH V

Output Low Voltage, VOL 0.4 V

Floating State Leakage Current ±0.01 ±1 µA

Floating State Output Capacitance

CONVERSION RATE

Conversion Time 1.25 ns

Track/Hold Acquisition Time

Throughput Rate 500 kSPS For 2.7 V ≤ V

POWER REQUIREMENTS Digital inputs = 0 V or V

V

CC

V

DD

V

SS

V

2.7 5.25 V

DRIVE

Normal Mode (Static)

IDD 370 550 µA VDD = 16.5 V

ISS 40 60 µA VSS = −16.5 V

ICC 1.5 2.25 mA VCC = 5.5 V

Normal Mode (Operational) fS = 500 kSPS

IDD 1 1.2 mA VDD = 16.5 V

ISS 0.7 0.82 mA VSS = −16.5 V

ICC 3.4 4 mA VCC = 5.25 V, internal reference enabled

Shutdown Mode

IDD 0.01 1 µA VDD = 16.5 V

ISS 0.01 1 µA VSS = −16.5 V

ICC 0.3 3 µA VCC = 5.25 V

Power Dissipation

Normal Mode (Operational) 46 54.5 mW VDD = +16.5 V, VSS = −16.5 V, VCC = +5.25 V

15 mW ±10 V input range, fS = 100 kSPS

20 mW ±5 V and 0 V to +10 V input range, fS = 100 kSPS

Shutdown Mode 1.9 48.75 µW VDD = +16.5 V, VSS = −16.5 V, VCC = +5.25 V

1

See the Terminology section.

2

Sample tested during initial release to ensure compliance.

3

Refers to Pin D

A or Pin D

CAP

3

1

50 ppm

0.7 × V

INH

0.8 V

INL

2

IN

2

2

2.494 2.5 2.506 V ±0.2% maximum @ 25°C

7 Ω

V

DRIVE

DRIVE

6 pF

− 0.2 V

DRIVE

8 pF

140 ns Full-scale step input

DRIVE

4.75 5.25 V See Table 7

5 16.5 V See Tab le 7

−16.5 −5 V See Table 7

B.

CAP

≤ 5.25 V, f

DRIVE

CAP

= 20 MHz

SCLK

A/Pin D

CAP

B

Rev. A | Page 6 of 28

AD7366-5/AD7367-5

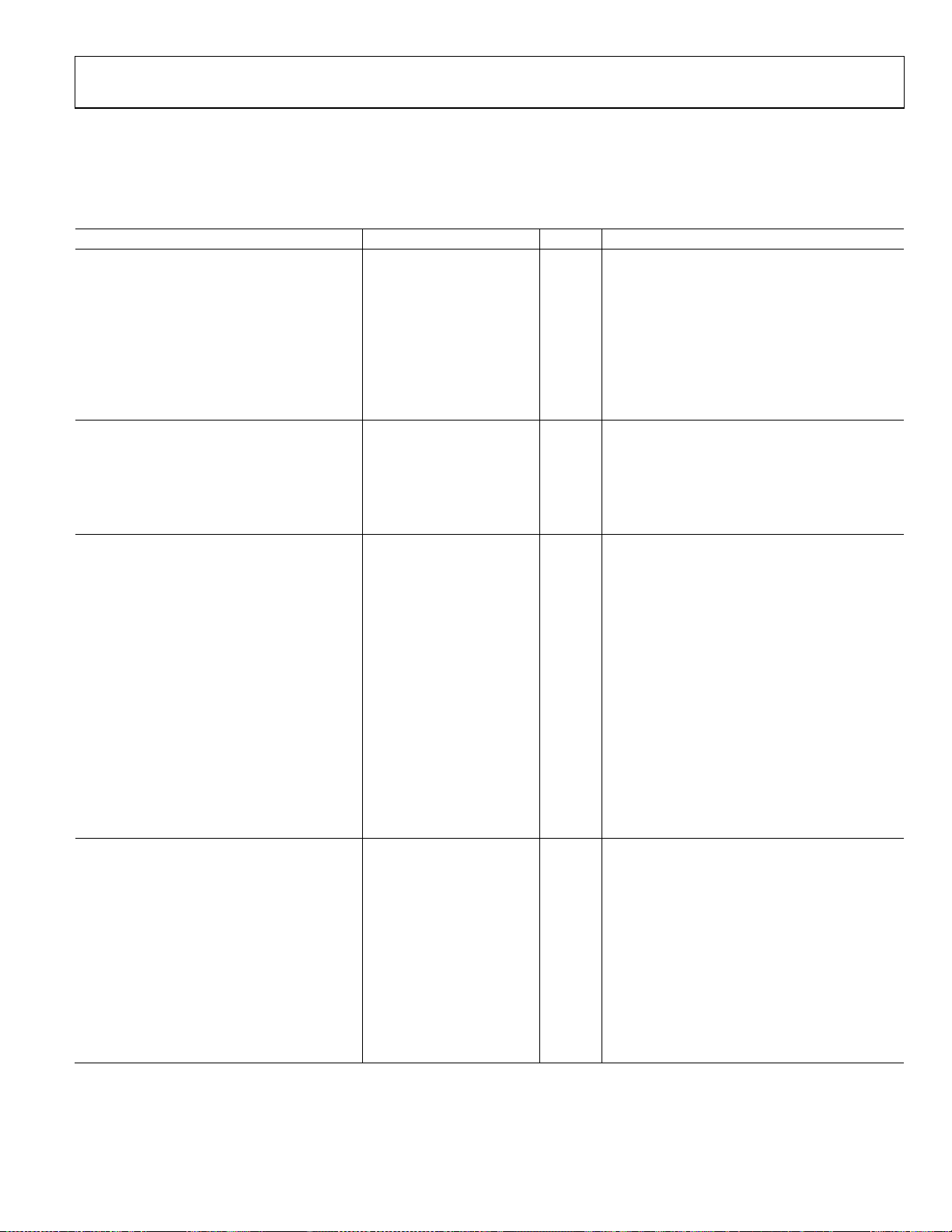

TIMING SPECIFICATIONS

AVCC = DVCC = 4.75 V to 5.25 V; VDD = 5 V to 16.5 V; VSS = −16.5 V to −5 V; V

Table 4.

Parameter 2.7 V ≤ V

t

CONVER T

≤ 5.25 V Unit Test Conditions/Comments

DRIVE

Conversion time, internal clock. CONVST

1.25 µs max For the AD7367-5.

1.25 µs max For the AD7366-5.

f

SCLK

10 kHz min Frequency of serial read clock.

20 MHz max

t

50 ns min

QUIET

Minimum quiet time required between the end of serial read and the start of the next

conversion.

t1 10 ns min

t

2

t

3

t

4

2

t

5

40 ns min

0 ns min

10 ns max

20 ns max Data access time after SCLK falling edge.

Minimum CONVST

CONVST

BUSY falling edge to MSB valid once CS

Delay from CS

falling edge to BUSY rising edge.

low pulse.

falling edge until Pin 1 (D

t6 7 ns min SCLK to data valid hold time.

t7 0.3 × t

t8 0.3 × t

t

9

t

POWER-UP

10 ns max

70 µs max

SCLK

ns min SCLK high pulse width.

SCLK

ns min SCLK low pulse width.

rising edge to D

CS

OUT

Power up time from shutdown mode; time required between CONVST

CONVST falling edge.

1

Sample tested during initial release to ensure compliance. All input signals are specified with tR = tF = 5 ns (10% to 90% of V

All timing specifications given are with a 25 pF load capacitance. With a load capacitance greater than this value, a digital buffer or latch must be used. See the

Terminology section and Figure 25.

2

The time required for the output to cross is 0.4 V or 2.4 V.

= 2.7 V to 5.25 V; TA = T

DRIVE

A, D

B, high impedance.

OUT

to T

MIN

, unless otherwise noted.1

MAX

falling edge to BUSY falling edge.

is low for t4 prior to BUSY going low.

A) and Pin 23 (D

OUT

B) are three-state disabled.

OUT

rising edge and

) and timed from a voltage level of 1.6 V.

DRIVE

Rev. A | Page 7 of 28

AD7366-5/AD7367-5

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter Rating

VDD to AGND, DGND −0.3 V to +16.5 V

VSS to AGND, DGND −16.5 V to +0.3 V

V

to DGND −0.3 V to DVCC

DRIVE

VDD to AVCC (VCC − 0.3 V) to +16.5 V

AVCC to AGND, DGND −0.3 V to +7 V

DVCC to AVCC −0.3 V to +0.3 V

DVCC to DGND −0.3 V to +7 V

V

to AGND −0.3 V to DVCC

DRIVE

AGND to DGND −0.3 V to +0.3 V

Analog Input Voltage to AGND VSS − 0.3 V to VDD + 0.3 V

Digital Input Voltage to DGND −0.3 V to V

Digital Output Voltage to GND −0.3 V to V

D

B, D

CAP

B Input to AGND −0.3 V to AVCC + 0.3 V

CAP

DRIVE

DRIVE

+ 0.3 V

+ 0.3 V

Input Current to Any Pin Except Supplies1 ±10 mA

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Junction Temperature 150°C

TSSOP Package

θJA Thermal Impedance 128°C/W

θJC Thermal Impedance 42°C/W

Pb-free Temperature, Soldering

Reflow 260(+0)°C

ESD 1.5 kV

1

Transient currents of up to 100 mA do not cause latch-up.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

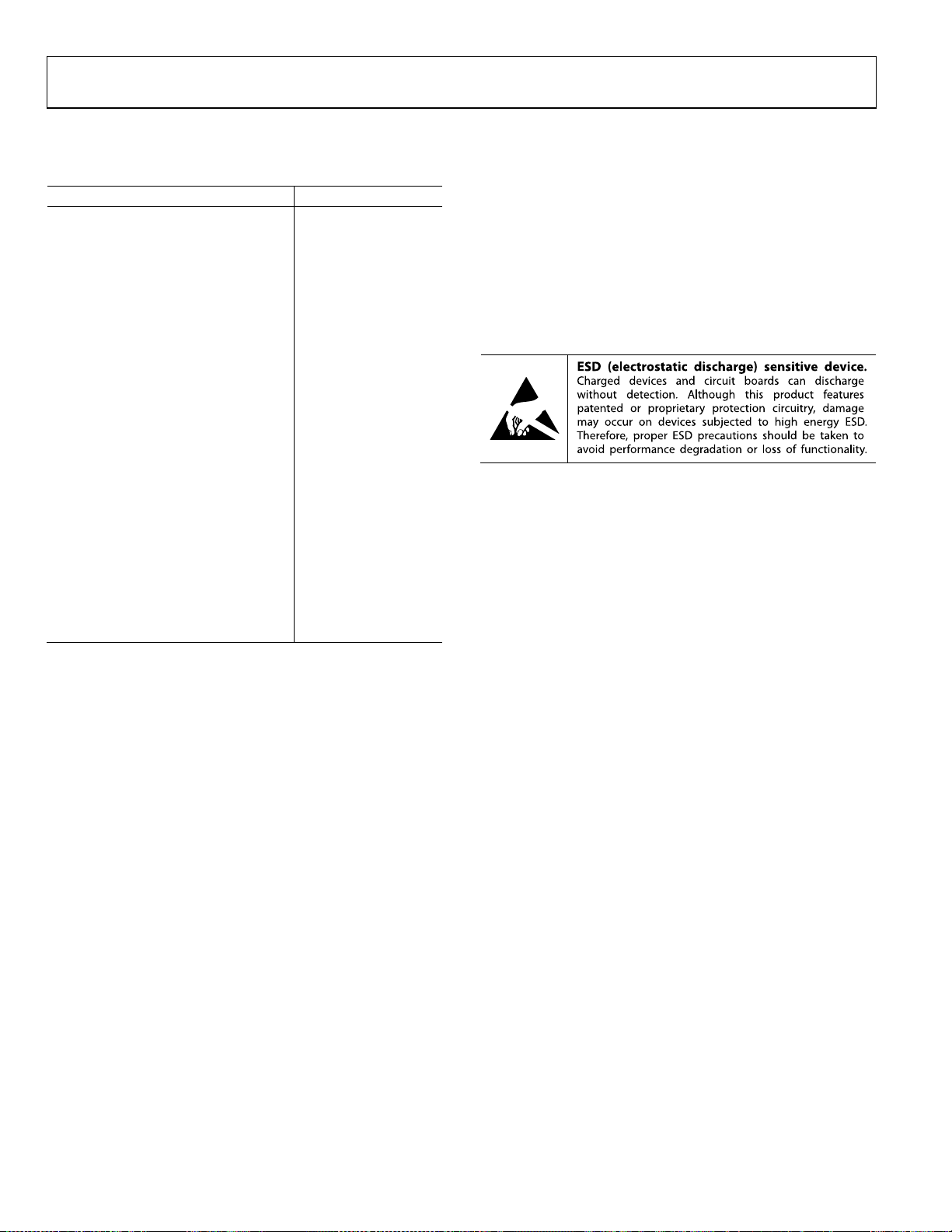

ESD CAUTION

Rev. A | Page 8 of 28

AD7366-5/AD7367-5

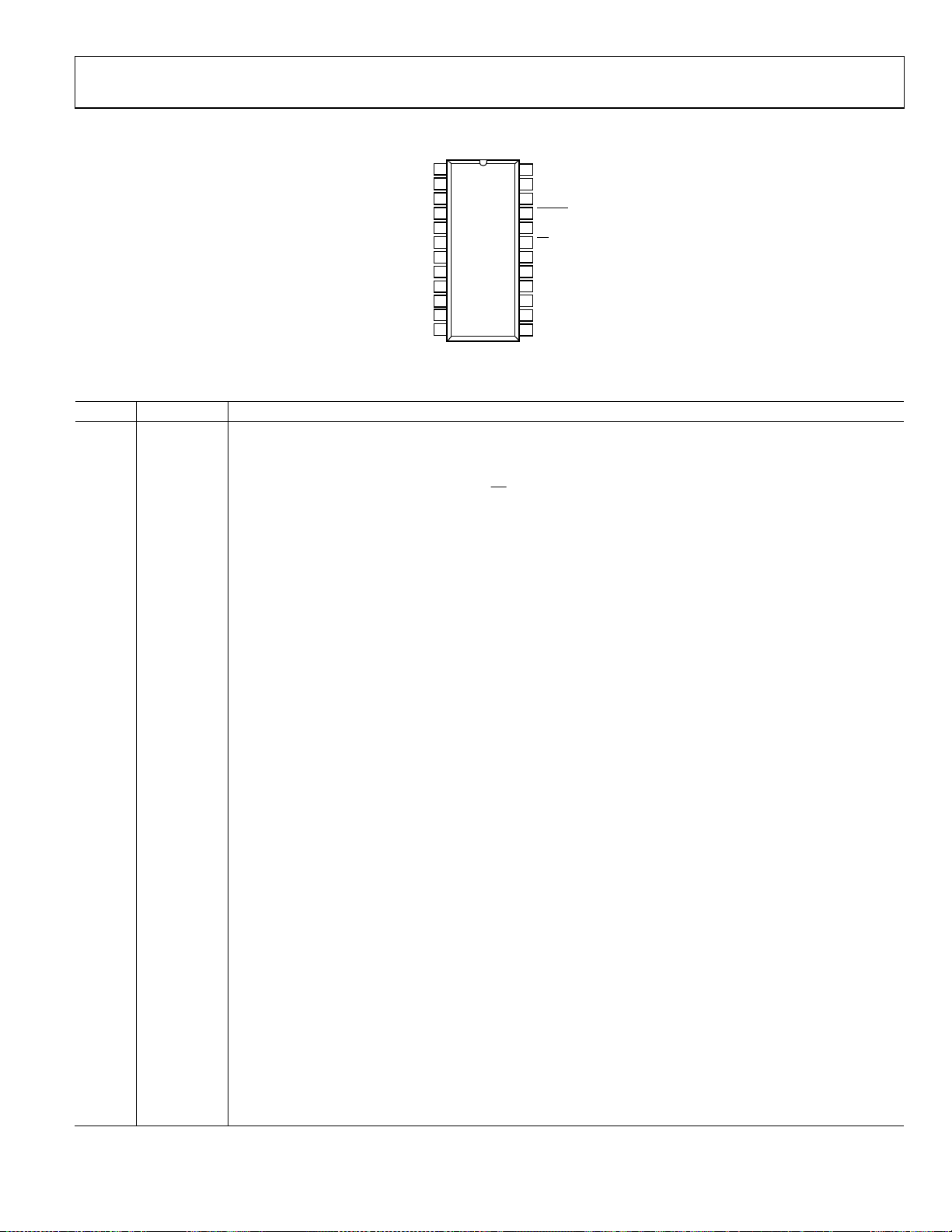

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

D

A

Table 6. Pin Function Descriptions

Pin No. Mnemonic Description

1, 23 D

OUT

A, D

B

Serial Data Outputs. The data output is supplied to each pin as a serial data stream. The bits are clocked out on

OUT

the falling edge of the SCLK input and 12 SCLK cycles are required to access the data from the AD7366-5 while

14 SCLK cycle are required for the AD7367-5. The data simultaneously appears on both pins from the simultaneous

conversions of both ADCs. The data stream consists of the 12 bits of conversion data for the AD7366-5 and 14 bits

for the AD7367-5 and is provided MSB first. If CS

cycles for the AD7367-5, on either D

allows data from a simultaneous conversion on both ADCs to be gathered in serial format on either D

B using only one serial port. See the section for more information. Serial Interface

D

OUT

2 V

DRIVE

Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates.

This pin should be decoupled to DGND. The voltage range on this pin is 2.7 V to 5.25 V and may be different than

the voltage at AV

3 DVCC

Digital Supply Voltage, 4.75 V to 5.25 V. The DV

For best performance, it is recommended that the DV

voltage difference between them never exceeds 0.3 V, even on a transient basis. This supply should be decoupled

to DGND. Place 10 µF and 100 nF decoupling capacitors on the DV

4, 5

6 ADDR

RANGE1,

RANGE0

Analog Input Range Selection, Logic Inputs. The polarity on these pins determines the input range of the analog

input channels. See the Analog Inputs section and Tabl e 8 for details.

Multiplexer Select, Logic Input. This input is used to select the pair of channels to be simultaneously converted,

either Channel 1 of both ADC A and ADC B, or Channel 2 of both ADC A and ADC B. The logic state on this pin is

latched on the rising edge of BUSY to set up the multiplexer for the next conversion.

7, 17 AGND

Analog Ground. Ground reference point for all analog circuitry on the AD7366-5/AD7367-5. All analog input

signals and any external reference signal should be referred to this AGND voltage. Both AGND pins should

connect to the AGND plane of a system. The AGND and DGND voltages ideally should be at the same potential

and must not be more than 0.3 V apart, even on a transient basis.

8 AVCC

Analog Supply Voltage, 4.75 V to 5.25 V. This is the supply voltage for the ADC cores. The AV

should ideally be at the same potential. For best performance, it is recommended that the DV

shorted together to ensure that the voltage difference between them never exceeds 0.3 V even on a transient

basis. This supply should be decoupled to AGND. Place 10 µF and 100 nF decoupling capacitors on the AVCC pin.

9, 16 D

CAP

A, D

B

Decoupling Capacitor Pins. Decoupling capacitors are connected to these pins to decouple the reference buffer

CAP

for each respective ADC. For best performance, it is recommended to use a 680 nF decoupling capacitor on these

pins. Provided the output is buffered, the on-chip reference can be taken from these pins and applied externally

to the rest of a system.

10 VSS

Negative Power Supply Voltage. This is the negative supply voltage for the high voltage analog input structure

of the AD7366-5/AD7367-5. The supply must be less than or equal to −5 V (see Table 7 for further details).

Place 10 µF and 100 nF decoupling capacitors on the V

11, 12 VA1, VA2

Analog Inputs of ADC A. These are both single-ended analog inputs. The analog input range on these channels is

determined by the RANGE0 and RANGE1 pins.

13, 14 VB2, VB1

Analog Inputs of ADC B. These are both single-ended analog inputs. The analog input range on these channels is

determined by the RANGE0 and RANGE1 pins.

15 VDD

Positive Power Supply Voltage. This is the positive supply voltage for the high voltage analog input structure

of the AD7366-5/AD7367-5. The supply must be greater than or equal to 5 V (see Table 7 for further details).

Place 10 µF and 100 nF decoupling capacitors on the V

1

OUT

V

2

DRIVE

DV

3

CC

AD7366-5/

RANGE1

RANGE0

4

AD7367-5

5

ADDR

AGND

AV

D

CAP

V

V

V

TOP VIEW

6

(Not to Scale)

7

8

CC

AD

9

10

SS

11

A1

12

A2

Figure 2. Pin Configuration

A or D

OUT

and DVCC, but should never exceed either by more than 0.3 V.

CC

DGND

24

D

B

23

OUT

BUSY

22

21

CNVST

SCLK

20

CS

19

18

REFSEL

17

AGND

B

16

CAP

15

V

DD

14

V

B1

V

13

B2

06842-002

is held low for a further 12 SCLK cycles for the AD7366-5 or 14 SCLK

B, the data from the other ADC follows on that D

OUT

and AVCC voltages should ideally be at the same potential.

CC

and AVCC pins be shorted together, to ensure that the

CC

pin.

CC

pin.

SS

pin.

DD

pin. This

OUT

A or

OUT

and DVCC voltages

CC

and AVCC pins be

CC

Rev. A | Page 9 of 28

Loading...

Loading...