Quad-Channel, 12-Bit, Serial Input, 4 mA to 20 mA Output

A

V

DAC with Dynamic Power Control and HART Connectivity

Data Sheet

FEATURES

12-bit resolution and monotonicity

Dynamic power control for thermal management

or external PMOS mode

Current output ranges: 0 mA to 20 mA, 4 mA to 20 mA,

and 0 mA to 24 mA

±0.1% total unadjusted error (TUE) maximum

User-programmable offset and gain

On-chip diagnostics

On-chip reference: ±10 ppm/°C maximum

−40°C to +105°C temperature range

APPLICATIONS

Process control

Actuator control

PLCs

HART network connectivity

GENERAL DESCRIPTION

The AD5737 is a quad-channel current output DAC that

operates with a power supply range from 10.8 V to 33 V.

On-chip dynamic power control minimizes package power

dissipation by regulating the voltage on the output driver from

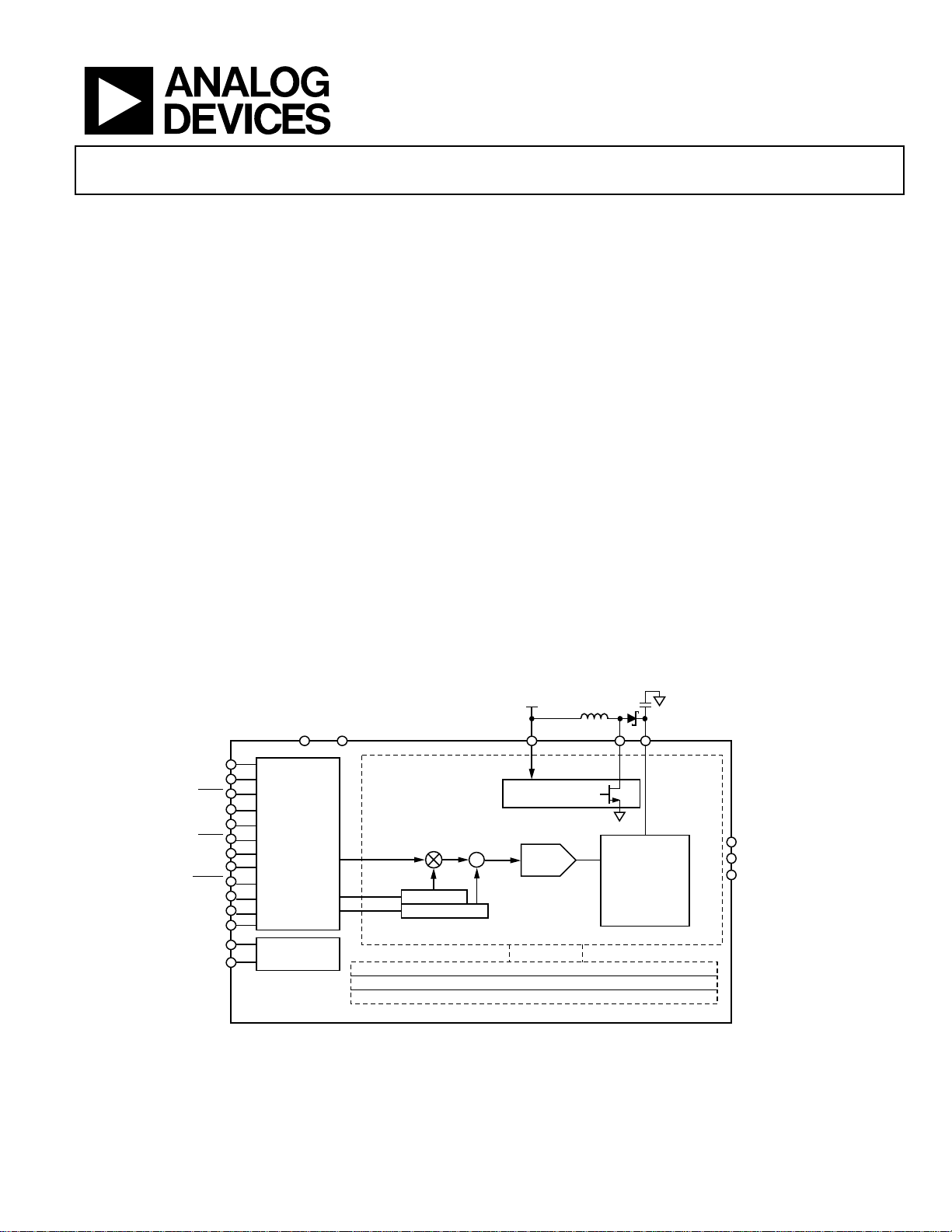

FUNCTIONAL BLOCK DIAGRAM

AV

+15V

DD

AGND

AD5737

7.4 V to 29.5 V using a dc-to-dc boost converter optimized for

minimum on-chip power dissipation.

Each channel has a corresponding CHART pin so that HART

signals can be coupled onto the current output of the AD5737.

The AD5737 uses a versatile 3-wire serial interface that operates

at clock rates of up to 30 MHz and is compatible with standard

SPI, QSPI™, MICROWIRE®, DSP, and microcontroller interface

standards. The serial interface also features optional CRC-8 packet

error checking, as well as a watchdog timer that monitors activity

on the interface.

PRODUCT HIGHLIGHTS

1. Dynamic power control for thermal management.

2. 12-bit performance.

3. Quad channel.

4. HART compliant.

COMPANION PRODUCTS

Product Family: AD5755, AD5755-1, AD5757, AD5735

External References: ADR445, ADR02

Digital Isolators: ADuM1410, ADuM1411

Power: ADP2302, ADP2303

Additional companion products on the AD5737 product page

CC

5.0V

SW

V

x

BOOST_x

DV

DD

DGND

LDAC

SCLK

SDIN

SYNC

SDO

CLEAR

FAU LT

ALERT

AD1

AD0

REFOUT

REFIN

NOTES

1. x = A, B, C, OR D.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

DIGITAL

INTERFACE

REFERENCE

AD5737

GAIN REG A

OFFSET REG A

DAC CHANNEL A

DAC CHANNEL B

DAC CHANNEL C

DAC CHANNEL D

7.4V TO 29.5V

DC-TO-DC

CONVERTER

I

OUT_x

+

DAC A

CURRENT

OUTPUT RANGE

SCALING

R

SET_x

CHARTx

10067-101

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

AD5737 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Companion Products ....................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

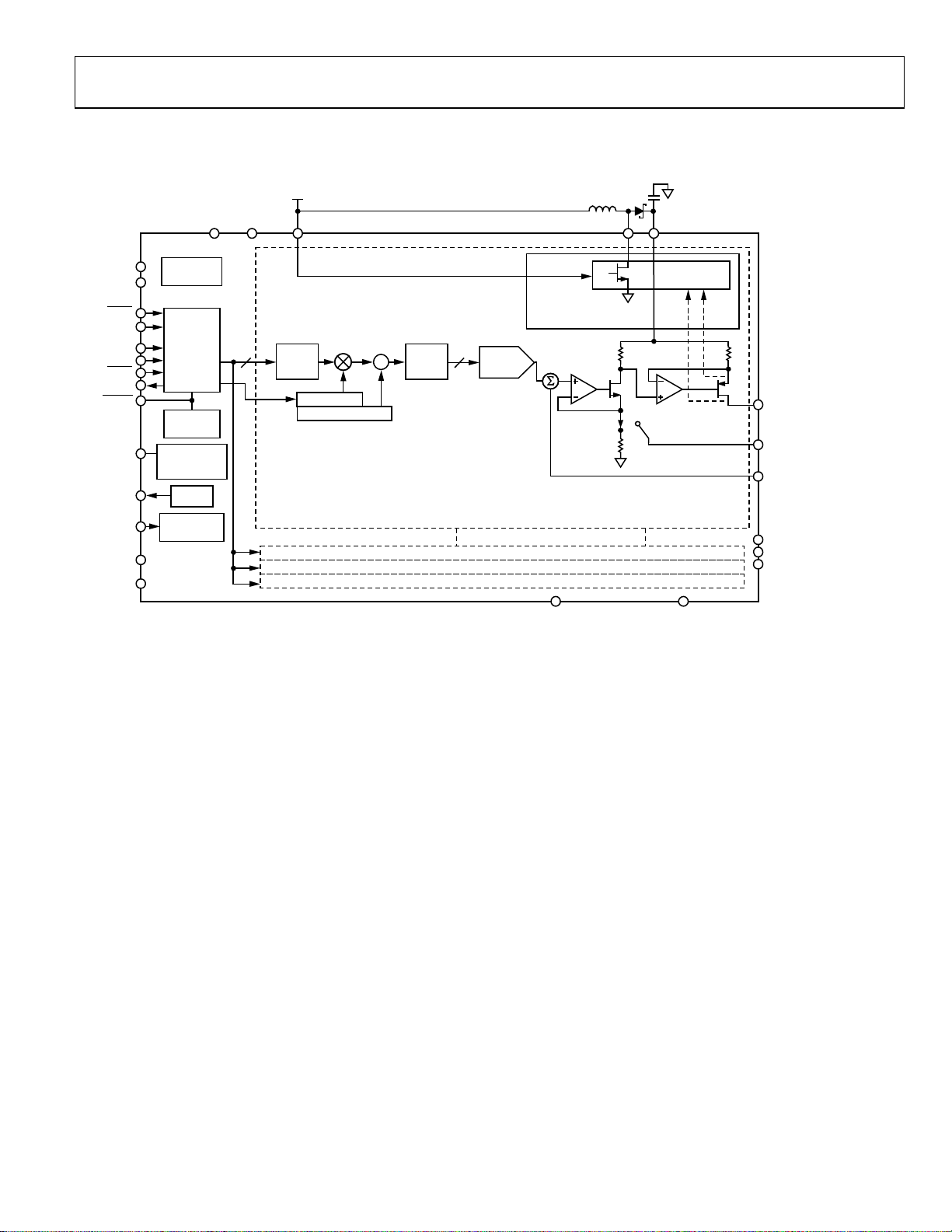

Detailed Functional Block Diagram .............................................. 3

Specifications ..................................................................................... 4

AC Performance Characteristics ................................................ 6

Timing Characteristics ................................................................ 6

Absolute Maximum Ratings ............................................................ 9

Thermal Resistance ...................................................................... 9

ESD Caution .................................................................................. 9

Pin Configuration and Function Descriptions ........................... 10

Typical Performance Characteristics ........................................... 13

Current Outputs ......................................................................... 13

DC-to-DC Converter ................................................................. 17

Reference ..................................................................................... 18

General ......................................................................................... 19

Terminology .................................................................................... 20

Theory of Operation ...................................................................... 21

DAC Architecture ....................................................................... 21

Power-On State of the AD5737 ................................................ 21

Serial Interface ............................................................................ 21

Transfer Function ....................................................................... 22

Registers ........................................................................................... 23

Enabling the Output ................................................................... 24

Reprogramming the Output Range ......................................... 24

Data Registers ............................................................................. 25

REVISION HISTORY

11/11—Rev. 0 to Rev. A

Change to Accuracy, External R

Changes to Power-On State of the AD5737 Section .................. 21

Changes to Readback Operation Section and Readback

Example Section.............................................................................. 30

7/11—Revision 0: Initial Version

Parameter in Table 1 ............ 4

SET

Control Registers ........................................................................ 27

Readback Operation .................................................................. 30

Device Features ............................................................................... 32

Fault Output ................................................................................ 32

Digital Offset and Gain Control ............................................... 32

Status Readback During a Write .............................................. 32

Asynchronous Clear ................................................................... 32

Packet Error Checking ............................................................... 33

Watchdog Timer ......................................................................... 33

Alert Output ................................................................................ 33

Internal Reference ...................................................................... 33

External Current Setting Resistor ............................................ 33

HART Connectivity ................................................................... 34

Digital Slew Rate Control .......................................................... 34

Dynamic Power Control ............................................................ 35

DC-to-DC Converters ............................................................... 35

AICC Supply Requirements—Static .......................................... 36

AICC Supply Requirements—Slewing ...................................... 37

External PMOS Mode ................................................................ 38

Applications Information .............................................................. 39

Current Output Mode with Internal R

Precision Voltage Reference Selection ..................................... 39

Driving Inductive Loads ............................................................ 39

Transient Voltage Protection .................................................... 40

Microprocessor Interfacing ....................................................... 40

Layout Guidelines....................................................................... 40

Galvanically Isolated Interface ................................................. 41

Outline Dimensions ....................................................................... 42

Ordering Guide .......................................................................... 42

................................ 39

SET

Rev. A | Page 2 of 44

Data Sheet AD5737

A

V

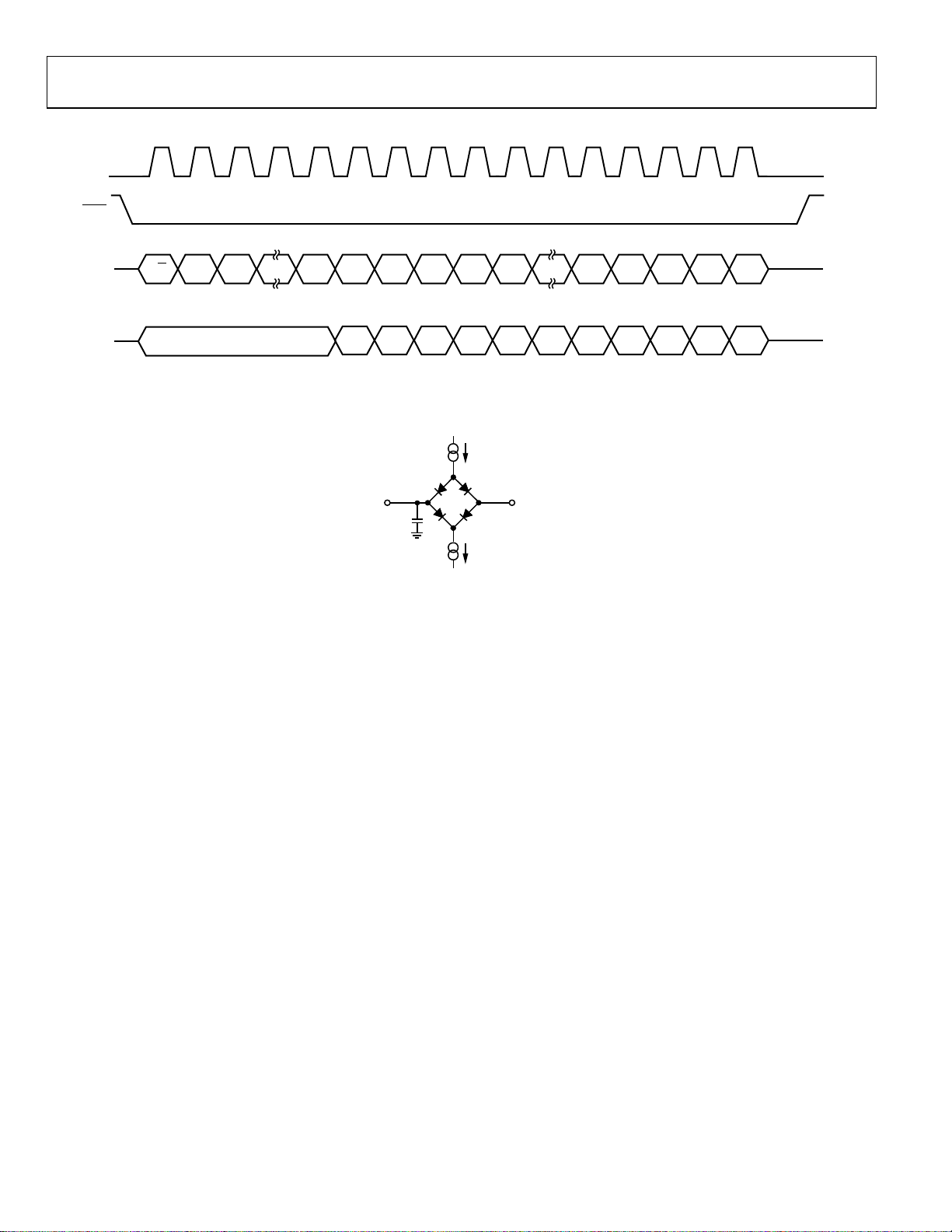

DETAILED FUNCTIONAL BLOCK DIAGRAM

CC

5.0V

AV

+15V

DD

SW

V

A

BOOST_A

AGND

DV

DGND

LDAC

CLEAR

SCLK

SDIN

SYNC

SDO

FAULT

ALERT

REFOUT

REFIN

AD1

AD0

DD

POWER-ON

RESET

INPUT

SHIFT

REGIS TER

AND

CONTROL

STATUS

REGIS TER

WATCHDOG

TIMER

(SPI ACTIVITY)

V

REF

REFERENCE

BUFFERS

AD5737

12

DAC

REG A

GAIN REG A

OFFSET REG A

DAC CHANNEL A

DAC CHANNEL B

DAC CHANNEL C

DAC CHANNEL D

DC-TO-DC

CONVERT ER

DYNAMIC

POWER

CONTROL

DAC

12

+

INPUTDATA

REG A

DAC A

SWB, SWC, SW

7.4V TO 29.5V

R2 R3

R1

D

V

SEN1VSEN2

V

BOOST_ B,VBOOST_C,VBOOST_D

I

OUT_A

R

SET_A

CHARTA

I

, I

SET_B

OUT_C

, R

SET_C

, I

OUT_D

, R

SET_D

OUT_B

R

CHARTB, CHARTC, CHARTD

10067-001

Figure 2.

Rev. A | Page 3 of 44

AD5737 Data Sheet

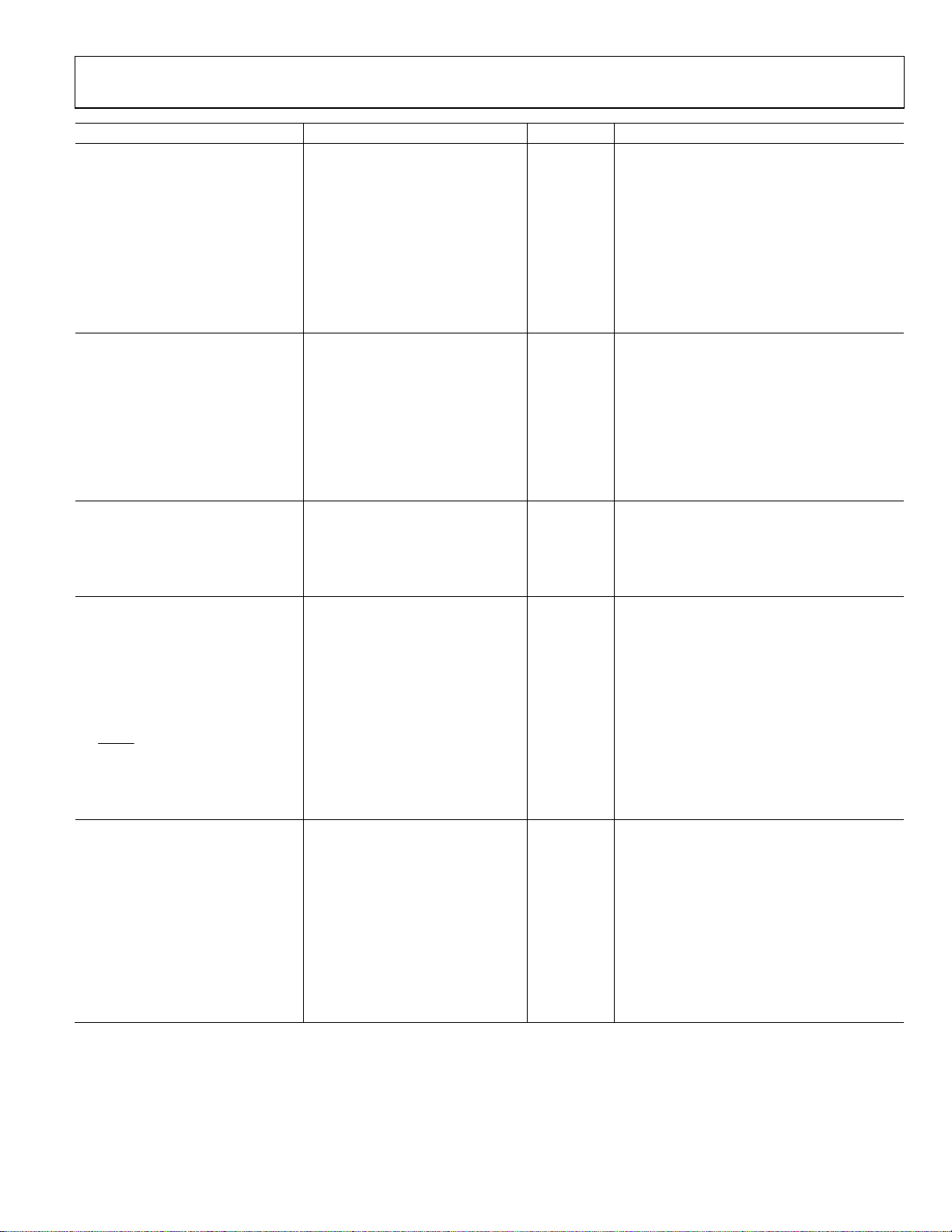

SPECIFICATIONS

AVDD = V

REFIN = 5 V; R

Table 1.

Parameter

CURRENT OUTPUT

Output Current Ranges 0 24 mA

0 20 mA

4 20 mA

Resolution 12 Bits

ACCURACY, EXTERNAL R

Total Unadjusted Error (TUE) −0.1 ±0.019 +0.1 % FSR

TUE Long-Term Stability 100 ppm FSR Drift after 1000 hours, TJ = 150°C

Relative Accuracy (INL) −0.032 ±0.006 +0.032 % FSR

Differential Nonlinearity (DNL) −1 +1 LSB Guaranteed monotonic

Offset Error −0.1 ±0.012 +0.1 % FSR

Offset Error Drift

Gain Error −0.1 ±0.004 +0.1 % FSR

Gain TC

Full-Scale Error −0.1 ±0.014 +0.1 % FSR

Full-Scale TC

DC Crosstalk 0.0005 % FSR External R

ACCURACY, INTERNAL R

Total Unadjusted Error (TUE)

TUE Long-Term Stability 180 ppm FSR Drift after 1000 hours, TJ = 150°C

Relative Accuracy (INL) −0.032 ±0.006 +0.032 % FSR

Differential Nonlinearity (DNL) −1 +1 LSB Guaranteed monotonic

Offset Error

Offset Error Drift

Gain Error −0.12 ±0.004 +0.12 % FSR

Gain TC

Full-Scale Error

Full-Scale TC

DC Crosstalk

OUTPUT CHARACTERISTICS

Current Loop Compliance Voltage

Output Current Drift vs. Time Drift after 1000 hours, ¾ scale output, TJ = 150°C

90 ppm FSR External R

140 ppm FSR Internal R

Resistive Load 1000 Ω

DC Output Impedance 100 MΩ

DC PSRR 0.02 1 μA/V

REFERENCE INPUT/OUTPUT

Reference Input

Reference Input Voltage 4.95 5 5.05 V For specified performance

DC Input Impedance 45 150 MΩ

Reference Output

Output Voltage 4.995 5 5.005 V TA = 25°C

Reference TC

= 15 V; DVDD = 2.7 V to 5.5 V; AVCC = 4.5 V to 5.5 V; dc-to-dc converter disabled; AGND = DGND = GNDSWx = 0 V;

BOOST_x

= 300 Ω; all specifications T

L

1

SET

Min Typ Max Unit Test Conditions/Comments

MIN

to T

, unless otherwise noted.

MAX

Assumes ideal resistor (see the External Current

Setting Resistor section for more information)

2

2

±3 ppm FSR/°C

2

±5 ppm FSR/°C

SET

3, 4

3, 4

−0.1 ±0.017 +0.1 % FSR

2

±6 ppm FSR/°C

2

±9 ppm FSR/°C

3, 4

−0.14 ±0.02 +0.14 % FSR

2

4

2

±4 ppm FSR/°C

−0.14 ±0.022 +0.14 % FSR

±14 ppm FSR/°C

−0.011 % FSR Internal R

V

BOOST_x

2.4

−

V

BOOST_x

2.7

V

−

SET

SET

SET

SET

The dc-to-dc converter has been characterized

with a maximum load of 1 kΩ, chosen such that

compliance is not exceeded; see Figure 30 and

the DC-DC MaxV bits in Table 27

2

2

−10 ±5 +10 ppm/°C

Rev. A | Page 4 of 44

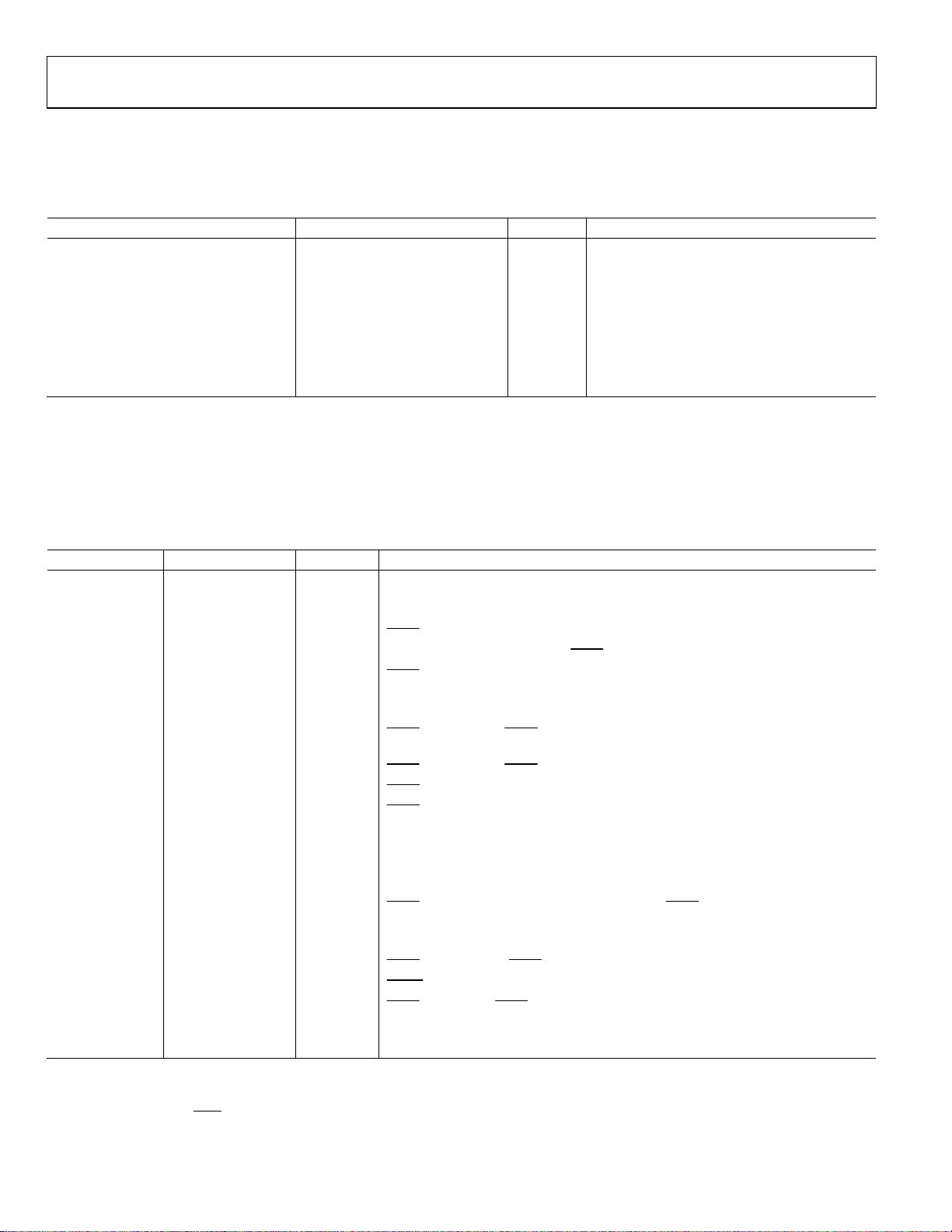

Data Sheet AD5737

Parameter

1

Output Noise (0.1 Hz to 10 Hz)

2

Noise Spectral Density

Output Voltage Drift vs. Time

2

Capacitive Load

Min Typ Max Unit Test Conditions/Comments

2

7 μV p-p

100 nV/√Hz At 10 kHz

2

180 ppm Drift after 1000 hours, TJ = 150°C

1000 nF

Load Current 9 mA See Figure 41

Short-Circuit Current 10 mA

Line Regulation

Load Regulation

Thermal Hysteresis

2

3 ppm/V See Figure 42

2

95 ppm/mA See Figure 41

2

160 ppm First temperature cycle

5 ppm Second temperature cycle

DC-TO-DC CONVERTER

Switch

Switch On Resistance 0.425 Ω

Switch Leakage Current 10 nA

Peak Current Limit 0.8 A

Oscillator

Oscillator Frequency 11.5 13 14.5 MHz

This oscillator is divided down to provide the

dc-to-dc converter switching frequency

Maximum Duty Cycle 89.6 % At 410 kHz dc-to-dc switching frequency

DIGITAL INPUTS

2

JEDEC compliant

Input High Voltage, VIH 2 V

Input Low Voltage, VIL 0.8 V

Input Current −1 +1 μA Per pin

Pin Capacitance 2.6 pF Per pin

DIGITAL OUTPUTS

2

SDO, ALERT Pins

Output Low Voltage, VOL 0.4 V Sinking 200 μA

Output High Voltage, VOH DVDD − 0.5 V Sourcing 200 μA

High Impedance Leakage

−1 +1 μA

Current

High Impedance Output

2.5 pF

Capacitance

FAU LT Pin

Output Low Voltage, VOL 0.4 V 10 kΩ pull-up resistor to DVDD

0.6 V At 2.5 mA

Output High Voltage, VOH 3.6 V 10 kΩ pull-up resistor to DVDD

POWER REQUIREMENTS

AVDD 9 33 V

DVDD 2.7 5.5 V

AVCC 4.5 5.5 V

AIDD 7 7.5 mA

DICC 9.2 11 mA

= DVDD, VIL = DGND, internal oscillator

V

IH

running, over supplies

AICC 1 mA Outputs unloaded, over supplies

5

I

BOOST

Power Dissipation 155 mW

1 mA Per channel, 0 mA output

= 15 V, DVDD = 5 V, dc-to-dc converter

AV

DD

enabled, outputs disabled

1

Temperature range: −40°C to +105°C; typical at +25°C.

2

Guaranteed by design and characterization; not production tested.

3

For current outputs with internal R

and loaded with the same code.

4

See the Current Output Mode with Internal R

5

Efficiency plots in Figure 32 through Figure 35 include the I

, the offset, full-scale, and TUE measurements exclude dc crosstalk. The measurements are made with all four channels enabled

SET

section for more information about dc crosstalk.

SET

quiescent current.

BOOST

Rev. A | Page 5 of 44

AD5737 Data Sheet

AC PERFORMANCE CHARACTERISTICS

AVDD = V

REFIN = 5 V; R

= 15 V; DVDD = 2.7 V to 5.5 V; AVCC = 4.5 V to 5.5 V; dc-to-dc converter disabled; AGND = DGND = GNDSWx = 0 V;

BOOST_x

= 300 Ω; all specifications T

L

MIN

to T

, unless otherwise noted.

MAX

Table 2.

Parameter

DYNAMIC PERFORMANCE, CURRENT

1

Min Typ Max Unit Test Conditions/Comments

OUTPUT

Output Current Settling Time 15 μs To 0.1% FSR, 0 mA to 24 mA range

See Test Conditions/Comments ms

For settling times when using the dc-to-dc converter, see Figure 25, Figure 26, and Figure 27

Output Noise (0.1 Hz to 10 Hz

0.15 LSB p-p 12-bit LSB, 0 mA to 24 mA range

Bandwidth)

Output Noise Spectral Density 0.5 nA/√Hz

Measured at 10 kHz, midscale output, 0 mA

to 24 mA range

1

Guaranteed by design and characterization; not production tested.

TIMING CHARACTERISTICS

AVDD = V

REFIN = 5 V; R

Table 3.

Parameter

t1 33 ns min SCLK cycle time

t2 13 ns min SCLK high time

t3 13 ns min SCLK low time

t4 13 ns min

t5 13 ns min

t6 198 ns min

t7 5 ns min Data setup time

t8 5 ns min Data hold time

t9 20 μs min

5 μs min

t10 10 ns min

t11 500 ns max

t12 See Table 2 μs max DAC output settling time

t13 10 ns min CLEAR high time

t14 5 μs max CLEAR activation time

t15 40 ns max SCLK rising edge to SDO valid

t16

21 μs min All DACs updated

5 μs min Single DAC updated

t17 500 ns min

t18 800 ns min

4

t

19

20 μs min All DACs updated

5 μs min Single DAC updated

1

Guaranteed by design and characterization; not production tested.

2

All input signals are specified with t

3

See Figure 3, Figure 4, Figure 5, and Figure 6.

4

This specification applies if

= 15 V; DVDD = 2.7 V to 5.5 V; AVCC = 4.5 V to 5.5 V; dc-to-dc converter disabled; AGND = DGND = GNDSWx = 0 V;

BOOST_x

= 300 Ω; all specifications T

L

1, 2, 3

Limit at T

MIN

, T

Unit Description

MAX

MIN

to T

, unless otherwise noted.

MAX

falling edge to SCLK falling edge setup time

SYNC

24th/32nd SCLK falling edge to SYNC

high time

SYNC

rising edge to LDAC falling edge (all DACs updated or any channel has

SYNC

rising edge (see ) Figure 53

digital slew rate control enabled)

rising edge to LDAC falling edge (single DAC updated)

SYNC

pulse width low

LDAC

falling edge to DAC output response time

LDAC

rising edge to DAC output response time (LDAC = 0)

SYNC

falling edge to SYNC rising edge

LDAC

pulse width

RESET

high to next SYNC low (digital slew rate control enabled)

SYNC

= t

= 5 ns (10% to 90% of DVDD) and timed from a voltage level of 1.2 V.

RISE

FALL

LDAC

is held low during the write cycle; otherwise, see t9.

Rev. A | Page 6 of 44

Data Sheet AD5737

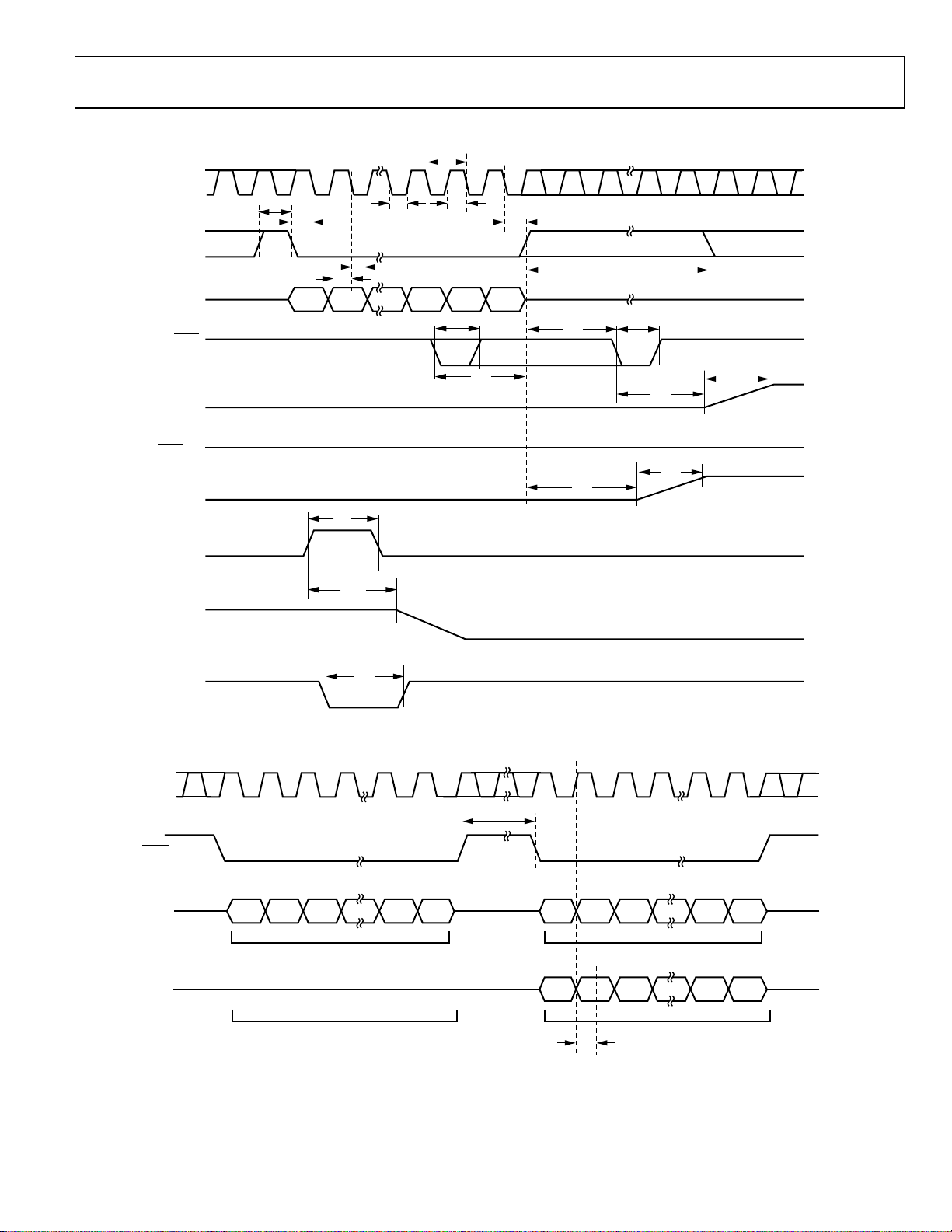

Timing Diagrams

t

1

SCLK

SYNC

SDIN

LDAC

I

OUT_x

LDAC = 0

I

OUT_x

CLEAR

I

OUT_x

12 24

t

6

t

4

t

7

MSB

t

13

t

t

3

t

8

14

t

2

t

10

t

5

t

19

LSB

t

t

9

t

17

t

16

10

t

t

11

t

12

12

t

RESET

18

10067-002

Figure 3. Serial Interface Timing Diagram

SCLK

SYNC

SDIN

SDO

1 1

MSB MSBLSB LSB

INPUT WORD SPECIFIES

REGISTER TO BE RE AD

UNDEFINED SELECTED REGISTER DATA

24 24

t

6

NOP CONDITI ON

MSB LSB

t

15

CLOCKED OUT

Figure 4. Readback Timing Diagram

10067-003

Rev. A | Page 7 of 44

AD5737 Data Sheet

C

SCLK

SYN

SDIN

SDO

LSB MSB

12 16

DUT_

R/W

DUT_

AD1

SDO DISABLED

XXXD15D14 D1D0

AD0

SDO_

ENAB

STATUSSTATUSSTATUSSTATUS

10067-004

Figure 5. Status Readback During Write, Timing Diagram

200µA I

TO OUTPUT

PIN

C

L

50pF

200µA I

Figure 6. Load Circuit for SDO Timing Diagrams

OL

OH

VOH (MIN) OR

V

(MAX)

OL

10067-005

Rev. A | Page 8 of 44

Data Sheet AD5737

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted. Transient currents of up to

100 mA do not cause SCR latch-up.

Table 4.

Parameter Rating

AVDD, V

to AGND, DGND −0.3 V to +33 V

BOOST_x

AVCC to AGND −0.3 V to +7 V

DVDD to DGND −0.3 V to +7 V

Digital Inputs to DGND

−0.3 V to DV

+ 0.3 V or +7 V

DD

(whichever is less)

Digital Outputs to DGND

−0.3 V to DV

+ 0.3 V or +7 V

DD

(whichever is less)

REFIN, REFOUT to AGND

−0.3 V to AV

+ 0.3 V or +7 V

DD

(whichever is less)

I

OUT_x

to AGND

AGND to V

BOOST_x

or 33 V if

using the dc-to-dc converter

SWx to AGND −0.3 V to +33 V

AGND, GNDSWx to DGND −0.3 V to +0.3 V

Operating Temperature Range ( TA)

Industrial1 −40°C to +105°C

Storage Temperature Range −65°C to +150°C

Junction Temperature (TJ max) 125°C

Power Dissipation (TJ max − TA)/θJA

Lead Temperature JEDEC industry standard

Soldering J-STD-020

1

Power dissipated on chip must be derated to keep the junction temperature

below 125°C.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

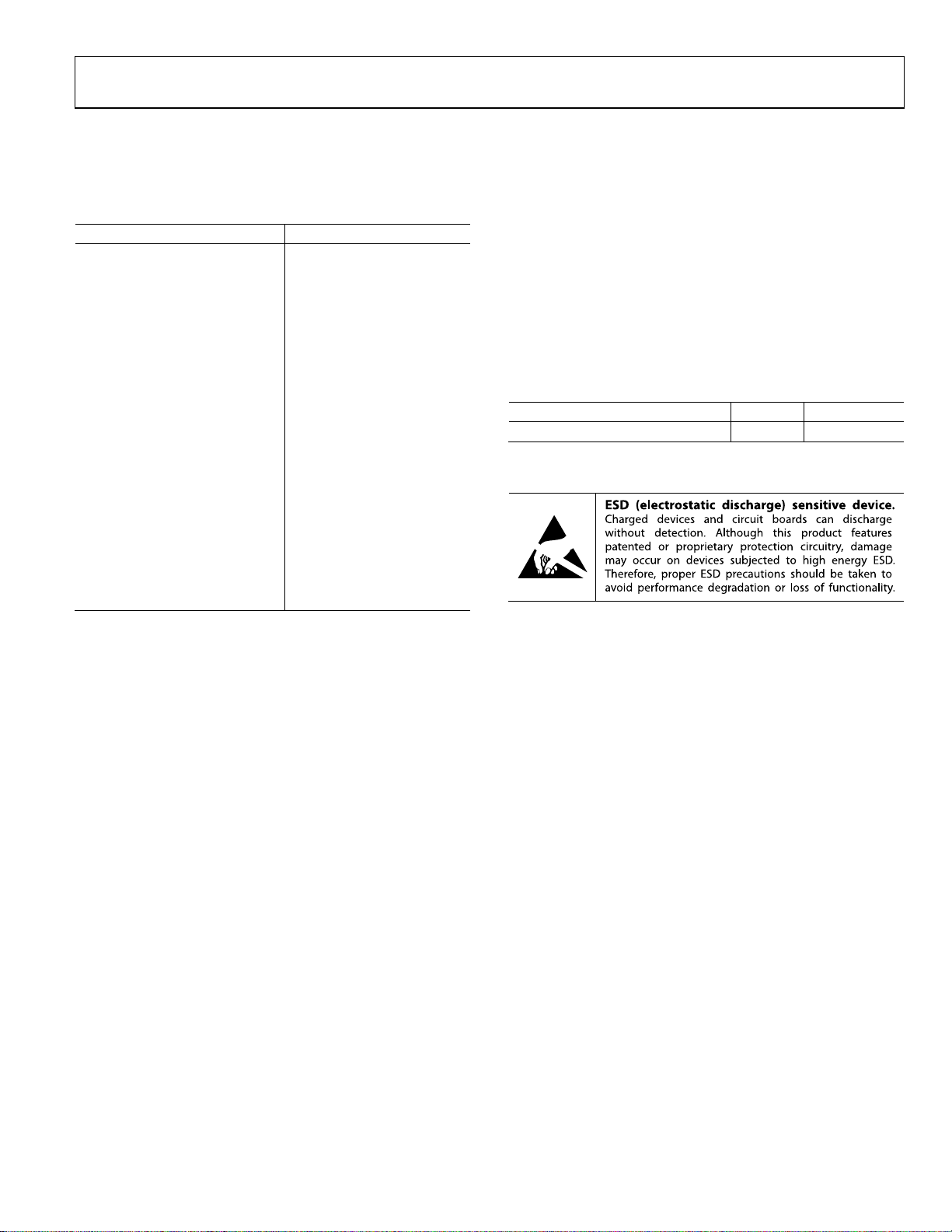

THERMAL RESISTANCE

Junction-to-air thermal resistance (θJA) is specified for a JEDEC

4-layer test board.

Table 5. Thermal Resistance

Package Type θJA Unit

64-Lead LFCSP (CP-64-3) 20 °C/W

ESD CAUTION

Rev. A | Page 9 of 44

AD5737 Data Sheet

C

2

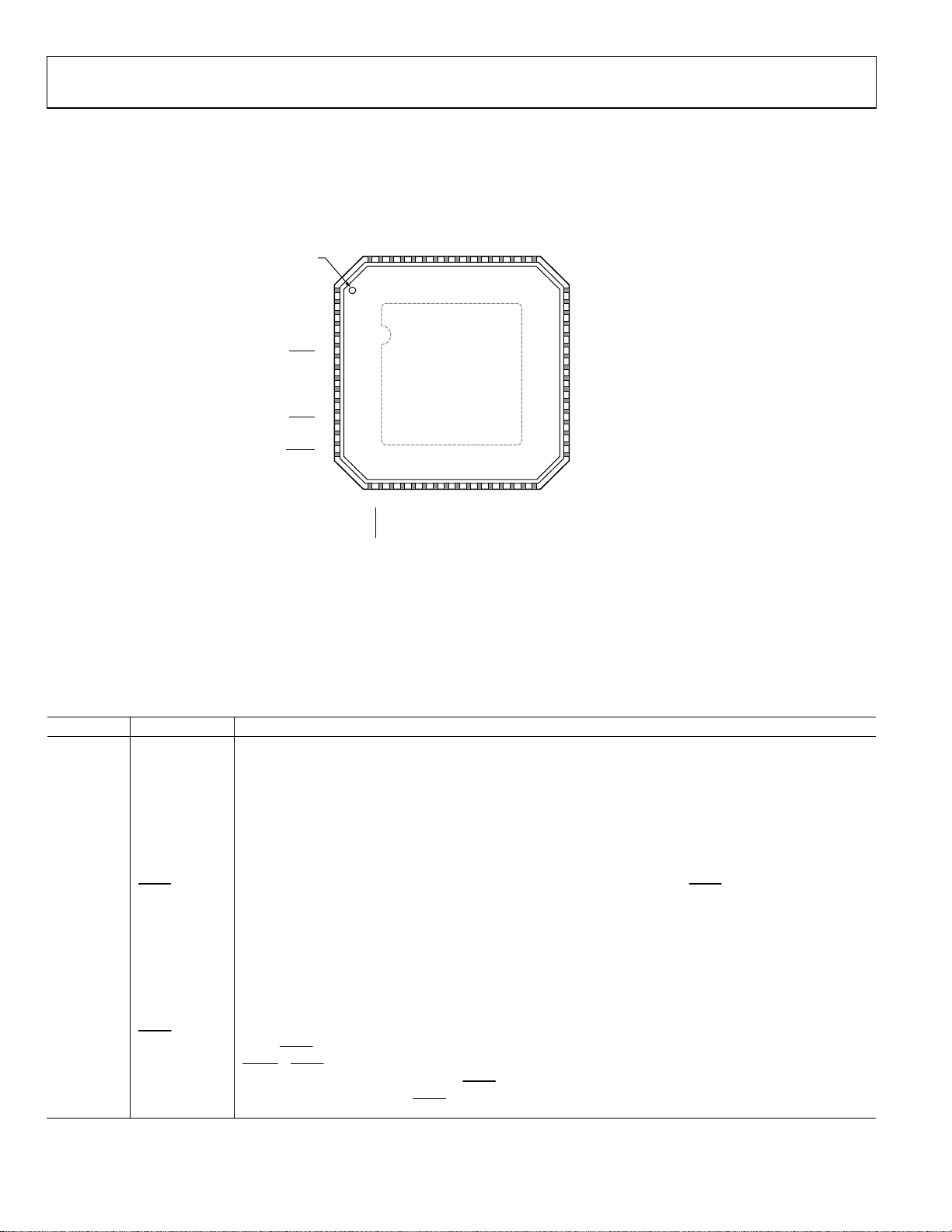

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

DCDC_D

INDI

PIN 1

ATO R

SET_CRSET_D

REFOUT

REFINNCCHARTD

R

646362616059585756555453525150

BOOST_ D

OUT_D

IGATED

COMP

V

NC

I

AGNDNCCHARTCNCIGATEC

49

R

1

SET_B

2

R

SET_A

AD0

AD1

SYNC

SCLK

SDIN

SDO

DV

DGND

LDAC

CLEAR

ALERT

FAU LT

3

4

5

6

7

8

9

10

11

DD

12

13

14

15

16

171819202122232425262728293031

DGND

RESET

DD

NC

AV

AD5737

TOP VIEW

(Not to Scale)

NC

DCDC_A

IGATEA

BOOST_A

CHARTA

V

COMP

32

NC

NC

OUT_A

AGND

I

DCDC_B

IGATEB

CHARTB

COMP

REFGND

REFGND

NOTES

1. NC = NO CONNEC T. DO NOT CONNECT TO THIS PIN.

. THE EXPOSED PADDLE SHOULD BE CONNECTED TO AGND, OR, ALTERNATIVELY,

IT CAN BE LEFT ELECTRI CALLY UNCONNECTED. IT IS RECOMMENDED THAT

THE PADDLE BE THERMALLY CONNECTED TO A COPPER PLANE F OR ENHANCED

THERMAL PERFO RMANCE.

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

COMP

I

OUT_C

V

BOOST_C

AV

CC

SW

C

GNDSW

GNDSW

SW

D

AGND

SW

A

GNDSW

GNDSW

SW

B

AGND

V

BOOST_B

I

OUT_B

DCDC_C

C

D

A

B

10067-006

Figure 7. Pin Configuration

Table 6. Pin Function Descriptions

Pin No. Mnemonic Description

1 R

2 R

SET_B

SET_A

An external, precision, low drift, 15 kΩ current setting resistor can be connected to this pin to improve the

temperature drift performance. For more information, see the External Current Setting Resistor section.

I

OUT_B

An external, precision, low drift, 15 kΩ current setting resistor can be connected to this pin to improve the

temperature drift performance. For more information, see the External Current Setting Resistor section.

I

OUT_A

3 REFGND Ground Reference Point for Internal Reference.

4 REFGND Ground Reference Point for Internal Reference.

5 AD0 Address Decode for the Device Under Test (DUT) on the Board.

6 AD1 Address Decode for the DUT on the Board.

7

Frame Synchronization Signal for the Serial Interface. Active low input. When SYNC is low, data is clocked

SYNC

into the input shift register on the falling edge of SCLK.

8 SCLK

Serial Clock Input. Data is clocked into the input shift register on the falling edge of SCLK. The serial interface

operates at clock speeds of up to 30 MHz.

9 SDIN Serial Data Input. Data must be valid on the falling edge of SCLK.

10 SDO Serial Data Output. Used to clock data from the serial register in readback mode (see Figure 4 and Figure 5).

11 DVDD Digital Supply Pin. The voltage range is from 2.7 V to 5.5 V.

12 DGND Digital Ground.

13

Load DAC. This active low input is used to update the DAC register and, consequently, the DAC outputs.

LDAC

When LDAC is tied permanently low, the addressed DAC data register is updated on the rising edge of

SYNC. If LDAC is held high during the write cycle, the DAC input register is updated, but the DAC output

(see ). Using this mode, all analog outputs can be

is updated only on the falling edge of LDAC

updated simultaneously. The

LDAC pin must not be left unconnected.

Figure 3

Rev. A | Page 10 of 44

Data Sheet AD5737

Pin No. Mnemonic Description

14 CLEAR

15 ALERT

16

FAU LT

17 DGND Digital Ground.

18

RESET

19 AVDD Positive Analog Supply Pin. The voltage range is from 9 V to 33 V.

20 NC No Connect. Do not connect to this pin.

21 CHARTA HART Input Connection for DAC Channel A. For more information, see the HART Connectivity section.

22 IGATEA

23 COMP

24 V

BOOST_A

DCDC_A

25 NC No Connect. Do not connect to this pin.

26 I

Current Output Pin for DAC Channel A.

OUT_A

27 AGND Ground Reference Point for Analog Circuitry. This pin must be connected to 0 V.

28 NC No Connect. Do not connect to this pin.

29 CHARTB HART Input Connection for DAC Channel B. For more information, see the HART Connectivity section.

30 NC No Connect. Do not connect to this pin.

31 IGATEB

32 COMP

33 I

34 V

DCDC_B

Current Output Pin for DAC Channel B.

OUT_B

BOOST_B

35 AGND Ground Reference Point for Analog Circuitry. This pin must be connected to 0 V.

36 SWB

37 GNDSWB Ground Connection for DC-to-DC Switching Circuit. This pin should always be connected to ground.

38 GNDSWA Ground Connection for DC-to-DC Switching Circuit. This pin should always be connected to ground.

39 SWA

40 AGND Ground Reference Point for Analog Circuitry. This pin must be connected to 0 V.

41 SWD

42 GNDSWD Ground Connection for DC-to-DC Switching Circuit. This pin should always be connected to ground.

43 GNDSWC Ground Connection for DC-to-DC Switching Circuit. This pin should always be connected to ground.

44 SWC

45 AVCC Supply for DC-to-DC Circuitry. The voltage range is from 4.5 V to 5.5 V.

46 V

47 I

48 COMP

BOOST_C

Current Output Pin for DAC Channel C.

OUT_C

DCDC_C

Active High, Edge Sensitive Input. When this pin is asserted, the output current is set to the programmed

clear code bit setting. Only channels enabled to be cleared are cleared. For more information, see the

Asynchronous Clear section. When CLEAR is active, the DAC output register cannot be written to.

Active High Output. This pin is asserted when there is no SPI activity on the interface pins for a preset time.

For more information, see the Alert Output section.

Active Low, Open-Drain Output. This pin is asserted low when any of the following conditions is detected:

open circuit, PEC error, or an overtemperature condition (see the Fault Output section).

Hardware Reset, Active Low Input.

Optional Connection for External Pass Transistor. Leave this pin unconnected when using the dc-to-dc

converter. For more information, see the External PMOS Mode section.

DC-to-DC Compensation Capacitor. Connect a 10 nF capacitor from this pin to ground. Used to regulate the

feedback loop of the Channel A dc-to-dc converter. Alternatively, if using an external compensation resistor,

place a resistor in series with a capacitor to ground from this pin. For more information, see the DC-to-DC

Converter Compensation Capacitors section and the AI

Supply Requirements—Slewing section.

CC

Supply for Channel A Current Output Stage (see Figure 48). To use the dc-to-dc converter, connect this pin

as shown in Figure 55.

Optional Connection for External Pass Transistor. Leave this pin unconnected when using the dc-to-dc

converter. For more information, see the External PMOS Mode section.

DC-to-DC Compensation Capacitor. Connect a 10 nF capacitor from this pin to ground. Used to regulate the

feedback loop of the Channel B dc-to-dc converter. Alternatively, if using an external compensation resistor,

place a resistor in series with a capacitor to ground from this pin. For more information, see the DC-to-DC

Converter Compensation Capacitors section and the AI

Supply Requirements—Slewing section.

CC

Supply for Channel B Current Output Stage (see Figure 48). To use the dc-to-dc converter, connect this pin

as shown in Figure 55.

Switching Output for Channel B DC-to-DC Circuitry. To use the dc-to-dc converter, connect this pin as

shown in Figure 55.

Switching Output for Channel A DC-to-DC Circuitry. To use the dc-to-dc converter, connect this pin as

shown in Figure 55.

Switching Output for Channel D DC-to-DC Circuitry. To use the dc-to-dc converter, connect this pin as

shown in Figure 55.

Switching Output for Channel C DC-to-DC Circuitry. To use the dc-to-dc converter, connect this pin as

shown in Figure 55.

Supply for Channel C Current Output Stage (see Figure 48). To use the dc-to-dc converter, connect this pin

as shown in Figure 55.

DC-to-DC Compensation Capacitor. Connect a 10 nF capacitor from this pin to ground. Used to regulate the

feedback loop of the Channel C dc-to-dc converter. Alternatively, if using an external compensation resistor,

place a resistor in series with a capacitor to ground from this pin. For more information, see the DC-to-DC

Converter Compensation Capacitors section and the AI

Rev. A | Page 11 of 44

Supply Requirements—Slewing section.

CC

AD5737 Data Sheet

Pin No. Mnemonic Description

49 IGATEC

50 NC No Connect. Do not connect to this pin.

51 CHARTC HART Input Connection for DAC Channel C. For more information, see the HART Connectivity section.

52 NC No Connect. Do not connect to this pin.

53 AGND Ground Reference Point for Analog Circuitry. This pin must be connected to 0 V.

54 I

Current Output Pin for DAC Channel D.

OUT_D

55 NC No Connect. Do not connect to this pin.

56 V

57 COMP

BOOST_D

DCDC_D

58 IGATED

59 CHARTD HART Input Connection for DAC Channel D. For more information, see the HART Connectivity section.

60 NC No Connect. Do not connect to this pin.

61 REFIN External Reference Voltage Input.

62 REFOUT

63 R

64 R

SET_D

SET_C

EPAD

Optional Connection for External Pass Transistor. Leave this pin unconnected when using the dc-to-dc

converter. For more information, see the External PMOS Mode section.

Supply for Channel D Current Output Stage (see Figure 48). To use the dc-to-dc converter, connect this pin

as shown in Figure 55.

DC-to-DC Compensation Capacitor. Connect a 10 nF capacitor from this pin to ground. Used to regulate the

feedback loop of the Channel D dc-to-dc converter. Alternatively, if using an external compensation resistor,

place a resistor in series with a capacitor to ground from this pin. For more information, see the DC-to-DC

Converter Compensation Capacitors section and the AICC Supply Requirements—Slewing section.

Optional Connection for External Pass Transistor. Leave this pin unconnected when using the dc-to-dc

converter. For more information, see the External PMOS Mode section.

Internal Reference Voltage Output. It is recommended that a 0.1 μF capacitor be placed between REFOUT

and REFGND.

An external, precision, low drift, 15 kΩ current setting resistor can be connected to this pin to improve the

temperature drift performance. For more information, see the External Current Setting Resistor section.

I

OUT_D

An external, precision, low drift, 15 kΩ current setting resistor can be connected to this pin to improve the

temperature drift performance. For more information, see the External Current Setting Resistor section.

I

OUT_C

Exposed Pad. The exposed paddle should be connected to AGND, or, alternatively, it can be left electrically

unconnected. It is recommended that the paddle be thermally connected to a copper plane for enhanced

thermal performance.

Rev. A | Page 12 of 44

Data Sheet AD5737

TYPICAL PERFORMANCE CHARACTERISTICS

CURRENT OUTPUTS

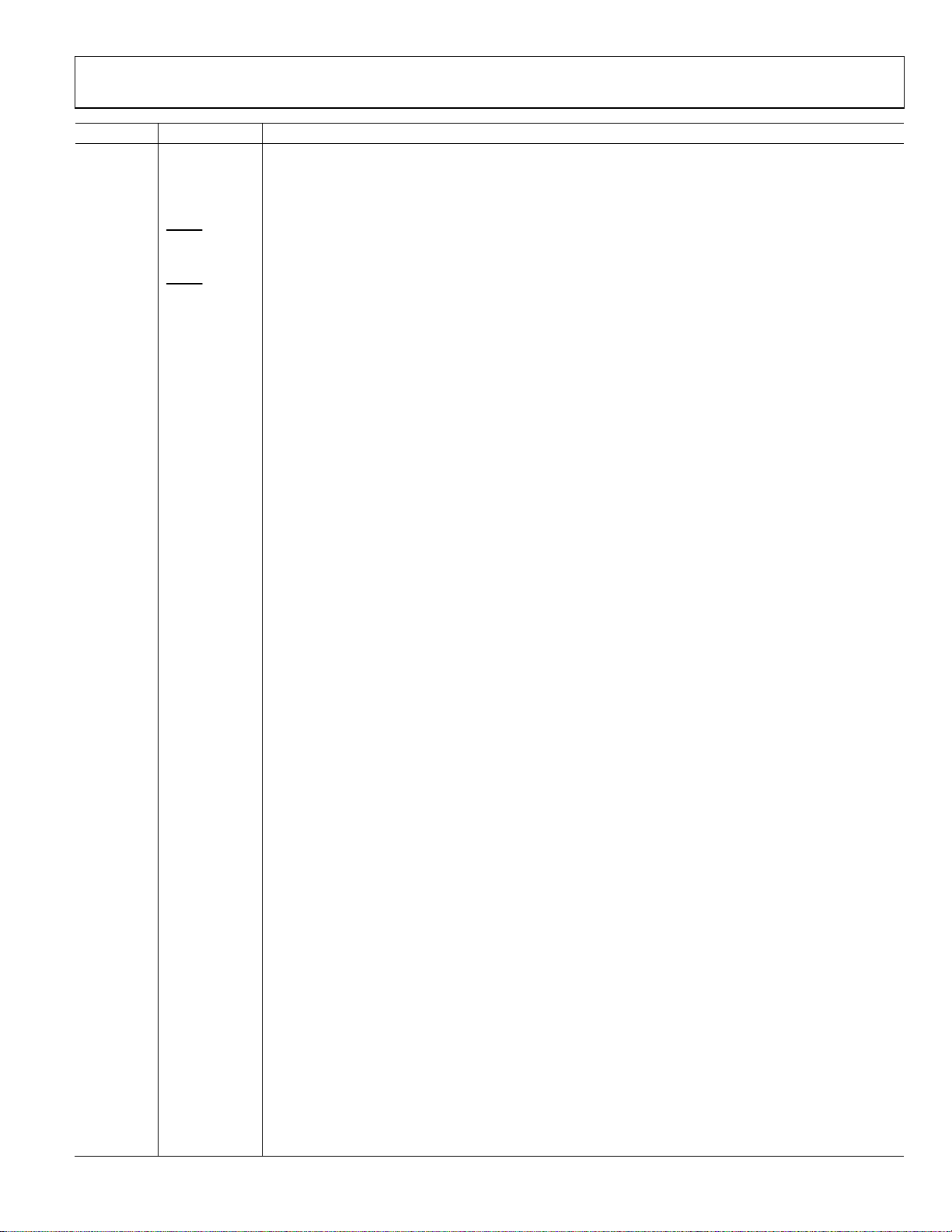

0.008

0.006

4mA TO 20mA, INTERNAL R

4mA TO 20mA, EXTERNAL R

4mA TO 20mA, INTERNAL R

4mA TO 20mA, EXTERNAL R

, WITH DC- TO-DC CONVERT ER

SET

,WITHDC-TO-DCCONVERTER

SET

SET

SET

0.004

0.002

0

INL ERROR (%FSR)

–0.002

–0.004

–0.006

AVDD=15V

T

=25°C

A

0 1000 2000 3000 4000

CODE

Figure 8. Integral Nonlinearity Error vs. DAC Code Figure 11. Integral Nonlinearity Error vs. Temperature, Internal R

10067-231

0.008

0.006

0.004

0.002

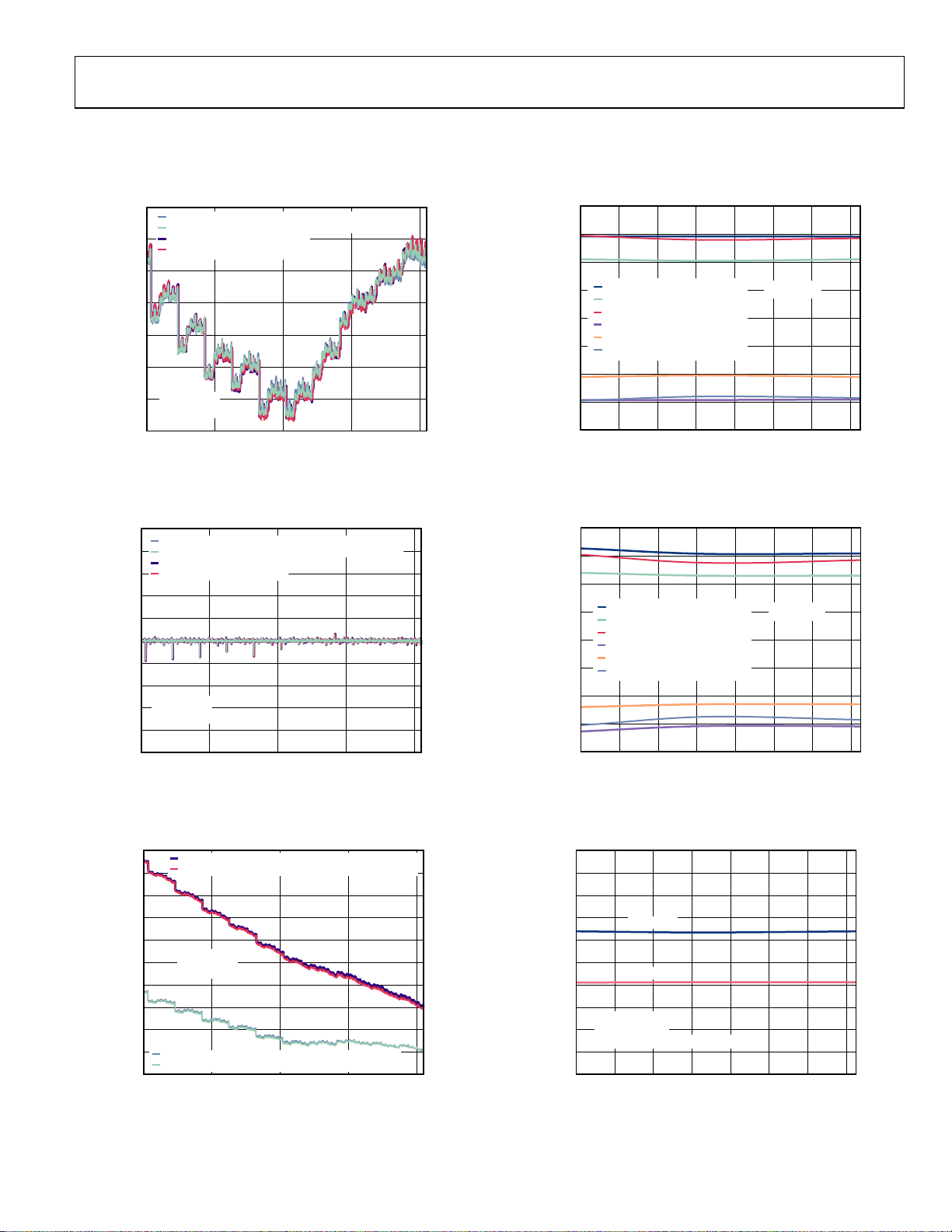

–0.002

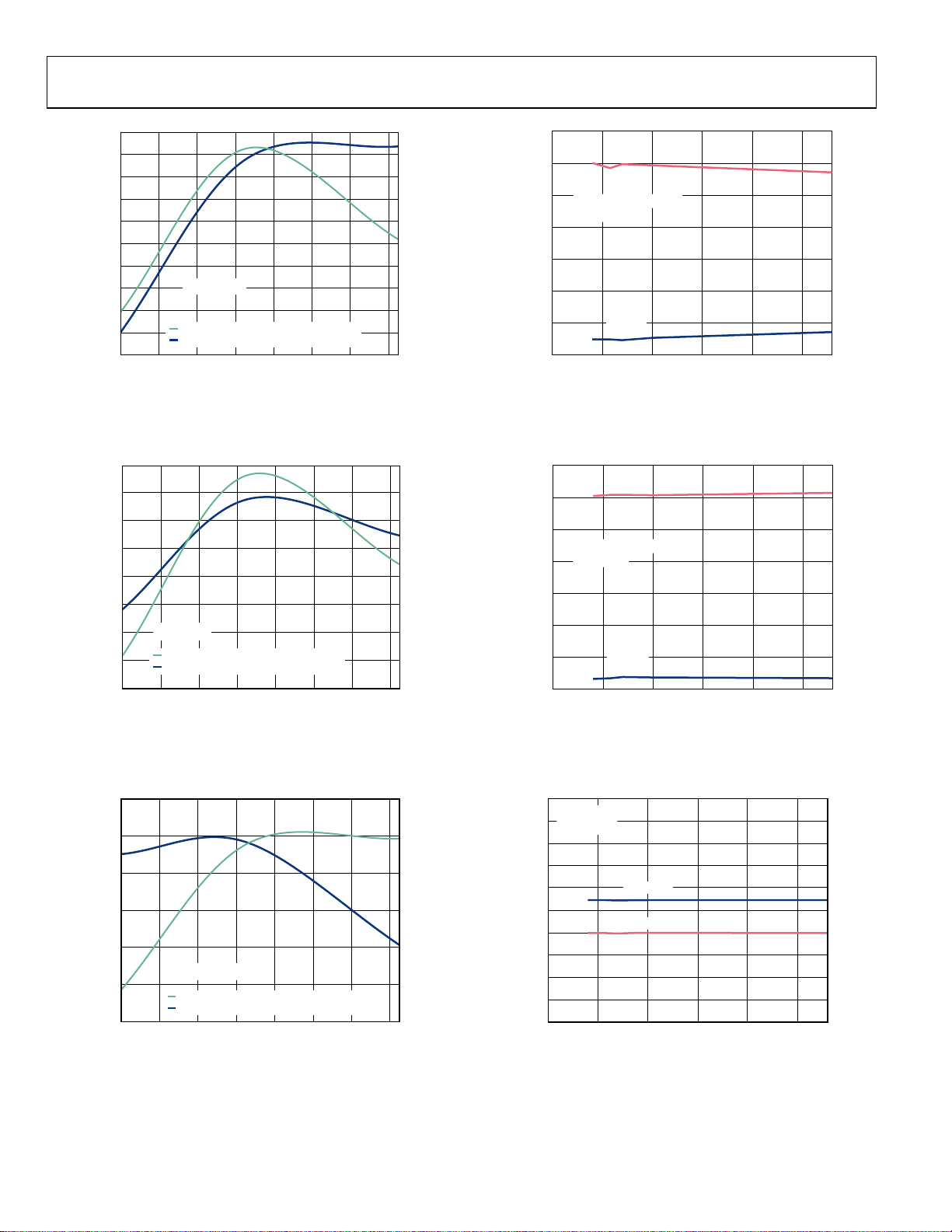

INL ERROR (%FSR)

4mA TO 20mA RANGE M AX INL

0mA TO 24mA RANGE M AX INL

0mA TO 20mA RANGE MAX INL

0

4mA TO 20mA RANGE MIN INL

0mA TO 24mA RANGE MIN INL

0mA TO 20mA RANGE MIN INL

AVDD=15V

–0.004

–0.006

–0.008

–40 –20 0 20 40 60 80 100

TEMPERATURE (°C)

10067-234

SET

1.0

4mA TO 20mA, INTERNAL R

0.8

4mA TO 20mA, EXTERNAL R

4mA TO 20mA, INTERNAL R

4mA TO 20mA, EXTERNAL R

0.6

,WITH DC-TO-DC CONVERTER

SET

,WITHDC-TO-DCCONVERTER

SET

SET

SET

0.4

0.2

0

–0.2

DNL ERROR (LSB)

–0.4

AVDD=15V

–0.6

T

=25°C

A

–0.8

–1.0

0 1000 2000 3000 4000

CODE

10067-232

0.008

0.006

0.004

–0.002

INL ERROR (%FSR)

0.002

4mA TO 20mA RANGE MAX INL

0mA TO 24mA RANGE MAX INL

0mA TO 20mA RANGE MAX INL

0

4mA TO 20mA RANGE MIN INL

0mA TO 24mA RANGE MIN INL

0mA TO 20mA RANGE MIN INL

AVDD=15V

–0.004

–0.006

–0.008

–40 –20 0 20 40 60 80 100

TEMPERATURE (°C)

Figure 9. Differential Nonlinearity Error vs. DAC Code Figure 12. Integral Nonlinearity Error vs. Temperature, External R

0.06

0.05

4mA TO 20mA, INTERNAL R

4mA TO 20mA, INTERNAL R

SET

, WITH DC- TO-DC CONVERT ER

SET

0.04

0.03

0.02

0.01

AVDD=15V

=25°C

T

A

0

–0.01

–0.02

TOTAL UNADJUSTED ERROR (%FSR)

–0.03

–0.04

4mA TO 20mA, EXTERNAL R

4mA TO 20mA, EXTERNAL R

SET

,WITHDC-TO-DCCONVERTER

SET

0 1000 2000 3000 4000

CODE

10067-233

1.0

0.8

0.6

0.4

MAX DNL

0.2

0

–0.2

DNL ERROR (LSB)

–0.4

–0.6

–0.8

–1.0

–40 –20 0 20 40 60 80 100

MIN DNL

AVDD=15V

ALL RANGES

INTERNAL AND EXTERNA L R

SET

TEMPERATURE (°C)

Figure 10. Total Unadjusted Error vs. DAC Code Figure 13. Differential Nonlinearity Error vs. Temperature

10067-235

SET

10067-236

Rev. A | Page 13 of 44

AD5737 Data Sheet

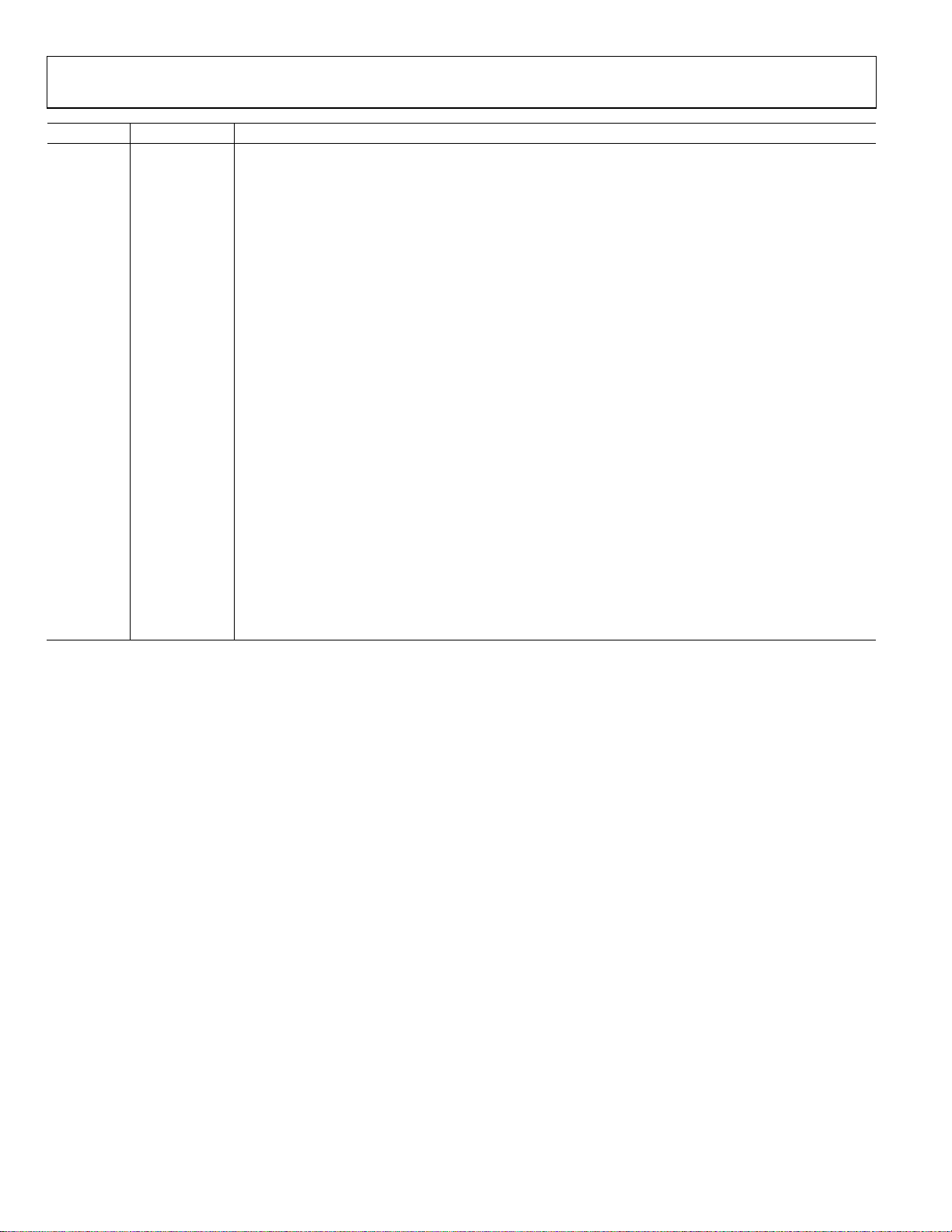

0.025

0.020

0.015

0.010

0.005

0

–0.005

–0.010

AVDD = 15V

–0.015

TOTAL UNADJUSTED ERROR (%FSR)

–0.020

–0.025

–40 –20 0 20 40 60 80 100

4mA TO 20mA RANGE, INTERNAL R

4mA TO 20mA RANGE, EXTERNAL R

TEMPERATURE (°C)

Figure 14. Total Unadjusted Error vs. Temperature

0.020

0.015

0.010

0.005

0

–0.005

–0.010

FULL-SCAL E ERROR (%FSR)

–0.015

–0.020

AVDD = 15V

4mA TO 20mA RANGE, INT ERNAL R

4mA TO 20mA RANGE, EXT ERNAL R

–40 –20 0 20 40 60 80 100

TEMPERATURE (°C)

Figure 15. Full-Scale Error vs. Temperature

SET

SET

SET

SET

10067-155

10067-157

0.008

0.006

0.004

MAX INL

4mA TO 20mA RANGE

TA = 25°C

0.002

0

INL ERROR (%FSR)

–0.002

–0.004

–0.006

51015202530

MIN INL

SUPPLY (V)

Figure 17. Integral Nonlinearity Error vs. Supply, External R

0.008

MAX INL

0.006

0.004

4mA TO 20mA RANGE

0.002

TA = 25°C

0

INL ERROR (%FSR)

–0.002

–0.004

–0.006

51015202530

MIN INL

SUPPLY (V)

Figure 18. Integral Nonlinearity Error vs. Supply, Internal R

10067-240

SET

10067-241

SET

0.005

0

–0.005

–0.010

–0.015

GAIN ERROR (%FS R)

AVDD = 15V

–0.020

–0.025

–40 –20 0 20 40 60 80 100

4mA TO 20mA RANGE, I NTERNAL R

4mA TO 20mA RANGE, EXT ERNAL R

TEMPERATURE (°C)

Figure 16. Gain Error vs. Temperature

SET

SET

10067-159

Rev. A | Page 14 of 44

1.0

ALL RANGES

0.8

TA = 25°C

0.6

0.4

0.2

MAX DNL

0

–0.2

DNL ERROR (LSB)

–0.4

MIN DNL

–0.6

–0.8

–1.0

5 1015202530

SUPPLY (V)

Figure 19. Differential Nonlinearity Error vs. Supply

10067-242

Loading...

Loading...