Analog Devices AD1990 2 4 6 pra Datasheet

Class-D Audio Power Amplifier

Preliminary Technical Data

FEATURES

Integrated Stereo Modulator & Power Stage

0.005% THD+N

101.5dB Dynamic Range

PSRR > 65 dB

< 0.3 Ω (per transistor)

R

DS-ON

Efficiency > 80% @ 5W/6 Ω

EMI Optimized Modulator

On-Off-Mute Pop Noise Suppression

Short Circuit Protection

Over-Temperature Protection

Low Cost DMOS Process

APPLICATIONS

Flat Panel Televisions

Automotive Amplifiers

PC Audio Systems

Mini Components

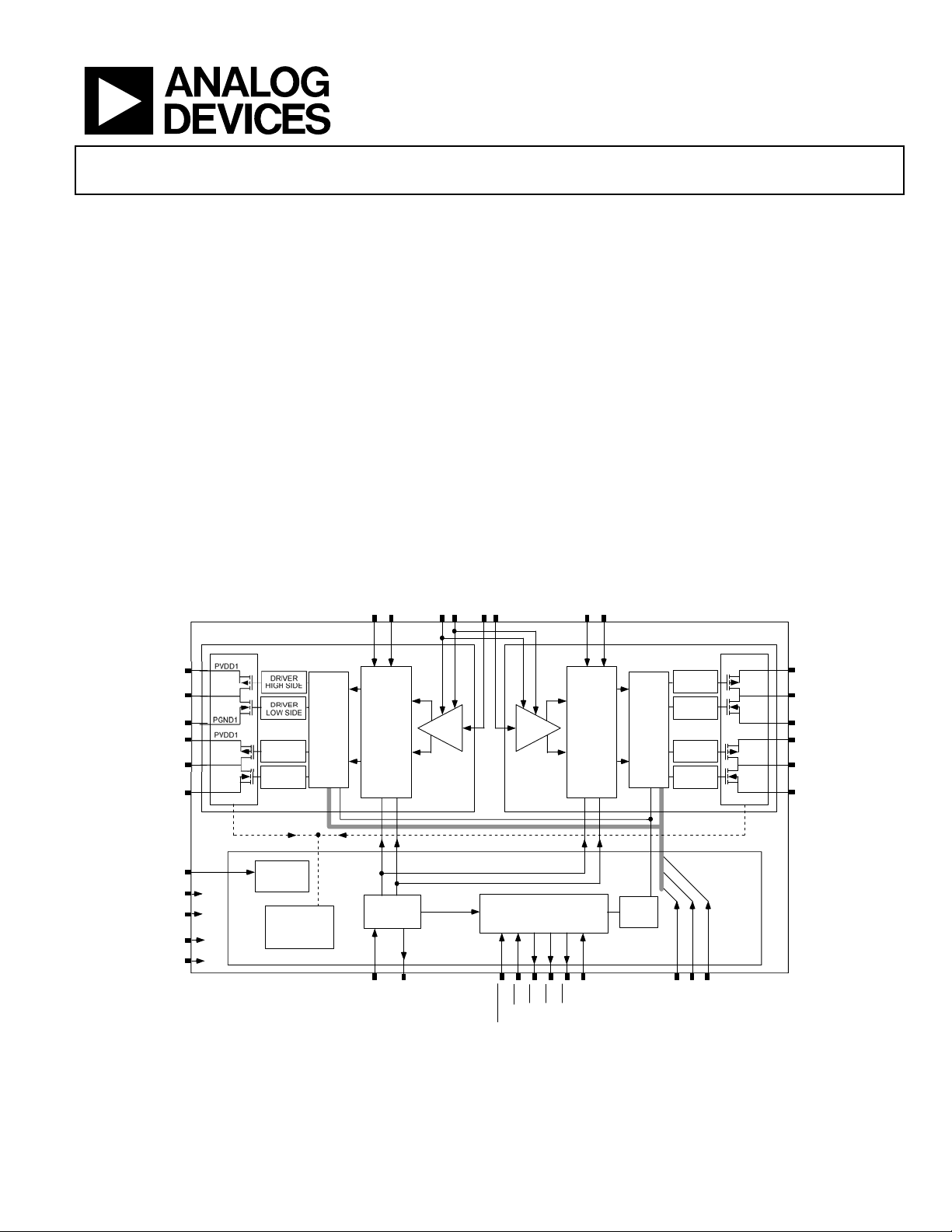

AD1990/AD1992/AD1994/AD1996

GENERAL DESCRIPTION

The AD199x is a two channel Bridge Tied Load (BTL)

switching audio power amplifier with integrated

The modulator accepts a 1Vrms input signal (maximum power)

and generates a switching waveform to drive speakers directly.

One of the two modulators can control both output stages

providing twice the current for single-channel applications. A

digital, microcontroller-compatible interface provides control of

reset, mute and PGA gain as well as output signals for thermal

and over-current error conditions. The output stage can operate

from supply voltages ranging from 8V to 20V. The analog

modulator and digital logic operate from a 5V supply.

AD1990: 5Wx2 (10Wx1)

AD1992: 10Wx2 (20Wx1)

AD1994: 25Wx2 (50Wx1)

AD1996: 40Wx2 (80Wx1)

0

+

-

L

L

F

F

N

N

62

63

1

L

A

G

P

3132

N

I

A

60 53

R

N

I

A

A

G

P

+

R

F

N

50 51

R

F

N

∑∆ modulator.

PVDD

OUTL+

PGND1

PVDD1

11,12,13

OUTL-

14,15,16

PGND1

REF_FILT

AVDD

AGND

DVDD

DGND

7,8

4,5,6

1,2,3

9,10

PGND1

55

57

56

24,25

23,26

LEFT CHANNEL

CONTROL

DRIVER

HIGH SIDE

DRIVER

LOW SIDE

VOLTAGE

REFERENCE

TEMPERATURE

SENSE &

OVER-CURRENT

PROTECTION

LEVEL

SHIFT

+

DEAD

TIME

Σ∆

MODULATOR

Ø1 Ø2

OSCILLATOR

27 28 22 21 20

CLKI

PGA

CLKO

Figure 1. Block Diagram

Rev. PrA – 1/20/05

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Anal og Devices. Trademarks and

registered trademarks are the property of their respective companies.

RIGHT CHANNEL

DRIVER

HIGH SIDE

DRIVER

LEVEL

LOW SIDE

SHIFT

+

DEAD

TIME

CONTROL

MUTE/

POP

CONTROL

DRIVER

HIGH SIDE

DRIVER

LOW SIDE

0

L

R

T

C

D

www.analog.com

18

17

1

R

R

E

Σ∆

MODULATOR

Ø1 Ø2

49

2

O

R

N

R

O

E

M

PGA

MODE CONTROL LOGIC

19

29

30

0

E

N

R

T

D

R

U

W

E

M

P

/

T

S

R

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

PVDD2

PGND2

PVDD2

PGND2

2

1

L

L

R

R

T

T

C

C

D

D

41,42

PVDD2

43,44,45

OUTR+

46,47,48

PGND2

39,40

PVDD2

36,37,38

OUTR-

33,34,35

PGND2

AD199x Preliminary Technical Data

TABLE OF CONTENTS

General Description ........................................................................ 1

AD199x—Specifications.................................................................. 3

test conditions unless otherwise noted...................................... 3

Absolute Maximum Ratings............................................................ 6

Pin Configurations And Functional Descriptions....................... 7

Typical Performance Characteristics ............................................. 8

Functional Description.................................................................. 10

Device Architecture ................................................................... 10

Amplifier Gain............................................................................ 10

System Design............................................................................. 11

Outline Dimensions....................................................................... 14

ESD Caution................................................................................ 14

Rev. PrA – 1/20/05 | Page 2 of 16

Preliminary Technical Data AD199x

AD199X—SPECIFICATIONS

TEST CONDITIONS UNLESS OTHERWISE NOTED

Supply Voltages

AV

5 V

DD

DV

5 V

DD

PV

12 V

DDX

Ambient Temperature 25 °C

Load Impedance 6 Ω

Clock Frequency 11.2896 MHz

Measurement Bandwidth 20 Hz to 20 KHz

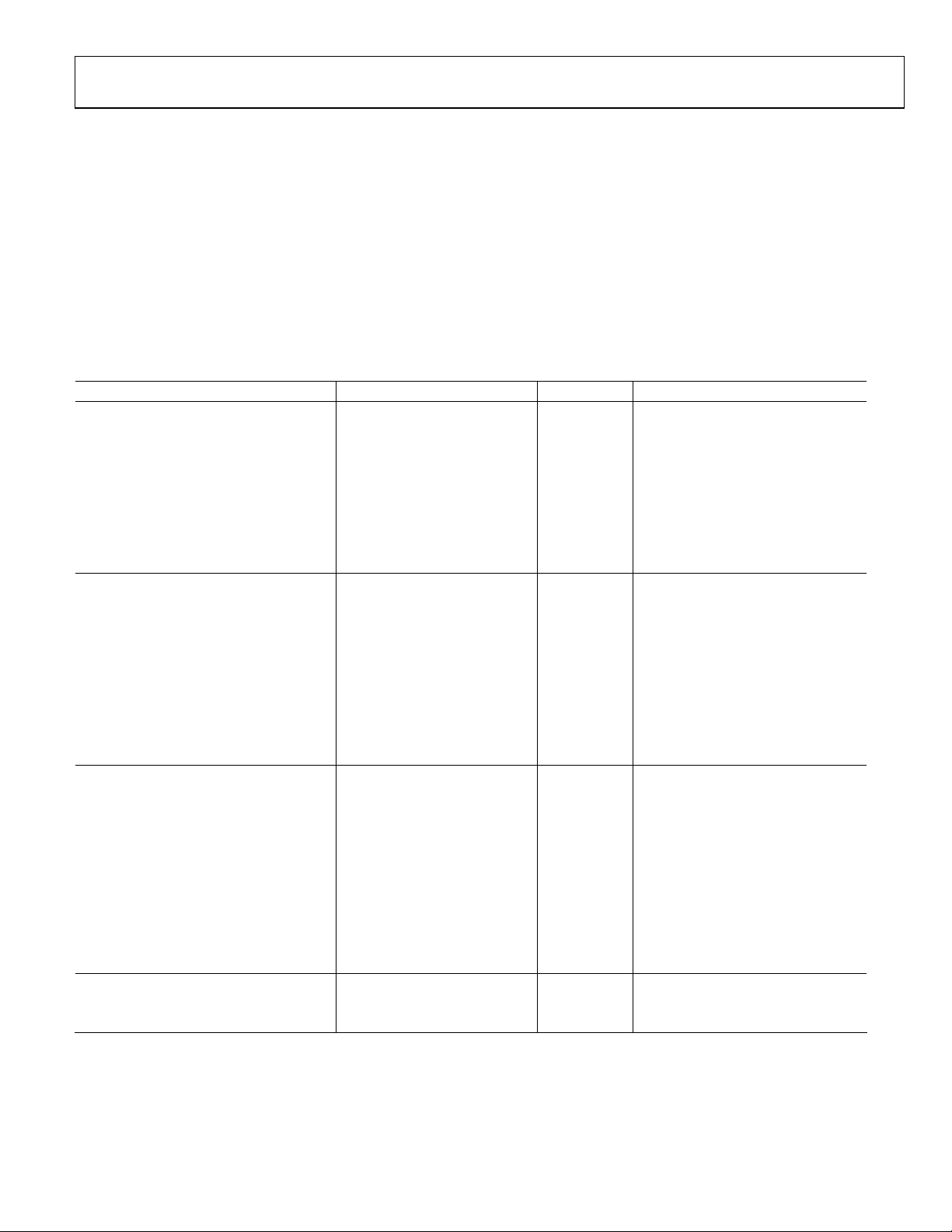

Table 1. Performance of both channels is identical

Parameter Min Typ Max Units Test Conditions/Comments

OUTPUT POWER (PO)

AD1990

AD1992

AD1994

AD1996

Efficiency 84 %

RON

per High Side Transistor

per Low Side Transistor

Maximum Current Through OUTx 4 A

Thermal Warning Active 135 °C Die temperature

Thermal Shutdown Active 150 °C Die temperature

Overcurrent Shutdown Active 4 A

Nominal Input Level 1.0 V

Modulation Factor 90 %

PERFORMANCE SPECIFICATIONS

Total Harmonic Distortion (THD+N) 0.005 % PGA = 0 dB, PO = 5 W

0.007 % PGA = 6 dB, PO = 5 W

0.01 % PGA = 12 dB, PO = 5 W

0.02 % PGA = 18 dB, PO = 5 W

Signal/Noise Ratio (SNR) 102 dB

Dynamic Range (DNR) 102 dB -60 dB Input

Crosstalk

Power supply rejection (PSRR)

60

45

DC SPECIFICATIONS

Input Impedance 20

Output DC Offset Voltage ±10 mV

4

5

8

10

16

25

25

40

-100

0.3

0.2

R

= 6Ω, PVDD = 20 V, 1 kHz (FTC)

W

W

W

W

W

W

W

W

Ω

Ω

PGA gain = 0 dB

RMS

dB

dB

dB

kΩ

L

@ <0.01% THD+N

@ 10% THD+N (FTC)

@ <0.01% THD+N

@ 10% THD+N (FTC)

@ <0.01% THD+N

@ 10% THD+N (FTC)

@ <0.01% THD+N

@ 10% THD+N (FTC)

f

=1 kHz, PO = 5 W, RL = 6Ω

IN

@ 1 A

@ 1 A

Measured channel input = 0 V

other channel = 1 kHz at 5W

20 Hz - 1 kHz

20 Hz – 20 kHz

AINL and AINR analog inputs

RMS

,

Rev. PrA – 1/20/05 | Page 3 of 16

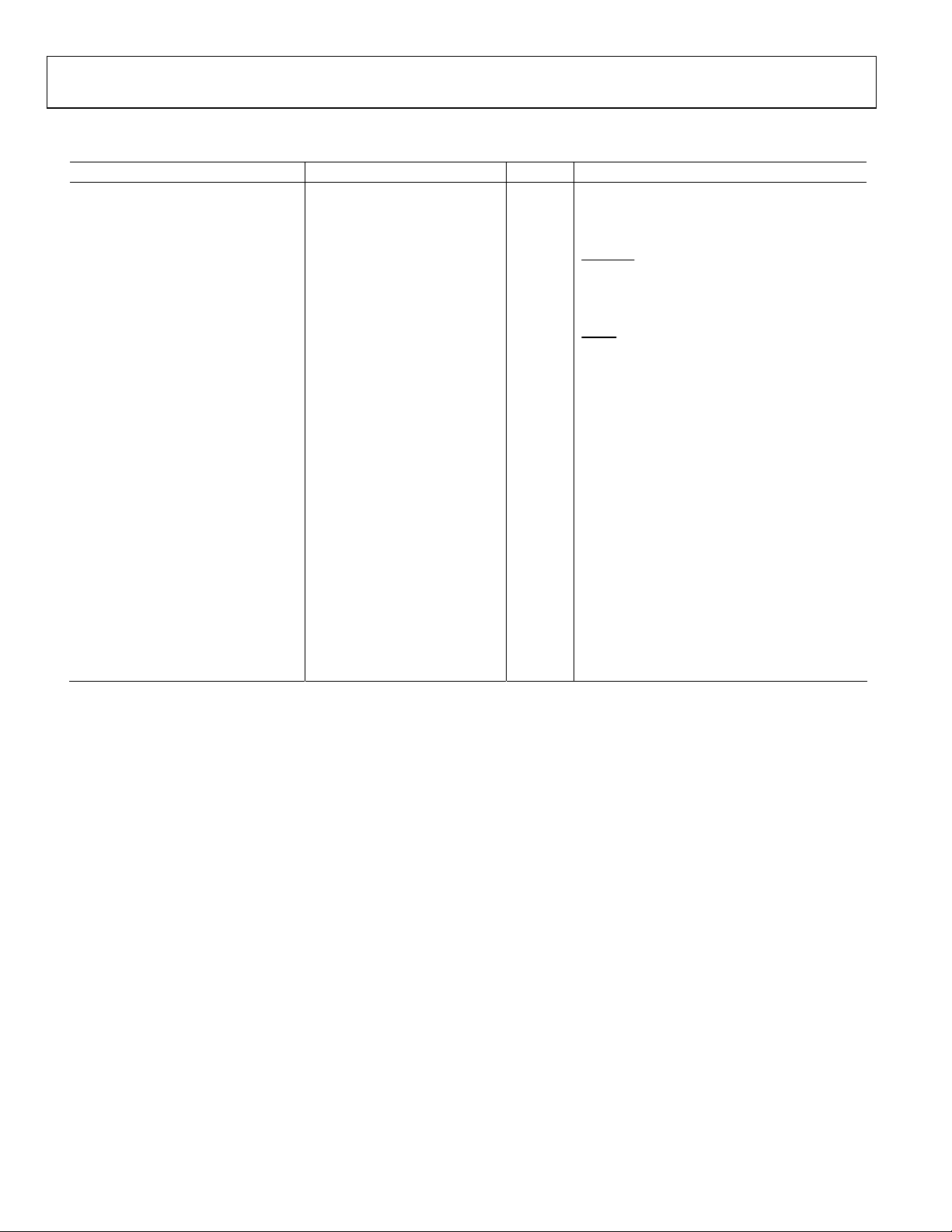

AD199x Preliminary Technical Data

Parameter Min Typ Max Units Test Conditions/Comments

POWER SUPPLIES

Supply Voltage AVDD 4.5 5 5.5 V

Supply Voltage DVDD 4.5 5 5.5 V

Supply Voltage PV

Powerdown Current

AVDD 0.1 0.5 µA

DVDD 0.1 0.5 µA

PV

19 25 µA

DDX

Mute Current

AVDD 19 mA

DVDD 2.7 mA

PVDD 1.5 mA

Quiesent Current Inputs Grounded, Non-Overlap Time = TBD

AVDD 20 mA

DVDD 5.2 mA

PV

3.2 mA

DDX

Operating Current VIN = 1V

AVDD 22 mA

DVDD 5.8 mA

PVDD 4 A per FET

DIGITAL I/O

Input Voltage High 2.0 DVDD V

Input Voltage Low 0.8 V

Output Voltage High DVDD-0.8 V @ 2 mA

Output Voltage Low 0.4 V @ 2 mA

Leakage Current on Digital Inputs 10 µA

6.5 8-20 22.5 V

DDX

RST/PDN

MUTE

held low

held low

, PO = 5 W

RMS

Rev. PrA – 1/20/05 | Page 4 of 16

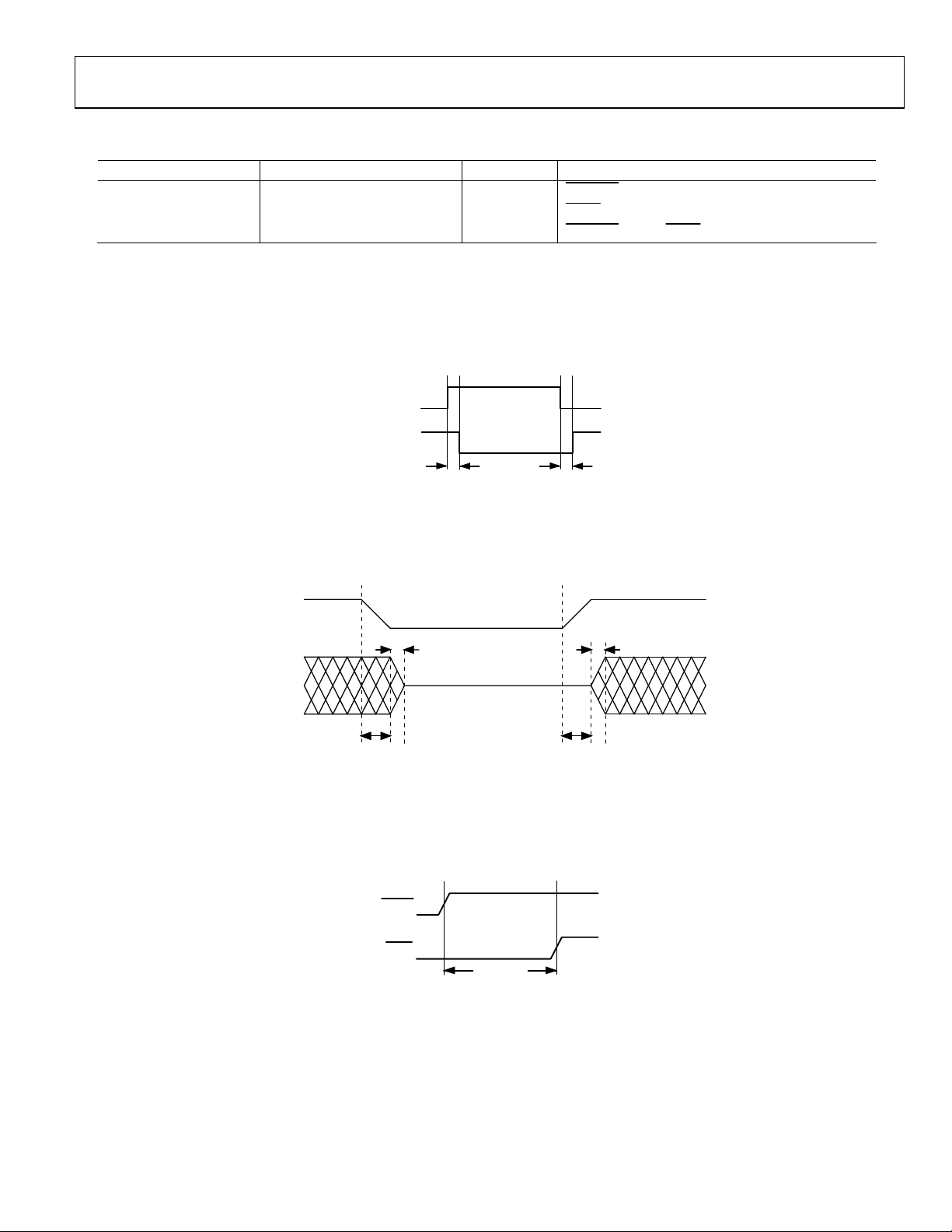

Preliminary Technical Data AD199x

Table 2 DIGITAL TIMING (Guaranteed over -40°C to +85°C, AV

= Shortest, See Table 6: Non-Overlap Time Settings)

t

NOL

Parameter Min Typ Max Units Comments

t

500 ns

PDRP

t

MPDL

t

1 sec

MUTEDLY

5 µs

OUTL+/

OUTR+

OUTL-/

OUTR-

= DVDD = 5.0V ± 10%, PV

DD

RST/PDN

MUTE

asserted to output initial response

RST/PDN

=12V ± 10%, Non Overlap Time

DDX

minimum low pulsewidth

high to

MUTE

high delay

MUTE

OUTX

t

MPDL

t

PST

RESET

t

NOL

Figure 2. Output Timing

Figure 3. Mute Ti ming

t

NOL

t

MPDL

t

PST

MUTE

t

MUTEDLY

Figure 4. Reset to Mute Delay

Rev. PrA – 1/20/05 | Page 5 of 16

Loading...

Loading...