High Definition Audio

ADC0

ADC1

DAC2

PORT D

PORT F

PORT G

MONO OUT

AD1882

H

D

A

U

D

I

O

I

N

T

E

R

F

A

C

E

PORT A

PORT C

DAC0

HP

HP

⌺

⌺

⌺

⌺

⌺

DAC1

PCBEEP

CD IN

⌺

⌺

PORT E

PORT B

⌺

DIGITAL

BEEP

www.BDTIC.com/ADI

SoundMAX Codec

AD1882

FEATURES

2 stereo headphone amplifiers

Microsoft Vista Premium logo for notebook and desktop

95 dB audio outputs, 90 dB audio inputs

Internal 32-bit arithmetic for greater accuracy

Impedance and presence detection on all jack pins

Digital synthesis PCBeep

C/LFE channel swapping

2 general-purpose digital I/O (GPIO) pins

Advanced power management modes

EAPD control for internal speakers

48-lead, Pb-free LFCSP_VQ package

SIX 96 kHz DACs

3 independent stereo DAC pairs

Independent 8 kHz, 11.025 kHz, 16 kHz, 22.05 kHz, 32 kHz,

44.1 kHz, 48 kHz, 88.2 kHz, and 96 kHz sample rates

16-, 20-, and 24-bit PCM resolution

Selectable stereo mixer on outputs

FOUR 96 kHz ADCs

2 independent stereo ADC pairs

Simultaneous record of up to 4 channels

Independent 8 kHz, 11.025 kHz, 16 kHz, 22.05 kHz, 32 kHz,

44.1 kHz, 48 kHz, 88.2 kHz, and 96 kHz sample rates

16-, 20-, and 24-bit resolution

S/PDIF OUTPUT

Supports 44.1 kHz, 48, kHz 88.2 kHz, and 96 kHz sample rates

16-, 20-, and 24-bit data widths; PCM and AC3 formats

Digital PCM gain control

DEDICATED AUXILIARY PINS

Stereo CD input w/GND sense

Mono out pin for internal speakers or telephony

Analog PCBeep input pin

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

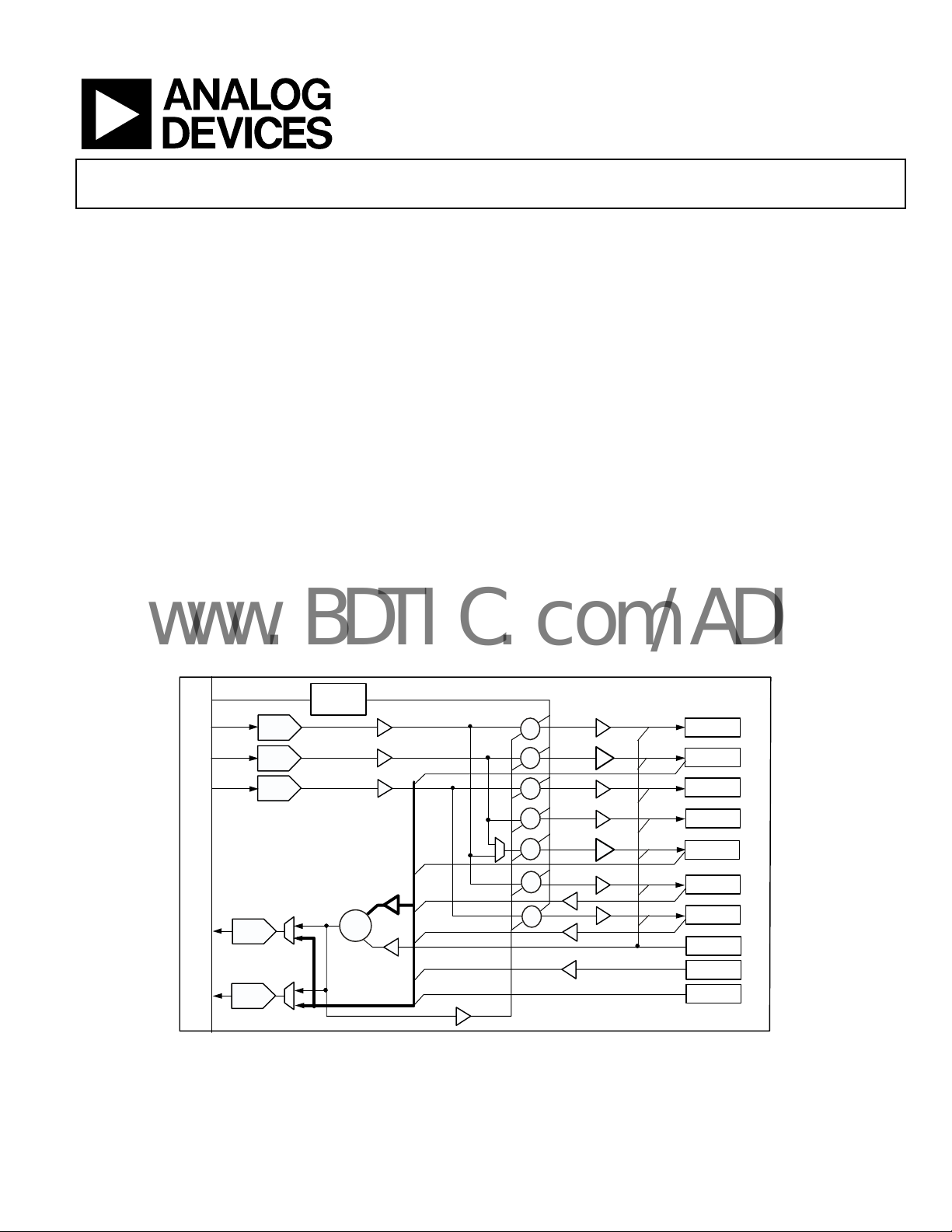

Figure 1. AD1882 Block Diagram

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel:781.329.4700 www.analog.com

Fax:781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

AD1882

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features ................................................................. 1

Revision History ...................................................... 2

General Description ................................................. 3

Additional Information .......................................... 3

Jack Configuration ................................................ 3

Specifications .......................................................... 4

Test Conditions .................................................... 4

Performance ........................................................ 4

General Specifications ............................................ 4

HD Audio Link Specifications .................................. 6

Power-Down States ............................................... 6

Absolute Maximum Ratings .................................... 7

ESD Caution ........................................................ 7

Environmental Conditions ...................................... 7

Pin Configuration and Function Descriptions ................. 8

HD Audio Widgets ................................................ 11

HD Audio Parameters ............................................. 12

Outline Dimensions ............................................... 16

Ordering Guide ..................................................... 16

REVISION HISTORY

4/08—Rev. 0 to Rev. A

Changed analog and digital power supply specifications......6

Changed analog and digital specifications and revised footnotes

in Power-Down States ............................................... 6

Changed revision ID in Widget Parameters .................. 13

Rev. A | Page 2 of 16 | April 2008

GENERAL DESCRIPTION

www.BDTIC.com/ADI

AD1882

The AD1882 audio codec and SoundMAX® software provides

superior HD audio quality that exceeds Vista Premium performance. The AD1882 has six DACs and four ADCs, two stereo

headphone ports, C/LFE swapping, digital and analog PCBeep,

and S/PDIF output, making the AD1882 the right choice for

desktop PCs where performance is the primary consideration.

The jack retasking feature on this product supports various configurations including platforms for 5.1 on 5 or 3 jacks, and front

panel jack retasking.

The AD1882 is available in a 48-lead RoHS compliant lead

frame chip scale package in both reels and trays. See Ordering

Guide on Page 16.

ADDITIONAL INFORMATION

This data sheet provides a general overview of the AD1882

SoundMAX codec’s architecture and functionality. Additional

information on the AD1882 is available in the AD1882 Programmers Reference Manual. Please contact your local Analog

Devices, Inc., sales representative for more information. For

information on SoundMAX codecs and software, see Analog

Devices website at www.analog.com/soundMAX.

JACK CONFIGURATION

The guidelines shown in Table 1 through Table 3 should be

used when selecting ports for particular functions.

Table 2. Typical Desktop Configuration with 5.1 on 3 Jacks

Port Function

Port A Front Panel Headphone

Port B Front Panel Microphone

Port C Rear Panel Line-In/Surround

Port D Rear Panel Line-Out/Headphone

Port E Rear Panel Microphone / C/LFE

Table 3. Typical Notebook Configuration

Port Function

Port A Headphone

Port B Microphone

Port C Internal Microphone

Port D Internal Stereo Speakers

Port E Docking Station Line-In/Microphone

Table 1. Typical Desktop Configuration with Discreet Jacks

Port Function

Port A Front Panel Headphone

Port B Front Panel Microphone

Port C Rear Panel Line-In

Port D Rear Panel Line-Out/Headphone

Port E Rear Panel Microphone

Port F Rear Panel Surround

Port G Rear Panel C/LFE

Rev. A | Page 3 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

SPECIFICATIONS

TEST CONDITIONS

Parameter Test Condition

Tem pe ra tu re

Digital Supply

Analog Supply

MIC_BIAS_IN (via Low-Pass Filter)

Sample Rate f

Input Signal (Frequency Sine Wave)

Amplitude for THD + N

Analog Output Pass Band

DAC 10 kΩ Output Load: Line Out Tests

ADC 0 dB Gain

S

PERFORMANCE

Parameter Min Typ Max Unit

Line-Out Drive (10 kΩ Loads—DAC to Pin)

Total Harmonic Distortion (THD + N)

Dynamic Range (–60 dB in Ref to fS A-Weighted)

Signal-to-Noise Ratio

Headphone Drive (32 Ω Loads—DAC to Pin)

Total Harmonic Distortion (THD + N)

Dynamic Range (–60 dB in Ref to f

Signal-to-Noise Ratio

Input Ports (Pin to ADC, Mic Boost = 0 dB)

Total Harmonic Distortion (THD + N)

Dynamic Range (–60 dB in Ref to f

Signal-to-Noise Ratio

A-Weighted)

S

A-Weighted)

S

25°C

3.3 V

3.3 V

5.0 V

48 kHz

1008 Hz

–3.0 dB Full Scale

20 Hz to 20 kHz

32 Ω Output Load: Headphone Tests

–85

95

95

–83

95

95

–81

90

90

dB

dB

dB

dB

dB

dB

dB

dB

dB

GENERAL SPECIFICATIONS

Table 4. AD1882 General Specifications

Parameter Min Typ Max Unit

DIGITAL DECIMATION AND INTERPOLATION FILTERS—f

Pass Band 00.4 f

Pass-Band Ripple ±0.005 dB

Stop Band 0.6 f

Stop-Band Rejection dB

Group Delay +20 –100 1/f

Group Delay Variation Over Pass Band 0 μs

ANALOG-TO-DIGITAL CONVERTERS

Resolution 24 Bits

Gain Error (Full-Scale Span Relative to Nominal Input Voltage)

Interchannel Gain Mismatch (Difference of Gain Errors) ±0.5 dB

ADC Offset Error

ADC Crosstalk

Line Inputs (Input L, Ground R, Read R; Input R, Ground L, Read L) –85 dB

Line Inputs to Other –100 –80 dB

1

1

= 8 kHz to 192 kHz

S

2

1

S

S

±10 %

±5mV

Hz

Hz

S

Rev. A | Page 4 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

Table 4. AD1882 General Specifications (Continued)

Parameter Min Typ Max Unit

DIGITAL TO ANALOG CONVERTERS

Resolution 24 Bits

Gain Error (Full-Scale Span Relative to Nominal Input Voltage)

Interchannel Gain Mismatch (Difference of Gain Errors) ±0.5 dB

Total Audible Out-of-Band Energy (Measured from 0.6 × f

DAC Crosstalk (Input L, Zero R, Read R_OUT; Input R, Zero L, Read L_OUT)

DAC VOLUMES

Step Size (DAC-0, DAC-1, DAC-2) 1.5 dB

Output Gain/Attenuation Range –58.5 0 dB

Mute Attenuation of 0 dB Fundamental

1

ADC VOLUMES

Step Size (ADCSEL-0, ADCSEL-1) 1.5 dB

PGA Gain/Attenuation Range –58.5 +22.5 dB

Mute Attenuation of 0 dB Fundamental

1

ANALOG MIXER

Signal-to-Noise Ratio (SNR) Input to Output

CD to Port D Output

Port B, C, or E to Port D Output

Port A to Port D Output

Port D to Port A Output

Step Size: All Mixer Inputs 1.5 dB

Input Gain/Attenuation Range: All Mixer Inputs –34.5 +12.0 dB

ANALOG LINE LEVEL OUTPUTS

Full-Scale Output Voltage 1.0 1.0 V rms

Ports C, E, F, and G Mono Out 2.83 V p-p

Output Impedance

External Load Impedance

Output Capacitance

External Load Capacitance 1000 pF

ANALOG HP DRIVE OUTPUTS

Full-Scale Output Voltage 1.0 V rms

Ports A and D 2.83 V p-p

Output Impedance

External Load Impedance

Output Capacitance

External Load Capacitance

ANALOG INPUTS

CD, Port D (When Used as Input) 1

Microphone Boost Amplifier, Ports B, C, or E

Boost = 0 dB 1

(When Used as Inputs)

Boost = 10 dB 0.316

Boost = 20 dB 0.1

Boost = 30 dB 0.032

Input Impedance

Input Capacitance

1

1

1

to 100 kHz)

S

1

1

1

1

±10 %

1

1

–85 dB

–95 dB

–80 dB

–80 dB

95

95

95

95

95

1

10 kΩ

300 Ω

dB

dB

dB

dB

dB

15 pF

1

1

32 Ω

15 pF

0.5 Ω

1000 pF

V rms

2.83

V p-p

V rms

2.83

V p-p

V rms

0.894

V p-p

V rms

0.283

V p-p

V rms

0.089

V p-p

20 kΩ

57.5 pF

3

3

3

3

3

3

3

Rev. A | Page 5 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

Table 4. AD1882 General Specifications (Continued)

Parameter Min Typ Max Unit

Digital GPIO Pins: GPIO_0, GPIO_1/EAPD

Input Signal High (V

Input Signal Low (V

Input Leakage Current (Signal High, (I

Input Leakage Current (Signal Low, (I

Output Signal High (V

Output Signal Low (V

)DV

IH

)0DV

IL

)I

OH

)I

OL

) 150 nA

IH

)50μA

IL

= –500 μADV

OUT

= +1500 μA0DV

OUT

S/PDIF_OUT

Output Signal High (VOH)I

Output Signal Low (V

)I

OL

= –500 μADV

OUT

= +1500 μA0DV

OUT

Power Supply

Analog (AVDD) 3.3 V ± 5%

Power Supply Range

Power Dissipation

Supply Current

Digital (DVDD) 3.3 V ± 10%

Power Supply Range

Power Dissipation

Supply Current

Digital I/O (DV

) 3.3 V ± 10%

IO

Power Supply Range

Power Dissipation

Supply Current

Power Supply Rejection (100 mV p-p Signal @ 1 kHz)1 80 dB

1

Guaranteed but not tested.

2

Measurements reflect main ADC.

3

RMS values assume sine wave input.

× 0.60 DV

IO

× 0.72 DV

IO

× 0.72 DVIO V

IO

3.13 3.30

IO

× 0.24 V

IO

IO

× 0.10 V

IO

× 0.10 V

IO

3.46 V

116

35

2.97 3.30

3.63 V

162

49

2.97 3.30

3.63 V

3.96

1.20

V

V

mW

mA

mW

mA

mW

mA

HD AUDIO LINK SPECIFICATIONS

HD Audio signals comply with the High Definition Audio specifications. Please refer to these specifications at

www.intel.com/standards/hdaudio.

POWER-DOWN STATES

Table 5. Power-Down States

Parameter ID

Function Node In D0, All Nodes Active 49 35 mA

Function Node in D3 16 0.7 mA

Codec in RESET

Individual block power savings

DAC Pair Powered Down Saves (Each)

ADC Pair Powered Down Saves (Each)

Mixer Power Control (and Associated Amps) Saves

MIC_BIAS Powered Down Saves

1

Powering down the MIC_BIAS powers down all port MIC_BIAS pins. This disables all microphone bias circuits set to 100% or 50%, setting them to the high-Z state. The

0 Ω and high-Z states remain unaffected by the MIC_BIAS power state.

1

Typ IA

VDD

Typ Un it

VDD

33mA

6

5

0

0

6

4.4

3

1.0

mA

mA

mA

mA

Rev. A | Page 6 of 16 | April 2008

AD1882

ESD (electrostatic discharge) sensitive device.

Charged devices and circuit boards can discharge

without detection. Although this product features

patented or proprietary protection circuitry, damage

may occur on devices subjected to high energy ESD.

Therefore, proper ESD precautions should be taken to

avoid

performance degradation or loss of functionality.

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Stresses greater than those listed below may cause permanent

damage to the device. This is a stress rating only; functional

operation of the device at these or any other conditions above

those indicated in the operational section of this specification is

not implied. Exposure to absolute maximum rating conditions

for extended periods may affect device reliability.

Power Supplies Rating

Digital (DV

Digital I/O (DV

Analog (AV

Input Current (Except Supply Pins) ±10.0 mA

Analog Input Voltage (Signal Pins) –0.30 V to AVDD + 0.3 V

Digital Input Voltage (Signal Pins) –0.30 V to DV

Ambient Temperature (Operating) 0°C to +70°C

Storage Temperature –65°C to +150°C

) –0.30 V to +3.65 V

DD

) –0.30 V to +3.65 V

IO

) –0.30 V to +3.65 V

DD

+ 0.3 V

IO

ESD CAUTION

ENVIRONMENTAL CONDITIONS

Ambient Temperature Rating:

T

= T

AMB

T

CASE

PD = power dissipation in W

= thermal resistance (case-to-ambient)

θ

CA

θ

= thermal resistance (junction-to-ambient)

JA

θ

= thermal resistance (junction-to-case)

JC

All measurements per EIA-JESD51 with 2S2P test board per

EIA-JESD51-7.

Package θ

LFCSP_VQ 47 15 32 °C/W

– (PD × θCA)

CASE

= case temperature in °C

JA

θ

JC

θ

CA

Unit

Rev. A | Page 7 of 16 | April 2008

AD1882

1

2

3

4

5

6

7

8

9

10

11

12

242313 14 15 16 17 18 19 20 21 22

34

33

36

35

25

26

27

28

29

30

31

32

44 434748 4546 373839404142

AD1882JCPZ

TOP VIEW

(NotToScale)

DV

CORE

GPIO_0

DV

I/O

DV

SS

SDATA_OUT

BIT_CLK

DV

SS

SDATA_IN

DV

DD

SYNC

RESET

PCBEEP

PORT-D_R

PORT-D_L

P

O

R

T

-

C

_

R

P

O

R

T

-

C

_

L

P

O

R

T

-

B

_

R

P

O

R

T

-

E

_

L

P

O

R

T

-

F

_

R

P

O

R

T

-

F

_

L

P

O

R

T

-

B

_

L

P

O

R

T

-

E

_

R

C

D

_

L

C

D

_

R

C

D

_

G

N

D

S

E

N

S

E

_

A

/

S

R

C

_

B

SENSE_B/SRC_A

P

O

R

T

-

A

_

L

M

O

N

O

_

O

U

T

G

P

I

O

_

1

/E

A

P

D

P

O

R

T

-

G

_

R

A

V

D

D

P

O

R

T

-

G

_

L

P

O

R

T

-

A

_

R

A

V

S

S

S

P

D

I

F

_

O

U

T

MIC_BIAS_IN

MIC_BIAS-B

MIC_BIAS-C

MIC_BIAS-E

AV

DD

AV

SS

VREF_FLT

RESERVED (NC)

RESERVED(NC)

R

E

S

E

R

V

E

D

(

N

C

)

R

E

S

E

R

V

E

D

(

N

C

)

R

E

S

E

R

V

E

D

(

N

C

)

www.BDTIC.com/ADI

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. AD1882 48-Lead Package and Pinout

Rev. A | Page 8 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

Table 6. AD1882 Pin Descriptions

Mnemonic Pin No. Function Description

DIGITAL INTERFACE

SDATA_OUT

BIT_CLK

SDATA_IN

SYNC

RESET

DIGITAL I/O

GPIO_0

GPIO_1/EAPD

SPDIF_OUT

JACK SENSE AND EAPD

SENSE_A/SRC_B

SENSE_B/SRC_A

ANALOG I/O

PCBEEP

PORT-E_L

PORT-E_R

PORT-F_L

PORT-F_R

CD_L

CD_GND

CD_R

PORT-B_L

PORT-B_R

PORT-C_L

PORT-C_R

PORT-D_L

PORT-D_R

PORT-A_L

MONO_OUT

PORT-A_R

PORT-G_L

PORT-G_R

FILTER/REFERENCE

MIC_BIAS-B

MIC_BIAS-C

MIC_BIAS-E

DV

CORE

VREF_FLT 27 O Voltage Reference Filter. This pin must be connected to filter caps: 1.0 μF and 0.1μF

The symbols used in this table are defined as: I = Input, O = Output, LI = Line level input, LO = Line level output, HP = Output capable of

driving headphone load, MIC = Input supports microphones with MIC bias and boost amplifier, SWAP = Outputs can swap L/R channels

(typically used to support C/LFE or shared C/LFE function).

5

6

8

10

11

2

47

48

13

34

12

14

15

16

17

18

19

20

21

22

23

24

35

36

39

40

41

43

44

28

29

31

1 O CAUTION: DO NOT APPLY 3.3 V TO THIS PIN!

I

I

I/O

I

I

I/O

I/O

O

I/O

I/O

LI

LI, MIC, LO, SWAP

LI, MIC, LO, SWAP

I/O

I/O

LI

LI

LI

LI, MIC, HP, LO

LI, MIC, HP, LO

LI, MIC, LO

LI, MIC, LO

LI, HP, LO

LI, HP, LO

LI, MIC, HP, LO

LO

LI, MIC, HP, LO

LO, SWAP

LO, SWAP

O

O

O

Link Serial Data Output. AD1882 input stream. Clocked on both edges of the

BIT_CLK.

Link Bit Clock. 24.000 MHz serial data clock.

Link Serial Data Input. AD1882 output stream Clocked only on one edge of BIT_CLK.

Link Frame Sync.

Link Reset. AD1882 master hardware reset

General-Purpose Input/Output Pin. Digital signal used to control external circuitry.

General-Purpose Input/Output Pin/EAPD Pin. Digital signal used to control external

circuitry. Defaults to high-Z. When used as EAPD: high-Z = amp-on, DV

S/PDIF_OUT. Supports S/PDIF output.

JACK SENSE A-D Input/Sense B Drive.

JACK SENSE E-H Input/Sense A Drive.

Monaural Input from System for Analog PCBeep.

Auxiliary Input/Output Left Channel.

Auxiliary Input/Output Right Channel.

Auxiliary Input/Output Left Channel.

Auxiliary Input/Output Right Channel.

CD Audio Left Channel.

CD Audio Analog Ground Reference (for Differential CD Input). Must be connected to

AGND via 0.1 mF capacitor if not in use as CD_GND.

CD Audio Right Channel.

Front Panel Stereo MIC/Line-In.

Front Panel Stereo MIC/Line-In.

Rear Panel Stereo MIC/Line-In.

Rear Panel Stereo MIC/Line-In.

Rear Panel Headphone/Line-Out.

Rear Panel Headphone/Line-Out.

Front Panel Headphone/Line-Out.

Monaural Output to Internal Speaker or Telephony Subsystem Speakerphone.

Front Panel Headphone/Line-Out.

Rear Panel C/LFE Output.

Rear Panel C/LFE Output.

Switchable Microphone Bias. For use with Port B (Pins 21, 22).

Switchable Microphone Bias. For use with Port C (Pins 23, 24).

Switchable Microphone Bias. For use with Port E (Pins 14, 15).

Filter connection for internal core voltage regulator.

This pin must be connected to filter caps: 10 μF, 1.0 μF, and 0.1 μF connected in

parallel between Pin 1 and DV

connected in parallel between Pin 27 and AV

(Pin 4).

SS

(Pins 26, 42).

SS

= amp off.

SS

Rev. A | Page 9 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

Table 6. AD1882 Pin Descriptions (Continued)

Mnemonic Pin No. Function Description

POWER AND GROUND

(3.3V) 3 I Connect to the I/O Voltage Used for the HD Audio Controller Signals.

DV

I/O

DV

SS

(3.3 V) 9 I Digital Supply Voltage 3.3 V. This is regulated down to DV

DV

DD

(3.3 V) 25, 38 I CAUTION: DO NOT APPLY 5.0 V TO THESE PINS!

AV

DD

MIC_BIAS_IN 33 I Source Power for Microphone Bias Boost Circuitry.

AV

SS

The symbols used in this table are defined as: I = Input, O = Output, LI = Line level input, LO = Line level output, HP = Output capable of

driving headphone load, MIC = Input supports microphones with MIC bias and boost amplifier, SWAP = Outputs can swap L/R channels

(typically used to support C/LFE or shared C/LFE function).

4, 7 I Digital Supply Return (Ground).

on Pin 1 to supply the

internal digital core internal to the AD1882.

Analog supply voltage 3.3 V ONLY.

Note: AV

audio performance.

26, 42 I Analog Supply Return (Ground). AVSS should be connected to DVSS using a

conductive trace under, or close to, the AD1882.

supplies should be well regulated and filtered as supply noise degrades

DD

CORE

Rev. A | Page 10 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

HD AUDIO WIDGETS

In the following table, node IDs that are not shown are reserved

for future use.

Table 7. HD Audio Widgets

Node ID Name Type ID Type Description

00 ROOT x Root Device identification

01 FUNCTION x Function Designates this device as an audio codec

02 S/PDIF DAC 0 Audio Output S/PDIF digital stream output interface

03 DAC_0 0 Audio Output Headphone/surround side (7.1) channel digital/audio converters

04 DAC_1 0 Audio Output Stereo front channel digital/audio converters

05 DAC_2 0 Audio Output Stereo C/LFE channel digital/audio converters

08 ADC_0 1 Audio Input Stereo record channel 1 audio/digital converters

09 ADC_1 1 Audio Input Stereo record channel 2 audio/digital converters

0B S/PDIF Mix Selector 3 Audio Selector Selects which ADC drives the S/PDIF mixer

0C ADC Selector 0 3 Audio Selector Selects and amplifies/attenuates the input to ADC_0

0D ADC Selector 1 3 Audio Selector Selects and amplifies/attenuates the input to ADC_1

10 Digital Beep 7 Beep Generator Internal digital PCBeep signal

11 Port A (Headphone) 4 Pin Complex Front panel headphone/microphone jack

12 Port D (Front L/R) 4 Pin Complex Rear panel front/headphone jack

13 Mono Out 4 Pin Complex Monorail output pin (internal speakers or telephony system)

14 Port B (Front Mic) 4 Pin Complex Front panel microphone/headphone jack

15 Port C (Line In) 4 Pin Complex Rear panel line-in jack

16 Port F (Surr Back) 4 Pin Complex Rear panel surround-rear (5.1) jack

17 Port E (Rear Mic) 4 Pin Complex Rear panel mic jack

18 CD In 4 Pin Complex Analog CD input

19 Mixer Power-Down 5 Power Widget Powers down the analog mixer and associated amps

1A Analog PCBeep 4 Pin Complex External analog PCBeep signal input

1B S/PDIF Out 4 Pin Complex S/PDIF output pin

1D S/PDIF Mixer 2 Audio Mixer Mixes the selected ADC with the digital stream to drive S/PDIF out

1E Mono Out Mixer 2 Audio Mixer Selects which source drives the mono out signal

20 Analog Mixer 2 Audio Mixer Mixes individually gainable analog inputs

21 Mixer Output Atten 3 Audio Selector Attenuates the mixer output to drive the Port mixers

22 Port A Mixer 2 Audio Mixer Mixes the Port A selected DAC and mixer output amps to drive Port A

23 VREF Power-Down F Vendor Defined Powers down the internal and external VREF circuitry

24 Port G (C/LFE) 4 Pin Complex Rear panel C/LFE jack

26 Port E Mixer 2 Audio Mixer Mixes DAC_1 and mixer output amps to drive Port E

27 Port G Mixer 2 Audio Mixer Mixes DAC_1 and mixer output amps to drive Port G

29 Port D Mixer 2 Audio Mixer Mixes DAC_0 and mixer output amps to drive Port D

2A Port F Mixer 2 Audio Mixer Mixes DAC_2 and mixer output amps to drive Port F

2C Port C Mixer 2 Audio Mixer Mixes the Port C selected DAC and mixer output amps to drive Port C

2D Stereo Mix Down 2 Audio Mixer Mixes the stereo L/R channels to drive mono output

2F BIAS Power-Down F Vendor Defined Powers down the internal MIC_BIAS_FILT and all MIC_BIAS pins

37 Port A Out Selector 3 Audio Selector Selects the Port A DAC (0, 1)

39 Port B Boost 3 Audio Selector Microphone boost amp for Port B

3A Port C Boost 3 Audio Selector Microphone boost amp for Port C

3C Port E Boost 3 Audio Selector Microphone boost amp for Port E

Rev. A | Page 11 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

HD AUDIO PARAMETERS

The SSID value is set on codec power-up only. SSID is not reset

by link or soft reset in order to preserve modifications by BIOS

control.

Table 8. Root and Function Node Parameters

Sub Node

Vendor ID

Node ID Name

00 ROOT 0x11D4 1882 0x0010 0300 0x0001 0001

01 FUNCTION 0x0002 003B 0x0000 0001 0x0001 0C0C 0x4000 0002

1

Subject to change with silicon stepping.

Table 9. Subsystem ID

Node ID Name Type Value

0x01 FUNCTION Function 0xBFD2 0000 0xBFD2 0x00 0x00

1

The default SSID is over-written by platform BIOS after power on. It is preserved across HD Audio link reset and verb reset.

00 01

1

Revision ID

1

02

03

Count

04

31:16

SSID

Func. Group

Typ e

05

15:8

SKU

Audio F.G.

Caps

08

7:0

ASM ID

GPIO Caps

11

Rev. A | Page 12 of 16 | April 2008

Table 10. Widget Parameters

www.BDTIC.com/ADI

AD1882

Output

Widget

Capabilities 09PCM Size,

Node ID

01 00000480 000E01FF 00000001 80000000 00000009 00052727

02 0003031D 000E01E0 00000005 00000001 80052727

03 00000405 000E01FF 00000001 00000000 00000009 00052727

04 00000405 000E01FF 00000001 00000000 00000009 00052727

05 00000405 000E01FF 00000001 00000000 00000009 00052727

08 00100501 000E01FF 00000001 00000001 00000009

09 00100501 000E01FF 00000001 00000001 00000009

0B 00300301 00000002

0C 0030010D 00000008 80053627

0D 0030010D 00000008 80053627

10 0070000C 00000000 800B0F0F

11 0040018D 0000373F 00000001 80000000

12 0040058D 0001003F 00000001 00000009 80000000

13 0040050C 00010010 00000001 00000009 80051F1F

14 00400081 00003727 00000000

15 0040018D 00003737 00000001 80000000

16 0040018D 00000017 00000001 80000000

17 0040098D 00003737 00000001 80000000

18 00400001 00000020 00000000

19 00500500 00000002 00000009

1A 00400000 00000020 00000000

1B 00400301 00000010 00000001

1D 00200303 80000000 00000002

1E 00200103 80000000 00000002

1F 00F00100 00000010 00000001

20 0020010B 80051F17 00000008

21 0030010D 00000001 80051F1F

22 00200103 80000000 00000002

23 00F00100 00000008

24 0040098D 00000017 00000001 80000000

26 00200103 80000000 00000002

27 00200103 80000000 00000002

29 00200103 80000000 00000002

2A 00200103 80000000 00000002

2C 00200103 80000000 00000002

2D 00200100 00000001

2F 00F00100 00000003

37 00300101 00000002

39 0030010D 00000001 00270300

3A 0030010D 00000001 00270300

3C 0030010D 00000001 00270300

Rate 0A

Stream

Formats

0B

Pin

Capabilities

0C

Input Amp

Capabilities

0D

ConnList

Length

0E

Power

States

0F

Processing

Caps

10

Amp

Capabilities

12

Volume

Knob

Capabilities

13

Rev. A | Page 13 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

Table 11. Connection List

Node IDConnections01234567

[0–3] [4–7] NID I NID I NID I NID I NID I NID I NID I NID

02 0000001D 1D

03

04

05

08 0000000C 0C

09 0000000D 0D

0B 00000908 08 09

0C 18BC3911 20123B3B 11 39 1 3C 18 3B 3B 12 20

0D 18BC3911 20123B3B 11 39 1 3C 18 3B 3B 12 20

10

11 00000022 22

12 00000029 29

13 0000002D 2D

14

15 0000002C 2C

16 0000002A 2A

17 00000026 26

18

19 00002120 20 21

1A

1B 00000002 02

1D 00000B01 01 0B

1E 00002104 04 21

1F 00000002 02

20 12113A39 1A183B3C 39 3A 11 12 3C 3B 18 1A

21 00000020 20

22 00002137 37 21

23 A2209811 BC30AE24 11 1 18 20 1 22 24 1 2E 30 1 3C

24 00000027 27

26 00002105 05 21

27 00002105 05 21

29 00002104 04 21

2A 00002106 03 21

2C 00002131 03 21

2D 0000001E 1E

2F 00171514 14 15 17

37 00000403 03 04

39 00000014 14

3A 00000015 15

3C 00000017 17

Rev. A | Page 14 of 16 | April 2008

AD1882

www.BDTIC.com/ADI

In Table 12, default configuration values are set on codec

power-up only. Default configuration values are not reset by

link or soft reset to preserve modifications by BIOS control.

Table 12. Default Configuration Bytes

31:30 29:28 27:24 23:20 19:16 15:12 8 7:4 3:0

Location

Connectivity

Port A (Headphone) 0221401F Jack External Front HP Out 1/8” Jack Green 0 1 F

Port D (Front L/R) 01014010 Jack External Rear Line Out 1/8” Jack Green 0 1 0

Mono Out 901701F0 Fixed Internal N/A Speaker Other Analog Unknown 1 F 0

Port B (Front Mic) 02A190F0 Jack External Front Mic In 1/8” Jack Pink 0 F 0

Port C (Line In) 01813021 Jack External Rear Line In 1/8” Jack Blue 0 2 1

Port F (Surr Back) 01011012 Jack External Rear Line Out 1/8” Jack Black 0 1 2

Port E (Rear Mic) 01A19020 Jack External Rear Mic In 1/8” Jack Pink 0 2 0

CD IN 9933012E Fixed Internal Special 3 CD ATAPI Unknown 1 2 E

Analog PCBeep 90F701F0 Fixed Internal N/A Other Other Analog Unknown 1 F 0

S/PDIF Out 014511F0 Jack External Rear SPDIF Out Optical Black 1 F 0

Port G (C/LFE) 01016011 Jack External Rear Line Out 1/8” Jack Orange 0 1 1

Def. Device Conn Type Color

Misc.

JD Over

Ride

Def Assn SequenceName Value Chasis Position

Rev. A | Page 15 of 16 | April 2008

AD1882

PIN 1

INDICATOR

TOP

VIEW

6.75

BSC SQ

7.00

BSC SQ

1

48

12

13

37

36

24

25

5.25

5.10 SQ

4.95

0.50

0.40

0.30

0.30

0.23

0.18

0.50 BSC

12° MAX

0.20 REF

0.80 MAX

0.65 TYP

1.00

0.85

0.80

5.50

REF

0.05 MAX

0.02 NOM

0.60 MAX

0.60 MAX

PIN 1

INDICATOR

COPLANARITY

0.08

SEATING

PLANE

0.25 MIN

EXPOSED

PAD

(BOTTOM VIEW)

COMPLIANT TO JEDEC STANDARDS MO-220-VKKD-2

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

Dimensions are shown in millimeters.

Figure 3. 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

7 mm x 7 mm Body, Very Thin Quad

(CP-48-1)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD1882JCPZ

AD1882JCPZ-RL

1

Z = RoHS Compliant Part.

1

1

0°C to 70°C 48-Lead LFCSP_VQ CP-48-1

0°C to 70°C 48-Lead LFCSP_VQ, 13” Tape and Reel CP-48-1

©2008 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D06826-0-4/08(A)

Rev. A | Page 16 of 16 | April 2008

Loading...

Loading...