Complete Dual

a

FEATURES

Dual Serial Input, Voltage Output DACs

No External Components Required

Operates at 8 3 Oversampling per Channel

65 V to 612 V Operation

Cophased Outputs

115 dB Channel Separation

60.3% Interchannel Gain Matching

0.0017% THD+N

APPLICATIONS

Multichannel Audio Applications:

Compact Disc Players

Multivoice Keyboard Instruments

DAT Players and Recorders

Digital Mixing Consoles

Multimedia Workstations

PRODUCT DESCRIPTION

The AD1864 is a complete dual 18-bit DAC offering excellent

THD+N, while requiring no external components. Two complete signal channels are included. This results in cophased

voltage or current output signals and eliminates the need for

output demultiplexing circuitry. The monolithic AD1864 chip

includes CMOS logic elements, bipolar and MOS linear

elements and laser-trimmed thin-film resistor elements, all

fabricated on Analog Devices BiMOS II process.

The DACs on the AD1864 chip employ a partially-segmented

architecture. The first four MSBs of each DAC are segmented

into 15 elements. The 14 LSBs are produced using standard

R-2R techniques. Segment and R-2R resistors are lasertrimmed to provide extremely low total harmonic distortion.

This architecture minimizes errors at major code transitions

resulting in low output glitch and eliminating the need for an

external deglitcher. When used in the current output mode, the

AD1864 provides two cophased ± 1 mA output signals.

Each channel is equipped with a high performance output

amplifier. These amplifiers achieve fast settling and high slew

rate, producing ±3 V signals at load currents up to 8 mA. Each

output amplifier is short-circuit protected and can withstand

indefinite short circuits to ground.

The AD1864 was designed to balance two sets of opposing

requirements, channel separation and DAC matching. High

channel separation is the result of careful layout techniques. At

the same time, both channels of the AD1864 have been designed

to ensure matched gain and linearity as well as tracking over time

and temperature. This assures optimum performance when used in

stereo and multi-DAC per channel applications.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

18-Bit Audio DAC

AD1864

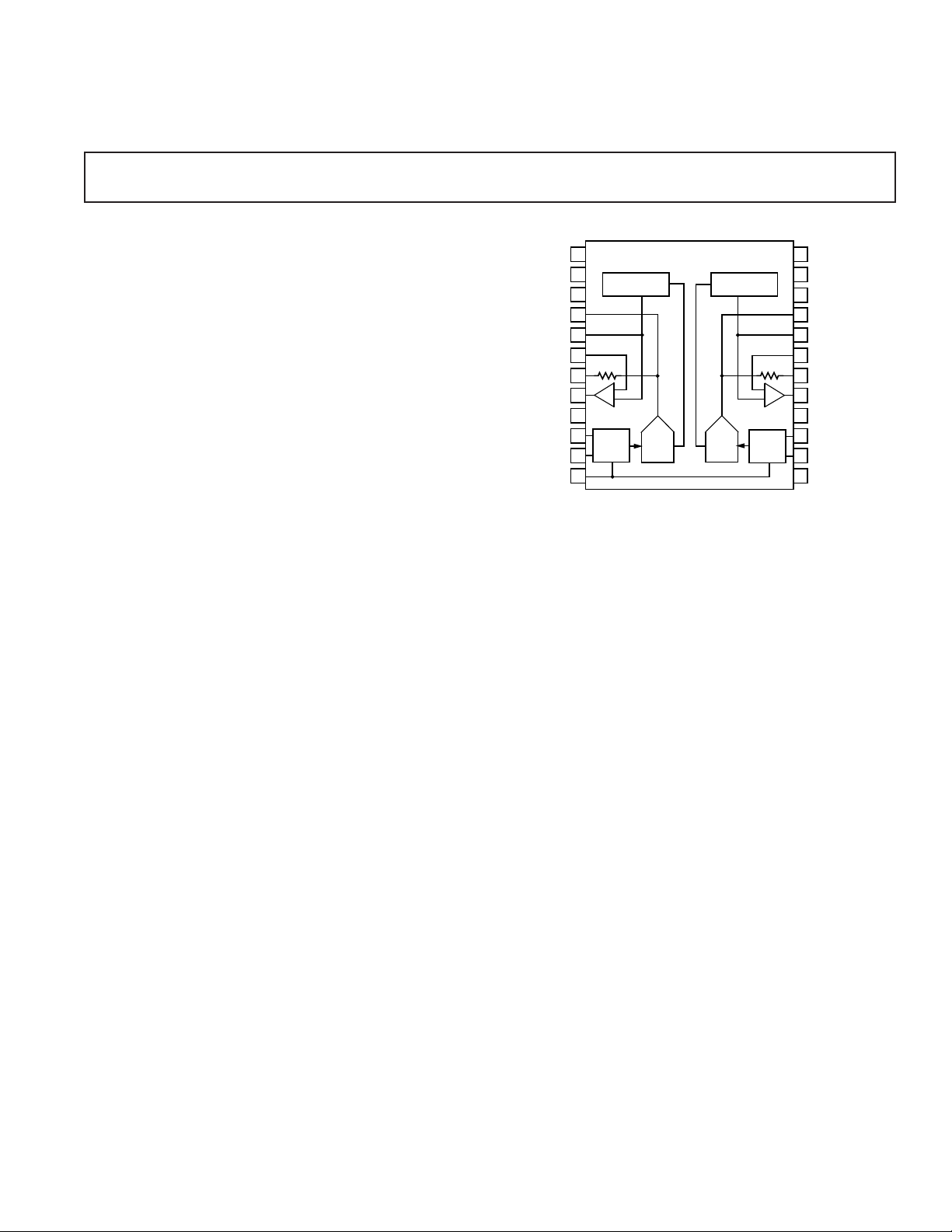

DIP BLOCK DIAGRAMS

24

1

–V

TRIM

MSB

I

OUT

AGND

SJ

R

V

OUT

+V

DR

LR

CLK

S

2

REFERENCE

3

4

5

6

7

F

–

8

+

9

L

10

18-BIT

LATCH

11

12

18-BIT

D/A

AD1864

REFERENCE

18-BIT

D/A

18-BIT

LATCH

A versatile digital interface allows the AD1864 to be directly

connected to standard digital filter chips. This interface employs

five signals: Data Left (DL), Data Right (DR), Latch Left (LL),

Latch Right (LR) and Clock (CLK). DL and DR are the serial

input pins for the left and right DAC input registers. Input data

bits are clocked into the input register on the rising edge of

CLK. A low going latch edge updates the respective DAC

output. For systems using only a single latch signal, LL and LR

may be connected together. For systems using only one DATA

signal, DR and DL may be connected together.

The AD1864 operates from ± 5 V to ±12 V power supplies. The

digital supplies, V

supplies, V

S

and –VL, can be separated from the analog

L

and –VS, for reduced digital feedthrough. Separate

analog and digital ground pins are also provided. The AD1864

typically dissipates only 225 mW, with a maximum power

dissipation of 265 mW.

The AD1864 is packaged in both a 24-pin plastic DIP and a

28-pin PLCC. Operation is guaranteed over the temperature

range of –25°C to +70°C and over the voltage supply range of

±4.75 V to ±13.2 V.

PRODUCT HIGHLIGHTS

1. The AD1864 is a complete dual 18-bit audio DAC.

2. 108 dB signal-to-noise ratio for low noise operation.

3. THD+N is typically 0.0017%.

4. Interchannel gain and midscale matching.

5. Output voltages and currents are cophased.

6. Low glitch for improved sound quality.

7. Both channels are 100% tested at 8 × F

S

8. Low Power—only 225 mW typ, 265 mW max.

9. Five-wire Interface for individual DAC control.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1997

+V

S

23

TRIM

22

MSB

21

I

OUT

20

AGND

19

SJ

18

R

–

+

F

17

V

OUT

16

–V

L

15

DL

14

LL

13

DGND

.

(TA = +258C, 6VL = 6VS = 65 V, FS = 352.8 kHz, without MSB adjustment

AD1864–SPECIFICATIONS

RESOLUTION 18 Bits

DIGITAL INPUTS

V

IH

V

IL

, VIH = +V

I

IH

, V

I

IL

IL

Clock Input Frequency 12.7 MHz

ACCURACY

Gain Error 0.4 1.0 % of FSR

Interchannel Gain Matching 0.3 0.8 % of FSR

Midscale Error 4 mV

Interchannel Midscale Matching 5 mV

Gain Linearity Error (0 dB to –90 dB) <2 dB

DRIFT (0°C to +70°C)

Gain Drift ±25 ppm of FSR/°C

Midscale Drift ±4 ppm of FSR/°C

TOTAL HARMONIC DISTORTION + NOISE*

0 dB, 990.5 Hz AD1864N, P 0.004 0.006 %

—20 dB, 990.5 Hz AD1864N, P 0.010 0.040 %

—60 dB, 990.5 Hz AD1864N, P 1.0 4.0 %

CHANNEL SEPARATION*

0 dB, 990.5 Hz 110 115 dB

SIGNAL-TO-NOISE RATIO*

(20 Hz to 30 kHz) N, N-J, N-K 102 108 dB

P, P-J 95 108 dB

D-RANGE* (WITH A-WEIGHT FILTER)

–60 dB, 990.5 Hz AD1864N, P 88 100 dB

OUTPUT

Voltage Output Configuration

Output Range (±3%) 62.88 ±3.0 63.12 V

Output Impedance 0.1 Ω

Load Current ±8mA

Short-Circuit Duration Indefinite to Common

Current Output Configuration

Bipolar Output Range (±30%) ±1mA

Output Impedance (±30%) 1.7 kΩ

POWER SUPPLY

+VL and +V

–VL and –V

+I, (+V

–I, (–VL and –VS = –5 V) –23 –28 mA

POWER DISSIPATION, ±VL = ±VS = ±5 V 225 265 mW

TEMPERATURE RANGE

Specification 0 +25 +70 °C

Operation –25 +70 °C

Storage –60 +100 °C

WARM-UP TIME 1

NO

TES

Specifications shown in boldface are tested on production units at final test without optional MSB adjustment.

*Tested in accordance with EIAJ Test Standard CP-307 with 18-bit data.

Specifications subject to cha

L

= 0.4 V –10 µA

AD1864N-J, P-J 0.003 0.004 %

AD1864N-K 0.0017 0.0025 %

AD1864N-J, P-J 0.010 0.020 %

AD1864N-K 0.010 0.020 %

AD1864N-J, P-J 1.0 2.0 %

AD1864N-K 1.0 2.0 %

AD1864N-J, P-J 94 100 dB

AD1864N-K 94 100 dB

S

S

and +VS = +5 V) 22 25 mA

L

nge without notice.

unless otherwise noted)

Min Typ Max Units

2.0 +V

L

0.8 V

1.0 µA

4.75 5.0 13.2 V

–13.2 –5.0 –4.75 V

–2–

V

min

REV. A

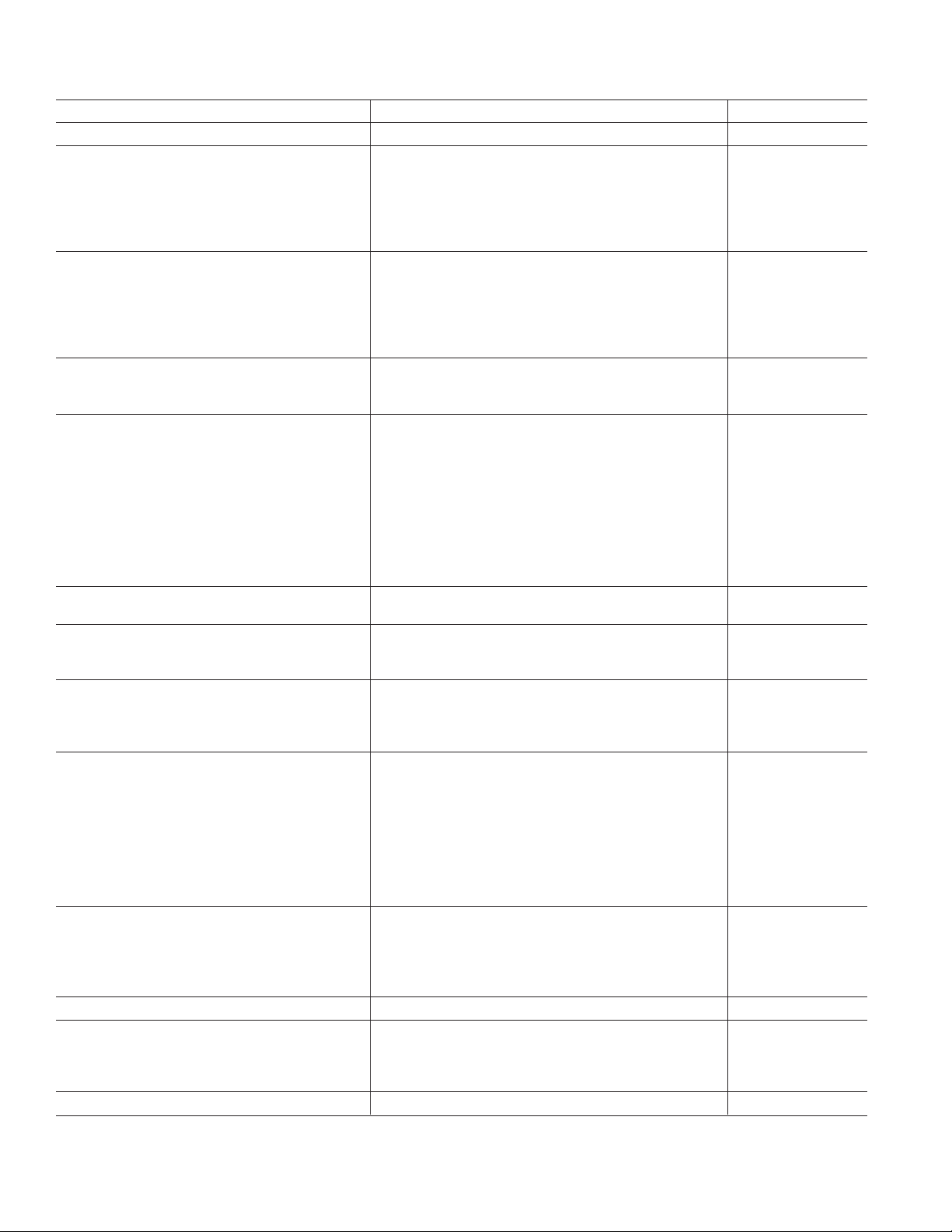

Typical Performance Data—

5

700

100

0

10

0

AD1864

100

90

80

70

60

50

40

THD+N – dB

30

20

10

0

0

24

0dB

–20dB

–60dB

FREQUENCY – kHz

6810

Figure 1. THD+N vs. Frequency

130

120

110

100

90

80

70

60

50

40

CHANNEL SEPARATION – dB

30

20

10

0

0

5

FREQUENCY – kHz

10 1

Figure 2. Channel Separation vs. Frequency

600

500

400

300

200

POWER DISSIPATION – mW

100

0

0681012

SUPPLY VOLTAGE –+V

Figure 4. Power Dissipation vs. Supply Voltage

90

80

70

60

50

40

THD+N – dB

30

20

10

0

500 1000

1500

LOAD RESISTANCE – Ω

2000

2500 300

Figure 5. THD+N vs. Load Resistance

100

8

95

90

THD+N – dB

85

80

0

20 40 60

TEMPERATURE – C

Figure 3. THD+N vs. Temperature

REV. A

–3–

6

4

2

0

–2

–4

GAIN LINEARITY ERROR – dB

–6

–8

–10

–100

–80

–70

–60

INPUT AMPLITUDE – dB

–40

–10–90

–20–50 –30

Figure 6. Gain Linearity Error vs. Input Amplitude

AD1864

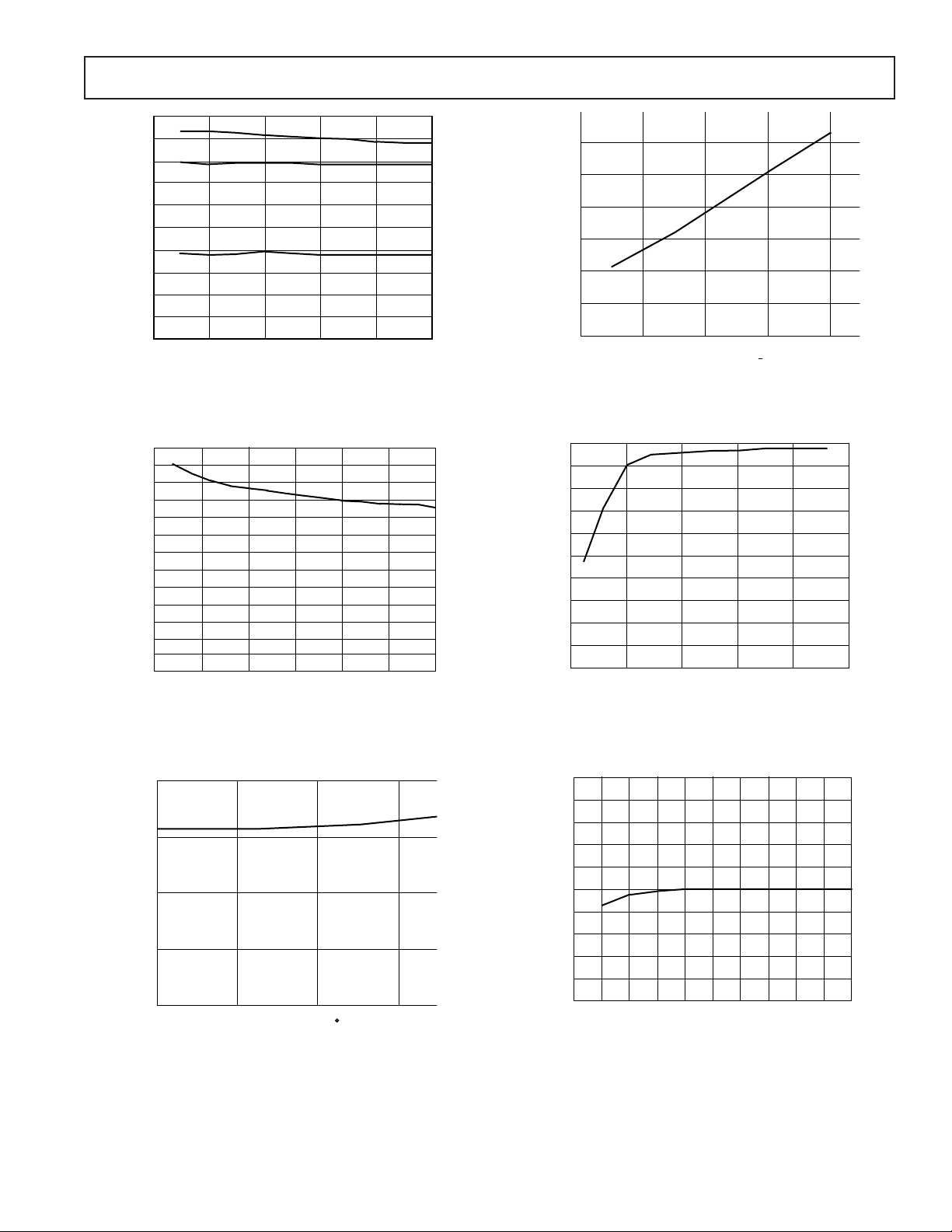

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

VL to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to 13.2 V

V

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to 13.2 V

S

–V

to DGND . . . . . . . . . . . . . . . . . . . . . . . . . –13.2 V to 0 V

L

–V

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . –13.2 V to 0 V

S

AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V

Digital Inputs to DGND . . . . . . . . . . . . . . . . . . . –0.3 V to V

Short-Circuit Protection . . . . . . . . Indefinite Short to Ground

Soldering (10 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . .+300°C

*Stresses greater than those listed under Absolute Maximum Ratings may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD1864 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

L

RIGHT

CHANNEL

I

OUT

AGND

SJ

NC

RF

V

OUT

+V

L

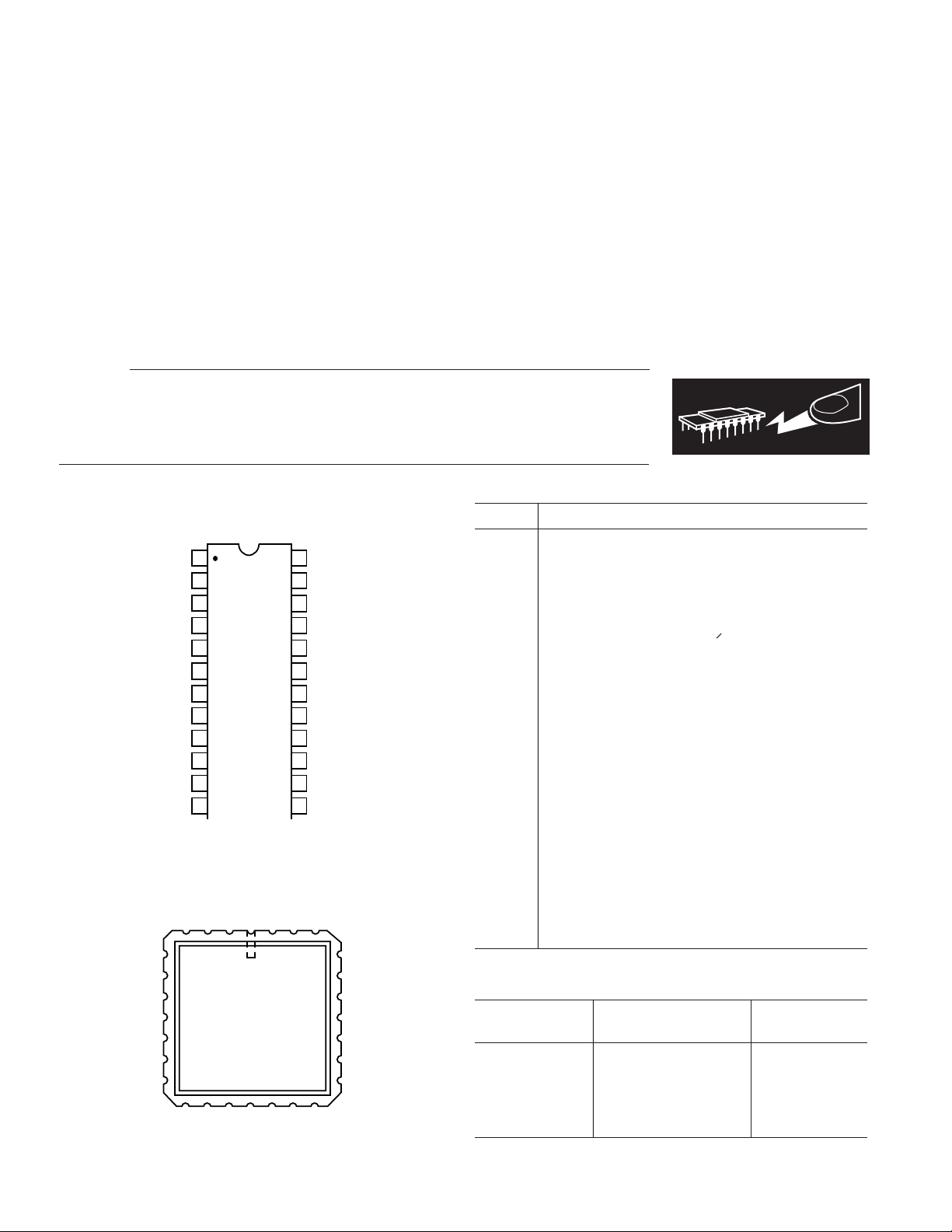

PIN CONFIGURATIONS

DIP Package

1

–V

S

2

TRIM

3

MSB

4

I

OUT

AGND

5

AD1864

6

V

+V

CLK

SJ

R

OUT

DR

LR

7

F

8

9

L

10

11

12

TOP VIEW

(Not to Scale)

PLCC Package

S

CK

S

NC

+V

28 27 26

NC

DGND

TRIM

–V

MSB

321

4

5

6

7

8

9

10

11

12 13

AD1864

TOP VIEW

(Not to Scale)

14 15 16

LR

DR

NC = NO CONNECT

24

23

22

21

20

19

18

17

16

15

14

13

TRIM

17 18

LL

+V

S

TRIM

MSB

I

OUT

AGND

SJ

R

F

V

OUT

–V

DL

LL

DGND

MSB

DL

L

LEFT

CHANNEL

25

I

OUT

24

AGND

23

SJ

22

NC

RF

21

V

20

OUT

–V

19

PIN FUNCTION DESCRIPTIONS

Signal Description

–V

S

Negative Analog Supply

TRIM Right Channel Trim Network Connection

MSB Right Channel Trim Potentiometer Connection

I

OUT

Right Channel Output Current

AGND Right Channel Analog Common Pin

SJ Right Channel Amplifier Summing Junction

R

V

+V

F

OUT

L

Right Channel Feedback Resistor

Right Channel Output Voltage

Positive Digital Supply

DR Right Channel Data Input Pin

LR Right Channel Latch Pin

CLK Clock Input Pin

DGND Digital Common Pin

LL Left Channel Latch Pin

DL Left Channel Data Input Pin

–V

V

R

L

OUT

F

Negative Digital Supply

Left Channel Output Voltage

Left Channel Feedback Resistor

SJ Left Channel Amplifier Summing Junction

AGND Left Channel Analog Common Pin

I

OUT

Left Channel Output Current

MSB Left Channel Trim Potentiometer Wiper Connection

TRIM Left Channel Trim Network Connection

+V

S

Positive Analog Supply

ORDERING GUIDE

THD+N Package

Model @ Full Scale Option*

AD1864N 0.006% N-24

L

AD 1864N-J 0.004% N-24

AD1864N-K 0.0025% N-24

AD1864P 0.006% P-28A

AD1864P-J 0.004% P-28A

*N = Plastic DIP; P = Plastic Leaded Chip Carrier.

–4–

REV. A

Loading...

Loading...