Analog Devices AD1849 Datasheet

Serial-Port 16-Bit

a

FEATURES

Single-Chip Integrated SD Digital Audio Stereo Codec

Multiple Channels of Stereo Input and Output

Digital Signal Mixing

On-Chip Speaker and Headphone Drive Capability

Programmable Gain and Attenuation

On-Chip Signal Filters

Digital Interpolation and Decimation

Analog Output Low-Pass

Sample Rates from 5.5 kHz to 48 kHz

44-Lead PLCC and TQFP Packages

Operation from +5 V and Mixed +5 V/+3.3 V Supplies

Serial Interface Compatible with ADSP-21xx Fixed-

Point DSmPs

Compatible with CS4215 (See Text)

PRODUCT OVERVIEW

The Serial-Port AD1849K SoundPort® Stereo Codec integrates

the key audio data conversion and control functions into a single

integrated circuit. The AD1849K is intended to provide a complete, single-chip audio solution for multimedia applications

requiring operation from a single +5 V supply. External signal

path circuit requirements are limited to three low tolerance

capacitors for line level applications; anti-imaging filters are

incorporated on-chip. The AD1849K includes on-chip monaural

SoundPort is a registered trademark of Analog Devices, Inc.

SoundPort Stereo Codec

AD1849K

speaker and stereo headphone drive circuits that require no

additional external components. Dynamic range exceeds 80 dB

over the 20 kHz audio band. Sample rates from 5.5 kHz to

48 kHz are supported from external crystals, from an external

clock, or from the serial interface bit clock.

The Codec includes a stereo pair of Σ∆ analog-to-digital

converters and a stereo pair of Σ∆ digital-to-analog converters.

Analog signals can be input at line levels or microphone levels.

A software controlled programmable gain stage allows

independent gain for each channel going into the ADC. The

ADCs’ output can be digitally mixed with the DACs’ input.

The left and right channel 16-bit outputs from the ADCs are

available over a single bidirectional serial interface that also supports 16-bit digital input to the DACs and control information.

The AD1849K can accept and generate 8-bit µ-law or A-law

companded digital data.

The Σ∆ DACs are preceded by a digital interpolation filter. An

attenuator provides independent user volume control over each

DAC channel. Nyquist images and shaped quantization noise

are removed from the DACs’ analog stereo output by on-chip

switched-capacitor and continuous-time filters. Two independent

stereo pairs of line-level (or one line-level and one headphone)

outputs are generated, as well as drive for a monaural (mono)

speaker.

(Continued on page 8)

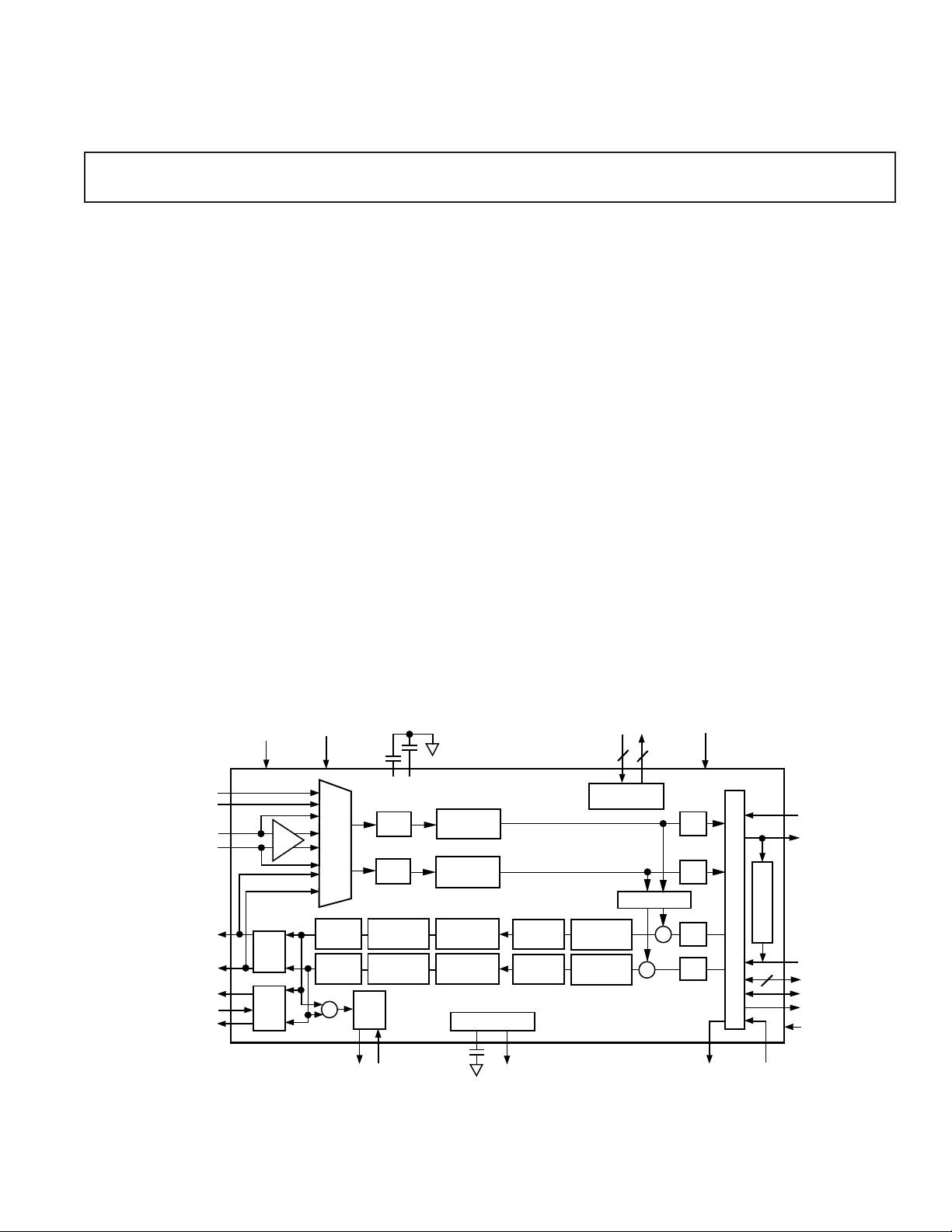

FUNCTIONAL BLOCK DIAGRAM

dB

DIGITAL

SUPPLY

L

20

L

R

L

R

MUX

ANALOG

FILTER

ANALOG

FILTER

∑

OUT RETURN

MONO SPEAKER

GAIN

R

GAIN

ATTENUATE

ATTENUATE

MUTE

∑∆ A/D

CONVERTER

∑∆ A/D

CONVERTER

∑∆ D/A

CONVERTER

∑∆ D/A

CONVERTER

LINE L

ANALOG

OUT

ANALOG

IN

HEADPHONE RETURN

LINE R

MIC L

MIC R

LINE 0 L

LINE 0 R

LINE 1 L

LINE 1 R

ANALOG

SUPPLY

LOOPBACK

MUTE

MUTE

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

CRYSTALS

2

OSCILLATORS

MONITOR MIX

INTERPOL

INTERPOL ATTENUATE

REFERENCE

2.25V

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

ATTENUATE

AD1849K

2

∑

POWER DOWN

µ/A

LAW

µ/A

LAW

µ/A

∑

LAW

µ/A

LAW

CHAINING

OUTPUT

S

E

R

I

A

L

P

O

R

T

CHAINING

INPUT

L

O

O

P

B

A

C

K

2

DATA/CONTROL

MODE

DATA/CONTROL

TRANSMIT

DATA/CONTROL

RECEIVE

PARALLEL I/O

BIT CLOCK

FRAME SYNC

RESET

DIGITAL

I/O

AD1849K–SPECIFICA TIONS

ELECTRICAL SPECIFICATIONS

STANDARD TEST CONDITIONS UNLESS OTHERWISE NOTED

Temperature 25 °C DAC Input Conditions

Digital Supply (V

Analog Supply (V

Clock (SCLK) 256 F

Master Mode 256 Bits per Frame OLB = 1

Word Rate (F

Input Signal 1 kHz 0 dB PGA Gain

Analog Output Passband 20 Hz to 20 kHz –3.0 dB Relative to Full Scale

V

IH

V

IL

External Load Impedance 10 kΩ

(Line 0)

External Load Impedance 48 Ω

(Line 1)

External Load Capacitance 100 pF

(Line 0, 1)

ANALOG INPUT

Input Voltage*

(RMS Values Assume Sine Wave Input)

Line and Mic with 0 dB Gain 0 94 0.99 1.04 V rms

Mic with +20 dB Gain 0.094 0.099 0.104 V rms

Input Capacitance 15 pF

*Accounts for Sum of Worst Case Reference Errors and Worst Case Gain Errors.

PROGRAMMABLE GAIN AMPLIFIER—ADC

) 5.0 V 0 dB Attenuation

DD

) 5.0 V Full-Scale Digital Inputs

CC

S

) 48 kHz ADC Input Conditions

S

16-Bit Linear Mode

2.4 V Line Input

0.8 V 16-Bit Linear Mode

All tests are performed on all ADC and DAC channels.

Min Typ Max Units

2.66 2.80 2.94 V p-p

0.266 0.280 0.294 V p-p

Min Typ Max Units

Step Size (0 dB to 22.5 dB) 1.3 1.5 1.7 dB

(All Steps Tested, –30 dB Input)

PGA Gain Range*

Line and Mic with 0 dB Gain –0.2 22.7 dB

Mic with +20 dB Gain 19.8 42.7 dB

DIGITAL DECIMATION AND INTERPOLATION FILTERS*

Min Max Units

Passband 0 0.45 × F

Hz

S

Passband Ripple ±0.1 dB

Transition Band 0.45 × F

Stopband ≥0.55 × F

S

S

0.55 × F

Hz

S

Hz

Stopband Rejection 74 dB

Group Delay 30/F

S

Group Delay Variation Over Passband 0.0 µs

–2–

REV. 0

AD1849K

ANALOG-TO-DIGITAL CONVERTERS

Min Typ Max Units

Resolution* 16 Bits

ADC Dynamic Range, A-Weighted 78 83 dB

Line and Mic with 0 dB Gain (–60 dB Input,

THD+N Referenced to Full Scale)

Mic with +20 dB Gain (–60 dB Input, 72 74 dB

THD+N Referenced to Full Scale)

ADC THD+N, (Referenced to Full Scale)

Line and Mic with 0 dB Gain 0.013 0.020 %

–78 –74 dB

Mic with +20 dB Gain 0.032 0.056 %

–70 –65 dB

ADC Crosstalk

Line to Line (Input L, Ground R, –80 dB

Read R; Input R, Ground L, Read L)

Line to Mic (Input LINL & R, –60 dB

Ground and Select MINL & R,

Read Both Channels)

Gain Error (Full-Scale Span Relative to Nominal) 0.75 dB

ADC Interchannel Gain Mismatch (Line and Mic) 0.3 dB

(Difference of Gain Errors)

DIGITAL-TO-ANALOG CONVERTERS

Min Typ Max Units

Resolution* 16 Bits

DAC Dynamic Range

(–60 dB Input, THD+N Referenced 80 86 dB

to Full Scale)

DAC THD+N (Referenced to Full Scale)

Line 0 and 1 (10 kΩ Load) 0.010 0.020 %

–80 –74 dB

Line 1 (48 Ω Load) 0.022 0.100 %

–73 –60 dB

Mono Speaker (48 Ω Load) 0.045 0.100 %

–67 –60 dB

DAC Crosstalk (Input L, Zero R, Measure –80 dB

LOUT0R & 1R; Input R, Zero L,

Measure LOUT0L & 1L)

Gain Error (Full-Scale Span Relative to Nominal) 0.75 dB

DAC Interchannel Gain Mismatch (Line 0 and 1) 0.3 dB

(Difference of Gain Errors)

Total Out-of-Band Energy* –60 dB

(Measured from 0.55 × FS to 100 kHz)

Audible Out-of-Band Energy* –72 dB

(Measured from 0.55 F

All Selectable Sampling Frequencies)

*Guaranteed, not tested.

REV. 0

to 22 kHz,

S

–3–

AD1849K

MONITOR MIX ATTENUATOR

Min Typ Max Units

Step Size (0.0 dB to –60 dB)* 1.3 1.5 1.7 dB

Step Size (–61.5 dB to –94.5 dB)* 1.0 1.5 2.0 dB

Output Attenuation* –95 0.2 dB

DAC ATTENUATOR

Min Typ Max Units

Step Size (0.0 dB to –60 dB) 1.3 1.5 1.7 dB

(Tested at Steps –1.5 dB, –19.5 dB,

–39 dB and –60 dB)

Step Size (–61.5 dB to –94.5 dB)* 1.0 1.5 2.0 dB

Output Attenuation* –95 0.2 dB

SYSTEM SPECIFICATIONS

Min Typ Max Units

System Frequency Response* –0.5 +0.2 dB

(Line In to Line Out,

0 to 0.45 × F

Differential Nonlinearity* ± 0.9 LSB

Phase Linearity Deviation* 5 Degrees

)

S

ANALOG OUTPUT

Min Typ Max Units

Full-Scale Output Voltage (Line 0 & 1) 0.707 V rms

[OLB = 1] 1.85 2.0 2.1 V p-p

Full-Scale Output Voltage (Line 0) 1.0 V rms

[OLB = 0] 2.8 V p-p

Full-Scale Output Voltage (Line 1) 4.0 V p-p

[OLB = 0]

Full-Scale Output Voltage (Mono Speaker) 4.0 V p-p

[OLB = 1]

Full-Scale Output Voltage (Mono Speaker) 8.0 V p-p

[OLB = 0]

CMOUT Voltage (No Load) 1.80 2.25 2.50 V

CMOUT Current Drive* 100 µA

CMOUT Output Impedance 4 kΩ

Mute Attenuation of 0 dB –80 dB

Fundamental* (LINE 0, 1, & MONO)

STATIC DIGITAL SPECIFICATIONS

Min Max Units

High Level Input Voltage (V

Digital Inputs 2.4 (V

XTAL1/2I 2.4 (V

Low Level Input Voltage (V

High Level Output Voltage (V

Low Level Output Voltage (V

)

IH

) –0.3 0.8 V

IL

) at IOH = –2 mA 2.4 V

OH

) at IOL = 2 mA 0.4 V

OL

+) + 0.3 V

DD

+) + 0.3 V

DD

Input Leakage Current –10 10 µA

(GO/NOGO Tested)

Output Leakage Current –10 10 µA

(GO/NOGO Tested)

–4–

REV. 0

DIGITAL TIMING PARAMETERS (Guaranteed over +4.75 V to +5.25 V, 0 8C to +708C)

Min Typ Max Units

AD1849K

SCLK Period (t

CLK

)

Slave Mode, MS = 0 80 ns

Master Mode, MS = 1* 1/(F

SCLK HI (t

)*

HI

× Bits per Frame) s

S

Slave Mode, MS = 0 25 ns

SCLK LO (t

LO

)*

Slave Mode, MS = 0 25 ns

CLKIN Frequency 13.5 MHz

CLKIN HI 30 ns

CLKIN LO 30 ns

Crystals Frequency 27

Input Setup Time (t

Input Hold Time (t

Output Delay (t

Output Hold Time (t

Output Hi-Z to Valid (t

Output Valid to Hi-Z (t

Power Up

RESET LO Time 50 ms

)15 ns

S

)10 ns

IH

) 25 ns

D

)0 ns

OH

)15 ns

ZV

) 20 ns

VZ

Operating RESET LO Time 100 ns

POWER SUPPLY

Min Typ Max Units

Power Supply Voltage Range* 4.75 5.25 V

–Digital and Analog

Power Supply Current—Operating 100 130 mA

(50% I

VDD

, 50% I

, Unloaded Outputs)

VCC

Power Supply Current—Power Down 20 200 µA

Power Supply Rejection (@ 1 kHz)* 40 dB

(At Both Analog and Digital

Supply Pins, Both ADCs and DACs)

CLOCK SPECIFICATIONS*

Min Max Units

Input Clock Frequency, Crystals 27 MHz

Clock Duty Cycle Tolerance ±10 %

Sample Rate (FS) 5.5125 50 kHz

*Guaranteed, not tested.

Specifications subject to change without notice.

REV. 0

–5–

AD1849K

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

Min Max Units

Power Supplies

Digital (V

Analog (V

) –0.3 6.0 V

DD

) –0.3 6.0 V

CC

Input Current

(Except Supply Pins and MOUT, ±10.0 mA

MOUTR, LOUT1R, LOUT1L,

LOUT1C)

Analog Input Voltage (Signal Pins) –0.3 (V

Digital Input Voltage (Signal Pins) –0.3 (V

+) + 0.3 V

CC

+) + 0.3 V

DD

Ambient Temperature (Operating) 0 +70 °C

Storage Temperature –65 +150 °C

ESD Tolerance (Human Body 500 V

Model per Method 3015.2

of MIL-STD-883B)

WARNING: CMOS device. May be susceptible to high voltage

transient-induced latchup.

*Stresses greater than those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

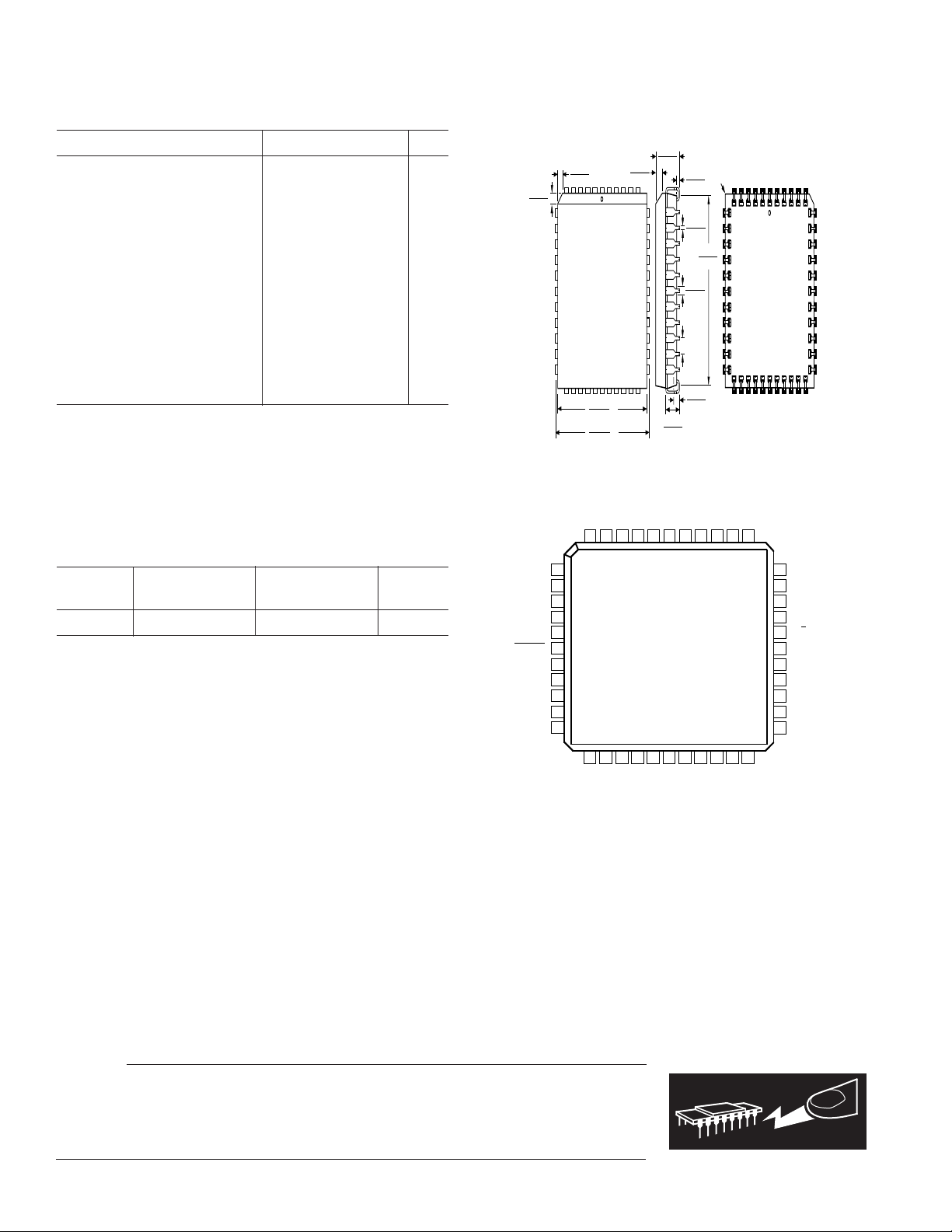

AD1849KP 0°C to +70°C 44-Lead PLCC P-44A

44-Lead Plastic Leaded Chip Carrier Pinout

0.180 (4.57)

0.165 (4.19)

PIN 1

IDENTIFIER

TOP VIEW

0.656 (16.66)

SQ

0.650 (16.51)

0.695 (17.65)

SQ

0.685 (17.40)

0.056 (1.42)

0.042 (1.07)

40 6

39

29

28

0.025 (0.63)

0.015 (0.38)

0.021 (0.53)

0.013 (0.33)

0.032 (0.81)

0.026 (0.66)

0.050

(1.27)

BSC

0.040 (1.01)

0.025 (0.64)

0.110 (2.79)

0.085 (2.16)

0.020 (0.50) R

0.63 (16.00)

0.59 (14.99)

PIN 1

IDENTIFIER

BOTTOM VIEW

0.048 (1.21)

0.042 (1.07)

0.048 (1.21)

0.042 (1.07)

7

17

18

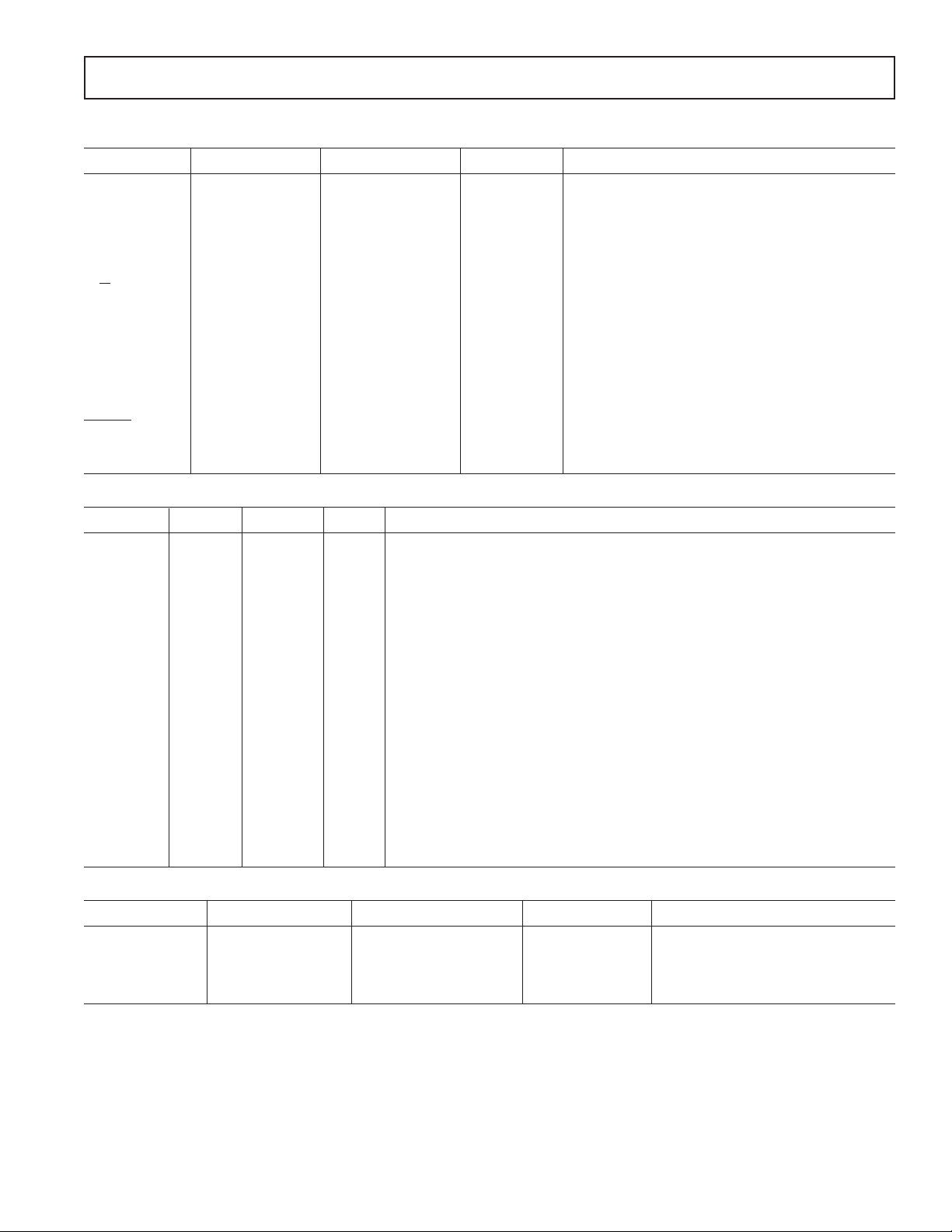

44-Lead TQFP

COUT1

V

GNDD

CIN2

COUT2

RESET

PDN

MINR

LINR

MINL

DD

V

SDRX

CLKOUT

CIN1

1

2

DD

3

4

5

6

7

8

C0

9

10

11

GNDD

CLKIN

AD1849KST

SoundPort®

STEREO CODEC

SDTX

SCLK

36 35 3444 43 42 41 40 39 38 37

TSOUT

FSYNC

TSIN

33

32

31

30

29

28

27

26

25

24

23

GNDD

V

DD

PIO1

PIO0

D/C

N/C

LOUT0R

LOUT0L

LOUT1L

LOUT1C

LOUT1R

N/C = NO CONNECT

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD1849K features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–6–

12 13 14 15 16 17 18 19 20 21 22

LINL

C1

CMOUT

CC

GNDA

CC

V

N/C

V

GNDA

MOUT

REF

V

MOUTR

REV. 0

AD1849K

PIN DESCRIPTION

Digital Signals

Pin Name PLCC TQFP I/O Description

SDRX 1 39 I Receive Serial Data Pin

SDTX 44 38 O Transmit Serial Data Pin

SCLK 43 37 I/O Bidirectional Serial Bit Clock

FSYNC 42 36 O Frame Sync Output Signal

TSOUT 41 35 O Chaining Word Output

TSIN 40 34 I Chaining Word Input

D/

C 35 29 I Data/Control Select Input

CIN1 6 44 I Crystal 1 Input

COUT1 7 1 O Crystal 1 Output

CIN2 10 4 I Crystal 2 Input

COUT2 11 5 O Crystal 2 Output

CLKIN 4 42 I External Sample Clock Input (256 × F

CLKOUT 5 43 O External Sample Clock Output (256 × F

PDN 13 7 I Power Down Input (Active HI)

RESET 12 6 I Reset Input (Active LO)

PIO1 37 31 I/O Parallel Input/Output Bit 1

PIO0 36 30 I/O Parallel Input/Output Bit 0

Analog Signals

Pin Name PLCC TQFP I/O Description

)

S

)

S

LINL 18 12 I Left Channel Line Input

LINR 16 10 I Right Channel Line Input

MINL 17 11 I Left Channel Microphone Input (–20 dB from Line Level if MB = 0 or Line

Level if MB = 1)

MINR 15 9 I Right Channel Microphone Input (–20 dB from Line Level if MB = 0 or Line

Level if MB = 1)

LOUT0L 32 26 O Left Channel Line Output 0

LOUT0R 33 27 O Right Channel Line Output 0

LOUT1L 31 25 O Left Channel Line Output 1

LOUT1R 29 23 O Right Channel Line Output 1

LOUT1C 30 24 I Common Return Path for Large Current from External Headphones

MOUT 27 21 O Mono Speaker Output

MOUTR 28 22 I Mono Speaker Output Return

C0 14 8 O External 1.0 µF Capacitor (±10%) Connection

C1 20 14 O External 1.0 µF Capacitor (±10%) Connection

N/C 26 20 No Connect (Do Not Connect)

N/C 34 28 No Connect (Do Not Connect)

V

REF

21 15 O Voltage Reference (Connect to Bypass Capacitor)

CMOUT 19 13 O Common Mode Reference Datum Output (Nominally 2.25 V)

Power Supplies

Pin Name PLCC TQFP I/O Description

V

CC

23 & 24 17, 18 I Analog Supply Voltage (+5 V)

GNDA 22 & 25 16, 19 I Analog Ground

V

DD

3, 8, 38 41, 2, 32 I Digital Supply Voltage (+5 V)

GNDD 2, 9, 39 40, 3, 33 I Digital Ground

REV. 0

–7–

AD1849K

(Continued from page 1)

FUNCTIONAL DESCRIPTION

This section overviews the functionality of the AD1849K and is

intended as a general introduction to the capabilities of the

device. As much as possible, detailed reference information has

been placed in “Control Registers” and other sections. The user

is not expected to refer repeatedly to this section.

Analog Inputs

The AD1849K SoundPort Stereo Codec accepts stereo

line-level and mic-level inputs. These analog stereo signals are

multiplexed to the internal programmable gain amplifier (PGA)

stage. The mic inputs can be amplified by +20 dB prior to the

PGA to compensate for the voltage swing difference between

line levels and typical condenser microphones. The mic inputs

can bypass the +20 dB fixed gain block and go straight to the

input multiplexer, which often results in an improved system

signal-to-noise ratio.

The PGA following the input multiplexer allows independent

selectable gains for each channel from 0 to 22.5 dB in +1.5 dB

steps. The Codec can operate either in a global stereo mode or

in a global mono mode with left-channel inputs appearing at

both channel outputs.

Analog-to-Digital Datapath

The AD1849K ∑∆ ADCs incorporate a proprietary fourth-order

modulator. A single pole of passive filtering is all that is required

for anti-aliasing the analog input because of the ADC’s high 64

times oversampling ratio. The ADCs include linear-phase digital

decimation filters that low-pass filter the input to 0.45 × F

S

(“FS” is the word rate or “sampling frequency”). ADC input

overrange conditions will cause a sticky bit to be set that can be

read.

Digital-to-Analog Datapath

The ∑∆ DACs are preceded by a programmable attenuator and

a low-pass digital interpolation filter. The attenuator allows

independent control of each DAC channel from 0 dB to –94.5dB

in 1.5 dB steps plus full digital mute. The anti-imaging interpolation filter oversamples by 64 and digitally filters the higher

frequency images. The DACs’ ∑∆ noise shapers also oversample

by 64 and convert the signal to a single-bit stream. The DAC

outputs are then filtered in the analog domain by a combination

of switched-capacitor and continuous-time filters. They remove

the very high frequency components of the DAC bitstream

output, including both images at the oversampling rate and

shaped quantization noise. No external components are required.

Phase linearity at the analog output is achieved by internally

compensating for the group delay variation of the analog output

filters.

Attenuation settings are specified by control bits in the data

stream. Changes in DAC output level take effect only on zero

crossings of the digital signal, thereby eliminating “zipper”

noise. Each channel has its own independent zero-crossing

detector and attenuator change control circuitry. A timer

guarantees that requested volume changes will occur even in the

absence of an input signal that changes sign. The time-out

period is 10.7 milliseconds at a 48 kHz sampling rate and 64

milliseconds at an 8 kHz sampling rate (Time-out [ms] ≈ 512/

Sampling Rate [kHz]).

Monitor Mix

A monitor mix is supported that digitally mixes a portion of the

digitized analog input with the analog output (prior to digitization). The digital output from the ADCs going out of the serial

data port is unaffected by the monitor mix. Along the monitor

mix datapath, the 16-bit linear output from the ADCs is

attenuated by an amount specified with control bits. Both

channels of the monitor data are attenuated by the same

amount. (Note that internally the AD1849K always works with

16-bit PCM linear data, digital mixing included; format

conversions take place at the input and output.)

Sixteen steps of –6 dB attenuation are supported to –94.5 dB. A

“0” implies no attenuation, while a “14” implies 84 dB of

attenuation. Specifying full scale “15” completely mutes the

monitor datapath, preventing any mixing of the analog input

with the digital input. Note that the level of the mixed output

signal is also a function of the input PGA settings since they

affect the ADCs’ output.

The attenuated monitor data is digitally summed with the DAC

input data prior to the DACs’ datapath attenuators. Because

both stereo signals are mixed before the output attenuators, mix

data is attenuated a second time by the DACs’ datapath

attenuators. The digital sum of digital mix data and DAC input

data is clipped at plus or minus full scale and does not wrap

around.

Analog Outputs

One stereo line-level output, one stereo headphone output, and

one monaural (mono) speaker output are available at external

pins. Each of these outputs can be independently muted.

Muting either the line-level stereo output or the headphone

stereo output mutes both left and right channels of that output.

When muted, the outputs will settle to a dc value near

CMOUT, the midscale reference voltage. The mono speaker

output is differential. The chip can operate either in a global

stereo mode or in a global mono mode with left channel inputs

appearing at both outputs.

Digital Data Types

The AD1849K supports four global data types: 16-bit twoscomplement linear PCM, 8-bit unsigned linear PCM, 8-bit

companded µ-law, and 8-bit companded A-law, as specified by

control register bits. Data in all four formats is always transferred MSB first. Sixteen-bit linear data output from the ADCs

and input to the DACs is in twos-complement format. Eight-bit

data is always left-justified in 16-bit fields; in other words, the

MSBs of all data types are always aligned; in yet other words,

full-scale representations in all three formats correspond to

equivalent full-scale signals. The eight least-significant bit

positions of 8-bit linear and companded data in 16-bit fields are

ignored on input and zeroed on output.

The 16-bit PCM data format is capable of representing 96 dB of

dynamic range. Eight-bit PCM can represent 48 dB of dynamic

range. Companded µ-law and A-law data formats use nonlinear

coding with less precision for large-amplitude signals. The loss

of precision is compensated for by an increase in dynamic range

to 64 dB and 72 dB, respectively.

–8–

REV. 0

AD1849K

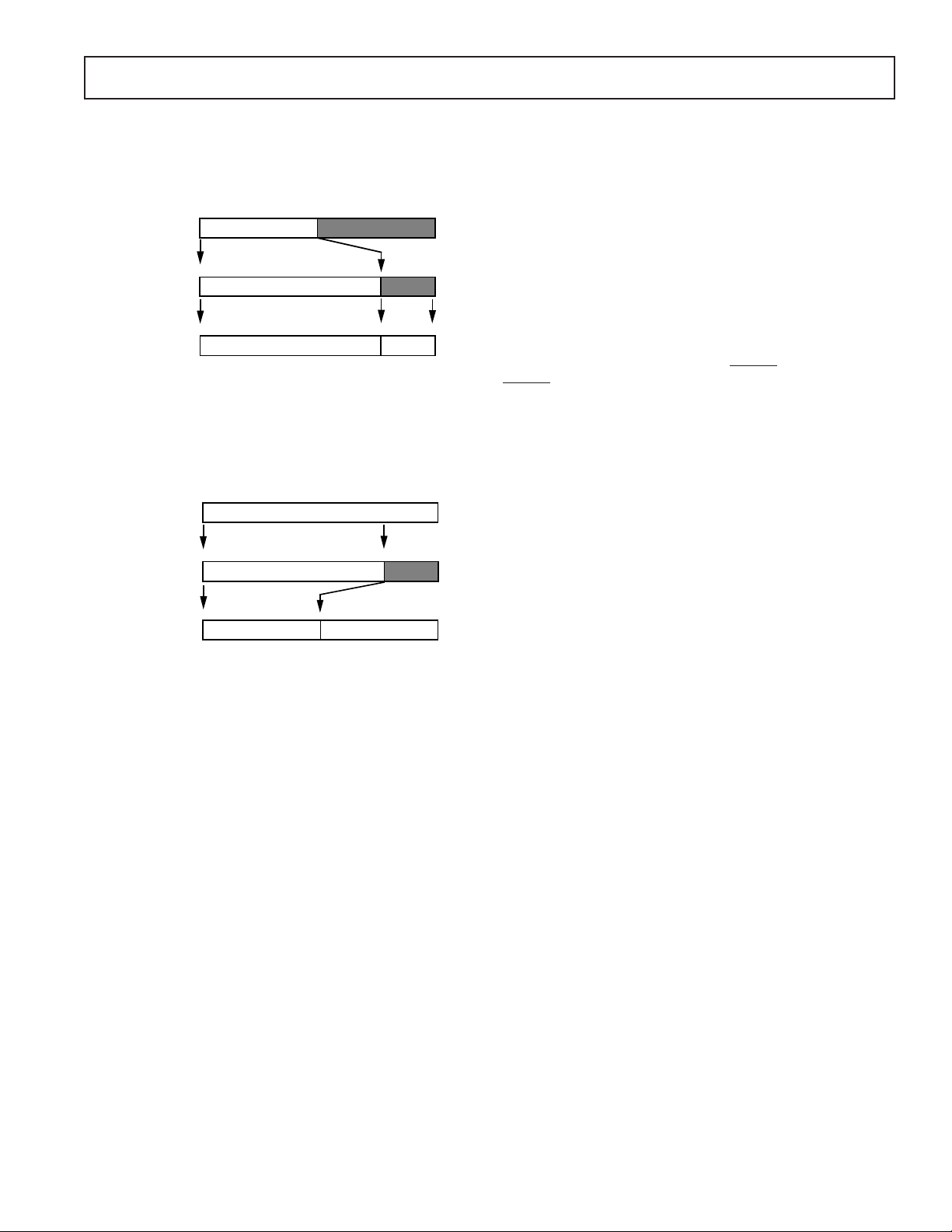

On input, 8-bit companded data is expanded to an internal

linear representation, according to whether µ-law or A-law was

specified in the Codec’s internal registers. Note that when µ-law

compressed data is expanded to a linear format, it requires 14

bits. A-law data expanded requires 13 bits, see Figure 1.

COMPRESSED

INPUT DATA

EXPANSION

DAC INPUT

15 0

MSB

15 0

MSB

15 0

MSB

LSB

8 7

3/2 2/1

LSB

3/2 2/1

LSB

0 0 0 / 0 0

Figure 1. A-Law or µ-Law Expansion

When 8-bit companding is specified, the ADCs’ linear output is

compressed to the format specified prior to output. See Figure 2.

Note that all format conversions take place at input or output.

Internally, the AD1849K always uses 16-bit linear PCM

representations to maintain maximum precision.

15 0

ADC OUTPUT

TRUNCATION

COMPRESSION

MSB

15 0

MSB

15 0

MSB

8 7

LSB

3/2

LSB

0 0 0 0 0 0 0 0

LSB

2/1

Figure 2. A-Law or µ-Law Compression

Power Supplies and Voltage Reference

The AD1849K operates from +5 V power supplies. Independent

analog and digital supplies are recommended for optimal

performance, though excellent results can be obtained in single

supply systems. A voltage reference is included on the Codec

and its 2.25 V buffered output is available on an external pin

(CMOUT). The CMOUT output can be used for biasing op

amps used in dc coupling. The internal reference is externally

bypassed to analog ground at the V

pin. Note that V

REF

REF

should only be connected to its bypass capacitors.

Autocalibration

The AD1849K supports an autocalibration sequence to eliminate

DAC and ADC offsets. The autocalibration sequence is

initiated in the transition from Control Mode to Data Mode,

regardless of the state of the AC bit. The user should specify

that analog outputs be muted to prevent undesired outputs.

Monitor mix will be automatically disabled by the Codec.

During the autocalibration sequence, the serial data output from

the ADCs is meaningless and the ADI bit is asserted. Serial data

inputs to the DACs are ignored. Even if the user specified the

muting of all analog outputs, near the end of the autocalibration

sequence, dc analog outputs very close to CMOUT will be

produced at the line outputs and mono speaker output.

An autocalibration sequence is also performed when the

AD1849K leaves the reset state (i.e.,

RESET goes HI). The

RESET pin should be held LO for 50 ms after power up or after

leaving power-down mode to delay the onset of the autocalibration

sequence until after the voltage reference has settled.

Loopback

Digital and analog loopback modes are supported for device and

system testing. The monitor mix datapath is always available for

loopback test purposes. Additional loopback tests are enabled by

setting the ENL bit (Control Word Bit 33) to a “1.”

Analog loopback mode D-A-D is enabled by setting the ADL

bit (Control Word Bit 32) to a “1” when ENL is a “1.” In this

mode, the DACs’ analog outputs are re-input to the PGAs prior

to the ADCs, allowing digital inputs to be compared to digital

outputs. The monitor mix will be automatically disabled by the

Codec during D-A-D loopback. The analog outputs can be

individually attenuated, and the analog inputs are internally

disconnected. Note that muting the line 0 output mutes the

looped-back signal in this mode.

Digital loopback mode D-D is enabled by resetting the ADL bit

(Control Word Bit 32) to a “0” when ENL is a “1.” In this

mode, the control and data bit pattern presented on the SDRX

pin is echoed on the SDTX pin with a two frame delay, allowing

the host controller to verify the integrity of the serial interface

starting on the third frame after D-D loopback is enabled.

During digital loopback mode, the output DACs are

operational.

REV. 0

–9–

Loading...

Loading...