Page 1

AMD Geode™ SC3200 Processor

Data Book

February 2007

Publication ID: 32581C

AMD Geode™ SC3200 Processor Data Book

Page 2

© 2007 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro

Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with

respect to the accuracy or completeness of the contents of this publication and

reserves the right to make changes to specifications and product descriptions at

any time without notice. No license, whether express, implied, arising by estoppel

or otherwise, to any intellectual property rights is granted by this publication.

Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD

assumes no liability whatsoever, and disclaims any express or implied warranty,

relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual

property right.

AMD’s products are not designed, intended, authorized or warranted for use as

components in systems intended for surgical implant into the body, or in other

applications intended to support or sustain life, or in any other application in which

the failure of AMD’s product could create a situation where personal injury, death,

or severe property or environmental damage may occur. AMD reserves the right to

discontinue or make changes to its products at any time without notice.

Contacts

www.amd.com

Trademarks

AMD, the AMD Arrow logo, AMD Geode, and combinations thereof, are trademarks of

Advanced Micro Devices, Inc.

Microsoft and Windows are registered trademarks of Microsoft Corporation in the United States and/or

other jurisdictions.

MMX is a trademark of Intel Corporation in the United States and/or other jurisdictions.

Other product names used in this publication are for identification purposes only and may be trademarks

of their respective companies.

2 AMD Geode™ SC3200 Processor Data Book

Page 3

Contents 32581C

Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.0 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.0 Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.1 GX1 Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.2 Video Processor Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.3 Core Logic Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.4 Super I/O Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.5 Clock, Timers, and Reset Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.0 Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.1 Ball Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.2 Strap Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.3 Multiplexing Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.4 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

4.0 General Configuration Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.1 Configuration Block Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.2 Multiplexing, Interrupt Selection, and Base Address Registers . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.3 WATCHDOG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.4 High-Resolution Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

4.5 Clock Generators and PLLs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.0 SuperI/O Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

5.2 Module Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.3 Configuration Structure / Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.4 Standard Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5.5 Real-Time Clock (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.6 System Wakeup Control (SWC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

5.7 ACCESS.bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

5.8 Legacy Functional Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

AMD Geode™ SC3200 Processor Data Book 3

Page 4

32581C

Contents

6.0 Core Logic Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

6.1 Feature List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

6.2 Module Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

6.3 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

6.4 Chipset Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

7.0 Video Processor Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 309

7.1 Module Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 310

7.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

7.3 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

8.0 Debugging and Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

8.1 Testability (JTAG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

9.0 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

9.1 General Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

9.2 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

9.3 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

10.0 Package Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

10.1 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

10.2 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 423

Appendix A Support Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

A.1 Order Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

A.2 Data Book Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 426

4 AMD Geode™ SC3200 Processor Data Book

Page 5

List of Figures 32581C

List of Figures

Figure 1-1. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

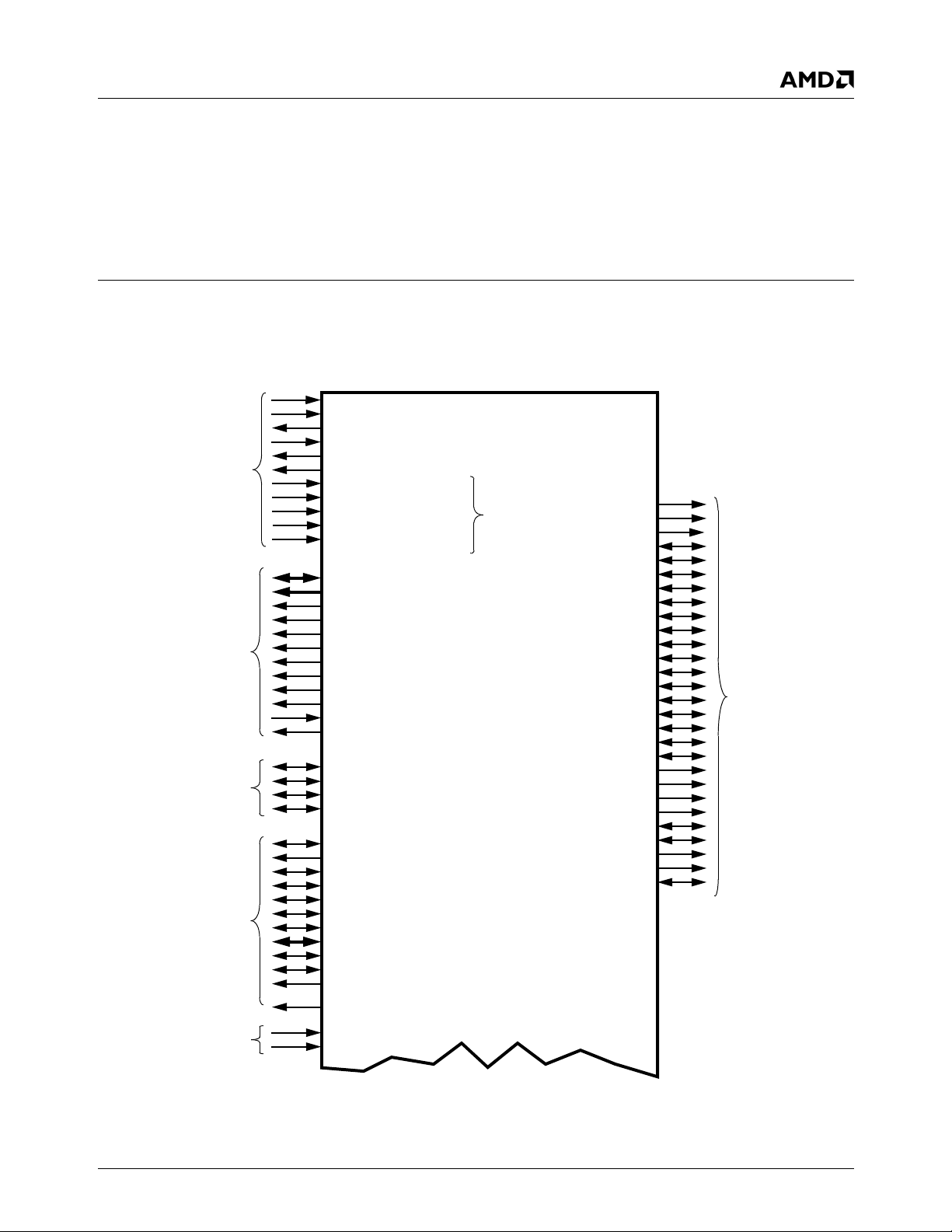

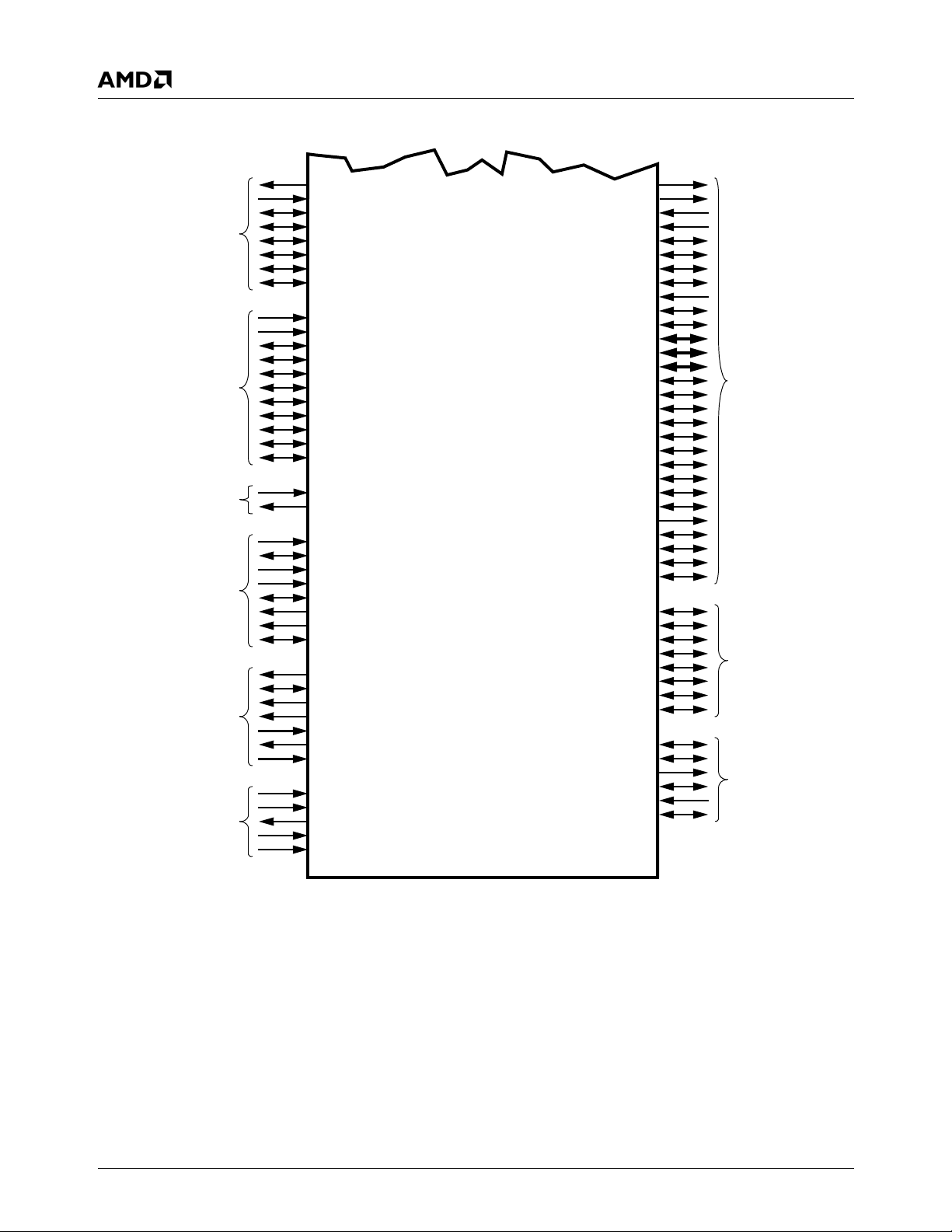

Figure 3-1. Signal Groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

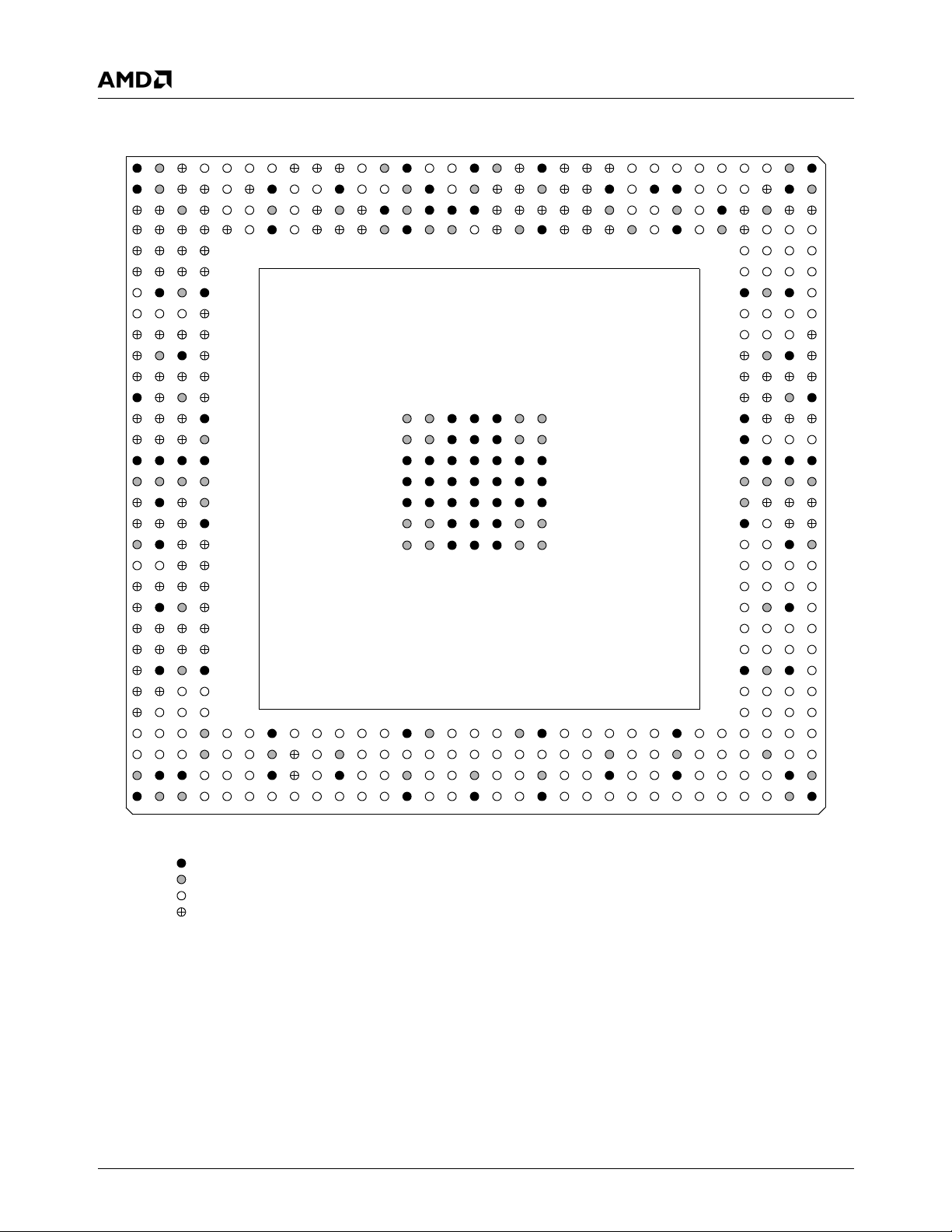

Figure 3-2. BGU481 Ball Assignment Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 4-1. WATCHDOG Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 4-2. Clock Generation Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 4-3. Recommended Oscillator External Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 5-1. SIO Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 5-2. Detailed SIO Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 5-3. Structure of the Standard Configuration Register File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Figure 5-4. Standard Configuration Registers Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 5-5. Recommended Oscillator External Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Figure 5-6. External Oscillator Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 5-7. Divider Chain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 5-8. Power Supply Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Figure 5-9. Typical Battery Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Figure 5-10. Typical Battery Current: Battery Backed Power Mode @ T

Figure 5-11. Typical Battery Current: Normal Operation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Figure 5-12. Interrupt/Status Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Figure 5-13. Bit Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Figure 5-14. Start and Stop Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Figure 5-15. ACCESS.bus Data Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Figure 5-16. ACCESS.bus Acknowledge Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Figure 5-17. A Complete ACCESS.bus Data Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Figure 5-18. UART Mode Register Bank Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 5-19. IRCP/SP3 Register Bank Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Figure 6-1. Core Logic Module Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Figure 6-2. Non-Posted Fast-PCI to ISA Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Figure 6-3. PCI to ISA Cycles with Delayed Transaction Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Figure 6-4. ISA DMA Read from PCI Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Figure 6-5. ISA DMA Write to PCI Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Figure 6-6. PCI Change to Sub-ISA and Back . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Figure 6-7. PIT Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Figure 6-8. PIC Interrupt Controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Figure 6-9. PCI and IRQ Interrupt Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Figure 6-10. SMI Generation for NMI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Figure 6-11. General Purpose Timer and UDEF Trap SMI Tree Example . . . . . . . . . . . . . . . . . . . . . . . . 163

Figure 6-12. PRD Table Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Figure 6-13. AC97 V2.0 Codec Signal Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Figure 6-14. Audio SMI Tree Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Figure 6-15. Typical Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Figure 7-1. Video Processor Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 310

Figure 7-2. NTSC 525 Lines, 60 Hz, Odd Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

Figure 7-3. NTSC 525 Lines, 60 Hz, Even Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

Figure 7-4. VIP Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

Figure 7-5. Capture Video Mode Bob Example Using One Video Frame Buffer . . . . . . . . . . . . . . . . . . 315

= 25°C . . . . . . . . . . . . . . . . . 106

C

AMD Geode™ SC3200 Processor Data Book 5

Page 6

32581C

List of Figures

Figure 7-6. Capture Video Mode Weave Example Using Two Video Frame Buffers . . . . . . . . . . . . . . . 316

Figure 7-7. Video Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

Figure 7-8. Horizontal Downscaler Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 318

Figure 7-9. Linear Interpolation Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

Figure 7-10. Mixer/Blender Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 320

Figure 7-11. Graphics/Video Frame with Alpha Windows . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

Figure 7-12. Color Key and Alpha Blending Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

Figure 7-13. TFT Power Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

Figure 7-14. PLL Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

Figure 9-1. Differential Input Sensitivity for Common Mode Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

Figure 9-2. Drive level and Measurement Points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

Figure 9-3. Memory Controller Drive Level and Measurement Points . . . . . . . . . . . . . . . . . . . . . . . . . . 363

Figure 9-4. Memory Controller Output Valid Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 365

Figure 9-5. Read Data In Setup and Hold Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 365

Figure 9-6. Video Input Port Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

Figure 9-7. TFT Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

Figure 9-8. ACB Signals: Rising Time and Falling Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

Figure 9-9. ACB Start and Stop Condition Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

Figure 9-10. ACB Start Condition Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

Figure 9-11. ACB Data Bit Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

Figure 9-12. Testing Setup for Slew Rate and Minimum Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

Figure 9-13. V/I Curves for PCI Output Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

Figure 9-14. PCICLK Timing and Measurement Points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

Figure 9-15. Load Circuits for Maximum Time Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 374

Figure 9-16. Output Timing Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375

Figure 9-17. Input Timing Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376

Figure 9-18. PCI Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376

Figure 9-19. Sub-ISA Read Operation Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

Figure 9-20. Sub-ISA Write Operation Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

Figure 9-21. LPC Output Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

Figure 9-22. LPC Input Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

Figure 9-23. IDE Reset Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

Figure 9-24. Register Transfer to/from Device Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

Figure 9-25. PIO Data Transfer to/from Device Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 386

Figure 9-26. Multiword DMA Data Transfer Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 388

Figure 9-27. Initiating an UltraDMA Data in Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 390

Figure 9-28. Sustained UltraDMA Data In Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 391

Figure 9-29. Host Pausing an UltraDMA Data In Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . 392

Figure 9-30. Device Terminating an UltraDMA Data In Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . 393

Figure 9-31. Host Terminating an UltraDMA Data In Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . . . 394

Figure 9-32. Initiating an UltraDMA Data Out Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

Figure 9-33. Sustained UltraDMA Data Out Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 396

Figure 9-34. Device Pausing an UltraDMA Data Out Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . . . 397

Figure 9-35. Host Terminating an UltraDMA Data Out Burst Timing Diagram . . . . . . . . . . . . . . . . . . . . . 398

Figure 9-36. Device Terminating an UltraDMA Data Out Burst Timing Diagram . . . . . . . . . . . . . . . . . . . 399

Figure 9-37. Data Signal Rise and Fall Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 402

Figure 9-38. Source Differential Data Jitter Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 402

Figure 9-39. EOP Width Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

Figure 9-40. Receiver Jitter Tolerance Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

Figure 9-41. UART, Sharp-IR, SIR, and Consumer Remote Control Timing Diagram . . . . . . . . . . . . . . . 404

Figure 9-42. Fast IR (MIR and FIR) Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 405

Figure 9-43. Standard Parallel Port Typical Data Exchange Timing Diagram . . . . . . . . . . . . . . . . . . . . . 406

Figure 9-44. Enhanced Parallel Port Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 407

Figure 9-45. ECP Forward Mode Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408

Figure 9-46. ECP Reverse Mode Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

6 AMD Geode™ SC3200 Processor Data Book

Page 7

List of Figures

32581C

Figure 9-47. AC97 Reset Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 410

Figure 9-48. AC97 Sync Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 410

Figure 9-49. AC97 Clocks Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 411

Figure 9-50. AC97 Data TIming Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 412

Figure 9-51. AC97 Rise and Fall Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 413

Figure 9-52. AC97 Low Power Mode Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 414

Figure 9-53. PWRBTN# Trigger and ONCTL# Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

Figure 9-54. GPWIO and ONCTL# Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

Figure 9-55. Power-Up Sequencing With PWRBTN# Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 416

Figure 9-56. Power-Up Sequencing Without PWRBTN# Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . 417

Figure 9-57. TCK Measurement Points and Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 418

Figure 9-58. JTAG Test Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

Figure 10-1. Heatsink Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

Figure 10-2. BGU481 Package - Top View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 423

Figure 10-3. BGU481 Package - Bottom View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 424

AMD Geode™ SC3200 Processor Data Book 7

Page 8

32581C

List of Figures

8 AMD Geode™ SC3200 Processor Data Book

Page 9

List of Tables 32581C

List of Tables

Table 2-1. SC3200 Memory Controller Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 2-2. SC3200 Memory Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

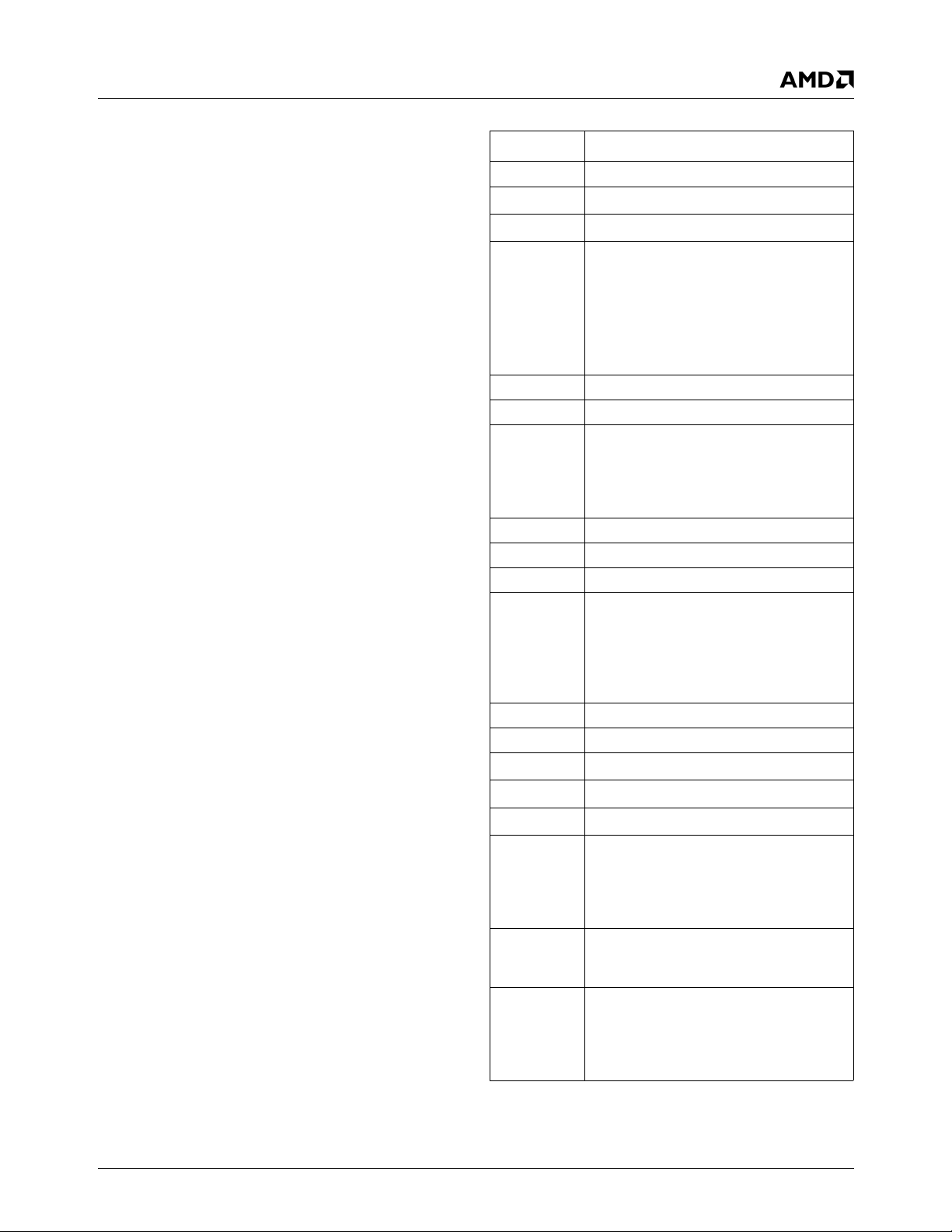

Table 3-1. Signal Definitions Legend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

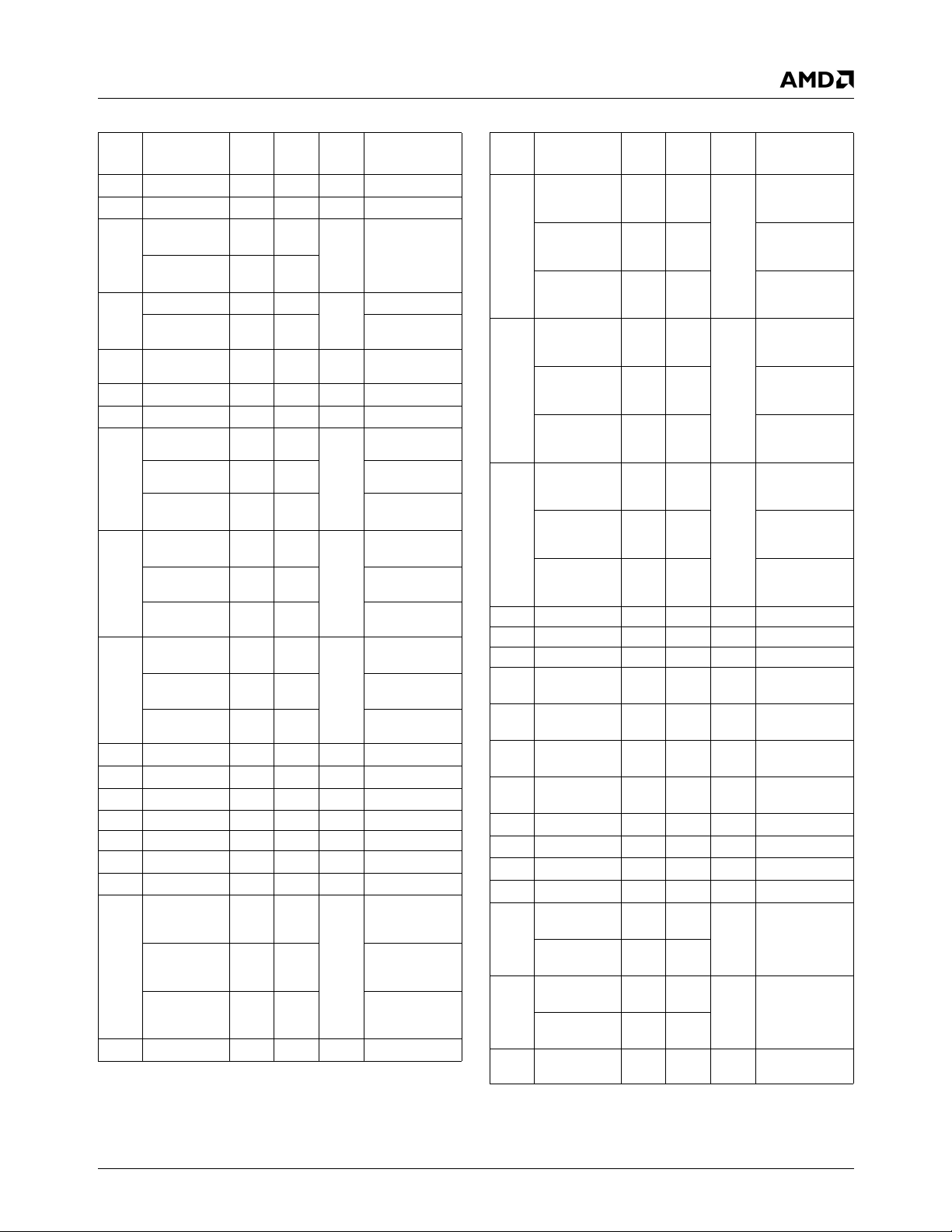

Table 3-2. BGU481 Ball Assignment - Sorted by Ball Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 3-3. BGU481 Ball Assignment - Sorted Alphabetically by Signal Name . . . . . . . . . . . . . . . . . . . 40

Table 3-4. Strap Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 3-5. Two-Signal/Group Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 3-6. Three-Signal/Group Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 3-7. Four-Signal/Group Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 4-1. General Configuration Block Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 4-2. Multiplexing, Interrupt Selection, and Base Address Registers . . . . . . . . . . . . . . . . . . . . . . . 70

Table 4-3. WATCHDOG Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 4-4. High-Resolution Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 4-5. Crystal Oscillator Circuit Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 4-6. Core Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 4-7. Strapped Core Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 4-8. Clock Generator Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 5-1. SIO Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 5-2. LDN Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 5-3. Standard Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 5-4. SIO Control and Configuration Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 5-5. SIO Control and Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

Table 5-6. Relevant RTC Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

Table 5-7. RTC Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 5-8. Relevant SWC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 5-9. Relevant IRCP/SP3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 5-10. IRCP/SP3 Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 5-11. Relevant Serial Ports 1 and 2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 5-12. Serial Ports 1 and 2 Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 5-13. Relevant ACB1 and ACB2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 5-14. ACB1 and ACB2 Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 5-15. Relevant Parallel Port Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 5-16. Parallel Port Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 5-17. Crystal Oscillator Circuit Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 5-18. System Power States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 5-19. RTC Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 5-20. RTC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 5-21. Divider Chain Control / Test Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 5-22. Periodic Interrupt Rate Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 5-23. BCD and Binary Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 5-24. Standard RAM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 5-25. Extended RAM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 5-26. Time Range Limits for CEIR Protocols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 5-27. Banks 0 and 1 - Common Control and Status Register Map . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 5-28. Bank 1 - CEIR Wakeup Configuration and Control Register Map . . . . . . . . . . . . . . . . . . . . 115

AMD Geode™ SC3200 Processor Data Book 9

Page 10

32581C

List of Tables

Table 5-29. Banks 0 and 1 - Common Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 5-30. Bank 1 - CEIR Wakeup Configuration and Control Registers . . . . . . . . . . . . . . . . . . . . . . . 117

Table 5-31. ACB Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 5-32. ACB Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 5-33. Parallel Port Register Map for First Level Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Table 5-34. Parallel Port Register Map for Second Level Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Table 5-35. Parallel Port Bit Map for First Level Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 5-36. Parallel Port Bit Map for Second Level Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 5-37. Bank 0 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Table 5-38. Bank Selection Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Table 5-39. Bank 1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Table 5-40. Bank 2 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Table 5-41. Bank 3 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Table 5-42. Bank 0 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Table 5-43. Bank 1 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Table 5-44. Bank 2 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 5-45. Bank 3 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 5-46. Bank 0 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Table 5-47. Bank Selection Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 5-48. Bank 1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 5-49. Bank 2 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 5-50. Bank 3 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 5-51. Bank 4 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 5-52. Bank 5 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 5-53. Bank 6 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 5-54. Bank 7 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 5-55. Bank 0 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 5-56. Bank 1 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 5-57. Bank 2 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 5-58. Bank 3 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 5-59. Bank 4 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 5-60. Bank 5 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Table 5-61. Bank 6 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Table 5-62. Bank 7 Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Table 6-1. Physical Region Descriptor Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Table 6-2. UltraDMA/33 Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 6-3. Cycle Multiplexed PCI / Sub-ISA Balls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 6-4. PIC Interrupt Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 6-5. Wakeup Events Capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Table 6-6. Power Planes Control Signals vs. Sleep States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Table 6-7. Power Planes vs. Sleep/Global States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Table 6-8. Power Management Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Table 6-9. Device Power Management Programming Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 6-10. Bus Masters That Drive Specific Slots of the AC97 Interface . . . . . . . . . . . . . . . . . . . . . . . 165

Table 6-11. Physical Region Descriptor Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Table 6-12. Cycle Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Table 6-13. PCI Configuration Address Register (0CF8h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 6-14. F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support Summary . . . 174

Table 6-15. F0BAR0: GPIO Support Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Table 6-16. F0BAR1: LPC Support Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Table 6-17. F1: PCI Header Registers for SMI Status and ACPI Support Summary . . . . . . . . . . . . . . . 178

Table 6-18. F1BAR0: SMI Status Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Table 6-19. F1BAR1: ACPI Support Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Table 6-20. F2: PCI Header Registers for IDE Controller Support Summary . . . . . . . . . . . . . . . . . . . . . 180

Table 6-21. F2BAR4: IDE Controller Support Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

10 AMD Geode™ SC3200 Processor Data Book

Page 11

List of Tables

32581C

Table 6-22. F3: PCI Header Registers for Audio Support Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

Table 6-23. F3BAR0: Audio Support Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Table 6-24. F5: PCI Header Registers for X-Bus Expansion Support Summary . . . . . . . . . . . . . . . . . . 183

Table 6-25. F5BAR0: I/O Control Support Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Table 6-26. PCIUSB: USB PCI Configuration Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Table 6-27. USB_BAR: USB Controller Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Table 6-28. ISA Legacy I/O Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Table 6-29. F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support . . . . . . . . . . . 188

Table 6-30. F0BAR0+I/O Offset: GPIO Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

Table 6-31. F0BAR1+I/O Offset: LPC Interface Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . 226

Table 6-32. F1: PCI Header Registers for SMI Status and ACPI Support . . . . . . . . . . . . . . . . . . . . . . . 234

Table 6-33. F1BAR0+I/O Offset: SMI Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

Table 6-34. F1BAR1+I/O Offset: ACPI Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Table 6-35. F2: PCI Header/Channels 0 and 1 Registers for IDE Controller Configuration . . . . . . . . . . 255

Table 6-36. F2BAR4+I/O Offset: IDE Controller Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . 259

Table 6-37. F3: PCI Header Registers for Audio Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

Table 6-38. F3BAR0+Memory Offset: Audio Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Table 6-39. F5: PCI Header Registers for X-Bus Expansion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

Table 6-40. F5BAR0+I/O Offset: X-Bus Expansion Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

Table 6-41. PCIUSB: USB PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

Table 6-42. USB_BAR+Memory Offset: USB Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285

Table 6-43. DMA Channel Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

Table 6-44. DMA Page Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

Table 6-45. Programmable Interval Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

Table 6-46. Programmable Interrupt Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

Table 6-47. Keyboard Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

Table 6-48. Real-Time Clock Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 307

Table 6-49. Miscellaneous Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 307

Table 7-1. Valid Mixing/Blending Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 321

Table 7-2. Truth Table for Alpha Blending . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

Table 7-3. F4: PCI Header Registers for Video Processor Support Summary . . . . . . . . . . . . . . . . . . . 327

Table 7-4. F4BAR0: Video Processor Configuration Registers Summary . . . . . . . . . . . . . . . . . . . . . . 327

Table 7-5. F4BAR2: VIP Support Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 329

Table 7-6. F4: PCI Header Registers for Video Processor Support Registers . . . . . . . . . . . . . . . . . . . 330

Table 7-7. F4BAR0+Memory Offset: Video Processor Configuration Registers . . . . . . . . . . . . . . . . . . 332

Table 7-8. F4BAR2+Memory Offset: VIP Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

Table 8-1. JTAG Mode Instruction Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

Table 9-1. Electro Static Discharge (ESD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

Table 9-2. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

Table 9-3. Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352

Table 9-4. Power Planes of External Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 353

Table 9-5. System Conditions Used to Measure SC3200 Current During On State . . . . . . . . . . . . . . . 354

Table 9-6. DC Characteristics for On State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354

Table 9-7. DC Characteristics for Active Idle, Sleep, and Off States . . . . . . . . . . . . . . . . . . . . . . . . . . 355

Table 9-8. Ball Capacitance and Inductance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 355

Table 9-9. Balls with PU/PD Resistors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

Table 9-10. Buffer Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

Table 9-11. Default Levels for Measurement of Switching Parameters . . . . . . . . . . . . . . . . . . . . . . . . . 362

Table 9-12. Memory Controller Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

Table 9-13. Video Input Port Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

Table 9-14. TFT Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

Table 9-15. ACCESS.bus Input Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368

Table 9-16. ACCESS.bus Output Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368

Table 9-17. PCI AC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

Table 9-18. PCI Clock Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

AMD Geode™ SC3200 Processor Data Book 11

Page 12

32581C

List of Tables

Table 9-19. PCI Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 374

Table 9-20. Measurement Condition Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375

Table 9-21. Sub-ISA Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

Table 9-22. LPC and SERIRQ Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

Table 9-23. IDE General Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

Table 9-24. IDE Register Transfer to/from Device Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . 383

Table 9-25. IDE PIO Data Transfer to/from Device Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . 385

Table 9-26. IDE Multiword DMA Data Transfer Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . 387

Table 9-27. IDE UltraDMA Data Burst Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 389

Table 9-28. USB Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400

Table 9-29. UART, Sharp-IR, SIR, and Consumer Remote Control Timing Parameters . . . . . . . . . . . . 404

Table 9-30. Fast IR Port Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 405

Table 9-31. Standard Parallel Port Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

Table 9-33. ECP Forward Mode Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408

Table 9-34. ECP Reverse Mode Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

Table 9-35. AC Reset Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 410

Table 9-36. AC97 Sync Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 410

Table 9-37. AC97 Clocks Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 411

Table 9-38. AC97 I/O Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 412

Table 9-39. AC97 Signal Rise and Fall Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 413

Table 9-40. AC97 Low Power Mode Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 414

Table 9-41. PWRBTN# Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

Table 9-42. Power Management Event (GPWIO) and ONCTL# Timing Parameters . . . . . . . . . . . . . . . 415

Table 9-43. Power-Up Sequence Using the Power Button Timing Parameters . . . . . . . . . . . . . . . . . . . 416

Table 9-44. Power-Up Sequence Not Using the Power Button Timing Parameters . . . . . . . . . . . . . . . . 417

Table 9-45. JTAG Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 418

Table 10-1. q

(×C/W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

JC

Table 10-2. Case-to-Ambient Thermal Resistance Example @ 85×C . . . . . . . . . . . . . . . . . . . . . . . . . . 421

Table A-1. Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 426

12 AMD Geode™ SC3200 Processor Data Book

Page 13

Overview 32581C

1.0Overview

1.1 General Description

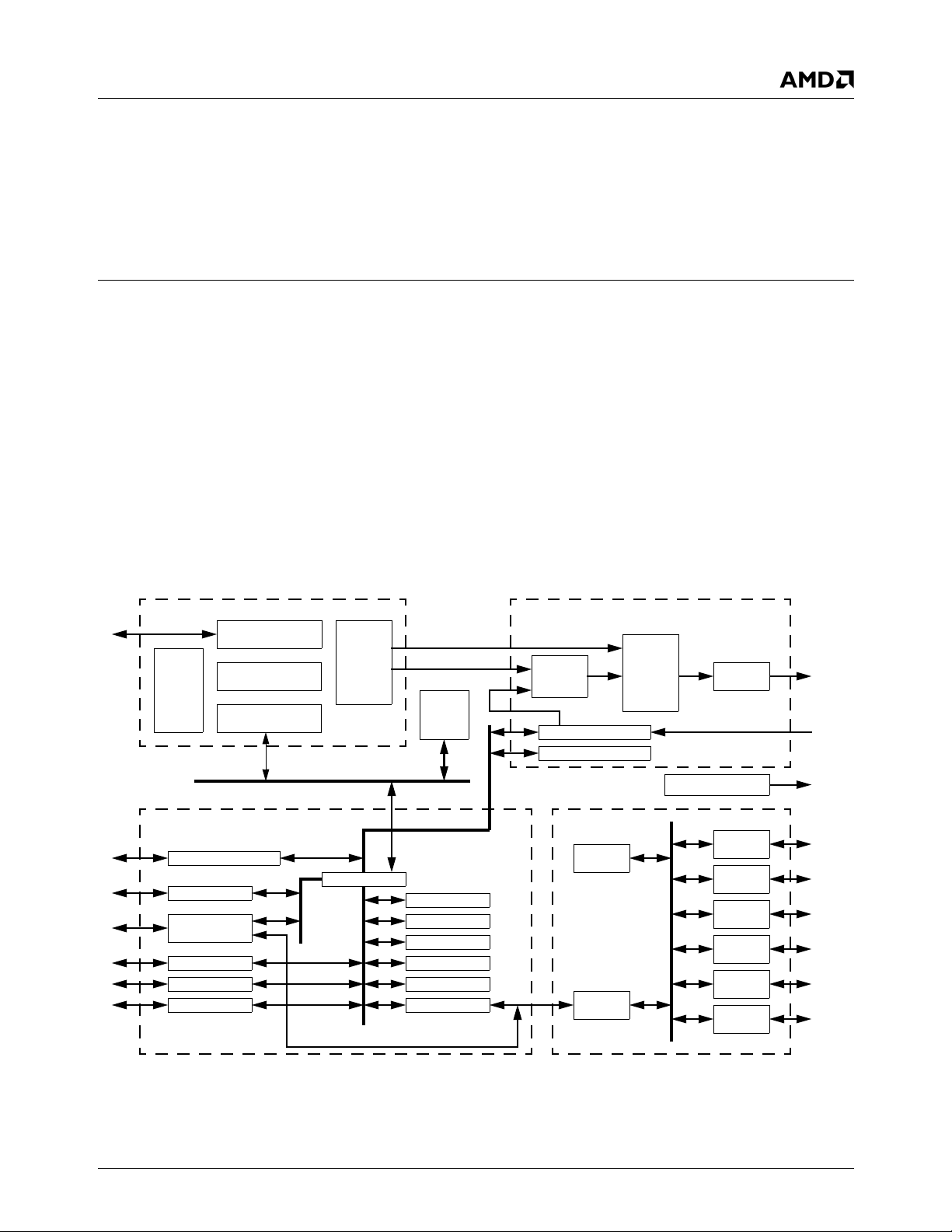

The AMD Geode™ SC3200 processor is a member of the

AMD Geode family of fully integrated x86 system chips.

The SC3200 processor includes:

• The AMD Geode GX1 processor module combines

advanced CPU performance with MMX™ support, fully

accelerated 2D graphics, a 64-bit synchronous DRAM

(SDRAM) interface, a PCI bus controller, and a display

controller.

• A low-power TFT Video Processor module with a Video

Input Port (VIP), and a hardware video accelerator for

scaling, filtering, and color space conversion.

• The Core Logic module includes: PC/AT functionality, a

USB interface, an IDE interface, a PCI bus interface, an

LPC bus interface, Advanced Configuration Power Interface (ACPI) version 1.0 compliant power management,

and an audio codec interface.

• The SuperI/O module has: three serial ports (UART1,

UART2, and UART3 with fast infrared), a parallel port,

two ACCESS.bus (ACB) interfaces, and a real-time

clock (RTC).

These features, combined with the device’s low power consumption, enable a small form factor design making it ideal

as the core for a WebPAD™ system application.

1

GX1

CPU

Core

IDE I/F

USB

PCI/Sub-ISA

Bus I/F

GPIO

Audio Codec I/F

LPC I/F

Memory Controller

2D Graphics

Accelerator

PCI Bus

Controller

Display

Controller

Fast-PCI Bus

Bridge

PCI Bus

X-Bus

Config.

Block

Fast X-Bus

Core Logic

PIT

PIC

DMAC

Pwr Mgmnt

Configuration

ISA Bus I/F

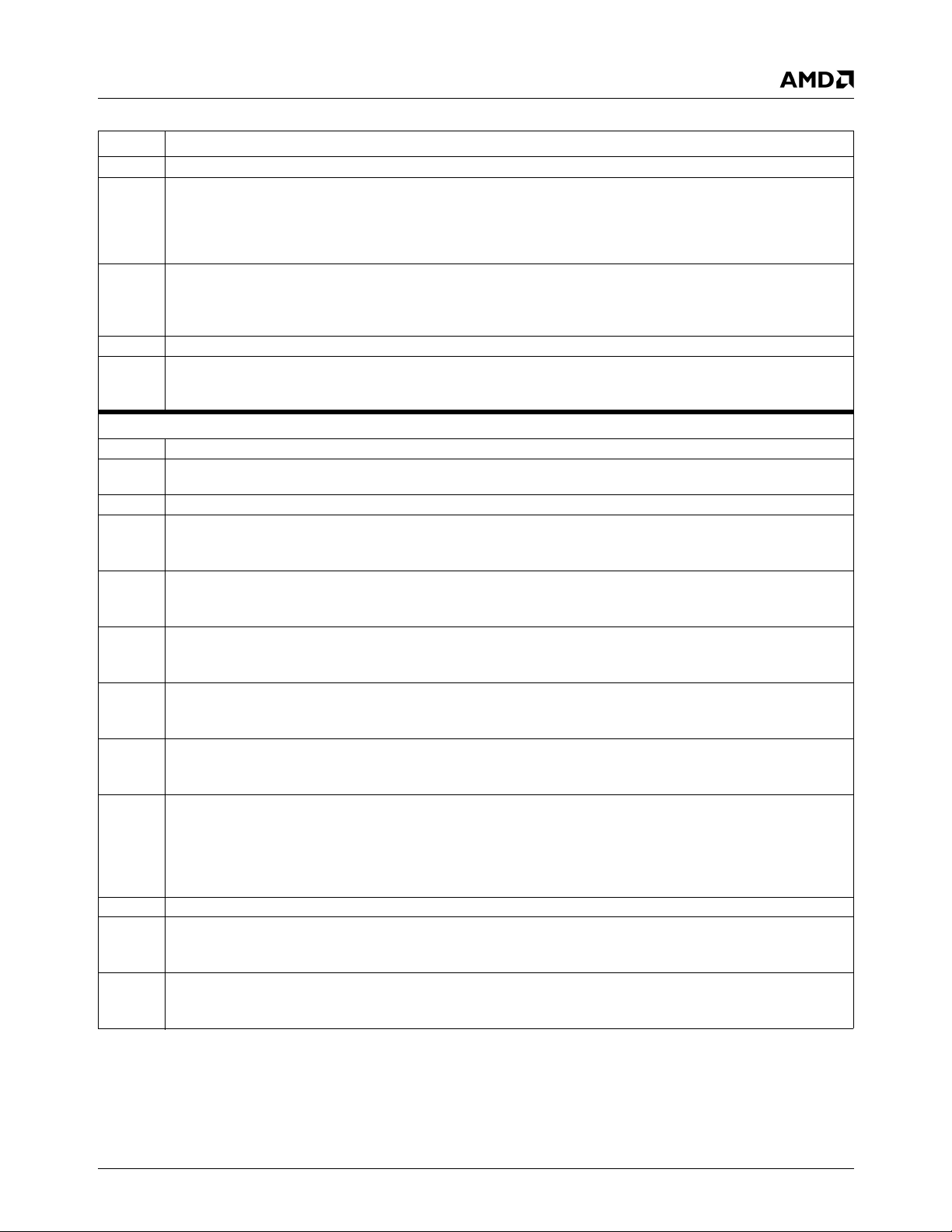

Figure 1-1 shows the relationships between the modules.

Video Processor

RTC

I/F

Video

Mixer

Clock & Reset Logic

TFT I/F

Parallel

Por t

ACB1

I/F

ACB2

I/F

UART1

UART2

UART3

& IR

Video

Scaling

Video Input Port (VIP)

Host Interface

SuperI/O

ISA Bus

Figure 1-1. Block Diagram

AMD Geode™ SC3200 Processor Data Book 13

Page 14

1.2 Features

32581C

Overview

General Features

■ 32-Bit x86 processor, up to 266 MHz, with MMX instruc-

tion set support

■ Memory controller with 64-bit SDRAM interface

■ 2D graphics accelerator

■ CCIR-656 video input port with direct video for full

screen display

■ PC/AT functionality

■ PCI bus controller

■ IDE interface, two channels

■ USB, three ports, OHCI (OpenHost Controller Interface)

version 1.0 compliant

■ Audio, AC97/AMC97 version 2.0 compliant

■ Virtual System Architecture (VSA) technology support

■ Power management, ACPI (Advanced Configuration

Power Interface) version 1.0 compliant

■ Package:

— BGU481 (481-Terminal Ball Grid Array Cavity Up)

GX1 Processor Module

■ CPU Core:

— 32-Bit x86, 266 MHz, with MMX compatible instruc-

tion set support

— 16 KB unified L1 cache

— Integrated FPU (Floating Point Unit)

— Re-entrant SMM (System Management Mode)

enhanced for VSA

■ 2D Graphics Accelerator:

— Accelerates BitBLTs, line draw and text

— Supports all 256 raster operations

— Supports transparent BLTs

— Runs at core clock frequency

■ Memory Controller:

— 64-Bit SDRAM interface

— 66 MHz to 100 MHz frequency range

— Direct interface with CPU/cache, display controller

and 2D graphic accelerator

— Supports clock suspend and power-down/

self-refresh

— Up to two banks of SDRAM (8 devices total) or one

SODIMM

■ Display Controller:

— Hardware graphics frame buffer compress/

decompress

— Hardware cursor, 32x32 pixels

Video Processor Module

■ Video Accelerator:

— Flexible video scaling support of up to 800%

(horizontally and vertically)

— Bilinear interpolation filters (with two taps, and eight

phases) to smooth output video

■ Video/Graphics Mixer:

— 8-bit value alpha blending

— Three blending windows with constant alpha value

— Color key

■ Video Input Port (VIP):

— Video capture or display

— CCIR-656 and VESA Video Interface Port v1.1

compliant

— Lock display timing to video input timing (GenLock)

— Able to transfer video data into main memory

— Direct video transfer for full screen display

— Separate memory location for VBI

■ TFT Interface:

— Direct connection to TFT panels

— 800x600 non-interlaced TFT @ 16 bpp graphics,

up to 85 Hz

— 1024x768 non-interlaced TFT @ 16 bpp graphics,

up to 75 Hz

— TFT on IDE: FPCLK max is 40 MHz

— TFT on Parallel Port: FPCLK max is 80 MHz

Core Logic Module

■ Audio Codec Interface:

— AC97/AMC97 (Rev. 2.0) codec interface

— Six DMA channels

■ PC/AT Functionality:

— Programmable Interrupt Controller (PIC),

8259A-equivalent

— Programmable Interval Timer (PIT), 8254-equivalent

— DMA Controller (DMAC), 8237-equivalent

■ Power Management:

— ACPI v1.0 compliant

— Sx state control of three power planes

— Cx/Sx state control of clocks and PLLs

— Thermal event input

— Wakeup event support:

– Three general-purpose events

– AC97 codec event

– UART2 RI# signal

– Infrared (IR) event

■ General Purpose I/Os (GPIOs):

— 27 multiplexed GPIO signals

■ Low Pin Count (LPC) Bus Interface:

— Specification v1.0 compatible

14 AMD Geode™ SC3200 Processor Data Book

Page 15

Overview

■

PCI Bus Interface:

— PCI v2.1 compliant with wakeup capability

— 32-Bit data path, up to 33 MHz

— Glueless interface for an external PCI device

— Fixed priority

— 3.3V signal support only

■ Sub-ISA Bus Interface:

— Up to 16 MB addressing

— Supports a chip select for ROM or Flash EPROM

boot device

— Supports either:

– M-Systems DiskOnChip DOC2000 Flash file

system

– NAND EEPROM

— Supports up to two chip selects for external I/O

devices

— 8-Bit (optional 16-bit) data bus width

— Shares balls with PCI signals

— Is not a subtractive agent

■ IDE Interface:

— Two IDE channels for up to four external IDE devices

— Supports ATA-33 synchronous DMA mode transfers,

up to 33 MB/s

32581C

Other Features

■ High-Resolution Timer:

— 32-Bit counter with 1 μs count interval

■ WATCHDOG Timer:

— Interfaces to INTR, SMI, Reset

■ Clocks:

— Input (external crystals):

– 32.768 KHz (internal clock oscillator)

– 27 MHz (internal clock oscillator)

—Output:

– AC97 clock (24.576 MHz)

– Memory controller clock (66 MHz to 100 MHz)

– PCI clock (33 MHz)

■ JTAG Testability:

— Bypass, Extest, Sample/Preload, IDcode, Clamp, HiZ

■ Voltages

— Internal logic: 266 or 233 MHz @ 1.8V

— Standby logic: 266 or 233 MHz @ 1.8V

— I/O: 3.3V

— Standby I/O: 3.3V

— Battery (if used): 3.0V

■ Universal Serial Bus (USB):

— USB OpenHCI v1.0 compliant

— Three ports

SuperI/O Module

■ Real-Time Clock (RTC):

— DS1287, MC146818 and PC87911 compatible

— Multi-century calendar

■ ACCESS.bus (ACB) Interface:

— Two ACB interface ports

■ Parallel Port:

— EPP 1.9 compliant

— IEEE 1284 ECP compliant, including level 2

■ Serial Port (UART):

— UART1, 16550A compatible (SIN, SOUT, BOUT

pins), used for SmartCard interface

— UART2, 16550A compatible

— Enhanced UART with fast Infrared (IR)

AMD Geode™ SC3200 Processor Data Book 15

Page 16

32581C

Overview

16 AMD Geode™ SC3200 Processor Data Book

Page 17

Architecture Overview 32581C

2.0Architecture Overview

2

As illustrated in Figure 1-1 on page 13, the SC3200 processor contains the following modules in one integrated

device:

• GX1 Module:

— Combines advanced CPU performance with MMX

support, fully accelerated 2D graphics, a 64-bit

synchronous DRAM (SDRAM) interface and a PCI

bus controller. Integrates GX1 silicon revision 8.1.1.

• Video Processor Module:

— A low-power TFT support module with a video input

port, and a hardware video accelerator for scaling,

filtering and color space conversion.

• Core Logic Module:

— Includes PC/AT functionality, an IDE interface, a

Universal Serial Bus (USB) interface, ACPI v1.0

compliant power management, and an audio codec

interface.

• SuperI/O Module:

— Includes two Serial Ports, an Infrared (IR) Port, a

Parallel Port, two ACCESS.bus interfaces, and a

Real-Time Clock (RTC).

2.1 GX1 Module

The GX1 processor (silicon revision 8.1.1) is the central

module of the SC3200. For detailed information regarding

the GX1 module, refer to the AMD Geode™ GX1 Proces-

sor Data Book and the AMD Geode™ GX1 Processor Silicon Revision 8.1.1 Specification Update documents.

The SC3200 processor’s device ID is contained in the GX1

module. Software can detect the revision by reading the

DIR0 and DIR1 Configuration registers (see Configuration

registers in the AMD Geode™ GX1 Processor Data Book).

The AMD Geode™ SC3200 Specification Update document contains the specific values.

2.1.1 Memory Controller

The GX1 module is connected to external SDRAM devices.

For more information see Section 3.4.2 "Memory Interface

Signals" on page 50, and the “Memory Controller” chapter

in the AMD Geode™ GX1 Processor Data Book.

There are some differences in the SC3200 processor’s

memory controller and the stand-alone GX1 processor’s

memory controller:

1) There is drive strength/slew control in the SC3200 that

is not in the GX1. The bits that control this function are

in the MC_MEM_CNTRL1 and MC_MEM_CNTRL2

registers. In the GX1 processor, these bits are marked

as reserved.

2) The SC3200 supports two banks of memory. The GX1

supports four banks of memory. In addition, the

SC3200 supports a maximum of eight devices and the

GX1 supports up to 32 devices. With this difference,

the MC_BANK_CFG register is different.

Table 2-1 summarizes the 32-bit registers contained in the

SC3200 processor’s memory controller. Table 2-2 gives

detailed register/bit formats.

AMD Geode™ SC3200 Processor Data Book 17

Page 18

32581C

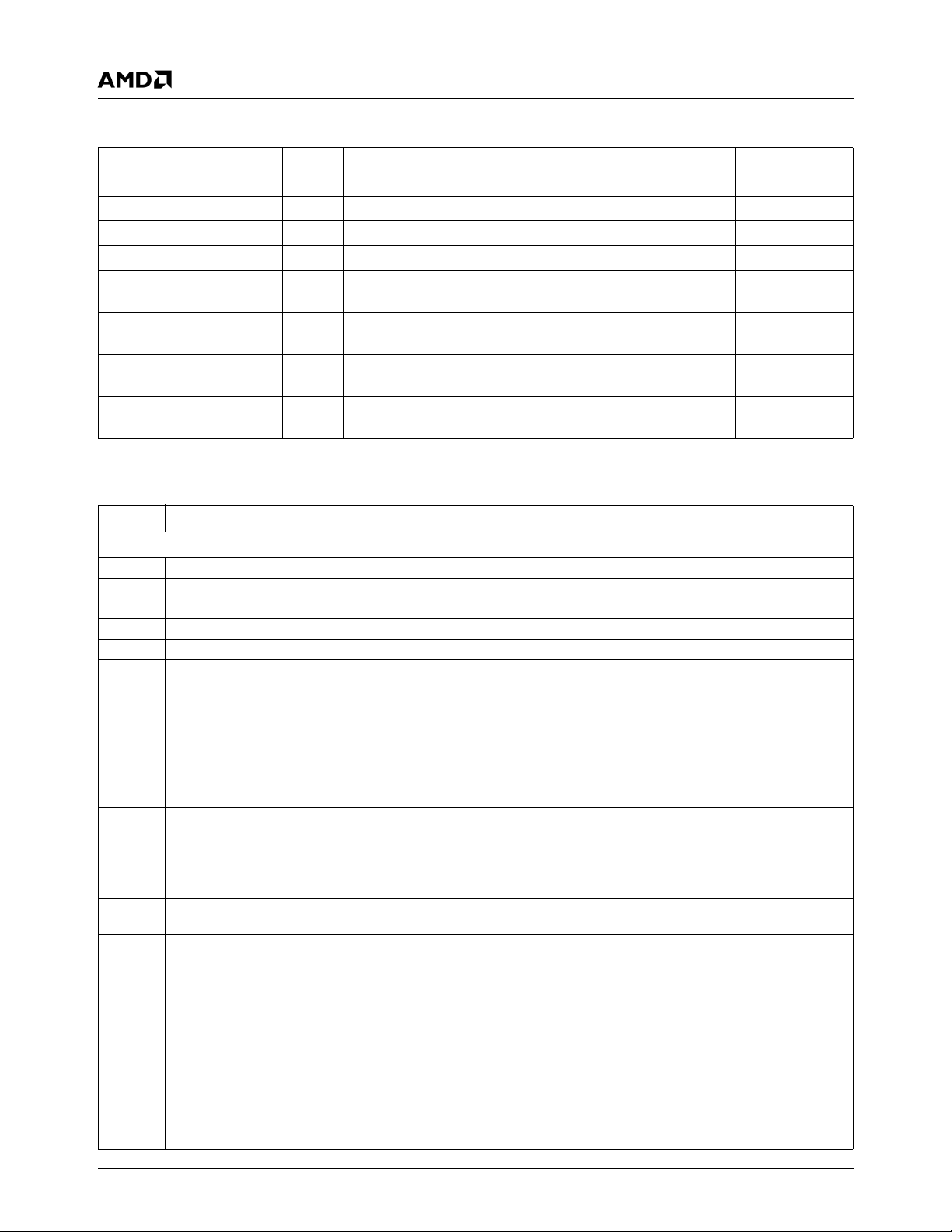

Table 2-1. SC3200 Memory Controller Register Summary

Architecture Overview

GX_BASE+

Memory Offset

Width

(Bits) Type Name/Function Reset Value

8400h-8403h 32 R/W MC_MEM_CNTRL1. Memory Controller Control Register 1 248C0040h

8404h-8407h 32 R/W MC_MEM_CNTRL2. Memory Controller Control Register 2 00000801h

8408h-840Bh 32 R/W MC_BANK_CFG. Memory Controller Bank Configuration 41104110h

840Ch-840Fh 32 R/W MC_SYNC_TIM1. Memory Controller Synchronous Timing

2A733225h

Register 1

8414h-8417h 32 R/W MC_GBASE_ADD. Memory Controller Graphics Base

00000000h

Address Register

8418h-841Bh 32 R/W MC_DR_ADD. Memory Controller Dirty RAM Address

00000000h

Register

841Ch-841Fh 32 R/W MC_DR_ACC. Memory Controller Dirty RAM Access

0000000xh

Register

Table 2-2. SC3200 Memory Controller Registers

Bit Description

GX_BASE+ 8400h-8403h MC_MEM_CNTRL1 (R/W) Reset Value: 248C0040h

31:30 MDCTL (MD[63:0] Drive Strength). 11 is strongest, 00 is weakest.

29 RSVD (Reserved) Write as 0.

28:27 MABACTL (MA[12:0] and BA[1:0] Drive Strength). 11 is strongest, 00 is weakest.

26 RSVD (Reserved). Write as 0.

25:24 MEMCTL (RASA#, CASA#, WEA#, CS[1:0]#, CKEA, DQM[7:0] Drive Strength). 11 is strongest, 00 is weakest.

23:22 RSVD (Reserved). Write as 0.

21 RSVD (Reserved). Must be written as 0. Wait state on the X-Bus x_data during read cycles - for debug only.

20:18 SDCLKRATE (SDRAM Clock Ratio). Selects SDRAM clock ratio.

000: Reserved 100: ÷ 3.5

001: ÷ 2 101: ÷ 4

010: ÷ 2.5 110: ÷ 4.5

011: ÷ 3 (Default) 111: ÷ 5

Ratio does not take effect until the SDCLKSTRT bit (bit 17 of this register) transitions from 0 to 1.

17 SDCLKSTRT (Start SDCLK). Start operating SDCLK using the new ratio and shift value (selected in bits [20:18] of this reg-

ister).

0: Clear.

1: Enable.

This bit must transition from zero (written to zero) to one (written to one) in order to start SDCLK or to change the shift value.

16:8 RFSHRATE (Refresh Interval). This field determines the number of processor core clocks multiplied by 64 between refresh

cycles to the DRAM. By default, the refresh interval is 00h. Refresh is turned off by default.

7:6 RFSHSTAG (Refresh Staggering). This field determines number of clocks between the RFSH commands to each of the

four banks during refresh cycles:

00: 0 SDRAM clocks

01: 1 SDRAM clocks (Default)

10: 2 SDRAM clocks

11: 4 SDRAM clocks

Staggering is used to help reduce power spikes during refresh by refreshing one bank at a time. If only one bank is installed,

this field must be written as 00.

5 2CLKADDR (Two Clock Address Setup). Assert memory address for one extra clock before CS# is asserted.

0: Disable.

1: Enable.

This can be used to compensate for address setup at high frequencies and/or high loads.

18 AMD Geode™ SC3200 Processor Data Book

Page 19

Architecture Overview

32581C

Table 2-2. SC3200 Memory Controller Registers (Continued)

Bit Description

4 RFSHTST (Test Refresh). This bit, when set high, generates a refresh request. This bit is only used for testing purposes.

3 XBUSARB (X-Bus Round Robin). When round robin is enabled, processor, graphics pipeline, and low priority display con-

troller requests are arbitrated at the same priority level. When disabled, processor requests are arbitrated at a higher priority

level. High priority Display Controller requests always have the highest arbitration priority.

0: Disable.

1: Enable round robin.

2 SMM_MAP (SMM Region Mapping). Maps the SMM memory region at GX_BASE+400000 to physical address A0000 to

BFFFF in SDRAM.

0: Disable.

1: Enable.

1 RSVD (Reserved). Write as 0.

0 SDRAMPRG (Program SDRAM). When this bit is set, the memory controller will program the SDRAM MRS register using

LTMODE in MC_SYNC_TIM1.

This bit must transition from zero (written to zero) to one (written to one) in order to program the SDRAM devices.

GX_BASE+8404h-8407h MC_MEM_CNTRL2 (R/W) Reset Value: 00000801h

31:14 RSVD (Reserved). Write as 0.

13:12 SDCLKCTL (SDCLK High Drive/Slew Control). Controls the high drive and slew rate of SDCLK[3:0] and SDCLK_OUT.

11 is strongest, 00 is weakest.

11 RSVD (Reserved). Write as 0.

10 SDCLKOMSK# (Enable SDCLK_OUT). Turns on the output.

0: Enable.

1: Disable.

9 SDCLK3MSK# (Enable SDCLK3). Turns on the output.

0: Enable.

1: Disable.

8 SDCLK2MSK# (Enable SDCLK2). Turns on the output.

0: Enable.

1: Disable.

7 SDCLK1MSK# (Enable SDCLK1). Turns on the output. 0

0: Enable.

1: Disable.

6 SDCLK0MSK# (Enable SDCLK0). Turns on the output.

0: Enable.

1: Disable.

5:3 SHFTSDCLK (Shift SDCLK). This function allows shifting SDCLK to meet SDRAM setup and hold time requirements. The

shift function will not take effect until the SDCLKSTRT bit (bit 17 of MC_MEM_CNTRL1) transitions from 0 to 1:

000: No shift 100: Shift 2 core clocks

001: Shift 0.5 core clock 101: Shift 2.5 core clocks

010: Shift 1 core clock 110: Shift 3 core clocks

011: Shift 1.5 core clock 111: Reserved

2 RSVD (Reserved). Write as 0.

1 RD (Read Data Phase). Selects if read data is latched one or two core clock after the rising edge of SDCLK.

0: 1 Core clock.

1: 2 Core clocks.

0 FSTRDMSK (Fast Read Mask). Do not allow core reads to bypass the request FIFO.

0: Disable.

1: Enable.

AMD Geode™ SC3200 Processor Data Book 19

Page 20

32581C

Architecture Overview

Table 2-2. SC3200 Memory Controller Registers (Continued)

Bit Description

GX_BASE+8408h-840Bh MC_BANK_CFG (R/W) Reset Value: 41104110h

31:16 RSVD (Reserved). Write as 0070h

15 RSVD (Reserved). Write as 0.

14 SODIMM_MOD_BNK (SODIMM Module Banks - Banks 0 and 1). Selects number of module banks installed per SODIMM

for SODIMM:

0: 1 Module bank (Bank 0 only)

1: 2 Module banks (Bank 0 and 1)

13 RSVD (Reserved). Write as 0.

12 SODIMM_COMP_BNK (SODIMM Component Banks - Banks 0 and 1). Selects the number of component banks per

module bank for SODIMM:

0: 2 Component banks

1: 4 Component banks

Banks 0 and 1 must have the same number of component banks.

11 RSVD (Reserved). Write as 0.

10:8 SODIMM_SZ (SODIMM Size - Banks 0 and 1). Selects the size of SODIMM:

000: 4 MB 010: 16 MB 100: 64 MB 110: 256 MB

001: 8 MB 011: 32 MB 101: 128 MB 111: 512 MB

This size is the total of both banks 0 and 1. Also, banks 0 and 1 must be the same size.

7 RSVD (Reserved). Write as 0.

6:4 SODIMM_PG_SZ (SODIMM Page Size - Banks 0 and 1). Selects the page size of SODIMM:

000: 1 KB 010: 4 KB 1xx: 16 KB

001: 2 KB 011: 8 KB 111: SODIMM not installed

Both banks 0 and 1 must have the same page size.

3:0 RSVD (Reserved). Write as 0.

GX_BASE+840Ch-840Fh MC_SYNC_TIM1 (R/W) Reset Value: 2A733225h

31 RSVD (Reserved). Write as 0.

30:28 LTMODE (CAS Latency). CAS latency is the delay, in SDRAM clock cycles, between the registration of a read command

27:24 RC (RFSH to RFSH/ACT Command Period, tRC). Minimum number of SDRAM clock between RFSH and RFSH/ACT

23:20 RAS (ACT to PRE Command Period, tRAS). Minimum number of SDRAM clocks between ACT and PRE commands:

18:16 RP (PRE to ACT Command Period, tRP). Minimum number of SDRAM clocks between PRE and ACT commands:

14:12 RCD (Delay Time ACT to READ/WRT Command, tRCD). Minimum number of SDRAM clock between ACT and READ/

and the availability of the first piece of output data. This parameter significantly affects system performance. Optimal setting

should be used. If an SODIMM is used, BIOS can interrogate EEPROM across the ACCESS.bus interface to determine this

value:

000: Reserved 010: 2 CLK 100: 4 CLK 110: 6 CLK

001: Reserved 011: 3 CLK 101: 5 CLK 111: 7 CLK

This field will not take effect until SDRAMPRG (bit 0 of MC_MEM_CNTRL1) transitions from 0 to 1.

commands:

0000: Reserved 0100: 5 CLK 1000: 9 CLK 1100: 13 CLK

0001: 2 CLK 0101: 6 CLK 1001: 10 CLK 1101: 14 CLK

0010: 3 CLK 0110: 7 CLK 1010: 11 CLK 1110: 15 CLK

0011: 4 CLK 0111: 8 CLK 1011: 12 CLK 1111: 16 CLK

0000: Reserved 0100: 5 CLK 1000: 9 CLK 1100: 13 CLK

0001: 2 CLK 0101: 6 CLK 1001: 10 CLK 1101: 14 CLK

0010: 3 CLK 0110: 7 CLK 1010: 11 CLK 1110: 15 CLK

0011: 4 CLK 0111: 8 CLK 1011: 12 CLK 1111: 16 CLK

19 RSVD (Reserved). Write as 0.

000: Reserved 010: 2 CLK 100: 4 CLK 110: 6 CLK

001: 1 CLK 011: 3 CLK 101: 5 CLK 111: 7 CLK

15 RSVD (Reserved). Write as 0.

WRT commands. This parameter significantly affects system performance. Optimal setting should be used:

000: Reserved 010: 2 CLK 100: 4 CLK 110: 6 CLK

001: 1 CLK 011: 3 CLK 101: 5 CLK 111: 7 CLK

20 AMD Geode™ SC3200 Processor Data Book

Page 21

Architecture Overview

32581C

Table 2-2. SC3200 Memory Controller Registers (Continued)

Bit Description

11 RSVD (Reserved). Write as 0.

10:8 RRD (ACT(0) to ACT(1) Command Period, tRRD). Minimum number of SDRAM clocks between ACT and ACT command

to two different component banks within the same module bank. The memory controller does not perform back-to-back Activate commands to two different component banks without a READ or WRITE command between them. Hence, this field

should be written as 001.

7 RSVD (Reserved). Write as 0.

6:4 DPL (Data-in to PRE command period, tDPL). Minimum number of SDRAM clocks from the time the last write datum is

3:0 RSVD (Reserved). Leave unchanged. Always returns a 101h.

Note: Refer to the SDRAM manufacturer’s specification for more information on component banks.

GX_BASE+8414h-8417h MC_GBASE_ADD (R/W) Reset Value: 00000000h

31:18 RSVD (Reserved). Write as 0.

15:12 SEL (Select). This field is used for debug purposes only and should be left at zero for normal operation.

10:0 GBADD (Graphics Base Address). This field indicates the graphics memory base address, which is programmable on 512

GX_BASE+8418h-841Bh MC_DR_ADD (R/W) Reset Value: 00000000h

31:10 RSVD (Reserved). Write as 0.

9:0 DRADD (Dirty RAM Address). This field is the address index that is used to access the Dirty RAM with the MC_DR_ACC

GX_BASE+841Ch-841Fh MC_DR_ACC (R/W) Reset Value: 0000000xh

31:2 RSVD (Reserved). Write as 0.

sampled till the bank is precharged:

000: Reserved 010: 2 CLK 100: 4 CLK 110: 6 CLK

001: 1 CLK 011: 3 CLK 101: 5 CLK 111: 7 CLK

17 TE (Test Enable TEST[3:0]).

0: TEST[3:0] are driven low (normal operation).

1: TEST[3:0] pins are used to output test information

16 TECTL (Test Enable Shared Control Pins).

0: RASB#, CASB#, CKEB, WEB# (normal operation).

1: RASB#, CASB#, CKEB, WEB# are used to output test information

11 RSVD (Reserved). Write as 0.

KB boundaries. This field corresponds to address bits [29:19].

Note that BC_DRAM_TOP must be set to a value lower than the Graphics Base Address.

register. This field does not auto increment.

1 D (Dirty Bit). This bit is read/write accessible.

0 V (Valid Bit). This bit is read/write accessible.

AMD Geode™ SC3200 Processor Data Book 21

Page 22

32581C

Architecture Overview

2.1.2 Fast-PCI Bus

The GX1 module communicates with the Core Logic module via a Fast-PCI bus that can work at up to 66 MHz. The

Fast-PCI bus is internal for the SC3200 and is connected to

the General Configuration Block (see Section 4.0 on page

69 for details on the General Configuration Block).

This bus supports seven bus masters. The requests

(REQs) are fixed in priority. The seven bus masters in order

of priority are:

1) VIP

2) IDE Channel 0

3) IDE Channel 1

4) Audio

5) USB

6) External REQ0#

7) External REQ1#

2.1.3 Display

The GX1 module generates display timing, and controls

internal VSYNC and HSYNC signals of the Video Processor module.

The GX1 module interfaces with the Video Processor via a

video data bus and a graphics data bus.

• Video data. The GX1 module uses the core clock,

divided by 2 or 4 (typically 100 - 133 MHz). It drives the

video data using this clock. Internal signals VID_VAL

and VID_RDY are used as data-flow handshake signals

between the GX1 module and the Video Processor.

• Graphics data. The GX1 module uses the internal

signal DCLK, supplied by the PLL of the Video

Processor, to drive the 18-bit graphics-data bus of the

Video Processor. Each six bits of this bus define a

different color. Each of these 6-bit color definitions is

expanded (by adding two zero LSB lines) to form an 8bit bus, at the Video Processor.

For more information about the GX1 module’s interface to

the Video Processor, see the “Display Controller” chapter

in the AMD Geode™ GX1 Processor Data Book.

2.2 Video Processor Module

The Video Processor provides high resolution and graphics

for a TFT/DSTN interface. The following subsections provide a summary of how the Video Processor interfaces with

the other modules of the SC3200. For detailed information

about the Video Processor, see Section 7.0 "Video Processor Module" on page 309.

2.2.1 GX1 Module Interface

The Video Processor is connected to the GX1 module in

the following way:

• The Video Processor’s DOTCLK output signal is used as

the GX1 module’s DCLK input signal.

• The GX1 module’s PCLK output signal is used as the

GFXCLK input signal of the Video Processor.

2.2.2 Video Input Port

The Video Input Port (VIP) within the Video Processor contains a standard interface that is typically connected to a

media processor or TV encoder. The clock is supplied by

the externally connected device; typically at 27 MHz.

Video input can be sent to the GX1 module’s video frame

buffer (Capture Video mode) or can be used directly (Direct

Video mode).

2.2.3 Core Logic Module Interface

The Video Processor interfaces to the Core Logic module

for accessing PCI function configuration registers.

2.3 Core Logic Module

The Core Logic module is described in detail in Section 6.0

"Core Logic Module" on page 139.

The Core Logic module is connected to the Fast-PCI bus. It

uses signal AD28 as the IDSEL for all PCI configuration

functions except for USB which uses AD29.

2.3.1 Other Core Logic Module Interfaces

The following interfaces of the Core Logic module are

implemented via external balls of the SC3200. Each interface is listed below with a reference to the descriptions of

the relevant balls.

• IDE: See Section 3.4.9 "IDE Interface Signals" on page

58.

• AC97: See Section 3.4.14 "AC97 Audio Interface

Signals" on page 63.

• PCI: See Section 3.4.6 "PCI Bus Interface Signals" on

page 53.

• USB: See Section 3.4.10 "Universal Serial Bus (USB)

Interface Signals" on page 59. The USB function uses

signal AD29 as the IDSEL for PCI configuration.

• LPC: See Section 3.4.8 "Low Pin Count (LPC) Bus Interface Signals" on page 58.

22 AMD Geode™ SC3200 Processor Data Book

Page 23

Architecture Overview

32581C

• Sub-ISA: See Section 3.4.7 "Sub-ISA Interface Signals"

on page 57, Section 6.2.5 "Sub-ISA Bus Interface" on

page 145, and Section 4.2 "Multiplexing, Interrupt Selection, and Base Address Registers" on page 70

• GPIO: See Section 3.4.16 "GPIO Interface Signals" on

page 65.

• More detailed information about each of these interfaces

is provided in Section 6.2 "Module Architecture" on page

140.

• Super/IO Block Interfaces: See Section 4.2 "Multiplexing, Interrupt Selection, and Base Address Registers" on page 70, Section 3.4.5 "ACCESS.bus Interface

Signals" on page 52, Section 3.4.13 "Fast Infrared (IR)

Port Interface Signals" on page 62, and Section 3.4.12

"Parallel Port Interface Signals" on page 61.