Page 1

AMD SB600

Register Reference

(Public Version)

Technical Reference Manual

©2008 Advanced Micro Devices, Inc.

Manual

P/N: 46155_sb600_rrg_pub_3.03

Rev. 3.03

Page 2

Trademarks

AMD, the AMD Arrow logo, Athlon, and combinations thereof, A TI, ATI logo, Radeon, and Crossfire are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Microsoft and Windows are registered trademarks and Windows Vista is trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Disclaimer

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with

respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time

without notice. No license, w hether express, implied, aris ing by estoppel, or otherwi se, to any intellectual property rights are granted by this publication. Except as set forth

in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including,

but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any in tellectual property right.

AMD's products are not designed, intended, authorize d or warranted for use as components in systems intended for surgical implant into the body, or in other applications

intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe

property or environmental damage may occur. AMD reserves the righ t to discontinue or make changes to its products at any time without notice.

© 2008 Advanced Micro Devices, Inc. All rights reserved.

Page 3

Table of Contents

1 Introduction .............................................................................................................7

1.1 About this Manual........................................................................................................................... 7

1.2 Nomenclature and Conventions..................................................................................................... 7

1.2.1 Recent Updates .....................................................................................................................................7

1.2.2 Numeric Representations....................................................................................................................... 7

1.2.3 Register Description...............................................................................................................................7

1.3 Features of the SB600 ................................................................................................................... 9

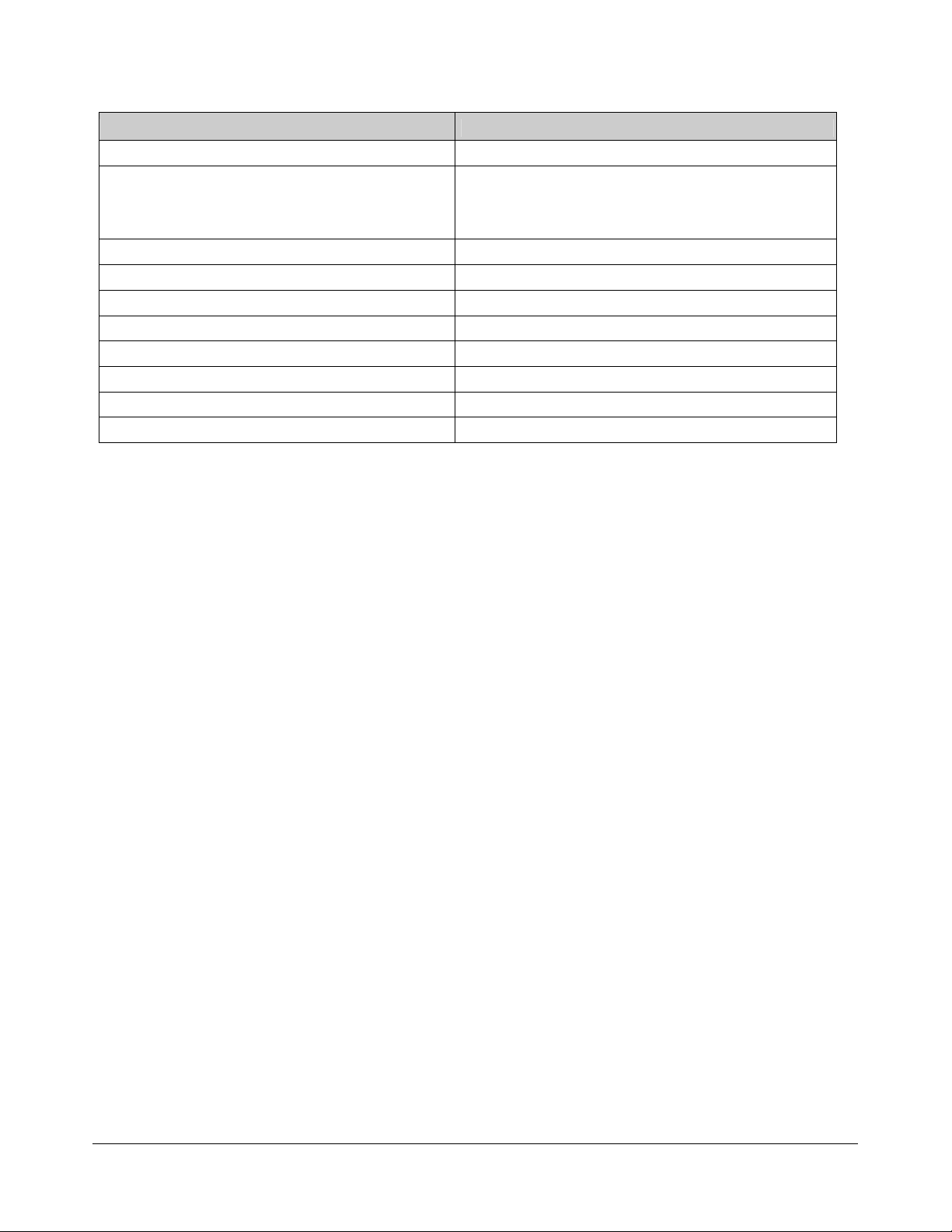

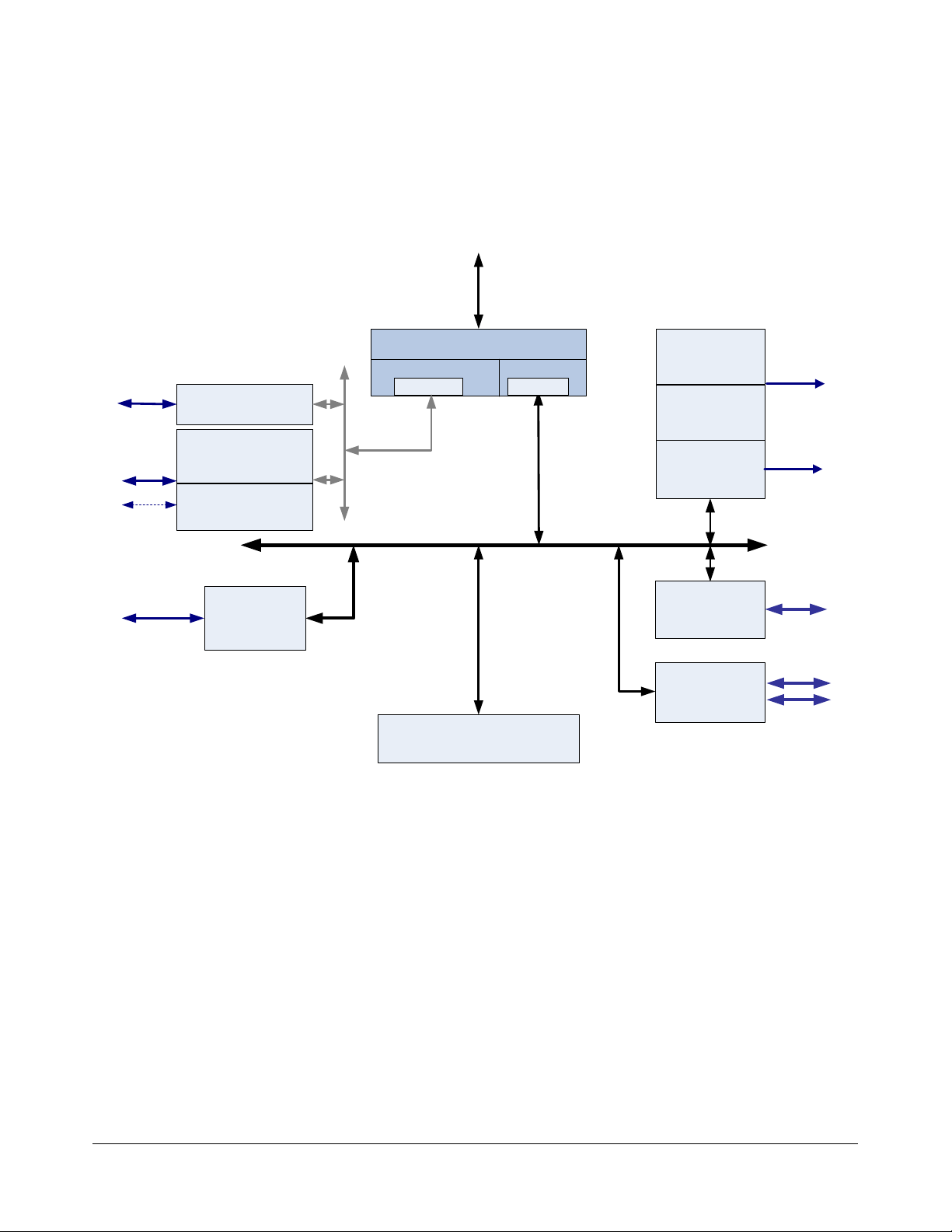

1.4 Block Diagrams ............................................................................................................................ 11

2 Register Descriptions: PCI Devices.....................................................................13

2.1 SATA Registers (Device 18, Function 0) ..................................................................................... 13

2.1.1 PCI Configuration Space...................................................................................................................... 13

2.1.2 BAR0/BAR2/BAR1/BAR3 Registers (SATA I/O Register for IDE mode)..............................................24

2.1.3 BAR4 Registers (SATA I/O Register for IDE mode).............................................................................24

2.1.4 BAR5 Registers....................................................................................................................................25

2.1.4.1 Generic Host Control ............................................................................................................................................ 25

2.1.4.2 Port Registers (One Set Per Port) ........................................................................................................................ 31

2.2 OCHI USB 1.1 and EHCI USB 2.0 Controllers ............................................................................ 44

2.2.1 OHCI Registers (Device 19, Function 0, 1, 2, 3, 4) ..............................................................................44

2.2.1.1 PCI Configuration Registers (PCI_Reg) ............................................................................................................... 44

2.2.1.2 OHCI Operational Registers (MEM_Reg)............................................................................................................. 51

2.2.2 USB Legacy Keyboard Operation ........................................................................................................66

2.2.2.1 Overview............................................................................................................................................................... 66

2.2.2.2 System Requirements .......................................................................................................................................... 67

2.2.2.3 Programming Interface ......................................................................................................................................... 68

2.2.3 EHCI Registers (Device 19, Function 5) ..............................................................................................70

2.2.3.1 PCI Configuration Registers ................................................................................................................................. 70

2.2.3.2 Host Controller Capability Registers (MEM_Reg) ................................................................................................ 79

2.2.3.3 Host Controller Operational Registers (EOR_Reg) .............................................................................................. 82

2.2.3.4 USB2.0 Debug Port Registers .............................................................................................................................. 92

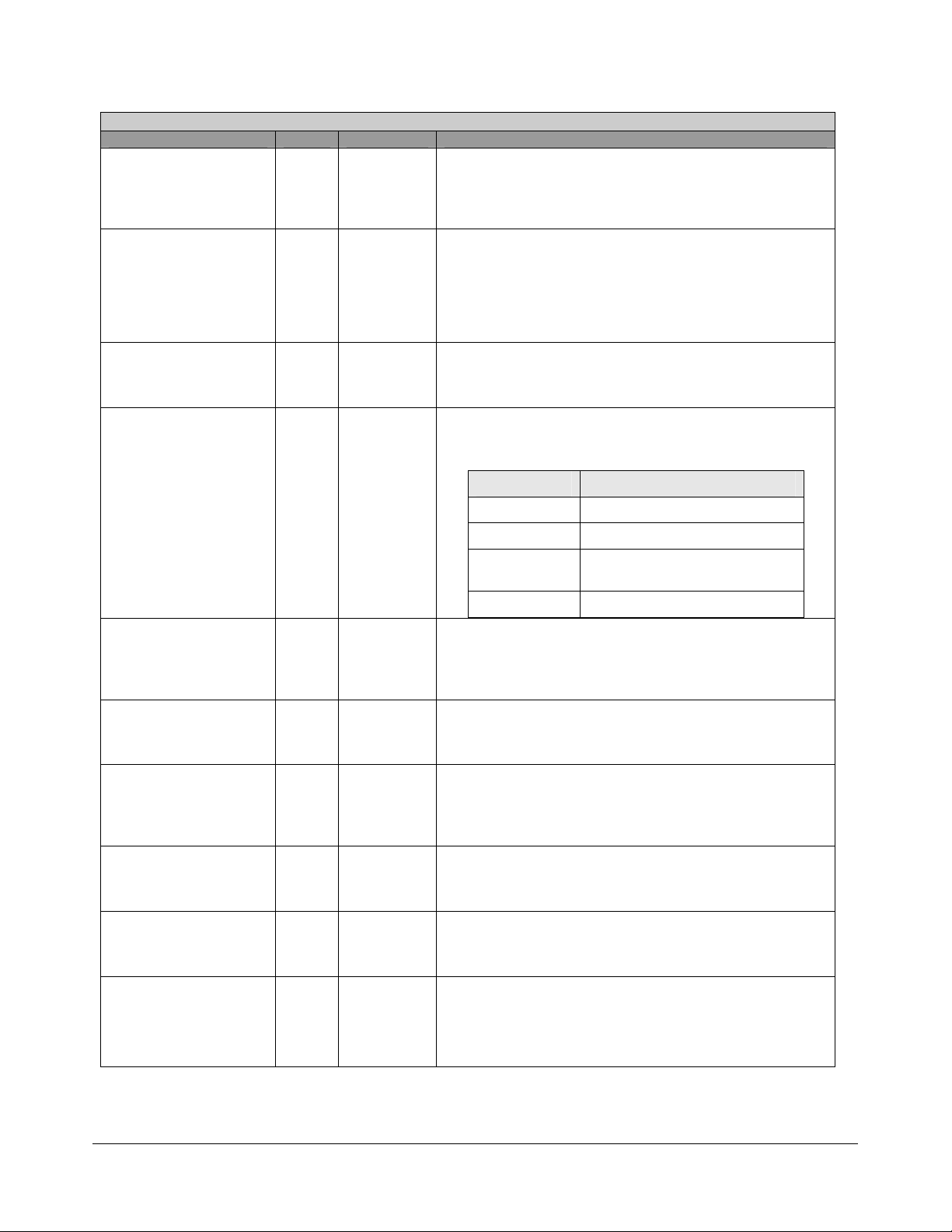

2.3 SMBus Module and ACPI Block (Device 20, Function 0) ............................................................ 96

2.3.1 PCI Configuration Registers and Extended Registers..........................................................................97

2.3.1.1 PCIE Configuration Registers............................................................................................................................... 97

2.3.1.2 Extended Registers ............................................................................................................................................ 120

2.3.2 SMBus Registers ...............................................................................................................................123

2.3.3 Legacy ISA and ACPI Controller........................................................................................................ 126

2.3.3.1 Legacy Block Registers ...................................................................................................................................... 126

2.3.3.1.1 IO-Mapped Control Registers.....................................................................................................................126

2.3.3.1.2 Client Management Registers (Accessed through C50h and C51h) .........................................................137

2.3.3.1.3 System Reset Register (IO CF9)................................................................................................................139

2.3.3.2 Power Management (PM) Registers................................................................................................................... 139

2.3.3.3 ACPI Registers ................................................................................................................................................... 176

2.3.4 WatchDogTimer Registers .................................................................................................................181

2.3.5 ASF SM bus Host Interface Registers................................................................................................182

2.4 IDE Controller (Device 20, Function 1) ...................................................................................... 186

2.4.1 PCI Configuration Registers............................................................................................................... 186

2.4.2 IDE I/O Registers ...............................................................................................................................195

©2008 Advanced Micro Devices, Inc.

Table of Contents

AMD SB600 Register Reference Manual Proprietary Page 3

Page 4

2.5

AC ’97 Controller Functional Descriptions ................................................................................. 198

2.5.1 Audio Registers (Device 20, Function 5)............................................................................................198

2.5.1.1 PCI Configuration Registers ............................................................................................................................... 198

2.5.1.2 Audio Memory Mapped Registers ...................................................................................................................... 203

2.5.2 Modem Registers (Device 20, Function 6) .........................................................................................213

2.5.2.1 PCI Configuration Registers ............................................................................................................................... 213

2.5.2.2 Modem Memory Mapped Registers.................................................................................................................... 218

2.6 HD Audio Controllers Registers ................................................................................................. 227

2.6.1 HD Audio Controller PCI Configuration Space Registers (Device 20 Function 2) .............................. 227

2.6.2 HD Audio Controller Memory Mapped Registers ...............................................................................232

3 Register Descriptions: PCI Bridges...................................................................249

3.1 LPC ISA Bridge (Device 20, Function 3).................................................................................... 249

3.1.1 Programming Interface.......................................................................................................................249

3.1.2 PCI Configuration Registers............................................................................................................... 249

3.1.3 SPI ROM Controller Registers ...........................................................................................................260

3.1.4 Features of the LPC Block .................................................................................................................264

3.2 Host PCI Bridge Registers (Device 20, Function 4)................................................................... 265

4 Register Descriptions: General Purpose Functions/Interrupt Controllers/Support

Function Pins.............................................................................................................277

4.1 GPIO/GPOC............................................................................................................................... 277

4.1.1 GPIO .................................................................................................................................................. 277

4.1.2 GPOC ................................................................................................................................................282

4.2 GEVENT/GPE/GPM/ExtEvent ................................................................................................... 283

4.2.1 GEVENT as GPIO..............................................................................................................................283

4.2.2 General Purpose Event (GPE)...........................................................................................................283

4.2.3 GPM as GPIO ....................................................................................................................................286

4.2.3.1 GPM Pins as Input.............................................................................................................................................. 286

4.2.3.2 GPM pins as Output ........................................................................................................................................... 287

4.2.4 ExtEvent.............................................................................................................................................287

4.2.4.1 ExtEvent as GPIO............................................................................................................................................... 287

4.2.4.2 ExtEvent to Generate SMI# ................................................................................................................................ 287

4.3 THRMTRIP/TALERT.................................................................................................................. 288

4.3.1 Thermal Trip – THRMTRIP ................................................................................................................288

4.3.2 Temperature Alert – TALERT.............................................................................................................288

4.4 Real Time Clock (RTC) .............................................................................................................. 289

4.5 IOXAPIC Registers..................................................................................................................... 296

4.5.1 Direct Access Registers .....................................................................................................................296

4.5.2 Indirect Access Registers................................................................................................................... 297

Appendix A: AC97 Audio FAQs ...............................................................................299

Appendix B: Revision History..................................................................................300

©2008 Advanced Micro Devices, Inc.

AMD SB600 Register Reference Manual Proprietary Page 4

List of Figures

Page 5

List of Figures

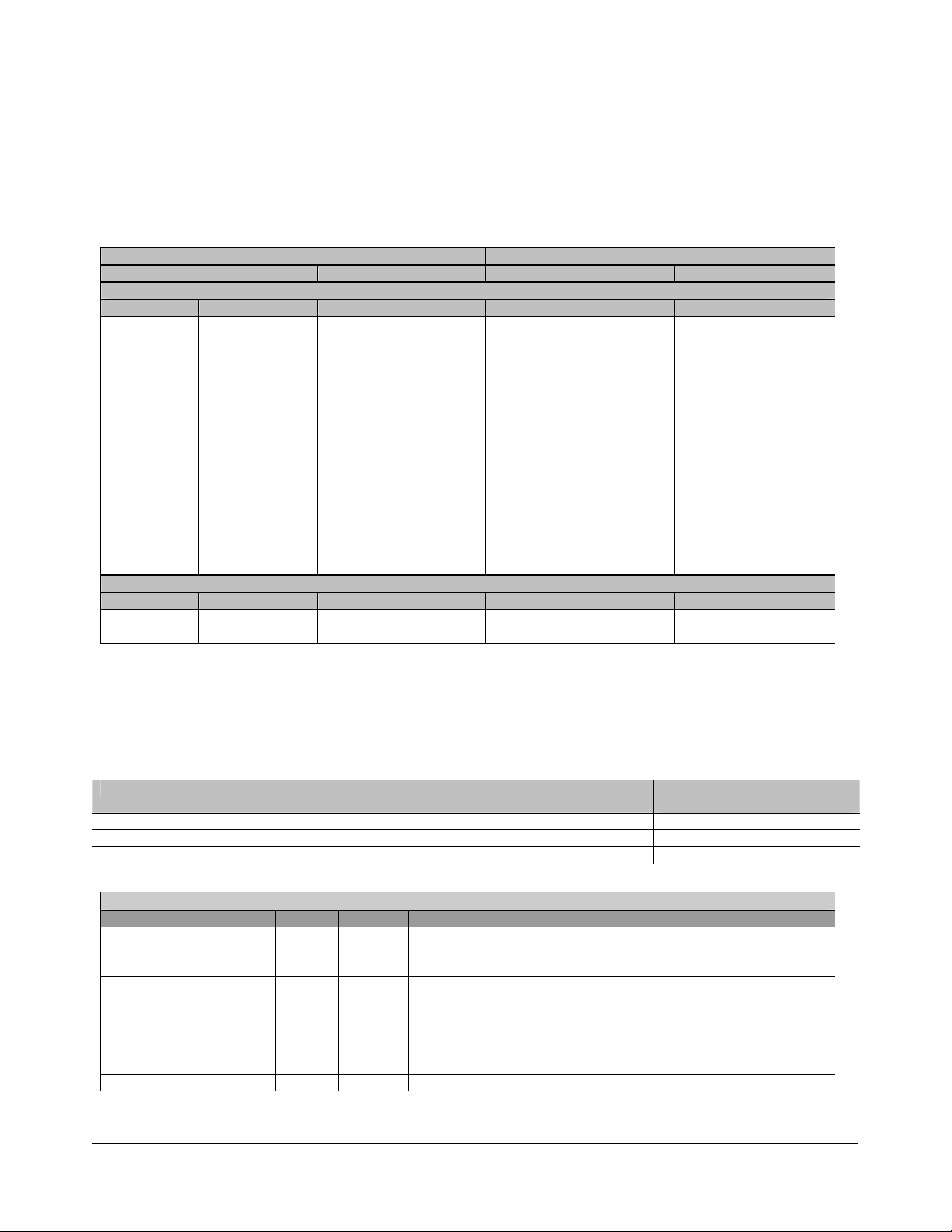

Figure 1 SB600 PCI Internal Devices ..........................................................................................................................11

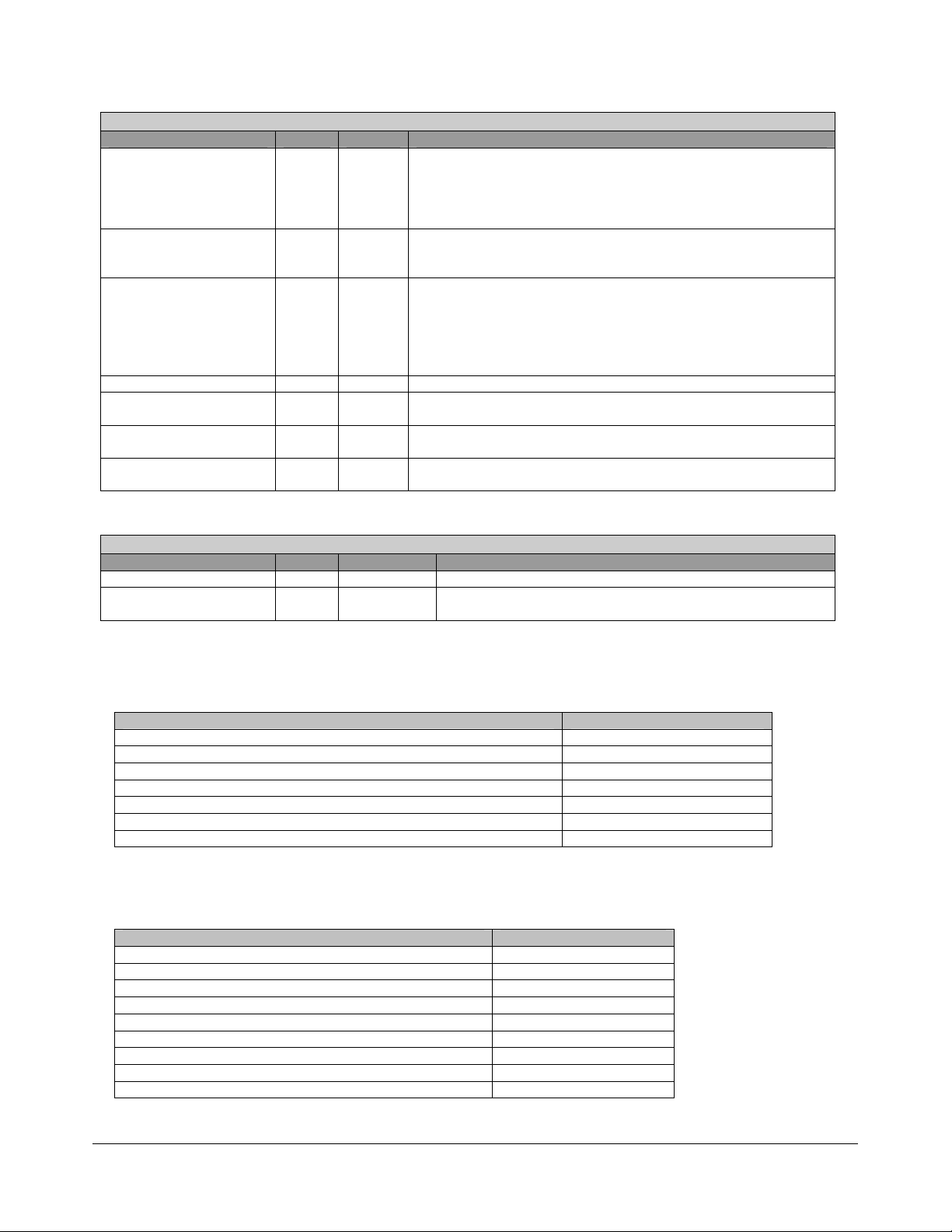

Figure 2 SB600 PCI Internal Devices and Major Function Blocks ...............................................................................12

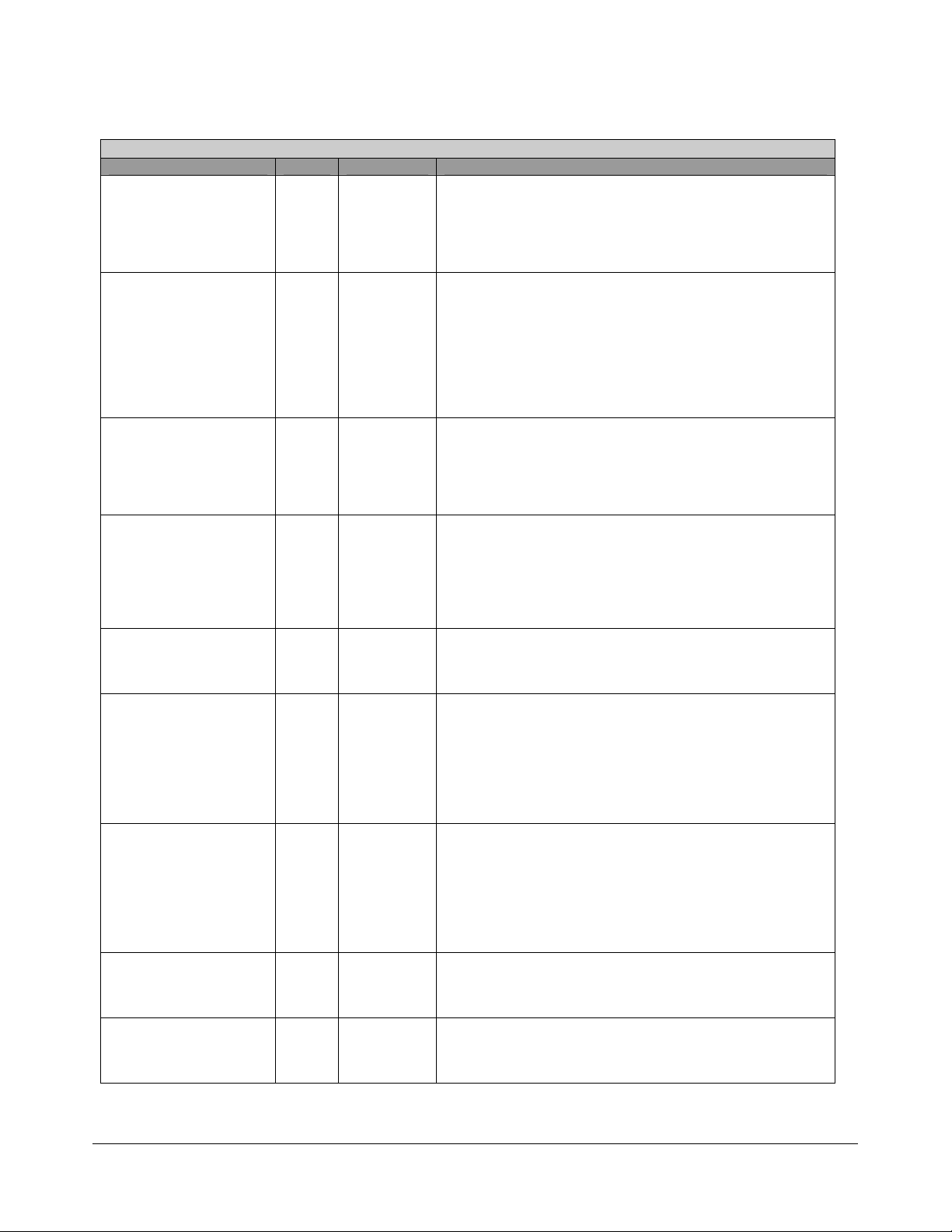

Figure 3 PCI Configuration Spaces for OHCI...............................................................................................................45

Figure 4 SMBus/ACPI PCI Configuration Space Function Block Association ..............................................................96

©2008 Advanced Micro Devices, Inc.

AMD SB600 Register Reference Manual Proprietary Page 5

List of Figures

Page 6

List of Tables

Table 1-1: Register Description Table Notation—Example ............................................................................................7

Table 2-1 HcRevision Register ....................................................................................................................................68

Table 2-2 Legacy Support Registers............................................................................................................................68

Table 2-3 Emulated Registers......................................................................................................................................68

Table 2-4 HceInput Registers ......................................................................................................................................69

Table 2-5 HceOutput Register .....................................................................................................................................69

Table 2-6 HceStatus Register ......................................................................................................................................69

Table 2-7 HceControl Register.....................................................................................................................................70

Table 2-8 IDE Device Registers Mapping ..................................................................................................................196

Table 3-1 PCI-to-PCI Bridge Configuration Registers Summary................................................................................265

Table 4-1: GPIO Pins.................................................................................................................................................277

Table 4-2: GPOC Pins ...............................................................................................................................................282

Table 4-3: GPE Pins ..................................................................................................................................................283

Table 4-4: ExtEvent Pins as GPIO.............................................................................................................................287

Table 4-5: ExtEvent Pins to Generate SMI# ..............................................................................................................287

Table 4-6: THRMTRIP Pin .........................................................................................................................................288

Table 4-7: TALERT# through GPE ............................................................................................................................288

Table 4-8: TALERT# to generate SMI#...................................................................................................................... 288

©2008 Advanced Micro Devices, Inc.

List of Tables

AMD SB600 Register Reference Manual Proprietary Page 6

Page 7

1 Introduction

1.1 About this Manual

This manual is a register reference guide for the AMD SB600 Southbridge. It integrates the key I/O,

communications, and audio features required in a state-of-the-art PC into a single device. It is specifically

designed to operate with AMD’s RADEON IGP Xpress family of integrated graphics processor products in

both desktop and mobile PCs.

1.2 Nomenclature and Conventions

1.2.1 Recent Updates

Updates recent to each revision are highlighted in red.

1.2.2 Numeric Representations

• Hexadecimal numbers are prefixed with “0x” or suffixed with “h,” whenever there is a possibility

of confusion. Other numbers are decimal.

• Registers (or fields) of an identical function are sometimes indicated by a single expression in

which the part of the signal name that changes is enclosed in square brackets. For example,

registers HOST_DATA0 through to HOST_DATA7 is represented by the single expression

HOST_DATA[7:0].

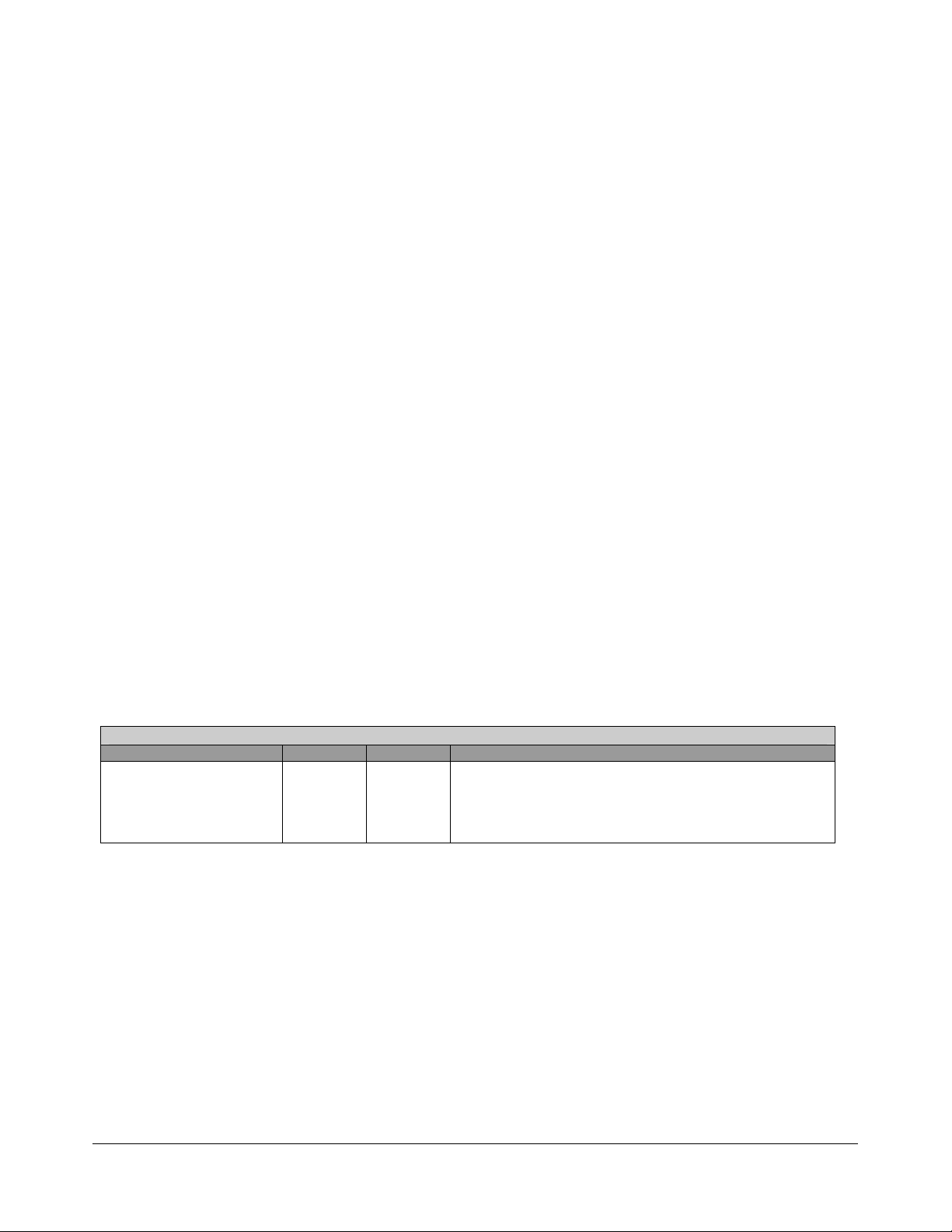

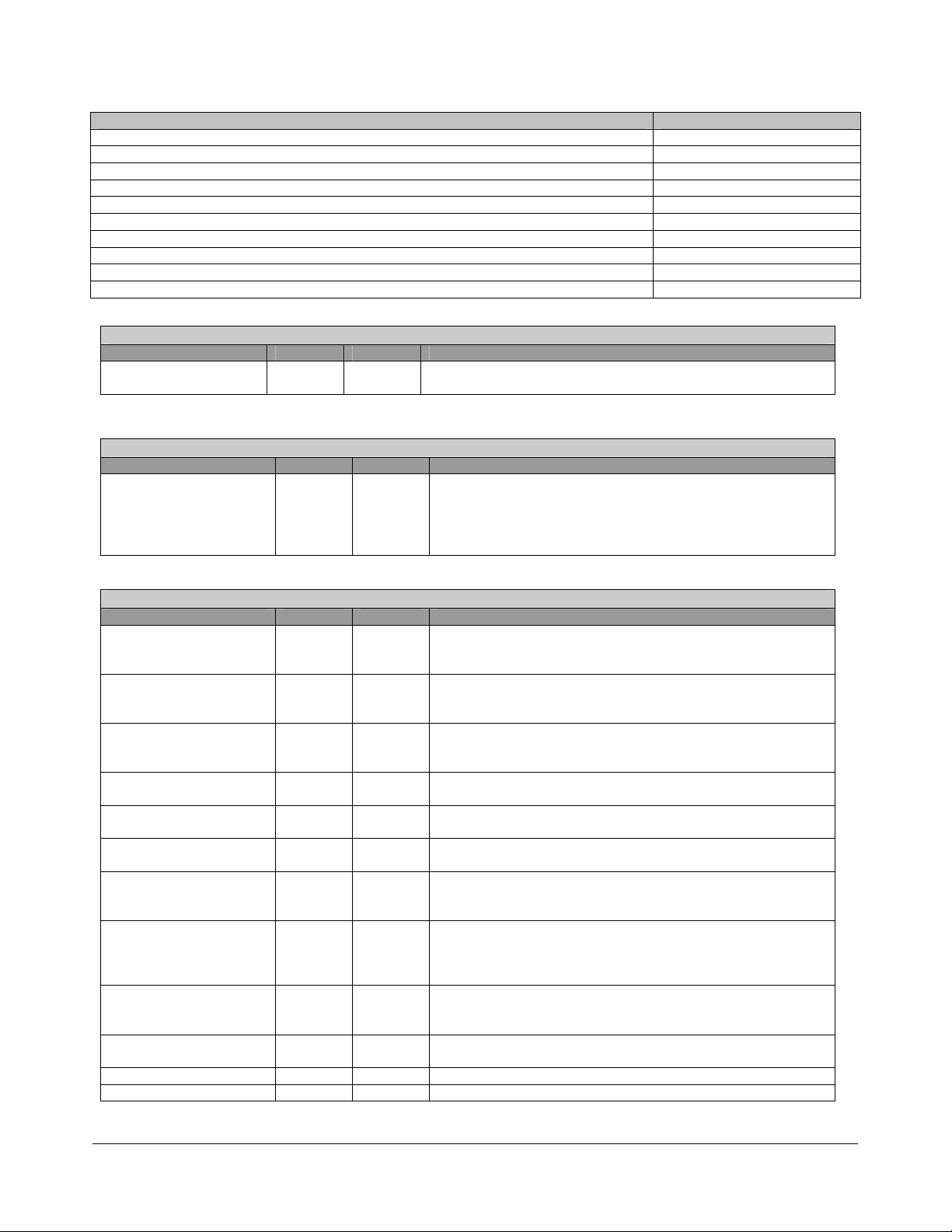

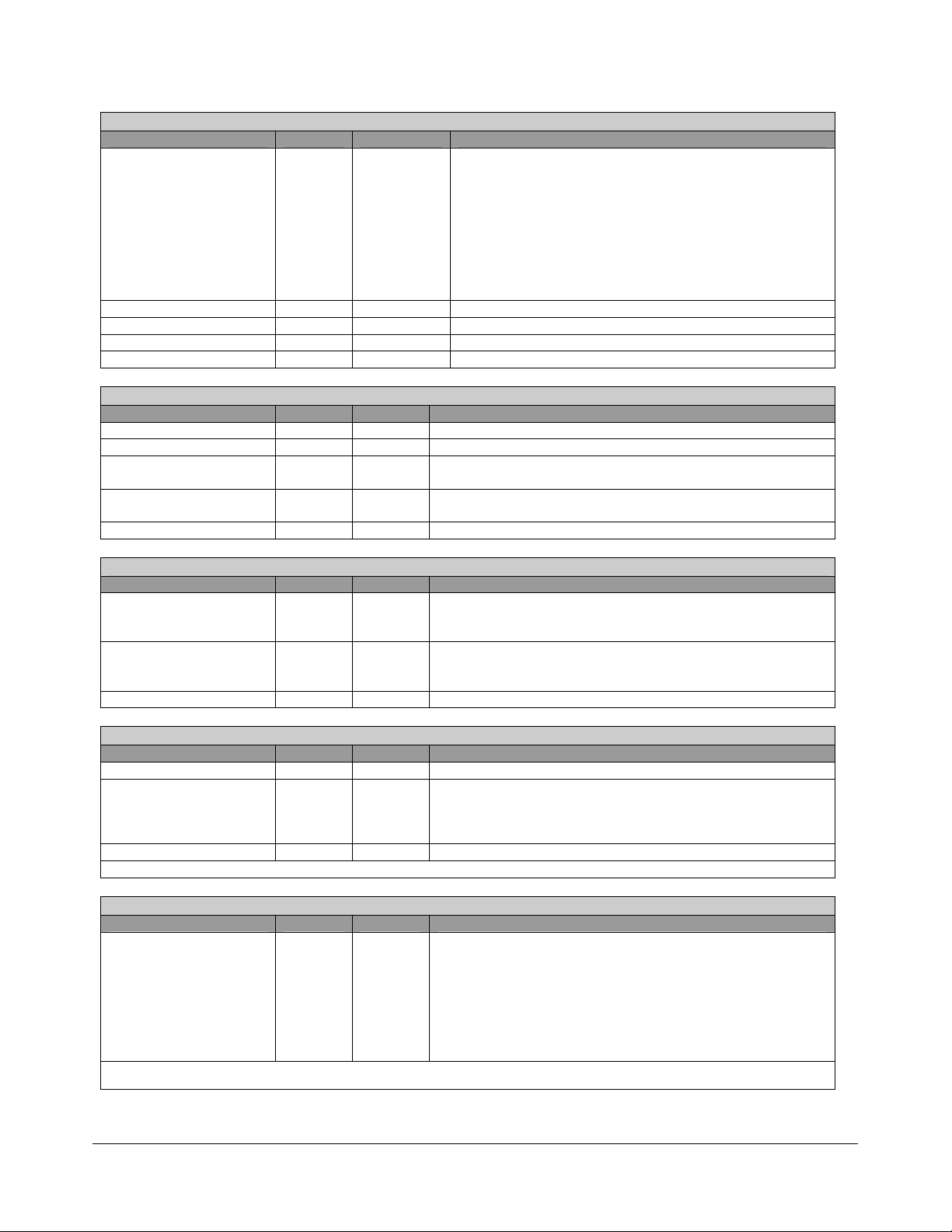

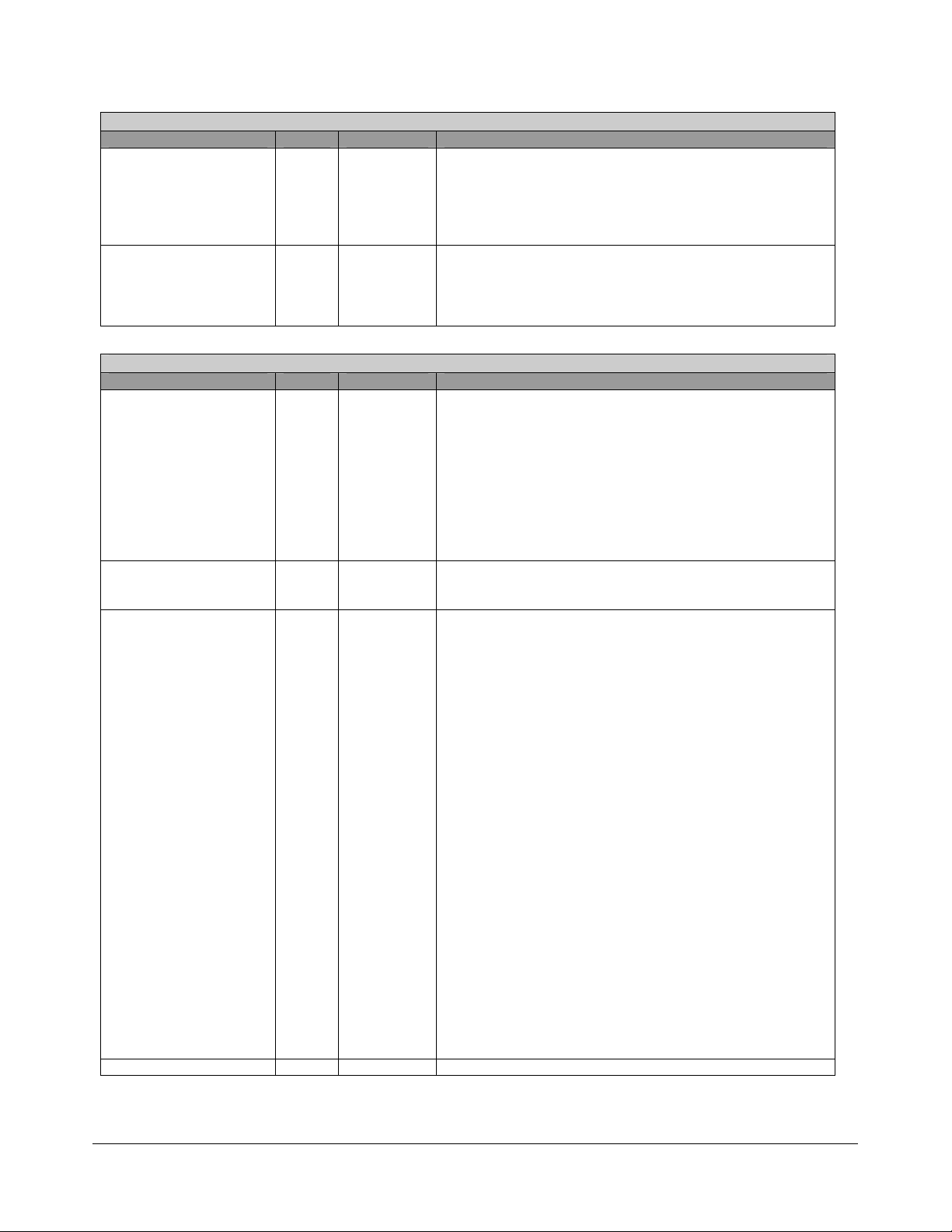

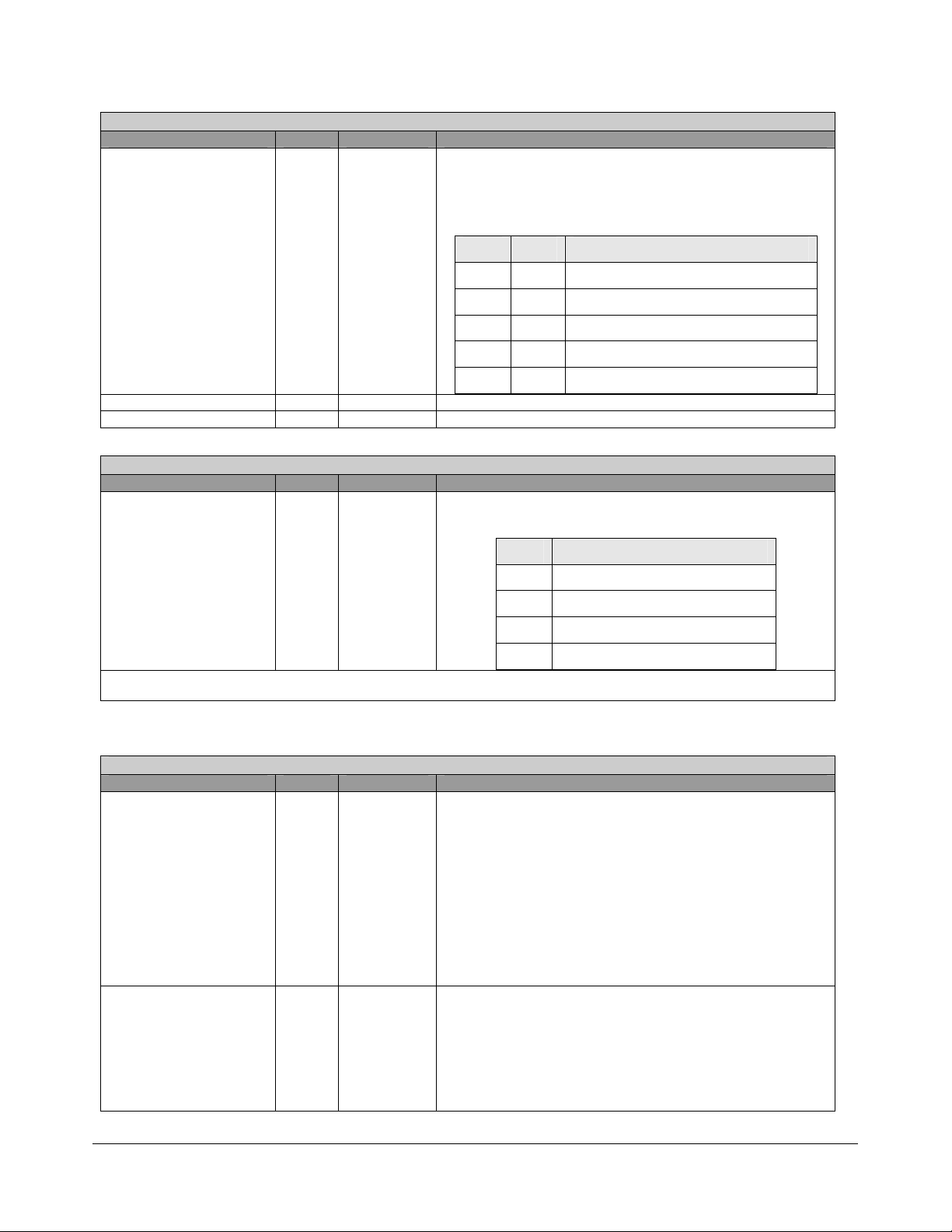

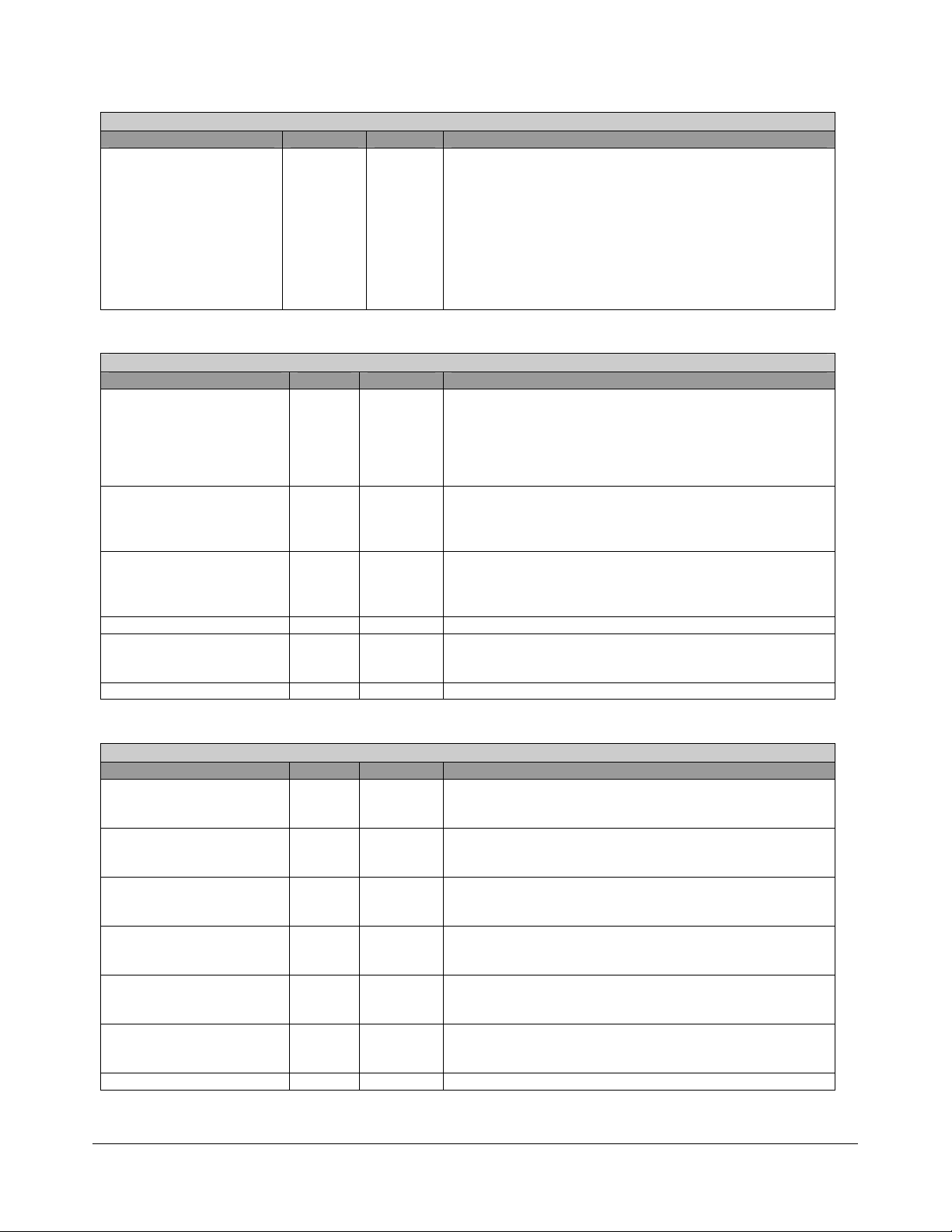

1.2.3 Register Description

All registers in this document are described with the format of the sample table below. All offsets are

in hexadecimal notation, while programmed bits are in either binomial or hexadecimal notation.

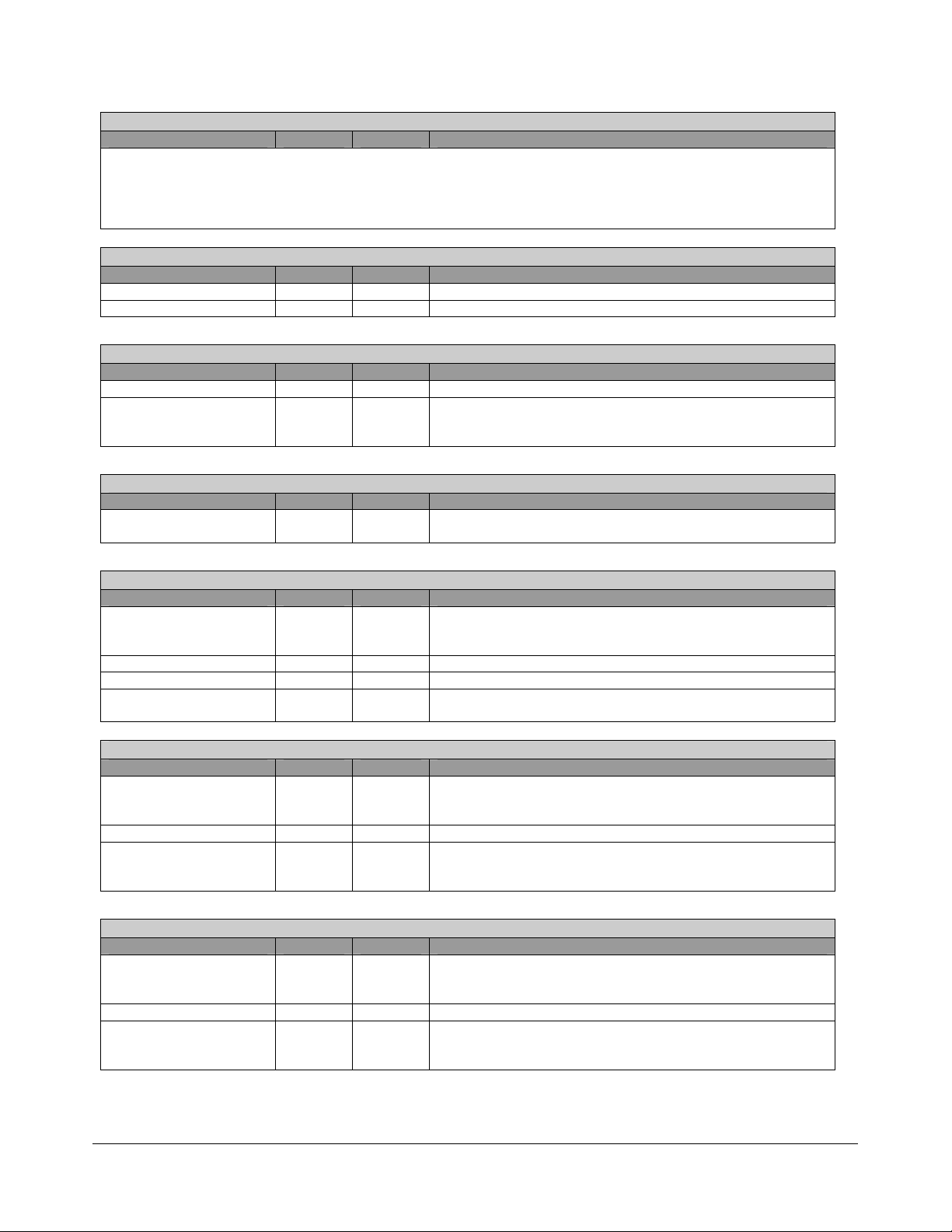

Table 1-1: Register Description Table Notation—Example

Latency Timer – RW – 8 bits – [Offset: 0Dh]

Field Name Bits Default Description

Latency Timer (R/W) 7:0 00h This bit field is used to specify the time in number of PCI

clocks, the SATA controller as a master is still allowed to

control the PCI bus after its GRANT_L is deasserted. The

lower three bits [0A:08] are hardwired to 0

time granularity of 8 clocks.

Latency Timer. Reset Value: 00h

h , resulting in a

©2008 Advanced Micro Devices, Inc.

AMD SB600 Register Reference Manual Proprietary Page 7

About this Manual

Page 8

Register Information Value/Content in the Example

Register name Latency Timer

Read / Write capability

R = Readable

W = Writable

RW = Readable and Writable

Register size 8 bits

Register address(es)* Offset: 0Dh

Field name Latency Timer (R/W)

Field position/size 7:0

Field default value 00h

Field description “This bit … 8 clocks.”

Field mirror information

Brief register description Latency Timer. Reset Value: 00h

* Note: There maybe more than one address; the convention used is as follows:

[aperName:offset] - single mapping, to one aperture/decode and one offset

[aperName1, aperName2, …, aperNameN:offset] - multiple mappings to different apertures/decodes but same

offset

[aperName:startOffset-endOffset] - mapped to an offset range in the same aperture/decode

RW

Warning: Do not attempt to modify values of registers or bit fields marked "Reserved." Doing so may cause

the system to behave in unexpected manners.

©2008 Advanced Micro Devices, Inc.

Nomenclature and Conventions

AMD SB600 Register Reference Manual Proprietary Page 8

Page 9

1.3 Features of the SB600

CPU Interface

Supports both Single and Dual core AMD

CPUs

Desktop: Athlon 64, Athlon 64 FX, Athlon

64 X2, Sempron, Opteron, dual-core

Opteron

Mobile: Athlon XP-M, Mobile Athlon 64,

Turion 64, Mobile Sempron

PCI Host Bus Controller

Supports PCI Rev. 2.3 specification

Supports PCI bus at 33MHz

Supports up to 6 bus master devices

Supports 40-bit addressing

Supports interrupt steering for plug-n-play

devices

Supports concurrent PCI operations

Supports hiding of PCI devices by

BIOS/hardware

Supports spread spectrum on PCI clocks

Supports serial interrupt on quiet and

continuous modes

DMA Controller

Two cascaded 8237 DMA controllers

Supports PC/PCI DMA

Supports LPC DMA

Supports type F DMA

LPC host bus controller

Supports LPC based super I/O and flash

devices

Supports two master/DMA devices

Supports TPM version 1.1/1.2 devices for

enhanced security

Supports SPI devices

SATA II AHCI Controller

Supports four SATA ports, complying with the

SATA 2.0 specification

USB controllers

5 OHCI and 1 EHCI Host controllers to

support 10 USB ports

All 10 ports are USB 1.1 (“Low Speed”, “Full

Speed”) and 2.0 (“High Speed”) compatible

Supports ACPI S1~S5

Supports legacy keyboard/mouse

Supports USB debug port

Supports port disable with individual control

SMBus Controller

SMBus Rev. 2.0 compliant

Support SMBALERT # signal / GPIO

Interrupt Controller

Supports IOAPIC/X-IO APIC mode for 24

channels of interrupts

Supports 8259 legacy mode for 15 interrupts

Supports programmable level/edge triggering

on each channels

Supports SATA II 3.0GHz PHY, with

backward compatibility with 1.5GHz

Supports RAID striping (RAID 0) across all 4

ports

Supports RAID mirroring (RAID 1) across all 4

ports

Supports RAID 10 (4 ports needed)

Supports both AHCI mode and IDE mode

Supports advanced power management with

ACHI mode

IDE Controller

Single PATA channel support

Supports PIO, Multi-word DMA, and Ultra

DMA 33/66/100/133 modes

32x32byte buffers on each channel for

buffering

Swap bay support by tri-state IDE signals

Supports Message Signaled Interrupt (MSI)

Integrated IDE series resistors

©2008 Advanced Micro Devices, Inc.

AMD SB600 Register Reference Manual Proprietary Page 9

Features of the SB600

Page 10

AC Link interface

Supports for both audio and modem codecs

Compliant with AC-97 codec Rev. 2.3

6/8 channel support on audio codec

Multiple functions for audio and modem

Codec operations

Bus master logic

Supports up to 3 codecs simultaneously

Supports SPDIF output

Separate bus from the HD audio

HD Audio

4 Independent output streams (DMA)

4 Independent input streams (DMA)

Up to 16 channels of audio output per stream

Supports up to 4 codecs

Up to 192kHz sample rate

Up to 32-bit per sample

Message Signaled Interrupt (MSI) capability

64-bit addressing capability for MSI

64-bit addressing capability for DMA bus

master

Unified Audio Architecture (UAA) compatible

HD Audio registers can be located anywhere

in the 64-bit address space

Timers

8254-compatible timer

Microsoft High Precision Event Timer (HPET)

ACPI power management timer

RTC (Real Time Clock)

256-byte battery-backed CMOS RAM

Hardware supported century rollover

RTC battery monitoring feature

Power Management

ACPI specification 2.0 compliant power

management schemes

Supports C2, C3, C4, ACPI states

Supports C1e and C3 pop-up

Supports S0, S1, S2, S3, S4, and S5

Wakeup events for S1, S2, S3, S4/S5

generated by:

Any GEVENT pin

Any GPM pin

USB

Power button

Internal RTC wakeup

SMI# event

Full support for On-Now™

Supports CPU SMM, generating SMI# signal

upon power management events

GPIO supports on external wake up events

Supports CLKRUN# on PCI power

management

Provides clock generator and CPU STPCLK#

control

Support for ASF

©2008 Advanced Micro Devices, Inc.

AMD SB600 Register Reference Manual Proprietary Page 10

Features of the SB600

Page 11

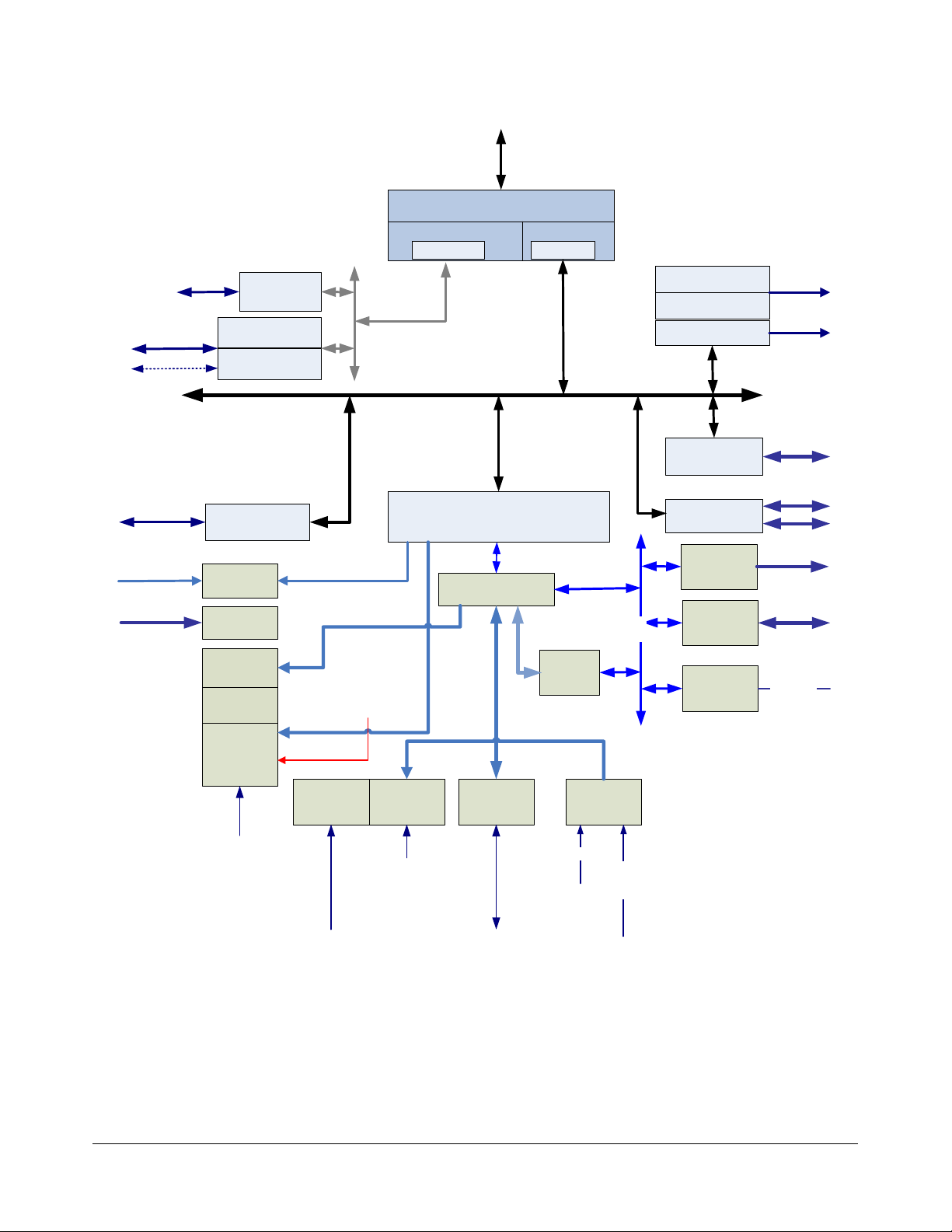

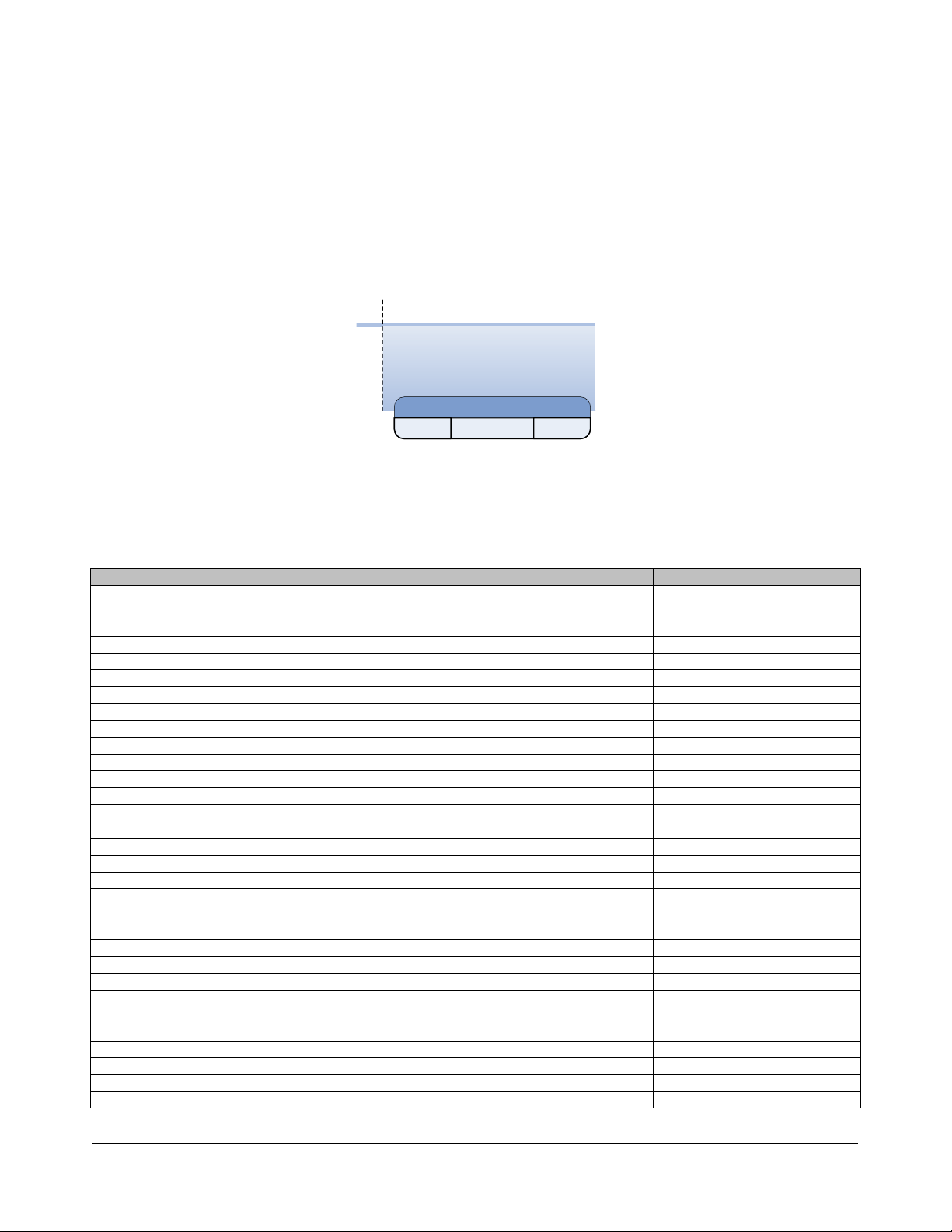

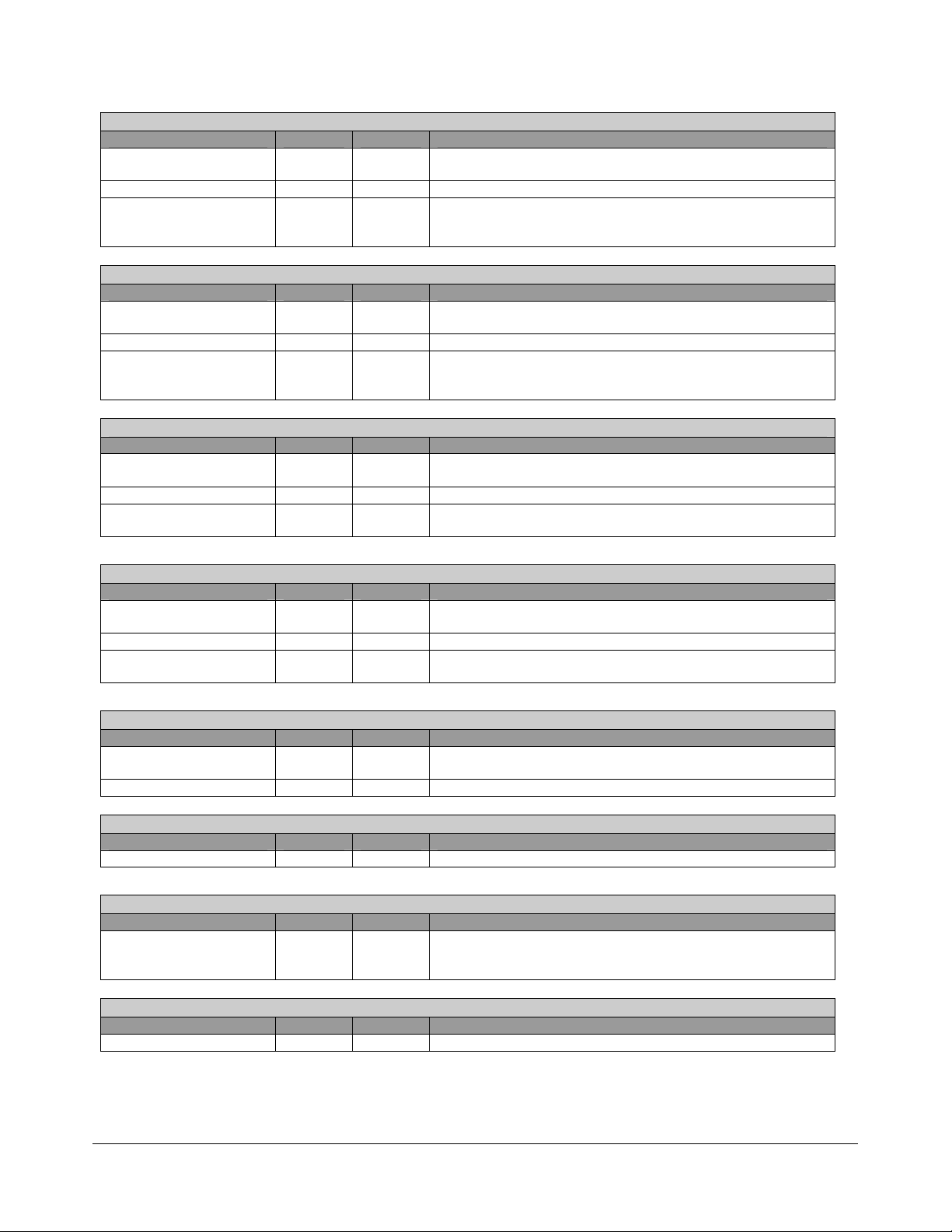

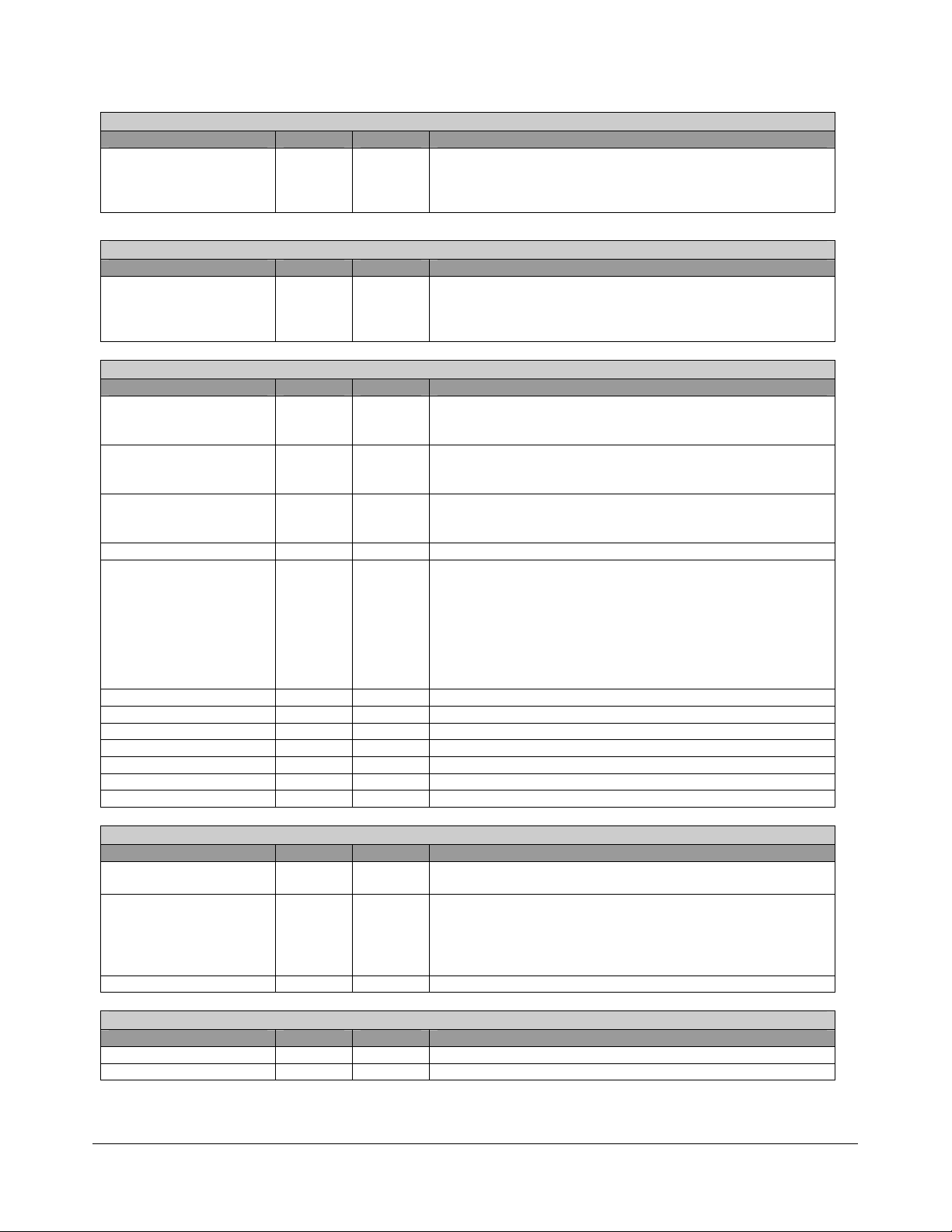

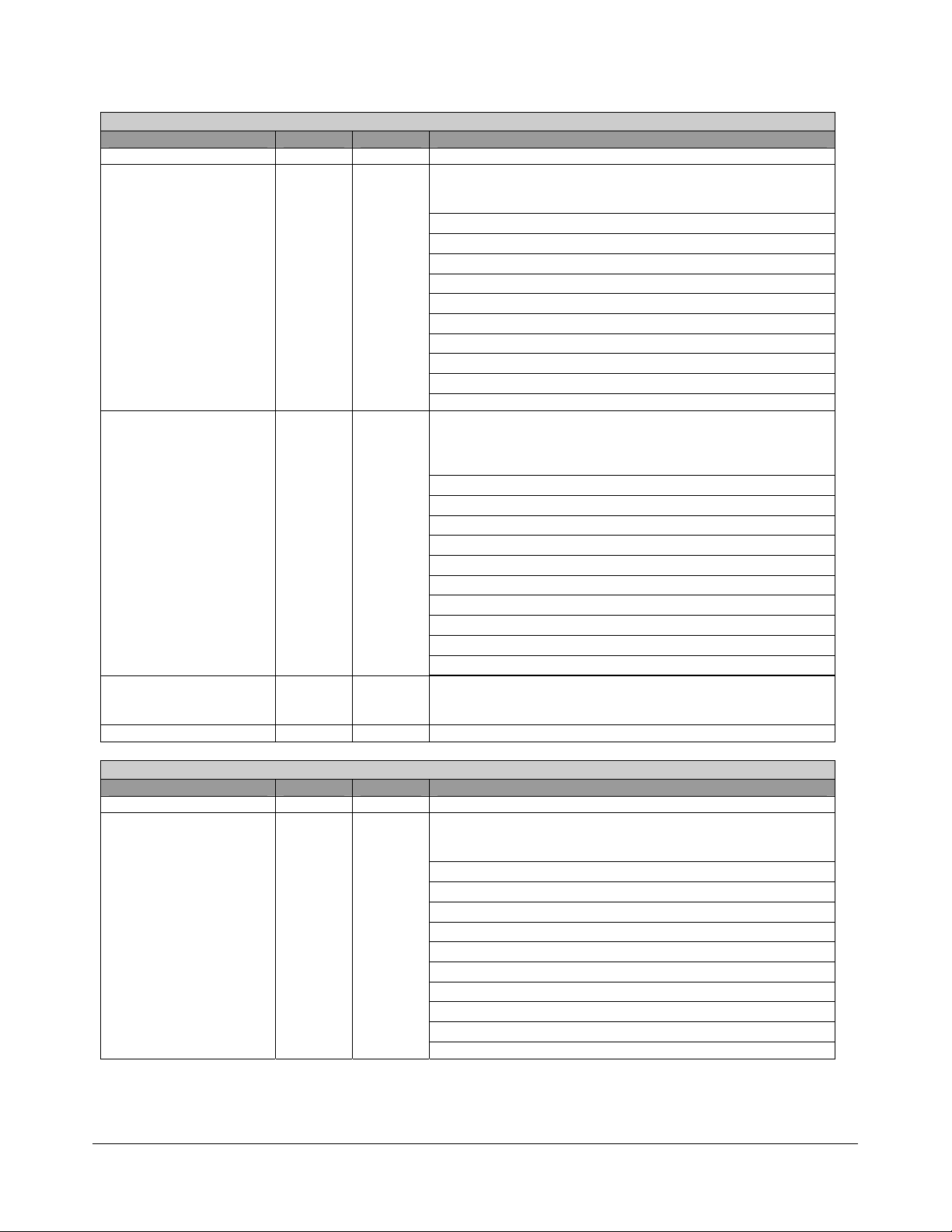

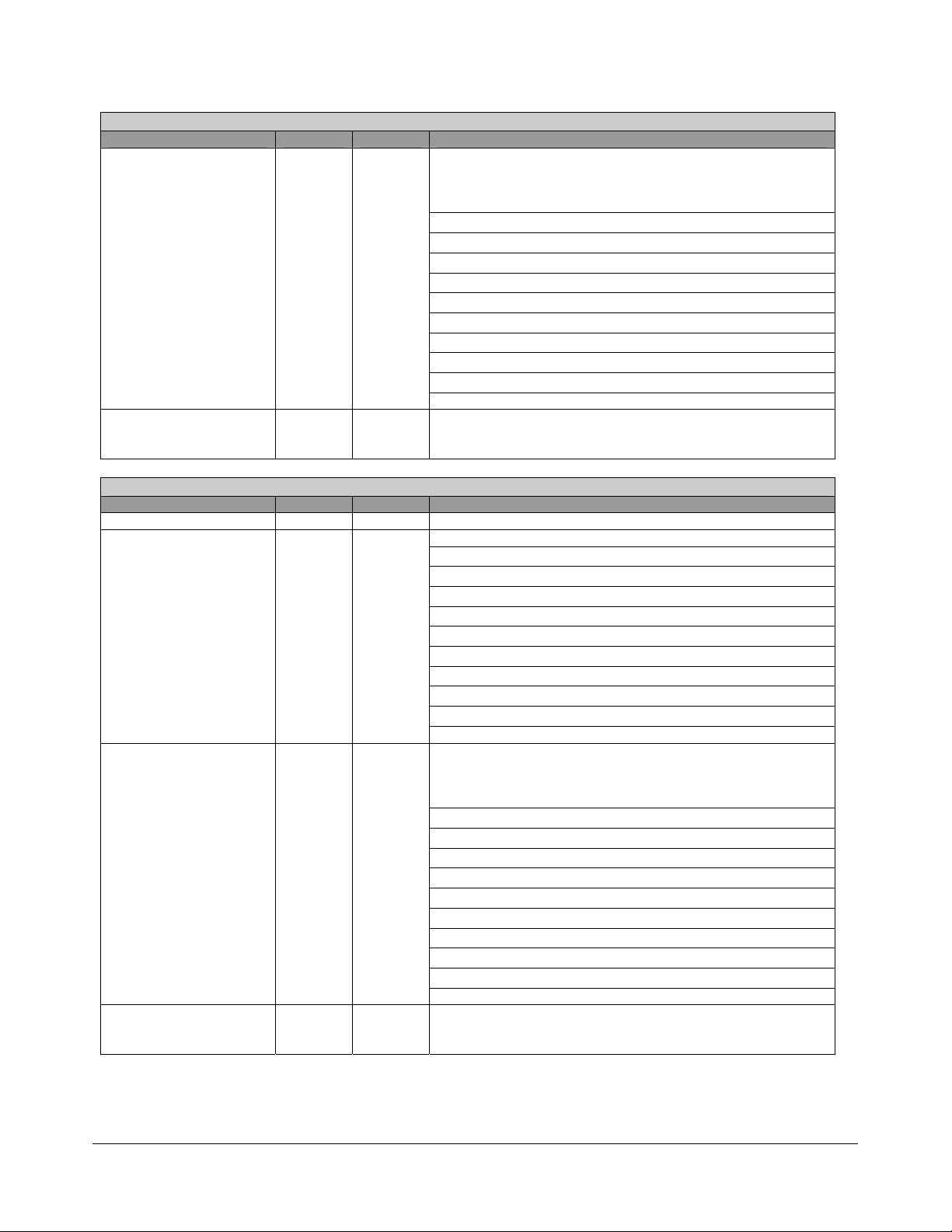

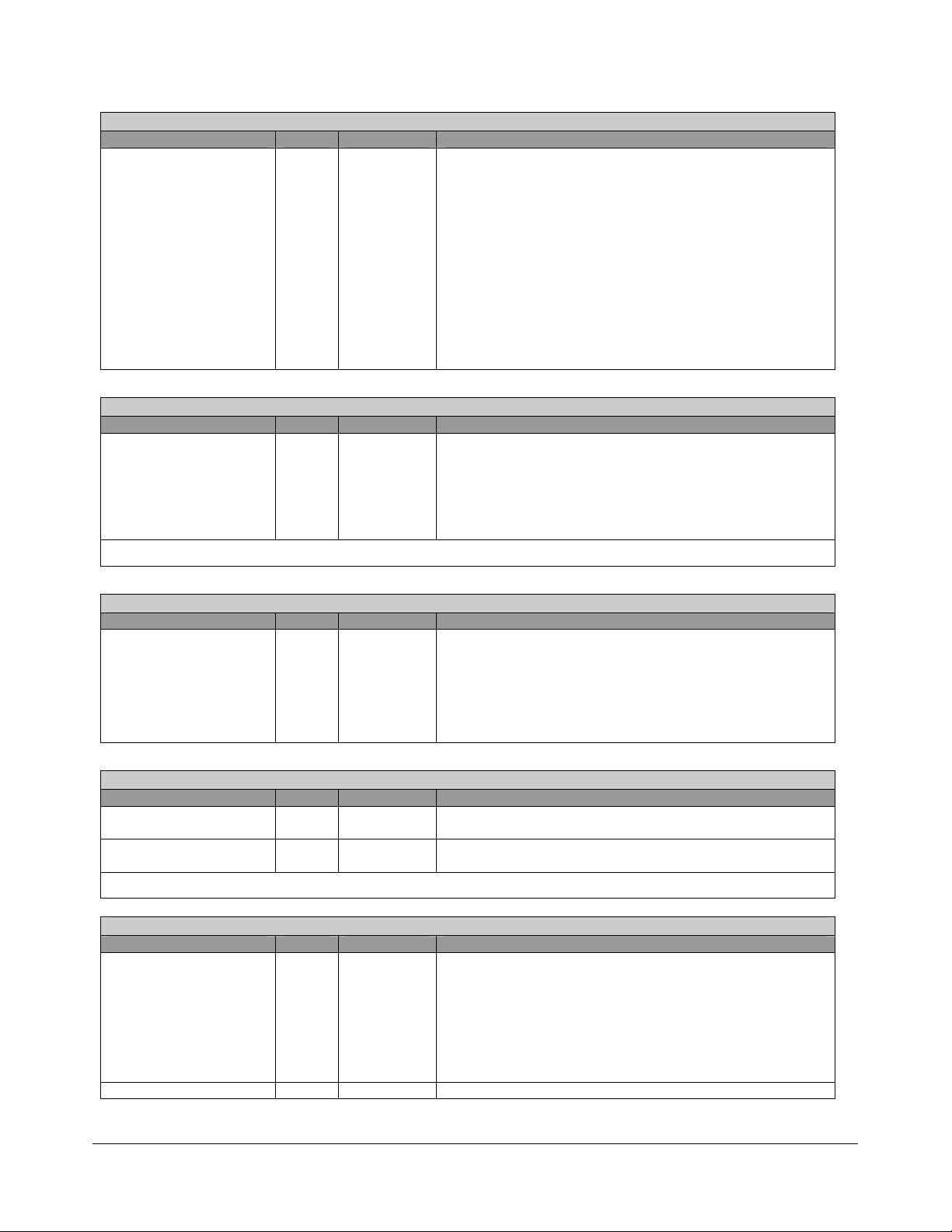

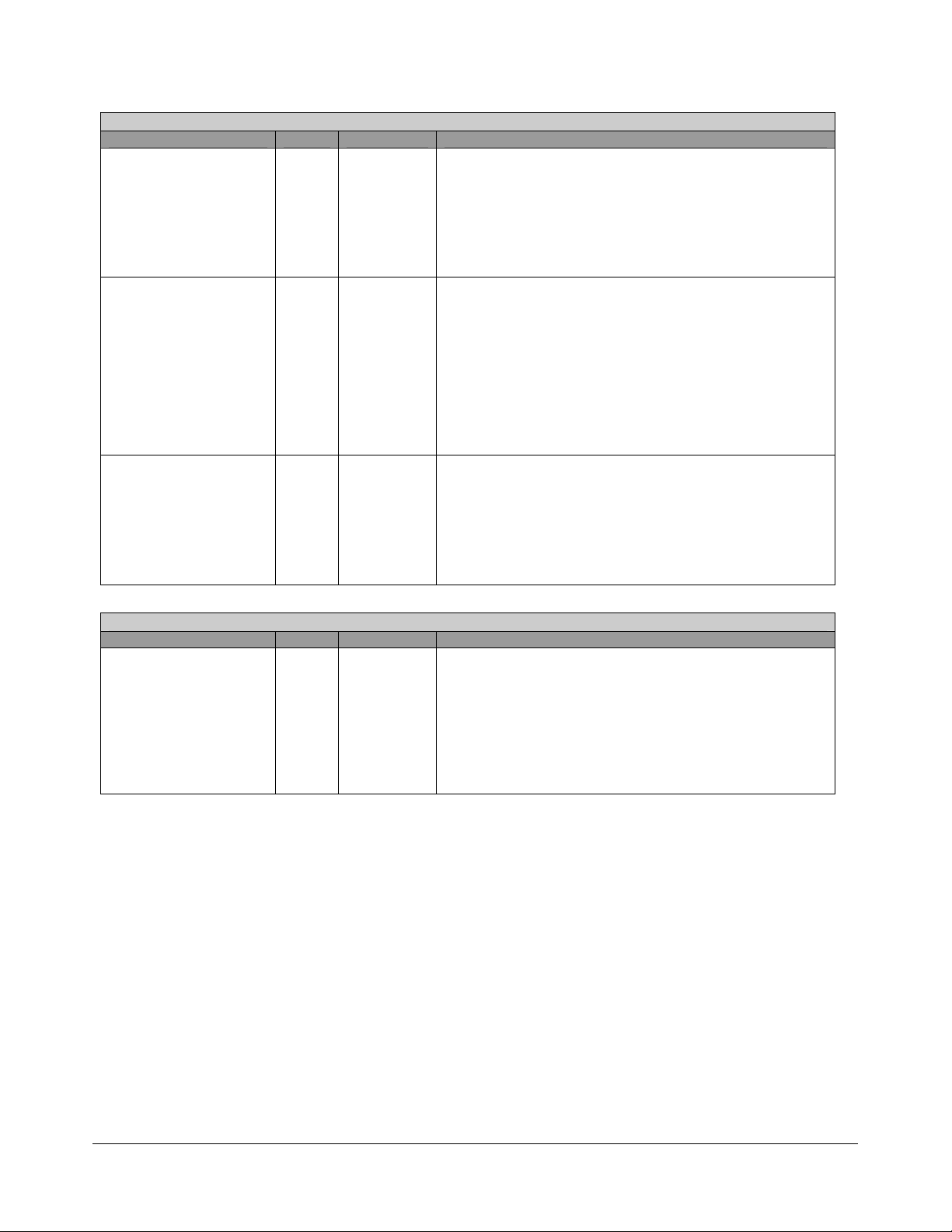

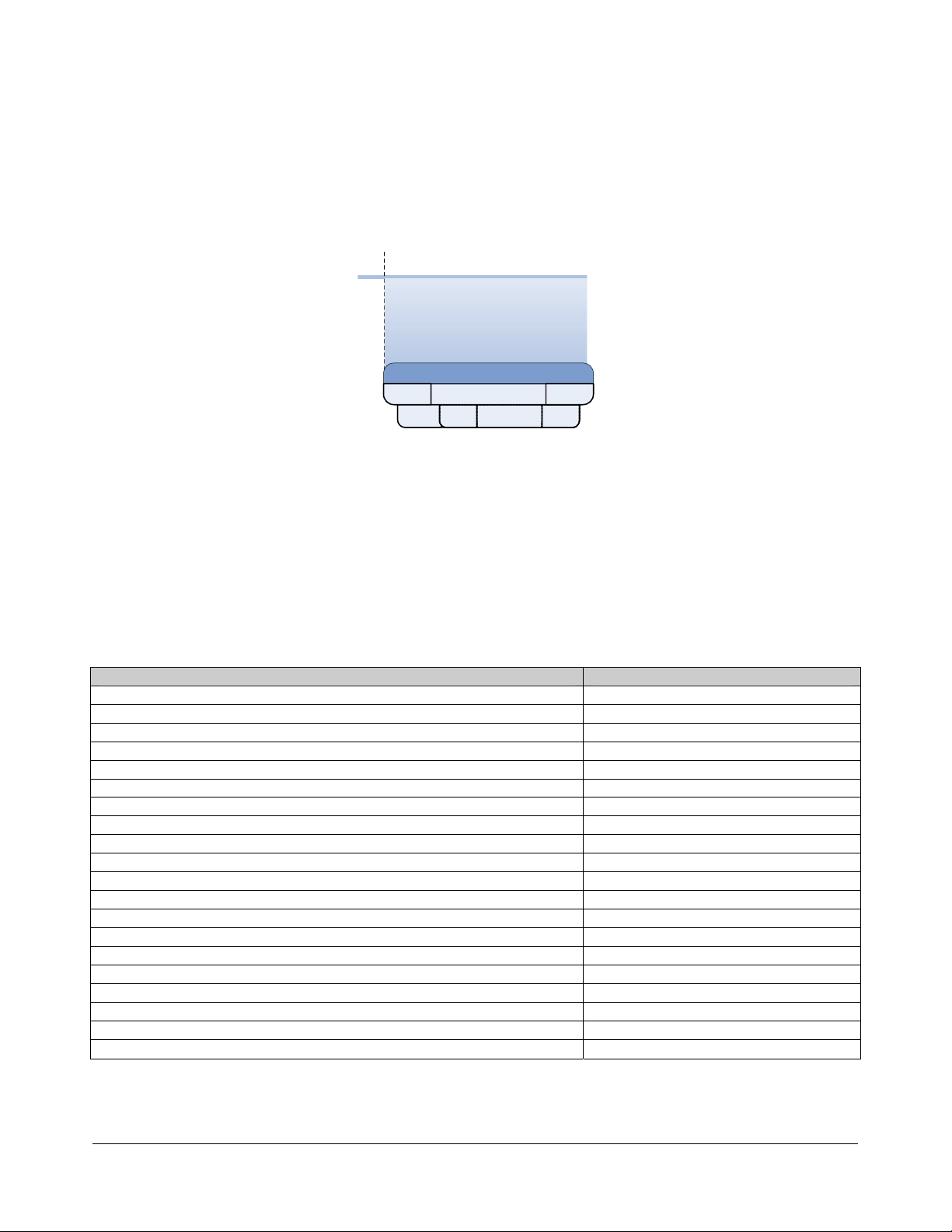

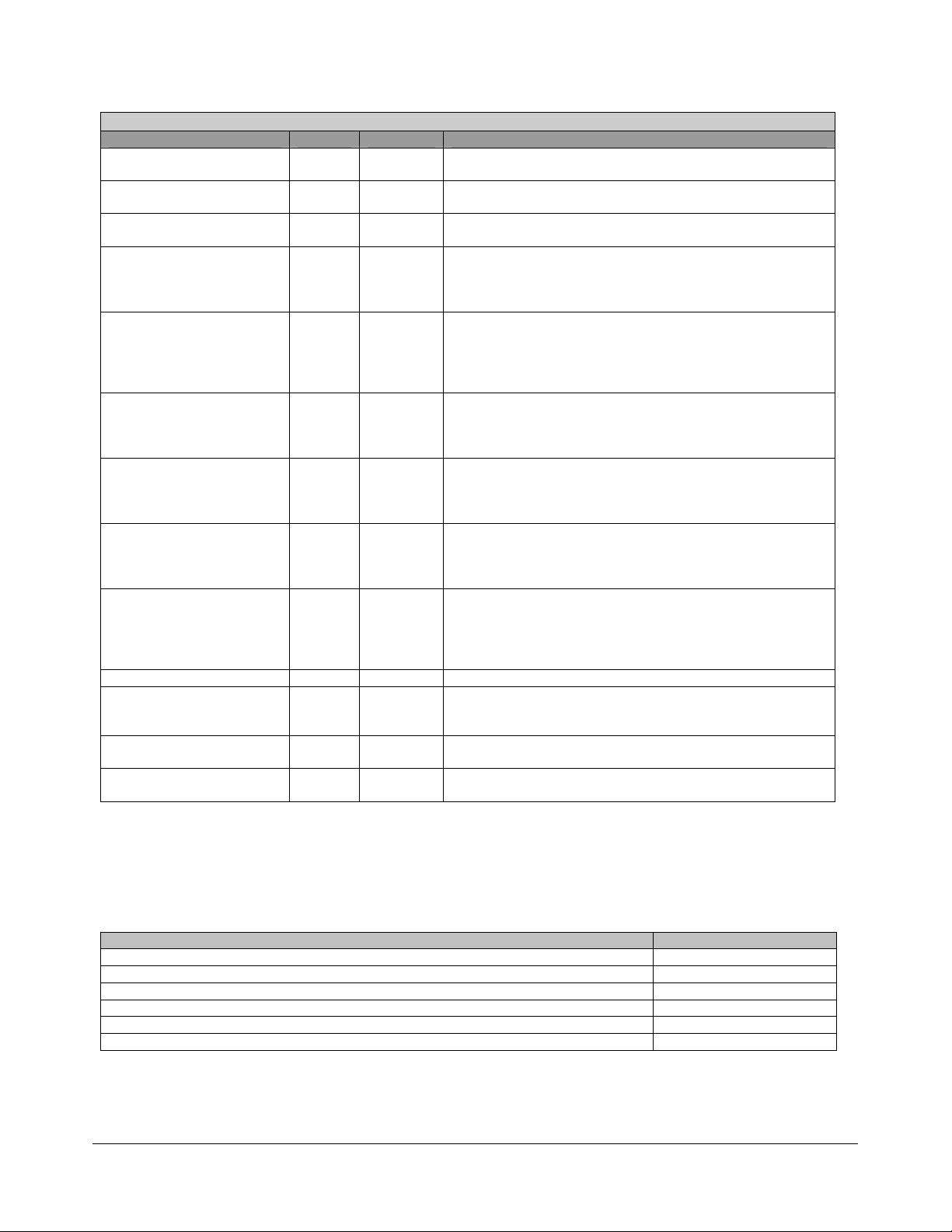

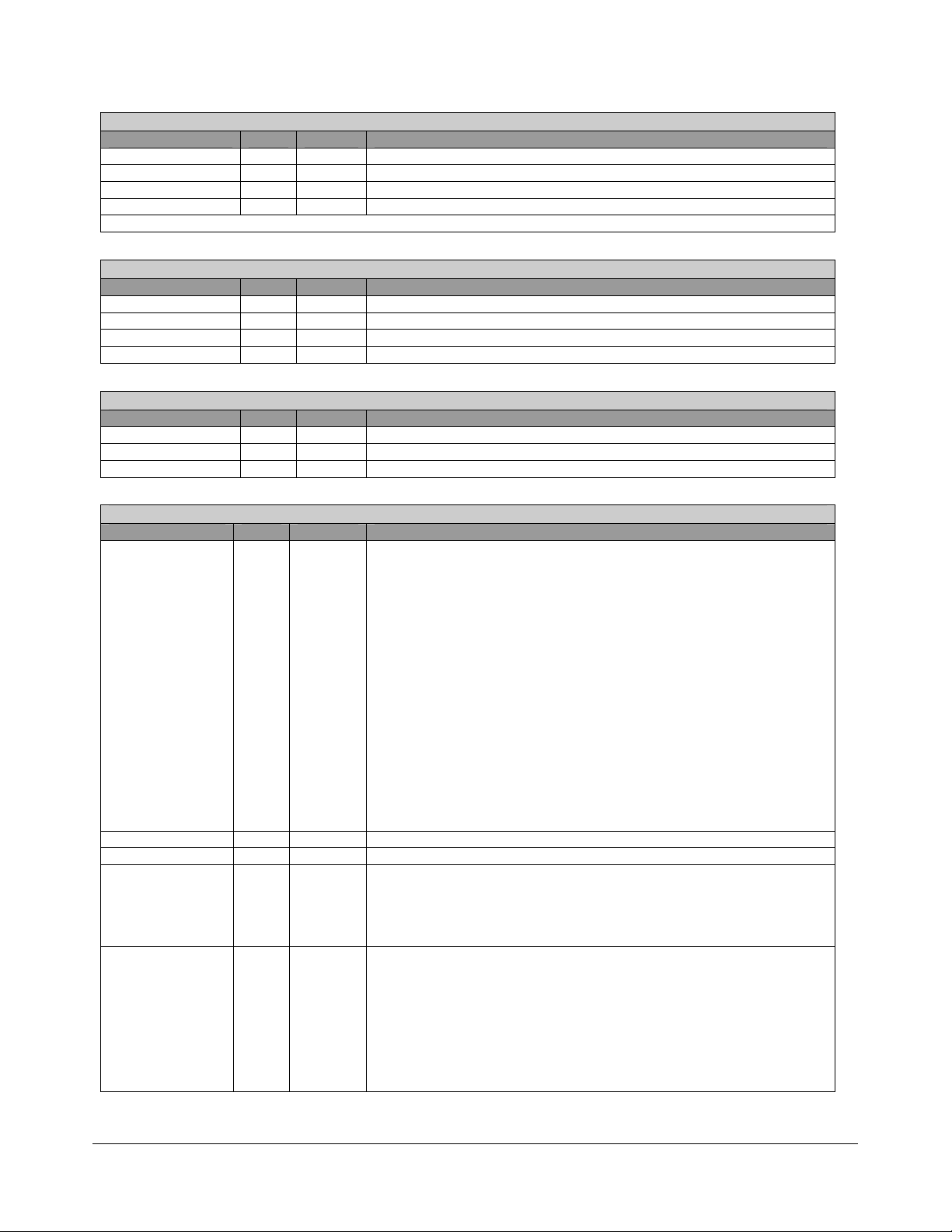

1.4 Block Diagrams

This section contains two block diagrams for the SB600. Figure 1 shows the SB600 internal PCI devices with

their assigned bus, device, and function numbers. Figure 2 shows the SB600 internal PCI devices and the

major function blocks.

ALINK-EXPRESS II

4 PORTS

10 PORTS

Debug port

SATA Controller 1

Bus 0 DEV 18 Function 0

USB:OHCI x5

Bus 0 DEV 19 Function 0:4

Device ID 4387h : 4388h :

4389h : 438Ah

Bus 0 DEV 19 Function 5

6 PCI SLOTS

Device ID 4380h

: 438Bh

USB:EHCI

Device ID 4386h

PCI Bridge

Bus 0 DEV 20

Function 4

Device ID 4384h

B-LINK A-LINK

PORT 1 PORT 0

B-LINK

ALINK

SMBUS /ACPI

Bus 0 DEV 20 Function 0

Device ID 4385h

AB

AC97 Audio

Bus 0 DEV 20

Function 5

Device ID 4382h

AC97 Modem

Bus 0 DEV 20

Function 6

Device ID 438Eh

HD Audio

Bus 0 DEV 20

Function 2

Device ID 4383h

IDE

Bus 0 DEV 20

Function 1

Device ID 438Ch

LPC

Bus 0 DEV 20

Function 3

Device ID 438Dh

AC97

1 CHANNEL

LPC bus

SPI bus

Figure 1 SB600 PCI Internal Devices

©2008 Advanced Micro Devices, Inc.

Block Diagrams

AMD SB600 Register Reference Manual Proprietary Page 11

Page 12

ALINK-EXPRESS II

AB

B-LINK A-LINK

PORT 1 PORT 0

10 PORTS

Debug port

6 PCI SLOTS

X1/X2

SERIRQ#

4 PORTS

SATA

Controller

USB:OHCI

USB:EHCI

PCI Bridge

RTC

SIRQ

APIC

PIC

B-LINK

PICD[0]

RTC_IRQ#,

PIDE_INTRQ,

SIDE_INTRQ,

USB_IRQ#,

AC97INTAB,

AC97INTBB

ALINK

SMBUS /ACPI

BUS Controler

BM

AC97 Modem

XBUS

AC97 Audio

HD Audio

IDE

LPC

ROM

GPIO

8250 TIMER

AC97

1

CHANNEL

LPC bus

SPI bus

SPEAKER

INTERRUPT

controller

INTR

IGNNE#,

FERRB#,

INT# F:A

SMI

ACPI / HW

Monitor

GEVENT[7:0],SLPBUTTON

TEMPDEAD, TEMPCAUT,

SHUTDOWN,DC_STOP#

SCIOUT, SLP#,

CPUSTP#, PCISTP#,

STPCLK#, SOFF#, SMI#,

SMIACT#

SMBUS

PM

PWRGOOD

CPURST,

INIT#,

RESET#

Figure 2 SB600 PCI Internal Devices and Major Function Blocks

©2008 Advanced Micro Devices, Inc.

Block Diagrams

AMD SB600 Register Reference Manual Proprietary Page 12

Page 13

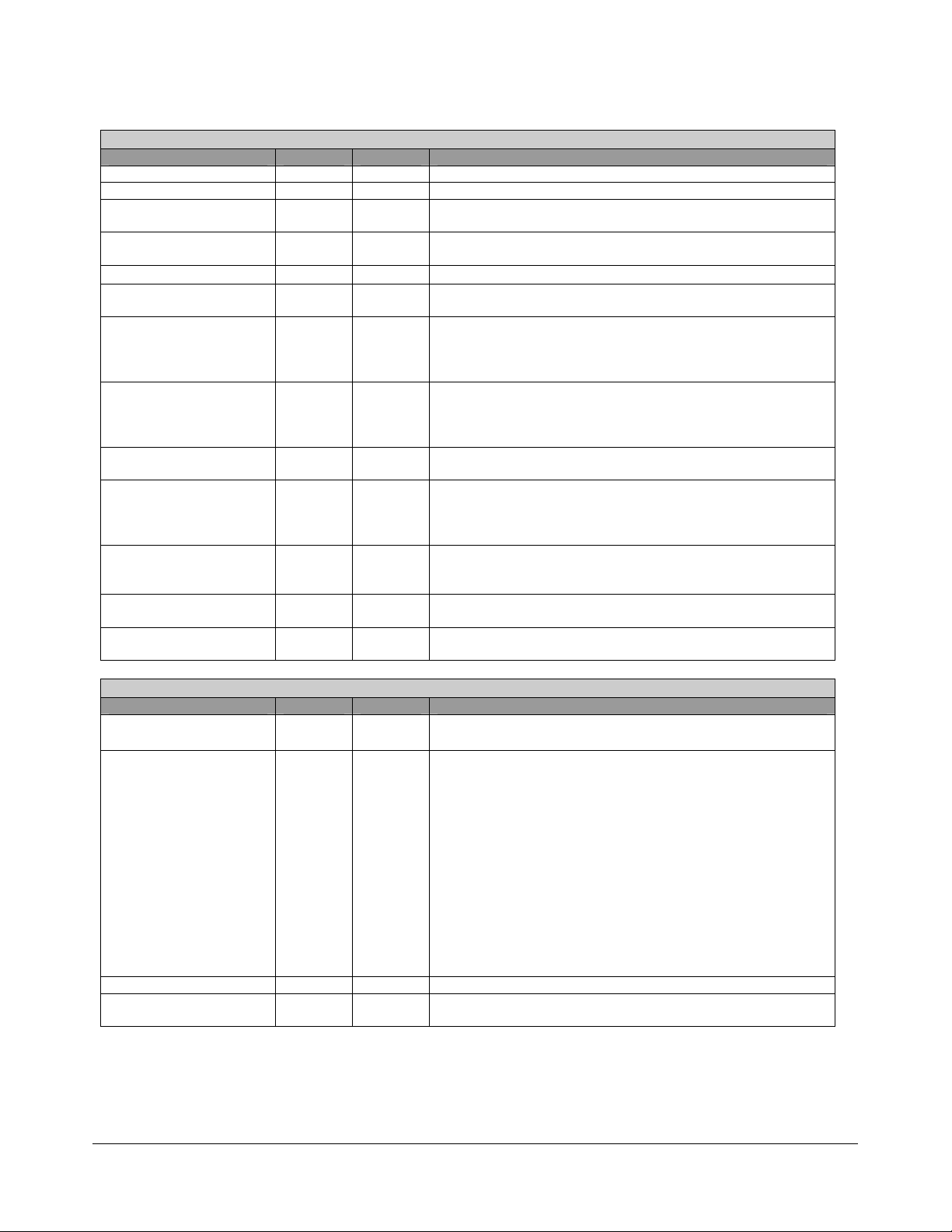

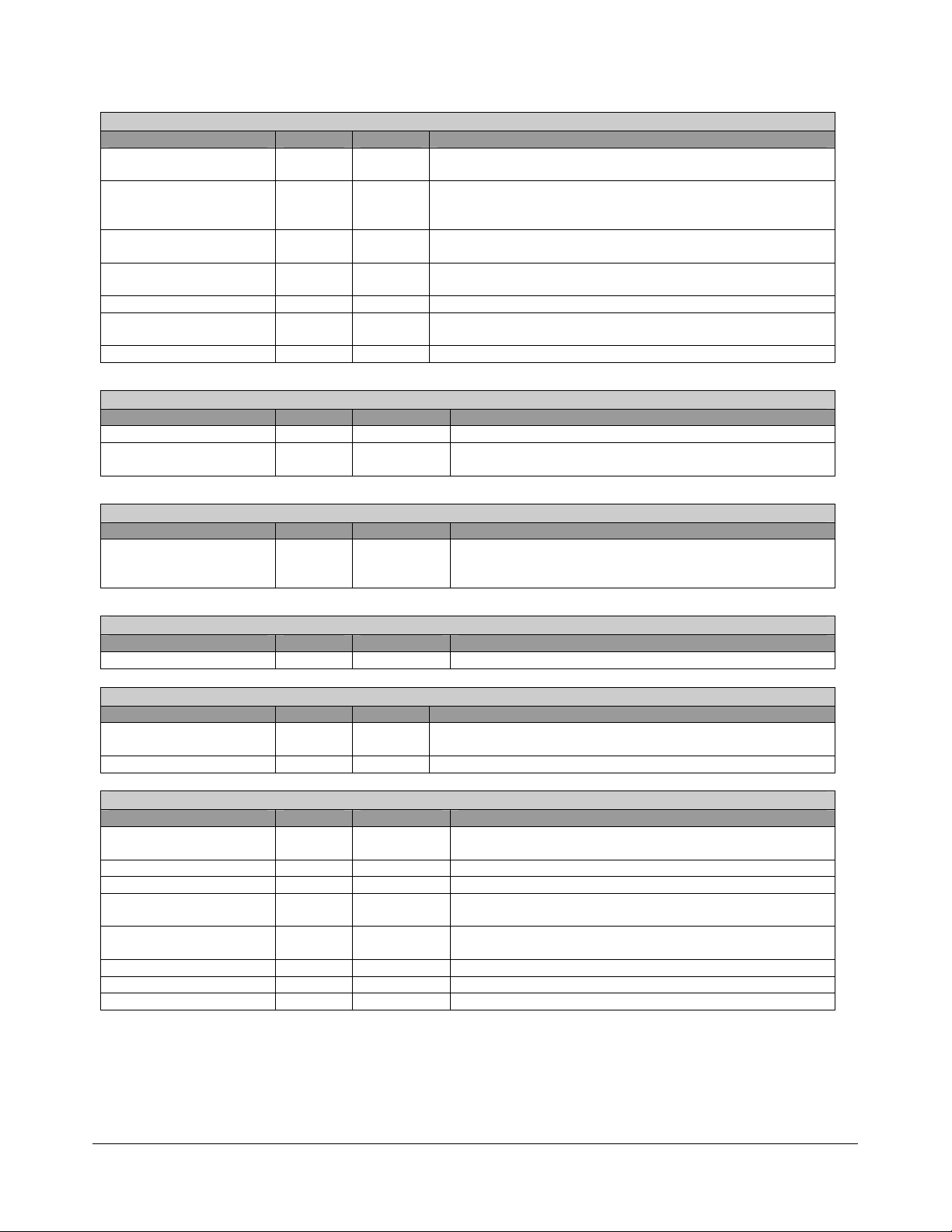

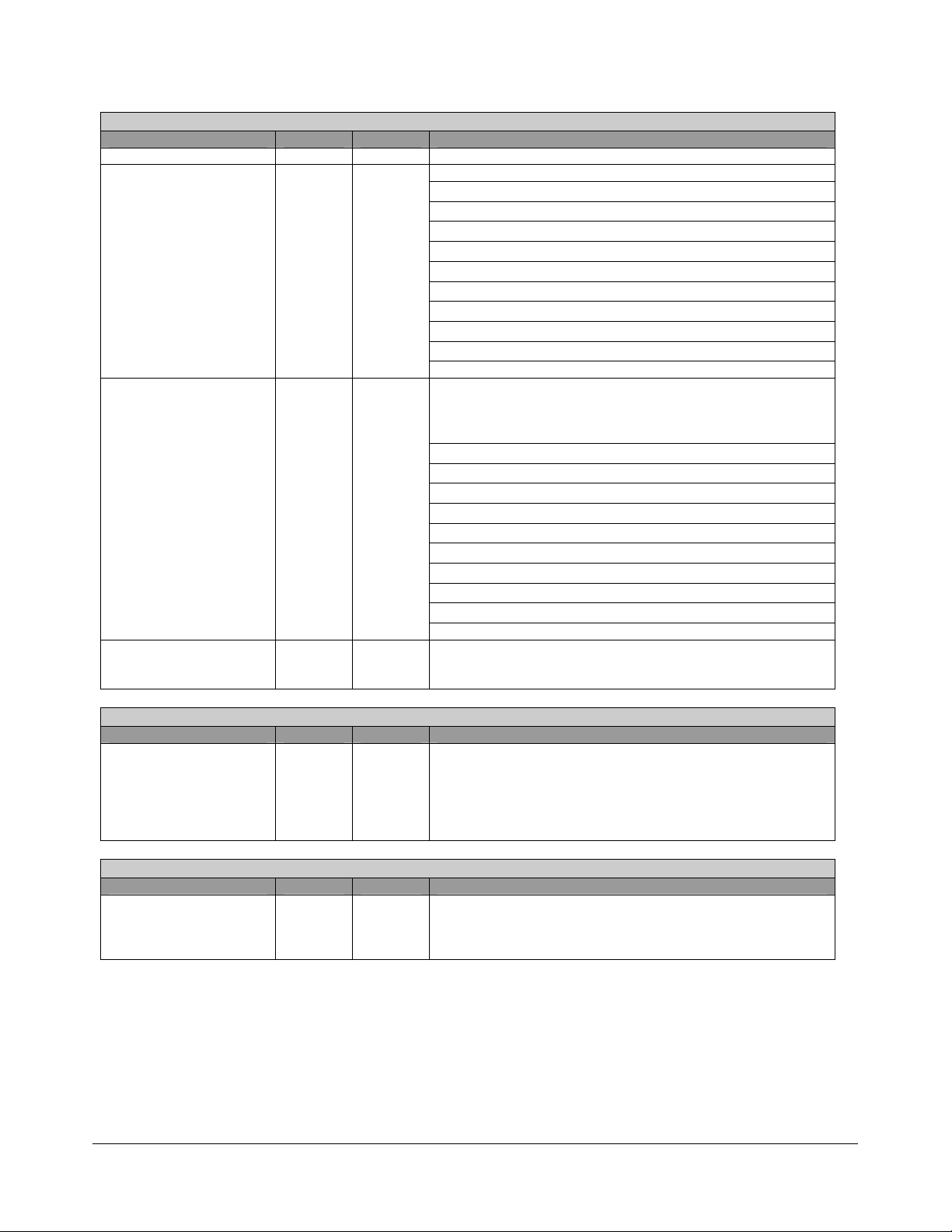

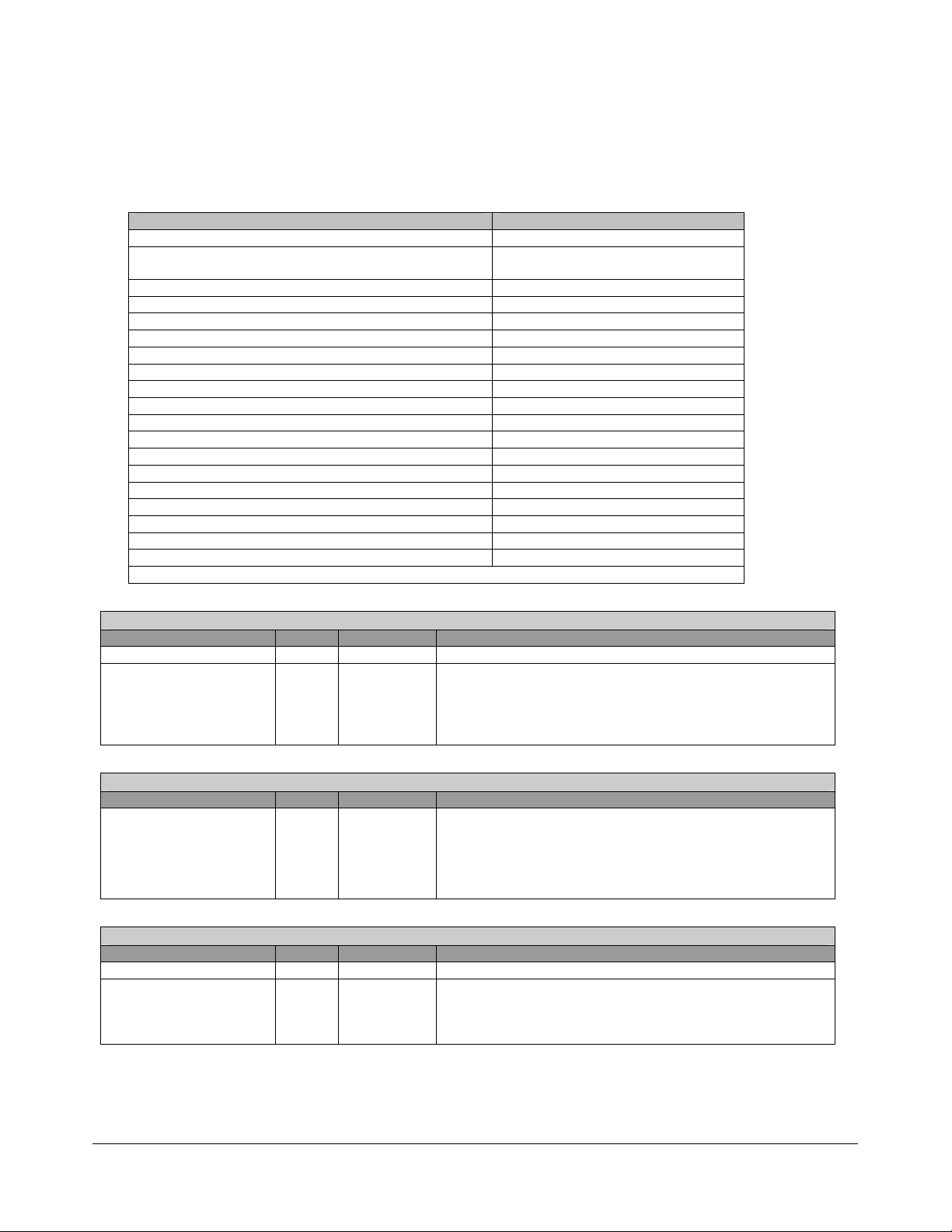

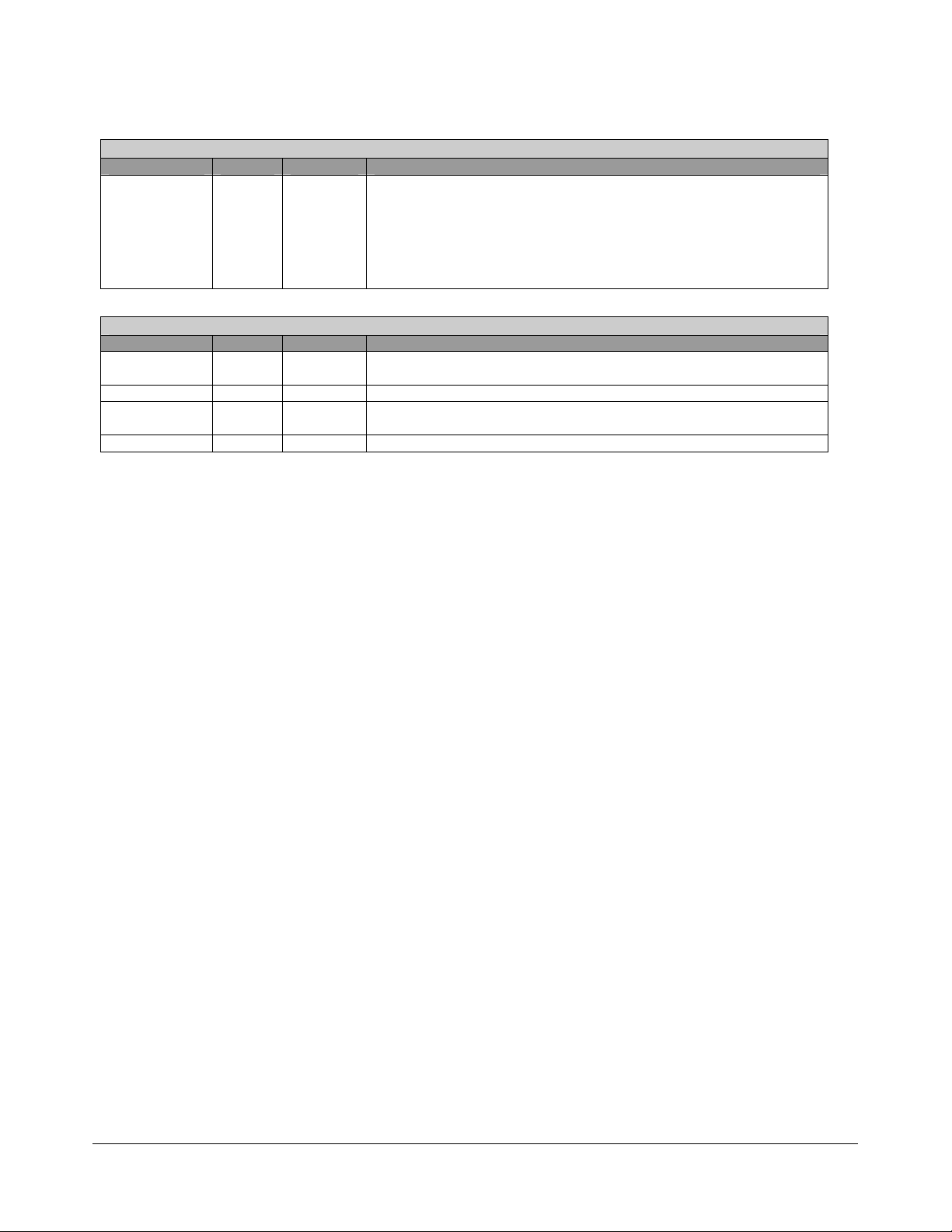

2 Register Descriptions: PCI Devices

2.1 SATA Registers (Device 18, Function 0)

Note: Some SATA functions are controlled by, and associated with, certain PCI configuration registers in the

SMBus/ACPI device. For more information refer to section 2.3: SMBus Module and ACPI Block (Device 20,

Function 0). The diagram below lists these SATA functions and the associated registers.

SATA

SATA Enables

SATA power saving

SATA Interrupt Map register

SATA Smart Power Control

PCI_Reg:

5Ch 98h

2.1.1 PCI Configuration Space

The PCI Configuration Space registers define the operation of the SB600’s SATA controller on the PCI bus.

These registers are accessible only when the SATA controller detects a Configuration Read or Write

operation, with its IDSEL asserted, on the 32-bit PCI bus.

Register Name Offset Address

Vendor ID 00h

Device ID 02h

Command 04h

Status 06h

Revision ID/Class Code 08h

Cache Link Size 0Ch

Master Latency Timer 0Dh

Header Type 0Eh

BIST Mode Type 0Fh

Base Address 0 10h

Base Address 1 14h

Base Address 2 18h

Base Address 3 1Ch

Bus Master Interface Base Address 20h

AHCI Base Address 24h

Subsystem ID and Subsystem Vendor ID 2Ch

Capabilities Pointer 34h

Interrupt Line 3Ch

Interrupt Pin 3Dh

Min_gnt 3Eh

Max_latency 3Fh

Misc control 40h

Watch Dog Control And Status 44h

Watch Dog Counter 46h

MSI Control 50h

MSI Address 54h

MSI Upper Address 58h

MSI Data 5Ch

Power Management Capability ID 60h

Power Management Capability 62h

Power Management Control And Status 64h

AC/AFh

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 13

Page 14

Register Name Offset Address

Serial ATA Capability Register 0 70h

Serial ATA Capability Register 1 74h

IDP Index 78h

IDP Data 7Ch

PHY Port0 Control 88h

PHY Port1 Control 8Ch

PHY Port2 Control 90h

PHY Port3 Control 94h

BIST pattern Count C0h

PCI Target Control TimeOut Counter C4h

Vendor ID - R - 16 bits - [PCI_Reg:00h]

Field Name Bits Default Description

Vendor ID 15:0 1002h This register holds a unique 16-bit value assigned to a vendor.

Combined with the device ID, it identifies any PCI device.

Device ID - R - 16 bits - [PCI_Reg:02h]

Field Name Bits Default Description

Device ID 15:0 4380h This register holds a unique 16-bit value assigned to a device.

Combined with the vendor ID, it identifies any PCI device.

4380h for the non-Raid5 controller

4381h for the Raid5 controller.

Bonding option default to the non-Raid 5 controller.

Command - RW - 16 bits - [PCI_Reg:04h]

Field Name Bits Default Description

I/O Access Enable 0 0b This bit controls access to the I/O space registers. When this

bit is 1, it enables the SATA controller to respond to PCI IO

space access.

Memory Access Enable 1 0b This bit controls access to the memory space registers. When

this bit is 1, it enables the SATA controller to respond to PCI

memory space access

Bus Master Enable 2 0b Bus master function enable.

1 = Enable

0 = Disable.

Special Cycle

Recognition Enable

Memory Write and

Invalidate Enable

VGA Palette Snoop

Enable

PERR- Detection Enable 6 0b If set to 1, the IDE host controller asserts PERR- when it is the

Wait Cycle Enable 7 0b Read Only.

SERR- Enable 8 0b If set to 1, and bit 6 is set, then the SATA controller asserts

Fast Back-to-Back

Enable

Interrupt Disable 10 0b Complies with the PCI 2.3 specification.

Reserved 15:11 Reserved.

3 0b Read Only. Hardwired to ‘0’

4 0b Read Only. Hardwired to ‘0’

5 0b Read Only. Hard-wired to ‘0’ indicating that the SATA host

controller does not need to snoop VGA palette cycles.

agent receiving data AND it detects a parity error. PERR- is

not asserted if this bit is 0.

Hard-wired to ‘0’ to indicate that the SATA controller does not

need to insert a wait state between the address and data on

the AD lines.

SERR- when it detects an address parity error. SERR- is not

asserted if this bit is 0.

9 0b Read Only. Hard-wired to ‘0’ to indicate that fast back to back

is only allowed to the same agent.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 14

Page 15

Status - RW - 16 bits - [PCI_Reg:06h]

Field Name Bits Default Description

Reserved 2:0 Reserved.

Interrupt Status 3 0b Interrupt status bit. Complies with the PCI 2.3 specification.

Capabilities List 4 1b Read Only. Hardwired to 1 to indicate that the Capabilities

Pointer is located at 34h.

66MHz Support 5 1b 66MHz capable. This feature is supported in the SATA

controller.

Reserved 6

Fast Back-to-Back

Capable

Data Parity Error 8 0b Data Parity reported. Set to 1 if the SATA controller detects

DEVSEL- Timing 10:9 01b Read only.

Signaled Target Abort 11 0b Signaled Target Abort. This bit is set to 1, when the SATA

Received Target Abort 12 0b Received Target Abort. This bit is set to 1 when the SATA

Received Master Abort

Status

SERR- Status 14 0b SERR- status. This bit is set to 1 when the SATA controller

Detected Parity Error 15 0b Detected Parity Error. This bit is set to 1 when the SATA

7 0b Read Only. Hard-wired to ‘0’ to indicate that it is fast back to

13 0b Received Master Abort Status. Set to 1 when the SATA

Reserved.

back incapable.

PERR- asserted while acting as the PCI master (whether

PERR- was driven by the SATA controller or not.). Write ‘1’ to

clear this bit.

These bits indicate DEVSEL- timing when performing a

positive decode. Since DEVSEL- is asserted to meet the

medium timing, these bits are encoded as 01b.

controller signals Target Abort. Write ‘1’ to clear this bit.

controller that generated the PCI cycle (SATA controller is the

PCI master) is aborted by a PCI target. Write ‘1’ to clear this

bit.

controller, acting as a PCI master, aborts a PCI bus memory

cycle. Write ‘1’ to clear this bit..

detects a PCI address parity error. Write ‘1’to clear this bit.

controller detects a parity error. Write ‘1’ to clear this bit.

Revision ID/Class Code- R - 32 bits - [PCI_Reg:08h]

Field Name Bits Default Description

Revision ID 7:0 00h These bits are hardwired to 00h to indicate the revision level of

the chip design.

Operating Mode

Selection

Sub-Class Code 23:16 01h Sub-Class Code. 01h to indicate an IDE Controller. See Note.

Class Code 31:24 01h Class Code. These 8 bits are read only and wired to 01h to

15:8 8Fh RW

Programmable I/F.

Bit [15] = Master IDE Device. Always 1.

Bits [14:12] = Reserved. Always read as 0’s.

Bit [11] = Programmable indicator for Secondary. Always 1 to

indicate that both modes are supported.

Bit [10] = Operating Mode for Secondary.

1 = Native PCI-mode.

0 = Compatibility Mode

Bit [9] = Programmable indicator for Primary. Always 1 to

indicate that both modes are supported.

Bit [8] = Operating Mode for Primary.

1 = Native PCI-mode.

0 = Compatibility

indicate a Mass-Storage Controller.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 15

Page 16

Revision ID/Class Code- R - 32 bits - [PCI_Reg:08h]

Field Name Bits Default Description

Note: This field is only writeable when PCI_Reg:40h[0] is set.

Sub-Class Code Program Interface Controller Type

01 8F IDE

06 01 AHCI

04 00 RAID

Cache Line Size - RW - 8 bits - [PCI_Reg:0Ch]

Field Name Bits Default Description

Reserved 3:0 Reserved.

Cache Line Size Register 7:4 0h If the value is 1, then the cache line size is 16 DW (64 byte).

Master Latency Timer - RW - 8 bits - [PCI_Reg:0 Dh]

Field Name Bits Default Description

Reserved 2:0 Reserved.

Master Latency Timer 7:3 00h Master Latency Timer. This number, in units of clocks,

represents the guaranteed time slice allowed to the IDE host

controller for burst transactions.

Header Type - R - 8 bits - [PCI_Reg:0Eh]

Field Name Bits Default Description

Header Type 7:0 00h Header Type. Since the IDE host controller is a single-function

device, this register contains a value of 00h.

BIST Mode Type - RW - 8 bits - [PCI_Reg:0Fh]

Field Name Bits Default Description

Completion Code 3:0 0h Read Only.

Indicates the completion code status of BIST. A non-zero

value indicates a failure.

Reserved 5:4 Reserved.

Start BIST 6 0b Since bit [7] is 0, program this bit take no effect.

BIST Capable 7 0b Read Only. Hard-wired to ‘0’ indicating that there is no HBA

related BIST function.

Base Address 0 - RW - 32 bits - [PCI_Reg:10h]

Field Name Bits Default Description

Resource Type Indicator 0 1b RTE (Resource Type Indicator). This bit is wired to 1 to

indicate that the base address field in this register maps to I/O

space.

Reserved 2:1 Reserved.

Primary IDE CS0 Base

Address

31:3 0000_

0000h

Base Address for Primary IDE Bus CS0. This register is used

for native mode only. Base Address 0 is not used in

compatibility mode.

Base Address 1 - RW - 32 bits - [PCI_Reg:14h]

Field Name Bits Default Description

Resource Type Indicator 0 1b RTE (Resource Type Indicator). This bit is wired to 1 to

indicate that the base address field in this register maps to I/O

space.

Reserved 1 Reserved.

Primary IDE CS1 Base

Address

31:2 0000_

0000h

Base Address for Primary IDE Bus CS1. This register is used

for native mode only. Base Address 1 is not used in

compatibility mode.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 16

Page 17

Base Address 2 - RW - 32 bits - [PCI_Reg:18h]

Field Name Bits Default Description

Resource Type Indicator 0 1b This bit is wired to 1 to indicate that the base address field in

this register maps to I/O space.

Reserved 2:1 Reserved.

Secondary IDE CS0

Base Address

31:3 0000_

0000h

Base Address for Secondary IDE Bus CS0. This register is

used for native mode only. Base Address 2 is not used in

compatibility mode.

Base Address 3 - RW - 32 bits - [PCI_Reg:1Ch]

Field Name Bits Default Description

Resource Type Indicator 0 1b This bit is wired to 1 to indicate that the base address field in

this register maps to I/O space.

Reserved 1 Reserved.

Secondary IDE CS1

Base Address

31:2 0000_

0000h

Base Address for Secondary IDE Bus CS1. This register is

used for native mode only. Base Address 3 is not used in

compatibility mode.

Bus Master Interface Base Address - RW - 32 bits - [PCI_ Reg:20h]

Field Name Bits Default Description

Resource Type Indicator 0 1b This bit is wired to 1 to indicate that the base address field in

this register maps to I/O space.

Reserved 3:1 Reserved.

Bus Master Interface

Register Base Address

31:4 0000_

000h

Base Address for the Bus Master interface registers, and

corresponds to AD[15:4].

AHCI Base Address - RW - 32 bits - [PCI_Reg:24h]

Field Name Bits Default Description

Resource Type Indicator 0 0b This bit is wired to 0 to indicate a request for register memory

space.

Reserved 9:1 Reserved.

AHCI Base Address 31:10 000000h Base address of register memory space. This represents a

memory space for support of 4 ports.

Subsystem ID and Subsystem Vendor ID - RW - 32 bits - [PCI_Reg:2Ch]

Field Name Bits Default Description

Subsystem Vendor ID 15:0 0000h Subsystem Vendor ID. This can only be written once by the

software.

Subsystem ID 31:16 0000h Subsystem ID. This can only be written once by the software.

Capabilities Pointer - R - 8 bits - [PCI_Reg:34h]

Field Name Bits Default Description

Capabilities Pointer 7:0 60h The first pointer of the Capability block

Interrupt Line - RW - 8 bits - [PCI_Reg:3Ch]

Field Name Bits Default Description

Interrupt Line 7:0 00h Identifies which input on the interrupt controller the function’s

PCI interrupt request pin (as specified in its Interrupt Pin

register) is routed to.

Interrupt Pin - R - 8 bits - [PCI_Reg:3Dh]

Field Name Bits Default Description

Interrupt Pin 7:0 01h Hard-wired to 01h.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 17

Page 18

Min_gnt - R - 8 bits - [PCI_Reg:3Eh]

Field Name Bits Default Description

Minimum Grant 7:0 00h This register specifies the desired settings for how long of a

burst the SATA controller needs. The value specifies a period

of time in units of ¼ microseconds.

Hard-wired to 0’s and always read as 0’s.

Max_latency - R - 8 bits - [PCI_Reg:3Fh]

Field Name Bits Default Description

Maximum Latency 7:0 00h This register specifies the Maximum Latency time required

before the SATA controller as a bus-master can start an

accesses

Hard-wired to 0’s and always read as 0’s.

Misc Control - RW - 32 bits - [PCI_Reg:40h]

Field Name Bits Default Description

Subclass code write

Enable

Disable Dynamic Sata

Memory Power Saving

Enable dynamic Sata

Core Power Saving

Reserved 3 Reserved.

Disable Speed up XP

Boot

Reserved 5 0b Reserved

Reserved 15:6 Reserved.

Disable port0 16 0b When set, port0 is disabled and port0 clock is shut down.

Disable port1 17 0b When set, port1 is disabled and port1 clock is shut down.

Disable port2 18 0b When set, port2 is disabled and port2 clock is shut down.

Disable port3 19 0b When set, port3 is disabled and port3 clock is shut down.

Reserved 31:20 Reserved.

0 0b Once set, Program Interface register (PCI_Reg:09h), subclass

code register (PCI_Reg:0Ah) and Multiple Message Capable

bits (PCI_Reg50h[19:17]) can be programmable.

1 0b When clear, dynamic power saving function for SATA internal

memory macros will be performed to reduce power

consumption.

2 0b When set, dynamic power saving function for SATA core clock

will be performed during partial/slumber mode to reduce power

consumption.

4 0b When clear, it fastens XP boot up in IDE mode. However, this

bit needs to be set, when enable SATA partial/slumber power

function is in IDE mode.

When set, the SATA partial/slumber power function can be

enabled in IDE mode, but the BIOS IO trap is needed to speed

up XP boot-up in IDE mode.

Please refer to BAR5 + offset 12C/1Ac/22C/2AC[11:8] for the

SATA partial/slumber modes that are allowed.

Watch Dog Control And Status - RW - 16 bits - [PCI_Reg:44h]

Field Name Bits Default Description

Watchdog Enable 0 0b Set this bit to enable the watchdog counter for all the PCI

down stream transaction.

Watchdog Timeout

Status

Reserved 15:2 Reserved.

1 0b Watchdog Counter Timeout Status bit. This bit indicates that

the watchdog counter has expired for PCI down stream

transaction and the transaction got aborted due to counter has

expired.

Software writes 1 to clear the status.

Watch Dog Counter - RW - 16 bits - [PCI_Reg:46h]

Field Name Bits Default Description

Watchdog Counter 7:0 80h Specifies the timeout retry count for PCI down stream retries.

Reserved 15:8 Reserved.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 18

Page 19

MSI Control - RW- 32 bits - [PCI_Reg:50h]

Field Name Bits Default Description

Capability ID 7:0 05h Read-Only.

Capability ID. It indicates that this is and MSI capability ID.

Capability Next Pointer 15:8 70h Read-Only.

Next Pointer (hard wired to 70h, points to Index Data pair

capability

Message Signaled

Interrupt Enable

Multiple Message

Capable

Multiple Message Enable 22:20 000b Multiple Message Enable.

MSI 64-bit Address 23 1b Read-Only

Reserved 31:24 Reserved.

16 0b MSI Enable.

19:17 010b Multiple Message Capable.

Support 64-bit address.

MSI Address - RW- 32 bits - [PCI_Reg:54h]

Field Name Bits Default Description

Reserved 1:0 Reserved.

MSI Address 31:2 0000_0000h Lower 32 bits of the system specified message address

always DW aligned.

MSI Upper Address - RW- 32 bits - [PCI_Reg:58h]

Field Name Bits Default Description

MSI Upper Address 31:0 0000_0000h Upper 32 bits of the system specified message address.

This register is optional and only implemented if

MC.C64=1.

MSI Data - RW- 16 bits - [PCI_Reg:5Ch]

Field Name Bits Default Description

MSI Data 15:0 0000h MSI Data

Power Management Capability ID - R- 16 bits - [PCI_Reg:60h]

Field Name Bits Default Description

Capability ID 7:0 01h Capability ID. Indicates this is power management capability

ID.

Capability Next Pointer 15:8 50h Next Pointer.

Power Management Capability - R- 16 bits - [PCI_Reg:62h]

Field Name Bits Default Description

Version 2:0 010b Indicates support for Revision 1.1 of the PCI Power

Management Specification.

PME Clock 3 0b Indicates that PCI clock is not required to generate PME#.

Reserved 4 Reserved

Device Specific

Initialization

Aux_Current 8:6 000b Reports the maximum Suspend well current required when

D1_Support 9 0b The D1 state is not supported.

D2_Support 10 0b The D2 state is not supported.

PME_Support 15:11 00h Read-Only.

5 1b Indicates whether device-specific initialization is required.

in the D3

state. Hard wired to 000b.

COLD

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 19

Page 20

PCI Power Management Control And Status - RW- 16 bits - [PCI_Reg:64h]

Field Name Bits Default Description

Power State 1:0 00b

Reserved 7:2 Reserved

PME Enable 8 0b Read-only. Hard-wired to ‘0’ indicates PME disable

Reserved 14:9 Reserved.

PME Status 15 0b Read-only. Hard-wired to ‘0’ as PME disable

This field is used both to determine the current power state

of the HBA and to set a new power state. The values are:

00 – D0 state

11 – D3

The D1 and D2 states are not supported. When in the

state, the configuration space is available, but the

D3

HOT

register memory spaces are not. Additionally, interrupts

are blocked.

HOT

state

Serial ATA Capability Register 0 - R- 32 bits - [PCI_Reg:70h]

Field Name Bits Default Description

Capability ID 7:0 12h Capability ID. Indicates this is a Serial ATA Capability ID.

Capability Next Pointer 15:8 00h Next Pointer, end of the list.

Minor Revision 19:16 0h Minor revision number of the SATA Capability Pointer

implemented.

Major Revision 23:20 1h Major revision number of the SATA Capability Pointer

implemented.

Reserved 31:24 Reserved

Serial ATA Capability Register 1 - R- 32 bits - [PCI_Reg:74h]

Field Name Bits Default Description

BAR Location 3:0 1111b Value 1111b indicates that the Index-Data Pair is implemented

in Dwords directly following SATACR1 in the PCI configuration

space.

BAR Offset 23:4 00000h Indicates the offset into the BAR where the Index-Data Pair

are located in Dword granularity. Since the BAR location is

setting at 1111b, this field is not used anymore.

Reserved 31:24 Reserved

IDP Index Register - RW- 32 bits - [PCI_Reg:78h]

Field Name Bits Default Description

Reserved 1:0 Reserved

IDP Index 9:2 00h This register selects the Dword offset of the memory mapped

AHCI register to be accessed. The IDP Index should be sized

such that it can access the entire ABAR register space for the

particular implementation. See Note.

Reserved 31:10 Reserved

Note: ABAR is AHCI memory map registers located at AHCI base address (BAR5) space.

IDP Data Register - RW- 32 bits - [PCI_Reg:7Ch ]

Field Name Bits Default Description

IDP Data 31:0 This register is a “window” through which data is read or

written to the memory mapped register pointed to by the IDP

Index register. Note that a physical register is not actually

implemented as the data is actually stored in the memory

mapped registers.

Since this is not a physical register, the “default” value is the

same as the default value of the register pointed to by IDP

Index.

All register accesses to IDP Data are Dword granularity

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 20

Page 21

PHY Port0 Control - RW- 32 bits - [PCI_Reg:88h]

Field Name Bits Default Description

Port0 PHY 23:0 B40014h PHY port0 fine-tune register.

TX main driver swing 4:0 10100b Port0 Tx driving swing[4:0] is valid for SATA 1.5G. It sets the

TX main driver swing. The user can program the optimum

value for each SATA port.

Bit 4 Bit 3 Bit 2 Bit 1 Bit0 Nominal Output

1 0 0 0 0 400mv

1 0 0 1 0 450mv

1 0 1 0 0 500mv

1 0 1 1 0 550mv

1 1 0 0 0 600mv

1 1 0 1 0 650mv

1 1 1 0 0 700mv

1 1 1 1 0 750mv

Note: This applies to all the ASIC Revisions A11 and above.

TX pre-emphasis driver

swing

TX pre-emphasis enable 13 0b Turns on TX pre-emphasis output

Reserved 31:24 Reserved.

7:5 000b Port0 Tx driving swing[7:5] is valid for both SATA 3G and

1.5G. It sets the TX pre-emphasis driver strength. The user

can program the optimum pre-emphasis value for each SATA

port if TX pre-emphasis enable bit is turned on.

Bit 7 Bit 6 Bit 5 pre-emphasis amount

0 0 0 0mv

0 0 1 25mv

0 1 0 50mv

0 1 1 75mv

1 0 0 100mv

1 0 1 125mv

1 1 0 150mv

1 1 1 175mv

Note: This applies to all the ASIC Revisions A11 and above.

1: Enable pre-emphasis

0: Disable pre-emphasis

PHY Port1 Control - RW- 32 bits - [PCI_Reg:8Ch]

Field Name Bits Default Description

Port1 PHY 23:0 B40014h PHY port1 fine-tune register.

TX main swing 4:0 10100b Port1 Tx driving swing[4:0] is valid at SATA 1.5G. It sets the

TX main driver swing. The user can program the optimum

value for each SATA port.

Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Nominal Output

1 0 0 0 0 400mv

1 0 0 1 0 450mv

1 0 1 0 0 500mv

1 0 1 1 0 550mv

1 1 0 0 0 600mv

1 1 0 1 0 650mv

1 1 1 0 0 700mv

1 1 1 1 0 750mv

Note: This applies to all the ASIC Revisions A11 and above.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 21

Page 22

PHY Port1 Control - RW- 32 bits - [PCI_Reg:8Ch]

Field Name Bits Default Description

TX pre-emphasis driver

swing

TX pre-emphasis enable 13 0b Turns on port1 TX pre-emphasis output.

7:5 000b Port1 Tx driving swing[7:5] is valid for both SATA 3G and

1.5G. It sets the TX pre-emphasis driver strength. The user

can program the optimum pre-emphasis value for each SATA

port if TX pre-emphasis enable bit turned on.

Bit 7 Bit 6 Bit 5 pre-emphasis amount

0 0 0 0mv

0 0 1 25mv

0 1 0 50mv

0 1 1 75mv

1 0 0 100mv

1 0 1 125mv

1 1 0 150mv

1 1 1 175mv

Note: This applies to all the ASIC Revisions A11 and above.

1: Enable pre-emphasis

0: Disable pre-emphasis

PHY Port2 Control - RW- 32 bits - [PCI_Reg:90h]

Field Name Bits Default Description

Port2 PHY 23:0 B40014h PHY port2 fine-tune register.

TX main swing 4:0 10100b Port2 Tx driving swing[4:0] is valid at SATA 1.5G.

Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Nominal Output

1 0 0 0 0 400mv

1 0 0 1 0 450mv

1 0 1 0 0 500mv

1 0 1 1 0 550mv

1 1 0 0 0 600mv

1 1 0 1 0 650mv

1 1 1 0 0 700mv

1 1 1 1 0 750mv

Note: This applies to all the ASIC Revisions A11 and above.

TX pre-emphasis driver

swing

TX pre-emphasis enable 13 0b Turns on port2 TX pre-emphasis output

7:5 000b Port2 Tx driving swing[7:5] is valid for both SATA 3G and

1.5G. It sets the TX pre-emphasis driver strength. The user

can program the optimum pre-emphasis value for each SATA

port if TX pre-emphasis enable bit turned on.

Bit 7 Bit 6 Bit 5 pre-emphasis amount

0 0 0 0mv

0 0 1 25mv

0 1 0 50mv

0 1 1 75mv

1 0 0 100mv

1 0 1 125mv

1 1 0 150mv

1 1 1 175mv

Note: This applies to all the ASIC Revisions A11 and above.

1: Enable pre-emphasis

0: Disable pre-emphasis

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 22

Page 23

PHY Port3 Control - RW- 32 bits - [PCI_Reg:94h]

Field Name Bits Default Description

Port3 PHY 23:0 B40014h PHY port3 fine-tune register.

TX main swing 4:0 10100b Port3 Tx driving swing[4:0] is valid at SATA 1.5G.

Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Nominal Output

1 0 0 0 0 400mv

1 0 0 1 0 450mv

1 0 1 0 0 500mv

1 0 1 1 0 550mv

1 1 0 0 0 600mv

1 1 0 1 0 650mv

1 1 1 0 0 700mv

1 1 1 1 0 750mv

Note: This applies to all the ASIC Revisions A11 and above.

TX pre-emphasis driver

swing

TX pre-emphasis enable 13 0b Turns on port3 TX pre-emphasis output

7:5 000b Port3 Tx driving swing[7:5] is valid for both SATA 3G and

1.5G. It sets the TX pre-emphasis driver strength. The user

can program the optimum pre-emphasis value for each SATA

port if TX pre-emphasis enable bit turned on.

Bit 7 Bit 6 Bit 5 pre-emphasis amount

0 0 0 0mv

0 0 1 25mv

0 1 0 50mv

0 1 1 75mv

1 0 0 100mv

1 0 1 125mv

1 1 0 150mv

1 1 1 175mv

Note: This applies to all the ASIC Revisions A11 and above.

1: Enable pre-emphasis

0: Disable pre-emphasis

BIST Pattern Count - RW - 32 bits - [PCI_Reg:C0h]

Field Name Bits Default Description

BIST Pattern Count 31:0 0000_20

00h

This count specifies how many Octal WORD pattern need to

be checked before BIST Done bit be set. This count value is

used fro all the 4 ports. 400h default value would be used for

tester, which means 32K DWORD pattern would be compared

for BIST test. Value of “0000_0000”h means the maximum

patterns (16,000, 000, 000) checked.

PCI Target Control TimeOut Counter - RW – 8 bits - [PCI_Reg:C4h]

Field Name Bits Default Description

PCI Target Control

TimeOut Count

7:0 80h This register is used for programming the PCI Target Control

TimeOut Count used to clear any stale target commands to

the hosts controller. Granularity is 15.5us (Count * 15.5 us)

The counter will be disabled if the count is programmed to 0x0.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 23

Page 24

2.1.2 BAR0/BAR2/BAR1/BAR3 Registers (SATA I/O Register for IDE mode)

BAR0/BAR2 uses 8 bytes of I/O space. BAR0 is used for Primary channel and BAR2 is used for Secondary

channel during IDE native mode. BAR1/BAR3 uses 2 bytes of I/O space. BAR1 is used for Primary channel

and BAR3 is used for Secondary channel during IDE native mode.

Address (hex) Name and Function

Compatibility Mode Native Mode (Offset) Read Function Write Function

IDE Command Block Registers

Primary Secondary BAR0/BAR2

1F0 170 (Primary or Secondary)

Base Address 0 + 0

1F1 171 (Primary or Secondary)

Base Address 0 + 1

1F2 172 (Primary or Secondary)

Base Address 0 + 2

1F3 173 (Primary or Secondary)

Base Address + 3

1F4 174 (Primary or Secondary)

Base Address + 4

1F5 175 (Primary or Secondary)

Base Address + 5

1F6 176 (Primary or Secondary)

Base Address + 6

1F7 177 (Primary or Secondary)

Base Address + 7

IDE Control Block Registers

Primary Secondary BAR1/BAR3

3F6 376 (Primary or Secondary)

Base Address + 2

Data (16 bit) Data (16 bit)

Error register Features register

Sector Count Sector Count

Sector Number Sector Number

Cylinder Low Cylinder Low

Cylinder High Cylinder High

Drive/Head Drive/Head

Status Command

Alternate Status Device Control

2.1.3 BAR4 Registers (SATA I/O Register for IDE mode)

BAR4 uses 16 bytes of I/O space. The Bus-master interface base address register (BAR4) defines the base

address of the IO spare.

Register Name Offset Address

[Primary/Secondary]

Bus-master IDE Command 00h/08h

Bus-master IDE Status 02h/0Ah

Descriptor Table Pointer 04h/0Ch

Bus-master IDE Command - RW- 8 bits - [IO_Reg: BAR4 + 00/08h]

Field Name Bits Default Description

Bus Master IDE

Start/Stop

Reserved 2:1 Reserved.

Bus Master Read/Write 3 0b Bus Master IDE r/w (direction) control

Reserved 7:4 Reserved.

0 0b Bus Master IDE Start (1)/Stop (0).

This bit will not be reset by interrupt from IDE device. This must

be reset by soft ware (device driver).

0 = Memory -> IDE

1 = IDE -> Memory

This bit should not change during Bus Master transfer cycle, even

if terminated by Bus Master IDE stop.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 24

Page 25

Bus-master IDE Status - RW- 8 bits - [IO_Reg: BAR4 + 02/0Ah]

Field Name Bits Default Description

Bus Master Active 0 0b Bus Master IDE active. This bit is set to 1 when bit 0 in the Bus

Master IDE command address register is set to 1. The IDE host

controller sets this bit to 0 when the last transfer for a region is

performed. This bit is also set to 0 when bit 0 of the Bus Master

IDE command register is set to 0.

Bus Master DMA Error 1 0b IDE DMA error. This bit is set when the IDE host controller

encounters a target abort, master abort, or Parity error while

transferring data on the PCI bus. Write ‘1’ clears this bit

IDE Interrupt 2 0b IDE Interrupt. Indicates when an IDE device has asserted its

interrupt line. IRQ14 is used for the Primary channel and IRQ15 is

used for the secondary channel. If the interrupt status bit is set to

0, by writing a 1 to this bit while the interrupt line is still at the

active level, this bit remains 0 until another assertion edge is

detected on the interrupt line.

Reserved 4:3 Reserved.

Master Device DMA

Capable

Slave Device DMA

Capable

Simplex Only 7 0b Read Only

5 0b Device 0 (Master) DMA capable.

6 0b Device 1 (Slave) DMA capable.

Simplex only. This bit is hard-wired as 0.

Descriptor Table Pointer - RW- 32 bits - [IO_Reg: BAR4 + 04/0Ch]

Field Name Bits Default Description

Reserved 1:0 0h Reserved. Always read as 0’s.

Descriptor Table Base

Address

31:2 0000_0000h Base Address of Descriptor Table. These bits correspond to

Address [31-02].

2.1.4 BAR5 Registers

These are the AHCI memory map registers. The base address is defined through the ABAR (BAR5) register.

Register Name Offset Address

Generic Host Control 00h-23h

Reserved

Vendor Specific registers A0h-FFh

Port 0 port control registers 100h-17Fh

Port 1 port control registers 180h-1FFh

Port 2 port control registers 200h-27Fh

Port 3 port control registers 280h-2FFh

24h-9Fh

2.1.4.1 Generic Host Control

The following registers apply to the entire HBA.

Register Name Offset Address

Host Capabilities(CAP) 00h-03h

Global Host Control(GHC) 04h-07h

Interrupt Status(IS) 08h-0Bh

Ports Implemented(PI) 0Ch-0Fh

Version(VS) 10h-13h

Command Completion Coalescing Control(CCC_CTL) 14h-17h

Command Completion Coalescing Ports(CCC_PORTS) 18h-1Bh

Enclosure Management Location(EM_LOC) 1Ch-1Fh

Enclosure Management Control(EM_CTL) 20h-23h

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 25

Page 26

HBA Capabilities – R - 32bits [Mem_reg: ABAR + 00h]

Field Name Bits Default Description

Number of Ports(NP) 4:0 00011b 0’s based value indicating the maximum number of ports

supported by the HBA silicon. A maximum of 32 ports can be

supported. A value of ‘0h’, indicating one port, is the

minimum requirement. Note that the number of ports

indicated in this field may be more than the number of ports

indicated in the GHC.PI register.

Supports External SATA

(SXS)

Enclosure Management

Supported (EMS)

Command Completion

Coalescing Supported

(CCCS)

Number of Command

Slots (NCS)

Partial State Capable

(PSC)

Slumber State Capable

(SSC)

PIO Multiple DRQ Block

(PMD)

FIS-based Switching

Supported (FBSS)

5 0b When set to ‘1’, indicates that the HBA has one or more

Serial ATA ports that has a signal only connector that is

externally accessible. If this bit is set to ‘1’, software may

refer to the PxCMD.ESP bit to determine whether a specific

port has its signal connector externally accessible as a signal

only connector (i.e. power is not part of that connector).

When the bit is cleared to ‘0’, indicates that the HBA has no

Serial ATA ports that have a signal only connector externally

accessible.

6 0b When set to ‘1’, indicates that the HBA supports enclosure

management. When enclosure management is supported,

the HBA has implemented the EM_LOC and EM_CTL global

HBA registers. When cleared to ‘0’, indicates that the HBA

does not support enclosure management and the EM_LOC

and EM_CTL global HBA registers are not implemented.

7 1b When set to ‘1’, indicates that the HBA supports command

completion coalescing. When command completion

coalescing is supported, the HBA has implemented the

CCC_CTL and the CCC_PORTS global HBA registers.

When cleared to ‘0’, indicates that the HBA does not support

command completion coalescing and the CCC_CTL and

CCC_PORTS global HBA registers are not implemented.

12:8 11111b 0’s based value indicating the number of command slots per

port supported by this HBA. A minimum of 1 and maximum

of 32 slots per port can be supported. The same number of

command slots is available on each implemented port.

13 1b Indicates whether the HBA can support transitions to the

Partial state. When cleared to ‘0’, software must not allow

the HBA to initiate transitions to the Partial state via

aggressive link power management nor the PxCMD.ICC field

in each port, and the PxSCTL.IPM field in each port must be

programmed to disallow device initiated Partial requests.

When set to ‘1’, HBA and device initiated Partial requests can

be supported.

14 1b Indicates whether the HBA can support transitions to the

Slumber state. When cleared to ‘0’, software must not allow

the HBA to initiate transitions to the Slumber state via

aggressive link power management nor the PxCMD.ICC field

in each port, and the PxSCTL.IPM field in each port must be

programmed to disallow device initiated Slumber requests.

When set to ‘1’, HBA and device initiated Slumber requests

can be supported.

15 1b If set to ‘1’, the HBA supports multiple DRQ block data

transfers for the PIO command protocol. If cleared to ‘0’ the

HBA only supports single DRQ block data transfers for the

PIO command protocol.

16 0b When set to ‘1’, indicates that the HBA supports Port

Multiplier FIS-based switching. When cleared to ‘0’, indicates

that the HBA does not support FIS-based switching. AHCI

1.0 and 1.1 HBAs shall have this bit cleared to ‘0’.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 26

Page 27

HBA Capabilities – R - 32bits [Mem_reg: ABAR + 00h]

Field Name Bits Default Description

Supports Port Multiplier

(SPM)

Supports AHCI mode

only (SAM)

Supports Non-Zero DMA

Offsets (SNZO)

Interface Speed Support

(ISS)

Supports Command List

Override (SCLO)

Supports Activity LED

(SAL)

Supports Aggressive

Link Power Management

(SALP)

Supports Staggered

Spin-up (SSS)

Supports Mechanical

Presence Switch (SMPS)

Supports SNotification

Register (SSNTF)

17 1b Indicates whether the HBA can support a Port Multiplier.

When set, a Port Multiplier using command-based switching

is supported. When cleared to ‘0’, a Port Multiplier is not

supported, and a Port Multiplier may not be attached to this

HBA.

18 0b The SATA controller may optionally support AHCI access

mechanisms only. A value of '0' indicates that in addition to

the native AHCI mechanism (via ABAR), the SATA controller

implements a legacy, task-file based register interface such

as SFF-8038i. A value of '1' indicates that the SATA

controller does not implement a legacy, task-file based

register interface.

19 0b When set to ‘1’, indicates that the HBA can support non-zero

DMA offsets for DMA Setup FISes. This bit is reserved for

future AHCI enhancements. AHCI 1.0 and 1.1 HBAs shall

have this bit cleared to ‘0’.

23:20 2h

24 1b When set to ‘1’, the HBA supports the PxCMD.CLO bit and its

25 1b When set to ‘1’, the HBA supports a single activity indication

26 1b When set to ‘1’, the HBA can support auto-generating link

27 0b When set to ‘1’, the HBA supports staggered spin-up on its

28 1b When set to ‘1’, the HBA supports mechanical presence

29 1b

Indicates the maximum speed the HBA can support on its

ports. These encodings match the system software

programmable PxSCTL.DET.SPD field. Values are:

Bits Definition

0000 Reserved

0001 Gen 1 (1.5 Gbps)

0010

0011 - 1111 Reserved

associated function. When cleared to ‘0’, the HBA is not

capable of clearing the BSY and DRQ bits in the Status

register in order to issue a software reset if these bits are still

set from a previous operation.

output pin. This pin can be connected to an LED on the

platform to indicate device activity on any drive. When

cleared to ‘0’, this function is not supported.

requests to the Partial or Slumber states when there are no

commands to process. When cleared to ‘0’, this function is

not supported and software shall treat the PxCMD.ALPE and

PxCMD.ASP bits as reserved.

ports, for use in balancing power spikes. When cleared to ‘0’,

this function is not supported. This value is loaded by the

BIOS prior to OS initialization.

switches on its ports for use in hot plug operations. When

cleared to ‘0’, this function is not supported. This value is

loaded by the BIOS prior to OS initialization.

When set to ‘1’, the

HBA supports the PxSNTF

(SNotification) register and its associated functionality.

When cleared to ‘0’, the HBA does not support the

PxSNTF (SNotification) register and its associated

functionality.

Gen 1 (1.5 Gbps) and Gen 2 (3

Gbps)

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 27

Page 28

HBA Capabilities – R - 32bits [Mem_reg: ABAR + 00h]

Field Name Bits Default Description

Supports Native

Command Queuing

(SNCQ)

Supports 64-bit

Addressing (S64A)

30 1b Indicates whether the HBA supports Serial ATA native

command queuing. If set to ‘1’, an HBA shall handle DMA

Setup FISes natively, and shall handle the auto-activate

optimization through that FIS. If cleared to ‘0’, native

command queuing is not supported and software should not

issue any native command queuing commands.

31 1b Indicates whether the HBA can access 64-bit data structures.

When set to ‘1’, the HBA shall make the 32-bit upper bits of

the port DMA Descriptor, the PRD Base, and each PRD entry

read/write. When cleared to ‘0’, these are read-only and

treated as ‘0’ by the HBA.

Global HBA Control – RW - 32bits [Mem_reg: ABAR + 04h]

Field Name Bits Default Description

HBA Reset (HR) 0 0b

Interrupt Enable (IE) 1 0b This global bit enables interrupts from the HBA. When

MSI Revert to Single

Message (MRSM)

Reserved 30:3 Reserved.

2 0b

When set by SW, this bit causes an internal reset of the HBA.

All state machines that relate to data transfers and queuing

shall return to an idle condition, and all ports shall be reinitialized via COMRESET (if staggered spin-up is not

supported). If staggered spin-up is supported, then it is the

responsibility of software to spin-up each port after the reset

has completed.

When the HBA has performed the reset action, it shall reset

this bit to ‘0’. A software write of ‘0’ shall have no effect. For

a description on which bits are reset when this bit is set.

cleared (reset default), all interrupt sources from all ports are

disabled. When set, interrupts are enabled.

Read Only

When set to ‘1’ by hardware, indicates that the HBA

requested more than one MSI vector but has reverted to

using the first vector only. When this bit is cleared to ‘0’, the

HBA has not reverted to single MSI mode (i.e. hardware is

already in single MSI mode, software has allocated the

number of messages requested, or hardware is sharing

interrupt vectors if MC.MME < MC.MMC).

The HBA may revert to single MSI mode when the number of

vectors allocated by the host is less than the number

requested. This bit shall only be set to ‘1’ when the following

conditions hold:

• MC.MSIE = ‘1’ (MSI is enabled)

• MC.MMC > 0 (multiple messages requested)

• MC.MME > 0 (more than one message allocated)

• MC.MME != MC.MMC (messages allocated not

equal to number requested)

When this bit is set to ‘1’, single MSI mode operation is in use

and software is responsible for clearing bits in the IS register

to clear interrupts.

This bit shall be cleared to ‘0’ by hardware when any of the

four conditions stated is false. This bit is also cleared to ‘0’

when MC.MSIE = ‘1’ and MC.MME = 0h. In this case, the

hardware has been programmed to use single MSI mode,

and is not “reverting” to that mode.

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 28

Page 29

Global HBA Control – RW - 32bits [Mem_reg: ABAR + 04h]

Field Name Bits Default Description

AHCI Enable (AE) 31 0b

Interrupt Status - RW -32 bits [Mem_reg: ABAR + 08h]

Field Name Bits Default Description

Interrupt Pending Status

(IPS)

Write 1 to clear these status bits.

31:0 0000_

0000h

When set, indicates that communication to the HBA shall be

via AHCI mechanisms. This can be used by an HBA that

supports both legacy mechanisms (such as SFF-8038i) and

AHCI to know when the HBA is running under an AHCI

driver.

When set, software shall only communicate with the HBA

using AHCI. When cleared, software shall only communicate

with the HBA using legacy mechanisms. When cleared

FISes are not posted to memory and no commands are sent

via AHCI mechanisms.

Software shall set this bit to ‘1’ before accessing other AHCI

registers.

If set, indicates that the corresponding port has an interrupt

pending. Software can use this information to determine

which ports require service after an interrupt.

The IPS[x] bit is only defined for ports that are implemented

or for the command completion coalescing interrupt defined

by CCC_CTL.INT. All other bits are reserved.

Ports Implemented Register - R -32 bits [Mem_reg: ABAR + 0Ch]

Field Name Bits Default Description

Port Implemented (PI) 31:0 0000000Fh This register is bit significant. If a bit is set to ‘1’, the

corresponding port is available for software to use. If a bit is

cleared to ‘0’, the port is not available for software to use.

The maximum number of bits set to ‘1’ shall not exceed

CAP.NP + 1, although the number of bits set in this register

may be fewer than CAP.NP + 1. At least one bit shall be set

to ‘1’.

AHCI Version- R – 32 bits [Mem_reg: ABAR + 10h]

Field Name Bits Default Description

Minor Version Number

(MNR)

Major Version Number

(MJR)

Version: V1.10

15:0 0100h Indicates the minor version is “10”.

31:16 0001h Indicates the major version is “1”

Command Completion Coalescing Control(CCC_CTL) - RW – 32 bits [Mem_reg: ABAR + 14h]

Field Name Bits Default Description

CCC_CTL Enable 0 0b When cleared to ‘0’, the command completion coalescing

feature is disabled and no CCC interrupts are generated.

When set to ‘1’, the command completion coalescing feature

is enabled and CCC interrupts may be generated based on

timeout or command completion conditions. Software shall

only change the contents of the TV and CC fields when EN is

cleared to ‘0’. On transition of this bit from ‘0’ to ‘1’, any

updated values for the TV and CC fields shall take effect.

Reserved 2:1 Reserved

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 29

Page 30

Command Completion Coalescing Control(CCC_CTL) - RW – 32 bits [Mem_reg: ABAR + 14h]

Field Name Bits Default Description

CCC Interrupt (INT) 7:3 1Fh Read Only

Specifies the interrupt used by the CCC feature. This

interrupt must be marked as unused in the Ports

Implemented (PI) register by the corresponding bit being set

to ‘0’. Thus, the CCC interrupt corresponds to the interrupt

for an unimplemented port on the controller. When a CCC

interrupt occurs, the IS.IPS[INT] bit shall be asserted to ‘1’.

This field also specifies the interrupt vector used for MSI.

Command Completions

(CC)

Timeout Value (TV) 31:16 0001h The timeout value is specified in 1 millisecond intervals. The

15:8 01h Specifies the number of command completions that are

necessary to cause a CCC interrupt. The HBA has an

internal command completion counter, hCccComplete.

hCccComplete is incremented by one each time a selected