Page 1

AMD 780G Family

Register Programming Requirements

For the RS780, RS780C, RS780D, RS780M,

RS780E, RS780MC, and RX781

Technical Reference Manual

Rev. 1.01

P/N: 43291_rs780_rpr_pub_1.01

© 2009 Advanced Micro Devices, Inc.

Page 2

Trademarks

AMD, the AMD Arrow logo, AMD Athlon, ATI, Mobility, PowerPlay, CrossFire, Radeon, and combinations thereof, are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Disclaimer

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect

to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice.

No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD's Standard

Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the

implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications

intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or

environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

© 2009 Advanced Micro Devices, Inc. All rights reserved.

Page 3

Table of Contents

Chapter 1: Introduction

1.1 About This Manual .............................................................................................................................................................1-1

Chapter 2: I/O Control (IOC)

2.1 RS780 Device Mapping ......................................................................................................................................................2-1

2.2 RS780 Device IDs...............................................................................................................................................................2-1

2.3 Configuration Access to RS780 Device Registers..............................................................................................................2-2

2.3.1 Using CF8/CFC I/O Pair ......................................................................................................................................2-2

2.3.2 Using BAR3 Memory Mapped Register Access..................................................................................................2-2

2.4 General RS780 IOC Programming After Boot-Up.............................................................................................................2-3

2.5 Miscellaneous IOC Features Programming ........................................................................................................................2-4

2.5.1 Power Management Register Access Setup .........................................................................................................2-4

2.5.2 S3 PME_Turn_Off/PME_To_Ack Sequence.......................................................................................................2-4

2.5.3 Disabling Internal Graphics..................................................................................................................................2-4

2.5.4 GFX MSI Enable..................................................................................................................................................2-4

2.5.5 Disabling Bus0 Device 3 PCI Bridge (Secondary External PCIE Graphics).......................................................2-4

2.5.6 Disabling Bus0 Device 3 PCI Bridges (Dev2, Dev4 to Dev7, Dev9-Dev10) ......................................................2-4

2.6 Broadcast CPU Requests to Dual External Graphics PCIE Devices ..................................................................................2-5

2.7 Enabling/Disabling Peer-To-Peer Traffic Access...............................................................................................................2-6

2.8 Enabling/Disabling MVPU .................................................................................................................................................2-6

2.9 IOC Dynamic Clock Setup .................................................................................................................................................2-6

2.10 Interrupt Mapping .............................................................................................................................................................2-7

2.11 GSM Enable......................................................................................................................................................................2-7

Chapter 3: Clock Settings

3.1 SBIOS Memory Clock Initialization...................................................................................................................................3-1

3.1.1 UMA Mode ..........................................................................................................................................................3-1

3.1.2 Side-Port Async Mode .........................................................................................................................................3-1

3.2 Memory Clock Changes For POWERPLAY......................................................................................................................3-3

3.3 Switching Back From PM Mode to Nominal Mode ...........................................................................................................3-4

3.4 Power Saving Settings ........................................................................................................................................................3-5

3.4.1 Enabling Dynamic Clocks ...................................................................................................................................3-5

3.4.2 Powering Down Efuse and Strap Block Clocks After Boot-Up...........................................................................3-5

3.4.3 Powering Down Graphics Core and Memory Clocks in Northbridge-Only Mode ..............................................3-6

3.4.4 Powering Down IOC GFX Clock in No External Graphics Mode ......................................................................3-6

3.4.5 PWM Controller ...................................................................................................................................................3-6

3.5 DOS Mode Power Saving ...................................................................................................................................................3-7

3.6 HTPLL VCO Mode Setting ................................................................................................................................................3-7

Chapter 4: Memory Initialization

4.1 Memory Initialization .........................................................................................................................................................4-1

Chapter 5: PCIE Initialization

5.1 Introduction.........................................................................................................................................................................5-1

5.2 PCI Express Configuration Space.......................................................................................................................................5-1

5.2.1 PCIE Port Configuration Space............................................................................................................................5-1

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

Table of Contents-1

Page 4

Table of Contents

5.2.2 PCIE Core Index Space ....................................................................................................................................... 5-2

5.2.3 PCIE Port Index Space ........................................................................................................................................ 5-2

5.2.4 PCIE Extended Configuration Space................................................................................................................... 5-2

5.3 Power-On and Reset State.................................................................................................................................................. 5-4

5.4 PCIE GFX Configurations ................................................................................................................................................. 5-4

5.4.1 PCIE Modes Only................................................................................................................................................ 5-4

5.4.2 DDI Modes Only ................................................................................................................................................. 5-5

5.4.3 PCIE and DDI Combined Modes ........................................................................................................................ 5-6

5.5 PCIE GPPSB Configurations ............................................................................................................................................. 5-6

5.5.1 Device Remapping............................................................................................................................................... 5-7

5.5.2 Default Configuration E (STRAP_BIF_LINK_CONFIG_GPPSB = 4’b0100) .................................................. 5-7

5.5.3 Configuration A (STRAP_BIF_LINK_CONFIG_GPPSB = 4’b0000) .............................................................. 5-8

5.5.4 Configuration B (STRAP_BIF_LINK_CONFIG_GPPSB = 4’b0001)............................................................... 5-8

5.5.5 Configuration C (STRAP_BIF_LINK_CONFIG_GPPSB = 4’b0010)............................................................... 5-8

5.5.6 Configuration D (STRAP_BIF_LINK_CONFIG_GPPSB = 4’b0011) .............................................................. 5-8

5.5.7 Switching GPPSB Configurations....................................................................................................................... 5-9

5.6 PCIE GPP Configurations................................................................................................................................................ 5-10

5.6.1 Default Configuration D .................................................................................................................................... 5-10

5.6.2 Configuration C ................................................................................................................................................. 5-10

5.7 PCIE Link Training Sequence...........................................................................................................................................5-11

5.8 Overall PCIE Programming Sequence ............................................................................................................................. 5-13

5.9 PCIE-GFX Core Initialization.......................................................................................................................................... 5-14

5.9.1 REFCLK Options .............................................................................................................................................. 5-14

5.9.2 Lane Reversal (CMOS Option - Disabled by Default)...................................................................................... 5-15

5.9.3 GFX Overclocking............................................................................................................................................. 5-15

5.9.4 Reset PCIE-GFX Core....................................................................................................................................... 5-16

5.9.5 Reset PCIE-GFX Slot ........................................................................................................................................ 5-16

5.9.6 Delay Training Option (CMOS Option – Default 2ms) ................................................................................... 5-16

5.9.7 Transmitter Drive Strength (CMOS Option – Default 22mA) .......................................................................... 5-16

5.9.8 Program PCIE Memory Mapped Configuration Space ..................................................................................... 5-17

5.9.9 GEN1 Software Compliance (CMOS Option – Disabled by Default) .............................................................. 5-17

5.9.10 GEN2 Software Compliance (CMOS Option – Disabled by Default) .............................................................. 5-18

5.9.11 De-Emphasis Strength -3.5dB/-6dB in GEN2 (CMOS Option - Disabled by Default) .................................... 5-18

5.9.12 Core Initialization .............................................................................................................................................. 5-19

5.9.13 Autonomous GEN2 Speed Change (CMOS Option – Disabled by Default) .................................................... 5-21

5.9.14 Link Training ..................................................................................................................................................... 5-22

5.9.15 Power Down Control ......................................................................................................................................... 5-22

5.9.16 Software Initiated Speed Change to GEN2 (CMOS Option – Disabled by Default)

5.9.17 Active State Power Management (ASPM) ........................................................................................................ 5-31

5.9.18 Clock Gating...................................................................................................................................................... 5-34

5.10 PCIE-GPPSB and PCIE-GPP Cores Initialization......................................................................................................... 5-35

5.10.1 REFCLK Options .............................................................................................................................................. 5-35

5.10.2 Lane Reversal (CMOS Option – Disabled by Default) ..................................................................................... 5-35

5.10.3 Transmitter Drive Strength (CMOS Option – Disabled 22mA)........................................................................ 5-37

5.10.4 Reset PCIE-GPP Slot......................................................................................................................................... 5-37

5.10.5 GEN1 Software Compliance (CMOS Option – Disabled by Default) .............................................................. 5-37

5.10.6 GEN2 Software Compliance (CMOS Option – Disabled by Default) .............................................................. 5-38

5.10.7 De-Emphasis Strength -3.5dB/-6dB in GEN2 (CMOS Option - Disabled by Default) .................................... 5-39

5.10.8 Core Initialization .............................................................................................................................................. 5-40

5.10.9 Device Remapping............................................................................................................................................. 5-43

5.10.10 Dynamic Slave CPL Buffer Allocation (CMOS Option – Enabled by Default) ............................................... 5-43

5.10.11 Autonomous GEN2 Speed Change (CMOS Option – Disabled by Default) .................................................... 5-45

5.10.12 Link Training ..................................................................................................................................................... 5-46

5.10.13 Power Down Control ......................................................................................................................................... 5-46

........................................ 5-29

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

Table of Contents-2

Page 5

Table of Contents

5.10.14 Software Initiated Speed Change to GEN2 (CMOS Option – Disabled by Default).........................................5-49

5.10.15 Active State Power Management (ASPM).........................................................................................................5-51

5.10.16 Clock Gating.......................................................................................................................................................5-54

5.10.17 Non-Posted VC1 Traffic Support on SB Link (CMOS Option – Disabled by Default) ....................................5-55

5.11 Dynamic Link Width Control (CMOS Option – Disabled by Default) ..........................................................................5-56

5.12 PCI Enumeration and Special Features Programming Sequence ...................................................................................5-59

5.12.1 PCI Enumeration ................................................................................................................................................5-59

5.12.2 Program the Common Clock Configuration.......................................................................................................5-59

5.12.3 Slot Power Limit (CMOS Option - Default 75W) .............................................................................................5-59

5.12.4 Update Hot-Plug Info .........................................................................................................................................5-59

5.12.5 Disable Immediate Timeout on Link Down .......................................................................................................5-59

5.12.6 Register Locking ................................................................................................................................................5-60

5.12.7 Optional Features................................................................................................................................................5-60

5.12.8 Dynamic Link Width Control.............................................................................................................................5-60

5.12.9 Special Features Programming Sequence ..........................................................................................................5-60

Chapter 6: Graphics Core Settings

6.1 Bus Interface (BIF) .............................................................................................................................................................6-1

6.2 DEVICE_IDs, MAJOR_REV_IDs, MINOR_REV_IDs....................................................................................................6-1

6.3 CFG_ATI_REV_ID ............................................................................................................................................................6-1

6.4 GFX_DEBUG_BAR...........................................................................................................................................................6-1

6.5 Gpuioreg BAR For Accessing nbconfig Registers (A12)...................................................................................................6-2

6.6 Initialization ........................................................................................................................................................................6-2

6.7 Master Abort Status ............................................................................................................................................................6-3

6.8 HDP/MC Write Combiner ..................................................................................................................................................6-3

6.9 Graphics UMA FB Size ......................................................................................................................................................6-3

6.10 Suggested FB Interleaving Ratios.....................................................................................................................................6-4

Chapter 7: PCIE Initialization for DDI

7.1 PCIE Modes ........................................................................................................................................................................7-1

7.1.1 Case 1: PCIE 1x16 GFX.......................................................................................................................................7-1

7.1.2 Case 2: PCIE 1x8 GFX on Lanes 0-7...................................................................................................................7-1

7.1.3 Case 3: PCIE 1x8 GFX on Lanes 8-15.................................................................................................................7-2

7.1.4 Case 4: PCIE 2x8 .................................................................................................................................................7-3

7.1.5 Case 5: PCIE 1x4 GPP on Lanes 0-3 ..................................................................................................................7-3

7.1.6 Case 6: PCIE 1x4 GPP on Lanes 4-7 ..................................................................................................................7-3

7.1.7 Case 7: PCIE 1x4 GPP on Lanes 8-11 ................................................................................................................7-3

7.1.8 Case 8: PCIE 1x4 GPP on Lanes 12-15 ...............................................................................................................7-3

7.1.9 Case 9: PCIE 2x4 GPPs on Lanes 0-7..................................................................................................................7-4

7.1.10 Case 10: PCIE 1x4 GPP on Lanes 0-3 and 1x4 GPP on Lanes 8-11 ...................................................................7-5

7.1.11 Case 11: PCIE 1x4 GPP on Lanes 0-3 and 1x4 GPP on Lanes 12-15 .................................................................7-5

7.1.12 Case 12: PCIE 1x4 GPP on Lanes 4-7 and 1x8 GFX on Lanes 8-15...................................................................7-5

7.1.13 Case 13: PCIE 2x4 GPPs on Lanes 8-15..............................................................................................................7-5

7.1.14 Case 14: PCIE 1x8 GFX on Lanes 0-7 and 1x4 GPP on Lanes 8-11...................................................................7-7

7.1.15 Case 15: PCIE 1x8 GFX on Lanes 0-7 and 1x4 GPP on Lanes 12-15.................................................................7-7

7.1.16 Case 16: PCIE 1x8 GFX on Lanes 8-15 and 1x4 GPP on Lanes 4-7...................................................................7-9

7.1.17 Case 17: PCIE 1x4 GPP on Lanes 0-3 and 1x8 GFX on Lanes 8-15.................................................................7-10

7.2 DDI Modes........................................................................................................................................................................7-11

7.2.1 DDI Programming Sequence..............................................................................................................................7-11

7.2.2 Initialization Sequence .......................................................................................................................................7-14

7.2.3 Adjustable PHY Parameters for Better Quality Display ....................................................................................7-43

7.3 PCIE + DDI Modes...........................................................................................................................................................7-45

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

Table of Contents-3

Page 6

Table of Contents

Chapter 8: HTIU Settings

8.1 HT Link Initialization......................................................................................................................................................... 8-1

8.2 HTIU Indirect Register Space ............................................................................................................................................ 8-1

8.3 CPU Register Access ......................................................................................................................................................... 8-1

8.3.1 Normal Registers ................................................................................................................................................. 8-1

8.3.2 PHY Dataport Register Access............................................................................................................................ 8-1

8.4 Changing to High-Speed Mode.......................................................................................................................................... 8-1

8.4.1 Identifying Supported HT Frequencies ............................................................................................................... 8-1

8.4.2 Changing to High-Speed HyperTransport 1 Mode.............................................................................................. 8-2

8.4.3 Changing to HyperTransport 3 Mode.................................................................................................................. 8-2

8.4.4 HT Link Width + LVM Support.......................................................................................................................... 8-5

8.5 Workarounds ..................................................................................................................................................................... 8-5

8.5.1 LPC DMA Deadlock ........................................................................................................................................... 8-5

8.5.2 CPU Access To UMA Memory Deadlock .......................................................................................................... 8-6

8.6 HT Register Settings .......................................................................................................................................................... 8-6

8.6.1 HT General Register Settings .............................................................................................................................. 8-6

8.6.2 UnitID Clumping ................................................................................................................................................. 8-7

8.6.3 Isochronous Flow-Control Mode......................................................................................................................... 8-7

8.6.4 AMD Family 10h Processor Buffer Allocation Settings .................................................................................... 8-8

8.6.5 AMD Family 11h Buffer Allocation Settings ................................................................................................... 8-17

8.6.6 K8 Buffer Allocation Settings (Special Settings For UMA Mode)................................................................... 8-24

8.6.7 Additional UMA Settings .................................................................................................................................. 8-24

8.6.8 Transmitter Deemphasis ................................................................................................................................... 8-25

8.7 Power Management Settings............................................................................................................................................ 8-25

8.7.1 AMD Family 10h PMM Programming ............................................................................................................. 8-25

8.7.2 AMD Family 11h PMM Programming ............................................................................................................. 8-25

8.8 K8 PMM Programming.................................................................................................................................................... 8-25

8.8.1 K8 PMM1 Programming ................................................................................................................................... 8-26

8.8.2 Low-Power HyperTransport Features ............................................................................................................... 8-26

8.8.3 ATIVumaSysInfoRev3 Programming ............................................................................................................... 8-28

8.8.4 Generalized Stutter Mode .................................................................................................................................. 8-29

8.9 Programming Guidelines.................................................................................................................................................. 8-29

8.9.1 Debug Menu Features........................................................................................................................................ 8-29

Chapter 9: CLMC Programming

9.1 Global CLMC Settings....................................................................................................................................................... 9-1

9.1.1 CLMC Enable...................................................................................................................................................... 9-1

9.1.2 Default Inactive Lane State ................................................................................................................................. 9-1

9.2 Capability Registers ........................................................................................................................................................... 9-2

9.2.1 Programming Sequence ....................................................................................................................................... 9-2

9.3 Sub-Feature Registers ........................................................................................................................................................ 9-3

9.3.1 Programming the NBMCIND Registers.............................................................................................................. 9-3

9.4 CLMC Control Features..................................................................................................................................................... 9-4

9.4.1 CDLD (Centralized Dynamic Link Disconnection) ............................................................................................ 9-4

9.4.2 CDLC (Centralized Dynamic Link Configuration) ............................................................................................. 9-4

9.4.3 CDLW (Centralized Dynamic Link Width) ........................................................................................................ 9-9

9.5 CLMC Refresh Features..................................................................................................................................................... 9-9

9.5.1 CDLR (Centralized Disconnected Link Refresh)................................................................................................ 9-9

9.5.2 CILR (Centralized Inactive Lane Refresh).......................................................................................................... 9-9

9.6 CLMC Stutter Mode......................................................................................................................................................... 9-10

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

Table of Contents-4

Page 7

Table of Contents

Appendix A: Revision History

A.1 Rev. 1.06 (June 2009) ....................................................................................................................................................... A-1

A.2 Rev. 1.05 (April 2009) ...................................................................................................................................................... A-1

A.3 Rev. 1.04 (Jan 2009) ......................................................................................................................................................... A-1

A.4 Rev. 1.03 (June 2008) ....................................................................................................................................................... A-2

A.5 Rev 1.02 (February 2008) ................................................................................................................................................. A-3

A.6 Rev 1.01 (August 2007) .................................................................................................................................................... A-4

A.7 Rev 1.00 (June 2007) ........................................................................................................................................................ A-5

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

Table of Contents-5

Page 8

Table of Contents

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

Table of Contents-6

Page 9

1.1 About This Manual

This document is intended for BIOS engineers designing BIOSes for systems based on AMD’s 780G family of

northbridges. It describes the register programming requirements needed to ensure the proper functioning of the 780G

ASIC. Use this document in conjunction with the related AMD 780G Family Register Reference Guide and AMD 780G

Family BIOS Developer’s Guide.

Unless indicated otherwise, the programming information in this document applies to the following 780G variants (note

that Chapter 9 only applies to 780G mobile variants):

• RS780 (AMD 780G)

• RS780C (AMD 780V)

• RS780D (AMD 790GX)

• RS780E (AMD 780E)

• RS780M (AMD M780G)

• RS780MC (AMD M780V)

• RX781 (AMD M770) (Chapter 6 does not apply to the RX781 variant)

Some of the settings indicated in this document are workarounds for items that are expected to be solved in subsequent

ASIC revisions. This document will therefore be updated as frequently as required.

Chapter 1

Introduction

Changes and additions to the previous release of this document are highlighted in red. Refer to Appendix A: Revision

History at the end of this document for a detailed revision history.

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

1-1

Page 10

About This Manual

This page intentionally left blank.

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

1-2

Page 11

2.1 RS780 Device Mapping

The RS780 has the following devices:

• Bus0Dev0Fun0: Host bridge

• Bus0Dev0Fun1: Clock control

• Bus0Dev1: Internal graphics P2P bridge

• Bus0Dev2: PCIE P2P bridge (external graphics)

• Bus0Dev3: PCIE P2P bridge (external graphics)

• Bus0Dev4: PCIE P2P bridge

• Bus0Dev5: PCIE P2P bridge

• Bus0Dev6: PCIE P2P bridge

• Bus0Dev7: PCIE P2P bridge

• Bus0Dev9: PCIE P2P bridge

• Bus0Dev10: PCIE P2P bridge

• Bus0Dev8: NB/SB Link P2P bridge (hidden by default)

Note: Each device has a P2P bridge header, except Dev0, which has a PCI device header.

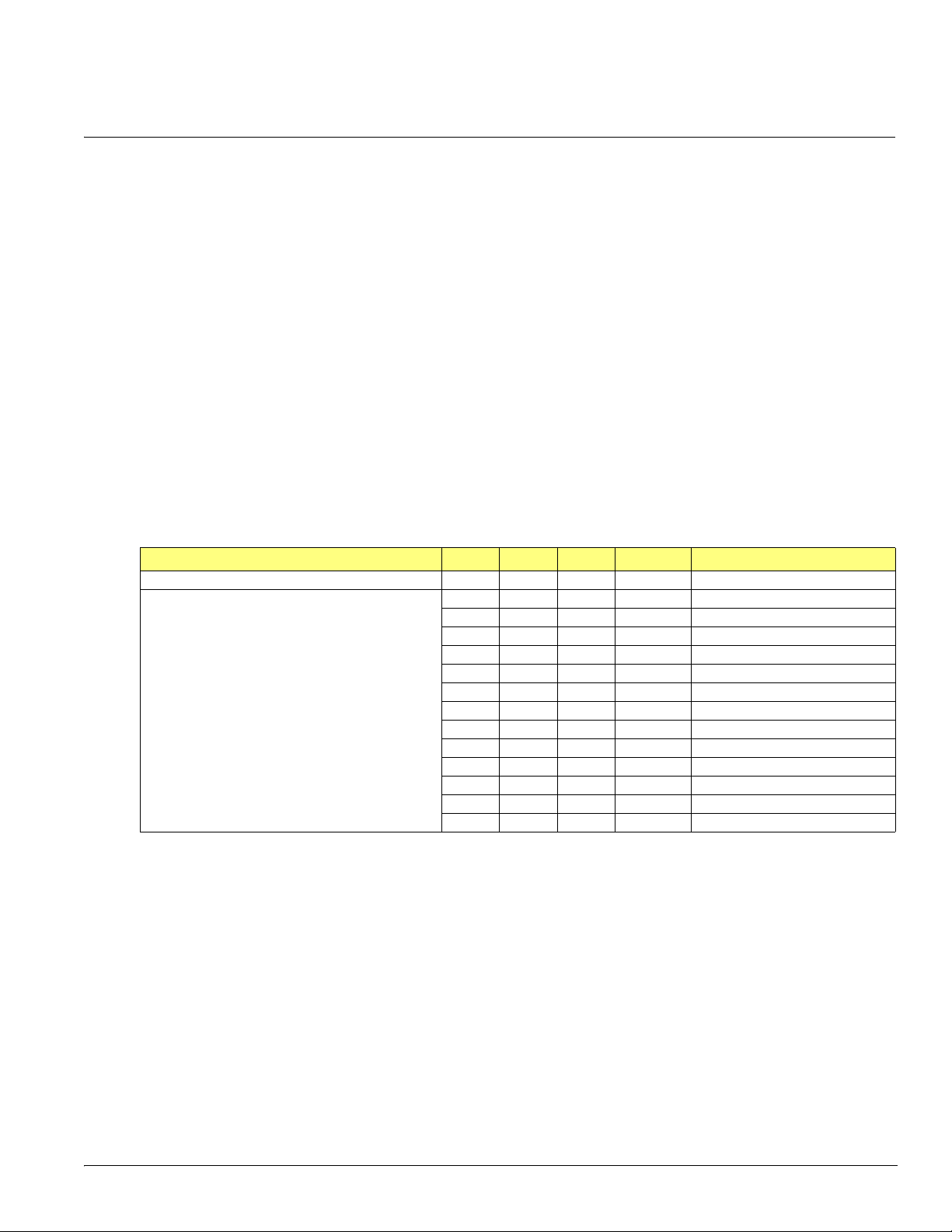

2.2 RS780 Device IDs

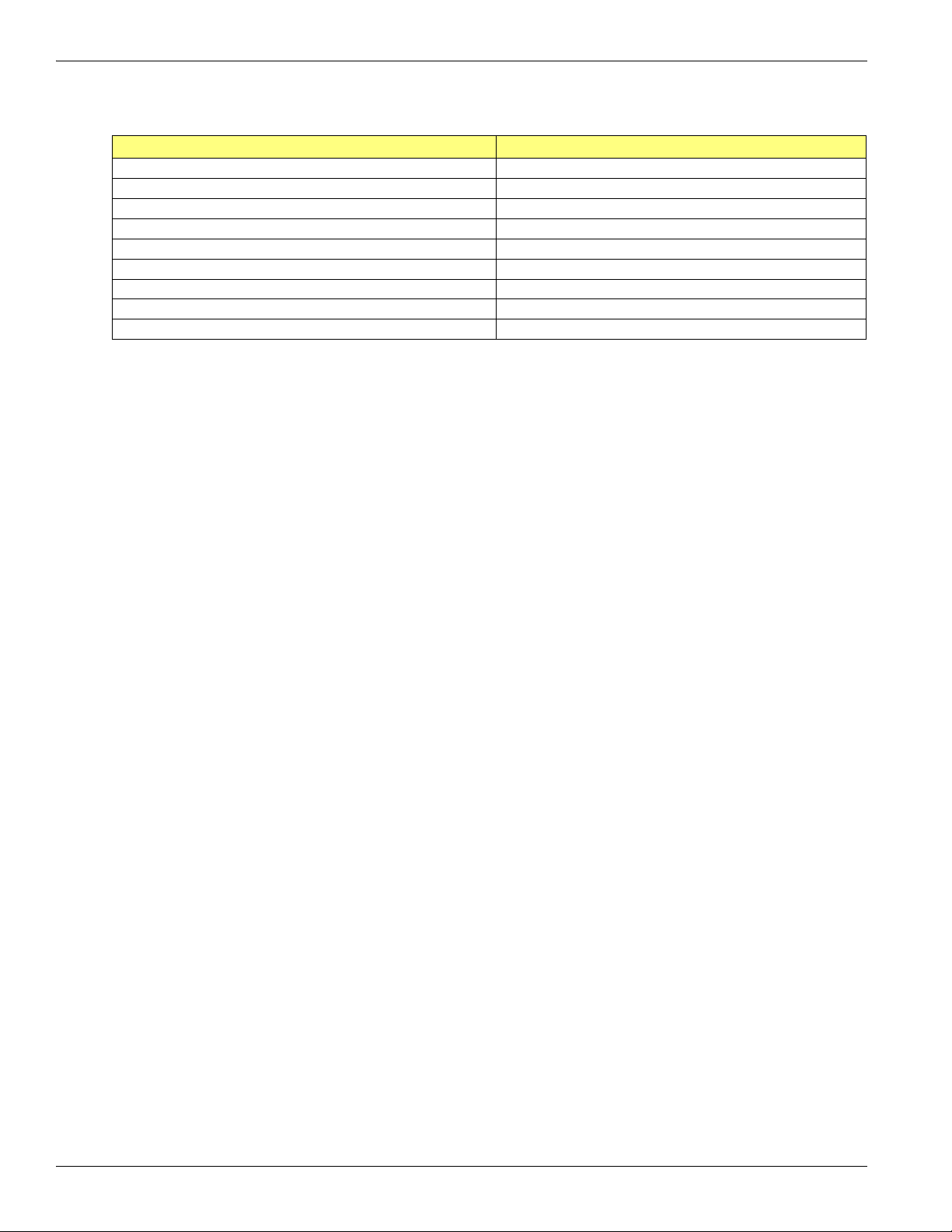

Table 2-1 RS780 Device IDs

Chapter 2

I/O Control (IOC)

Register RS780 RS780C RS780M RS780MC Description

NB_DEVICE_ID<nbcfg:0X02>DEVICE_ID [15:0] 0x9600 Northbridge configuration space ID

APC_DEVICE_ID<APCCFG:0x02>DEVICE_ID [15:0] 0x9602 Internal PCI-PCI bridge ID

0x9603 External GFX - port 0

0x960B External GFX - port 1

0x9610 0x9611 0x9612 0x9613 Internal graphics

0x9604 PCI-PCI bridge - Port 0

0x9605 PCI-PCI bridge - Port 1

0x9606 PCI-PCI bridge - Port 2

0x9607 PCI-PCI bridge - Port 3

0x9608 PCI-PCI bridge - Port 4

0x9609 PCI-PCI bridge - Port 5

0x960A PCI-PCI bridge (SB)

0x960F HD Audio controller

0x791A HDMI Audio codec

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

2-1

Page 12

Configuration Access to RS780 Device Registers

2.3 Configuration Access to RS780 Device Registers

Configuration access to the RS780 can be accomplished through one of the following two methods described in sections

2.3.1 and 2.3.2 below.

2.3.1 Using CF8/CFC I/O Pair

This method works for all registers of Dev0 and Dev1, and all PCI registers of Dev2 to Dev10. This method DOES NOT

work for PCIE extended registers of Dev2 to Dev10. The address mapping follows the standard PCI specification:

• Addr[11:8] = FunNum

• Addr[15:12] = DevNum

• Addr[23:16] = BusNum

• Addr[7:2] = RegNum

Note: For conventional CF8/CFC IO pair configuration access, the first IO write to CF8 (which is a register index access),

has to set Data[31] to indicate that this is a configuration access. Otherwise, it will be treated as a regular IO cycle.

2.3.2 Using BAR3 Memory Mapped Register Access

This method works for all PCI registers of Dev0, all PCI registers, and PCIE extended registers of Dev2 to Dev8. The

address mapping follows the PCIE specification:

• Addr[14:12] = FunNum

• Addr[19:15] = DevNum

• Addr[11:2] = RegNum (Addr[11:8] is an extended register field)

• Addr[20 + n-1:20] = BusNum *

• Addr[33:20 + n] = Reserved for BAR3 match *

* Note: ‘n’ indicates how many bits are allocated for the bus number. This value is decided by nbcfg0x84[18:16]. These

relations are listed in Table 2-2 below:

Table 2-2 nbcfg0x84[18:16] Relations

nbcfg0x84[18:16] n

3’b001 1

3’b010 2

3’b011 3

3’b100 4

3’b101 5

3’b110 6

3’b111 7

3’b000 8

The programming procedure to enable BAR3 is as follows:

• Step 1: Enable BAR3 register access (set nbcfg0x7C[30])

• Step 2: Program BAR3 bus range (nbcfg0x84[18:16]).

• Step 3: Program the BAR3 register (nbcfg0x1C[31:21] and nbcfg0x20[1:0])

• Step 4: Enable BAR3 decoding (set htiunbind 0x32[28]).

Note: nbcfg0x20 is the BAR3 memory upper address register (above 4G). The RS780 could support memory up to 16G,

so this register must be set correctly.

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

2-2

Page 13

2.4 General RS780 IOC Programming After Boot-Up

After system boot-up, all registers should keep the default values.

The BIOS starts the bus enumeration, and detects the following: Bus0Dev0Fun0, Dev0Fun1, Dev1Fun0, Dev1Fun1,

Dev2Fun0, Dev3Fun0, Dev4Fun0, Dev5Fun0, Dev6Fun0, Dev7Fun0. Then, for all of these PCI device headers or P2P

device headers, the BIOS enables IOSpace (0x04[0]) and MemSpaceEn (0x04[1]). It also defines the primary bus number,

the secondary bus number, and the subordinate bus number.

The following registers in Table 2-3 need to be programmed after boot-up. Note: After boot-up to Windows occurs, the

IOC register default values follow the values in this table.

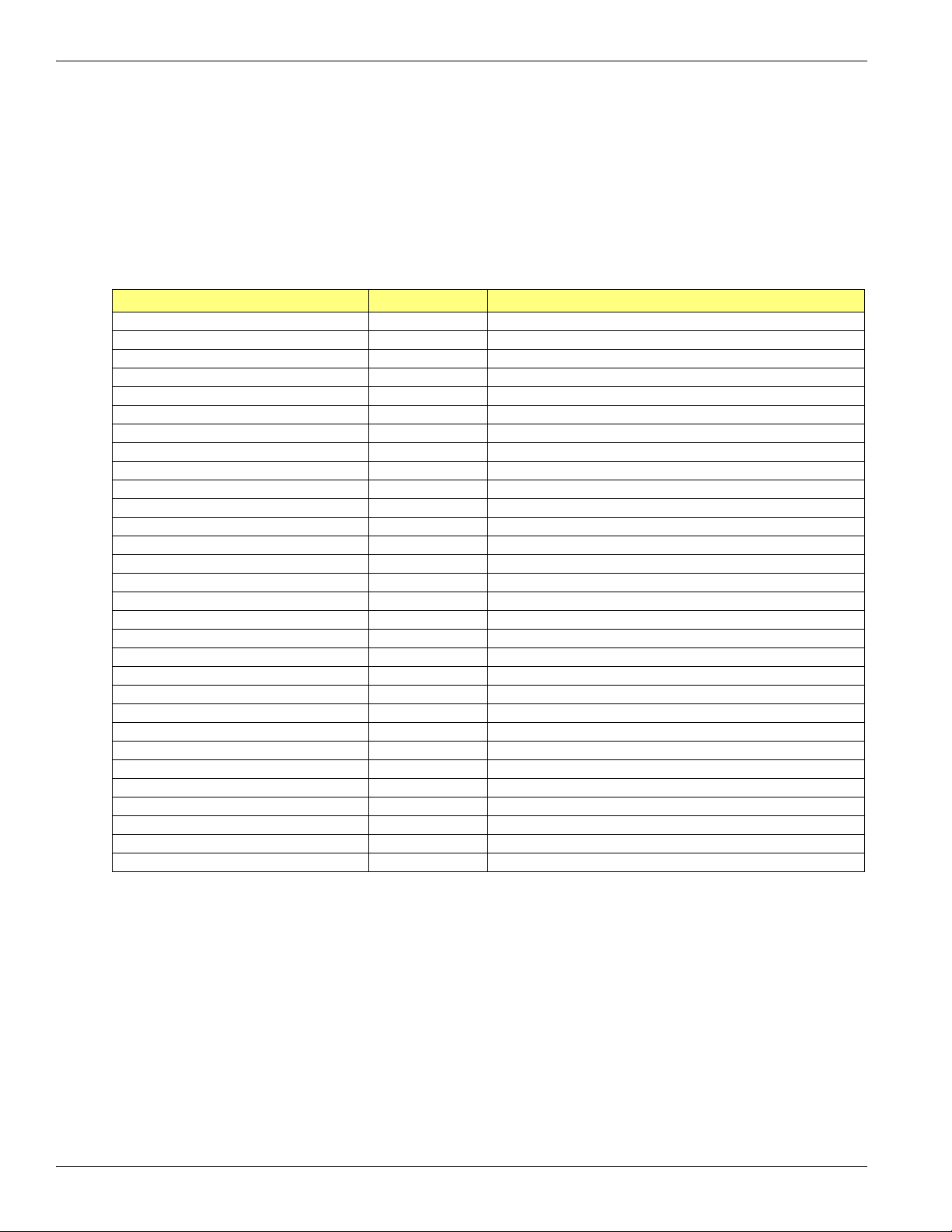

Table 2-3 Expected Register Values

Register Offset Expected Value

NB_BAR1_RCRB nbcfg0x14 32’hxxxx_xxxx

NB_BAR2_PM2 nbcfg0x18 32’hxxxx_xxxx

NB_BAR3_PCIEXP_MMCFG nbcfg0x1C 32’hxxxx_xxxx

NB_BAR3_UPPER_PCIEXP_MMCFG nbcfg0x20 32’h0000_000x

NB_PCI_CTRL nbcfg0x4C 32’h0000_0000_0x00_01x1_0010_0000_1100_00xx

NB_IO_CFG_CNTL nbcfg0x7C 32’h4000_0000

NB_PCI_ARB nbcfg0x84 32’b0000_0000_0000_0xxx_0000_00xx_1001_0101

IOC_DMA_ARBITER nbmisc0x09 32’hxxxx_xxxx

IOC_PCIE_CSR_COUNT nbmisc0x0A 32’hxxxx_xxxx

IOC_PCIE_CNTL nbmisc0x0B 32’h0000_0180

IOC_P2P_CNTL nbmisc0x0C 32’b0000_0000_0000_0000_0xx1_0111_xxxx_xx00

CMP_MSK_EOB nbmisc0x0D 32’hxxxx_xxxx

IOC_DMA_ARBITER nbmisc0x0E 32’hxxxx_xxxx

IOC_DMA_ARBITER nbmisc0x0F 32’hxxxx_xxxx

IOC_DMA_ARBITER nbmisc0x11 32’hxxxx_xxxx

NB_TOM_PCI nbmisc0x16 32’hxxxx_000x

NB_MMIOBASE nbmisc0x17 32’h0000_0000

NB_MMIOLIMIT nbmisc0x18 32’h0000_0000

NB_BROADCAST_BASE_LO nbmisc0x3A 32’hxxx0_0000

NB_BROADCAST_BASE_HI nbmisc0x3B 32’h0000_000x

NB_BROADCAST_CNTL nbmisc0x3C 32’hxxxx_xxxx

IOC_PCIE_D2_CNTL nbmisc0x51 32’h0010_0100

IOC_PCIE_D3_CNTL nbmisc0x53 32’h0010_0100

IOC_PCIE_D4_CNTL nbmisc0x55 32’h0010_0100

IOC_PCIE_D5_CNTL nbmisc0x57 32’h0010_0100

IOC_PCIE_D6_CNTL nbmisc0x59 32’h0010_0100

IOC_PCIE_D7_CNTL nbmisc0x5B 32’h0010_0100

IOC_PCIE_D9_CNTL nbmisc0x5D 32’h0010_0100

IOC_PCIE_D10_CNTL nbmisc0x5F 32’h0010_0100

NB_IOC_DEBUG nbmisc0x1 32’h0000_0048

General RS780 IOC Programming After Boot-Up

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

2-3

Page 14

Miscellaneous IOC Features Programming

2.5 Miscellaneous IOC Features Programming

2.5.1 Power Management Register Access Setup

BAR2 is used to access the Power Management registers. The programming procedure to setup BAR2 is as follows:

• Step 1: Enable BAR2 register access (set nbcfg0x4C[17]).

• Step 2: Program the BAR2 register (assign values to nbcfg0x18[31:5]). A 32 bytes IO space is reserved for

BAR2(ACPI PM) registers.

• Step 3: Enable BAR2 decoding (set nbcfg0x84[7]).

Note: The above programming procedure is necessary before enabling ACPI. BAR2 is a memory mapped IO base register

that could be used to reserve some space for the ACPI registers. After BAR2 is setup, IO access which address matches

BAR[31:5] should be treated as ACPI register access, and Addr[4:0] is used as the register offset. The current offset 0x00

and 0x04 are used, as PM2_CNTL and PM1_Status, respectively.

2.5.2 S3 PME_Turn_Off/PME_To_Ack Sequence

No programming is required in the RS780. However, a backup sequence is required in case there is a mis-communication

between the northbridge and the southbridge.

2.5.3 Disabling Internal Graphics

Internal graphics disabling is controlled by an efuse bit, but may also be disabled by writing 1 to register nbcfg0x7C[0]

(NBCFG.NB_IOC_CFG_CNTL[0])

2.5.4 GFX MSI Enable

The SBIOS must enable internal graphics MSI capability in GCCFG by setting the following:

• NBCFG.NB_CNTL.STRAP_MSI_ENABLE=’1’

The OS will determine if MSI’s are supported by the system, and if so, the OS will set the following:

• GCCFG.MSI_MSG_CNTL.MSI_EN=’1’

Note: At the time of this writing, to enable MSI in Vista, set the registry key as follows:

• MSIsupported=1

2.5.5 Disabling Bus0 Device 3 PCI Bridge (Secondary External PCIE Graphics)

Set nbmiscind0x0C[3] to disable Bus0 Device3 register access and decoding. Note: An efuse called CrossFireDisable is

also used that could disable Device 3. Either bit as 1 would disable device 3.

2.5.6 Disabling Bus0 Device 3 PCI Bridges (Dev2, Dev4 to Dev7, Dev9-Dev10)

Set any bit according to the information in Table 2-4:

Table 2-4 Disabling Bus0 Device3 PCI Bridges Settings

Devices Bit Settings

Bus0 Device2 nbmiscind 0x0C[2]

Bus0 Device4 nbmiscind 0x0C[4]

Bus0 Device5 nbmiscind 0x0C[5]

Bus0 Device6 nbmiscind 0x0C[6]

Bus0 Device7 nbmiscind 0x0C[7]

Bus0 Device9 nbmiscind 0x0C[16]

Bus0 Device10 nbmiscind 0x0C[17]

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

2-4

Page 15

Broadcast CPU Requests to Dual External Graphics PCIE Devices

2.6 Broadcast CPU Requests to Dual External Graphics PCIE Devices

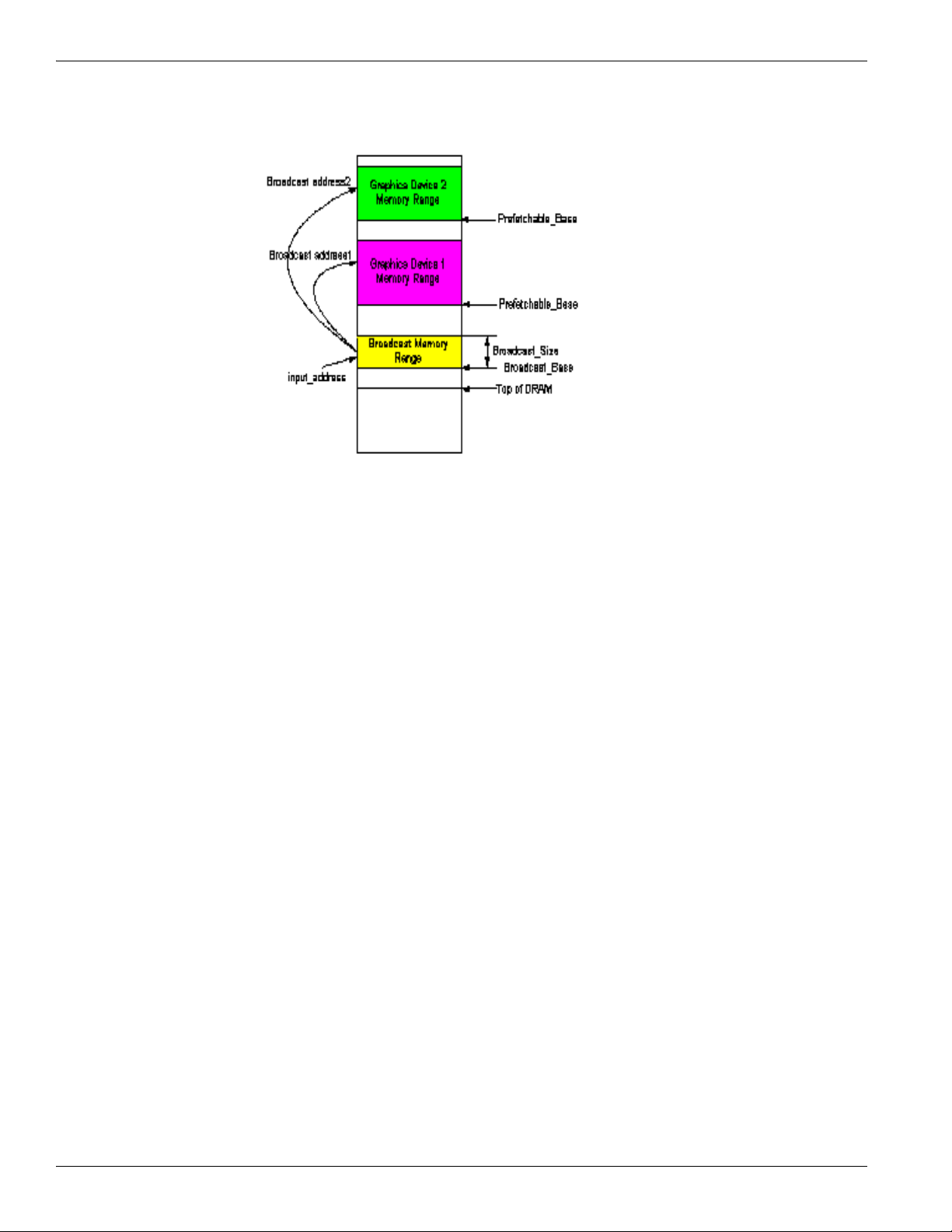

Figure 2-1 describes the algorithm for address translation and broadcast:

Figure 2-1 Address Translation And Broadcast

The Address Translation and Broadcast Algorithm is as follows:

• Broadcast_Address = input_address[63:0] – {BROADCAST_BASE[63:20], 20’b0} +

{Bridge_Prefetchable_BASE[63:20], 20’h} + {32’h0, BROADCAST_OFFSET[31:12], 12’h0}.

• Input_address refers the request address IOC received from CPU.

• BROADCAST_BASE refers to the broadcast memory range start address.

• Bridge_Prefetchable_BASE refers to external graphics device memory range start address.

• BROADCAST_OFFSET is the offset between translated broadcast base address and bridge Prefetchable_BASE

address.

Two broadcast addresses are obtained by applying two Bridge_Prefetchable_BASE addresses from the two PCI

configuration space. Therefore, a single CPU memory write request could be translated and redirected to two external

graphics devices by IOC. Note that this address translation and broadcast algorithm is only applicable to CPU memory

write requests. For CPU memory read requests, the address translation to the primary graphics device is performed using

the above equation, and the request is only forwarded to the primary graphics devices since only one response is expected

by the CPU.

• The 32-bit registers are defined as follows:

• [63:20] GPU_FB_BROADCAST_BASE // 1M aligned broadcast address

• [31:12] GPU_FB_BROADCAST_OFFSET // 4K aligned broadcast offset address

• [11:11] GPU_FB_BROADCAST_EN // Enable broadcast feature

• [10:10] GPU_FB_BROADCAST_PRIMARY // Primary GPU

• 0 = Lower device/port#

• 1 = Higher device/port#

• [07:00] GPU_FB_BROADCAST_SIZE // Size (8MB)

• If enabled, and the address is in range (address -> address + size), then the broadcast memory writes to both ports.

• Broadcast only works for applicable memory writes, and applicable reads will be sent to the primary device only.

• Broadcast is enabled when the enable bit is set, when both device 2 and device 3 bridges are enabled, and when the

memory space is enabled.

• The broadcast memory range should not conflict with any existing P2P memory range, or any BAR memory range.

• Broadcast address = input_address[63:0] - {GPU_FB_BROADCASE_BASE[63:20], 20'h0} +

{bridge_prefetchable_bar[63:20], 20'h0}

• + { 32'h0, GPU_FB_BROADCAST_OFFSET[31:12], 12'h0}

• Address [63:34] does not need to be checked since they are not used (the RS780 supports up to 16G memory space)

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

2-5

Page 16

Enabling/Disabling Peer-To-Peer Traffic Access

2.7 Enabling/Disabling Peer-To-Peer Traffic Access

The P2P master could be any device from the southbridge, devices connected behind P2P bridge 2, 3, 4, 5, 6, 7,9 and 10.

The P2P targets could be devices connected behind P2P bridge 1, 2, 3, 4, 5, 6, 7,9, 10. The southbridge cannot be a target

for trusted-PC purposes. The P2P traffic could be only memory writes. After bootup, by default all P2P traffic listed

above should be enabled. In order to disable a P2P target at a specific device, the following register bits in Table 2-5 need

to be set as follows:

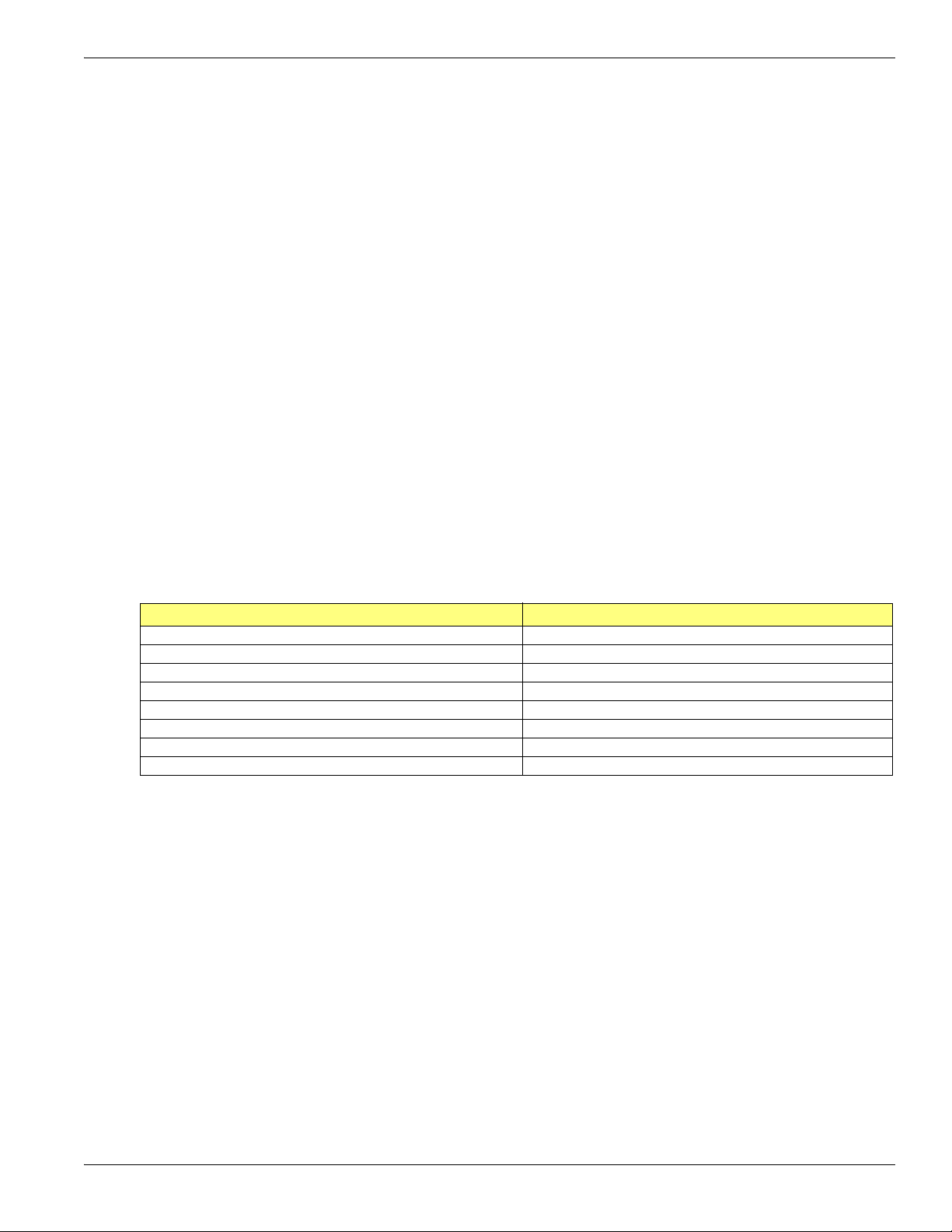

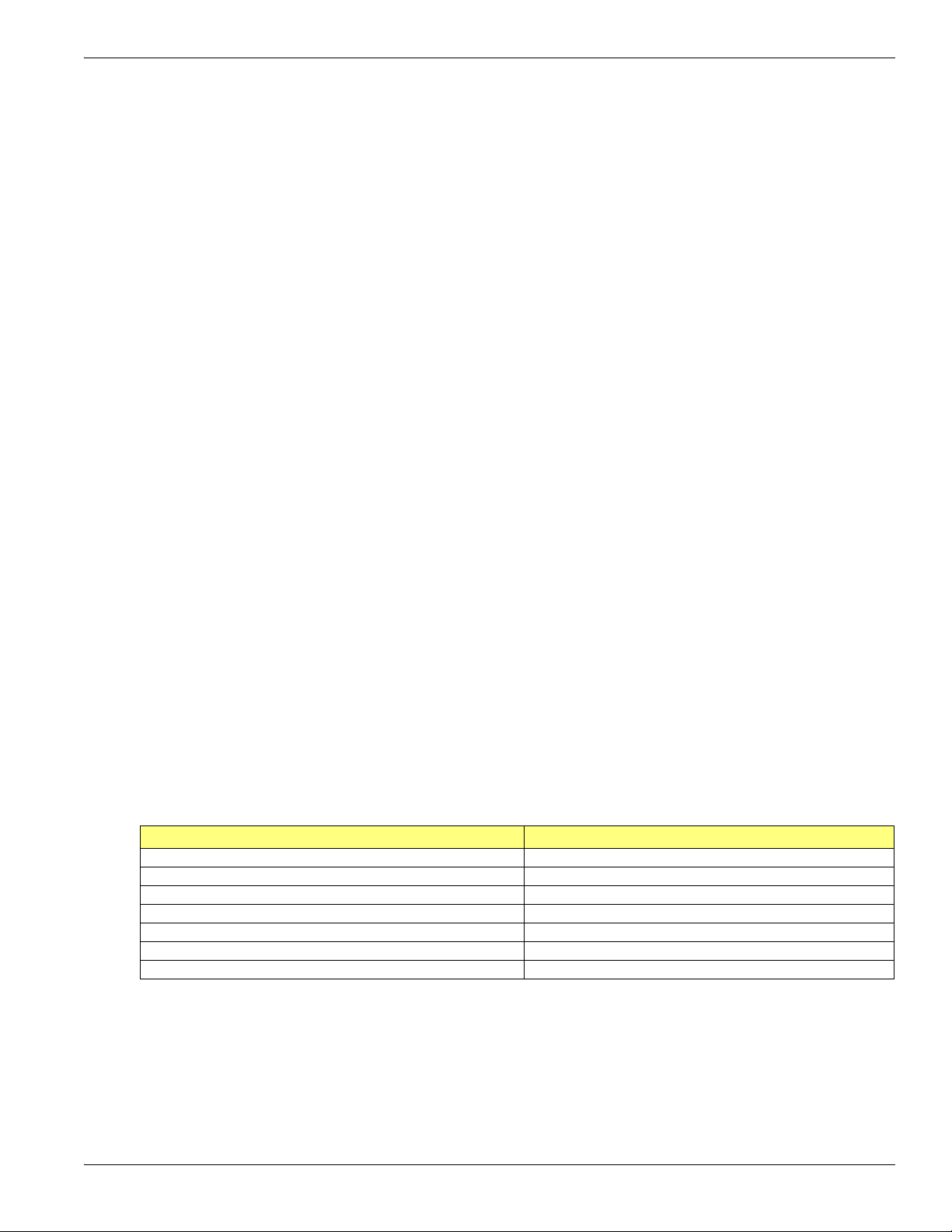

Table 2-5 Enabling/Disabling Peer-To-Peer Traffic Settings

Devices Bit Settings

Bus0 Device1 nbmisc0x4C[2]

Bus0 Device2 nbmisc0x51[3]

Bus0 Device3 nbmisc0x53[3]

Bus0 Device4 nbmisc0x55[3]

Bus0 Device5 nbmisc0x57[3]

Bus0 Device6 nbmisc0x59[3]

Bus0 Device7 nbmisc0x5B[3]

Bus0 Device9 nbmisc0x5D[3]

Bus0 Device10 nbmisc0x5F[3]

2.8 Enabling/Disabling MVPU

MVPU is a feature that enables P2P traffic between external graphics devices (the devices behind P2P bridge 2 and 3) and

the internal graphics device (the device behind P2P bridge 1). The corresponding P2P traffic access enable bits are

described in section Table 2-5 above.

2.9 IOC Dynamic Clock Setup

The following clocks are in IOC:

• LCLK (free running)

• LCLK_MST (master branch)

• LCLK_SLV (slave branch - Note: This dynamic branch should not be used)

Note: Only LCLK_MST (master branch) and LCLK_SLV (slave branch) can be dynamically turned on and off.

The two bits that control IOC dynamic clocks are as follows:

• clkcfg0x8C[13] CLKGATE_DIS_IOC_LCLK_MST

• clkcfg0x8C[14] CLKGATE_DIS_IOC_LCLK_SLV (Note: Ensure that this bit is programmed to 1 in order to avoid

system instability)

Note: Clkconfig:0x94[27] CLKGATE_IOC_SLV_GFX - BIOS should program to 1 to disable clock gating on this

branch.

For both of these bits:

• 1=Dynamic clock is disabled

• 0=Dynamic clock is enabled

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

2-6

Page 17

2.10 Interrupt Mapping

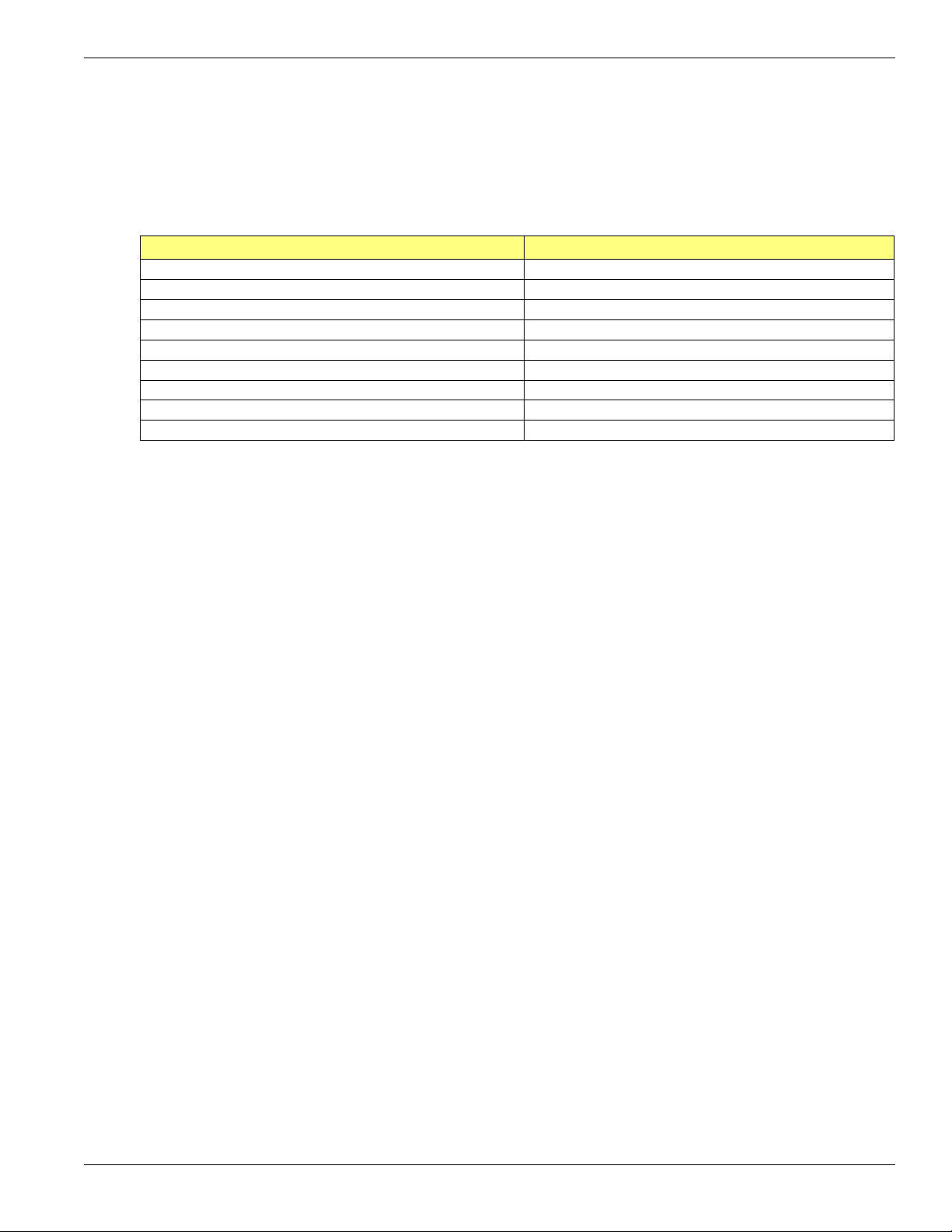

Table 2-6 Interrupt Mapping Settings

1 (internal graphics) INTA -> INTC, INTB->INTD

2.11 GSM Enable

Set nbmisind0x0C[13]=1 to enable GSM in the RS780.

Interrupt Mapping

Devices Bit Settings

2INTA -> INTC

3INTA -> INTD

4 INTA -> INTA

5 INTA -> INTB

6INTA -> INTC

7INTA -> INTD

9 INTA -> INTB

10 INTA -> INTC

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

2-7

Page 18

GSM Enable

This page intentionally left blank.

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

2-8

Page 19

3.1 SBIOS Memory Clock Initialization

3.1.1 UMA Mode

RS780 boots up in synchronous UMA clock mode. The memory clock and HT clock are driven by the same HT PLL. In

UMA sync mode the memory PLL is not used and should be powered down.

• Program <NBMCIND:0x6> Bit[31] MC_MPLL_CONTROL.MPLL_POWERDOWN = ‘1’ to power down memory

PLL in sync mode.

3.1.2 Side-Port Async Mode

•

Step 1: Program IO 1XCLK skew delay by setting

• <NBMCIND:0x6> Bit[10:8] MC_MPLL_CONTROL.MPLL_SKEW1=0x1

• Step 2: Program current control for SCL for PLL to 0%

• < NBMCIND:0x8 > Bit[20:18] MC_MPLL_CONTROL3.MPLL_SCLBIAS = 0x1

• Step 3: Select memory PLL reference clock. Default is 100MHz HT reference and it should be used in normal

operation.

• <NBMCIND : 0x8> Bit[10] MC_MPLL_CONTROL3.MPLL_REFCLK_SEL (‘0’=100 MHz HT reference

clock; ‘1’=PCIE reference clock)

• Step 4: Program memory PLL settings for different operating frequencies.

• Feedback divider : < NBMCIND:0x7 > Bit[8:0] MC_MPLL_CONTROL2.MPLL_FBDIV

• Reference divider : < NBMCIND:0x7 > Bit[13:9] MC_MPLL_CONTROL2.MPLL_REFDIV

• Post divider (postdiv) : < NBMCIND:0x7 > Bit[15:14] MC_MPLL_CONTROL2.MPLL_POSTDIV

• Charge pump : < NBMCIND:0x7 > Bit[19:16] MC_MPLL_CONTROL2.MPLL_CP

• VCO mode : < NBMCIND:0x7 > Bit[21:20] MC_MPLL_CONTROL2.MPLL_VCO_MODE

• Loop filter mode: < NBMCIND:0x7 > Bit[31:28] MC_MPLL_CONTROL2.MPLL_LF_MODE

Chapter 3

Clock Settings

• Consider the following equation to calculate MCLK:

• P1 = 100MHz / (MPLL_REFDIV + 1)

• P2 = (MPLL_FBDIV[2:0] + 1) * (MPLL_FBDIV[8:3] + 1) * 2

• P3 = 2 * (MPLL_POSTDIV+1)

• MCLK = P1 * P2 / P3

• The divider settings should use the frequency plan in Table 3-1 from memory PLL specification.

• 200MHz settings:

• <NBMCIND:0x7> MC_MPLL_CONTROL2=0x00004018;

• 266MHz settings:

• <NBMCIND:0x7> MC_MPLL_CONTRO2=0x00114478;

• 333MHz settings:

• <NBMCIND:0x7> MC_MPLL_CONTROL2=0x00224498;

• 400MHz settings:

• <NBMCIND:0x7> MC_MPLL_CONTROL2=0x00000018;

• 533MHz settings:

• <NBMCIND:0x7> MC_MPLL_CONTROL2=0x00110478;

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

3-1

Page 20

SBIOS Memory Clock Initialization

• 667MHz settings:

• <NBMCIND:0x7> MC_MPLL_CONTROL2=0x00220498

• Note: For other frequencies, refer to TABLE X below.

• Step 5: Program PM mode PLL setting the same as nominal mode setting

• 200MHz:

• <NBMCIND:0xB> MC_MPLL_DIV_CONTROL=0x00004018

• <NBMCIND:0x9> Bit[11:8] MC_MPLL_FREQ_CONTROL.PM_MPLL_CP=0x0

• <NBMCIND:0x9> Bit[13:12] MC_MPLL_FREQ_CONTROL.PM_MPLL_VCO_MODE=0x0

• <NBMCIND:0x9> Bit[19:16] MC_MPLL_FREQ_CONTROL.PM_MPLL_LF_MODE=0x6

• 266MHz:

• <NBMCIND:0xB> MC_MPLL_DIV_CONTROL=0x00004478

• <NBMCIND:0x9> Bit[11:8] MC_MPLL_FREQ_CONTROL.PM_MPLL_CP=0x1

• <NBMCIND:0x9> Bit[13:12] MC_MPLL_FREQ_CONTROL.PM_MPLL_VCO_MODE=0x1

• <NBMCIND:0x9> Bit[19:16] MC_MPLL_FREQ_CONTROL.PM_MPLL_LF_MODE=0x4

• 333MHz:

• <NBMCIND:0xB> MC_MPLL_DIV_CONTROL=0x00004498

• <NBMCIND:0x9> Bit[11:8] MC_MPLL_FREQ_CONTROL.PM_MPLL_CP=0x2

• <NBMCIND:0x9> Bit[13:12] MC_MPLL_FREQ_CONTROL.PM_MPLL_VCO_MODE=0x2

• <NBMCIND:0x9> Bit[19:16] MC_MPLL_FREQ_CONTROL.PM_MPLL_LF_MODE=0x4

• 400MHz:

• <NBMCIND:0xB> MC_MPLL_DIV_CONTROL=0x00000018

• <NBMCIND:0x9> Bit[11:8] MC_MPLL_FREQ_CONTROL.PM_MPLL_CP=0x0

• <NBMCIND:0x9> Bit[13:12] MC_MPLL_FREQ_CONTROL.PM_MPLL_VCO_MODE=0x0

• <NBMCIND:0x9> Bit[19:16] MC_MPLL_FREQ_CONTROL.PM_MPLL_LF_MODE=0x6

• 533MHz:

• <NBMCIND:0xB> MC_MPLL_DIV_CONTROL=0x00000478

• <NBMCIND:0x9> Bit[11:8] MC_MPLL_FREQ_CONTROL.PM_MPLL_CP=0x1

• <NBMCIND:0x9> Bit[13:12] MC_MPLL_FREQ_CONTROL.PM_MPLL_VCO_MODE=0x1

• <NBMCIND:0x9> Bit[19:16] MC_MPLL_FREQ_CONTROL.PM_MPLL_LF_MODE=0x4

• 667MHz:

• <NBMCIND:0xB> MC_MPLL_DIV_CONTROL=0x00000498

• <NBMCIND:0x9> Bit[11:8] MC_MPLL_FREQ_CONTROL.PM_MPLL_CP=0x2

• <NBMCIND:0x9> Bit[13:12] MC_MPLL_FREQ_CONTROL.PM_MPLL_VCO_MODE=0x2

• <NBMCIND:0x9> Bit[19:16] MC_MPLL_FREQ_CONTROL.PM_MPLL_LF_MODE=0x4

• Note: For other PM frequencies, refer to Table 3-1 below.

• Step 6: Program memory PLL and DLL lock time

• Min. 10us calibration setup time: Calibration setup time = 10ns x <NBMCIND:0xA> Bit[11:8]

MC_MPLL_SEQ_CONTRL.MPLL_CAL_S_TIME x 512

• Min. 50ns calibration hold time: Calibration hold time = 10ns x <NBMCIND:0xA> Bit[15:12]

MC_MPLL_SEQ_CONTROL.MPLL_CAL_H_TIME x 4

• Min. 50us PLL lock time: MPLL lock time = 10ns x <NBMCIND:0xA> Bit[23:16]

MC_MPLL_SEQ_CONTROL.MPLL_LOCK_TIME x 256

• Min. 50us DLL lock time: MDLL lock time = 10ns x <NBMCIND:0xA> Bit[31:24]

MC_MPLL_SEQ_CONTROL.MDLL_LOCK_TIME x 256

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

3-2

Page 21

• Step 7: Recalibrate the memory PLL

• Set < NBMCIND:0x6 > Bit[0] MC_MPLL_CONTROL.MPLL_CAL_TRIGGER = ’1’;

• Step 8: Wait for 200us;

• Step 9: Poll PLL lock signal < NBMCIND:0x6 > Bit[1] MC_MPLL_CONTROL.MPLL_LOCKED = ’1’;

• Step 10: Set < NBMCIND:0x6 > Bit[0] MC_MPLL_CONTROL.MPLL_CAL_TRIGGER = ’0’

• Step 11: Program <NBMCIND:0x2> Bit[20] MC_GENERAL_PURPOSE_2.MCLK_SRC_USE_MPLL = ‘0’ to

select asynchronous clock mode.

• Step 12: Start the memory initialization sequence.

3.2 Memory Clock Changes For POWERPLAY

Note: PowerPlay MCLK switching only applies to asynchronous clock mode for memory side port

• Step 1: Program MPLL divider in PM mode by setting

• < NBMCIND:0xB > Bit[8:0] MC_MPLL_DIV_CONTROL.PM_MPLL_FBDIV

• < NBMCIND:0xB > Bit[13:9] MC_MPLL_DIV_CONTROL.PM_MPLL_REFDIV

• < NBMCIND:0xB > Bit[15:14] MC_MPLL_DIV_CONTROL.PM_MPLL_POSTDIV

• Consider the following Equation to calculate MCLK in PM mode:

• P1 = 100MHz / (PM_MPLL_REFDIV + 1)

• P2 = (PM_MPLL_FBDIV[2:0] + 1) * (PM_MPLL_FBDIV[8:3] + 1) * 2

• P3 = 2 * (PM_MPLL_POSTDIV+1)

• MCLK = P1 * P2 / P3

• Use the settings in Table 3-1 to get the divider settings for the required frequencies. For example:

• 133MHz in PM mode

• MC_MPLL_DIV_CONTROL.PM_MPLL_FBDIV = 0x78

• MC_MPLL_DIV_CONTROL.PM_MPLL_REFDIV = 0x2

• MC_MPLL_DIV_CONTROL.PM_MPLL_POSTDIVS = 0x3

• Step 2: If MCLK < HT_CLK in PM mode, set < NBMCIND:0x9 > Bit[29]

MC_MPLL_FREQ_CONTROL.PM_MPLL_SLOWMCLK = 0x1 else 0x0

Memory Clock Changes For POWERPLAY

• Step 3: Program < NBMCIND:0x9 > Bit[0] MC_MPLL_FREQ_CONTROL.MPLL_PM_EN = 0x1

• Step 4: Program MPLL parameters in PM mode by setting the following:

• <NBMCIND:0x9> Bit[11:8] MC_MPLL_FREQ_CONTROL.PM_MPLL_CP

• <NBMCIND:0x9> Bit[13:12] MC_MPLL_FREQ_CONTROL.PM_MPLL_VCO_MODE

• <NBMCIND:0x9> Bit[19:16] MC_MPLL_FREQ_CONTROL.PM_MPLL_LF_MODE

• Use the settings in Table 3-1 to program the required frequencies. For example:

• MPLL parameter for 133MHz in PM mode

• MC_MPLL_FREQ_CONTROL.PM_MPLL_CP = 0x1

• MC_MPLL_FREQ_CONTROL.PM_VCO_MODE = 0x1

• MC_MPLL_FREQ_CONTROL.PM_LF_MODE = 0x4

• Step 5: Program the memory controller settings in different PM mode speed

• Refer to the AMD RS780 BIOS Developer’s Guide for more information.

• Step 6: Switch to PM mode MCLK by setting < NBMCIND:0x9 > Bit[1]

MC_MPLL_FREQ_CONTROL.MPLL_FREQ_SEL = 0x1

• Step 7: Poll for < NBMCIND:0x9 > Bit[6] MC_MPLL_FREQ_CONTROL.PM_SWITCHMCLK_BUSY = 0x0

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

3-3

Page 22

Switching Back From PM Mode to Nominal Mode

3.3 Switching Back From PM Mode to Nominal Mode

• Step 1: Set < NBMCIND:0x9 > Bit[1] MC_MPLL_FREQ_CONTROL.MPLL_FREQ_SEL = 0

• Step 2: Poll for < NBMCIND:0x9 > Bit[6] MC_MPLL_FREQ_CONTROL.PM_SWITCHMCLK_BUSY = 0x0.

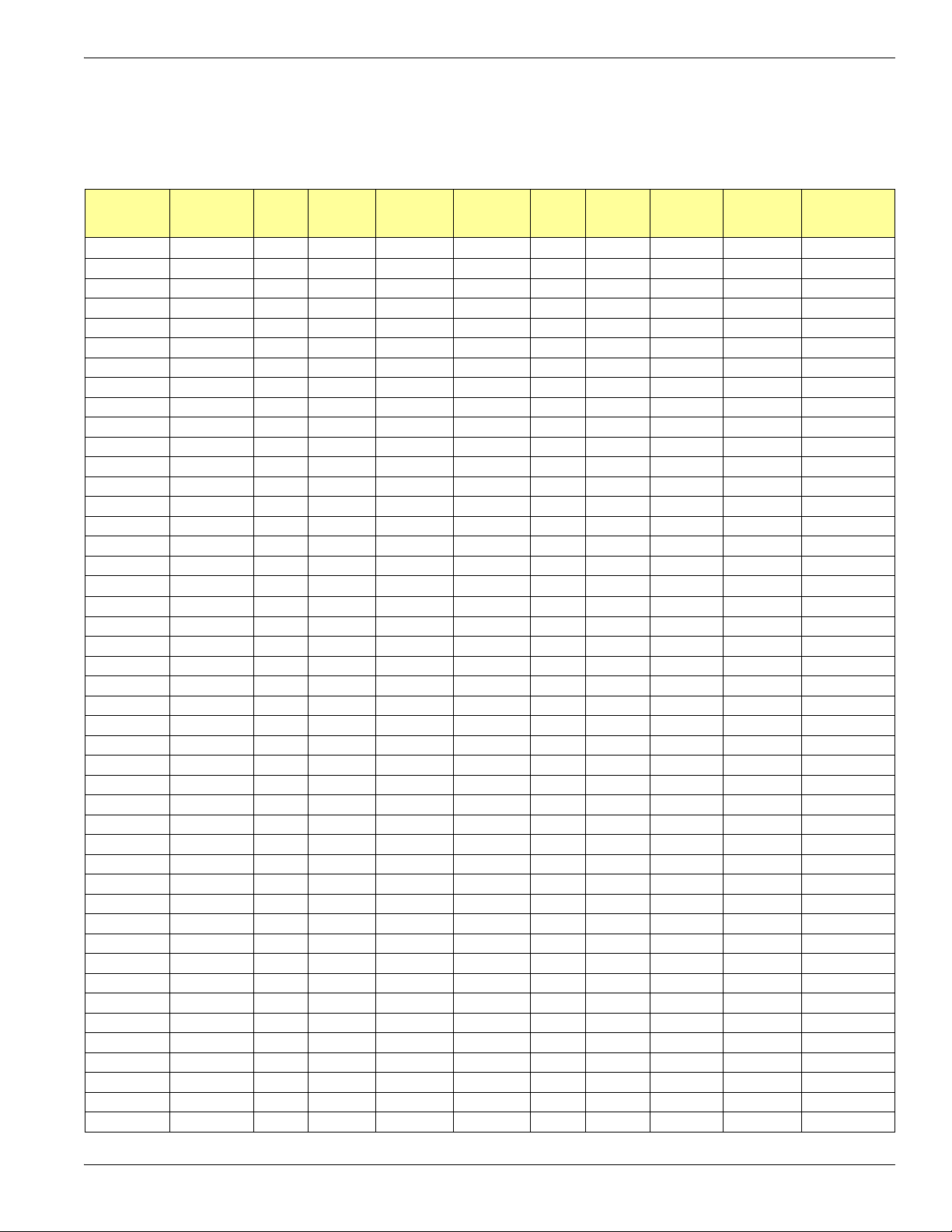

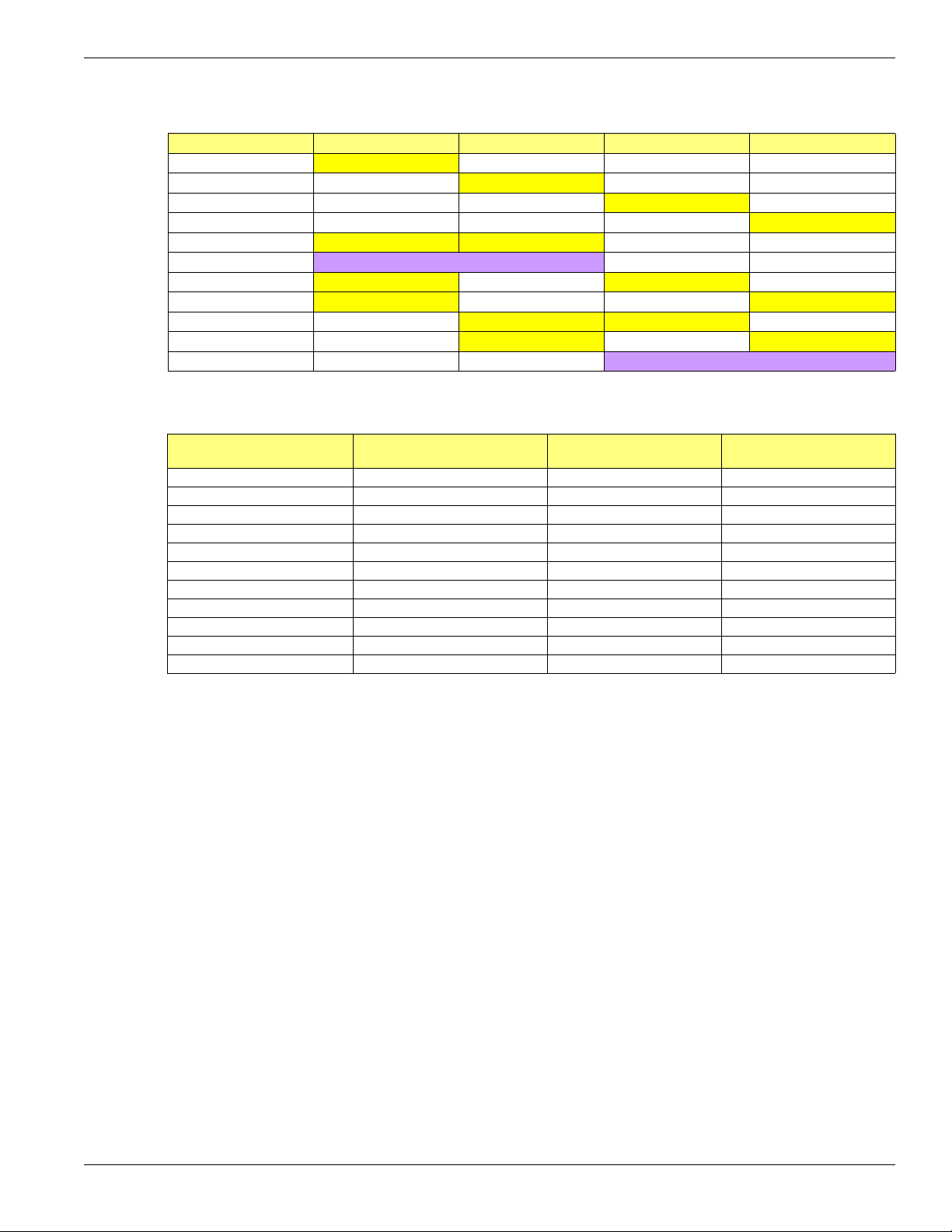

Table 3-1 Memory PLL Settings For Supposed Frequencies

Target

(MHz)

100 100 0 1 1 4 4 0000 0110 00 800

133.3333 133.3333 0 3 1 16 4 0001 0100 01 1066.6667

166.6666 166.6666 0 1 1 5 3 0000 0110 01 1000

200 200 0 1 1 4 2 0000 0110 00 800

233.3333 233.3333 0 1 1 7 3 0000 0100 10 1400

266.6666 266.6666 0 3 1 16 2 0001 0100 01 1066.6667

300 300 0 1 1 6 2 0000 0100 01 1200

333.3333 333.3333 0 3 1 20 2 0010 0100 10 1333.3333

366.6666 366.6666 0 3 1 11 1 0001 0100 00 733.33333

400 400 0 1 1 4 1 0000 0110 00 800

433.3333 433.3333 0 3 1 13 1 0001 0100 00 866.66667

466.6666 466.6666 0 3 1 14 1 0001 0100 00 933.33333

500 500 0 1 1 5 1 0000 0110 01 1000

533.3333 533.3333 0 3 1 16 1 0001 0100 01 1066.6667

566.6666 566.6666 0 3 1 17 1 0001 0100 01 1133.3333

600 600 0 1 1 6 1 0000 0100 01 1200

633.3333 633.3333 0 3 1 19 1 0010 0100 10 1266.6667

666.6666 666.6666 0 3 1 20 1 0010 0100 10 1333.3333

100 100 0 1 1 4 4 0000 0110 00 800

112 112.5 0.5 2 1 9 4 0000 0100 00 900

124 123.8095 0.2 7 1 26 3 0010 1000 00 742.85714

136 136.1111 0.1 9 1 49 4 0011 1100 01 1088.8889

148 148.1481 0.15 9 1 40 3 0011 1000 00 888.88889

160 160 0 5 1 24 3 0010 0100 01 960

172 171.875 0.1 8 1 55 4 0011 1100 10 1375

184 184.375 0.4 8 1 59 4 0011 1100 10 1475

196 195.8333 0.15 8 1 47 3 0011 1100 01 1175

208 208.3333 0.35 4 1 25 3 0010 0100 01 1250

220 220 0 5 1 33 3 0010 1000 10 1320

232 231.25 0.75 8 1 37 2 0011 1000 00 925

244 243.75 0.25 8 1 39 2 0011 1000 01 975

256 256.25 0.25 8 1 41 2 0011 1100 01 1025

268 268.75 0.75 8 1 43 2 0011 1100 01 1075

280 280 0 5 1 28 2 0010 1000 01 1120

292 291.6666 0.35 6 1 35 2 0010 1000 01 1166.6667

304 305.5555 1.55 9 1 55 2 0011 1100 01 1222.2222

316 316.6666 0.65 3 1 19 2 0010 0100 10 1266.6667

328 327.7777 0.2 9 1 59 2 0011 1100 10 1311.1111

340 340 0 5 1 34 2 0010 1000 10 1360

352 350 2 1 1 7 2 0000 0100 10 1400

364 364.2857 0.3 7 1 51 2 0011 1100 10 1457.1429

376 375 1 4 1 15 1 0001 0100 00 750

388 387.5 0.5 8 1 31 1 0010 1000 00 775

400 400 0 1 1 4 1 0000 0110 00 800

412 412.5 0.5 8 1 33 1 0010 1000 00 825

Achieved

(MHz)

Error

(MHz)

Ref_div

3-bit

CMOS FB

div

6-bit

CMOS FB

div

POST

IICP

[3:0]

ILF_MOD

E[3 :0]

IVCO_MO

DE[1:0]

VCO freq

(MHz)

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

3-4

Page 23

Power Saving Settings

Target

(MHz)

424 425 1 4 1 17 1 0001 0100 00 850

436 437.5 1.5 8 1 35 1 0010 1000 00 875

448 450 2 2 1 9 1 0000 0100 00 900

460 460 0 5 1 23 1 0010 0100 00 920

472 471.4285 0.55 7 1 33 1 0010 1000 01 942.85714

484 483.3333 0.65 6 1 29 1 0010 1000 01 966.66667

496 500 4 1 1 5 1 0000 0110 01 1000

508 511.1111 3.1 9 1 46 1 0011 1100 01 1022.2222

520 520 0 5 1 26 1 0010 1000 01 1040

532 533.3333 1.35 3 1 16 1 0001 0100 01 1066.6667

544 544.4444 0.45 9 1 49 1 0011 1100 01 1088.8889

556 555.5555 0.45 9 1 50 1 0011 1100 01 1111.1111

568 566.6666 1.35 3 1 17 1 0001 0100 01 1133.3333

580 580 0 5 1 29 1 0010 1000 01 1160

592 588.8888 3.1 9 1 53 1 0011 1100 01 1177.7778

604 600 4 1 1 6 1 0000 0100 01 1200

616 616.6666 0.65 6 1 37 1 0011 1000 01 1233.3333

628 628.5714 0.55 7 1 44 1 0011 1100 10 1257.1429

640 640 0 5 1 32 1 0010 1000 10 1280

652 650 2 2 1 13 1 0001 0100 10 1300

664 662.5 1.5 8 1 53 1 0011 1100 10 1325

676 675 1 4 1 27 1 0010 1000 10 1350

Achieved

(MHz)

Error

(MHz)

Ref_div

3-bit

CMOS FB

div

6-bit

CMOS FB

div

POST

IICP

[3:0]

ILF_MOD

E[3 :0]

IVCO_MO

DE[1:0]

VCO freq

(MHz)

3.4 Power Saving Settings

3.4.1 Enabling Dynamic Clocks

Table 3-2 Dynamic Clocks Settings

ASIC Rev Settings Function/Comment

CFG_CT_CLKGATE_HTIU <clkcfg:0xf8> = 0xcf30

CLKCFG.CLKGATE_DISABLE[31], [28], [26], [24] = 0x0

All Revs

3.4.2 Powering Down Efuse and Strap Block Clocks After Boot-Up

Table 3-3 Powering Down Efuse and Strap Block Clocks Settings

ASIC Rev Settings Function/Comment

All Revs

CLKCFG.CLKGATE_DISABLE2[26:24] = 0x0

CLKCFG.CLKGATE_DISABLE2[14] = 0x1

CLKCFG.CLK_TOP_SPARE_C[31:28]=0xe [27:26]=0x3

NBMCIND.MC_MCLK_CONTROL = 0xf000000

Intgfx mode: <CLKCFG: 0xCC> Bit[24:23] = 0x3;

<GpuF0MMReg:0x3080> Bit[8]

CG.CG_INTGFX_MISC.CG_CT_NB_EFUSE_CLK_DISABLE= 0x1

NB only mode: <CLKCFG: 0xCC> Bit[24:23] = 0x3

Enables North Bridge dynamic clocks to htiu and

mc

Powerdown efuse and strap block clocks in

integrated graphics mode

Powerdown efuse and strap block clocks in

northbridge only mode

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

3-5

Page 24

Power Saving Settings

3.4.3 Powering Down Graphics Core and Memory Clocks in Northbridge-Only Mode

Table 3-4 Powering Down Graphics core and Memory Clocks in NB-Only Mode Settings

ASIC Rev Settings Function/Comment

All Revs

<CLKCFG:0x8C> Bit[21] = 0x1

<CLKCFG:00xE4> Bit[0] = 0x1

Powers down reference clock to graphics core PLL in

northbridge only mode

Powers down clock to memory controller in

northbridge only mode

3.4.4 Powering Down IOC GFX Clock in No External Graphics Mode

Table 3-5 Powering Down IOC GFX Clock In No External Graphics Mode Settings

ASIC Rev Settings Function/Comment

All Revs

<CLKCFG:0xE8> Bit[17] = 0x1 Powers down clock to IOC GFX block in no external

graphics mode

3.4.5 PWM Controller

There are five PWM controllers mapped to five GPIO pins that can be used for voltage adjustment purpose after boot-up.

Table 3-6 PWM Controller/GPIO Pins Mapping

ASIC Rev Register setting Function/Comment

All Revs

1.CLK_TOP_PWM1_CTRL<CLKCFG:0xB0>

2. CLK_TOP_PWM2_CTRL<CLKCFG:0xB4>

3. CLK_TOP_PWM3_CTRL <CLKCFG:0xCC>

4. CLK_TOP_PWM4_CTRL<CLKCFG:0x4C>

5. CLK_TOP_PWM5_CTRL<CLKCFG:0x50>

1. PWM control on LVDS_BLON GPIO pin

2. PWM control on LVDS_ENA_BL GPIO pin

3. PWM control on STRP_DATA GPIO pin

4. PWM control on LVDS_DIGON GPIO pin

5. PWM control on TMDS_HPD GPIO pin

Each of the above PWM registers in PWM Controller/GPIO Pins Mapping has the following register fields:

• Bit[0]: Enable the PWM controller

• Bits[12:1]: Number of cycles in pulse period of a 100MHz reference clock

• Bits[24:13]: Number of high cycles in pulse period of a 100MHz reference clock

• Bit[25]: Output enable of the GPIO

The STRP_DATA pin by default is driving low, and register setting <clkcfg:0xE0> Bit[0] = ‘1’ is required before using

PWM or GPIO control.

The STRP_DATA pin is also used for core voltage scaling purposes. The CLK_TOP_PWM3_CTRL < CLKCFG:0xCC >

Bit[0] = ’0’ is required to enable the graphics device driver to have control on the STRP_DATA pin.

The register settings < nbmisind:0x40 > Bit[8] = ‘1’ and Bit[10] = ’1’ are required for using PWM1 on the LVDS_BLON

pin.

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

3-6

Page 25

3.5 DOS Mode Power Saving

To disable the graphics engine clock branches when in DOS mode, program the following register in Table 3-7 during

boot.

Table 3-7 DOS Mode Power Saving Settings

ASIC Rev Settings Function/Comment

A12 1. CG_MISC_INPUT_3[9] = 0 <CLKCFG:0x90>

2. CG_INTGFX_MISC[31:20] = 0x9F3

3.6 HTPLL VCO Mode Setting

The HTPLL VCO mode setting should be configured in high-speed mode after boot-up.

• <clkcfg:0xD4> CLK_CFG_HTPLL_CNTL Bit[16:15] = “00”

• <clkcfg:0xD4> CLK_CFG_HTPLL_CNTL Bit[2:0] = “010”

• <clkcfg:0xE8> CLK_TOP_SPARE_C Bit[16] = “0”

DOS Mode Power Saving

Write 0x1

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

3-7

Page 26

HTPLL VCO Mode Setting

This page intentionally left blank.

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

3-8

Page 27

4.1 Memory Initialization

For memory controller programming information, refer to the AMD RS780 BIOS Developer’s Guide.

Chapter 4

Memory Initialization

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

4-1

Page 28

Memory Initialization

This page intentionally left blank.

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

4-2

Page 29

5.1 Introduction

This chapter describes the initialization and feature programming of the northbridge PCI Express subsystem. The

northbridge implements PCI Express point-to-point links to external devices.

There are 9 configurable PCI Express ports, which can be divided into 3 groups (implemented in hardware as 3 separate

cores):

• PCIE-GFX: 2 ports, 16 lanes in total. Each port is configurable from x1 to x8 link. The 2 ports can also be combined

to provide 1 x16 port (default configuration).

• PCIE-GPPSB: 1 SB port and 4 GPP ports, 8 lanes in total. The SB port provides a dedicated x4 link to the

southbridge. The remaining 4 lanes are distributed across the 4 GPP ports to support 4 different configurations: a)

4:0:0:0:0, b) 4:4:0:0:0, c) 4:2:2:0:0, d) 4:2:1:1:0 and e) 4:1:1:1:1 (default configuration).

• PCIE-GPP: 2 ports, 2 lanes in total. Each port provides a x1 link. The 2 ports can also be combined to provide a x2

link.

5.2 PCI Express Configuration Space

The PCI Express configuration space consists of the following four groups:

• PCIE Port Configuration Space (section 5.2.1)

• PCIE Core Index Space (section 5.2.2)

Chapter 5

PCIE Initialization

• PCIE Port Index Space (section 5.2.3)

• PCIE Extended Configuration Space (section 5.2.4)

5.2.1 PCIE Port Configuration Space

Each PCIE port has a standard Type 1 Virtual PCI-to-PCI bridge header in the PCI configuration space. These are devices

2 through 10 on PCI bus 0.

• GFX Port A: Device 2 (GFX0)

• GFX Port B: Device 3 (GFX1)

• GPPSB Port A: Device 8 (SB link, hidden by default)

• GPPSB Port B: Device 4 (GPP0)

• GPPSB Port C: Device 5 (GPP1)

• GPPSB Port D: Device 6 (GPP2)

• GPPSB Port E: Device 7 (GPP3)

• GPP Port A: Device 9 (GPP4)

• GPP Port B: Device 10 (GPP5)

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

5-1

Page 30

PCI Express Configuration Space

5.2.2 PCIE Core Index Space

The PCIE Core Index Space contains control and status registers that are generic to all PCIE ports in the northbridge.

This register space is accessed through an index/data register pair:

• NB_BIF_NB: NB_PCIE_INDX_ADDR: nbconfig: 0xe0

• NB_PCIE_INDX_ADDR: [7:0] - Address in PCIE Core

• GFX_GPPSB_SEL [18:16]:

• 000 – PCIE GFX Core

• 001 – PCIE GPPSB Core

• 010 – PCIE GPP Core

• 011 – Broadcast to all 3 cores

• All other values are unused

• NB_BIF_NB: NB_PCIE_INDX_DATA: nbconfig: 0xe4

Note: Registers in the core index space are referenced with the name PCIEIND or BIF_NB.

5.2.3 PCIE Port Index Space

The Port Index Space contains control and status registers that are specific to each port within the core. Each PCIE device

implements its own set of registers in this space.

Each PCIE device contains an index/data pair in its Virtual Bridge PCI configuration space to access the Port Index Space

registers. Please note the following information for the index/data register pair:

• Index register: bus 0, device X, register 0xE0.

• Data register: bus 0, device X, register 0xE4.

Note: Register descriptions are referenced with the name PCIEIND_P or BIF_NBP.

5.2.4 PCIE Extended Configuration Space

PCI Express extends the PCI configuration space from 256 bytes to 4096 bytes. Extended PCIE configuration space

memory maps 4KB for each device. The first 256 bytes of each 4KB are the same as PCI 2.3 configuration registers, and

the remaining 3840 bytes are PCIE specific configuration registers.

The northbridge uses NBCFG:NB_BAR3_PCIEXP_MMCFG nbconfig:0x1C (BAR3) to map the PCI Express Extended

Configuration Space to a 256MB range within the first 4GB of addressable memory. PCIE devices are accessed by

reading/writing to a memory mapped address that is based on the base address in BAR3. The PCIE target address is

formed as follows:

• Addr[11:2] = RegNum (Addr[11:8] is extended register field)

• Addr[14:12] = FunNum

• Addr[19:15] = DevNum

• Addr[20 + n-1:20] = BusNum

• Addr[33:20 + n] = Reserved for BAR3 match

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

5-2

Page 31

PCI Express Configuration Space

Note: ‘n’ indicates how many bits are allocated for the bus number. This value is decided by BAR3BusRange in

NBCFG:NB_PCI_ARB[18:16] nbconfig:0x84 register. These relations are listed in Table 5-1 below:

Table 5-1 NBCFG:NB_PCI_ARB[18:16] nbconfig:0x84 register

ASIC Rev NBCFG:NB_PCI_ARB[18:16]· nbconfig:0x84 ‘n’

RS780 All Revs 3’b001 1

3’b010 2

3’b011 3

3’b100 4

3’b101 5

3’b110 6

3’b111 7

3’b000 8

Table 5-2 contains the programming procedure to enable BAR3:

Table 5-2 Enabling BAR3

ASIC

Rev

RS780 All

Revs

Step Register Settings Function/Comment

1 NBCFG:NB_IOC_CFG_CNTL[30]=1’b1 nbconfig:0x7c

NB_BAR3_PCIEXP_REG_WREN

Set bit [30] to 1

2 NBCFG:NB_PCI_ARB[18:16] nbconfig:0x84

BAR3BusRange

Enables BAR3 Register Access.

Programs BAR3 bus range.

Program bits [18:16]

3 NBCFG:NB_BAR3_PCIEXP_MMCFG[31:21] nbconfig:0x1c

MEM_BASE_HIGH

NBCFG:NB_BAR3_UPPER_PCIEXP_MMCFG[1:0]

nbconfig:0x20

MEM_BASE_UPPER

4 HTIUNBCFG:NB_HTIU_CFG[28]=1’b1 HTIUNBIND:0x32

NB_BAR3_PCIEXP_ENABLE

Set bit [28] to 1

Programs the BAR3 register.

Enables BAR3 decoding.

Note: The BAR3 memory upper address register is nbcfg0x20 (above 4G). The RS780 could support memory up to 16G,

so this register has to be set properly.

© 2009 Advanced Micro Devices, Inc. AMD 780G Register Programming Requirements 1.01

5-3

Page 32

Power-On and Reset State

5.3 Power-On and Reset State

After a Power-On or Reset event the North Bridge puts all of its PCI Express devices into their default states, which are

shown in Table 5-3 below:

Table 5-3 Power-On and Reset State

ASIC Rev PCI Device Number (PCIE Port) Link Training Number of Lanes Supported

RS780 All Revs Dev 2 (PCIE-GFX Port A) Disabled 1, 2, 4, 8, or 16

Dev 3 (PCIE-GFX Port B) Disabled 1, 2, 4, or 8

Dev 4 (PCIE-GPPSB Port B) Disabled 1, 2, or 4

Dev 5 (PCIE-GPPSB Port C) Disabled 1

Dev 6 (PCIE-GPPSB Port D or - C in 4:2:x:x:0 mode) Disabled 1 or 2

Dev 7 (PCIE-GPPSB Port E or - D in 4:2:1:1:0 mode) Disabled 1

Dev 8 (PCIE-GPPSB Port A) Enabled 1 or 2 or 4

Dev 9 (PCIE-GPP Port A) Disabled 1

Dev 10 (PCIE-GPP Port B) Disabled 1

Note: PCI device 8 (Dev 8) does not appear in the PCI configuration space by default.

5.4 PCIE GFX Configurations

The x16 PCIE GFX interface is fully multiplexed to provide as many directly connected display options as possible. Each

output format can be mapped to any of the four-lane groups (0-3, 4-7, 8-11 and 12-15) in the 16 available lanes.

However, there are only 3 separate PLLs associated with lanes 0-3 (PLL A), 4-7 (PLL B) and 8-15 (PLL C). The

supported configurations in RS780 are detailed below.

5.4.1 PCIE Modes Only

The PCIE GFX core can support up to 2 PCIE devices. Each PCIE device can be a GFX or a GPP device. Table 5-4

outlines all the supported PCIE configurations.

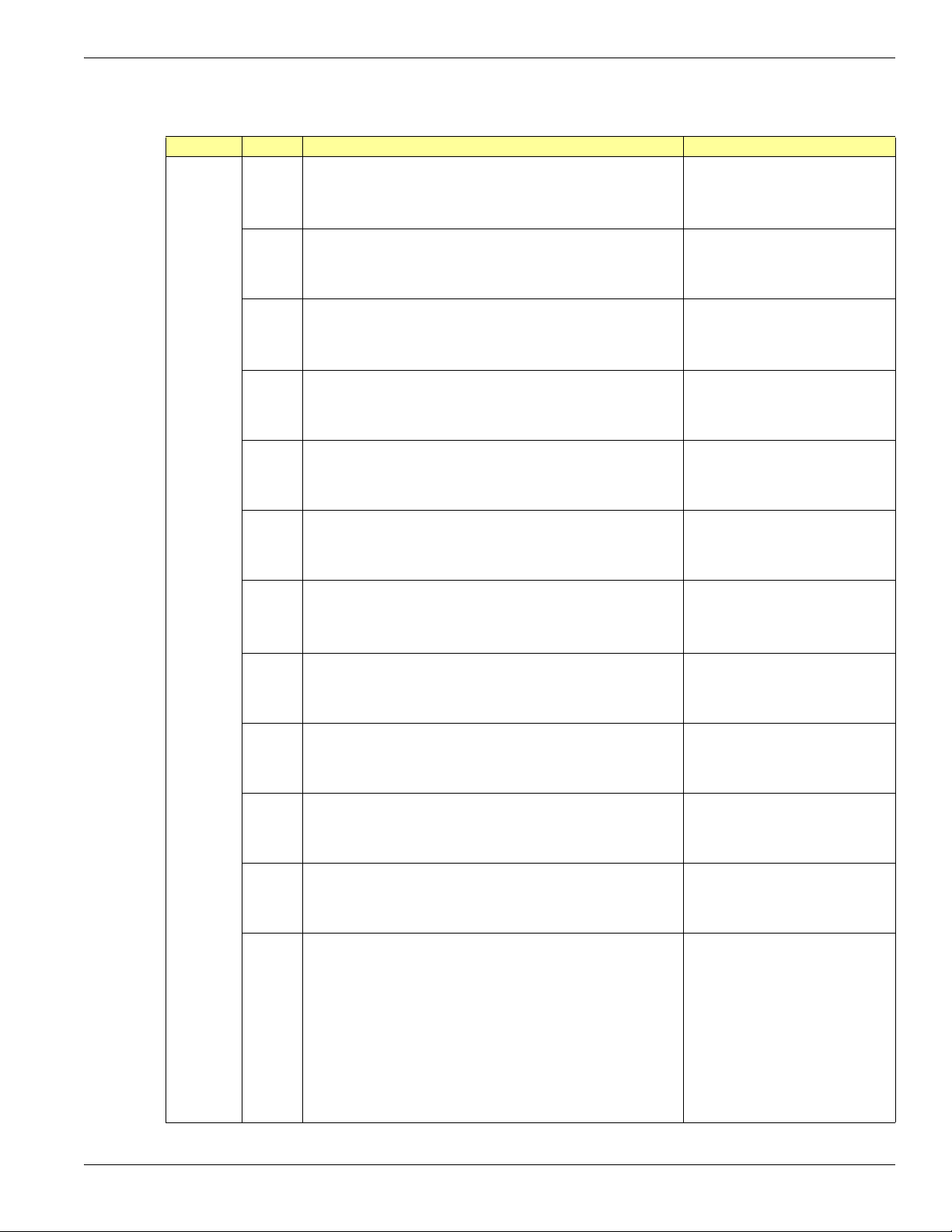

Table 5-4 PCIE Configurations

Lanes 0 to 3 4 to 7 8 to 11 12 to 15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

GFX x16 A

GFX x8 A

GFX x8 A

GFX x8 A GFX x8 B

GPP x4 A

GPP x4 B

GPP x4 A

GPP x4 B

GPP x4 A GPP x4 B

GPP x4 A GPP x4 B

GPP x4 A GPP x4 B

GPP x4 B GPP x4 A

GPP x4 A GPP x4 B

GFX x8 A GPP x4 B

GFX x8 A GPP x4 B

GPP x4 B GFX x8 A

GPP x4 A GFX x8 B

The core should be configured to run in single port mode if only Port A is present and in dual port mode whenever Port B

is present (regardless of Port A). The GFX ports are held from link training by default. To enable a GFX port, the

corresponding HOLD_TRAINING bit must be set to 0 to allow link training to proceed.

The SBIOS is responsible for programming the lane and clock muxing specific to each case. Refer to Chapter 7: PCIE

Initialization for DDI for programming details.

Note: This programming must be done before hold training is released.

AMD 780G Register Programming Requirements 1.01 © 2009 Advanced Micro Devices, Inc.

5-4

Page 33

5.4.1.1 Single Port Configuration (Default)

• PCIE_LINK_CFG – NBMISCIND:0x8

• Set MULTIPORT_CONFIG_GFX (Bits[11:8]) = 4’b0000

Table 5-5 Single Port Configuration (Default)

Device Possible Link Width HOLD_TRAINING Bit

Dev 2 1, 2, 4, 8 or 16 PCIE_LINK_CFG[4]

5.4.1.2 Dual Port Configuration

• PCIE_LINK_CFG – NBMISCIND:0x8

• Set MULTIPORT_CONFIG_GFX (Bits[11:8]) = 4’b0101

Table 5-6 Dual Port Configuration

Device Possible Link Width HOLD_TRAINING Bit

Dev 2 1, 2, 4 or 8 PCIE_LINK_CFG[4]

Dev 3 1, 2, 4 or 8 PCIE_LINK_CFG[5]

Table 5-7 Dual Port Configuration Register Settings

ASIC Rev Step Register Settings Function/Comment

RS780 All Revs 1 PCIE_NBCFG_REG6 – NBMISCIND:0x36

STRAP_BIF_all_valid (active low)

PCIE GFX Configurations

De-asserts STRAP_BIF_all_valid for PCIE-GFX

core.

5.4.2 DDI Modes Only

In the RS780, DDI is a collective term used to describe the supported display formats, which include DVI, HDMI and

DisplayPort. DVI and HDMI can run in either single link (x4, DDI_SL) or dual link (x8, DDL_DL) mode. DisplayPort

can run in x1, x2 or x4 mode.

Due to the fact that lanes 8-15 are sharing PLL C, the subgroups of lanes 8-11 and lanes 12-15 cannot be used