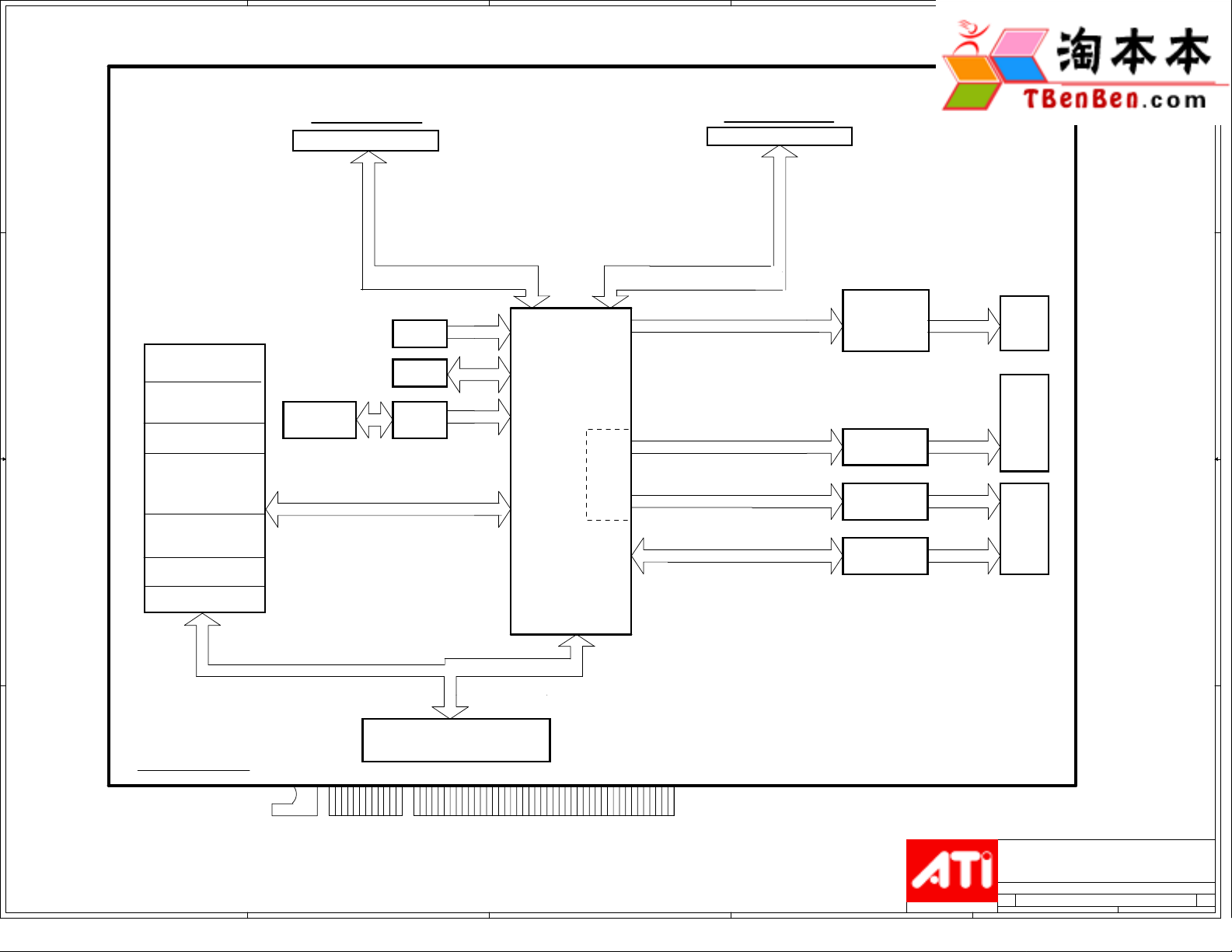

Page 1

5

4

3

2

1

D D

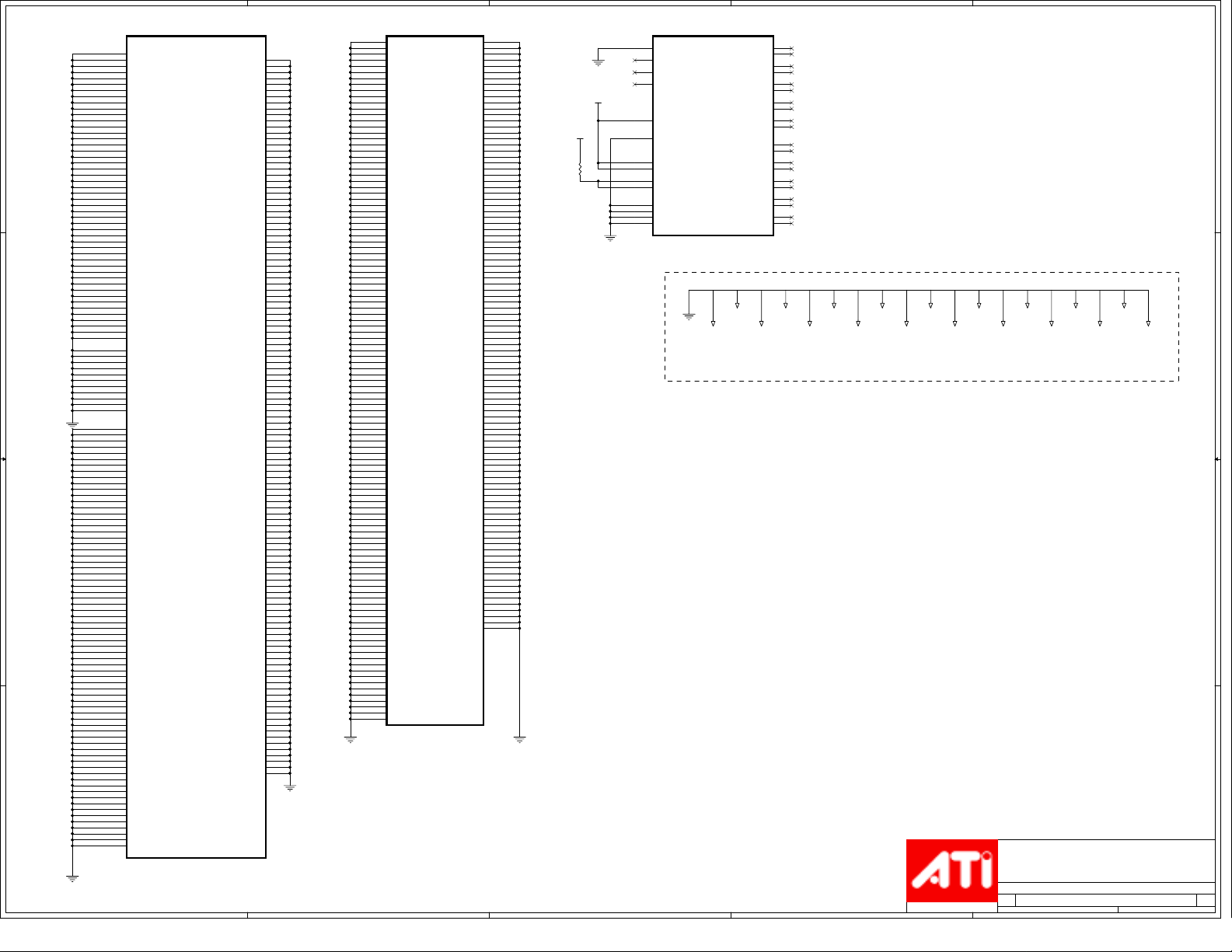

From +12V DIRECT:

FAN

C C

B B

POWER

REGULATION

SHT 14,15,16,17

From +12V_Bus

SWITCHING

+MVDDQ, +MVDDC, +VTT,

+VDDC, +PCIE_VDDRC

From +12V_Bus

Linear

+5V

From +3.3V_Bus

Linear

+VDD_1.8V, +VDDC_CT

+VPCIE_VDDR, +A2VDD,

+PVDD, +TPVDD, +MPVDD

PCIE_PVDD_18, VDDCI

From +3.3V DIRECT:

VDDR3

From +3.3V direct Or drivitive

VDDR4,5

From on board +5V

+RTAVDD

From +12V DIRECT:

FAN

MEMORY CHANNEL A B

GDDR3 8M X 32 (BGA)

Speed control

& temperature

sense

SHT 12

Channel A-B memory Address, Data nad Control signals

SHT 19

POWER DELIVERY

STRAPS

SHT 7

BIOS

SHT 4

FAN

SHT 19

ROMCS#

Channel C-D memory Address, Data nad Control signals

MEM A B MEM C D

GPIO

DAC1

ROM

R423

SHEET 3, 4, 5, 6, 8, 9

VIP

TVO

DAC2

CRT

TMDS

TMDS_TX[C,2..0]N TMDS_TX[C,2..0]P HPD, DDC2CLK DDC2DATA

MEMORY CHANNEL C D

GDDR3 8M X 32 (BGA)

R G B HSY VSY DDC1DATA DDC1CLK

SHT 13

CRT1

FILTERS

SHT 20, 22

TVOUT

FILTERS

SHT 23

CRT2 FILTERS

SHT 21

IMPEDANCE

MATCHING

Slim_VGA

slim

CONN

SHT 20

TVout

CONN

SHT 24

DVI-I

CONN

SHT 21

PCIE

+3.3V

+12V

Receiver and Transmitter differential lanes (x16),

PERST# and JTAG signals

R423 Stingray

BLOCK DIAGRAM REFLECTING DELL UHMGA11

CONFIGURATION.

PCIE_Bus x16

SHT 2

A A

5

4

12V_Bus

3.3V_Bus

COMPONENTS THAT ARE NOT POPULATED FOR DELL

UHMGA11 SKU ARE MARKED AS "DNI"

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

3

2

Date: Sheet

105-A474XX-10

1

123Thursday, November 11, 2004

2

of

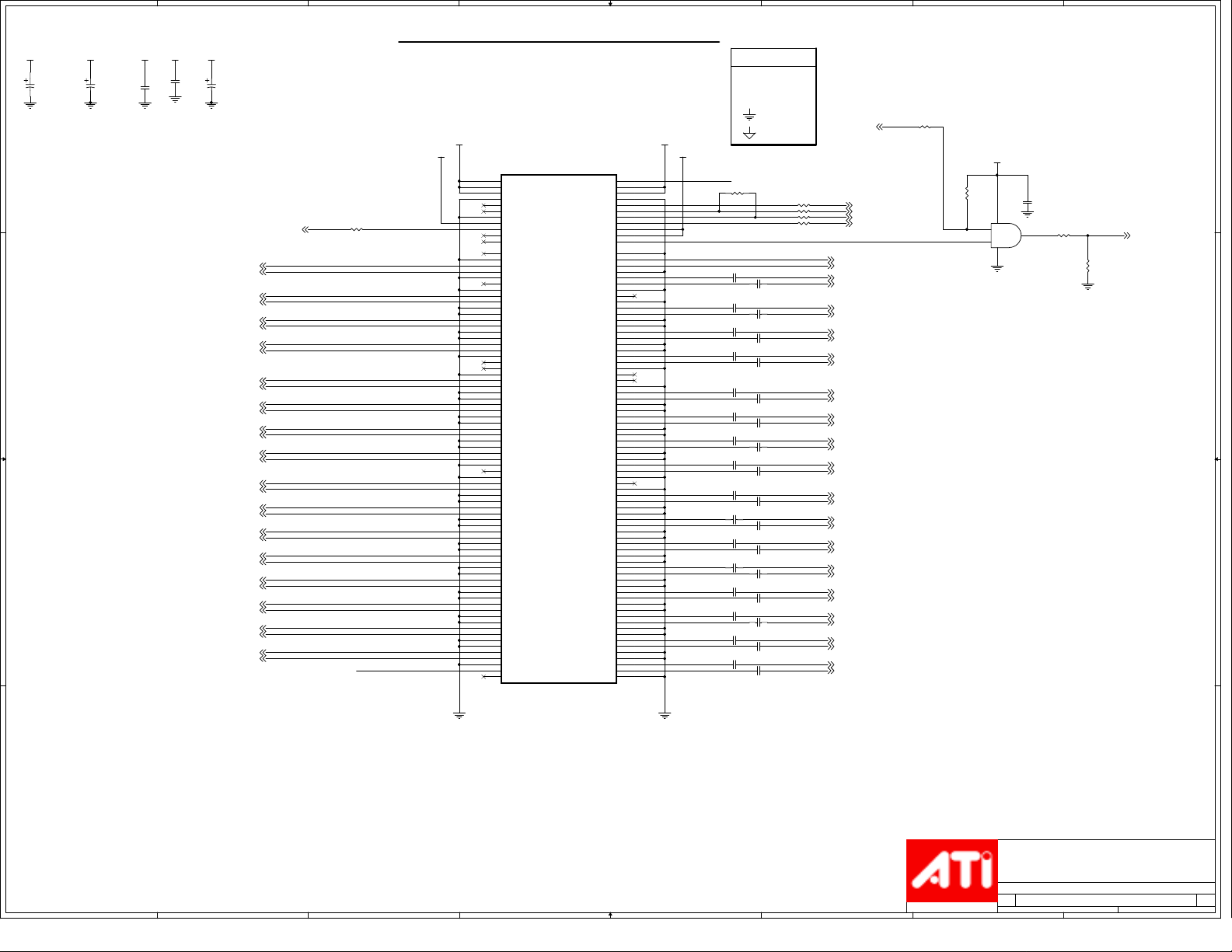

Page 2

8

7

6

5

4

3

2

1

PCI-EXPRESS EDGE CONNECTOR

+12V_BUS

C1616

100uF_16V

D D

C C

B B

C1617

100uF_16V

120nF

C11

+3.3V_BUS

+3.3V_BUS+12V_BUS+3.3V_BUS

USE 47uF TANTALUM

PETp10_GFXRp10(3)

PETn10_GFXRn10(3)

PETp11_GFXRp11(3)

PETn11_GFXRn11(3)

PETp12_GFXRp12(3)

PETn12_GFXRn12(3)

PETp13_GFXRp13(3)

PETn13_GFXRn13(3)

PETp14_GFXRp14(3)

PETn14_GFXRn14(3)

PETp15_GFXRp15(3)

PETn15_GFXRn15(3)

C1619

47uF_16V

>=6.3V

PETn0_GFXRn0(3)

PETp1_GFXRp1(3)

PETn1_GFXRn1(3)

PETp2_GFXRp2(3)

PETn2_GFXRn2(3)

PETp3_GFXRp3(3)

PETn3_GFXRn3(3)

PETp4_GFXRp4(3)

PETn4_GFXRn4(3)

PETp5_GFXRp5(3)

PETn5_GFXRn5(3)

PETp6_GFXRp6(3)

PETn6_GFXRn6(3)

PETp7_GFXRp7(3)

PETn7_GFXRn7(3)

PETp8_GFXRp8(3)

PETn8_GFXRn8(3)

PETp9_GFXRp9(3)

PETn9_GFXRn9(3)

CAPACITOR OR HIGHER

HSYNC_DAC1(4,14,16)

R1008 0R

DNI

PRESENCE

JTAG_TRST#

+3.3V_BUS

+12V_BUS

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

RSVD#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

Mechanical Key

x16 PCIe

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

MPCIE1

+12V_BUS

+3.3V_BUS

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

PRESENCE

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

100nF

C18

R1835

SYMBOL LEGEND

DNI

#

0R

RP216D 0R

RP216C 0R

RP216B 0R

RP216A 0R

C1620

100nF

C1621

100nF

C1622

100nF

C1623

100nF

C1624

100nF

C1625

100nF

C1626

100nF

C1627

100nF

C1628

100nF

C1629

100nF

C1630

100nF

C1631

100nF

C1632

100nF

C1633

100nF

C1634

100nF

C1635

100nF

C1636

100nF

C1637

100nF

C1638

C1639

100nF

100nF

C1640

100nF

C1641

100nF

C1642

100nF

C1643

100nF

C1644

100nF

C1645

100nF

C1646

100nF

C1647

100nF

C1648

100nF

C1649

100nF

C1650

100nF

C1651

100nF

DO NOT

INSTALL

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

54

63

72

81

VDDC_PGOOD(7)

DNI

VSYNC_DAC1 (4,14,16)

DNI

CRT1DDCDATA (4,16)

DNI

SCL (4,15,19)

DNI

CRT1DDCCLK (4,16)

PCIE_REFCLKP (3)

PCIE_REFCLKN (3)PETp0_GFXRp0(3)

GFXTp0_PERp0 (3)

GFXTn0_PERn0 (3)

GFXTp1_PERp1 (3)

GFXTn1_PERn1 (3)

GFXTp2_PERp2 (3)

GFXTn2_PERn2 (3)

GFXTp3_PERp3 (3)

GFXTn3_PERn3 (3)

GFXTp4_PERp4 (3)

GFXTn4_PERn4 (3)

GFXTp5_PERp5 (3)

GFXTn5_PERn5 (3)

GFXTp6_PERp6 (3)

GFXTn6_PERn6 (3)

GFXTp7_PERp7 (3)

GFXTn7_PERn7 (3)

GFXTp8_PERp8 (3)

GFXTn8_PERn8 (3)

GFXTp9_PERp9 (3)

GFXTn9_PERn9 (3)

GFXTp10_PERp10 (3)

GFXTn10_PERn10 (3)

GFXTp11_PERp11 (3)

GFXTn11_PERn11 (3)

GFXTp12_PERp12 (3)

GFXTn12_PERn12 (3)

GFXTp13_PERp13 (3)

GFXTn13_PERn13 (3)

GFXTp14_PERp14 (3)

GFXTn14_PERn14 (3)

GFXTp15_PERp15 (3)

GFXTn15_PERn15 (3)

R1833 0R

DNI

PERST#

74ACT08MTC

R1834

10K

+5V

C972

100nF

14

+-U2A

1

2

R1837 100R

3

7

R1838

180R

PERST#_buf (3,19,20)

A A

<Core Design>

8

7

6

5

4

3

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

Date: Sheet

2

105-A474XX-10

223Thursday, November 11, 2004

of

1

2

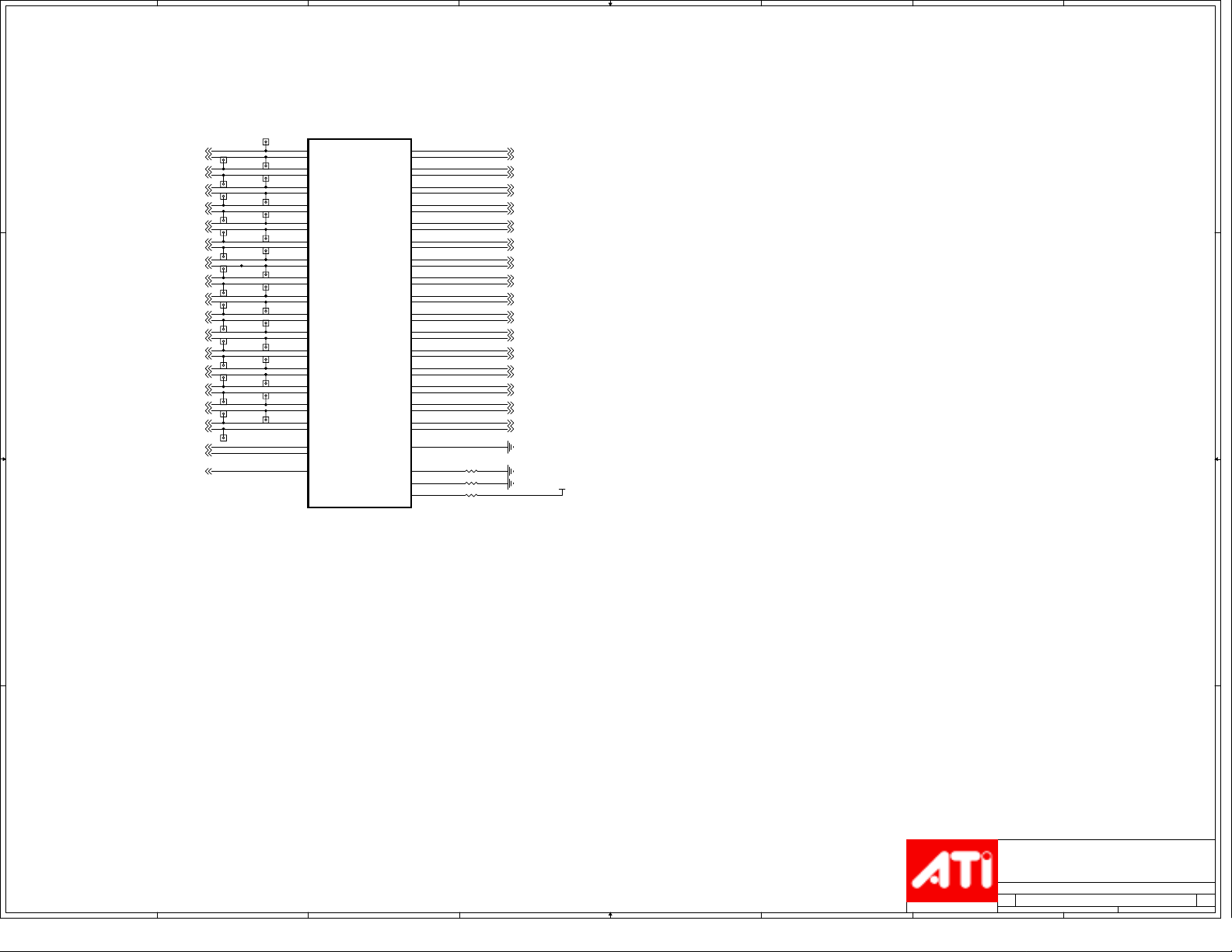

Page 3

8

7

6

5

4

3

2

1

D D

PETp0_GFXRp0(2) GFXTp0_PERp0 (2)

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

PETn3_GFXRn3(2)

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETn8_GFXRn8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

PETp10_GFXRp10(2)

C C

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

PCIE_REFCLKP(2)

PCIE_REFCLKN(2)

TP30

TP31

TP34

TP35

TP38

TP39

TP42

TP43

TP46

TP47

TP50

TP51

TP54

TP55

TP58

TP59

PERST#_buf(2,19,20)

ATI PN# 215RBKAGA11F

U1A

TP28

AU38

PCIE_RX0P

AU39

PCIE_RX0N

TP29

AT38

PCIE_RX1P

AR38

PCIE_RX1N

TP32

AR39

PCIE_RX2P

AP39

PCIE_RX2N

TP33

AP38

PCIE_RX3P

AN38

PCIE_RX3N

TP36

AM38

PCIE_RX4P

AM39

PCIE_RX4N

TP37

AL39

PCIE_RX5P

AL38

PCIE_RX5N

TP40

AK38

PCIE_RX6P

AJ38

PCIE_RX6N

TP41

AJ39

PCIE_RX7P

AH39

PCIE_RX7N

TP44

AH38

PCIE_RX8P

AG38

PCIE_RX8N

TP45

AG37

PCIE_RX9P

AF37

PCIE_RX9N

TP48

AF38

PCIE_RX10P

AF39

PCIE_RX10N

215RBKAGA11F

TP49

AE39

PCIE_RX11P

AE38

PCIE_RX11N

TP52

AD38

PCIE_RX12P

AC38

PCIE_RX12N

TP53

AC39

PCIE_RX13P

AB39

PCIE_RX13N

TP56

AB38

PCIE_RX14P

AA38

PCIE_RX14N

TP57

Y38

PCIE_RX15P

Y39

PCIE_RX15N

AH31

PCIE_REFCLKP

AG31

PCIE_REFCLKN

AM34

PERSTB

PART 1 OF 10

PCI

Express

Interface

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

PERSTb_MASK

CALRP

CALRN

AN36

AM36

AK34

AJ34

AK36

AJ36

AK35

AJ35

AH33

AG33

AE32

AE33

AG34

AF34

AG35

AF35

AD34

AC34

AD36

AC36

AD35

AC35

AE31

AD31

AB32

AA32

AB33

AA33

AA36

Y36

AA35

AA34

GFXTn0_PERn0 (2)

GFXTp1_PERp1 (2)

GFXTn1_PERn1 (2)

GFXTp2_PERp2 (2)

GFXTn2_PERn2 (2)

GFXTp3_PERp3 (2)

GFXTn3_PERn3 (2)

GFXTp4_PERp4 (2)

GFXTn4_PERn4 (2)

GFXTp5_PERp5 (2)

GFXTn5_PERn5 (2)

GFXTp6_PERp6 (2)

GFXTn6_PERn6 (2)

GFXTp7_PERp7 (2)

GFXTn7_PERn7 (2)

GFXTp8_PERp8 (2)

GFXTn8_PERn8 (2)

GFXTp9_PERp9 (2)

GFXTn9_PERn9 (2)

GFXTp10_PERp10 (2)

GFXTn10_PERn10 (2)

GFXTp11_PERp11 (2)

GFXTn11_PERn11 (2)

GFXTp12_PERp12 (2)

GFXTn12_PERn12 (2)

GFXTp13_PERp13 (2)

GFXTn13_PERn13 (2)

GFXTp14_PERp14 (2)

GFXTn14_PERn14 (2)

GFXTp15_PERp15 (2)

GFXTn15_PERn15 (2)

AL34

AV38

CALI

AN35

AM35

R101110K

R1009150R

R1010100R

PCIE_VDDR

B B

A A

<Variant Name>

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

8

7

6

5

4

3

Date: Sheet

2

105-A474XX-10

323Thursday, November 11, 2004

1

2

of

Page 4

8

VID[7..0]

VID[7..0](20)

D D

CLK_VIDCLK(20)

DVALID(14)

PSYNC(14)

VHAD1(20)

VHAD0(20)

VPHCTL(20)

CLK_VIPCLK(20)

DVOMODE_0(14)

DVOMODE_1(14)

DVO[11..0](19)

Install close to ASIC to provide

return path for EMI

C C

DC_Strap2(14)

DC_Strap3(14,21)

DC_Strap4(14)

PAL/NTSC(14)

DEMUX_SEL(14)

GPIO[6..0](14)

GPIO[13..8](8,14)

GPIO15(8)

ThermINT(15)

GPU_DPLUS(15)

GPU_DMINUS(15)

+PVDD

C27

C26

22uF_16V

OUT

C45

100nF

E/D

100nF

1.0uF

C44

3

1

B B

GND_PVSS

+MPVDD

C46

22uF_16V

GND_MPVSS

+3.3V_BUS

B3

220R

C1522

R1625

1K

1.0uF

A A

C1523

100nF

Oscillator Circuit

4

2

8

Y3

VCC

GND

27.000MHz

DVO[11..0]

C41

1.0uF

1.0uF

C43

R1623 22R

DNI

R57

221R

1.0uF

C42

7

PVDD

PVSS

7

6

+3.3V_BUS

+3.3V_BUS +3.3V_BUS

R51

4.7K

TP12

TP13

DVO_VSYNC(19)

DVO_HSYNC(19)

DVO_DE(19)

CLK_DVOCLK0(19)

DVO0

DVO1

DVO2

DVO3

DVO4

DVO5

DVO6

DVO7

DVO8

R587499R

DVO9

DVO10

DVO11

+3.3V_BUS

C52582pF

R586499R

MPVDD

MPVSS

R60

R58

4.7K

4.7K

DVOMODE_0

DVOMODE_1

HPD2_INT(19)

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

XTALIN

XTALOUT

To Rage Theater

XTALIN

R65

0R

221R

R63

R66

150R

XTALOUT

6

CLK_RT_XTALIN (20)

AK26

AJ26

AL24

AN25

AM23

AL23

AK23

AJ23

AM27

AL26

AK28

AJ20

AK20

AK19

AK18

AL20

AK22

AW20

AP23

AU13

AV14

AW14

AU14

AW15

AV15

AU15

AV16

AU16

AV17

AW17

AU17

AW18

AV18

AV19

AV20

AP17

AR17

AT17

AM18

AP19

AN19

AM19

AM21

AP20

AM22

AP22

AN22

AV13

AU12

AV12

AW12

AU11

AW11

AV11

AU10

AV10

AT13

AR14

AT14

AN15

AT15

AT16

AN16

AP16

AK15

AJ16

AJ17

AW36

AV36

AV37

AW37

AV9

A10

A11

5

U1B

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

Video Capture/

VID_7

VIP

VPCLK0

DVALID

PSYNC

VHAD_1

VHAD_0

VPHCTL

VIPCLK

SDA

SCL

DVOVMODE_0

DVOVMODE_1

ZV_LCDCNTL_0

ZV_LCDCNTL_1

ZV_LCDCNTL_2

215RBKAGA11F

ZV_LCDCNTL_3

ZV_LCDDATA_0

ZV_LCDDATA_1

ZV_LCDDATA_2

ZV_LCDDATA_3

ZV_LCDDATA_4

ZV_LCDDATA_5

ZV_LCDDATA_6

ZV_LCDDATA_7

ZV_LCDDATA_8

ZV_LCDDATA_9

ZV_LCDDATA_10

ZV_LCDDATA_11

ZV_LCDDATA_12

ZV_LCDDATA_13

ZV_LCDDATA_14

ZV_LCDDATA_15

ZV_LCDDATA_16

ZV_LCDDATA_17

ZV_LCDDATA_18

ZV_LCDDATA_19

ZV_LCDDATA_20

ZV_LCDDATA_21

ZV_LCDDATA_22

ZV_LCDDATA_23

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

VREFG

DPLUS

DMINUS

PVDD

PVSS

MPVDD

MPVSS

XTALIN

XTALOUT

5

PART 2 OF 10

DVO

GPIO

Thermal

Diode

Mem PLL

XTAL

TMDS

I2C

DAC1

DAC2

Hot Plug

DDC

PLL

TEST

ROM

GPIO9

ROMCS#

TXCM

TXCP

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TPVDD

TPVSS

TXVDDR_1

TXVDDR_2

TXVSSR_1

TXVSSR_2

TXVSSR_3

VSYNC

HSYNC

STEREOSYNC

AUXWIN

RSET

AVDD_1

AVDD_2

AVSSQ

AVSSN_1

AVSSN_2

VDD1DI

VSS1DI

H2SYNC

V2SYNC

COMP

R2SET

A2VDD_1

A2VDD_2

A2VSSN_1

A2VSSN_2

A2VDDQ

A2VSSQ

VDD2DI

VSS2DI

HPD1

DDC1DATA

DDC1CLK

DDC2DATA

DDC2CLK

DDC3DATA

DDC3CLK

TESTEN

ROMCSb

Test

AW23

AW24

AV24

AV25

AW26

AW27

AV27

AV28

AW21

AV22

AW29

AV30

AV29

AV26

AV23

AV33

R

AW33

G

AW32

B

AU36

AU35

AR36

AR35

AW35

AV34

AV35

AT34

AU34

AU33

AP35

AP36

AV31

R2

AU31

G2

AW30

B2

AN31

AP31

AR32

C

AT32

Y

AT31

AV32

AP28

AN28

AP29

AN29

AM28

AM29

AL29

AK29

AL16

AT36

AT35

AL17

AM16

AN32

AP32

AN33

AK13

81

54

63

72

SERIAL EEPROM 512K/1M

4

R52 499R

AVDD

GND_AVSSQ

R55 715R

1.0uF

C35

TESTEN

R91

10K

RP193A33R

RP193D33R

RP193C33R

RP193B33R

4

GND_R2SET

+3.3V_BUS

ROM_SOGPIO8

SI/A16

SCK/WEbGPIO10

CSb

HOLD1

GND_RSET

C36

100nF

R431K

+3.3V_BUS

INSTALL TERMINATION RESISTORS

CLOSE TO ASIC

R797 330R

R796 330R

R795 330R

R794 330R

1.0uF

C15

C9

22uF_16V

+AVDD

C40

C7

100nF

1.0uF

DNI

B8 Bead

C34

22uF_16V

C80

100nF

ALTERNATIVE PART :M25P05(512Kbit)

MU11

BIOS

113-A47401-001

U11

5

D

6

C

1

S

7

HOLD

3

W

8

VCC

M25P05-AVMN6T

+VDD_1.8V+VDD2DI

VSS

C23

22uF_16V

Q

C17

82pF

GND_AVSSN

1.0uF

DNI

C31

GND_A2VSSN

2

4

3

TXVDDR

B5

Bead

3

Ba3

C33

100nF

C13

100nF

C8

82pF

ROMCS#

+TPVDD

+VDD_1.8V

+A2VDD

C32

1.0uF

C37

C16

22uF_16V

GND_TPVSS

C21

100nF

22uF_16V

1.0uF

C29

+A2VDDQ

C38

100nF

GND_A2VSSQ

<Variant Name>

R44

Rk

0R

DNI

Ba2

B4

Bead

GND_TXVSSR

+VDDDI

C30

100nF

Ba5

C39

22uF_16V

2

TXCM (18)

TXCP (18)

TX0M (18)

TX0P (18)

TX1M (18)

TX1P (18)

TX2M (18)

TX2P (18)

+VDD_1.8V

+3.3V_BUS

R50

4.7K

R_DAC1 (16)

G_DAC1 (16)

B_DAC1 (16)

VSYNC_DAC1 (2,14,16)

HSYNC_DAC1 (2,14,16)

STEREOSYNC (21)

+VDD_1.8V

B7

C28

Bead

22uF_16V

R_DAC2 (17)

G_DAC2 (17)

B_DAC2 (17)

HSYNC_DAC2 (14,17)

VSYNC_DAC2 (14,17)

C_DAC2 (21)

Y_DAC2 (21)

COMP_DAC2 (21)

+VDD_1.8V

B9

Bead

+3.3V_BUS +3.3V_BUS

R53

R54

4.7K

4.7K

HPD1 (18)

SDA (15,19)

SCL (2,15,19)

CRT1DDCDATA (2,16)

CRT1DDCCLK (2,16)

CRT2DDCDATA (17)

CRT2DDCCLK (17)

+3.3V_BUS

R1836

10R

JU_LED

JU2

SDA

R25 33R

SCL

R26 33R

Title

Size Document Number Rev

C

Date: Sheet

2

1

2

3

4

4x2mm

JU_LED connector in

the vicinity of Top Left

corner

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

105-A474XX-10

1

423Thursday, November 11, 2004

1

2

of

Page 5

5

4

3

2

1

U1G

A7

VDDR1_1

E1

VDDR1_2

T36

VDDR1_3

A17

VDDR1_4

A19

VDDR1_5

A22

VDDR1_6

A26

D D

+MVDDQ

C600

10nF

C70

10uf

C72

10uf

C617

C616

10nF

10nF

C C

B B

+MVDDQ

B29 220R

B30 220R

C668

1.0uF

C669

100nF

C71

10uf

C618

10nF

C73

10uf

C667

1.0uF

C601

10nF

C602

10nF

C608

10nF

C612

10nF

C619

10nF

B31 220R

C670

100nF

C613

10nF

C620

10nF

C609

10nF

C603

10nF

C666

1.0uF

C604

10nF

C610

10nF

C615

C614

10nF

10nF

C621

C622

10nF

10nF

B32 220R

C671

100nF

C611

10nF

C605

10nF

GND_VSSRH0GND_VSSRH1GND_VSSRH2GND_VSSRH3

C623

10nF

C665

1.0uF

C707

C69

1uF

100nF

C606

10nF

C708

100nF

C676

100nF

C672

100nF

C607

10nF

AM15

AW9

AW6

AL15

AM14

AL10

AH10

AH12

AG14

AG13

AF13

W13

AE13

A29

A32

N14

K39

F8

J11

M14

AR1

AK1

AM7

AL8

G8

L14

U1

U11

AL7

H9

AK9

AG7

AK4

N13

AF8

N27

W7

L10

H8

G9

AF7

V13

AA1

AD1

AF1

Y8

K11

V11

U6

T33

U33

U34

M13

L13

G20

G19

L22

L23

N29

P29

L31

M1

M12

H20

M23

N25

N26

M30

M31

N16

N17

N18

N21

N22

N23

N39

R1

Y7

U27

T27

N28

U13

U12

C38

A13

H1

AM1

D36

A14

J1

AN1

VDDR1_7

VDDR1_8

VDDR1_9

VDDR1_10

VDDR1_11

VDDR1_12

VDDR1_13

VDDR1_14

VDDR1_15

VDDR1_16

VDDR1_17

VDDR1_18

VDDR1_19

VDDR1_20

VDDR1_21

VDDR1_22

VDDR1_23

VDDR1_24

VDDR1_25

VDDR1_26

VDDR1_27

VDDR1_28

VDDR1_29

VDDR1_30

VDDR1_31

VDDR1_32

215RBKAGA11F

VDDR1_33

VDDR1_34

VDDR1_35

VDDR1_36

VDDR1_37

VDDR1_38

VDDR1_39

VDDR1_40

VDDR1_41

VDDR1_42

VDDR1_43

VDDR1_44

VDDR1_45

VDDR1_46

VDDR1_47

VDDR1_48

VDDR1_49

VDDR1_50

VDDR1_51

VDDR1_52

VDDR1_53

VDDR1_54

VDDR1_55

VDDR1_56

VDDR1_57

VDDR1_58

VDDR1_59

VDDR1_60

VDDR1_61

VDDR1_62

VDDR1_63

VDDR1_64

VDDR1_65

VDDR1_66

VDDR1_67

VDDR1_68

VDDR1_69

VDDR1_70

VDDR1_71

VDDR1_72

VDDR1_73

VDDR1_74

VDDR1_75

VDDR1_76

VDDR1_77

VDDR1_78

VDDR1_79

VDDR1_80

VDDR1_81

VDDR1_82

VDDR1_83

VDDR1_84

VDDR1_85

VDDR1_86

VDDR1_87

VDDR1_88

VDDR1_89

VDDR1_90

VDDRH_0

VDDRH_1

VDDRH_2

VDDRH_3

VSSRH_0

VSSRH_1

VSSRH_2

VSSRH_3

Memory I/O

Memory I/O

Clock Generator

PART 7 OF 10

POWER

I/O

PCIE

CORE

I/O (INTERNAL)

PCIE_VDDR_12_10

PCIE_VDDR_12_9

PCIE_VDDR_12_1

PCIE_VDDR_12_2

PCIE_VDDR_12_3

PCIE_VDDR_12_4

PCIE_VDDR_12_5

PCIE_VDDR_12_6

PCIE_VDDR_12_7

PCIE_VDDR_12_8

PCIE_PVDD_12_1

PCIE_PVDD_12_2

PCIE_PVDD_12_3

PCIE_PVDD_12_4

PCIE_PVDD_12_5

PCIE_PVDD_18_1

PCIE_PVDD_18_2

PCIE_PVDD_18_3

PCIE_PVDD_18_4

PCIE_PVDD_18_5

PCIE_PVDD_18_6

PCIE_PVDD_18_7

VDDR3_1

VDDR3_2

VDDR3_3

VDDR3_4

VDDR3_5

VDDR3_6

VDDR3_7

VDDR3_8

VDDR4_1

VDDR4_2

VDDR4_3

VDDR4_4

VDDR4_5

VDDR4_6

VDDR5_1

VDDR5_2

VDDR5_3

VDDR5_4

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDDC_24

VDDC_25

VDDC_26

VDDC_27

VDDC_28

VDDC_29

VDDC_30

VDDC_31

VDDC_32

VDDC_33

VDDC_34

VDDC_35

VDDC_36

VDDC_37

VDDCI_8

VDDCI_7

VDDCI_6

VDDCI_5

VDDCI_4

VDDCI_3

VDDCI_2

VDDCI_1

VDD15_6

VDD15_5

VDD15_4

VDD15_3

AH16

AH28

AH27

AG16

AJ28

AJ29

AH15

AJ27

AH21

AJ22

AH22

AK21

AL21

AL22

AH18

AH19

AL18

AL19

AE28

AF28

AG29

AG28

AK31

AK30

AJ30

AJ31

AF30

AF29

AD28

AC27

AC29

AD27

AC28

AB30

AA30

AA29

AB29

AB28

AA28

AB27

AC21

U19

U21

AC19

V18

V19

V20

V21

V22

W18

W19

W20

W21

W22

Y19

Y20

Y21

AA18

AA19

AA20

AA21

AA22

AB18

AB19

AB20

AB21

AB22

W17

Y18

AA17

AA23

Y22

W23

U18

U22

AC18

AC22

Y27

Y13

N20

AG20

AC20

Y23

Y17

U20

AG22

AG21

AG18

AG17

+VDDR4

+VDDR5

change to 4210010600

+VDDC_CT

+3.3V_BUS

C66

C624

1.0uF

C709

C710

100nF

100nF

C1669

100nF

C1673

1nF

C1676

1nF

C53

22uF_16V

C634

10nF

C639

10nF

C1670

1nF

C1674

100nF

C1677

100nF

10nF

C59

10uF_10V

C635

10nF

C640

10nF

C646

10nF

C67

22uF_16V

B12 220R

C74

1.0uF

B14 220R

C75

1.0uF

C1668

C1702

10uF_6.3V

10uF_6.3V

PCIE_PVDD_12

C1703

10uF_6.3V

C1704

C1675

10uF_6.3V

10uF_6.3V

C632

C633

10nF

10nF

C637

C638

10nF

10nF

C62

C61

10uf

10uf

C48

100nF

C50

C49

100nF

100nF

C625

10nF

DNI

R69 0R

R70 0R

DNI

R67 0R

R68 0R

L81

60R

PCIE_PVDD_18

C636

1.0uF

C641

10nF

C63

10uF_10V

C648

10nF

C626

10nF

+3.3V_BUS

+VDD_1.8V

+3.3V_BUS

+VDD_1.8V

C56

1.0uF

C642

10nF

+VDDC

C60

10uf

C627

10nF

L82

42r@100MHz

PCIE_VDDR

C57

1.0uF

C643

10nF

C1952

10nF

+VDDC

C673

1.0uF

C644

10nF

C1953

10nF

C1954

10nF

C1955

10nF

A A

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

5

4

3

2

Date: Sheet

105-A474XX-10

1

2

of

523Thursday, November 11, 2004

Page 6

5

4

3

2

1

U1H

AB31

AD33

AD32

AD37

AG36

AE35

AE36

AH35

AG30

AF32

Y34

D D

C C

B B

A A

AH37

AH36

AE29

AN37

AH30

AC32

AK37

AD29

AF33

AL35

AM37

AJ33

AL37

AL32

AE34

AF36

AC30

AF27

AG32

AJ37

AC33

AH32

AH34

AF31

AD30

AB34

AC31

AB37

AC37

AL33

AB35

AB36

AE37

AA37

AE30

AA31

AE27

AR37

AT37

AP37

AN34

AL36

AK33

AK32

AJ32

AL11

AJ15

Y37

Y35

Y33

A8

J10

R33

A16

A20

A23

A25

A28

A31

B3

G37

Y6

D10

D13

D19

D28

D34

D35

F1

E4

E9

E10

E12

E13

E18

E19

E27

E28

E33

E34

E38

F4

F5

G6

H10

F13

F19

F28

H34

C34

G5

G7

H11

G11

G13

G14

G16

G17

G23

G33

G34

G35

V31

F25

G10

H7

F11

H14

H17

M29

H33

H39

J5

K5

F9

F10

F16

J15

PCIE_VSS_1

PCIE_VSS_2

PCIE_VSS_3

PCIE_VSS_4

PCIE_VSS_5

PCIE_VSS_6

PCIE_VSS_7

PCIE_VSS_8

PCIE_VSS_9

PCIE_VSS_10

PCIE_VSS_11

PCIE_VSS_12

PCIE_VSS_13

PCIE_VSS_14

PCIE_VSS_15

PCIE_VSS_16

PCIE_VSS_17

PCIE_VSS_18

PCIE_VSS_19

PCIE_VSS_20

PCIE_VSS_21

PCIE_VSS_22

PCIE_VSS_23

PCIE_VSS_24

PCIE_VSS_25

PCIE_VSS_26

PCIE_VSS_27

PCIE_VSS_28

PCIE_VSS_29

PCIE_VSS_30

PCIE_VSS_31

PCIE_VSS_32

PCIE_VSS_33

PCIE_VSS_34

PCIE_VSS_35

PCIE_VSS_36

PCIE_VSS_37

PCIE_VSS_38

PCIE_VSS_39

PCIE_VSS_40

PCIE_VSS_41

PCIE_VSS_42

PCIE_VSS_43

PCIE_VSS_44

PCIE_VSS_45

PCIE_VSS_46

PCIE_VSS_47

PCIE_VSS_48

PCIE_VSS_50

PCIE_VSS_51

PCIE_VSS_52

PCIE_VSS_53

PCIE_VSS_54

PCIE_VSS_55

PCIE_VSS_56

PCIE_VSS_57

PCIE_VSS_58

PCIE_VSS_59

PCIE_VSS_60

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

215RBKAGA11F

5

PART8OF10

GND

VSS_280

VSS_279

VSS_278

VSS_277

VSS_276

VSS_275

VSS_274

VSS_273

VSS_272

VSS_271

VSS_270

VSS_269

VSS_268

VSS_267

VSS_266

VSS_265

VSS_264

VSS_263

VSS_262

VSS_261

VSS_260

VSS_259

VSS_258

VSS_257

VSS_256

VSS_255

VSS_254

VSS_253

VSS_252

VSS_251

VSS_250

VSS_249

VSS_248

VSS_247

VSS_246

VSS_245

VSS_244

VSS_243

VSS_242

VSS_241

VSS_240

VSS_239

VSS_238

VSS_237

VSS_236

VSS_235

VSS_234

VSS_233

VSS_232

VSS_231

VSS_230

VSS_229

VSS_228

VSS_227

VSS_226

VSS_225

VSS_224

VSS_223

VSS_222

VSS_221

VSS_220

VSS_219

VSS_218

VSS_217

VSS_216

VSS_215

VSS_214

VSS_213

VSS_212

VSS_211

VSS_210

VSS_209

VSS_208

VSS_207

VSS_206

VSS_205

VSS_204

VSS_203

VSS_202

VSS_201

VSS_200

VSS_199

VSS_198

VSS_197

VSS_196

VSS_195

VSS_194

VSS_193

VSS_192

VSS_191

VSS_190

VSS_189

VSS_188

VSS_187

VSS_186

VSS_185

VSS_184

VSS_183

VSS_182

VSS_181

VSS_180

VSS_179

VSS_178

VSS_177

VSS_176

VSS_175

VSS_174

VSS_173

VSS_172

VSS_171

VSS_170

VSS_169

VSS_168

VSS_167

VSS_166

VSS_165

VSS_164

VSS_163

VSS_162

AL27

AH20

AK25

R35

T34

AK16

L20

AL5

AV21

AN7

AL6

AH5

AK27

AH26

AK6

AN26

AK17

AL12

U30

AM6

AK8

AG6

AG5

AG4

AR34

AJ18

AL25

AJ14

AK14

AP8

AJ8

AJ7

AJ1

AH17

AH14

AG19

AG23

AG15

AG1

AR33

AT33

AP33

J6

AU18

AP34

AE9

AE5

T35

F30

E30

K31

H31

F31

H32

AD13

AD11

AD10

AD9

AD7

AC6

AD5

AD6

E21

D22

G32

G36

AC13

AC12

AC11

AC8

AC7

AC1

E22

F22

M25

J7

AU37

AT12

H4

V23

AB23

AB13

AB9

AB5

AU32

W11

AF4

AA13

AA11

AA10

AA9

U7

W6

Y5

AA5

AJ9

AR19

Y28

AG25

AU9

Y12

Y11

U8

V7

Y1

AJ19

Y32

Y30

Y29

W35

W30

W34

W27

V35

W32

V27

AB17

V17

V1

AU27

AH23

AJ25

AM33

AC17

AC23

4

J16

J24

J25

L29

N36

N35

J35

F7

K16

K25

K33

K34

K35

K36

L1

L7

L9

L11

E16

L16

L17

L25

L26

J34

L33

L39

P4

N5

M8

M7

M9

M10

M11

E15

M17

M26

M35

P5

N9

L12

J4

D16

N15

N19

J30

N24

H23

G22

U28

U29

N30

N31

N33

N34

P1

P8

P7

P11

P12

P13

P27

P28

T29

L30

M33

P39

R4

R5

R6

R7

R9

R10

R11

R13

R27

T5

T9

T13

U17

Y31

U23

K30

H29

J29

K29

G28

H28

J28

G26

H26

D25

E25

G25

E24

J22

K22

J21

J19

K19

J18

J14

J13

K13

D7

E7

E6

U5

U1I

VSS_71

PART9OF10

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_156

VSS_158

VSS_159

VSS_160

VSS_371

VSS_372

VSS_373

VSS_374

VSS_375

VSS_376

VSS_377

VSS_378

VSS_379

VSS_380

VSS_381

VSS_382

VSS_383

VSS_384

VSS_385

VSS_386

VSS_387

VSS_388

VSS_389

VSS_390

VSS_391

VSS_392

VSS_393

VSS_394

VSS_395

VSS_396

215RBKAGA11F

VSS_363

VSS_362

VSS_361

VSS_360

VSS_359

VSS_358

VSS_357

VSS_356

VSS_355

VSS_354

VSS_353

VSS_352

VSS_351

VSS_350

VSS_349

VSS_348

VSS_347

VSS_346

VSS_345

VSS_344

VSS_343

VSS_342

VSS_341

VSS_340

VSS_339

VSS_338

VSS_337

VSS_336

VSS_335

VSS_334

VSS_333

VSS_332

VSS_331

VSS_330

VSS_329

VSS_328

VSS_327

VSS_326

VSS_325

VSS_324

VSS_323

VSS_322

VSS_321

VSS_320

VSS_319

VSS_318

VSS_317

VSS_316

VSS_315

VSS_314

VSS_313

VSS_312

VSS_311

VSS_310

VSS_309

VSS_308

VSS_307

VSS_306

VSS_305

VSS_304

VSS_303

VSS_302

VSS_301

VSS_300

VSS_299

VSS_298

VSS_297

VSS_296

VSS_295

VSS_294

VSS_293

VSS_292

VSS_291

VSS_290

VSS_289

VSS_288

VSS_287

VSS_286

VSS_285

VSS_284

VSS_283

VSS_282

VSS_281

VSS_411

VSS_410

VSS_409

VSS_408

VSS_407

VSS_406

VSS_405

VSS_404

VSS_403

VSS_402

VSS_401

VSS_400

VSS_399

VSS_398

VSS_397

AA27

W36

W37

W39

R32

D12

E36

AK24

AW8

AW5

AT6

AT1

R28

AT27

AT24

D26

AT21

F17

M20

AT11

AT7

AR8

AN5

AL4

AR31

AM26

AR28

AU24

AR25

AU21

AR22

AJ24

AR18

AR16

AR15

AP14

AR12

AR9

AT8

AR7

AP10

AP30

AP27

AN24

AP21

AP18

AP15

AN11

AP9

AR5

AR13

AN30

AH25

AN27

AN23

AM24

AU30

AN21

AN20

AN18

AN17

AJ21

AN14

AN10

AM10

AM8

AT3

AN8

AT30

AH29

AM31

AT18

AM30

AM25

AP24

AM20

AM17

L19

AM11

AN9

AP7

AL31

AL28

AK5

AK11

AJ12

AJ11

AH9

AG11

AG10

AG9

AF11

AF12

W9

V10

V9

V5

V4

+A2VDD

+VDD_1.8V

R71

4.7K

U1J

AM32

PART 10 OF 10

SSIN

AL30

NC_1

AL13

NC_2

AL14

NC_3

AP25

LPVDD

AP26

LPVSS

AH24

LVDDR_18/VDDL0_1

AG24

LVDDR_18/VDDL0_2

AG27

LVDDR_25/VDDL1_1

AG26

LVDDR_25/VDDL1_2

AR27

LVSSR_1

AR26

LVSSR_2

AR21

LVSSR_3

AR20

LVSSR_4

215RBKAGA11F

GND_MPVSS GND_TPVSS GND_RSETGND_AVSSQ

3

AR29

NC_4

AR30

NC_5

AU28

NC_6

AU29

NC_7

AT28

NC_8

AT29

NC_9

AU25

NC_10

AU26

NC_11

AT25

NC_12

AT26

NC_13

AR23

NC_14

AR24

NC_15

AU22

NC_16

AU23

NC_17

AT22

NC_18

AT23

NC_19

AU19

NC_20

AU20

NC_21

AT19

NC_22

AT20

NC_23

GND_A2VSSN

GND_A2VSSQ

NOTE: THIS IS A DRAWING. THESE GROUNDS MUST

BE MANUALLY CONNECTED TO THE GROUND PLANE

<Variant Name>

2

GND_VSSRH0

GND_TVVSSNGND_AVSSN GND_R2SET

GND_VSSRH2

GND_VSSRH1

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

Date: Sheet

GND_P

GND_VSSRH3GND_TXVSSRGND_PVSS

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

105-A474XX-10

GND_RT

GND_A GND_VIN

1

623Thursday, November 11, 2004

2

of

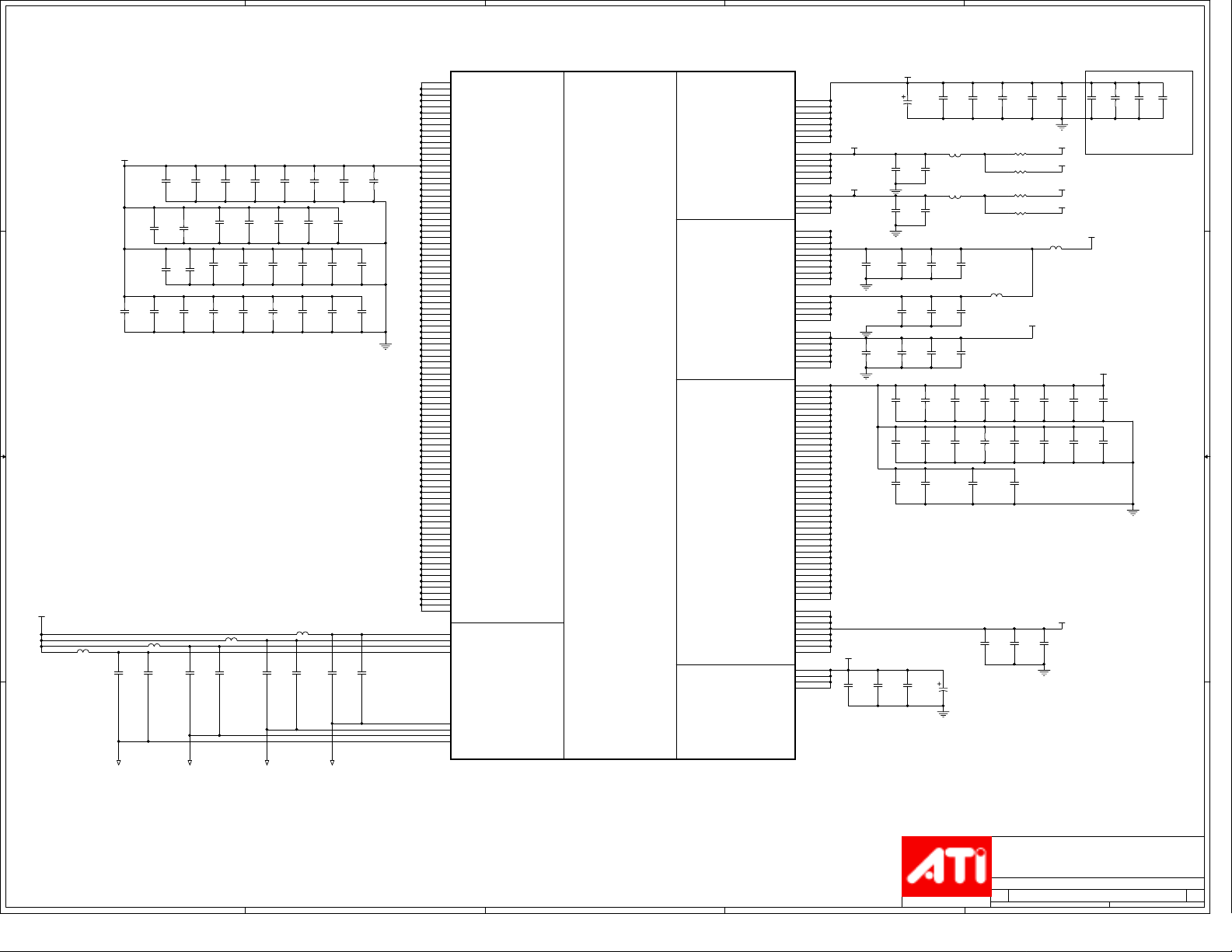

Page 7

8

7

6

5

4

3

2

1

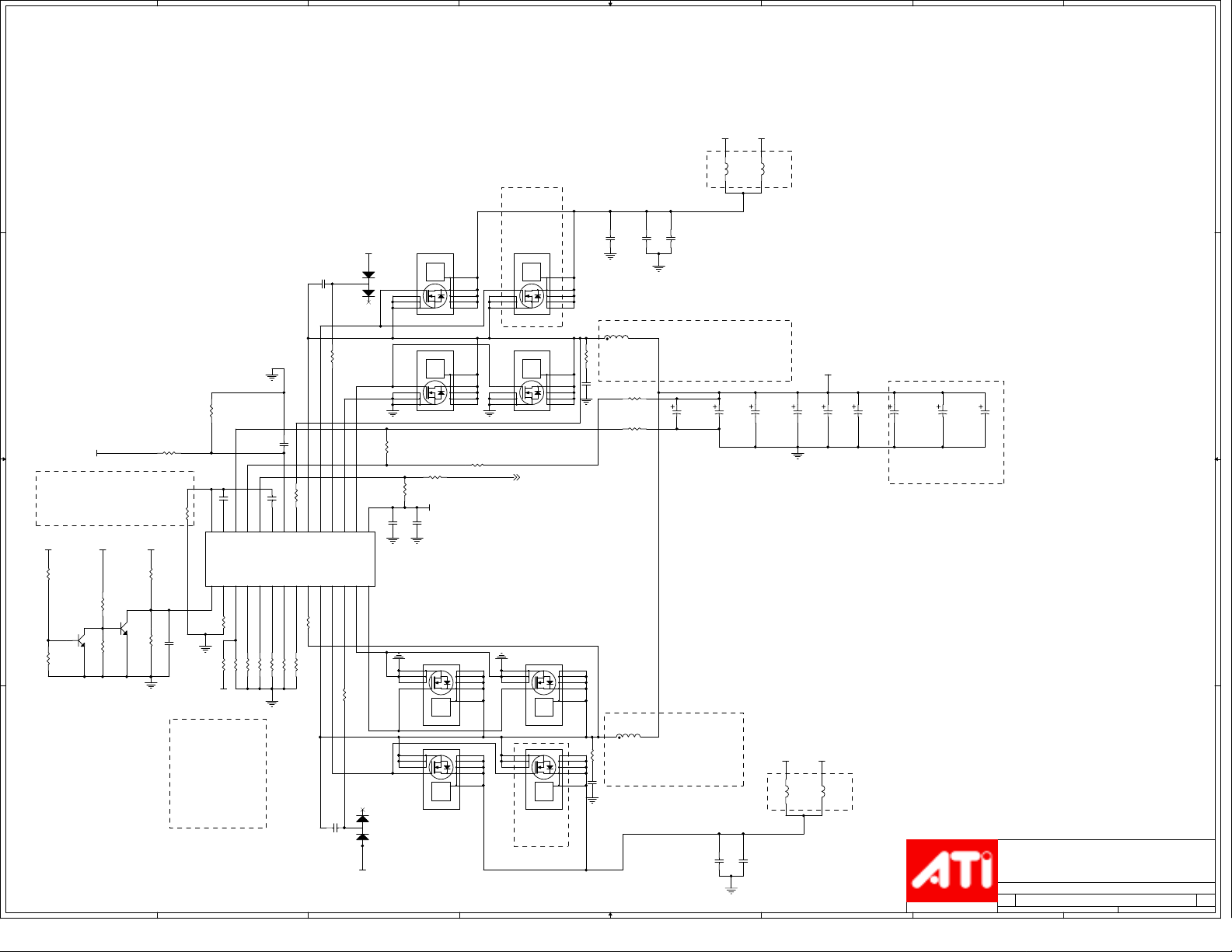

D D

OPTIONAL

CORE REGULATOR VDDC

Trace as short as possible for 2A current

*

C1151 100nF

C C

R1632

DNI

432R

C1173

1uF

C1157

1.00K

R1591

22nf

17

16

18

DELAY

VCORE-

R18531K

R18541K

R18521K

DNI

+5V

7

19

VCORE+

R18551K

21

20

SS

VIN

PGOOD

FAN5240MTCX

R18561K

R18571K

DNI

DNI

22

23

ISNS1

R1603

R18581K

1

R1860

15K

R1861

2K

Q37

CMPT3904

2 3

R1593 432R

R1619

0R

+5V

R1840

2K

R1602

4.7K

C1160

1nf

C1156

220nF

15

U43

AGND

14

R1596

41.2K

VID

4 3 2 1 0 +VDDC

--------------------------------1 0 0 1 1 1.200

1 0 0 1 0 1.225

1 0 0 0 1 1.250

1 0 0 0 0 1.275

0 1 1 1 0 1.300

0 1 1 0 1 1.350

0 1 1 0 0 1.400

+12V_BUS

Do not install

This resistor will

be shorted in layout.

+3.3V_BUS +12V_BUS

B B

A A

R1595

243R

Q225

CMPT3904

1

R1598

221R

2 3

8

BAT54SLT1

25

24

SW1

HDRV1

1.00K

C1161 100nF

BOOT1

R1589

0R

+5V

1

3

D28

2

*

27

28

26

LDRV1

PGND1

R1590

0R

2

3

D29

1

BAT54SLT1

+5V

VCC

LDRV21PGND22BOOT23HDRV24SW25ISNS26VID47VID38VID29VID110VID011FPWM12ILIM13EN

R1597

1.50K

R1594

10K

*

*

6

Q27

4 5

3

2

1

FDS7096N3

Q28

4 5

3

2

1

FDS7064N

R873 0R

C1159

C1158

0.22uF

10uf

FDS7064N

1

2

3

4 5

Q210

FDS7096N3

1

2

3

4 5

Q31

Thermal

Thermal

Pad

9

6

7

8

Pad

9

6

7

8

DNI

+5V

*

8

7

6

9

Pad

Thermal

8

7

6

9

Pad

Thermal

FDS7096N3

4 5

3

2

1

Q29

4 5

3

2

1

FDS7064N

R1592432R

1

2

3

4 5

1

2

3

4 5

Q232

Thermal

Pad

9

6

7

8

Q231

Thermal

Pad

9

6

7

8

***

VDDC_PGOOD (2)

FDS7064N

Pad

Thermal

Q224

Pad

Thermal

FDS7096N3

OPTIONAL

5

8

7

6

9

8

7

6

9

VIN1

C1692

C1688

10uF

100nF

L63 1.71uH

1 2

R1851

2.2R

C1706

1nF

R1617

0R

DNI

PADS SHORTED IN

LAYOUT

R1618

0R

DNI

PADS SHORTED IN

LAYOUT

L64

1 2

R1859

2.2R

CHANGE TO 1.5uH 23A

VISHAY IHLP5050EZRZ1R5M01

C1707

1nF

VIN2

CHANGE TO 1.5uH 23A

VISHAY IHLP5050EZRZ1R5M01

1.71uH

C1689

10uF

C1532

33uF_16V

4

+12VEXT+12V_BUS

C1691

10uF

C1153

1500uF

B78

60R

+VDDC

C1154

1500uF

+12VEXT+12V_BUS

60R

B79

DNI

C1155

1500uF

B80

60R

3

C1951

1500uF

C1948

330uF_2.5V

OPTIONAL

DNI

<Variant Name>

C1949

330uF_2.5V

C1950

330uF_2.5V

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

Date: Sheet

2

105-A474XX-10

723Thursday, November 11, 2004

of

1

2

60R

B72

DNI

C1152

1500uF

C1690

10uF

Page 8

8

7

6

5

4

3

2

1

+12V_BUS +5V

DNI

R372

R373

0R

2R2

1

D4

BAT54SLT1

3

DNI

C142

1uF

2

DNI

C136

0.22uF

C141

22nf

D D

Alternative 1

+PW_VDDC1

SS_VDDC1

COMP_VDDC1

Fb_VDDC1

C C

+12V_BUS +5V

DNI

R371

R370

2R2

0R

1

D5

BAT54SLT1

3

R112

DNI

0R

2

R314 0R

C158

0.22uF

DNI

C157

1uF

C169

22nf

B B

Alternative 1

R305 51K

+PW_VDDC2

R306 3K

SS_VDDC2

COMP_VDDC2

Fb_VDDC2

A A

8

MVDDQ Switching Regulator for

Memory Core for 256M

configuration

BST1

R376

0R

R251 0R

SS_VDDC1

Fb_VDDC1

COMP_VDDC1

UVIN1

SWN1

Alternative 2

R258 51K

R259 3K

BOOT_VDDC1

U31

DNI

7

BST

SS

GH

4

Vfb

5

GND

COMP

6

GL

UVIN

8

Vcc

SWN

SP6132

SIPEX SP6132

R257 10K

MU31

1

RT

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

ISL6522CB : SOIC

ISL6522CV : TSSOP

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

10

9

3

2

1

VCC

BST1

MVDDQ_UGATE

M<VDDQ_LGATE

MVDDQ_VCC

14

13

12

11

BOOT_VDDC1

10

9

8

MVDDC Switching Regulator for

Memory Core for 256M

configuration

BST2

SS_VDDC2

Fb_VDDC2

COMP_VDDC2

UVIN2

SWN2

Alternative 2

GPIO15(4)

BOOT_VDDC2

U32

DNI

7

BST

SS

GH

4

Vfb

5

GND

COMP

6

GL

UVIN

8

Vcc

SWN

SP6132

SIPEX SP6132

R307 10K

MU32

1

RT

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

ISL6522CB : SOIC

ISL6522CV : TSSOP

R909 0R

10

9

3

2

1

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

VCC

MVDDC_UGATE

MVDDC_LGATE

EXT_PWR#

BST2

MVDDC_VCC

14

13

12

11

10

9

8

7

C121 100nF

+12V_BUS

BOOT_VDDC2

C159

1uF

C113

1uF

SWN1

SWN2

GPIO8(4,14)

C122 100nF

+12V_BUS

EXTERNAL POWER DETECT

Q21

4 5

3

2

1

4 5

3

2

1

IRF7413A

Q22

IRF7413A

Fb_VDDC1

6

7

8

6

7

8

IRF7413ATR (2020005600)

C116

R255

1nF

2.2R

Q23

4 5

3

2

1

4 5

3

2

1

IRF7413A

Q24

IRF7413A

Fb_VDDC2

6

7

8

6

7

8

IRF7413ATR (2020005600)

R308

C160

2.2R

1nF

R874 0R

EXT_PWR#

DNI

6

+PW_VDDC1

C1680

C1678

C1679

10uF

100nF

L65

1.5uH

C110

1nf

R254

1.5K

C1683

100nF

L66

1.5uH

C161

1nf

Cc1 Cout1

R309

1.5K

Rc4

Q226

R1556 10K

1

CMPT3904

2 3

R1842

10K

10uF

***

Rc1

Cc1

R253

***

2K

1%

Rc4

Rc2

R256

1.24K

1%

+PW_VDDC2 UVIN2

C1681

C1682

10uF

10uF

***

Rc1

R310

***

1.87K

1%

Rc2

R311

1.24K

1%

+3.3V_BUS+3.3V_BUS +5V

R1841

10K

DNI

5

+12VEXT+12V_BUS

B21

B76

60R

60R

DNI

+MVDDQ

***

C106

C105

330uF_2.5V

330uF_2.5V

Cout1

***

+MVDDQ = REF * (1+Rc1/Rc2)

+12VEXT

+12V_BUS

B77

B28

60R

60R

DNI DNI

C165

330uF_2.5V

+MVDDC

330uF_2.5V

C164

***

***

+MVDDC = REF * (1+Rc1/Rc2)

J1

6P_HDER

+12V_1

+12V_2

+12V_3

GND_1

GND_2

Sense

Sense

R1867

10K

C104

330uF_2.5V

180uF_16V

R374

220K

C166

330uF_2.5V

1

2

3

4

6

5

DNI

C163

R377

63.4K

R375

100K

DNI

DNI

R1868 0R

1

C1957

1nF

2

R1869 0R

B81 220R

4

R378

100K

DNI

UVIN1

+MVDDC

R250

2K

R249

2.4K

1

Q9

CMPT3904

+12V_BUS

POWER SEQUENCING CIRCUIT:

R1849

1K

R1850

2.4K

D36

S3AB

1

Q228

CMPT3904

***

21

+12V_BUS

D37

S3AB

+VDDC

+12VEXT +12V_BUS

DNI

L84

61R

4

3

DNI

C1956

1nF

C1165

10uF_25V

Sense

C1166

10uF_25V

3

R248

20K

CMPT3904

2 3

R1848

20K

CMPT3904

2 3

21

<Variant Name>

DESIGN NOTES:POWER SEQUENCING CIRCUIT:

Add this Capacitor for SP6132

COMP_VDDC1

C140

DNI

SS_VDDC1

1

2 3

Q10

2.2nF

Compensation Circuit

COMP_VDDC1

Cc2

C112

10nF

Rc5

C111

33pF

R264

15K

Cc3

Fb_VDDC1

FOR ALTERNATE #2

Change C142 for 10uF

Change C122 for 1uF

Replace R251 with a bead

Swap Rc4 with Cc1

DESIGN NOTES:

Add this Capacitor for SP6132

SS_VDDC2

1

2 3

Q227

Compensation Circuit

Cc2

Cc4

COMP_VDDC2

C171

10nF

Rc5

C168

100pF

C170

33pF

R313

15K

COMP_VDDC2

DNI

Cc3

Fb_VDDC2

FOR ALTERNATE #2

Change C157 for 10 uF

D38

S3AB

21

Change C121 for 1 uF

Replace C764 by 0 Ohm resistor

Remove R954

Replace R314 with a bead

Swap Rc4 with Cc1

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

Date: Sheet

2

105-A474XX-10

823Thursday, November 11, 2004

1

2

of

Page 9

8

7

6

5

4

3

2

1

+1.8V Regulator for analog power supplies

C134

22uF_16V

+3.3V_BUS

B23

60R

C135

100nF

REG2

LT1117CST

IN3OUT

CASE

ADJ

1

+VDD_1.8V

2

4

R129

1.50K

1%

R126

681R

1%

C131

100nF

C132

22uF_16V

D D

+1.5V Regulator for VDDC_CT (VDD15)

+3.3V_BUS

C129

22uF_16V

C128

100nF

B22

60R

REG7

LT1117CST

IN3OUT

ADJ

1

CASE

+VDDC_CT

2

4

R128

1.0K

1%

R125

200R

1%

C127

100nF

C126

22uF_16V

Max 400 mA if all 1.8 V analog power supplies are connected

33R

+3.3V_BUS

C1618

22uF_16V

REGULATOR

FOR TPVDD

(+1.8V)

4

NC

1

NC

2

5 3

REG12

1

IN

REFEN4GND

RT9173ACL5

C975

1.0uF

REG6

SC431LC5SK-1

3

6

VOUT

TAB

VCNTL

+3.3V_BUS

B26 200R

R142

R144

681R

AS432S

1%

1

R146

MREG5

1.50K

3 2

1%

PCIE_VDDR

5

R1843

1K

402

***

C1705

22uF_16V

***

2

GND

VOUT

BYPASS

C1666

100nF

5

4

REG11

LT1117CST

IN3OUT

R1847

110R

REG10

LT1117CST

IN3OUT

REGULATOR

FOR

A2VDD(+2.5V)

+A2VDD

1uF

C146

C147

470pF

DNI

CASE

ADJ

1

CASE

ADJ

1

R1791

3.01K

1%

B25 200R

R139

R140

681R

AS432S

1%

1

MREG4

R141

DNI DNI DNI

1.50K

3 2

1%

+VDD_1.8V

PCIE_PVDD_18

2

4

R1792

1.50K

1%

R1793

681R

1%

+5V

2

4

R1790

1.00K

1%

C1667

100nF

C1664

22uF_16V

C1662

22uF_16V

+3.3V_BUS

B24

C C

200R

REG3

1

VIN

1uF

3

SHDN

C145

2.5V

2

GND_A2VSSN GND_A2VSSN

+1.8V Regulator for PCIE_PVDD_18

+3.3V_BUS

B70 50R

C1665

22uF_16V

B B

+12V_BUS

R1845

110R

C1663

1uF

R1846

110R

R1789

110R

+5V regulator

Vin = 12v

Vout = 5V

Iout =

A A

REGULATOR

FOR PVDD

(+1.8V)

+PVDD

33R

REG4

4

SC431LC5SK-1

NC

1

NC

2

5 3

GND_PVSS

Regulator for PCIE_VDDR

Vout = 1.2V

L83

60R

DNI

R1797

1.5K

R1799

2.4K

CMPT3904

+3.3V_BUS

Q216

1

PCIE_PVDD_18

R1795

20K

R1798 100R

2 3

+3.3V_BUS+3.3V_BUS

B27 200R

B66

BLM21A121SPT

1

3 2

32

AS432S

MREG6

R1781

1.0K

R1783

2K

Q215

2N7002LT1

1

+PVDD

R143

R145

681R

1%

R147

1.50K

1%

75R

C1655

22uF_6.3V

+MPVDD+TPVDD

4

1

2

REGULATOR

FOR

MPVDD(+1.8V)

REG5

NC

NC

5 3

GND_MPVSSGND_TPVSS

C1700

22uF_6.3V

SC431LC5SK-1

<Variant Name>

8

7

6

5

4

3

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

Date: Sheet

2

105-A474XX-10

923Thursday, November 11, 2004

of

1

2

Page 10

5

4

3

2

1

R423 MEMORY CHANNELS A and B

D D

MAA[13..0](12)

C C

+MVDDQ

B B

R137

40.2R

R138

100R

MAA[13..0]

MDA[63..0]

MDA[63..0](12)

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

C149

100nF

W38

V37

V38

U37

T39

T38

R37

R38

W33

V34

V36

V32

U36

T32

R36

R34

P37

P38

N37

N38

L38

K37

K38

J37

P34

P35

P36

M34

L35

J36

H35

H36

P30

P31

P32

P33

J33

K32

J32

J31

V28

V29

W31

T30

R31

R30

R29

T28

F36

F35

E35

D33

E32

D32

G31

D31

M28

L28

K28

M27

J27

J26

K26

H25

W29

W28

U1C

DQA_0

DQA_1

DQA_2

DQA_3

DQA_4

DQA_5

DQA_6

DQA_7

DQA_8

DQA_9

DQA_10

DQA_11

DQA_12

DQA_13

DQA_14

DQA_15

DQA_16

DQA_17

DQA_18

DQA_19

DQA_20

DQA_21

DQA_22

DQA_23

DQA_24

DQA_25

DQA_26

DQA_27

DQA_28

DQA_29

DQA_30

DQA_31

215RBKAGA11F

DQA_32

DQA_33

DQA_34

DQA_35

DQA_36

DQA_37

DQA_38

DQA_39

DQA_40

DQA_41

DQA_42

DQA_43

DQA_44

DQA_45

DQA_46

DQA_47

DQA_48

DQA_49

DQA_50

DQA_51

DQA_52

DQA_53

DQA_54

DQA_55

DQA_56

DQA_57

DQA_58

DQA_59

DQA_60

DQA_61

DQA_62

DQA_63

MVREFD_0

MVREFS_0

Part 3 of 10

Memory

Channel A

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

QSA_0B

QSA_1B

QSA_2B

QSA_3B

QSA_4B

QSA_5B

QSA_6B

QSA_7B

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

RASAb

CASAb

WEAb

CSAb_0

CSAb_1

CKEA

CLKA0

CLKA0b

CLKA1

CLKA1b

MAA0

B34

MAA1

B35

MAA2

A34

MAA3

B33

MAA4

J38

MAA5

H38

MAA6

G39

MAA7

H37

MAA8

F38

MAA9

G38

MAA10

A35

MAA11

B36

MAA12

A37

MAA13

E39

D38

DQMA#0

T37

DQMA#1

U35

DQMA#2

M37

DQMA#3

L34

DQMA#4

N32

DQMA#5

V30

DQMA#6

F32

DQMA#7

H27

QSA#0

U39

QSA#1

U32

QSA#2

M38

QSA#3

L36

QSA#4

M32

QSA#5

U31

QSA#6

F33

QSA#7

L27

QSA0

U38

QSA1

V33

QSA2

L37

QSA3

M36

QSA4

L32

QSA5

T31

QSA6

F34

QSA7

K27

RASA#

B37

CASA#

C37

WEA#

C39

CSA#0

D39

F37

CKEA

B38

D37

E37

C35

C36

DQMA#[7..0] (12)

QSA#[7..0] (12)

QSA[7..0] (12)

RASA# (12)

CASA# (12)

WEA# (12)

CSA#0 (12)

CKEA (12)

CLKA0 (12)

CLKA#0 (12)

CLKA1 (12)

CLKA#1 (12)

+MVDDQ

R158

40.2R

R159

100R

MAB[13..0](12)

MDB[63..0](12)

C151

100nF

MAB[13..0]

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

C33

B32

C32

B31

B29

C29

B28

C28

G30

H30

G29

F29

F27

E26

D27

F26

B27

C27

B26

C26

C24

B23

C23

B22

M24

L24

K24

M22

L21

M21

J20

K20

H24

F24

D24

G24

F21

F23

G21

H22

H21

H19

F20

E20

G18

H18

E17

D17

M19

K18

L18

M18

L15

M16

M15

K14

F15

G15

H16

H15

F12

G12

H13

H12

D30

E31

U1D

DQB_0

DQB_1

DQB_2

DQB_3

DQB_4

DQB_5

DQB_6

DQB_7

DQB_8

DQB_9

DQB_10

DQB_11

DQB_12

DQB_13

DQB_14

DQB_15

DQB_16

DQB_17

DQB_18

DQB_19

DQB_20

DQB_21

DQB_22

DQB_23

DQB_24

DQB_25

DQB_26

DQB_27

DQB_28

DQB_29

DQB_30

DQB_31

215RBKAGA11F

DQB_32

DQB_33

DQB_34

DQB_35

DQB_36

DQB_37

DQB_38

DQB_39

DQB_40

DQB_41

DQB_42

DQB_43

DQB_44

DQB_45

DQB_46

DQB_47

DQB_48

DQB_49

DQB_50

DQB_51

DQB_52

DQB_53

DQB_54

DQB_55

DQB_56

DQB_57

DQB_58

DQB_59

DQB_60

DQB_61

DQB_62

DQB_63

MVREFD_1

MVREFS_1

Part 4 of 10

Memory

Channel B

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

QSB_0B

QSB_1B

QSB_2B

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

RASBb

CASBb

WEBb

CSBb_0

CSBb_1

CKEB

CLKB0

CLKB0b

CLKB1

CLKB1b

MAB0

B12

MAB1

B13

MAB2

C13

MAB3

C12

MAB4

C22

MAB5

C21

MAB6

B20

MAB7

B21

MAB8

B19

MAB9

C20

MAB10

C14

MAB11

B14

MAB12

B15

MAB13

B18

C17

DQMB#0

C30

DQMB#1

G27

DQMB#2

B25

DQMB#3

K21

DQMB#4

E23

DQMB#5

D20

DQMB#6

K15

DQMB#7

D9

QSB#0

C31

QSB#1

D29

QSB#2

B24

QSB#3

K23

QSB#4

D21

QSB#5

F18

QSB#6

J17

QSB#7

D11

QSB0

B30

QSB1

E29

QSB2

C25

QSB3

J23

QSB4

D23

QSB5

D18

QSB6

K17

QSB7

E11

RASB#

C15

CASB#

C16

WEB#

B17

CSB#0

C18

C19

CKEB

B16

D15

D14

F14

E14

DQMB#[7..0] (12)

QSB#[7..0] (12)

QSB[7..0] (12)

RASB# (12)

CASB# (12)

WEB# (12)

CSB#0 (12)

CKEB (12)

CLKB0 (12)

CLKB#0 (12)

CLKB1 (12)

CLKB#1 (12)

+MVDDQ

R148

40.2R

R149

C148

100nF

100R

A A

5

4

3

+MVDDQ

R150

40.2R

R151

100R

C150

100nF

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

PCIe R480 GDDR3 256MB 8MX32 DVI-I DVI-I

Size Document Number Rev

C

2

Date: Sheet

105-A474XX-10

1

10 23Thursday, November 11, 2004

2

of

Page 11

5

4

3

2

1

R-420 MEMORY CHANNELS C and D

D D

C156

100nF

MAD[13..0]

MDD0

MDD1

MDD2

MDD3

MDD4

MDD5

MDD6

MDD7

MDD8

MDD9

MDD10

MDD11

MDD12

MDD13

MDD14

MDD15

MDD16

MDD17

MDD18

MDD19

MDD20

MDD21

MDD22

MDD23

MDD24

MDD25

MDD26

MDD27

MDD28

MDD29

MDD30

MDD31

MDD32

MDD33

MDD34

MDD35

MDD36

MDD37

MDD38

MDD39

MDD40

MDD41

MDD42

MDD43

MDD44

MDD45

MDD46

MDD47

MDD48

MDD49

MDD50

MDD51

MDD52

MDD53

MDD54

MDD55

MDD56

MDD57

MDD58

MDD59

MDD60

MDD61

MDD62

MDD63

AA12

AB10

AB11

AD12

AE12

AE11

AE10

AF10

AG12

AH11

AK10

AJ10

AK12

AJ13

AM12

AM13

AN13

AN12

AP11

AT10

AR10

AA2

AA3

AB2

AB3

AD3

AE2

AE3

AF2

AB8

AB6

AB7

AD8

AE6

AE7

AE4

AE8

AF3

AG2

AG3

AH2

AK2

AK3

AL2

AL3

AG8

AF6

AF5

AH8

AJ6

AJ5

AJ4

AK7

Y9

AF9

AN6

AP6

AP5

AR6

AU4

AU5

AU6

AU7

AT9

Y10

W10

U1F

DQD_0

DQD_1

DQD_2

DQD_3

DQD_4

DQD_5

DQD_6

DQD_7

DQD_8

DQD_9

DQD_10

DQD_11

DQD_12

DQD_13

DQD_14

DQD_15

DQD_16

DQD_17

DQD_18

DQD_19

DQD_20

DQD_21

DQD_22

DQD_23

DQD_24

DQD_25

DQD_26

DQD_27

DQD_28

DQD_29

DQD_30

DQD_31

215RBKAGA11F

DQD_32

DQD_33

DQD_34

DQD_35

DQD_36

DQD_37

DQD_38

DQD_39

DQD_40

DQD_41

DQD_42

DQD_43

DQD_44

DQD_45

DQD_46

DQD_47

DQD_48

DQD_49

DQD_50

DQD_51

DQD_52

DQD_53

DQD_54

DQD_55

DQD_56

DQD_57

DQD_58

DQD_59

DQD_60

DQD_61

DQD_62

DQD_63

MVREFD_3

MVREFS_3

Part 6 of 10

Memory

Channel D

MAD_0

MAD_1

MAD_2

MAD_3

MAD_4

MAD_5

MAD_6

MAD_7

MAD_8

MAD_9

MAD_10

MAD_11

MAD_12

MAD_13

MAD_14

DQMDb_0

DQMDb_1

DQMDb_2

DQMDb_3

DQMDb_4

DQMDb_5

DQMDb_6

DQMDb_7

QSD_0B

QSD_1B

QSD_2B

QSD_3B

QSD_4B

QSD_5B

QSD_6B

QSD_7B

QSD_0

QSD_1

QSD_2

QSD_3

QSD_4

QSD_5

QSD_6

QSD_7

RASDb

CASDb

WEDb

CSDb_0

CSDb_1

CKED

CLKD0

CLKD0b

CLKD1

CLKD1b

DRAM_RST

TEST_MCLK

TEST_YCLK

MEMTEST

AU8

AV6

AV7

AV8

AM2

AN2

AN3

AM3

AP3

AP2

AV5

AV4

AV3

AR3

AU2

AD2

AD4

AH3

AH4

AB12

AH13

AT5

AP13

AC2

AC5

AJ3

AH7

AC10

AL9

AT4

AP12

AC3

AC4

AJ2

AH6

AC9

AM9

AR4

AR11

AW3

AV2

AU1

AT2

AR2

AU3

AM4

AM5

AP4

AN4

B11

J12

K12

C11

MAD0

MAD1

MAD2

MAD3

MAD4

MAD5

MAD6

MAD7

MAD8

MAD9

MAD10

MAD11

MAD12

MAD13

DQMD#0

DQMD#1

DQMD#2

DQMD#3

DQMD#4

DQMD#5

DQMD#6

DQMD#7

QSD#0

QSD#1

QSD#2

QSD#3

QSD#4

QSD#5

QSD#6

QSD#7

QSD0

QSD1

QSD2

QSD3

QSD4

QSD5

QSD6

QSD7

RASD#

CASD#

WED#

CSD#0

CKED

RESET

TEST_MCLK

TEST_YCLK

R166

243R

R156

4.7K

DQMD#[7..0] (13)

QSD#[7..0] (13)

QSD[7..0] (13)

CLKD0 (13)

CLKD#0 (13)

CLKD1 (13)

CLKD#1 (13)

R157

4.7K

RASD# (13)

CASD# (13)

WED# (13)

CSD#0 (13)

CKED (13)

R163

4.7K

RESET (12,13)

DNI

+MVDDQ

+MVDDQ

R161

40.2R

R162

100R

R154

40.2R

R155

100R

MAD[13..0](13)

MDD[63..0](13)

C155

100nF

C154

100nF

C153

100nF

MAC[13..0]

MDC0

MDC1

MDC2

MDC3

MDC4

MDC5

MDC6

MDC7

MDC8

MDC9

MDC10

MDC11

MDC12

MDC13

MDC14

MDC15

MDC16

MDC17

MDC18

MDC19

MDC20

MDC21

MDC22

MDC23

MDC24

MDC25

MDC26

MDC27

MDC28

MDC29

MDC30

MDC31

MDC32

MDC33

MDC34

MDC35

MDC36

MDC37

MDC38

MDC39

MDC40

MDC41

MDC42

MDC43

MDC44

MDC45

MDC46

MDC47

MDC48

MDC49

MDC50

MDC51

MDC52

MDC53

MDC54

MDC55

MDC56

MDC57

MDC58

MDC59

MDC60

MDC61

MDC62

MDC63

B10

C10

B9

C9

C7

B6

C6

B5

D8

E8

D6

F6

E5

D4

C4

G4

A5

C5

A4

B4

C2

C3

D2

D3

K10

J9

J8

K9

K6

L6

M6

L5

N8

N7

M5

N6

T4

T8

T6

U4

N10

P10

P9

R12

U10

U9

V12

W12

R3

T2

T3

U2

W2

W3

Y2

Y3

V6

V8

W8

W4