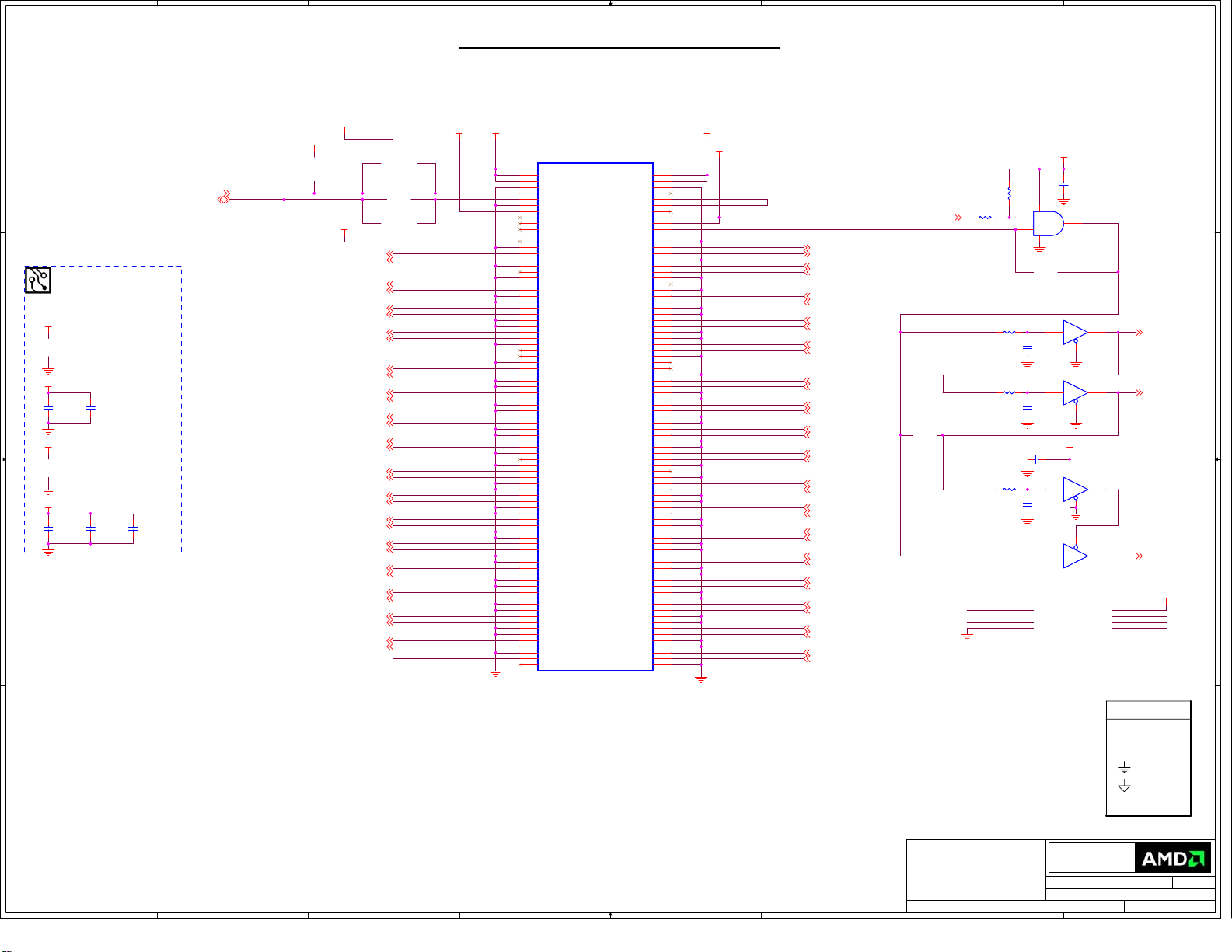

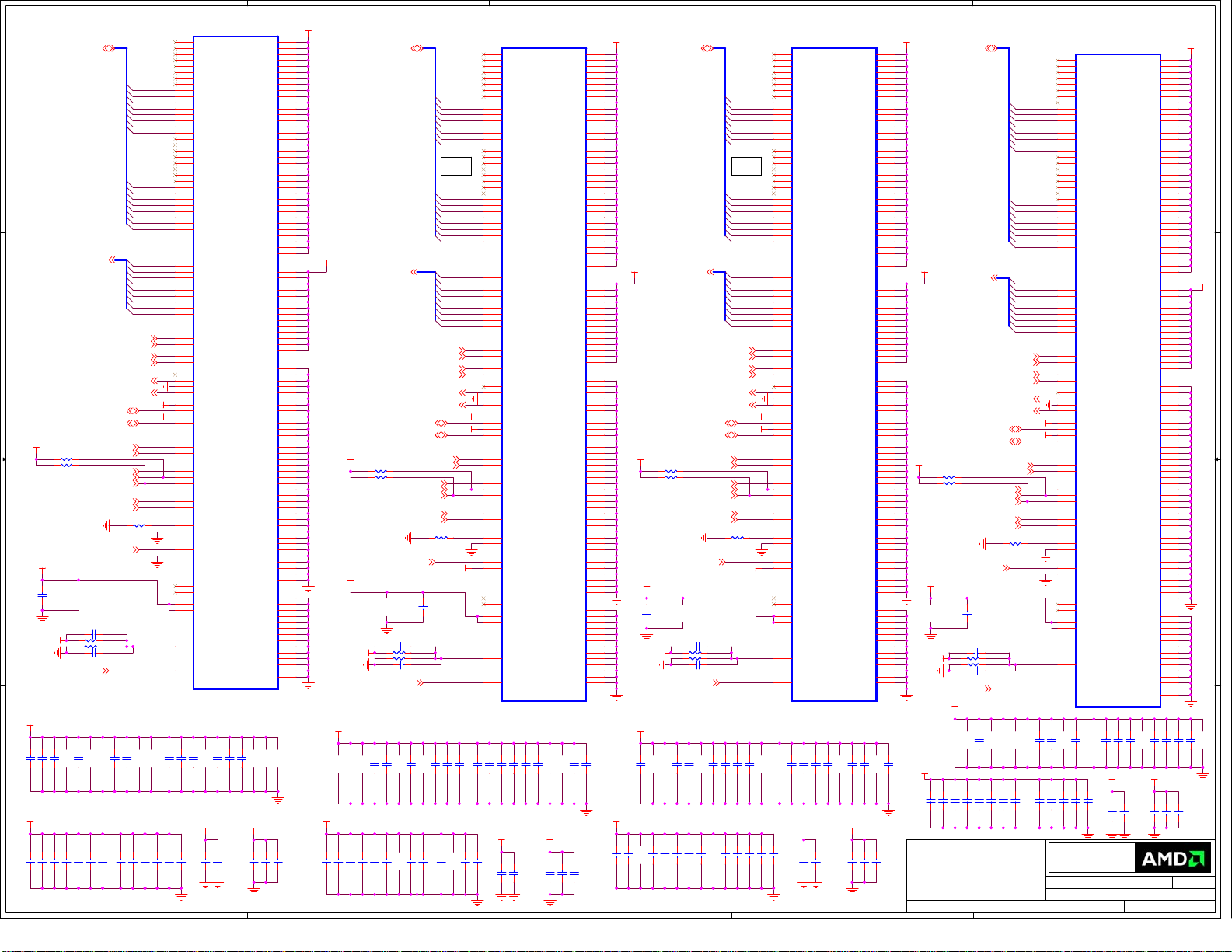

Page 1

8

7

6

5

4

3

2

1

C158

C158

100nF_6.3V

100nF_6.3V

4

PERST#_gated

DNI

U101C

U101C

74LCX125MTC

74LCX125MTC

10

U101B

U101B

74LCX125MTC

74LCX125MTC

4

14

U101A

U101A

74LCX125MTC

74LCX125MTC

1

7

PERST#_buf_delayed

13

U101D

U101D

74LCX125MTC

74LCX125MTC

C013

PERST#_gated

JTAG_TRSTB

JTAG_TRSTB p.19

PERST#_buf p.2,18

TESTEN p.19

+3.3V_BUS

PCI-EXPRESS EDGE CONNECTOR

D D

+3.3V_BUS

GPIO_4_SMBCLKp.6

GPIO_3_SMBDATAp.6

Place these caps as close to the PCIE

connector as possible

+12V_BUS

C C

CAP CER 10UF 20% 16V X5R

(1206)1.8MM H MAX

+12V_BUS

C152

C152

C151

C151

150nF_16V

150nF_16V

150nF_16V

150nF_16V

+3.3V_BUS

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

+3.3V_BUS

C155

C155

C156

1uF_6.3V

1uF_6.3V

C156

10nF

10nF

C154

C154

100nF_6.3V

100nF_6.3V

B B

+3.3V_BUS

DNIDNI

+3.3V_BUS

+3.3V_BUS

PETn0_GFXRn0p.2

PETp1_GFXRp1p.2

PETn1_GFXRn1p.2

PETp2_GFXRp2p.2

PETn2_GFXRn2p.2

PETp3_GFXRp3p.2

PETn3_GFXRn3p.2

PETp4_GFXRp4p.2

PETn4_GFXRn4p.2

PETp5_GFXRp5p.2

PETn5_GFXRn5p.2

PETp6_GFXRp6p.2

PETn6_GFXRn6p.2

PETp7_GFXRp7p.2

PETn7_GFXRn7p.2

PETp8_GFXRp8p.2

PETn8_GFXRn8p.2

PETp9_GFXRp9p.2

PETn9_GFXRn9p.2

PETp10_GFXRp10p.2

PETn10_GFXRn10p.2

PETp11_GFXRp11p.2

PETn11_GFXRn11p.2

PETp12_GFXRp12p.2

PETn12_GFXRn12p.2

PETp13_GFXRp13p.2

PETn13_GFXRn13p.2

PETp14_GFXRp14p.2

PETn14_GFXRn14p.2

PETp15_GFXRp15p.2

PETn15_GFXRn15p.2

DNI

DNI

PRESENCE

+3.3V_BUS

SMCLK

+12V_BUS

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

+12V#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

x16 PCIe

x16 PCIe

Mechanical Key

Mechanical Key

MPCIE100

MPCIE100

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PRESENCE

+12V_BUS

+3.3V_BUS

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

JTDIO_LOOPSMDAT

PERST#

SystemJTAGTDIandTDOarehardwired.

seep.20forGPUJTAGconnection

PCIE_REFCLKP p.2

PCIE_REFCLKN p.2PETp0_GFXRp0p.2

PERp0 p.2

PERn0 p.2

PERp1 p.2

PERn1 p.2

PERp2 p.2

PERn2 p.2

PERp3 p.2

PERn3 p.2

PERp4 p.2

PERn4 p.2

PERp5 p.2

PERn5 p.2

PERp6 p.2

PERn6 p.2

PERp7 p.2

PERn7 p.2

PERp8 p.2

PERn8 p.2

PERp9 p.2

PERn9 p.2

PERp10 p.2

PERn10 p.2

PERp11 p.2

PERn11 p.2

PERp12 p.2

PERn12 p.2

PERp13 p.2

PERn13 p.2

PERp14 p.2

PERn14 p.2

PERp15 p.2

PERn15 p.2

PCIe RESET Buffered

+3.3V_BUS

R102

R102

10K

10K

53

1

NC7SZ08P5X_NL

1V_LDO_POKp.6,15,18

R103 0RR103 0R

Place R104 in U100

PERST#_gated

R110 7.5KR110 7.5K

JTAG_TRSTB

R111 7.5KR111 7.5K

DNI

PERST#_buf

R112 7.5KR112 7.5K

PERST#_gated

1V_LDO_POK

PERST#_buf TESTEN

2

9 8

C160

C160

100pF_50V

100pF_50V

5 6

C161

C161

100pF_50V

100pF_50V

C159 100nF_6.3VC159 100nF_6.3V

2 3

C162

C162

100pF_50V

100pF_50V

12 11

NC7SZ08P5X_NL

U100

U100

+3.3V_BUS

SYMBOL LEGEND

DO NOT

DNI

INSTALL

ACTIVE

#

LOW

DIGITAL

GROUND

ANALOG

GROUND

of

of

of

BUO BRING UP

ONLY

Doc No.

Doc No.

Doc No.

102-C01301-00

102-C01301-00

102-C01301-00

1

RevDate:

RevDate:

RevDate:

50

50

50

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

8

7

6

5

4

3

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Tuesday, November 10, 2009

Tuesday, November 10, 2009

Tuesday, November 10, 2009

Sheet

Sheet

Sheet

121

121

121

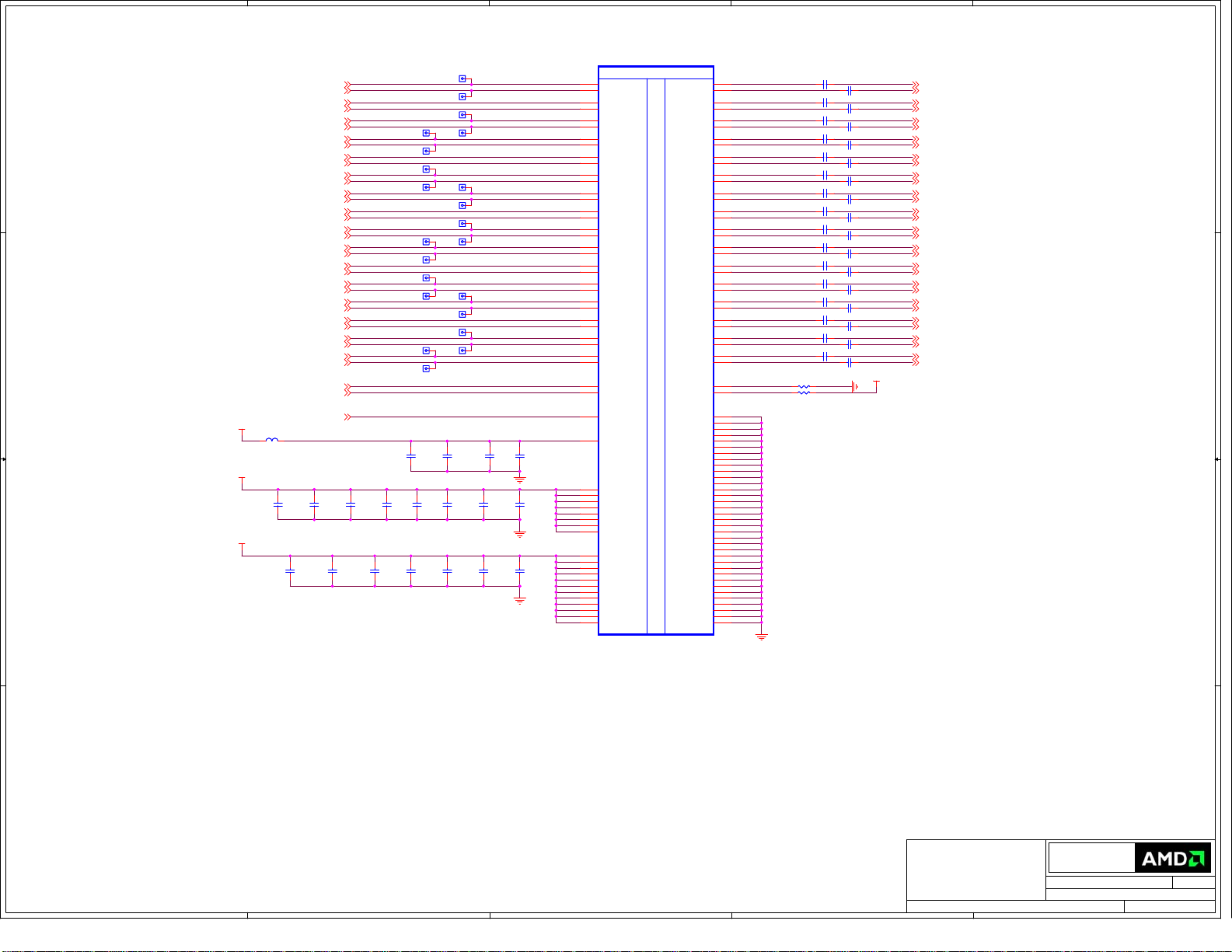

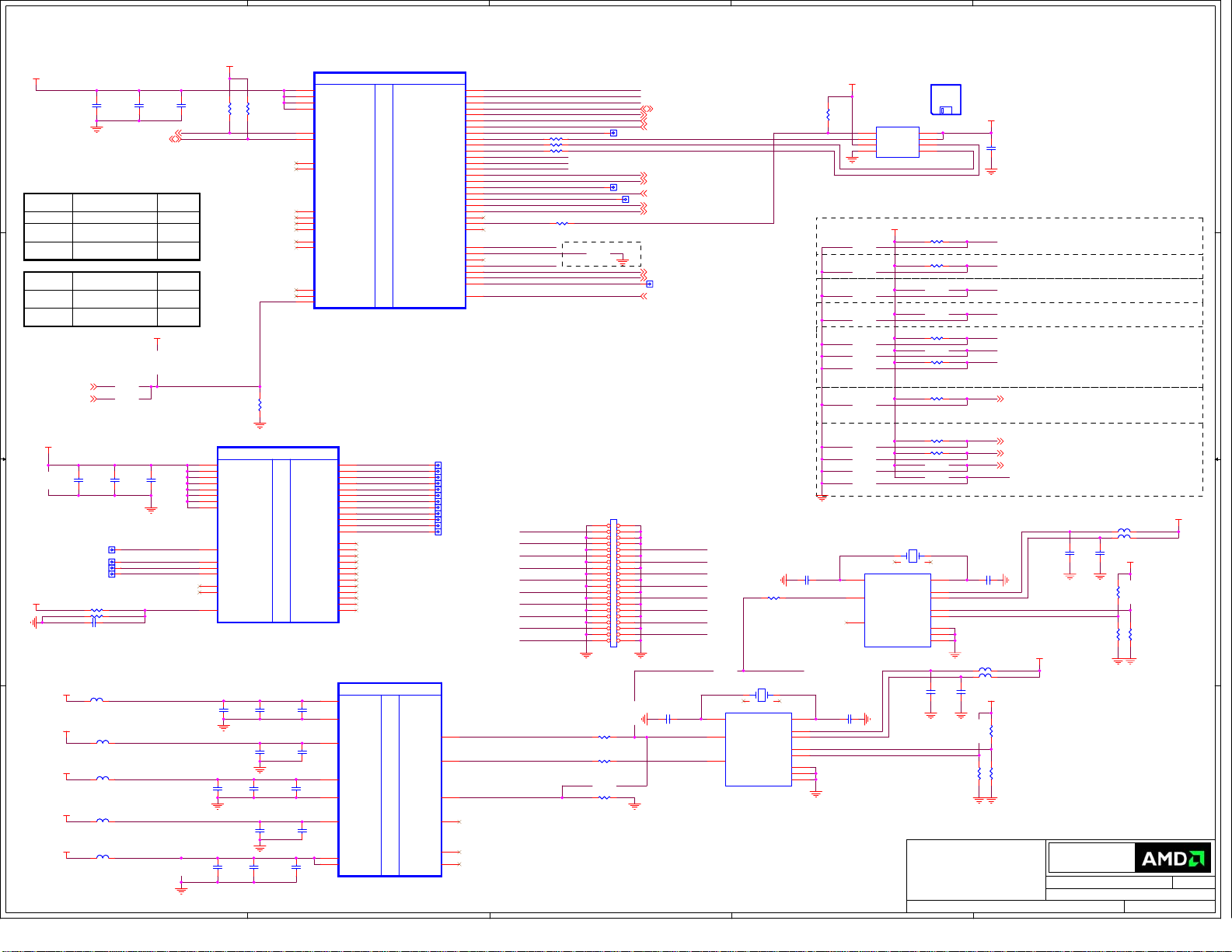

Page 2

5

4

3

2

1

(2) JUNIPER PCIe Interface

NOTE:SomeofthePCIEtestpointswill

beavailablethroughviasontraces.

C137

C137

TP105TP105

TP106TP106

TP107TP107

TP108TP108

TP113TP113

TP114TP114

TP115TP115

TP116TP116

TP121TP121

TP122TP122

C133

C133

1uF_6.3V

1uF_6.3V

C138

C138

1uF_6.3V

1uF_6.3V

C145

C145

1uF_6.3V

1uF_6.3V

TP101TP101

TP102TP102

TP103TP103

TP104TP104

TP109TP109

TP110TP110

TP111TP111

TP112TP112

TP117TP117

TP118TP118

TP119TP119

TP120TP120

100nF_6.3V

100nF_6.3V

C134

C134

100nF_6.3V

100nF_6.3V

C139

C139

C146

C146

1uF_6.3V

1uF_6.3V

C135

C135

10nF

10nF

C140

C140

100nF_6.3V

100nF_6.3V

C147

C147

1uF_6.3V

1uF_6.3V

PETp0_GFXRp0p.1

PETn0_GFXRn0p.1

PETp1_GFXRp1p.1

PETn1_GFXRn1p.1

D D

C C

+1.8V

+1.8V

+1V

B B

PETp2_GFXRp2p.1

PETn2_GFXRn2p.1

PETp3_GFXRp3p.1

PETn3_GFXRn3p.1

PETp4_GFXRp4p.1

PETn4_GFXRn4p.1

PETp5_GFXRp5p.1

PETn5_GFXRn5p.1

PETp6_GFXRp6p.1

PETn6_GFXRn6p.1

PETp7_GFXRp7p.1

PETn7_GFXRn7p.1

PETp8_GFXRp8p.1

PETn8_GFXRn8p.1

PETp9_GFXRp9p.1

PETn9_GFXRn9p.1

PETp10_GFXRp10p.1

PETn10_GFXRn10p.1

PETp11_GFXRp11p.1

PETn11_GFXRn11p.1

PETp12_GFXRp12p.1

PETn12_GFXRn12p.1

PETp13_GFXRp13p.1

PETn13_GFXRn13p.1

PETp14_GFXRp14p.1

PETn14_GFXRn14p.1

PETp15_GFXRp15p.1

PETn15_GFXRn15p.1

PCIE_REFCLKPp.1

PCIE_REFCLKNp.1

B100 BLM15AG121SN1DB100 BLM15AG121SN1D

C141

C141

4.7uF_6.3V

4.7uF_6.3V

1uF_6.3V

1uF_6.3V

C148

C148

10uF

10uF

C142

C142

PERST#_bufp.1,18

C149

C149

1uF_6.3V

1uF_6.3V

C143

C143

1uF_6.3V

1uF_6.3V

+PCIE_PVDD

1uF_6.3V

1uF_6.3V

C150

C150

1uF_6.3V

1uF_6.3V

C136

C136

C132

C132

10uF

10uF

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C144

C144

U1B

U1B

PART 2 OF 15

AA38

AB35

AA36

AA30

AB37

AA31

AA32

AA33

AA34

Y37

Y35

W36

W38

V37

V35

U36

U38

T37

T35

R36

R38

P37

P35

N36

N38

M37

M35

L36

L38

K37

K35

J36

J38

H37

H35

G36

G38

F37

F35

E37

V28

W29

W30

Y31

G30

G31

H29

H30

J29

J30

L28

M28

N28

R28

T28

U28

PART 2 OF 15

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCIE_REFCLKP

PCIE_REFCLKN

PERSTB

PCIE_PVDD

PCIE_VDDR#1

PCIE_VDDR#2

PCIE_VDDR#3

PCIE_VDDR#4

PCIE_VDDR#5

PCIE_VDDR#6

PCIE_VDDR#7

PCIE_VDDR#8

PCIE_VDDC#1

PCIE_VDDC#2

PCIE_VDDC#3

PCIE_VDDC#4

PCIE_VDDC#5

PCIE_VDDC#6

PCIE_VDDC#7

PCIE_VDDC#8

PCIE_VDDC#9

PCIE_VDDC#10

PCIE_VDDC#11

PCIE_VDDC#12

JUNIPER XT A12 HF MVD SLT BIN1 TSMC FB12

JUNIPER XT A12 HF MVD SLT BIN1 TSMC FB12

P

P

C

C

I

I

E

E

X

X

P

P

R

R

E

E

S

S

S

S

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

PCIE_CALRP

PCIE_CALRN

PCIE_VSS#1

PCIE_VSS#2

PCIE_VSS#3

PCIE_VSS#4

PCIE_VSS#5

PCIE_VSS#6

PCIE_VSS#7

PCIE_VSS#8

PCIE_VSS#9

PCIE_VSS#10

PCIE_VSS#11

PCIE_VSS#12

PCIE_VSS#13

PCIE_VSS#14

PCIE_VSS#15

PCIE_VSS#16

PCIE_VSS#17

PCIE_VSS#18

PCIE_VSS#19

PCIE_VSS#20

PCIE_VSS#21

PCIE_VSS#22

PCIE_VSS#23

PCIE_VSS#24

PCIE_VSS#25

PCIE_VSS#26

PCIE_VSS#27

PCIE_VSS#28

PCIE_VSS#29

PCIE_VSS#30

PCIE_VSS#31

PCIE_VSS#32

PCIE_VSS#33

PCIE_VSS#34

PCIE_VSS#35

Y33

Y32

W33

W32

U33

U32

U30

U29

T33

T32

T30

T29

P33

P32

P30

P29

N33

N32

N30

N29

L33

L32

L30

L29

K33

K32

J33

J32

K30

K29

H33

H32

Y30

Y29

AB39

E39

F34

F39

G33

G34

H31

H34

H39

J31

J34

K31

K34

K39

L31

L34

M34

M39

N31

N34

P31

P34

P39

R34

T31

T34

T39

U31

U34

V34

V39

W31

W34

Y34

Y39

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

PCIE_CALRP

PCIE_CALRN

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

100nF_6.3V

C100

C100

100nF_6.3V

100nF_6.3V

C102

C102

R1001.27K R1001.27K

R1012.0K R1012.0K

C104

C104

C106

C106

C108

C108

C111

C111

C112

C112

C114

C114

C116

C116

C118

C118

C120

C120

C122

C122

C124

C124

C126

C126

C128

C128

C130

C130

C101

C101

C103

C103

100nF_6.3V

100nF_6.3V

C105

C105

100nF_6.3V

100nF_6.3V

C107

C107

100nF_6.3V

100nF_6.3V

C110

C110

100nF_6.3V

100nF_6.3V

C109

C109

100nF_6.3V

100nF_6.3V

C113

C113

100nF_6.3V

100nF_6.3V

C115

C115

100nF_6.3V

100nF_6.3V

C117

C117

100nF_6.3V

100nF_6.3V

C119

C119

100nF_6.3V

100nF_6.3V

C121

C121

100nF_6.3V

100nF_6.3V

C123

C123

100nF_6.3V

100nF_6.3V

C125

C125

100nF_6.3V

100nF_6.3V

C127

C127

100nF_6.3V

100nF_6.3V

C129

C129

100nF_6.3V

100nF_6.3V

C131

C131

100nF_6.3V

100nF_6.3V

+1V

PERp0 p.1

PERn0 p.1

PERp1 p.1

PERn1 p.1

PERp2 p.1

PERn2 p.1

PERp3 p.1

PERn3 p.1

PERp4 p.1

PERn4 p.1

PERp5 p.1

PERn5 p.1

PERp6 p.1

PERn6 p.1

PERp7 p.1

PERn7 p.1

PERp8 p.1

PERn8 p.1

PERp9 p.1

PERn9 p.1

PERp10 p.1

PERn10 p.1

PERp11 p.1

PERn11 p.1

PERp12 p.1

PERn12 p.1

PERp13 p.1

PERn13 p.1

PERp14 p.1

PERn14 p.1

PERp15 p.1

PERn15 p.1

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

5

4

3

2

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Tuesday, November 10, 2009

Tuesday, November 10, 2009

Tuesday, November 10, 2009

Sheet

Sheet

Sheet

of

221

of

221

of

221

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

50

50

50

102-C01301-00

102-C01301-00

102-C01301-00

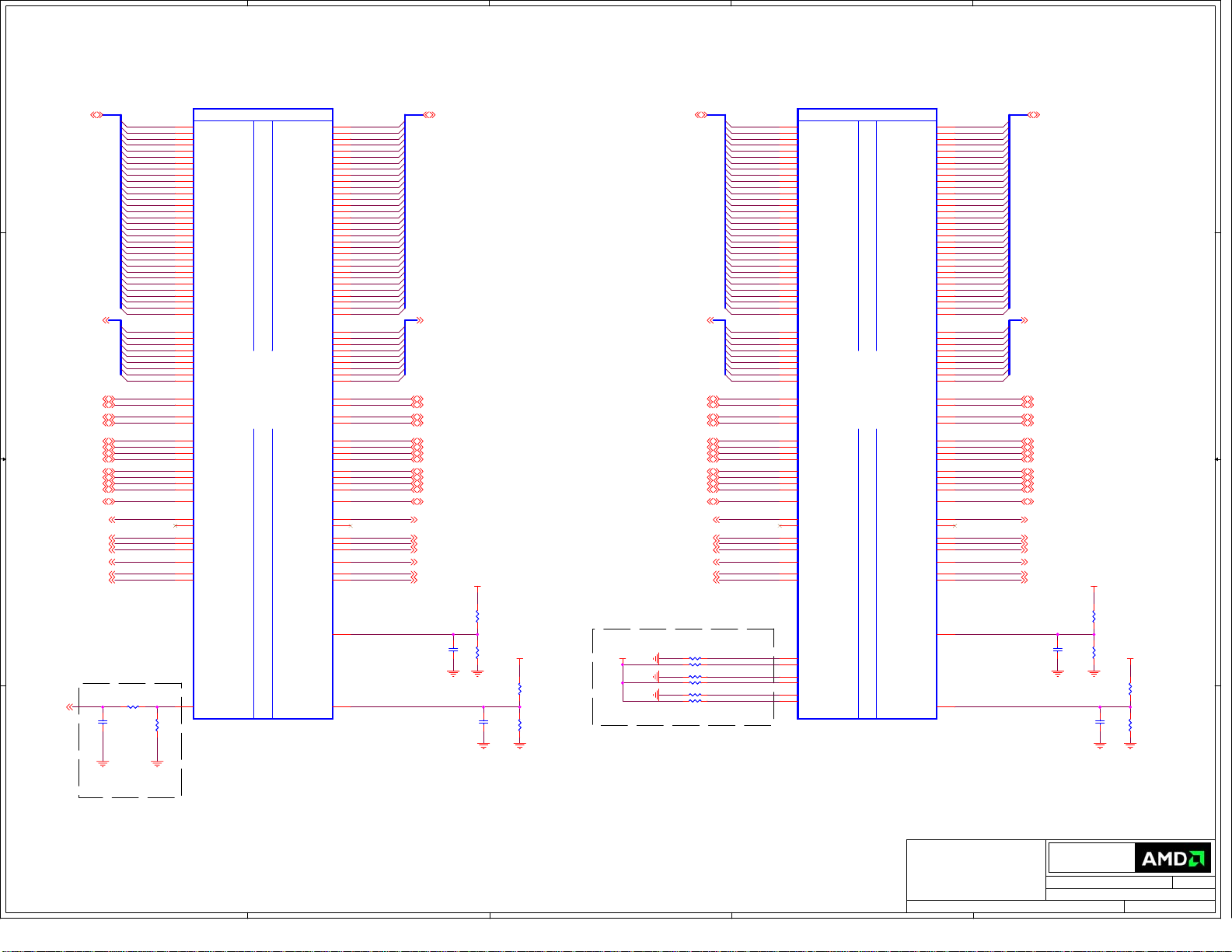

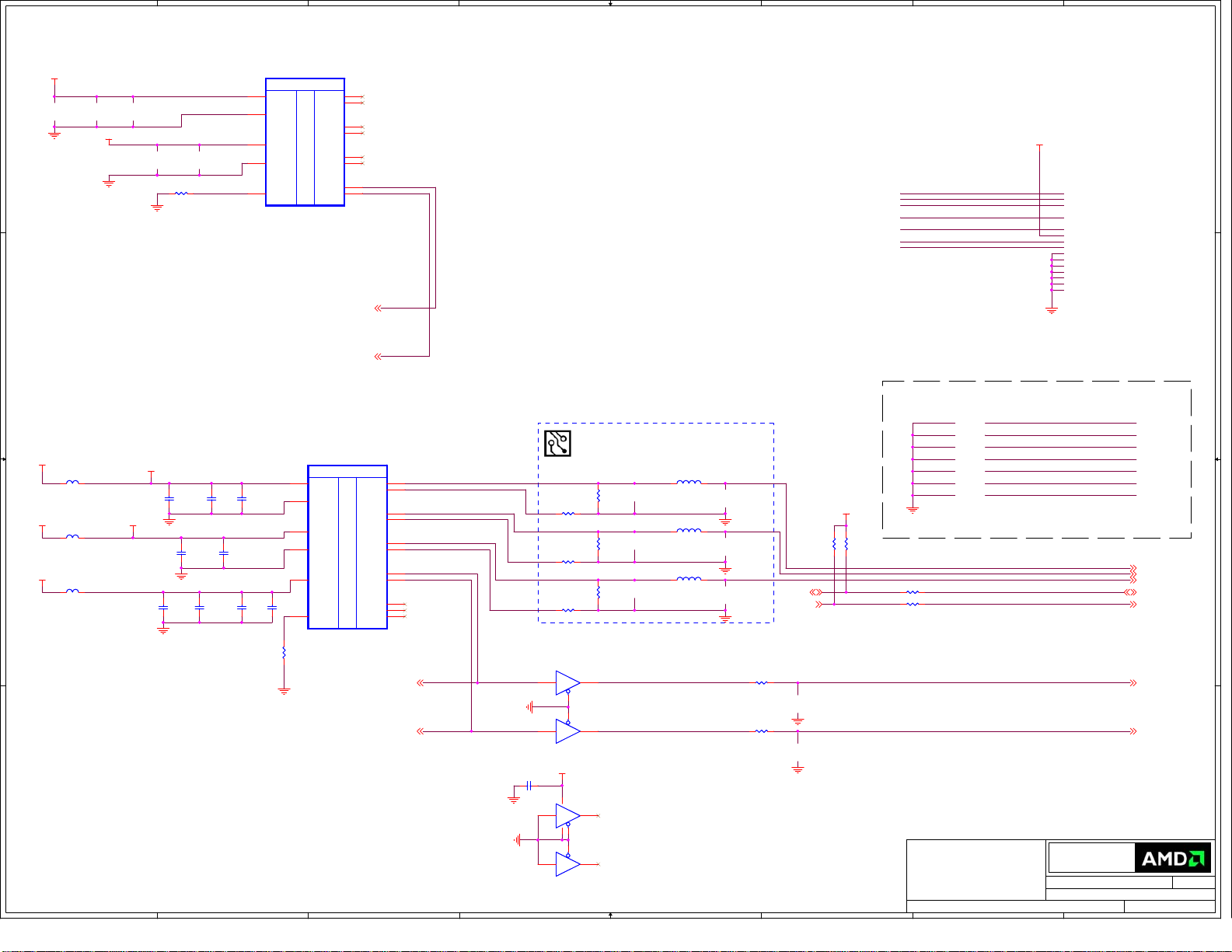

Page 3

5

4

3

2

1

(3) JUNIPER MEM Interface Ch A&B

U1C

U1C

D D

MAA0_[8..0]p.4

C C

WCKA0_0p.4

WCKA0b_0p.4

WCKA0_1p.4

WCKA0b_1p.4

EDCA0_0p.4

EDCA0_1p.4

EDCA0_2p.4

EDCA0_3p.4

DDBIA0_0p.4

DDBIA0_1p.4

DDBIA0_2p.4

DDBIA0_3p.4

ADBIA0p.4

B B

DQA0_0

DQA0_1

DQA0_2

DQA0_3

DQA0_4

DQA0_5

DQA0_6

DQA0_7

DQA0_8

DQA0_9

DQA0_10

DQA0_11

DQA0_12

DQA0_13

DQA0_14

DQA0_15

DQA0_16

DQA0_17

DQA0_18

DQA0_19

DQA0_20

DQA0_21

DQA0_22

DQA0_23

DQA0_24

DQA0_25

DQA0_26

DQA0_27

DQA0_28

DQA0_29

DQA0_30

DQA0_31

MAA0_0

MAA0_1

MAA0_2

MAA0_3

MAA0_4

MAA0_5

MAA0_6

MAA0_7

MAA0_8

CSA0b_0p.4

CASA0bp.4

RASA0bp.4

WEA0bp.4

CKEA0p.4

CLKA0p.4

CLKA0bp.4

C37

DQA0_0

C35

DQA0_1

A35

DQA0_2

E34

DQA0_3

G32

DQA0_4

D33

DQA0_5

F32

DQA0_6

E32

DQA0_7

D31

DQA0_8

F30

DQA0_9

C30

DQA0_10

A30

DQA0_11

F28

DQA0_12

C28

DQA0_13

A28

DQA0_14

E28

DQA0_15

D27

DQA0_16

F26

DQA0_17

C26

DQA0_18

A26

DQA0_19

F24

DQA0_20

C24

DQA0_21

A24

DQA0_22

E24

DQA0_23

C22

DQA0_24

A22

DQA0_25

F22

DQA0_26

D21

DQA0_27

A20

DQA0_28

F20

DQA0_29

D19

DQA0_30

E18

DQA0_31

G24

MAA0_0

J23

MAA0_1

H24

MAA0_2

J24

MAA0_3

H26

MAA0_4

J26

MAA0_5

H21

MAA0_6

G21

MAA0_7

H23

MAA0_8

A32

WCKA0_0

C32

WCKA0B_0

D23

WCKA0_1

E22

WCKA0B_1

C34

EDCA0_0

D29

EDCA0_1

D25

EDCA0_2

E20

EDCA0_3

A34

DDBIA0_0

E30

DDBIA0_1

E26

DDBIA0_2

C20

DDBIA0_3

J21

ADBIA0

K24

CSA0B_0

K27

CSA0B_1

K20

CASA0B

K23

RASA0B

K26

WEA0B

K21

CKEA0

H27

CLKA0

G27

CLKA0B

PART 3 OF 15

PART 3 OF 15

M

M

E

E

M

M

O

O

R

R

Y

Y

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

B

B

A

A

N

N

K

K

A

A

DQA1_0

DQA1_1

DQA1_2

DQA1_3

DQA1_4

DQA1_5

DQA1_6

DQA1_7

DQA1_8

DQA1_9

DQA1_10

DQA1_11

DQA1_12

DQA1_13

DQA1_14

DQA1_15

DQA1_16

DQA1_17

DQA1_18

DQA1_19

DQA1_20

DQA1_21

DQA1_22

DQA1_23

DQA1_24

DQA1_25

DQA1_26

DQA1_27

DQA1_28

DQA1_29

DQA1_30

DQA1_31

MAA1_0

MAA1_1

MAA1_2

MAA1_3

MAA1_4

MAA1_5

MAA1_6

MAA1_7

MAA1_8

WCKA1_0

WCKA1B_0

WCKA1_1

WCKA1B_1

EDCA1_0

EDCA1_1

EDCA1_2

EDCA1_3

DDBIA1_0

DDBIA1_1

DDBIA1_2

DDBIA1_3

ADBIA1

CSA1B_0

CSA1B_1

CASA1B

RASA1B

WEA1B

CKEA1

CLKA1

CLKA1B

C18

DQA1_0

A18

DQA1_1

F18

DQA1_2

D17

DQA1_3

A16

DQA1_4

F16

DQA1_5

D15

DQA1_6

E14

DQA1_7

F14

DQA1_8

D13

DQA1_9

F12

DQA1_10

A12

DQA1_11

D11

DQA1_12

F10

DQA1_13

A10

DQA1_14

C10

DQA1_15

G13

DQA1_16

H13

DQA1_17

J13

DQA1_18

H11

DQA1_19

G10

DQA1_20

G8

DQA1_21

K9

DQA1_22

K10

DQA1_23

G9

DQA1_24

A8

DQA1_25

C8

DQA1_26

E8

DQA1_27

A6

DQA1_28

C6

DQA1_29

E6

DQA1_30

A5

DQA1_31

H19

MAA1_0

H20

MAA1_1

L13

MAA1_2

G16

MAA1_3

J16

MAA1_4

H16

MAA1_5

J17

MAA1_6

H17

MAA1_7

J19

MAA1_8

C14

A14

E10

D9

E16

E12

J10

D7

C16

C12

J11

F8

G19

M13

K16

K17

K19

L15

J20

J14

H14

DQA1_[31..0] p.4DQA0_[31..0]p.4 DQB0_[31..0]p.5 DQB1_[31..0] p.5

MAA1_[8..0] p.4

WCKA1_0 p.4

WCKA1b_0 p.4

WCKA1_1 p.4

WCKA1b_1 p.4

EDCA1_0 p.4

EDCA1_1 p.4

EDCA1_2 p.4

EDCA1_3 p.4

DDBIA1_0 p.4

DDBIA1_1 p.4

DDBIA1_2 p.4

DDBIA1_3 p.4

ADBIA1 p.4

CSA1b_0 p.4

CASA1b p.4

RASA1b p.4

WEA1b p.4

CKEA1 p.4

CLKA1 p.4

CLKA1b p.4

+MVDD

MAB0_[8..0]p.5

WCKB0_0p.5

WCKB0b_0p.5

WCKB0_1p.5

WCKB0b_1p.5

EDCB0_0p.5

EDCB0_1p.5

EDCB0_2p.5

EDCB0_3p.5

DDBIB0_0p.5

DDBIB0_1p.5

DDBIB0_2p.5

DDBIB0_3p.5

ADBIB0p.5

DQB0_0

DQB0_1

DQB0_2

DQB0_3

DQB0_4

DQB0_5

DQB0_6

DQB0_7

DQB0_8

DQB0_9

DQB0_10

DQB0_11

DQB0_12

DQB0_13

DQB0_14

DQB0_15

DQB0_16

DQB0_17

DQB0_18

DQB0_19

DQB0_20

DQB0_21

DQB0_22

DQB0_23

DQB0_24

DQB0_25

DQB0_26

DQB0_27

DQB0_28

DQB0_29

DQB0_30

DQB0_31

MAB0_0

MAB0_1

MAB0_2

MAB0_3

MAB0_4

MAB0_5

MAB0_6

MAB0_7

MAB0_8

CSB0b_0p.5

CASB0bp.5

RASB0bp.5

WEB0bp.5

CKEB0p.5

CLKB0p.5

CLKB0bp.5

U1D

U1D

C5

DQB0_0

C3

DQB0_1

E3

DQB0_2

E1

DQB0_3

F1

DQB0_4

F3

DQB0_5

F5

DQB0_6

G4

DQB0_7

H5

DQB0_8

H6

DQB0_9

J4

DQB0_10

K6

DQB0_11

K5

DQB0_12

L4

DQB0_13

M6

DQB0_14

M1

DQB0_15

M3

DQB0_16

M5

DQB0_17

N4

DQB0_18

P6

DQB0_19

P5

DQB0_20

R4

DQB0_21

T6

DQB0_22

T1

DQB0_23

U4

DQB0_24

V6

DQB0_25

V1

DQB0_26

V3

DQB0_27

Y6

DQB0_28

Y1

DQB0_29

Y3

DQB0_30

Y5

DQB0_31

P8

MAB0_0

T9

MAB0_1

P9

MAB0_2

N7

MAB0_3

N8

MAB0_4

N9

MAB0_5

U9

MAB0_6

U8

MAB0_7

T8

MAB0_8

H3

WCKB0_0

H1

WCKB0B_0

T3

WCKB0_1

T5

WCKB0B_1

F6

EDCB0_0

K3

EDCB0_1

P3

EDCB0_2

V5

EDCB0_3

G7

DDBIB0_0

K1

DDBIB0_1

P1

DDBIB0_2

W4

DDBIB0_3

T7

ADBIB0

P10

CSB0B_0

L10

CSB0B_1

W10

CASB0B

T10

RASB0B

N10

WEB0B

U10

CKEB0

L9

CLKB0

L8

CLKB0B

PART 4 OF 15

PART 4 OF 15

M

M

E

E

M

M

O

O

R

R

Y

Y

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

B

B

A

A

N

N

K

K

B

B

DQB1_0

DQB1_1

DQB1_2

DQB1_3

DQB1_4

DQB1_5

DQB1_6

DQB1_7

DQB1_8

DQB1_9

DQB1_10

DQB1_11

DQB1_12

DQB1_13

DQB1_14

DQB1_15

DQB1_16

DQB1_17

DQB1_18

DQB1_19

DQB1_20

DQB1_21

DQB1_22

DQB1_23

DQB1_24

DQB1_25

DQB1_26

DQB1_27

DQB1_28

DQB1_29

DQB1_30

DQB1_31

MAB1_0

MAB1_1

MAB1_2

MAB1_3

MAB1_4

MAB1_5

MAB1_6

MAB1_7

MAB1_8

WCKB1_0

WCKB1B_0

WCKB1_1

WCKB1B_1

EDCB1_0

EDCB1_1

EDCB1_2

EDCB1_3

DDBIB1_0

DDBIB1_1

DDBIB1_2

DDBIB1_3

ADBIB1

CSB1B_0

CSB1B_1

CASB1B

RASB1B

WEB1B

CKEB1

CLKB1

CLKB1B

AA4

AB6

AB1

AB3

AD6

AD1

AD3

AD5

AF1

AF3

AF6

AG4

AH5

AH6

AJ4

AK3

AF8

AF9

AG8

AG7

AK9

AL7

AM8

AM7

AK1

AL4

AM6

AM1

AN4

AP3

AP1

AP5

Y9

W9

AC8

AC9

AA7

AA8

Y8

AA9

W8

AE4

AF5

AK6

AK5

AB5

AH1

AJ9

AM5

AC4

AH3

AJ8

AM3

W7

AD10

AC10

AA10

Y10

AB11

AA11

AD8

AD7

DQB1_0

DQB1_1

DQB1_2

DQB1_3

DQB1_4

DQB1_5

DQB1_6

DQB1_7

DQB1_8

DQB1_9

DQB1_10

DQB1_11

DQB1_12

DQB1_13

DQB1_14

DQB1_15

DQB1_16

DQB1_17

DQB1_18

DQB1_19

DQB1_20

DQB1_21

DQB1_22

DQB1_23

DQB1_24

DQB1_25

DQB1_26

DQB1_27

DQB1_28

DQB1_29

DQB1_30

DQB1_31

MAB1_0

MAB1_1

MAB1_2

MAB1_3

MAB1_4

MAB1_5

MAB1_6

MAB1_7

MAB1_8

MAB1_[8..0] p.5

WCKB1_0 p.5

WCKB1b_0 p.5

WCKB1_1 p.5

WCKB1b_1 p.5

EDCB1_0 p.5

EDCB1_1 p.5

EDCB1_2 p.5

EDCB1_3 p.5

DDBIB1_0 p.5

DDBIB1_1 p.5

DDBIB1_2 p.5

DDBIB1_3 p.5

ADBIB1 p.5

CSB1b_0 p.5

CASB1b p.5

RASB1b p.5

WEB1b p.5

CKEB1 p.5

CLKB1 p.5

CLKB1b p.5

+MVDD

R3605

R3605

40.2R

40.2R

C3603

C3603

1uF_6.3V

1uF_6.3V

1%

R3608

R3608

100R

100R

1%

C3606

C3606

1uF_6.3V

1uF_6.3V

+MVDD +MVDD

R3609

R3609

40.2R

40.2R

1%

R3611

R3611

100R

100R

1%

R3603243R R3603243R

R3604243R R3604243R

R3601243R R3601243R

R3602243R R3602243R

R3613243R R3613243R

R3614243R R3614243R

NOTFORPRODUCTION‐FORBACKUPONLY;

3

MEM_CALRP0

MEM_CALRN0

MEM_CALRP1

MEM_CALRN1

MEM_CALRP2

MEM_CALRN2

M27

MEM_CALRP0

L27

MEM_CALRN0

M12

MEM_CALRP1

N12

MEM_CALRN1

AH12

MEM_CALRP2

AG12

MEM_CALRN2

JUNIPER XT A12 HF MVD SLT BIN1 TSMC FB12

JUNIPER XT A12 HF MVD SLT BIN1 TSMC FB12

2

Y12

MVREFDB

MVREFSB

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

MVREFD_B

MVREFD/S =0.7*

VDDR1

(GDDR3/4/5)

AA12

MVREFS_B

1uF_6.3V

1uF_6.3V

L18

MVREFDA

AH11

DRST

DRAM_RSTp.4,5

A A

R3615 51.1RR3615 51.1R

C3608

C3608

10K

10K

PLEASESEEBOMFORQUALIFIEDVALUES

5

DRAM_RST

R3600

R3600

JUNIPER XT A12 HF MVD SLT BIN1 TSMC FB12

JUNIPER XT A12 HF MVD SLT BIN1 TSMC FB12

120pF_50V

120pF_50V

MVREFSA

MVREFD_A

MVREFD/S =0.7*

VDDR1

(GDDR3/4/5)

L20

MVREFS_A

4

R3606

R3606

40.2R

40.2R

1%

R3607

R3607

C3602

C3602

100R

100R

1%

C3607

C3607

1uF_6.3V

1uF_6.3V

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Tuesday, November 10, 2009

Tuesday, November 10, 2009

Tuesday, November 10, 2009

Sheet

Sheet

Sheet

of

321

of

321

of

321

+MVDD

R3610

R3610

40.2R

40.2R

1%

R3612

R3612

100R

100R

1%

RevDate:

RevDate:

RevDate:

50

50

50

Doc No.

Doc No.

Doc No.

102-C01301-00

102-C01301-00

1

102-C01301-00

Page 4

5

(4) GDDR5 x16 MEM Channel A

VDD-C5

VDD-G1

VDD-G4

VDD-L1

VDD-L4

VDD-L11

VDD-L14

VDD-R5

VSS-B5

VSS-G5

VSS-H1

VSS-K1

VSS-L5

VSS-T5

VSS-T10

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

+MVDD

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

U2000

DQA0_[31..0]p.3

DQA0_17

DQA0_16

DQA0_18

D D

MAA0_[8..0]p.3

C C

+MVDD +MVDD +MVDD

R2003 120RR2003 120R

R2004 120RR2004 120R

DQA0_19

DQA0_20

DQA0_23

DQA0_21

DQA0_22

DQA0_10

DQA0_8

DQA0_11

DQA0_9

DQA0_12

DQA0_13

DQA0_14

DQA0_15

MAA0_8

MAA0_7

MAA0_6

MAA0_5

MAA0_4

MAA0_3

MAA0_2

MAA0_1

MAA0_0

WCKA0_0p.3

WCKA0b_0p.3

WCKA0_1p.3

WCKA0b_1p.3

EDCA0_2p.3

EDCA0_1p.3

+MVDD

DDBIA0_2p.3

+MVDD

DDBIA0_1p.3

RASA0bp.3

CASA0bp.3

CKEA0p.3

CLKA0bp.3

CLKA0p.3

CSA0b_0p.3

WEA0bp.3

R2002 120RR2002 120R

DRAM_RSTp.3,5

B B

+MEM_VREF +MEM_VREF

C2003

C2003

100nF_6.3V

100nF_6.3V

C2004 1uF_6.3VC2004 1uF_6.3V

1% 1%

R2009 2.37KR2009 2.37K

+MVDD +MVDD +MVDD

R2010 5.49KR2010 5.49K

C2005 1uF_6.3VC2005 1uF_6.3V

VREFC_A0 VREFC_B0

1%

ADBIA0p.3

U2000

M2

M4

N2

N4

T2

T4

V2

V4

M13

M11

N13

N11

T13

T11

V13

V11

F13

F11

E13

E11

B13

B11

A13

A11

F2

F4

E2

E4

B2

B4

A2

A4

J5

K4

K5

K10

K11

H10

H11

H5

H4

D4

D5

P4

P5

R2

R13

C13

C2

P2

P13

D13

D2

G3

L3

J3

J11

J12

G12

L12

J13

1%

J10

J2

J1

A5

V5

A10

V10

J14

J4

23F41GB7ME50

23F41GB7ME50

DQ31 | DQ7

DQ30 | DQ6

DQ29 | DQ5

DQ28 | DQ4

DQ27 | DQ3

DQ26 | DQ2

DQ25 | DQ1

DQ24 | DQ0

DQ23 | DQ15

DQ22 | DQ14

DQ21 | DQ13

DQ20 | DQ12

DQ19 | DQ11

DQ18 | DQ10

DQ17 | DQ9

DQ16 | DQ8

DQ15 | DQ23

DQ14 | DQ22

DQ13 | DQ21

DQ12 | DQ20

DQ11 | DQ19

DQ10 | DQ18

DQ9 | DQ17

DQ8 | DQ16

DQ7 | DQ31

DQ6 | DQ30

DQ5 | DQ29

DQ4 | DQ28

DQ3 | DQ27

DQ2 | DQ26

DQ1 | DQ25

DQ0 | DQ24

RFU/A12/NC

A7/A8 | A0/A10

A6/A11 | A1/A9

A5/BA1 | A3/BA3

A4/BA2 | A2/BA0

A3/BA3 | A5/BA1

A2 /BA0 | A4/BA2

A1/A9 | A6/A11

A0/A10 | A7/A8

WCK01 | WCK23

WCK01# | WCK23#

WCK23 | WCK01

WCK23# | WCK01#

EDC3 | EDC0

EDC2 | EDC1

EDC1 | EDC2

EDC0 | EDC3

DBI3# | DBI0#

DBI2 #| DBI1#

DBI1# | DBI2#

DBI0# | DBI3#

RAS# | CAS#

CAS# | RAS#

CKE#

CK#

CK

CS# | WE#

WE# | CS#

ZQ

SEN

RESET#

MF

Vpp,NC

Vpp,NC1

VREFD1

VREFD2

VREFC

ABI#

GDDR5

VDDQ-B1

VDDQ-B3

VDDQ-B12

VDDQ-B14

VDDQ-D1

VDDQ-D3

VDDQ-D12

VDDQ-D14

VDDQ-E5

VDDQ-E10

VDDQ-F1

VDDQ-F3

VDDQ-F12

VDDQ-F14

VDDQ-G2

VDDQ-G13

VDDQ-H3

VDDQ-H12

VDDQ-K3

VDDQ-K12

VDDQ-L2

VDDQ-L13

VDDQ-M1

VDDQ-M3

VDDQ-M12

VDDQ-M14

VDDQ-N5

VDDQ-N10

VDDQ-P1

VDDQ-P3

VDDQ-P12

VDDQ-P14

VDDQ-T1

VDDQ-T3

VDDQ-T12

VDDQ-T14

VDD-C10

VDD-D11

VDD-G11

VDD-G14

VDD-P11

VDD-R10

VSSQ-A1

VSSQ-A3

VSSQ-A12

VSSQ-A14

VSSQ-C1

VSSQ-C3

VSSQ-C4

VSSQ-C11

VSSQ-C12

VSSQ-C14

VSSQ-E1

VSSQ-E3

VSSQ-E12

VSSQ-E14

VSSQ-F5

VSSQ-F10

VSSQ-H2

VSSQ-H13

VSSQ-K2

VSSQ-K13

VSSQ-M5

VSSQ-M10

VSSQ-N1

VSSQ-N3

VSSQ-N12

VSSQ-N14

VSSQ-R1

VSSQ-R3

VSSQ-R4

VSSQ-R11

VSSQ-R12

VSSQ-R14

VSSQ-V1

VSSQ-V3

VSSQ-V12

VSSQ-V14

VSS-G10

VSS-B10

VSS-D10

VSS-H14

VSS-K14

VSS-L10

VSS-P10

4

CH_A0 =U2000 & U2100

DQA0_[31..0]p.3

MAA0_[8..0]p.3

R2103 120RR2103 120R

R2104 120RR2104 120R

DRAM_RSTp.3,5

C2139

C2139

100nF_6.3V

100nF_6.3V

C2138 1uF_6.3VC2138 1uF_6.3V

1% 1%

R2109 2.37KR2109 2.37K

R2110 5.49KR2110 5.49K

C2140 1uF_6.3VC2140 1uF_6.3V

ADBIA0p.3

DDBIA0_0p.3

DDBIA0_3p.3

CKEA0p.3

CLKA0bp.3

CLKA0p.3

R2101 120RR2101 120R

VREFC_A1

3

CH_A1 =U2200 & U2300

DQA1_15

DQA1_14

DQA1_13

DQA1_8

DQA1_12

DQA1_10

DQA1_11

DQA1_9

M=1

Mirror

DQA1_23

DQA1_22

DQA1_20

DQA1_21

DQA1_16

DQA1_18

DQA1_19

DQA1_17

MAA1_8

MAA1_0

MAA1_1

MAA1_3

MAA1_2

MAA1_5

MAA1_4

MAA1_6

MAA1_7

WCKA1_1p.3

WCKA1b_1p.3

WCKA1_0p.3

WCKA1b_0p.3

EDCA1_1p.3

EDCA1_2p.3

+MVDD

DDBIA1_1p.3 DDBIA1_0p.3

+MVDD

DDBIA1_2p.3

CASA1bp.3

RASA1bp.3

CKEA1p.3

CLKA1bp.3

CLKA1p.3

WEA1bp.3

CSA1b_0p.3

R2201 120RR2201 120R

DRAM_RSTp.3,5

+MVDD

C2242

C2242

100nF_6.3V

100nF_6.3V

1% 1%

1%

ADBIA1p.3

U2200

U2200

M2

DQ31 | DQ7

M4

DQ30 | DQ6

N2

DQ29 | DQ5

N4

DQ28 | DQ4

T2

DQ27 | DQ3

T4

DQ26 | DQ2

V2

DQ25 | DQ1

V4

DQ24 | DQ0

M13

DQ23 | DQ15

M11

DQ22 | DQ14

N13

DQ21 | DQ13

N11

DQ20 | DQ12

T13

DQ19 | DQ11

T11

DQ18 | DQ10

V13

DQ17 | DQ9

V11

DQ16 | DQ8

F13

DQ15 | DQ23

F11

DQ14 | DQ22

E13

DQ13 | DQ21

E11

DQ12 | DQ20

B13

DQ11 | DQ19

B11

DQ10 | DQ18

A13

DQ9 | DQ17

A11

DQ8 | DQ16

F2

DQ7 | DQ31

F4

DQ6 | DQ30

E2

DQ5 | DQ29

E4

DQ4 | DQ28

B2

DQ3 | DQ27

B4

DQ2 | DQ26

A2

DQ1 | DQ25

A4

DQ0 | DQ24

J5

RFU/A12/NC

K4

A7/A8 | A0/A10

K5

A6/A11 | A1/A9

K10

A5/BA1 | A3/BA3

K11

A4/BA2 | A2/BA0

H10

A3/BA3 | A5/BA1

H11

A2 /BA0 | A4/BA2

H5

A1/A9 | A6/A11

H4

A0/A10 | A7/A8

D4

WCK01 | WCK23

D5

WCK01# | WCK23#

P4

WCK23 | WCK01

P5

WCK23# | WCK01#

R2

EDC3 | EDC0

R13

EDC2 | EDC1

C13

EDC1 | EDC2

C2

EDC0 | EDC3

P2

DBI3# | DBI0#

P13

DBI2 #| DBI1#

D13

DBI1# | DBI2#

D2

DBI0# | DBI3#

G3

RAS# | CAS#

L3

CAS# | RAS#

J3

CKE#

J11

CK#

J12

CK

G12

CS# | WE#

L12

WE# | CS#

J13

1%

ZQ

J10

SEN

J2

RESET#

J1

MF

A5

Vpp,NC

V5

Vpp,NC1

A10

VREFD1

V10

VREFD2

J14

VREFC

J4

ABI#

23F41GB7ME50

23F41GB7ME50

VDD-C5

VDD-G1

VDD-G4

VDD-L1

VDD-L4

VDD-R5

VSS-B5

VSS-G5

VSS-H1

VSS-K1

VSS-L5

VSS-T5

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

+MVDD

DQA1_[31..0]p.3

R2203 120RR2203 120R

R2204 120RR2204 120R

+MEM_VREF

MAA1_[8..0]p.3

C2239 1uF_6.3VC2239 1uF_6.3V

R2209 2.37KR2209 2.37K

R2210 5.49KR2210 5.49K

C2241 1uF_6.3VC2241 1uF_6.3V

U2100

U2100

M2

M4

N2

N4

T2

T4

V2

V4

M13

DQA0_4

M11

DQA0_3

N13

DQA0_2

N11

DQA0_0

T13

DQA0_1

T11

DQA0_6

V13

DQA0_7

V11

DQA0_5

F13

F11

E13

M=1

E11

Mirror

B13

B11

A13

A11

+MVDD

+MVDD

F2

F4

E2

E4

B2

B4

A2

A4

J5

K4

K5

K10

K11

H10

H11

H5

H4

D4

D5

P4

P5

R2

R13

C13

C2

P2

P13

D13

D2

G3

L3

J3

J11

J12

G12

L12

J13

1%

J10

J2

J1

A5

V5

A10

V10

J14

DQA0_31

DQA0_29

DQA0_30

DQA0_28

DQA0_26

DQA0_25

DQA0_27

DQA0_24

MAA0_8

MAA0_0

MAA0_1

MAA0_3

MAA0_2

MAA0_5

MAA0_4

MAA0_6

MAA0_7

WCKA0_1p.3

WCKA0b_1p.3

WCKA0_0p.3

WCKA0b_0p.3

EDCA0_0p.3

EDCA0_3p.3

CASA0bp.3

RASA0bp.3

WEA0bp.3

CSA0b_0p.3

+MVDD

VREFC_A1

1%

J4

DQ31 | DQ7

DQ30 | DQ6

DQ29 | DQ5

DQ28 | DQ4

DQ27 | DQ3

DQ26 | DQ2

DQ25 | DQ1

DQ24 | DQ0

DQ23 | DQ15

DQ22 | DQ14

DQ21 | DQ13

DQ20 | DQ12

DQ19 | DQ11

DQ18 | DQ10

DQ17 | DQ9

DQ16 | DQ8

DQ15 | DQ23

DQ14 | DQ22

DQ13 | DQ21

DQ12 | DQ20

DQ11 | DQ19

DQ10 | DQ18

DQ9 | DQ17

DQ8 | DQ16

DQ7 | DQ31

DQ6 | DQ30

DQ5 | DQ29

DQ4 | DQ28

DQ3 | DQ27

DQ2 | DQ26

DQ1 | DQ25

DQ0 | DQ24

RFU/A12/NC

A7/A8 | A0/A10

A6/A11 | A1/A9

A5/BA1 | A3/BA3

A4/BA2 | A2/BA0

A3/BA3 | A5/BA1

A2 /BA0 | A4/BA2

A1/A9 | A6/A11

A0/A10 | A7/A8

WCK01 | WCK23

WCK01# | WCK23#

WCK23 | WCK01

WCK23# | WCK01#

EDC3 | EDC0

EDC2 | EDC1

EDC1 | EDC2

EDC0 | EDC3

DBI3# | DBI0#

DBI2 #| DBI1#

DBI1# | DBI2#

DBI0# | DBI3#

RAS# | CAS#

CAS# | RAS#

CKE#

CK#

CK

CS# | WE#

WE# | CS#

ZQ

SEN

RESET#

MF

Vpp,NC

Vpp,NC1

VREFD1

VREFD2

VREFC

ABI#

23F41GB7ME50

23F41GB7ME50

GDDR5

VDDQ-B1

VDDQ-B3

VDDQ-B12

VDDQ-B14

VDDQ-D1

VDDQ-D3

VDDQ-D12

VDDQ-D14

VDDQ-E5

VDDQ-E10

VDDQ-F1

VDDQ-F3

VDDQ-F12

VDDQ-F14

VDDQ-G2

VDDQ-G13

VDDQ-H3

VDDQ-H12

VDDQ-K3

VDDQ-K12

VDDQ-L2

VDDQ-L13

VDDQ-M1

VDDQ-M3

VDDQ-M12

VDDQ-M14

VDDQ-N5

VDDQ-N10

VDDQ-P1

VDDQ-P3

VDDQ-P12

VDDQ-P14

VDDQ-T1

VDDQ-T3

VDDQ-T12

VDDQ-T14

VDD-C10

VDD-D11

VDD-G11

VDD-G14

VDD-L11

VDD-L14

VDD-P11

VDD-R10

VSSQ-A1

VSSQ-A3

VSSQ-A12

VSSQ-A14

VSSQ-C1

VSSQ-C3

VSSQ-C4

VSSQ-C11

VSSQ-C12

VSSQ-C14

VSSQ-E1

VSSQ-E3

VSSQ-E12

VSSQ-E14

VSSQ-F5

VSSQ-F10

VSSQ-H2

VSSQ-H13

VSSQ-K2

VSSQ-K13

VSSQ-M5

VSSQ-M10

VSSQ-N1

VSSQ-N3

VSSQ-N12

VSSQ-N14

VSSQ-R1

VSSQ-R3

VSSQ-R4

VSSQ-R11

VSSQ-R12

VSSQ-R14

VSSQ-V1

VSSQ-V3

VSSQ-V12

VSSQ-V14

VSS-B10

VSS-D10

VSS-G10

VSS-H14

VSS-K14

VSS-L10

VSS-P10

VSS-T10

GDDR5

VDDQ-B1

VDDQ-B3

VDDQ-B12

VDDQ-B14

VDDQ-D1

VDDQ-D3

VDDQ-D12

VDDQ-D14

VDDQ-E5

VDDQ-E10

VDDQ-F1

VDDQ-F3

VDDQ-F12

VDDQ-F14

VDDQ-G2

VDDQ-G13

VDDQ-H3

VDDQ-H12

VDDQ-K3

VDDQ-K12

VDDQ-L2

VDDQ-L13

VDDQ-M1

VDDQ-M3

VDDQ-M12

VDDQ-M14

VDDQ-N5

VDDQ-N10

VDDQ-P1

VDDQ-P3

VDDQ-P12

VDDQ-P14

VDDQ-T1

VDDQ-T3

VDDQ-T12

VDDQ-T14

VDD-C5

VDD-C10

VDD-D11

VDD-G1

VDD-G4

VDD-G11

VDD-G14

VDD-L1

VDD-L4

VDD-L11

VDD-L14

VDD-P11

VDD-R5

VDD-R10

VSSQ-A1

VSSQ-A3

VSSQ-A12

VSSQ-A14

VSSQ-C1

VSSQ-C3

VSSQ-C4

VSSQ-C11

VSSQ-C12

VSSQ-C14

VSSQ-E1

VSSQ-E3

VSSQ-E12

VSSQ-E14

VSSQ-F5

VSSQ-F10

VSSQ-H2

VSSQ-H13

VSSQ-K2

VSSQ-K13

VSSQ-M5

VSSQ-M10

VSSQ-N1

VSSQ-N3

VSSQ-N12

VSSQ-N14

VSSQ-R1

VSSQ-R3

VSSQ-R4

VSSQ-R11

VSSQ-R12

VSSQ-R14

VSSQ-V1

VSSQ-V3

VSSQ-V12

VSSQ-V14

VSS-B5

VSS-B10

VSS-D10

VSS-G5

VSS-G10

VSS-H1

VSS-H14

VSS-K1

VSS-K14

VSS-L5

VSS-L10

VSS-P10

VSS-T5

VSS-T10

2

+MVDD

+MEM_VREF

+MVDD

+MVDD

R2305 120RR2305 120R

R2304 120RR2304 120R

C2344

C2344

100nF_6.3V

100nF_6.3V

+MVDD

DQA1_[31..0]p.3

MAA1_[8..0]p.3

DDBIA1_3p.3

DRAM_RSTp.3,5

C2343 1uF_6.3VC2343 1uF_6.3V

R2309 2.37KR2309 2.37K

R2310 5.49KR2310 5.49K

C2345 1uF_6.3VC2345 1uF_6.3V

ADBIA1p.3

C2305 1uF_6.3VC2305 1uF_6.3V

CLKA1bp.3

CLKA1p.3

CSA1b_0p.3

WEA1bp.3

C2306 1uF_6.3VC2306 1uF_6.3V

DQA1_26

DQA1_27

DQA1_28

DQA1_25

DQA1_24

DQA1_29

DQA1_30

DQA1_31

DQA1_1

DQA1_0

DQA1_2

DQA1_3

DQA1_4

DQA1_6

DQA1_5

DQA1_7

MAA1_8

MAA1_7

MAA1_6

MAA1_5

MAA1_4

MAA1_3

MAA1_2

MAA1_1

MAA1_0

WCKA1_0p.3

WCKA1b_0p.3

WCKA1_1p.3

WCKA1b_1p.3

EDCA1_3p.3

EDCA1_0p.3

+MVDD

+MVDD

RASA1bp.3

CASA1bp.3

CKEA1p.3

R2302 120RR2302 120R

1%

1%

C2308 1uF_6.3VC2308 1uF_6.3V

1%

VREFC_B1

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

U2300

U2300

M2

M4

N2

N4

M13

M11

N13

N11

T13

T11

V13

V11

F13

F11

E13

E11

B13

B11

A13

A11

K10

K11

H10

H11

H5

H4

D4

D5

R2

R13

C13

C2

P13

D13

D2

G3

J11

J12

G12

L12

J13

J10

A10

V10

J14

C2312 1uF_6.3VC2312 1uF_6.3V

DQ31 | DQ7

DQ30 | DQ6

DQ29 | DQ5

DQ28 | DQ4

T2

DQ27 | DQ3

T4

DQ26 | DQ2

V2

DQ25 | DQ1

V4

DQ24 | DQ0

DQ23 | DQ15

DQ22 | DQ14

DQ21 | DQ13

DQ20 | DQ12

DQ19 | DQ11

DQ18 | DQ10

DQ17 | DQ9

DQ16 | DQ8

DQ15 | DQ23

DQ14 | DQ22

DQ13 | DQ21

DQ12 | DQ20

DQ11 | DQ19

DQ10 | DQ18

DQ9 | DQ17

DQ8 | DQ16

F2

DQ7 | DQ31

F4

DQ6 | DQ30

E2

DQ5 | DQ29

E4

DQ4 | DQ28

B2

DQ3 | DQ27

B4

DQ2 | DQ26

A2

DQ1 | DQ25

A4

DQ0 | DQ24

J5

RFU/A12/NC

K4

A7/A8 | A0/A10

K5

A6/A11 | A1/A9

A5/BA1 | A3/BA3

A4/BA2 | A2/BA0

A3/BA3 | A5/BA1

A2 /BA0 | A4/BA2

A1/A9 | A6/A11

A0/A10 | A7/A8

WCK01 | WCK23

WCK01# | WCK23#

P4

WCK23 | WCK01

P5

WCK23# | WCK01#

EDC3 | EDC0

EDC2 | EDC1

EDC1 | EDC2

EDC0 | EDC3

P2

DBI3# | DBI0#

DBI2 #| DBI1#

DBI1# | DBI2#

DBI0# | DBI3#

RAS# | CAS#

L3

CAS# | RAS#

J3

CKE#

CK#

CK

CS# | WE#

WE# | CS#

ZQ

SEN

J2

RESET#

J1

MF

A5

Vpp,NC

V5

Vpp,NC1

VREFD1

VREFD2

VREFC

J4

ABI#

23F41GB7ME50

23F41GB7ME50

C2313 2.2uF_4VC2313 2.2uF_4V

1

C2315 2.2uF_4VC2315 2.2uF_4V

GDDR5

C2316 2.2uF_4VC2316 2.2uF_4V

VDDQ-B12

VDDQ-B14

VDDQ-D12

VDDQ-D14

VDDQ-E10

VDDQ-F12

VDDQ-F14

VDDQ-G13

VDDQ-H12

VDDQ-K12

VDDQ-L13

VDDQ-M12

VDDQ-M14

VDDQ-N10

VDDQ-P12

VDDQ-P14

VDDQ-T12

VDDQ-T14

VSSQ-A12

VSSQ-A14

VSSQ-C11

VSSQ-C12

VSSQ-C14

VSSQ-E12

VSSQ-E14

VSSQ-F10

VSSQ-H13

VSSQ-K13

VSSQ-M10

VSSQ-N12

VSSQ-N14

VSSQ-R11

VSSQ-R12

VSSQ-R14

VSSQ-V12

VSSQ-V14

C2317 1uF_6.3VC2317 1uF_6.3V

VDDQ-B1

VDDQ-B3

VDDQ-D1

VDDQ-D3

VDDQ-E5

VDDQ-F1

VDDQ-F3

VDDQ-G2

VDDQ-H3

VDDQ-K3

VDDQ-L2

VDDQ-M1

VDDQ-M3

VDDQ-N5

VDDQ-P1

VDDQ-P3

VDDQ-T1

VDDQ-T3

VDD-C5

VDD-C10

VDD-D11

VDD-G1

VDD-G4

VDD-G11

VDD-G14

VDD-L1

VDD-L4

VDD-L11

VDD-L14

VDD-P11

VDD-R5

VDD-R10

VSSQ-A1

VSSQ-A3

VSSQ-C1

VSSQ-C3

VSSQ-C4

VSSQ-E1

VSSQ-E3

VSSQ-F5

VSSQ-H2

VSSQ-K2

VSSQ-M5

VSSQ-N1

VSSQ-N3

VSSQ-R1

VSSQ-R3

VSSQ-R4

VSSQ-V1

VSSQ-V3

VSS-B5

VSS-B10

VSS-D10

VSS-G5

VSS-G10

VSS-H1

VSS-H14

VSS-K1

VSS-K14

VSS-L5

VSS-L10

VSS-P10

VSS-T5

VSS-T10

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

C2321 1uF_6.3VC2321 1uF_6.3V

+MVDD

+MVDD

C2322 1uF_6.3VC2322 1uF_6.3V

C2323 2.2uF_4VC2323 2.2uF_4V

C2324 2.2uF_4VC2324 2.2uF_4V

C2025 1uF_6.3VC2025 1uF_6.3V

C2032 10uFC2032 10uF

+MVDD

+MVDD

C2145 1uF_6.3VC2145 1uF_6.3V

C2135 1uF_6.3VC2135 1uF_6.3V

C2101 1uF_6.3VC2101 1uF_6.3V

C2136 1uF_6.3VC2136 1uF_6.3V

C2137 2.2uF_4VC2137 2.2uF_4V

4

C2102 1uF_6.3VC2102 1uF_6.3V

C2127 1uF_6.3VC2127 1uF_6.3V

C2103 1uF_6.3VC2103 1uF_6.3V

C2126 2.2uF_4VC2126 2.2uF_4V

C2128 2.2uF_4VC2128 2.2uF_4V

C2108 1uF_6.3VC2108 1uF_6.3V

C2129 2.2uF_4VC2129 2.2uF_4V

C2109 2.2uF_4VC2109 2.2uF_4V

C2110 1uF_6.3VC2110 1uF_6.3V

C2122 1uF_6.3VC2122 1uF_6.3V

C2111 1uF_6.3VC2111 1uF_6.3V

C2133 1uF_6.3VC2133 1uF_6.3V

C2112 1uF_6.3VC2112 1uF_6.3V

C2134 1uF_6.3VC2134 1uF_6.3V

C2114 1uF_6.3VC2114 1uF_6.3V

C2113 2.2uF_4VC2113 2.2uF_4V

C2121 10uFC2121 10uF

C2132 10uFC2132 10uF

C2115 2.2uF_4VC2115 2.2uF_4V

C2116 1uF_6.3VC2116 1uF_6.3V

C2117 1uF_6.3VC2117 1uF_6.3V

+MVDD

C2125 10uFC2125 10uF

C2124 10uFC2124 10uF

+MVDD

Use internal Vref memory voltage

C2021 1uF_6.3VC2021 1uF_6.3V

C2011 2.2uF_4VC2011 2.2uF_4V

C2000 1uF_6.3VC2000 1uF_6.3V

C2010 2.2uF_4VC2010 2.2uF_4V

A A

C2001 2.2uF_4VC2001 2.2uF_4V

C2013 1uF_6.3VC2013 1uF_6.3V

C2014 2.2uF_4VC2014 2.2uF_4V

C2019 1uF_6.3VC2019 1uF_6.3V

C2020 1uF_6.3VC2020 1uF_6.3V

C2024 1uF_6.3VC2024 1uF_6.3V

+MVDD

C2041 2.2uF_4VC2041 2.2uF_4V

C2042 2.2uF_4VC2042 2.2uF_4V

C2038 2.2uF_4VC2038 2.2uF_4V

C2039 1uF_6.3VC2039 1uF_6.3V

C2036 2.2uF_4VC2036 2.2uF_4V

5

C2037 1uF_6.3VC2037 1uF_6.3V

C2034 1uF_6.3VC2034 1uF_6.3V

C2027 1uF_6.3VC2027 1uF_6.3V

C2028 1uF_6.3VC2028 1uF_6.3V

+MVDD +MVDD

C2026 10uFC2026 10uF

C2040 10uFC2040 10uF

C2030 10uFC2030 10uF

C2031 10uFC2031 10uF

C2119 1uF_6.3VC2119 1uF_6.3V

C2130 10uFC2130 10uF

+MVDD

C2200 1uF_6.3VC2200 1uF_6.3V

C2202 1uF_6.3VC2202 1uF_6.3V

C2205 2.2uF_4VC2205 2.2uF_4V

C2203 1uF_6.3VC2203 1uF_6.3V

C2207 2.2uF_4VC2207 2.2uF_4V

+MVDD

C2228 2.2uF_4VC2228 2.2uF_4V

C2234 2.2uF_4VC2234 2.2uF_4V

C2235 1uF_6.3VC2235 1uF_6.3V

C2227 2.2uF_4VC2227 2.2uF_4V

C2236 2.2uF_4VC2236 2.2uF_4V

3

C2237 2.2uF_4VC2237 2.2uF_4V

C2221 1uF_6.3VC2221 1uF_6.3V

C2208 1uF_6.3VC2208 1uF_6.3V

C2209 1uF_6.3VC2209 1uF_6.3V

C2222 1uF_6.3VC2222 1uF_6.3V

C2210 2.2uF_4VC2210 2.2uF_4V

C2223 1uF_6.3VC2223 1uF_6.3V

C2211 1uF_6.3VC2211 1uF_6.3V

C2226 1uF_6.3VC2226 1uF_6.3V

C2212 1uF_6.3VC2212 1uF_6.3V

C2225 1uF_6.3VC2225 1uF_6.3V

C2213 1uF_6.3VC2213 1uF_6.3V

C2232 1uF_6.3VC2232 1uF_6.3V

C2214 2.2uF_4VC2214 2.2uF_4V

+MVDD

C2224 10uFC2224 10uF

C2215 2.2uF_4VC2215 2.2uF_4V

C2229 10uFC2229 10uF

C2217 1uF_6.3VC2217 1uF_6.3V

2

C2218 1uF_6.3VC2218 1uF_6.3V

+MVDD+MVDD

+MVDD

C2340 2.2uF_4VC2340 2.2uF_4V

C2325 2.2uF_4VC2325 2.2uF_4V

C2330 2.2uF_4VC2330 2.2uF_4V

C2331 2.2uF_4VC2331 2.2uF_4V

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

C2230 10uFC2230 10uF

C2231 10uFC2231 10uF

C2233 10uFC2233 10uF

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

RH JUNIPER GDDR5 1GB DP+DP/HDMI+DVI /sVGA

C2332 2.2uF_4VC2332 2.2uF_4V

C2327 1uF_6.3VC2327 1uF_6.3V

C2328 2.2uF_4VC2328 2.2uF_4V

C2329 1uF_6.3VC2329 1uF_6.3V

C2341 1uF_6.3VC2341 1uF_6.3V

C2342 1uF_6.3VC2342 1uF_6.3V

C2326 1uF_6.3VC2326 1uF_6.3V

C2333 1uF_6.3VC2333 1uF_6.3V

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Tuesday, November 10, 2009

Tuesday, November 10, 2009

Tuesday, November 10, 2009

Sheet

Sheet

Sheet

of

421

of

421

of

421

1

+MVDD

C2335 10uFC2335 10uF

Doc No.

Doc No.

Doc No.

+MVDD

C2337 10uFC2337 10uF

C2336 10uFC2336 10uF

102-C01301-00

102-C01301-00

102-C01301-00

C2339 10uFC2339 10uF

C2338 10uFC2338 10uF

RevDate:

RevDate:

RevDate:

50

50

50

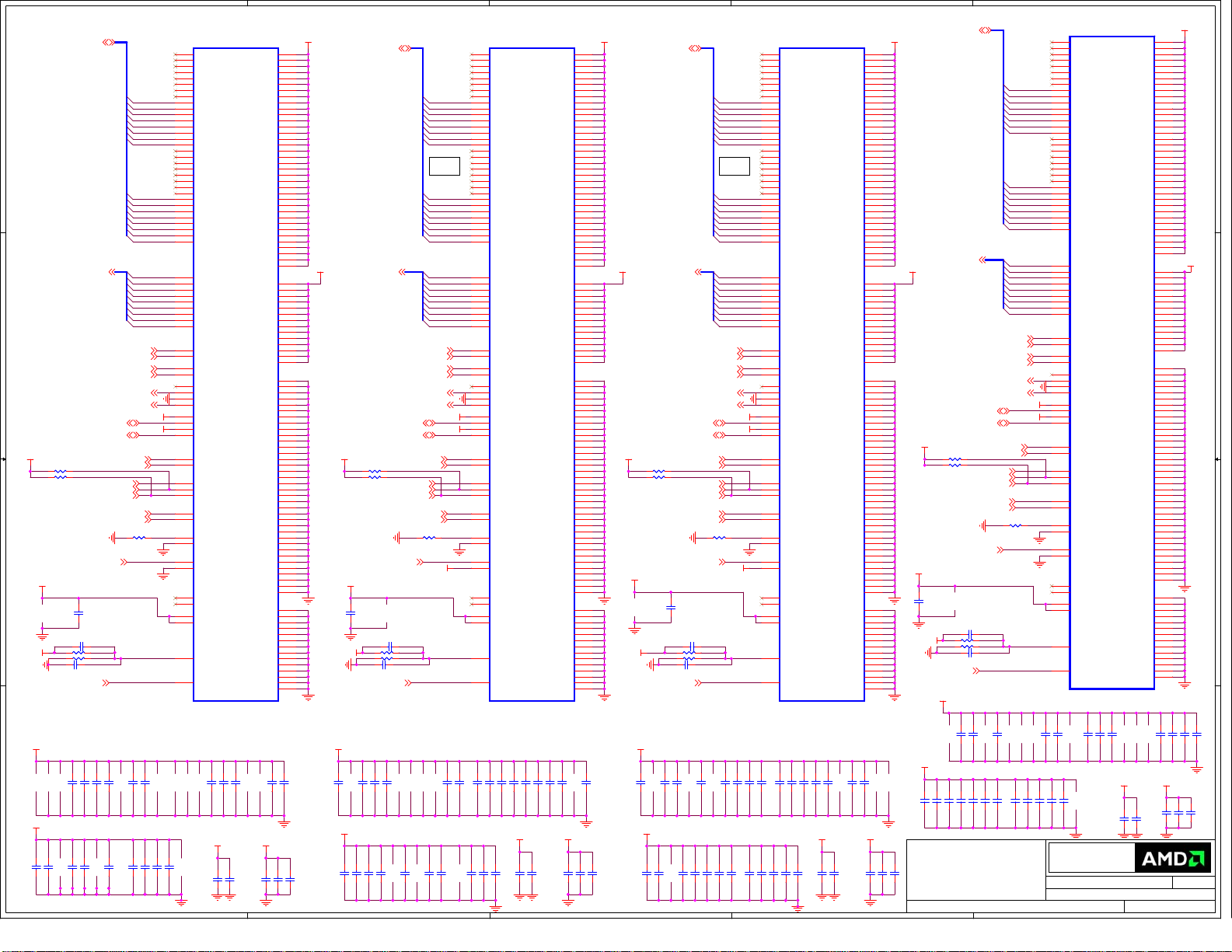

Page 5

5

(5) GDDR5 x16 MEM Channel B

DQB0_17

DQB0_16

DQB0_18

DQB0_19

DQB0_20

DDBIB0_2p.3

DDBIB0_1p.3

RASB0bp.3

CASB0bp.3

CSB0b_0p.3

WEB0bp.3

DRAM_RSTp.3,4

WCKB0_0p.3

WCKB0b_0p.3

WCKB0_1p.3

WCKB0b_1p.3

EDCB0_2p.3

EDCB0_1p.3

CKEB0p.3

CLKB0bp.3

CLKB0p.3

R2400 120RR2400 120R

1%

1%

DQB0_23

DQB0_21

DQB0_22

DQB0_10

DQB0_9

DQB0_11

DQB0_8

DQB0_14

DQB0_15

DQB0_13

DQB0_12

MAB0_8

MAB0_7

MAB0_6

MAB0_5

MAB0_4

MAB0_3

MAB0_2

MAB0_1

MAB0_0

+MVDD

+MVDD

VREFC_C0

D D

MAB0_[8..0]p.3

C C

+MVDD

R2403 120RR2403 120R

R2404 120RR2404 120R

+MEM_VREF

B B

C2400

C2400

100nF_6.3V

100nF_6.3V

C2401 1uF_6.3VC2401 1uF_6.3V

R2409 2.37KR2409 2.37K

+MVDD

R2410 5.49KR2410 5.49K

C2403 1uF_6.3VC2403 1uF_6.3V

ADBIB0p.3

1%

U2400

U2400

M2

DQ31 | DQ7

M4

DQ30 | DQ6

N2

DQ29 | DQ5

N4

DQ28 | DQ4

T2

DQ27 | DQ3

T4

DQ26 | DQ2

V2

DQ25 | DQ1

V4

DQ24 | DQ0

M13

DQ23 | DQ15

M11

DQ22 | DQ14

N13

DQ21 | DQ13

N11

DQ20 | DQ12

T13

DQ19 | DQ11

T11

DQ18 | DQ10

V13

DQ17 | DQ9

V11

DQ16 | DQ8

F13

DQ15 | DQ23

F11

DQ14 | DQ22

E13

DQ13 | DQ21

E11

DQ12 | DQ20

B13

DQ11 | DQ19

B11

DQ10 | DQ18

A13

DQ9 | DQ17

A11

DQ8 | DQ16

F2

DQ7 | DQ31

F4

DQ6 | DQ30

E2

DQ5 | DQ29

E4

DQ4 | DQ28

B2

DQ3 | DQ27

B4

DQ2 | DQ26

A2

DQ1 | DQ25

A4

DQ0 | DQ24

J5

RFU/A12/NC

K4

A7/A8 | A0/A10

K5

A6/A11 | A1/A9

K10

A5/BA1 | A3/BA3

K11

A4/BA2 | A2/BA0

H10

A3/BA3 | A5/BA1

H11

A2 /BA0 | A4/BA2

H5

A1/A9 | A6/A11

H4

A0/A10 | A7/A8

D4

WCK01 | WCK23

D5

WCK01# | WCK23#

P4

WCK23 | WCK01

P5

WCK23# | WCK01#

R2

EDC3 | EDC0

R13

EDC2 | EDC1

C13

EDC1 | EDC2

C2

EDC0 | EDC3

P2

DBI3# | DBI0#

P13

DBI2 #| DBI1#

D13

DBI1# | DBI2#

D2

DBI0# | DBI3#

G3

RAS# | CAS#

L3

CAS# | RAS#

J3

CKE#

J11

CK#

J12

CK

G12

CS# | WE#

L12

WE# | CS#

J13

ZQ

J10

SEN

J2

RESET#

J1

MF

A5

Vpp,NC

V5

Vpp,NC1

A10

VREFD1

V10

VREFD2

J14

VREFC

J4

ABI#

23F41GB7ME50

23F41GB7ME50

VDDQ-B1

VDDQ-B3

VDDQ-B12

VDDQ-B14

VDDQ-D1

VDDQ-D3

VDDQ-D12

VDDQ-D14

VDDQ-E5

VDDQ-E10

VDDQ-F1

VDDQ-F3

VDDQ-F12

VDDQ-F14

VDDQ-G2

VDDQ-G13

VDDQ-H3

VDDQ-H12

VDDQ-K3

VDDQ-K12

VDDQ-L2

VDDQ-L13

VDDQ-M1

VDDQ-M3

VDDQ-M12

VDDQ-M14

VDDQ-N5

VDDQ-N10

VDDQ-P1

VDDQ-P3

VDDQ-P12

VDDQ-P14

VDDQ-T1

VDDQ-T3

VDDQ-T12

VDDQ-T14

VDD-C10

VDD-D11

VDD-G11

VDD-G14

VDD-L11

VDD-L14

VDD-P11

VDD-R10

VSSQ-A1

VSSQ-A3

VSSQ-A12

VSSQ-A14

VSSQ-C1

VSSQ-C3

VSSQ-C4

VSSQ-C11

VSSQ-C12

VSSQ-C14

VSSQ-E1

VSSQ-E3

VSSQ-E12

VSSQ-E14

VSSQ-F5

VSSQ-F10

VSSQ-H2

VSSQ-H13

VSSQ-K2

VSSQ-K13

VSSQ-M5

VSSQ-M10

VSSQ-N1

VSSQ-N3

VSSQ-N12

VSSQ-N14

VSSQ-R1

VSSQ-R3

VSSQ-R4

VSSQ-R11

VSSQ-R12

VSSQ-R14

VSSQ-V1

VSSQ-V3

VSSQ-V12

VSSQ-V14

VSS-B10

VSS-D10

VSS-G10

VSS-H14

VSS-K14

VSS-L10

VSS-P10

VSS-T10

VDD-C5

VDD-G1

VDD-G4

VDD-L1

VDD-L4

VDD-R5

VSS-B5

VSS-G5

VSS-H1

VSS-K1

VSS-L5

VSS-T5

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

+MVDD

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

+MVDD

C2423 1uF_6.3VC2423 1uF_6.3V

C2410 2.2uF_4VC2410 2.2uF_4V

C2430 1uF_6.3VC2430 1uF_6.3V

C2405 2.2uF_4VC2405 2.2uF_4V

C2431 2.2uF_4VC2431 2.2uF_4V

C2414 1uF_6.3VC2414 1uF_6.3V

C2413 1uF_6.3VC2413 1uF_6.3V

C2443 1uF_6.3VC2443 1uF_6.3V

5

C2441 1uF_6.3VC2441 1uF_6.3V

C2432 1uF_6.3VC2432 1uF_6.3V

C2438 1uF_6.3VC2438 1uF_6.3V

C2417 2.2uF_4VC2417 2.2uF_4V

C2439 1uF_6.3VC2439 1uF_6.3V

C2407 2.2uF_4VC2407 2.2uF_4V

C2408 2.2uF_4VC2408 2.2uF_4V

C2406 2.2uF_4VC2406 2.2uF_4V

A A

C2435 2.2uF_4VC2435 2.2uF_4V

C2444 2.2uF_4VC2444 2.2uF_4V

C2434 2.2uF_4VC2434 2.2uF_4V

C2436 2.2uF_4VC2436 2.2uF_4V

C2418 2.2uF_4VC2418 2.2uF_4V

C2442 1uF_6.3VC2442 1uF_6.3V

C2419 2.2uF_4VC2419 2.2uF_4V

+MVDD

C2433 10uFC2433 10uF

C2421 1uF_6.3VC2421 1uF_6.3V

C2428 10uFC2428 10uF

C2422 2.2uF_4VC2422 2.2uF_4V

+MVDD

C2437 10uFC2437 10uF

C2440 10uFC2440 10uF

+MVDD+MVDD

C2429 10uFC2429 10uF

4

3

2

CH_B0 =U2400 & U2500 CH_B1 =U2600 & U2700

VDD-L1

VDD-L4

VSS-B5

VSS-G5

VSS-H1

VSS-K1

VSS-L5

VSS-T5

C2617 1uF_6.3VC2617 1uF_6.3V

C2635 10uFC2635 10uF

+MVDD

B1

B3

B12

B14

D1

D3

D12

D14

E5

E10

F1

F3

F12

F14

G2

G13

H3

H12

K3

K12

L2

L13

M1

M3

M12

M14

N5

N10

P1

P3

P12

P14

T1

T3

T12

T14

C5

C10

D11

G1

G4

G11

G14

L1

L4

L11

L14

P11

R5

R10

A1

A3

A12

A14

C1

C3

C4

C11

C12

C14

E1

E3

E12

E14

F5

F10

H2

H13

K2

K13

M5

M10

N1

N3

N12

N14

R1

R3

R4

R11

R12

R14

V1

V3

V12

V14

B5

B10

D10

G5

G10

H1

H14

K1

K14

L5

L10

P10

T5

T10

+MVDD

+MVDD