FINAL

MACH

®

111-5/7/10/12/15

COM’L: -5/7/10/12/15 IND: -7/10/12/14/18

High-Performance EE CMOS Programmable Logic

DISTINCTIVE CHARACTERISTICS

44 Pins in PLCC and TQFP

◆

32 Macrocells

◆

5 ns t

◆

182 MHz f

◆

32 I/Os; 4 dedicated inputs/clocks; 2 dedicated inputs

◆

32 Flip-flops; 4 clock choices

◆

2 “PALCE26V16” blocks

◆

SpeedLocking™ for guaranteed fixed timing

◆

Bus-Friendly™ Inputs and I/Os

◆

Peripheral Component Interconnect (PCI) compliant (-5/-7/-10/-12)

◆

Programmable power-down mode

◆

Safe for mixed supply voltage system designs

◆

Pin-compatible with the MACH211

◆

Commercial, 7.5 ns t

PD

CNT

Industrial

PD

GENERAL DESCRIPTION

The MACH111 is a member of Vantis’ high-performance EE CMOS MACH 1 & 2 families. This

device has approximately three times the logic macrocell capability of the popular P ALCE22V10

without loss of speed.

The MACH111 consists of two PAL

The two PAL blocks are essentially “PALCE26V16” structures complete with product-term arrays

and programmable macrocells, which can be programmed as high speed or low power. The

switch matrix connects the PAL blocks to each other and to all input pins, providing a high

degree of connectivity between the fully connected P AL blocks. This allows designs to be placed

and routed efficiently.

The MACH111 macrocell provides either registered or combinatorial outputs with programmable

polarity. If a registered configuration is chosen, the register can be configured as D-type or Ttype to help reduce the number of product terms. The register type decision can be made by

the designer or by the software. All macrocells can be connected to an I/O cell. If a buried

macrocell is desired, the internal feedback path from the macrocell can be used, which frees up

the I/O pin for use as an input.

Vantis offers software design support for MACH devices through its own development system

and device fitters integrated into third-party CAE tools. Platform support extends across PCs,

Sun and HP workstations under advanced operating systems such as Windows 3.1, Windows 95

and NT, SunOS and Solaris, and HPUX.

®

blocks interconnected by a programmable switch matrix.

Publication# 20420 Rev: B

Amendment/+1 Issue Date: June 1998

MACHXL

®

software is a complete development system for the PC, supporting Vantis' MACH

devices. It supports design entry with Boolean and behavioral syntax, state machine syntax and

truth tables. Functional simulation and static timing analysis are also included in this easy-touse system. This development system includes high-performance device fitters for all MACH

devices.

The same fitter technology included in MACHXL software is seamlessly incorporated into third-party

tools from leading CAE vendors such as Synario, Viewlogic, Mentor Graphics, Cadence and MINC.

Interface kits and MACHXL configurations are also available to support design entry and verification

with other leading vendors such as Synopsys, Exemplar, OrCAD, Synplicity and Model T echnology.

These MACHXL configurations and interfaces accept EDIF 2.0.0 netlists, generate JEDEC files for

MACH devices, and create industry-standard SDF , VIT AL-compliant VHDL and V erilog output files for

design simulation.

®

Vantis offers in-system programming support for MACH devices through its MACHPRO

software enabling MACH device programmability through JT AG compliant ports and easy-to-use

PC interface. Additionally, MACHPRO generated vectors work seamlessly with HP3070, GenRad

and Teradyne testers to program MACH devices or test them for connectivity.

All MACH devices are supported by industry standard programmers available from a number of

vendors. These programmer vendors include Advin Systems, BP Microsystems, Data I/O

Corporation, Hi-Lo Systems, SMS GmbH, Stag House, and System General.

2 MACH111-5/7/10/12/15

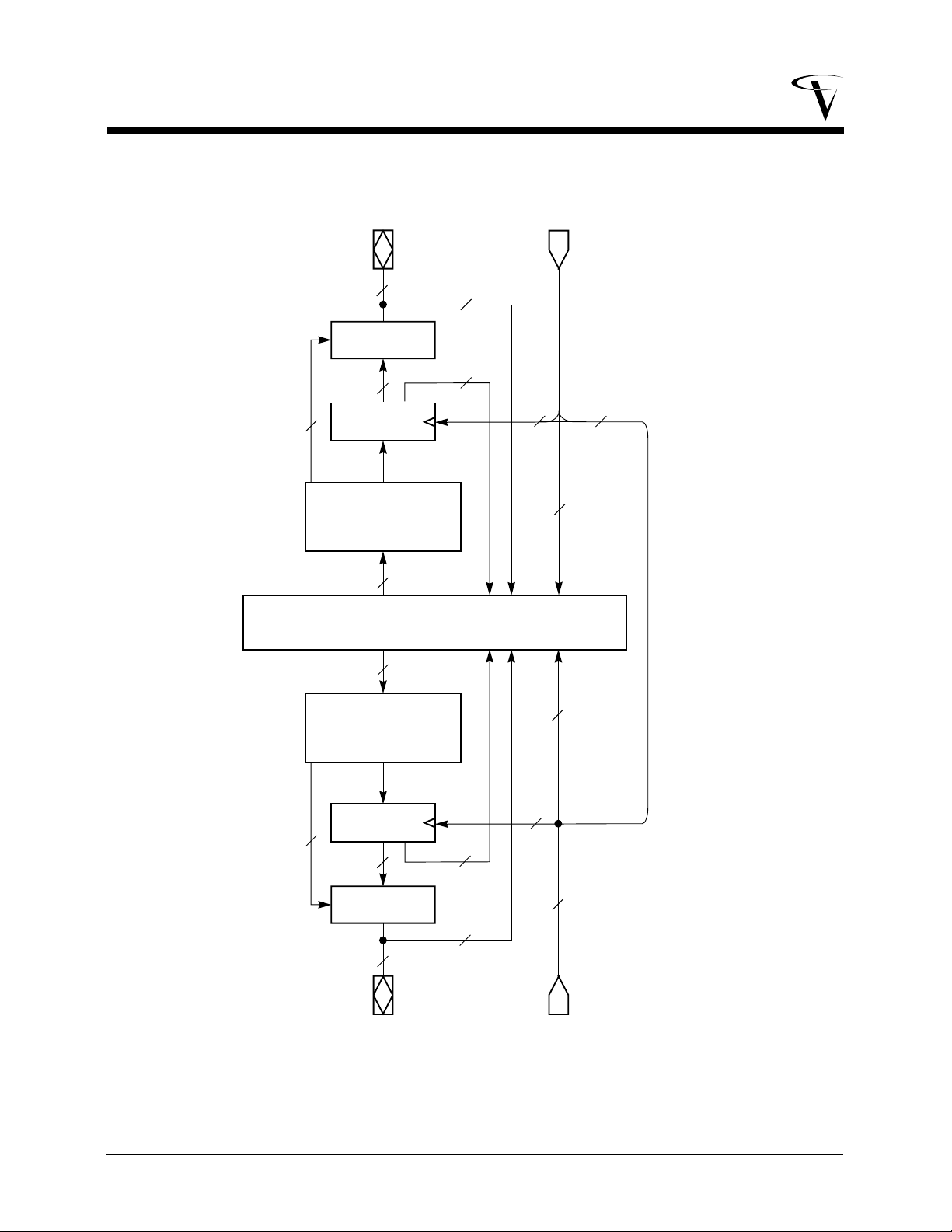

BLOCK DIAGRAM

Block A

I/O0 – I/O

I0-I1/CLK

15

I3-I4/CLK

0

2

4

OE

AND Logic Array

Logic Allocator

AND Logic Array

Logic Allocator

OE

16

I/O Cells

16

Macrocells

52 x 70

and

26

Switch Matrix

26

52 x 70

and

16

16

4

2

2

4

4

Macrocells

16

I/O Cells

16

I/O16 – I/O

Block B

16

16

31

4

2

CLK3/I

CLK1/I

5

2

20420B-1

MACH111-5/7/10/12/15 3

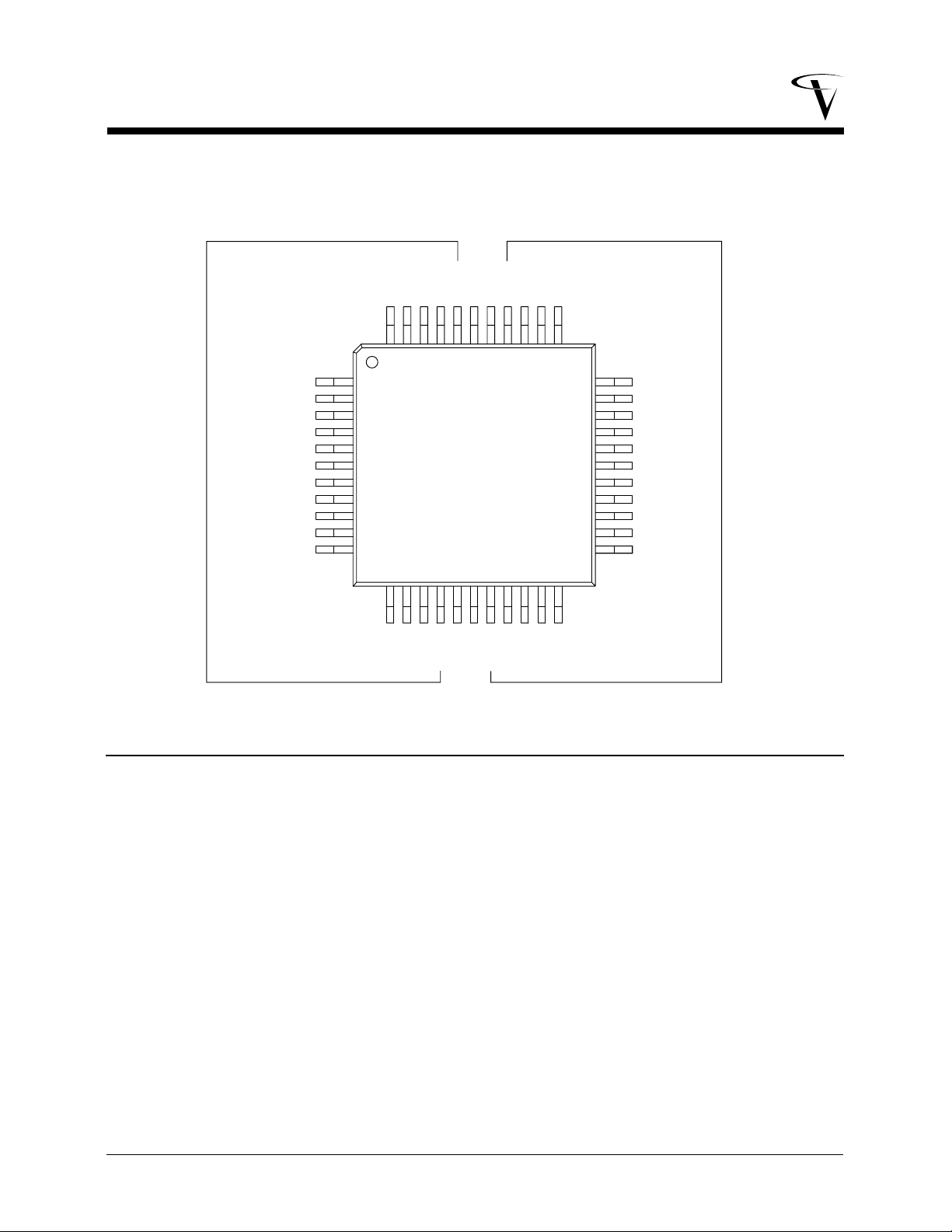

CONNECTION DIAGRAM

Top View

I/O4

I/O3

I/O2

I/O1

44-Pin PLCC

I/O0

GND

VCC

I/O31

I/O30

I/O29

I/O28

5

641

I/O5

I/O6

I/O7

CLK0/I1

Block A

Note:

Pin-compatible with the MACH211SP and MACH211.

GND

CLK1/I2

I/O8

I/O9

I/O10

I/O11

7

8

9

10

I0

11

12

13

14

15

16

17

19

18 27

I/O12

I/O13

PIN DESIGNATIONS

4

20

3

21

I/O14

2

22

I/O15

VCC

1

23

44

24

GND

43

25

I/O16

42

26

I/O17

I/O18

40

28

I/O19

39

38

37

36

35

34

33

32

31

30

29

I/O20

I/O27

I/O26

I/O25

I/O24

CLK3/I5

GND

CLK2/I4

I3

I/O23

I/O22

I/O21

Block B

20420B-2

CLK/I = Clock or Input

GND = Ground

I = Input

I/O = Input/Output

V

= Supply Voltage

CC

4 MACH111-5/7/10/12/15

CONNECTION DIAGRAM

Top View

I/O4

44-Pin TQFP

I/O3

I/O2

I/O1

I/O0

GND

VCC

I/O31

I/O30

I/O29

I/O28

I/O5

I/O6

I/O7

I0

CLK0/I1

GND

Block A

Note:

Pin-compatible with the MACH211SP.

CLK1/I2

I/O8

I/O9

I/O10

I/O11

PIN DESIGNATIONS

4443424140

1

2

3

4

5

6

7

8

9

10

11

1213141516

I/O12

I/O13

I/O14

VCC

I/O15

39

17

GND

38

373635

18

192021

I/O16

I/O17

I/O18

I/O19

34

33

32

31

30

29

28

27

26

25

24

23

22

I/O20

I/O27

I/O26

I/O25

I/O24

CLK3/I5

GND

CLK2/I4

I3

I/O23

I/O22

I/O21

Block B

20420B-3

CLK/I = Clock or Input

GND = Ground

I = Input

I/O = Input/Output

V

= Supply Voltage

CC

MACH111-5/7/10/12/15 5

ORDERING INFORMATION

Commercial Products

Vantis programmable logic products for commercial applications are available with several ordering options. The order number

(Valid Combination) is formed by a combination of:

MACH 111 -5 J C

FAMILY TYPE

MACH = Macro Array CMOS High-Speed

DEVICE NUMBER

111 = 32 Macrocells, 44 Pins,

Power-Down option,

Bus-Friendly Inputs

SPEED

-5 = 5 ns t

-7 = 7.5 ns t

-10 = 10 ns t

-12 = 12 ns t

-15 = 15 ns t

PD

PD

PD

PD

PD

Valid Combinations

MACH111-5

MACH111-7

MACH111-10

MACH111-12

MACH111-15

JC, VC

OPERATING CONDITIONS

C = Commercial (0°C to +70°C)

PACKAGE TYPE

J = 44-Pin Plastic Leaded Chip

Carrier (PL 044)

V = 44-Pin Thin Quad Flat Pack

(PQT044)

Valid Combinations

The Valid Combinations table lists configurations planned to

be supported in volume for this device. Consult the local

Vantis sales office to confirm availability of specific valid

combinations and to check on newly released combinations.

6 MACH111-5/7/10/12/15 (Com’l)

ORDERING INFORMATION

Industrial Products

Vantis programmable logic products for industrial applications are available with several ordering options. The order number

(Valid Combination) is formed by a combination of:

MACH 111 -7 J I

FAMILY TYPE

MACH = Macro Array CMOS High-Speed

DEVICE NUMBER

111 = 32 Macrocells, 44 Pins,

Power-Down option,

Bus-Friendly Inputs

SPEED

-7 = 7.5 ns t

-10 = 10 ns t

-12 = 12 ns t

-14 = 14 ns t

-18 = 18 ns t

PD

PD

PD

PD

PD

Valid Combinations

MACH111-7

MACH111-10

MACH111-12

MACH111-14

MACH111-18

OPERATING CONDITIONS

I = Industrial (–40

PACKAGE TYPE

J = 44-Pin Plastic Leaded Chip

Carrier (PL 044)

Valid Combinations

The Valid Combinations table lists configurations planned to

be supported in volume for this device. Consult the local

Vantis sales office to confirm availability of specific valid

combinations and to check on newly released combinations.

JI

°C to +85°C)

MACH111-7/10/12/14/18 (Ind) 7

FUNCTIONAL DESCRIPTION

The MACH111 consists of two PAL blocks connected by a switch matrix. There are 32 I/O pins

and 2 dedicated input pins feeding the switch matrix. These signals are distributed to the two

PAL blocks for efficient design implementation. There are four clock pins that can also be used

as dedicated inputs.

The PAL Blocks

Each PAL block in the MACH111 (Figure 1) contains a 64-product-term logic array, a logic

allocator, 16 macrocells, and 16 I/O cells. The switch matrix feeds each PAL block with 26 inputs.

This makes the PAL block look effectively like an independent “PALCE26V16.”

There are four additional output enable product terms in each P AL block. For purposes of output

enable, the 16 I/O cells are divided into 2 banks of 8 macrocells. Each bank is allocated two of

the output enable product terms.

An asynchronous reset product term and an asynchronous preset product term are provided for

flip-flop initialization. All flip-flops within the PAL block are initialized together.

The Switch Matrix

The MACH111 switch matrix is fed by the inputs and feedback signals from the P AL blocks. Each

P AL block provides 16 internal feedback signals and 16 I/O feedback signals. The switch matrix

distributes these signals back to the P AL blocks in an efficient manner that also provides for high

performance. The design software automatically configures the switch matrix when fitting a

design into the device.

The Product-term Array

The MACH111 product-term array consists of 64 product terms for logic use, and 6

special-purpose product terms. Four of the special-purpose product terms provide

programmable output enable; one provides asynchronous reset, and one provides asynchronous

preset. Two of the output enable product terms are used for the first eight I/O cells; the other

two control the last eight macrocells.

The Logic Allocator

The logic allocator in the MACH111 takes the 64 logic product terms and allocates them to the

16 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design

software automatically configures the logic allocator when fitting the design into the device.

Table 1 illustrates which product term clusters are available to each macrocell within a PAL

block. Refer to Figure 1 for cluster and macrocell numbers.

Table 1. Logic Allocation

Output Macrocell Available Clusters Output Macrocell Available Clusters

M

0

M

1

M

2

M

3

M

4

M

5

M

6

M

7

C

, C

0

C

, C

, C

0

1

C1, C2, C

C2, C3, C

C3, C4, C

C4, C5, C

C5, C6, C

C6, C

1

2

3

4

5

6

7

7

M

8

M

9

M

10

M

11

M

12

M

13

M

14

M

15

C

, C

8

9

, C9, C

C

8

C9, C10, C

C10, C11, C

C11, C12, C

C12, C13, C

C13, C14, C

C14, C

15

10

11

12

13

14

15

8 MACH111-5/7/10/12/15

The Macrocell

The MACH111 macrocells can be configured as either registered or combinatorial, with

programmable polarity. The macrocell provides internal feedback whether configured as

registered or combinatorial. The flip-flops can be configured as D-type or T-type, allowing for

product-term optimization.

The flip-flops can individually select one of four clock pins, which are also available as data inputs.

The registers are clocked on the LOW-to-HIGH transition of the clock signal. The flip-flops can also

be asynchronously initialized with the common asynchronous reset and preset product terms.

The I/O Cell

The I/O cell in the MACH111 consists of a three-state output buffer. The three-state buffer can

be configured in one of three ways: always enabled, always disabled, or controlled by a product

term. If product term control is chosen, one of two product terms may be used to provide the

control. The two product terms that are available are common to eight I/O cells. Within each

PAL block, two product terms are available for selection by the first eight three-state outputs;

two other product terms are available for selection by the last eight three-state outputs.

SpeedLocking for Guaranteed Fixed Timing

The unique MACH 1 & 2 architecture is designed for high performance—a metric that is met in

both raw speed, but even more importantly, guaranteed fixed speed. Using the design of the

central switch matrix, the MACH111 product offers the SpeedLocking feature, which allows a

stable fixed pin-to-pin delay, independent of logic paths, routing resources and design refits for

up to 12 product terms per output. Other non-Vantis CPLDs incur serious timing delays as

product terms expand beyond their typical 4 or 5 product-term limits. Speed and SpeedLocking

combine for continuous, high performance required in today's demanding designs.

Bus-Friendly Inputs and I/Os

The MACH111 inputs and I/Os include two inverters in series which loop back to the input. This

double inversion reinforces the state of the input and pulls the voltage away from the input

threshold voltage. Unlike a pull-up, this configuration cannot cause contention on a bus. For an

illustration of this configuration, please turn to the Input/Output Equivalent Schematics section.

PCI Compliant

The MACH111-5/7/10/12 is fully compliant with the PCI Local Bus Specification published by

the PCI Special Interest Group. The MACH111-5/7/10/12’s predictable timing ensures

compliance with the PCI AC specifications independent of the design.

Power-Down Mode

The MACH111 features a programmable low-power mode in which individual signal paths can be

programmed as low power. These low-power speed paths will be slightly slower than the

non-low-power paths. This feature allows speed critical paths to run at maximum frequency while

the rest of the paths operate in the low-power mode, resulting in power savings of up to 50%.

Safe for Mixed Supply Voltage System Designs

The MACH111 is safe for mixed supply voltage system designs. The 5-V device will not overdrive

3.3-V devices above the output voltage of 3.3 V , while it accepts inputs from other 3.3-V devices.

Thus, the MACH111 provides easy-to-use mixed-voltage design compatibility.

MACH111-5/7/10/12/15 9

Loading...

Loading...