®

Embedded

AMD-K6™

Processors

BIOS Design Guide

Application Note

Publication # 23913 Rev: A Amendment/0

Issue Date: November 2000

© 2000 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced

Micro Devices, Inc. ("AMD") products. AMD makes no representations or

warranties with respect to the accuracy or completeness of the contents of this

publication and reserves the right to make changes to specifications and

product descriptions at any time without notice. No license, whether express,

implied, arising by estoppel or otherwise, to any intellectual property rights

is granted by this publication. Except as set forth in AMD’s Standard Terms

and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims

any express or implied warranty, relating to its products including, but not

limited to, the implied warranty of merchantability, fitness for a particular

purpose, or infringement of any intellectual property right.

AMD’s products are not designed, intended, authorized or warranted for use

as components in systems intended for surgical implant into the body, or in

other applications intended to support or sustain life, or in any other

application in which the failure of AMD’s product could create a situation

where personal injury, death, or severe property or environmental damage

may occur. AMD reserves the right to discontinue or make changes to its

products at any time without notice.

Trademarks

AMD, the AMD logo, and combinations thereof, AMD-K6, 3DNow!, E86, AMD PowerNow!, and Super7 are

trademarks, and FusionE86 is a service mark of Advanced Micro Devices, Inc.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their

respective companies.

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xi

Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Processor Models and Steppings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

AMD-K6™E Embedded Processor . . . . . . . . . . . . . . . . . . . . . . . 3

AMD-K6™-2 Processor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

AMD-K6™-2E Embedded Processor. . . . . . . . . . . . . . . . . . . . . . 4

AMD-K6™-2E+ Embedded Processor. . . . . . . . . . . . . . . . . . . . . 4

AMD-K6™-III Processor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

AMD-K6™-IIIE+ Embedded Processor . . . . . . . . . . . . . . . . . . . 5

BIOS Consideration Checklist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

CPUID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

CPU Speed Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Model-Specific Registers (MSRs) . . . . . . . . . . . . . . . . . . . . . . . . 6

Cache Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

SMM Issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

States after RESET and INIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Register States after RESET and INIT . . . . . . . . . . . . . . . . . . . 8

Processor State after INIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Built-In Self-Test (BIST) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

CPUID Identification Algorithms . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

System Management Mode (SMM) . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

State-Save Map Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

I/O Trap Dword Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Model-Specific Registers Overview . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Standard Model-Specific Registers (All Models) . . . . . . . . . . 16

Model 7 and Model 8/[7:0] Registers. . . . . . . . . . . . . . . . . . . . . . . . . . 17

Extended Feature Enable Register (EFER) . . . . . . . . . . . . . . 18

Write Handling Control Register (WHCR) . . . . . . . . . . . . . . . 19

SYSCALL/SYSRET Target Address Register (STAR) . . . . . . 22

Contents iii

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Model 8/[F:8] Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Extended Feature Enable Register (EFER) . . . . . . . . . . . . . . 24

Write Handling Control Register (WHCR) . . . . . . . . . . . . . . . 27

UC/WC Cacheability Control Register (UWCCR) . . . . . . . . . 30

Processor State Observability Register (PSOR) . . . . . . . . . . . 34

Page Flush/Invalidate Register (PFIR) . . . . . . . . . . . . . . . . . . 36

Model 9 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Extended Feature Enable Register (EFER) . . . . . . . . . . . . . . 39

Level-2 Cache Array Access Register (L2AAR) . . . . . . . . . . . 40

Model D Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Processor State Observability Register (PSOR)

(Low-Power Versions) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Level-2 Cache Array Access Register (L2AAR) . . . . . . . . . . . 48

Enhanced Power Management Register (EPMR)

(Low-Power Versions) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

EPM 16-Byte I/O Block (Low-Power Versions Only). . . . . . . . 55

Embedded AMD Processor Recognition. . . . . . . . . . . . . . . . . . . . . . . 57

CPUID Instruction Overview . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Testing for the CPUID Instruction . . . . . . . . . . . . . . . . . . . . . . 58

Using CPUID Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Identifying the Processor’s Vendor . . . . . . . . . . . . . . . . . . . . . 60

Testing For Extended Functions . . . . . . . . . . . . . . . . . . . . . . . 61

Determining the Processor Signature . . . . . . . . . . . . . . . . . . . 61

Identifying Supported Features . . . . . . . . . . . . . . . . . . . . . . . . 63

Determining Instruction Set Support. . . . . . . . . . . . . . . . . . . . 64

Detection Algorithm for Determining Instruction Set

Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

AMD Processor Signature (Extended Function). . . . . . . . . . . 66

Displaying the Processor’s Name . . . . . . . . . . . . . . . . . . . . . . . 66

Displaying Cache Information . . . . . . . . . . . . . . . . . . . . . . . . . 67

Determining AMD PowerNow!™ Technology Information . . 67

Sample Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

New AMD-K6™ Processor Instructions. . . . . . . . . . . . . . . . . . . . . . . . 68

Additional Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

iv Contents

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Software Timing Dependencies Relative to Memory

Controller Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Pipelining Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Read-Only Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Appendix A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

CPUID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Standard Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Extended Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Cache Associativity Field Definitions . . . . . . . . . . . . . . . . . . . 80

Appendix B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Values Returned by the CPUID Instruction . . . . . . . . . . . . . . 81

Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Contents v

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

vi Contents

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

List of Figures

Figure 1. CPUID Instruction Flow Chart . . . . . . . . . . . . . . . . . . . . . 12

Figure 2. Extended Feature Enable Register (EFER)

(Models 7 and 8/[7:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 3. Write Handling Control Register (WHCR)

(Models 7 and 8/[7:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 4. SYSCALL/SYSRET Target Address Register (STAR)

(Models 8, 9, and D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 5. Extended Feature Enable Register (EFER)

(Model 8/[F:8]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 6. Write Handling Control Register (WHCR)

(Models 8/[F:8], 9, and D) . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 7. UC/WC Cacheability Control Register (UWCCR)

(Models 8/[F:8], 9, and D) . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 8. Processor State Observability Register (PSOR)

(Models 8/[F:8], 9, and Standard-Power D) . . . . . . . . . . . 34

Figure 9. Page Flush/Invalidate Register (PFIR)

(Models 8/[F:8], 9, and D) . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 10. Extended Feature Enable Register (EFER)

(Models 9 and D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 11. L2 Cache Organization (AMD-K6™-III Processor) . . . . . 40

Figure 12. L2 Cache Sector and Line Organization . . . . . . . . . . . . . 41

Figure 13. L2 Tag or Data Location (AMD-K6™-III

Processor)—EDX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 14. L2 Data—EAX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 15. L2 Tag Information (AMD-K6™-III Processor)—EAX . . 43

Figure 16. LRU Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 17. Processor State Observability Register (PSOR)

(Model D Low-Power Versions) . . . . . . . . . . . . . . . . . . . . 46

Figure 18. L2 Cache Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 19. L2 Cache Sector and Line Organization

(same as Figure 12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

List of Figures vii

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Figure 20. L2 Tag or Data Location (AMD-K6™-2E+

Processor)—EDX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 21. L2 Tag or Data Location (AMD-K6™-IIIE+

Processor)—EDX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 22. L2 Data—EAX (same as Figure 14) . . . . . . . . . . . . . . . . . 51

Figure 23. L2 Tag Information (AMD-K6™-2E+

Processor)—EAX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 24. L2 Tag Information (AMD-K6™-IIIE+

Processor)—EAX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 25. LRU Byte (same as Figure 16) . . . . . . . . . . . . . . . . . . . . . 53

Figure 26. Enhanced Power Management Register (EPMR)

(Low-Power Model D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 27. EPM 16-Byte I/O Block (Low-Power Model D) . . . . . . . . 55

Figure 28. Bus Divisor and Voltage ID Control (BVC) Field

(Low-Power Model D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 29. Contents of EAX Register Returned by Function 1 . . . . 62

Figure 30. Contents of EAX Register Returned by

Extended Function 8000_0001h . . . . . . . . . . . . . . . . . . . . 66

viii List of Figures

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

List of Tables

Table 1. Features of the AMD-K6™ Processor Family . . . . . . . . . . 2

Table 2. AMD-K6™E Processor (Model 7) and AMD-K6™ Processor

(Model 8/[7:0]) State after RESET . . . . . . . . . . . . . . . . . . . 8

Table 3. AMD-K6™ Processor (Model 8/[F:8]) and AMD-K6™-2E

Processor (Model 8/[F:8]) State after RESET . . . . . . . . . . 8

Table 4. AMD-K6™-2E+ (Model D), AMD-K6™-III (Model 9), and

AMD-K6™-IIIE+ Processors (Model D)

State after RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 5. Recommended Boot Strings for AMD-K6™ Processors . 11

Table 6. AMD-K6™ Processor I/O Trap Dword Configuration

at Offset FFA4h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 7. Summary by Register of MSR Differences within the

AMD-K6™ Family. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 8. Summary by Model of MSR Differences within the

AMD-K6™ Family. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 9. Model-Specific Registers Supported by Models 7 and

8/[7:0]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 10. Extended Feature Enable Register (EFER) Definition

(Models 7 and 8/[7:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 11. SYSCALL/SYSRET Target Address Register (STAR)

Definition (Models 8, 9, and D). . . . . . . . . . . . . . . . . . . . . 22

Table 12. Model-Specific Registers Supported by Model 8/[F:8]. . 23

Table 13. Extended Feature Enable Register (EFER)

Definition (Model 8/[F:8]) . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 14. Write Ordering and Performance Settings for EFER

Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 15. WC/UC Memory Type for UWCCR Register . . . . . . . . . . 31

Table 16. Valid Masks and Range Sizes for UWCCR Register. . . . 32

Table 17. Processor-to-Bus Clock Ratios (Models 8/[F:8] and 9) . . 35

List of Tables ix

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Table 18. Processor-to-Bus Clock Ratios

(Model Standard-Power D) . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 19. Model-Specific Registers Supported by Model 9 . . . . . . 38

Table 20. Extended Feature Enable Register (EFER) Definition

(Models 9 and D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 21. Tag versus Data Selector . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 22. Model-Specific Registers Supported by Model D . . . . . . 45

Table 23. Processor-to-Bus Clock Ratios (Low-Power Model D) . . . 47

Table 24. Tag versus Data Selector (same as Table 21). . . . . . . . . . 51

Table 25. Enhanced Power Management Register (EPMR)

Definition (Low-Power Model D) . . . . . . . . . . . . . . . . . . . 54

Table 26. EPM 16-Byte I/O Block Definition (Low-Power Model D)55

Table 27. Bus Divisor and Voltage ID Control (BVC) Definition

(Low-Power Model D). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 28. CPUID Functions in AMD-K6™ Processors. . . . . . . . . . . 60

Table 29. Processor Signatures for AMD-K6™ Processors . . . . . . . 62

Table 30. Standard and Extended Feature Bits . . . . . . . . . . . . . . . . 63

Table 31. Standard Feature Flag Descriptions. . . . . . . . . . . . . . . . . 74

Table 32. Extended Feature Flag Descriptions . . . . . . . . . . . . . . . . 76

Table 33. EBX Format Returned by Function 8000_0005h. . . . . . . 78

Table 34. ECX Format Returned by Function 8000_0005h. . . . . . . 78

Table 35. EDX Format Returned by Function 8000_0005h . . . . . . 78

Table 36. ECX Format Returned by Function 8000_0006h. . . . . . . 79

Table 37. EDX Format Returned by Function 8000_0007h . . . . . . 79

Table 38. Associativity Values for L2 Cache . . . . . . . . . . . . . . . . . . 80

Table 39. CPUID Values Returned by AMD-K6™ Processors . . . . 81

x List of Tables

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Revision History

Date Rev Description

November 2000 A Initial public release.

Revision History xi

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

xii Revision History

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Application Note

Embedded AMD-K6™

Processors BIOS Design Guide

Introduction

This document highlights the BIOS modifications required to

fully support the AMD-K6™ processors used by AMD’s

embedded customers. The information in this application note

pertains to the following processors in the AMD-K6 family:

■ AMD-K6E embedded processor

■ AMD-K6-2 processor

■ AMD-K6-2E embedded processor

■ AMD-K6-2E+ embedded processor

■ AMD-K6-III processor

■ AMD-K6-IIIE+ embedded processor

There can be more than one way to implement the functionality

detailed in this document, and the information provided is for

demonstration purposes.

All referenced AMD-K6 processor documents can be found on

the AMD website at http://www.amd.com/.

Audience

It is assumed that the reader has a solid understanding of the

x86 processors, the x86 architecture, and programming

requirements.

Introduction 1

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Processor Models and Steppings

Four models within the AMD-K6 family of processors—models

7, 8, 9, and D—are discussed in this document.

For most models, feature and function detection can be

determined by reading the standard and extended feature bits

by executing the CPUID instruction. However, for certain

models, it is necessary to check the stepping—by executing the

CPUID instruction—to determine specific function support.

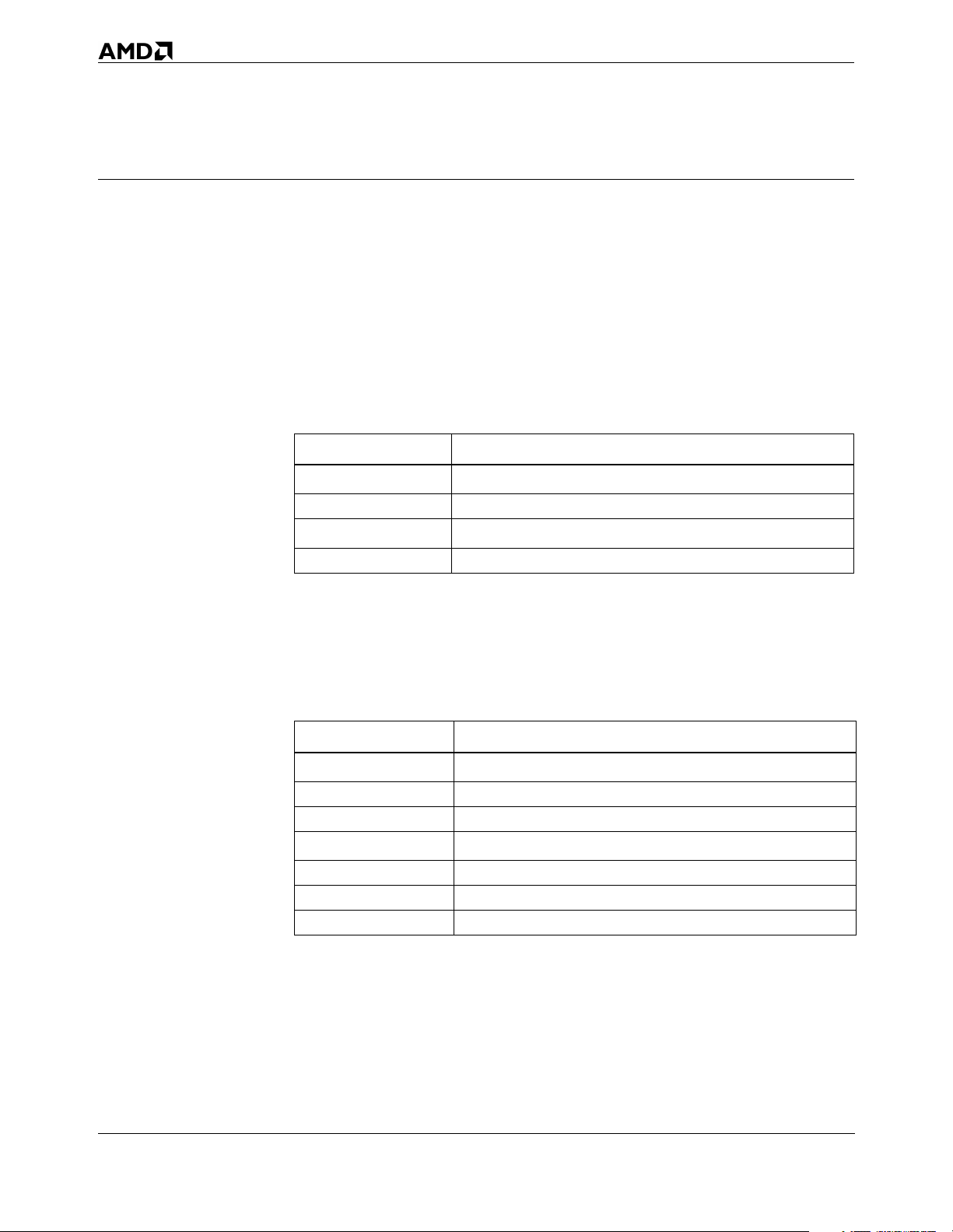

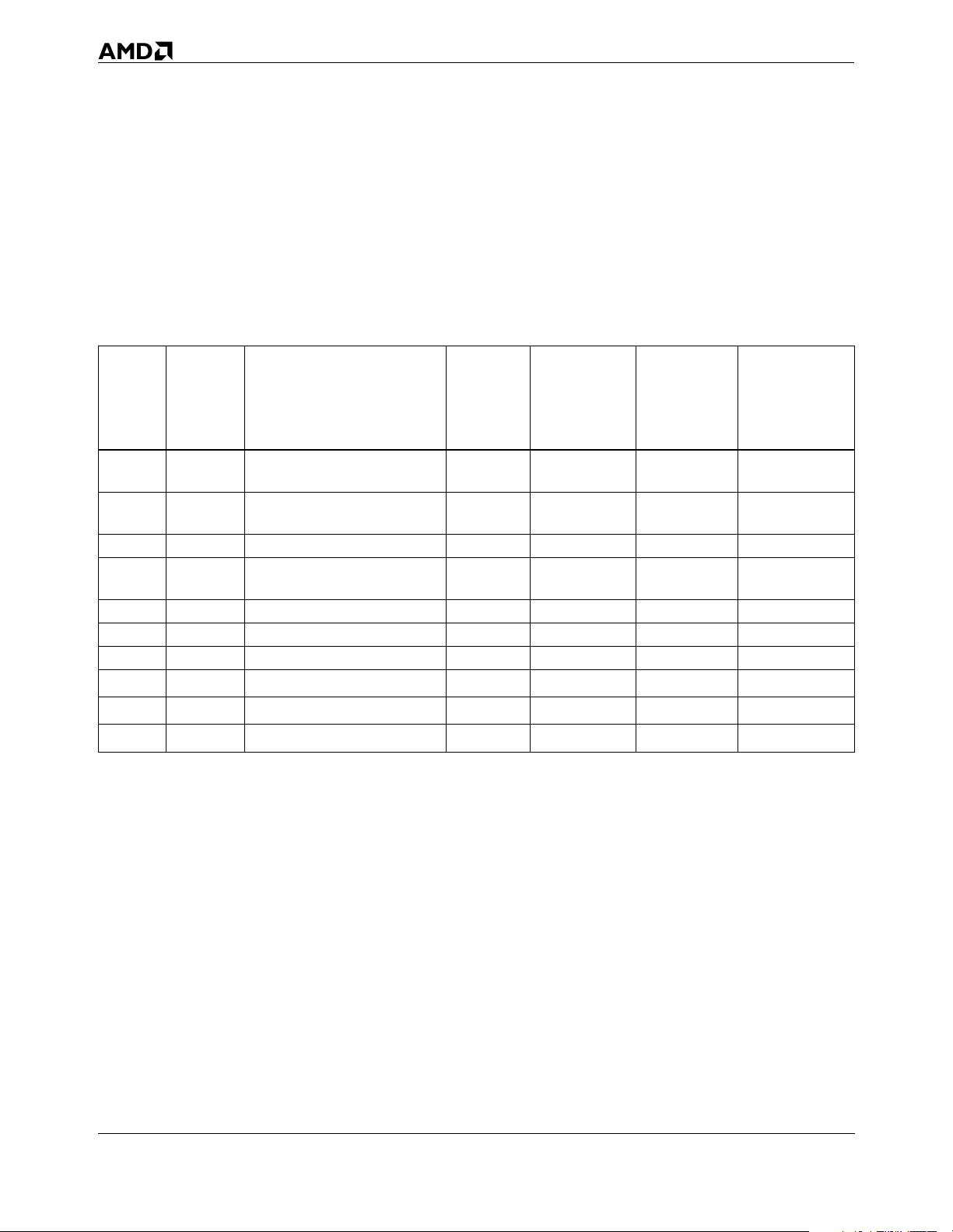

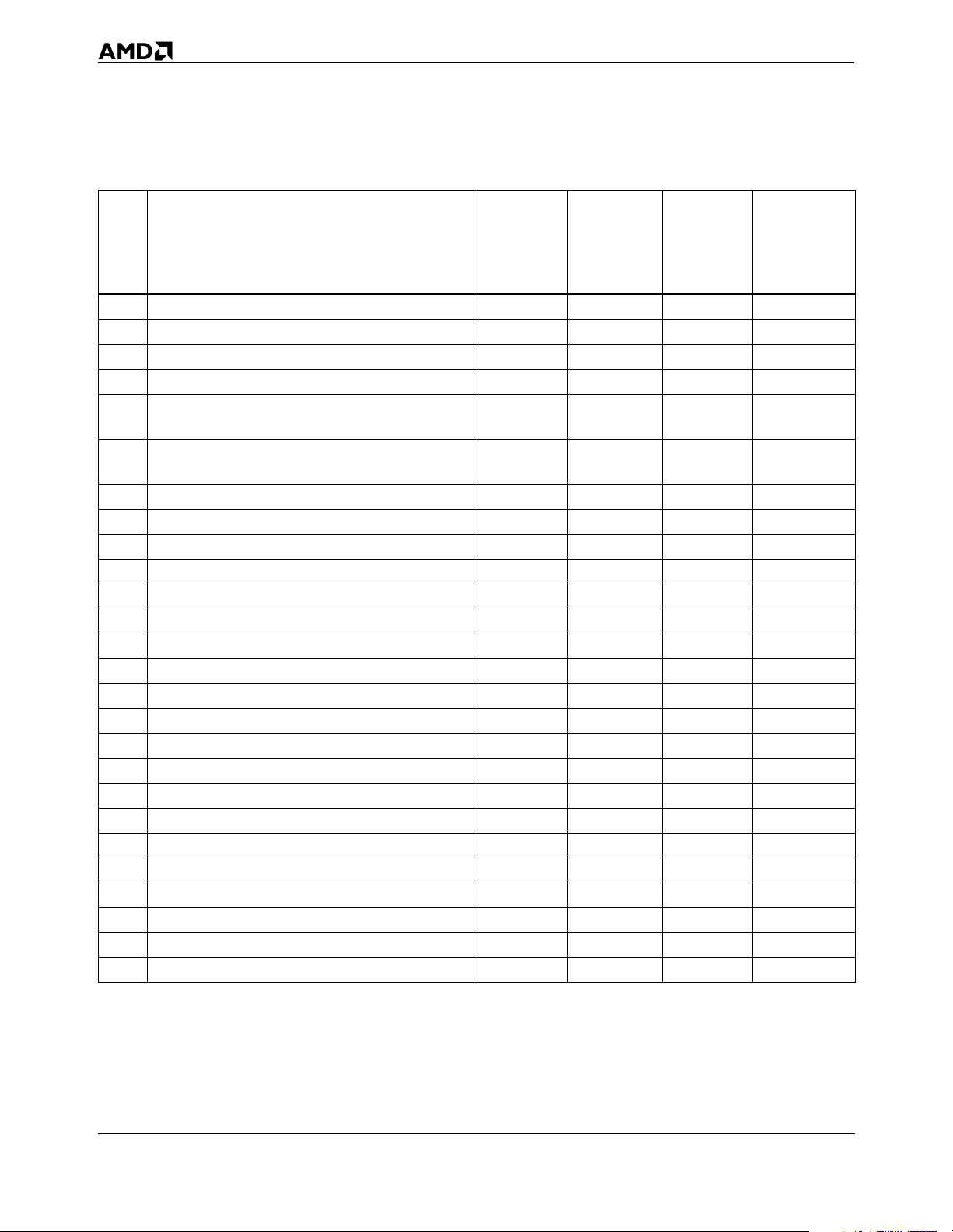

Table 1 shows the features of each model and stepping of the

AMD-K6 processor family.

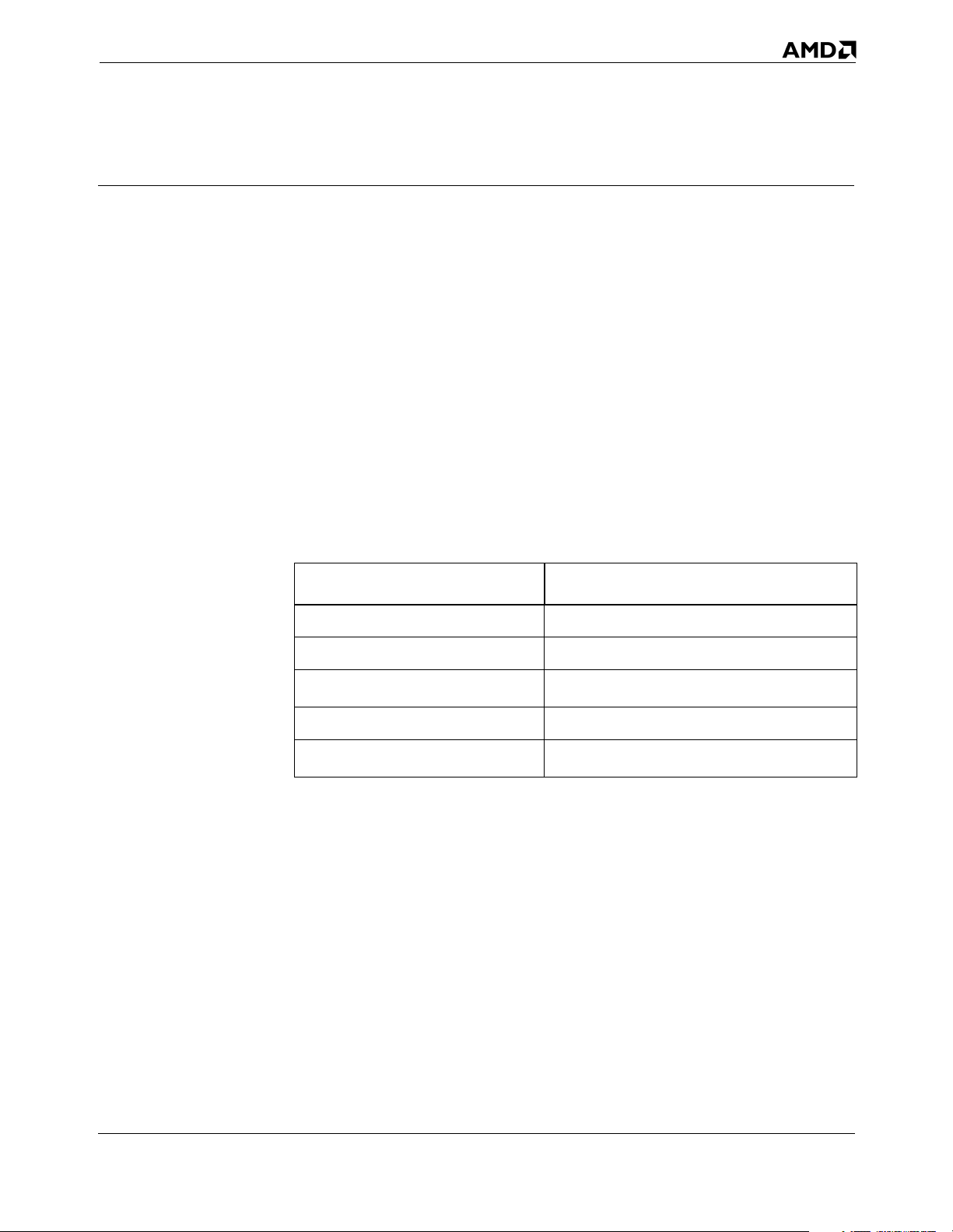

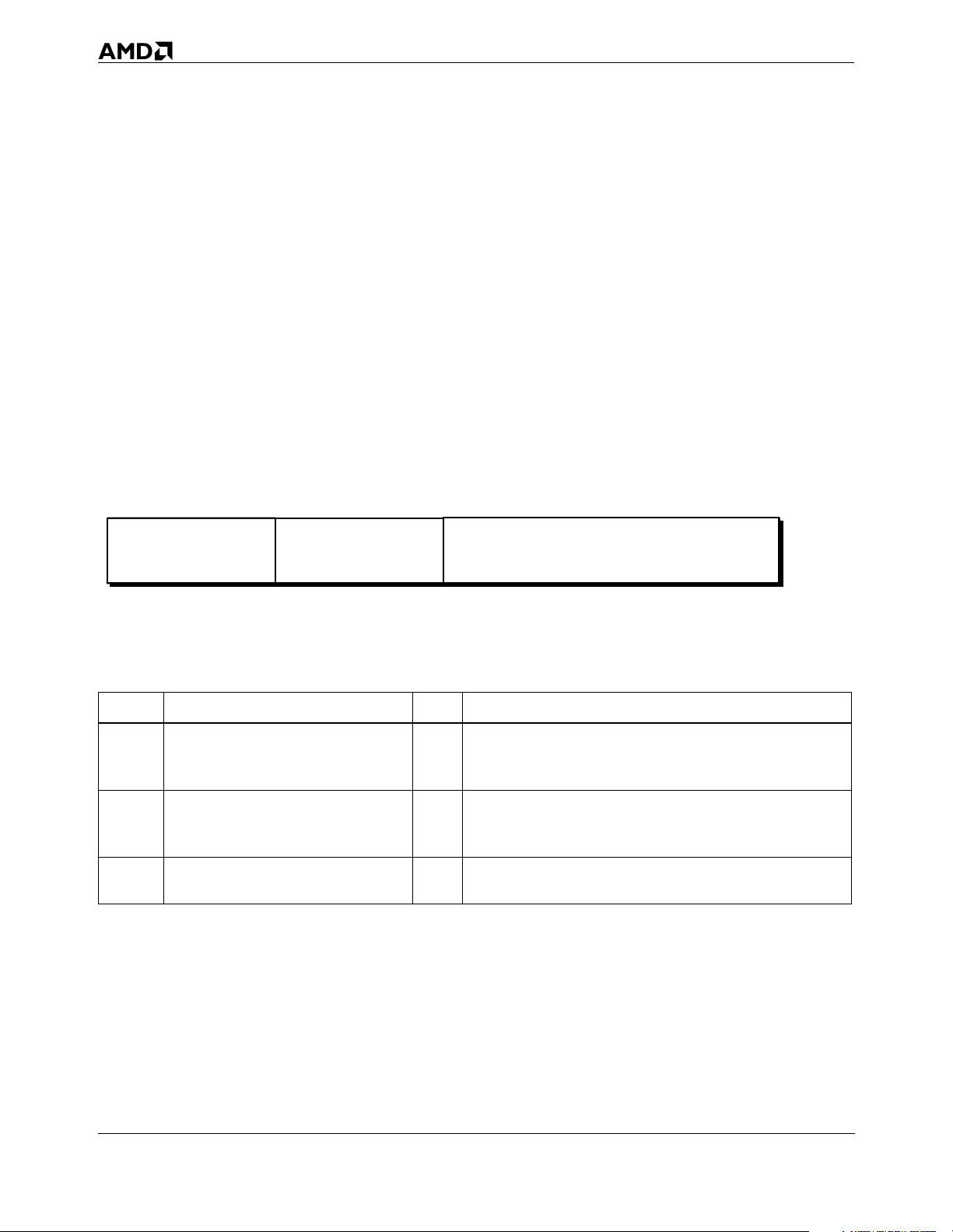

Table 1. Features of the AMD-K6™ Processor Family

Processor

AMD-K6E 7 0.25 6

AMD-K6-2 8/[7:0] 0.25 7 Yes

AMD-K6-2 and

AMD-K6-2E

AMD-K6-2E+ D/[7:4] 0.18

AMD-K6-III 9/[3:0] 0.25

AMD-K6-IIIE+ D/[3:0] 0.18

Notes:

1. Refer to “Model-Specific Registers Overview” on page 14 for more information.

2. Model 8/[F:8] defines the bits and fields in the Write Handling Control Register (WHCR) and Extended Feature Enable Register (EFER)

differently from the models 7 and 8/[7:0].

3. This model implements the same ten MSRs as the Model 8/[F:8]. With the exception of bit 4 (L2D) in the EFER register, the bits and

fields within these ten MSRs are defined identically.

4. Low-power versions implement one additional register to support AMD PowerNow!™ technology.

5. AMD PowerNow! technology is supported on low-power versions of these processors only.

Model/

Stepping

8/[F:8] 0.25

Process (in

microns)

Number

of MSRs

2

10

3,4

11

3

11

3,4

11

3DNow!™

1

Instructions

3DNow!

Extensions

Yes

Yes Yes

Yes

Yes Yes

AMD PowerNow!™

Technology

5

Yes

5

Yes

L2

Cache

128 Kbytes

256 Kbytes

The descriptions in the remainder of this section provide more

detailed information on the AMD-K6 processor family

members, and the models and steppings that comprise each

member.

Table 7 on page 14 and Table 8 on page 15 summarize the MSR

differences between the models and steppings of the AMD-K6

family of processors.

2 Processor Models and Steppings

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

AMD-K6™E Embedded Processor

Model 7 Model 7 is the first processor manufactured in the 0.25-micron

process.

■ Model 7 supports six model-specific registers (MSRs).

AMD-K6™-2 Processor

Some important features supported by the AMD-K6-2 processor

include the 3DNow!™ instruction set and a 100-MHz processor

bus.

Model 8/[7:0] Model 8/[7:0] is any of eight possible model/steppings—models

8/0, 8/1, 8/2, 8/3, 8/4, 8/5, 8/6, or 8/7. Model 8/[7:0] is

manufactured in the 0.25-micron process and was the original

version of the AMD-K6-2 available as a desktop product.

■ Model 8/[7:0] implements the same six MSRs as the Model 7,

and the bits and fields within these six MSRs are defined

identically.

■ Model 8/[7:0] also implements the SYSCALL/SYSRET

Target Address Register (STAR) MSR for a total of seven

MSRs.

Model 8/[F:8] Model 8/[F:8] is any of eight possible model/steppings—models

8/8, 8/9, 8/A, 8/B, 8/C, 8/D, 8/E, or 8/F. Model 8/[F:8] is

manufactured in the 0.25-micron process.

■ Model 8/[F:8] implements the same six MSRs as the models

7 and 8/[7:0], but the bits and fields within two of these

MSRs—WHCR and EFER—are not defined identically.

■ Also, Model 8/[F:8] supports the STAR MSR and three

additional MSRs, for a total of ten MSRs.

Processor Models and Steppings 3

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

AMD-K6™-2E Embedded Processor

The AMD-K6-2E processor also supports the 3DNow!

instruction set and a 100-MHz processor bus.

Model 8/[F:8] Model 8/[F:8] is any of eight possible model/steppings—models

8/8, 8/9, 8/A, 8/B, 8/C, 8/D, 8/E, or 8/F. Model 8/[F:8] is

manufactured in the 0.25-micron process.

■ Model 8/[F:8] implements the same six MSRs as the models

7 and 8/[7:0], but the bits and fields within two of these

MSRs—WHCR and EFER—are not defined identically.

■ Also, Model 8/[F:8] supports the STAR MSR and three

additional MSRs, for a total of ten MSRs.

AMD-K6™-2E+ Embedded Processor

In addition to supporting the 3DNow! instruction set and a 100MHz processor bus, the AMD-K6-2E+ processor contains a 128Kbyte backside L2 cache. It also supports the 3DNow! DSP

instructions extensions. Low-power versions of the processor

support AMD PowerNow!™ technology.

Model D/[7:4] Model D/[7:4] is any of four possible model/steppings—models

D/4, D/5, D/6, or D/7. Model D/[7:4] is manufactured in the 0.18micron process.

■ Model D/[7:4] implements the same ten MSRs as the Model

8/[F:8]. With the exception of bit 4 (L2D) in the EFER

register, the bits and fields within these ten MSRs are

defined identically for standard-power versions. The PSOR

register is defined differently for low-power versions.

■ Model D/[7:4] supports an additional MSR, the Level-2

Cache Array Access Register (L2AAR), for a total of eleven

MSRs.

■ Low-power versions of Model D/[7:4] support an additional

MSR, the Enhanced Power Management Register (EPMR),

for a total of twelve MSRs.

4 Processor Models and Steppings

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

AMD-K6™-III Processor

In addition to supporting the 3DNow! instruction set and a 100MHz processor bus, the AMD-K6-III processor contains a 256Kbyte backside L2 cache.

Model 9/[3:0] Model 9/[3:0] is any of four possible model/steppings—models

9/0, 9/1, 9/2, or 9/3. Model 9/[3:0] is manufactured in the 0.25micron process.

■ Model 9/[3:0] implements the same ten MSRs as the Model

8/[F:8]. With the exception of bit 4 (L2D) in the EFER

register, the bits and fields within these ten MSRs are

defined identically.

■ Model 9/[3:0] supports one additional MSR for a total of

eleven MSRs.

AMD-K6™-IIIE+ Embedded Processor

In addition to supporting the 3DNow! instruction set and a 100MHz processor bus, the AMD-K6-IIIE+ processor contains a 256Kbyte backside L2 cache. It also supports the 3DNow! DSP

instruction extensions. Low-power versions of the processor

support AMD PowerNow! technology.

Model D/[3:0] Model D/[3:0] is any of four possible model/steppings—models

D/0, D/1, D/2, or D/3. Model D/[3:0] is manufactured in the 0.18micron process.

■ Model D/[3:0] implements the same ten MSRs as the Model

8/[F:8]. With the exception of bit 4 (L2D) in the EFER

register, the bits and fields within these ten MSRs are

defined identically for standard-power versions. The PSOR

register is defined differently for low-power versions.

■ Model D/[7:4] supports an additional MSR, the Level-2

Cache Array Access Register (L2AAR), for a total of eleven

MSRs.

■ Low-power versions of Model D/[7:4] support an additional

MSR, the Enhanced Power Management Register (EPMR),

for a total of twelve MSRs.

Processor Models and Steppings 5

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

BIOS Consideration Checklist

CPUID

■ Use the CPUID instruction to properly identify the

processor. For information on the CPUID instruction, see

“CPUID Instruction Overview” on page 57.

■ Determine the processor model, stepping, and features

using functions 0000_0001h and 8000_0001h of the CPUID

instruction.

■ Display the processor name (BIOS boot strings) as described

in “CPUID Identification Algorithms” on page 11.

CPU Speed Detection

■ Use speed detection algorithms that do not rely on

repetitive instruction sequences.

■ Use the Time Stamp Counter (TSC) to ‘clock’ a timed

operation and compare the result to the real-time clock

(RTC) to determine the operating frequency. See the CPU

Speed Determination Program available on the AMD website

at http://www.amd.com/products/cpg/bin/.

■ Display the recommended BIOS boot string as shown in

Table 5 on page 11.

Model-Specific Registers (MSRs)

■ Only access MSRs implemented in the processor.

■ Enable write allocation by programming the Write Handling

Control Register (WHCR). See “Write Handling Control

Register (WHCR)” on page 19 and page 27, and the

Implementation of Write Allocate in the K86™ Processors

Application Note, order# 21326 for more information.

Note: The WHCR register as defined in models 7 and 8/[7:0] is

implemented differently in models 8/[F:8], 9, and D.

■ For the AMD-K6-2E, AMD-K6-2E+, AMD-K6-III, and

AMD-K6-IIIE+ processors, utilize the information provided

in the Processor State Observability Register (PSOR) to

display the correct processor bus frequency.

6 BIOS Consideration Checklist

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Cache Testing

■ The AMD-K6 family of processors does not contain MSRs to

allow for testing of the L1 cache. However, the AMD-K6-2E+,

AMD-K6-III, and AMD-K6-IIIE+ processors do contain an

MSR that allows for testing of their L2 caches. This MSR is

called L2AAR, and it is described in “Level-2 Cache Array

Access Register (L2AAR)” on page 40.

SMM Issues

■ The System Management Mode (SMM) functionality of the

processor is the same as the Pentium® processor.

■ Implement the processor SMM state-save area in a similar

manner as Pentium processors except for the IDT Base and

possibly Pentium processor-reserved areas. See “System

Management Mode (SMM)” on page 13 for more

information.

BIOS Consideration Checklist 7

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

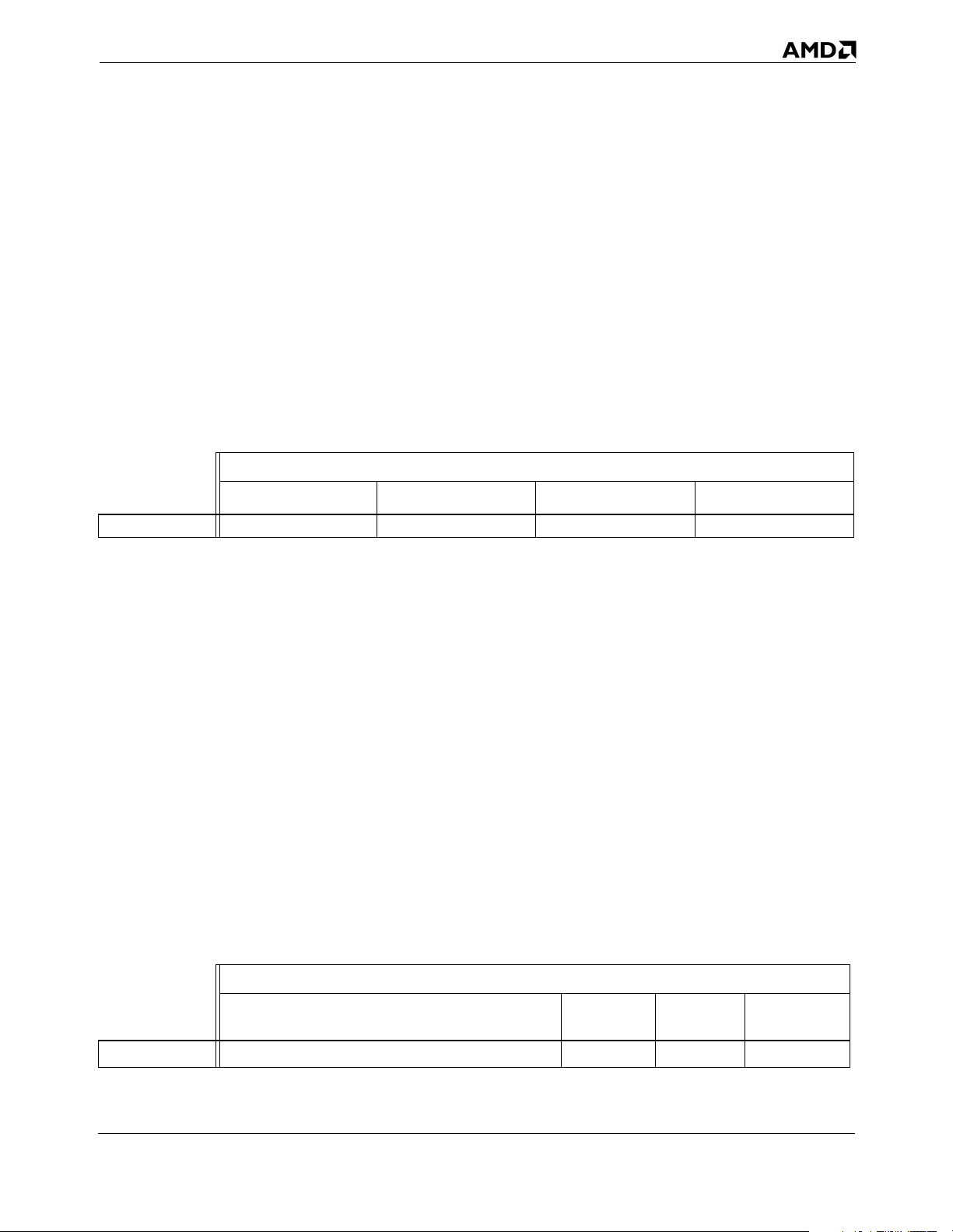

States after RESET and INIT

Register States after RESET and INIT

After the processor has completed its initialization following

the recognition of an asserted RESET or INIT signal, the states

of all architecture registers and MSRs are compatible with

those of Pentium processors. Differences are listed in Table 2

through Table 4.

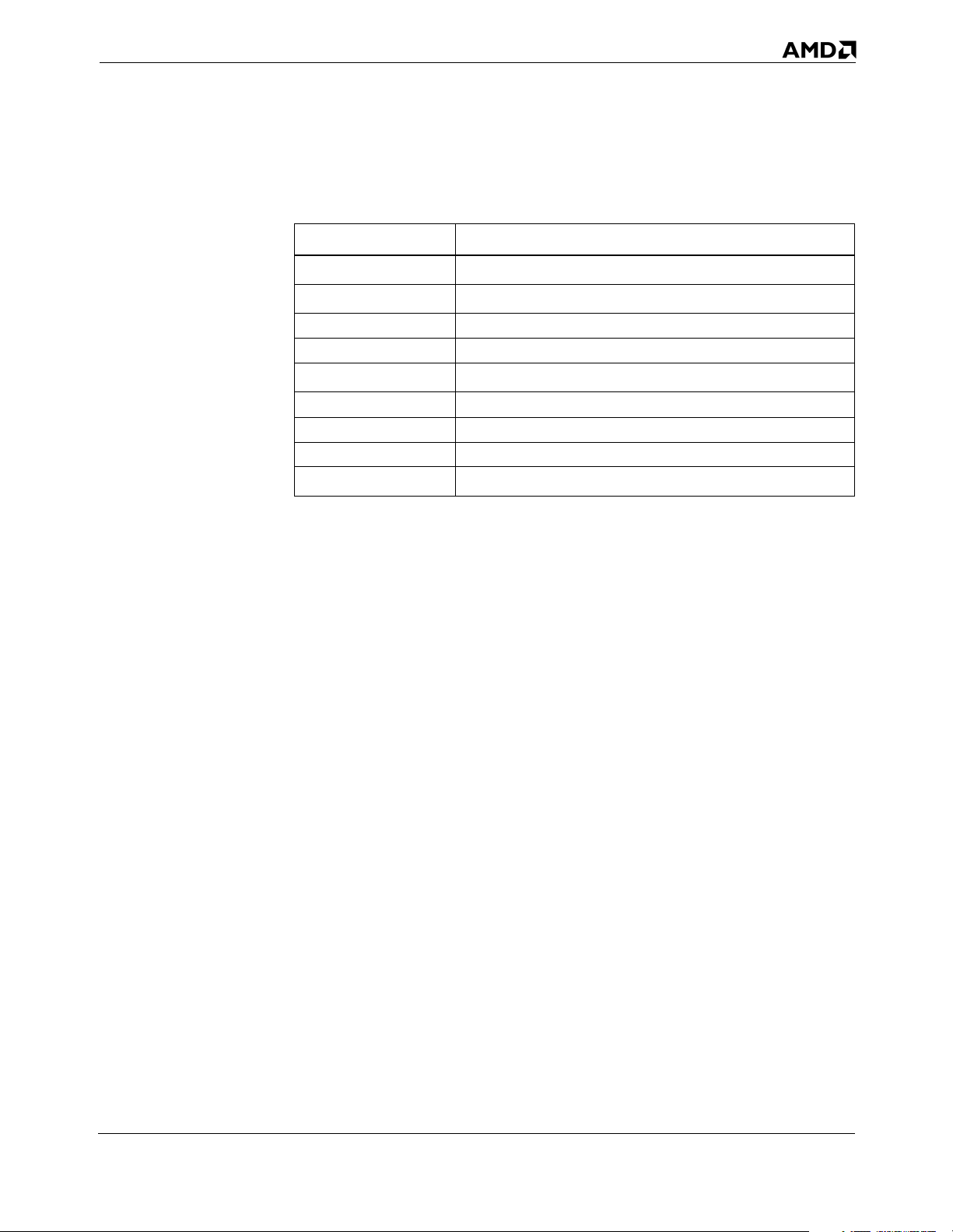

Table 2. AMD-K6™E Processor (Model 7) and AMD-K6™ Processor (Model

8/[7:0]) State after RESET

Register RESET State

EDX

EFER 0000_0000_0000_0000h

2

STAR

WHCR 0000_0000_0000_0000h

0000_05MSh

0000_0000_0000_0000h

1

Notes:

1. “M” represents the Model and “S” represents the Stepping.

2. Processor Model 7 does not support the STAR register.

Table 3. AMD-K6™ Processor (Model 8/[F:8]) and AMD-K6™-2E Processor

(Model 8/[F:8]) State after RESET

Register RESET State

EDX

EFER 0000_0000_0000_0002h

PFIR 0000_0000_0000_0000h

PSOR

STAR 0000_0000_0000_0000h

UWCCR 0000_0000_0000_0000h

WHCR 0000_0000_0000_0000h

Notes:

1. “M” represents the Model and “S” represents the Stepping.

2. “B” represents PSOR[3:0], where PSOR[3] equals 0, and PSOR[2:0] is equal to the value of the

BF[2:0] signals sampled during the falling transition of RESET.

0000_05MSh

0000_0000_0000_01SBh

1

1,2

8 States after RESET and INIT

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Table 4. AMD-K6™-2E+ (Model D), AMD-K6™-III (Model 9), and

AMD-K6™-IIIE+ Processors (Model D) State after RESET

Register RESET State

EDX

2

EFER

L2AAR 0000_0000_0000_0000h

PFIR 0000_0000_0000_0000h

PSOR

STAR 0000_0000_0000_0000h

UWCCR 0000_0000_0000_0000h

WHCR 0000_0000_0000_0000h

4

EPMR

0000_05MSh

0000_0000_0000_0002h

0000_0000_0000_00SBh

0000_0000_0000_0000h

1

1,3

Notes:

1. “M” represents the Model and “S” represents the Stepping.

2. Because EFER[4] equals 0 after RESET, the L2 cache is enabled by default after RESET.

3. “B” represents PSOR[3:0], where PSOR[3] equals 0, and PSOR[2:0] is equal to the value of the

BF[2:0] signals sampled during the falling transition of RESET.

4. Supported on low-power versions only of Model D processors.

Processor State after INIT

The assertion of INIT causes the processor to empty its

pipelines, initialize most of its internal state, and branch to

address FFFF_FFF0h—the same instruction execution starting

point used after RESET. Unlike RESET, the processor

preserves the contents of its caches, the floating-point state, the

SMM base, MSRs, and the CD and NW bits of the CR0 register.

The edge-sensitive interrupts FLUSH# and SMI# are sampled

and preserved during the INIT process and are handled

accordingly after the initialization is complete. However, the

processor resets any pending NMI interrupt upon sampling

INIT asserted.

INIT can be used as an accelerator for 80286 code that requires

a reset to exit from protected mode back to real mode.

States after RESET and INIT 9

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Built-In Self-Test (BIST)

For all models of the AMD-K6 processor, BIST is run

unconditionally following the falling transition of RESET. The

results of the test are contained in the general-purpose register

EAX. If EAX contains 0000_0000h, then BIST was successful. If

the contents of EAX are non-zero, the BIST failed. The internal

resources tested during BIST include the following:

■ L1 instruction and data caches

■ L2 unified cache (models 9 and D only)

■ Instruction and data translation lookaside buffers (TLBs)

10 States after RESET and INIT

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

CPUID Identification Algorithms

The CPUID instruction provides information about the

processor (vendor, type, name, etc.) and its capabilities

(features). After detecting the processor and its capabilities,

software can be accurately tuned to the system for maximum

performance and benefit to users. For more detailed

information about using the CPUID instruction, see

“Embedded AMD Processor Recognition” on page 57.

To determine if the processor is enabled with AMD PowerNow!

technology, use CPUID function 8000_0007, as described on

page 79.

The recommended boot strings (or processor names) to be

displayed for AMD-K6 processors are shown in Table 5.

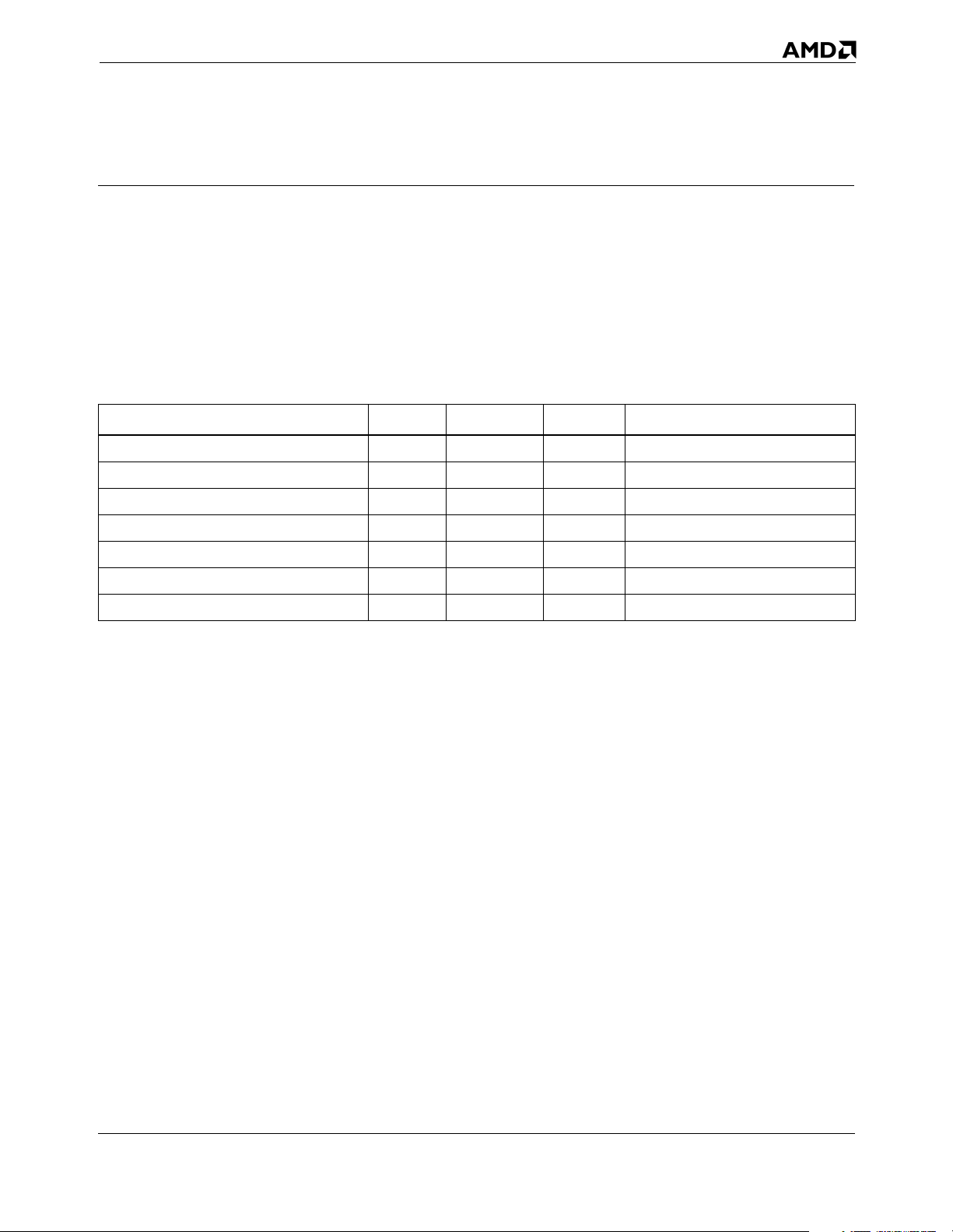

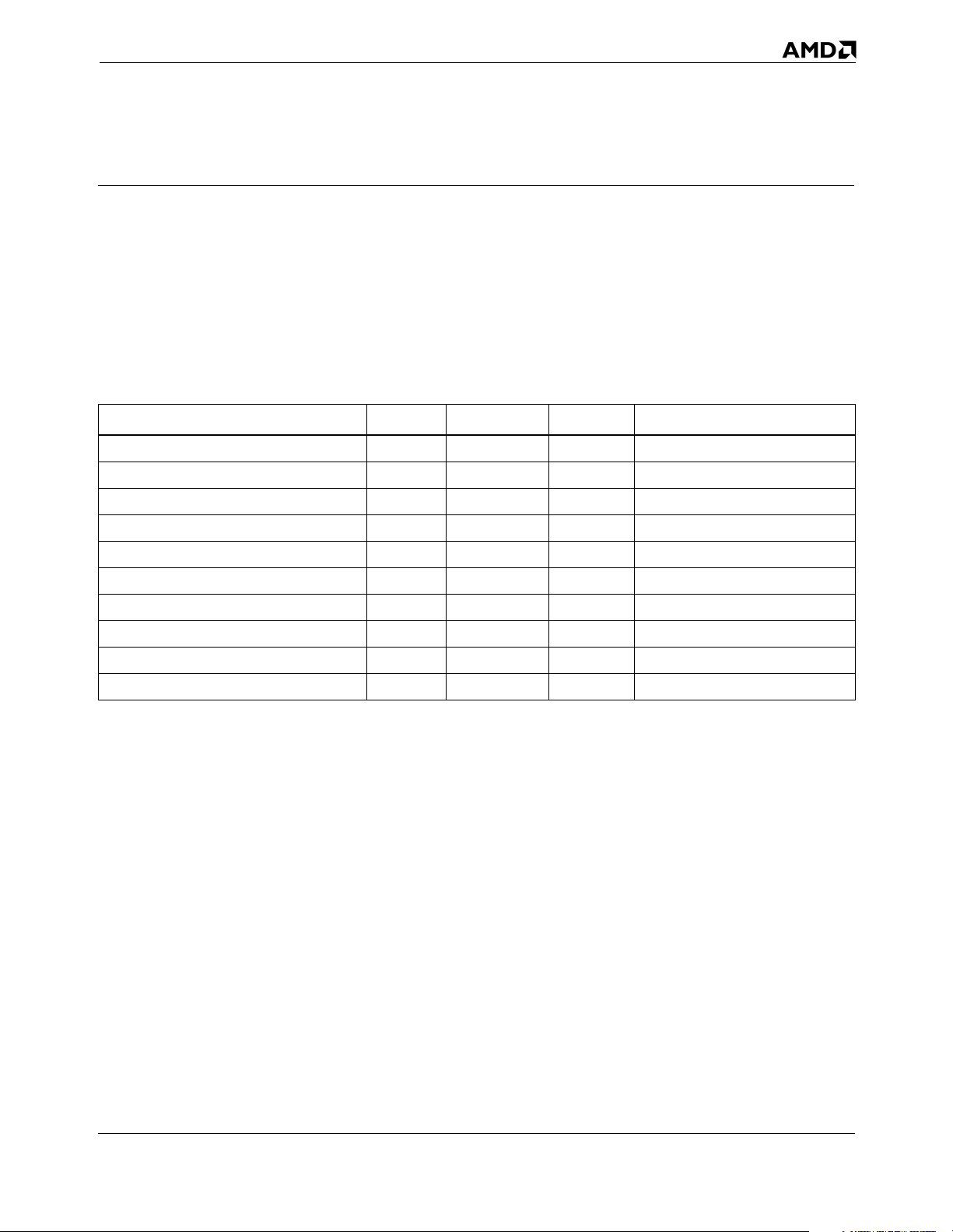

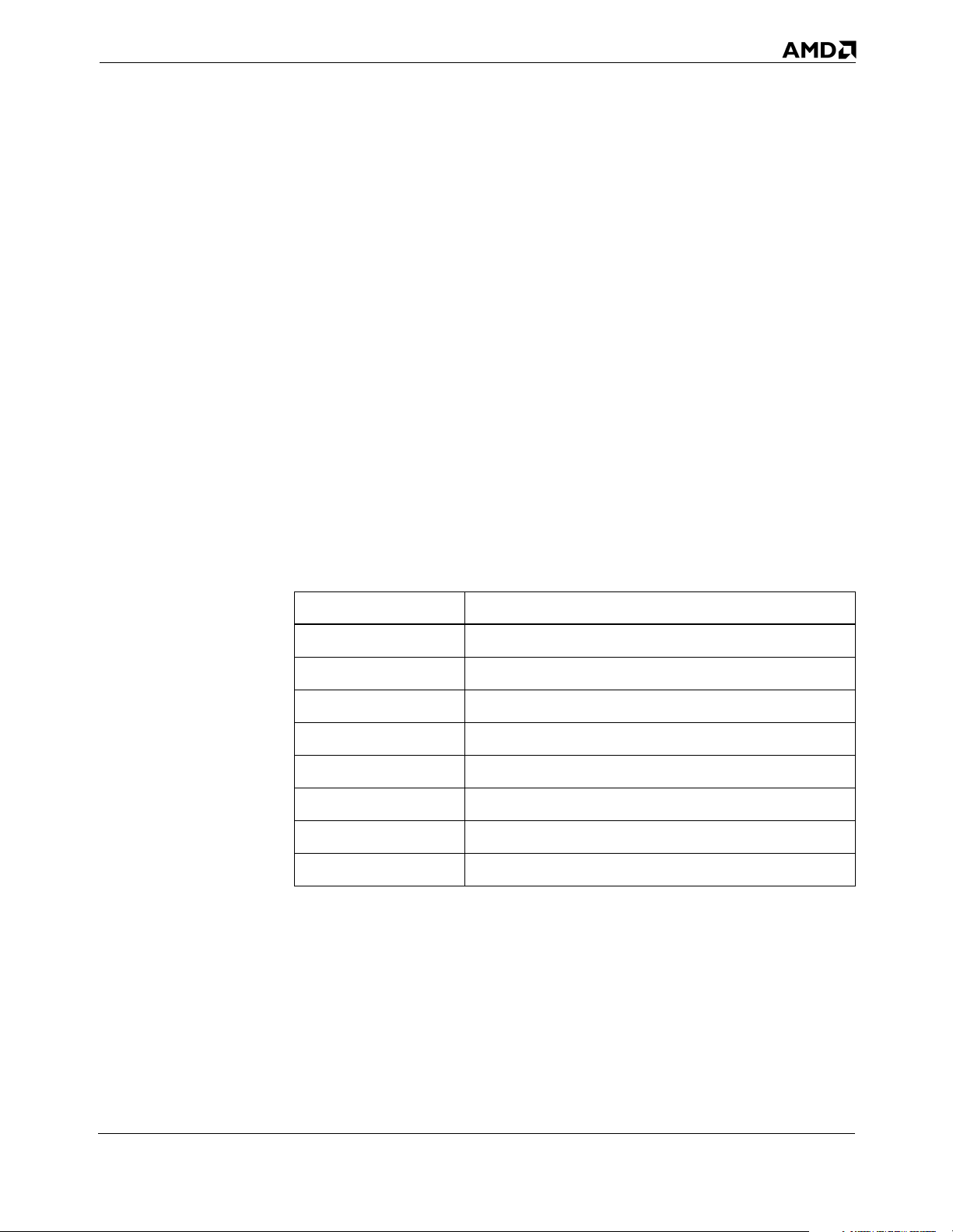

Table 5. Recommended Boot Strings for AMD-K6™ Processors

Model

Model 7 AMD-K6(tm)/XXX

All steppings of Models 8 AMD-K6(tm)-2/XXX

Model D/[7:4]

Model 9/[3:0] AMD-K6(tm)-III/XXX

Model D/[3:0]

Notes:

1. The value for XXX is determined by calculating the core frequency of the processor. Use the Time

Stamp Counter (TSC) to ‘clock’ a timed operation and compare the result to the real-time clock

(RTC) to determine the operating frequency.

2. See “Functions 8000_0002h, 8000_0003h, and 8000_0004h — Processor Name String” on page 77

for more information about these steppings.

2

2

Recommended Boot String Display

AMD-K6(tm)-2+/XXX

AMD-K6(tm)-III+/XXX

1

For example, a BIOS boot string for a Model 9, stepping 3, 450MHz AMD-K6-III processor would look like this:

■ AMD-K6(tm)-III/450

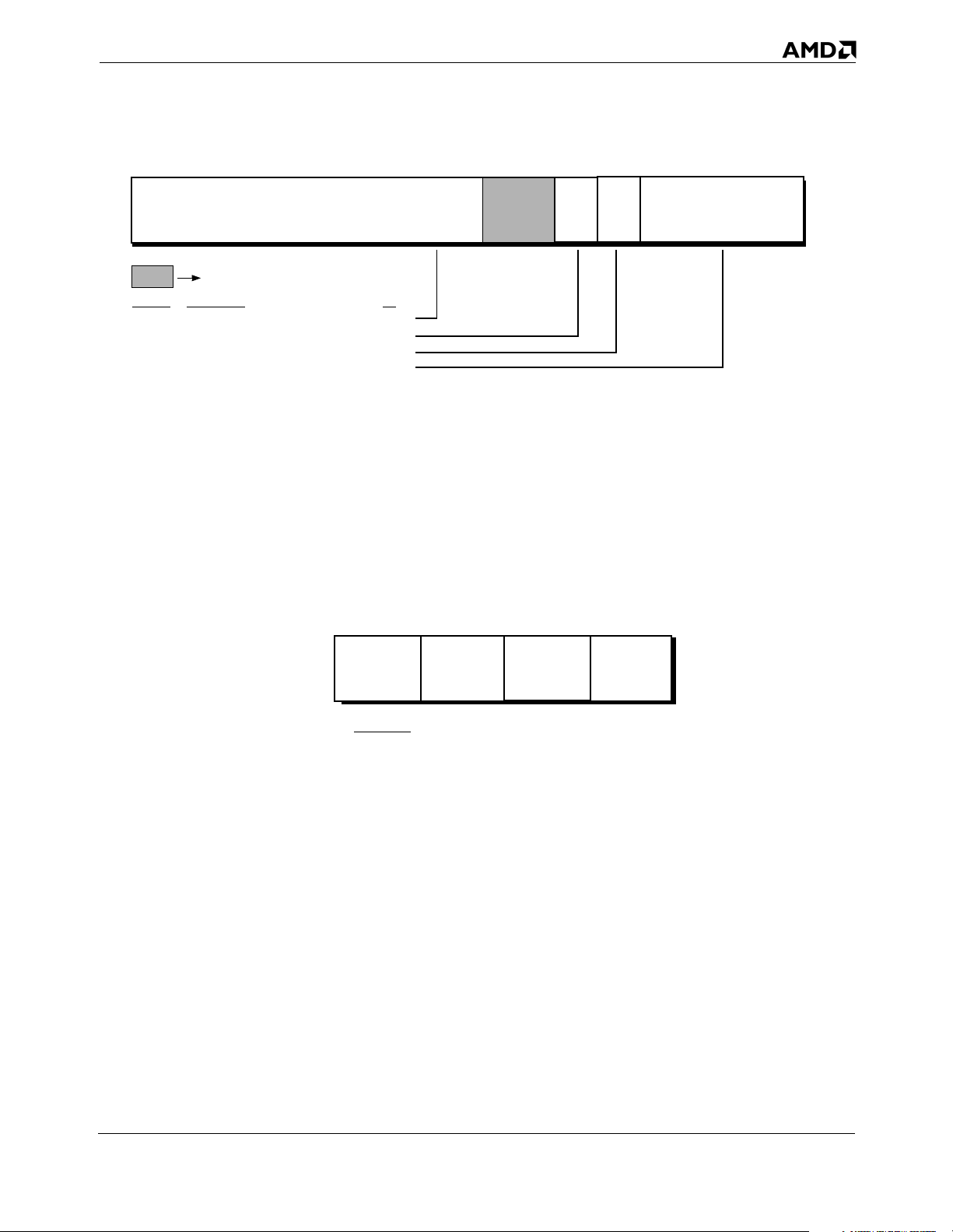

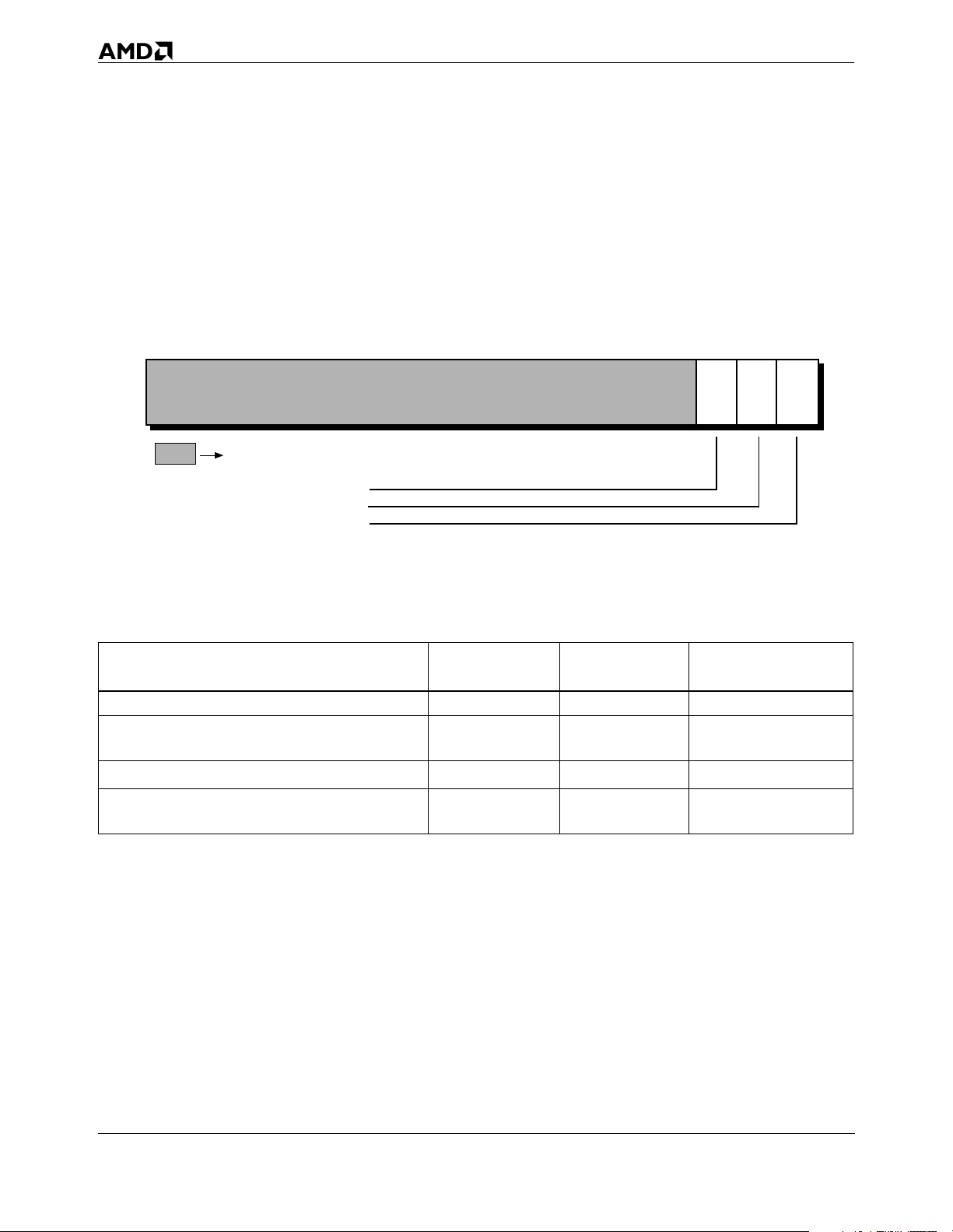

Figure 1 on page 12 shows a flow chart for the CPUID

instruction. Use this chart to implement a CPUID algorithm.

CPUID Identification Algorithms 11

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Check for CPUID

instruction support

Execute CPUID

Extended Function

EAX=8000_0001h

CPUID instruction

supported

Yes

Execute CPUID

Standard Function EAX=0

Store Vendor String

EAX > 1 ?

Yes

Execute CPUID

Standard Function EAX=1

Store returned Standard

Function Feature bits and

Processor Signature;

Determine MMX and,

optionally, SSE* support

Execute CPUID

Extended Function

EAX=8000_0000h to

determine number of

extended functions supported

No

No

No CPUID instruction--

Use other means

to detect CPU type

AMD processor not

present—Check for

other CPU brands

Extended Functions

Not Supported

No

EAX >

8000_0001h ?

Yes

Utilize Vendor String and

Extended Function Feature

bits to determine 3DNow!,

3DNow! Extensions, and

MMX™ Extensions support

Utilize Processor Signature to

determine MSR support

Execute CPUID

Extended Functions

EAX=8000_0002h,

8000_0003h,

and 8000_0004h

to display processor

name string

Execute CPUID

Extended Functions

EAX=8000_0005h and

EAX=8000_0006h (Model 9 &

Model D) to gather processor

cache and TLB information

Execute CPUID

Extended Function

EAX=8000_0007h (Model D)

to gather AMD PowerNow!

technology information for t he

processor

Tune software to optimize

for features present

* Streaming SIMD Extensions

Done

Figure 1. CPUID Instruction Flow Chart

12 CPUID Identification Algorithms

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

System Management Mode (SMM)

This section documents the System Management Mode (SMM)

differences between specified models of the AMD-K6 processor

and the Pentium

implementation in the K86 processors, see the appropriate

AMD-K6 or AMD-K6E processor data sheet.

State-Save Map Differences

The SMM implemented in the AMD-K6 processor differs from

the SMM implemented in the Pentium® processor in one way.

The Interrupt Descriptor Table (IDT) base location in the

AMD-K6 processors is located at offset FF90h. The Pentium

processor has the IDT base located at offset FF94h.

processor. For more information on SMM

I/O Trap Dword Differences

The I/O trap dword is located at offset FFA4h. Its AMD-K6

processor bit fields are shown in Table 6. This state-save area,

which is reserved in Pentium processors, contains information

regarding an I/O instruction that may have been trapped by an

SMI# assertion.

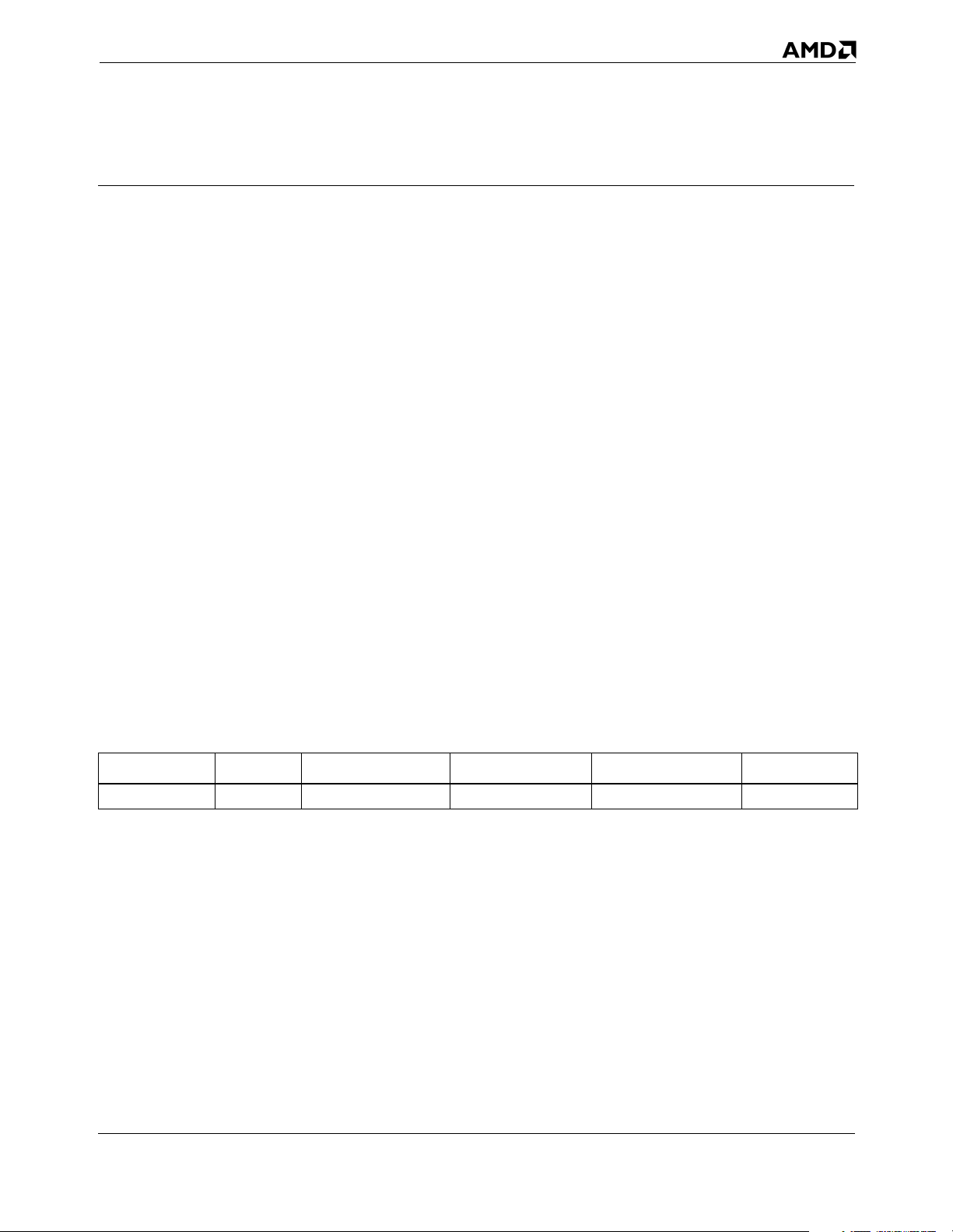

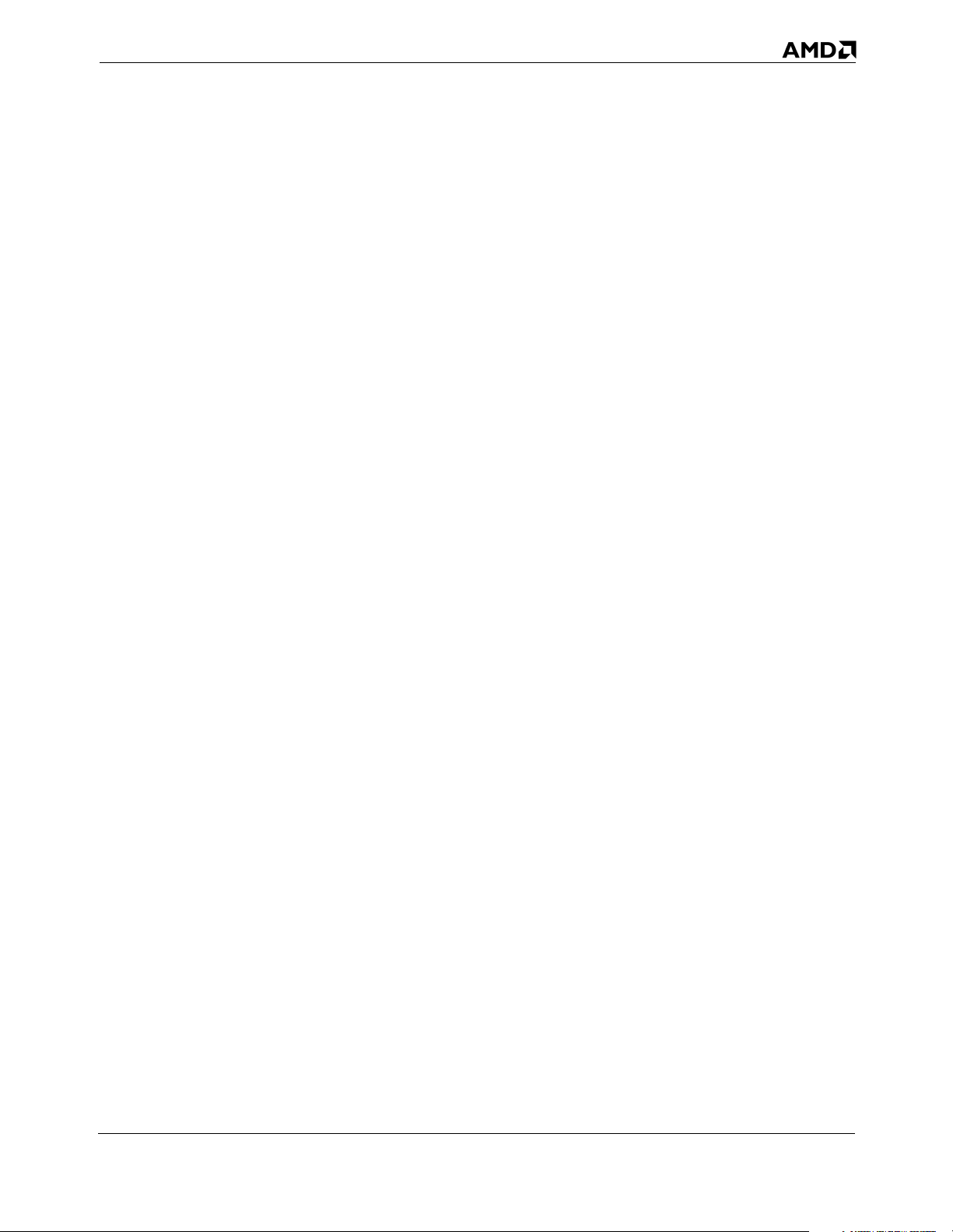

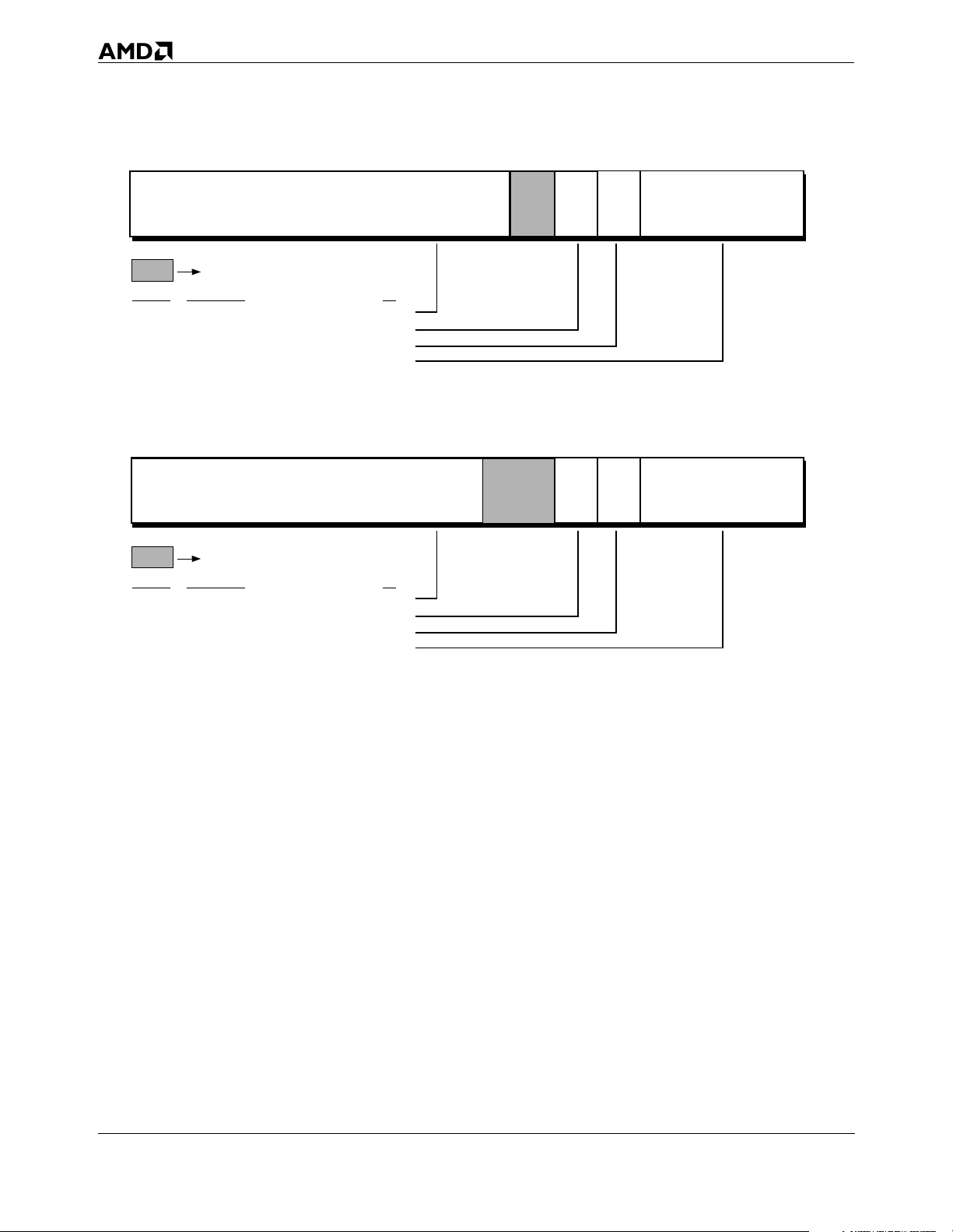

Table 6. AMD-K6™ Processor I/O Trap Dword Configuration at Offset FFA4h

Bits 31–16 Bits 15–4 Bit 3 Bit 2 Bit 1 Bit 0

I/O Port Address Reserved Rep String Operation I/O String Operation Valid I/O Instruction Input or Output

System Management Mode (SMM) 13

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

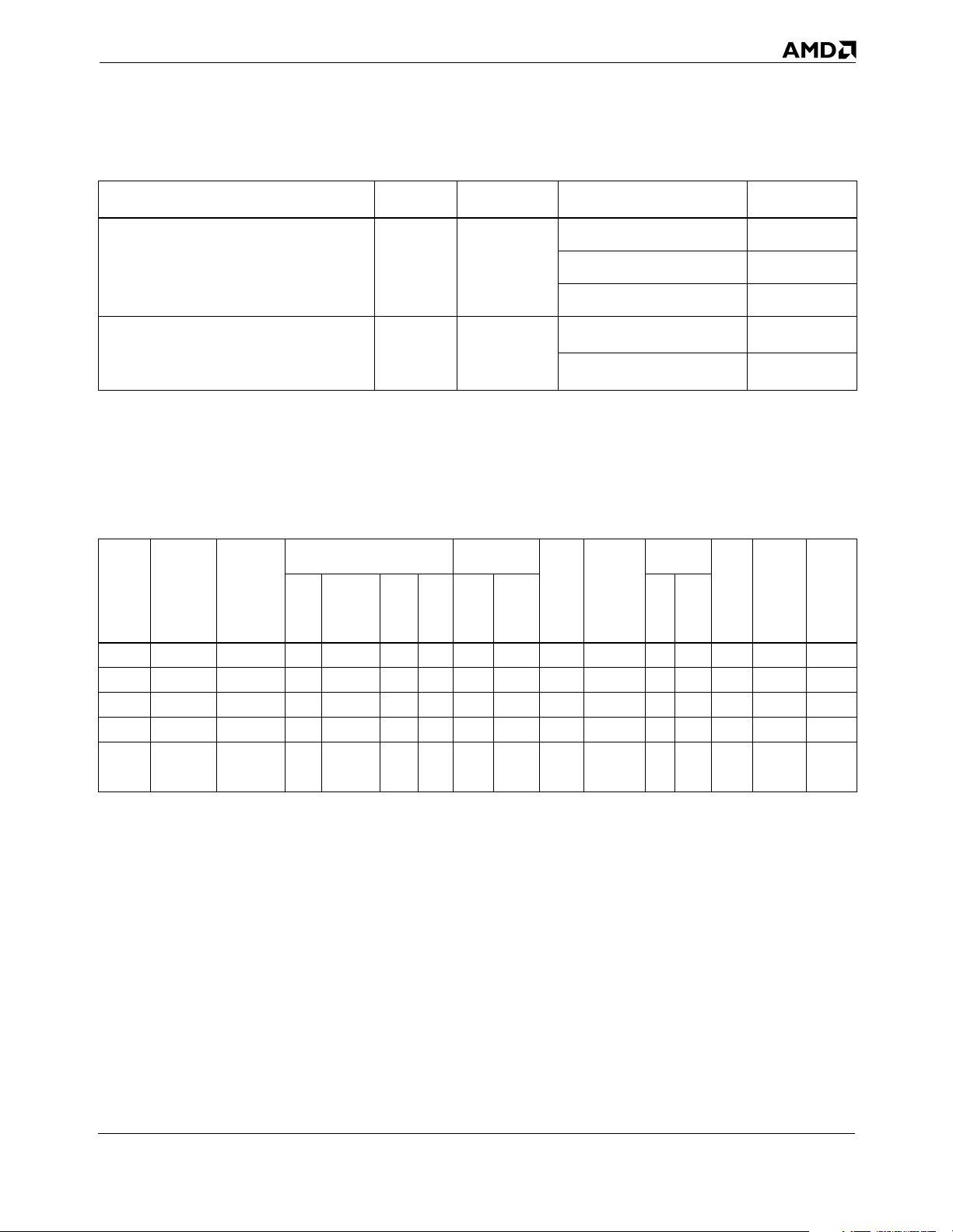

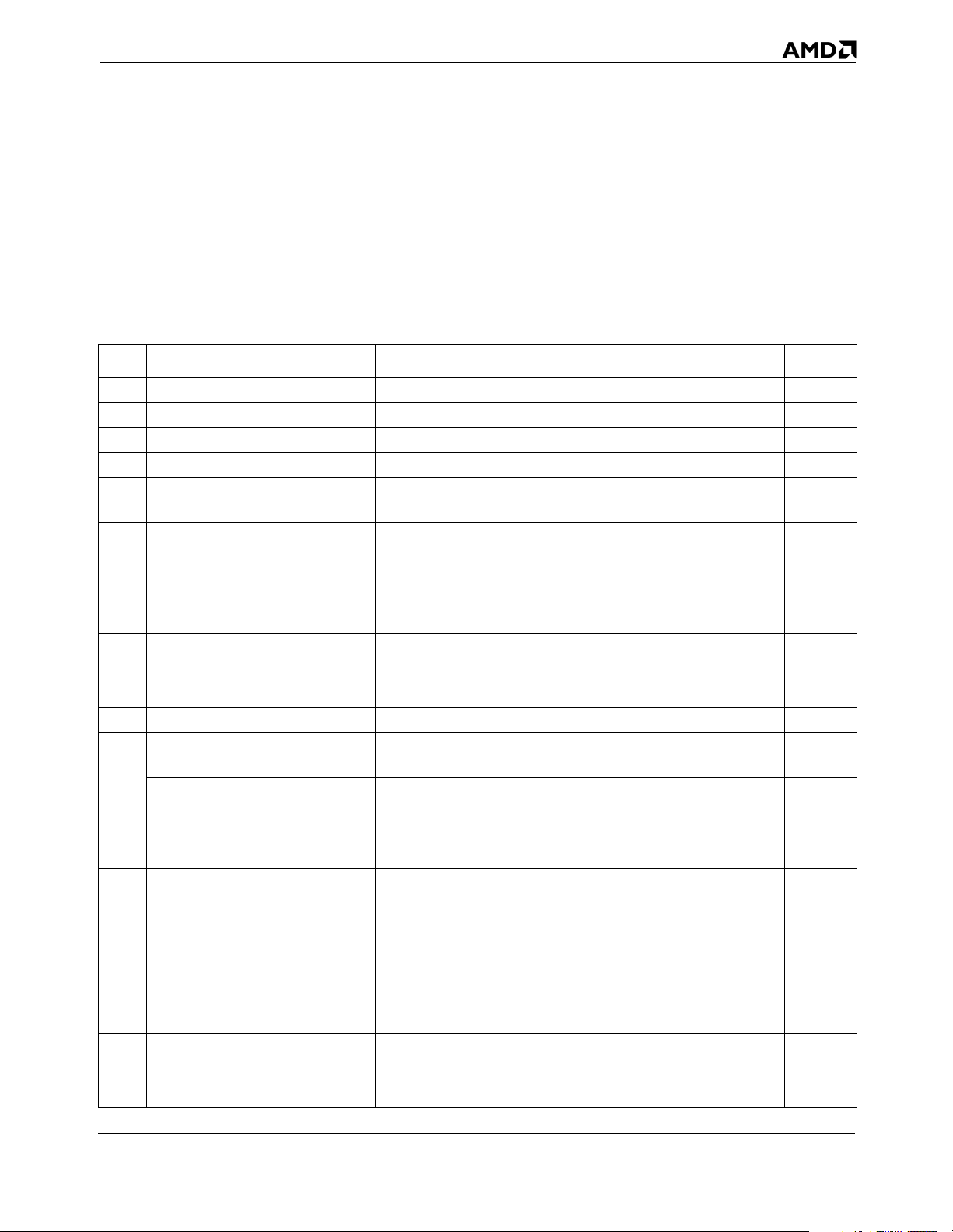

Model-Specific Registers Overview

Each of the models of the AMD-K6 processor family support a

different set of model-specific registers (MSRs). These

differences are summarized by register in Table 7. The

differences are summarized by model in Table 8 on page 15,

where an ‘X’ indicates support for a register or field.

The content of ECX selects the MSR to be addressed by the

RDMSR and WRMSR instruction.

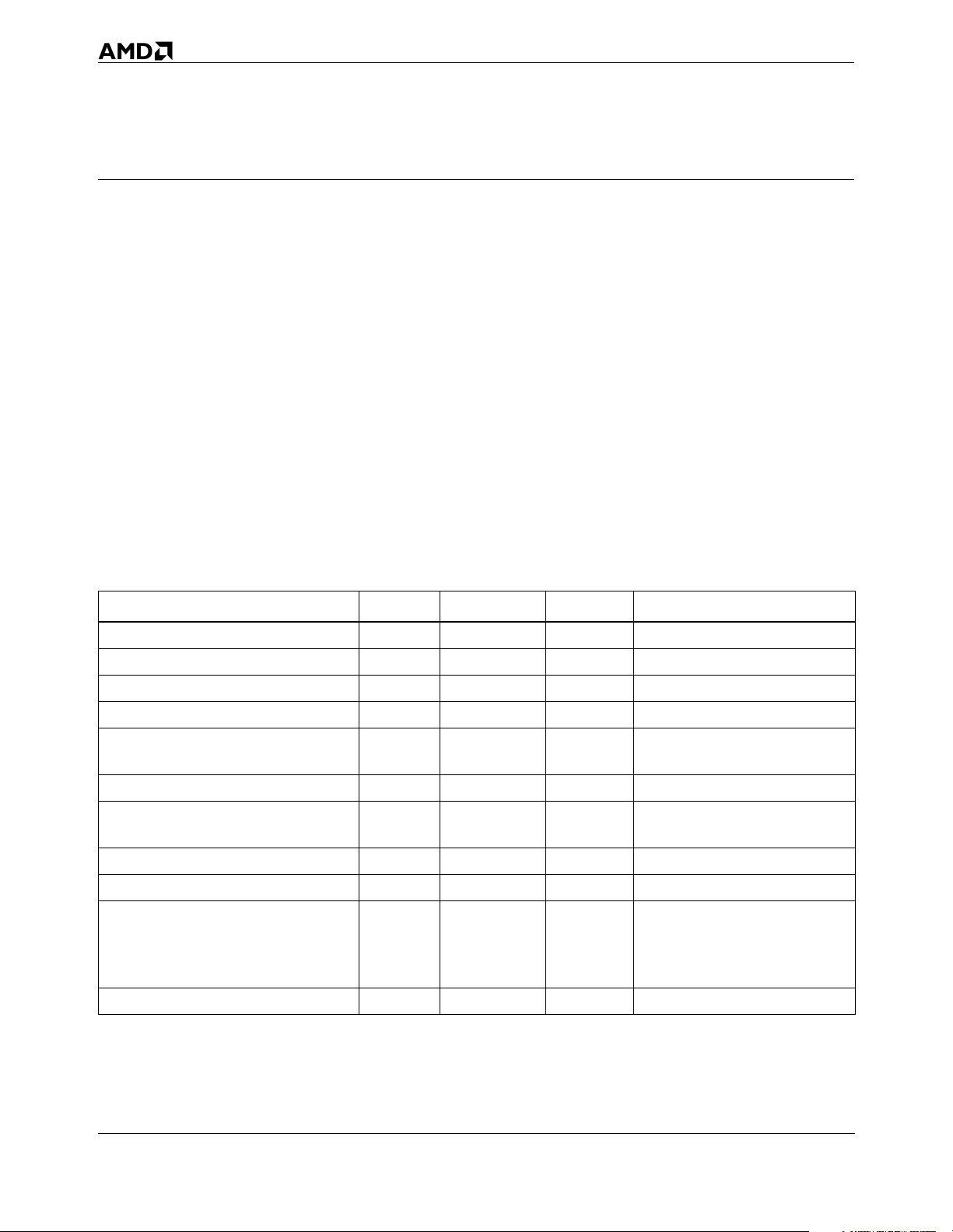

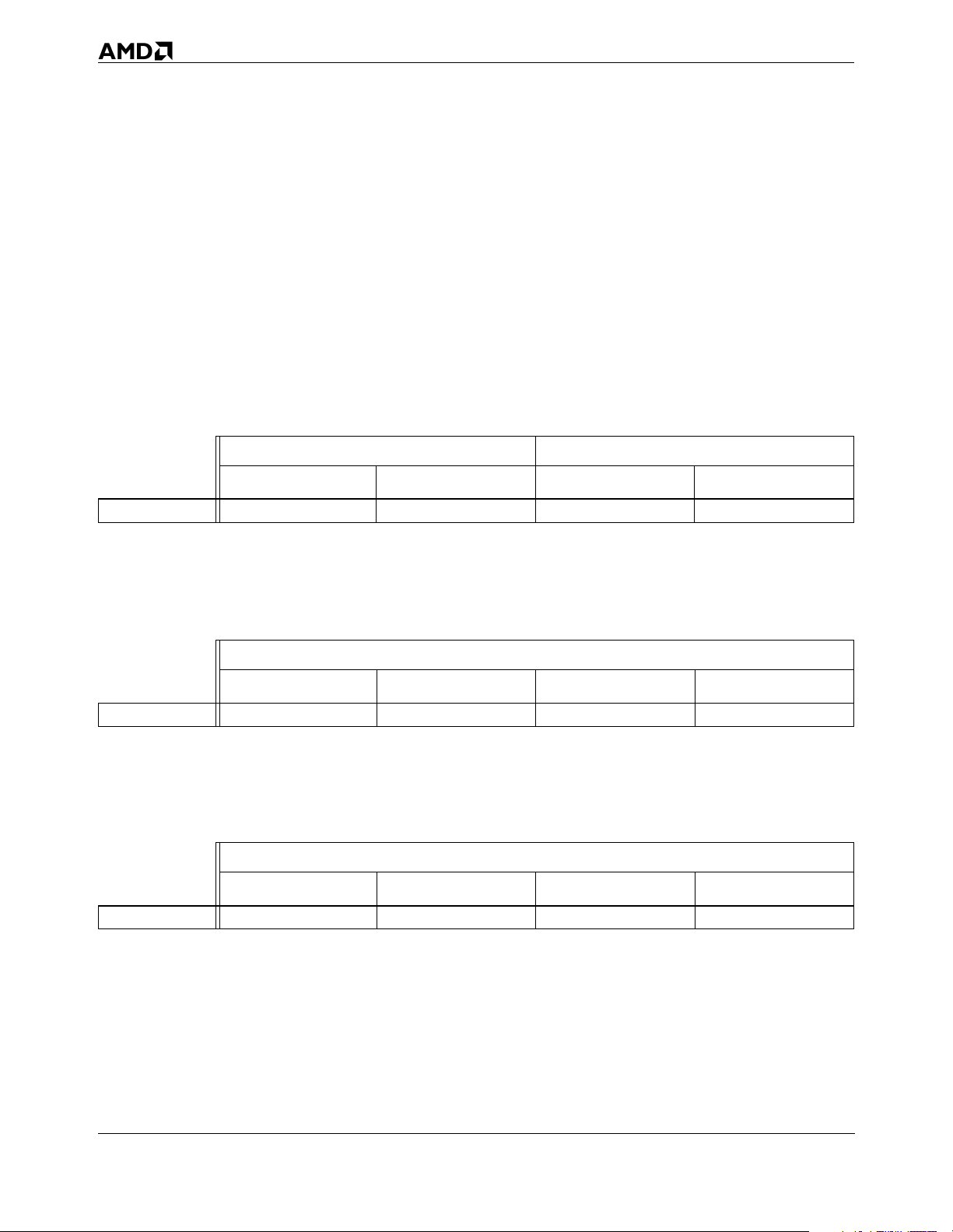

Table 7. Summary by Register of MSR Differences within the AMD-K6™ Family

Register Mnemonic ECX Value Models Description

Machine-Check Address Register MCAR 00h All page 16

Machine-Check Type Register MCTR 01h All page 16

Test Register 12 TR12 0Eh All page 16

Time Stamp Counter TSC 10h All page 16

7, 8/[7:0] page 18

Extended Feature Enable Register EFER C000_0080h

Write Handling Control Register WHCR C000_0082h

SYSCALL/SYSRET Target Address Register STAR C000_0081h

UC/WC Cacheability Control Register UWCCR C000_0085h

Processor State Observability Register PSOR C000_0087h

8/[F:8] page 24

9, D page 39

7, 8/[7:0] page 19

8/[F:8], 9, D page 27

7 Not supported

8, 9, D page 22

7, 8/[7:0] Not supported

8/[F:8], 9, D page 30

7, 8/[7:0] Not supported

8/[F:8], 9, D

1

page 34

Page Flush/Invalidate Register PFIR C000_0088h

2

D

7, 8/[7:0] Not supported

8/[F:8], 9, D page 36

page 46

14 Model-Specific Registers Overview

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Table 7. Summary by Register of MSR Differences within the AMD-K6™ Family (continued)

Register Mnemonic ECX Value Models Description

7, 8 Not supported

Level-2 Cache Array Access Register L2AAR C000_0089h

9 page 40

D page 48

7, 8, 9, D

1

Enhanced Power Management Register EPMR C000_0086h

2

D

Notes:

1. Standard-power versions only.

2. Low-power versions only.

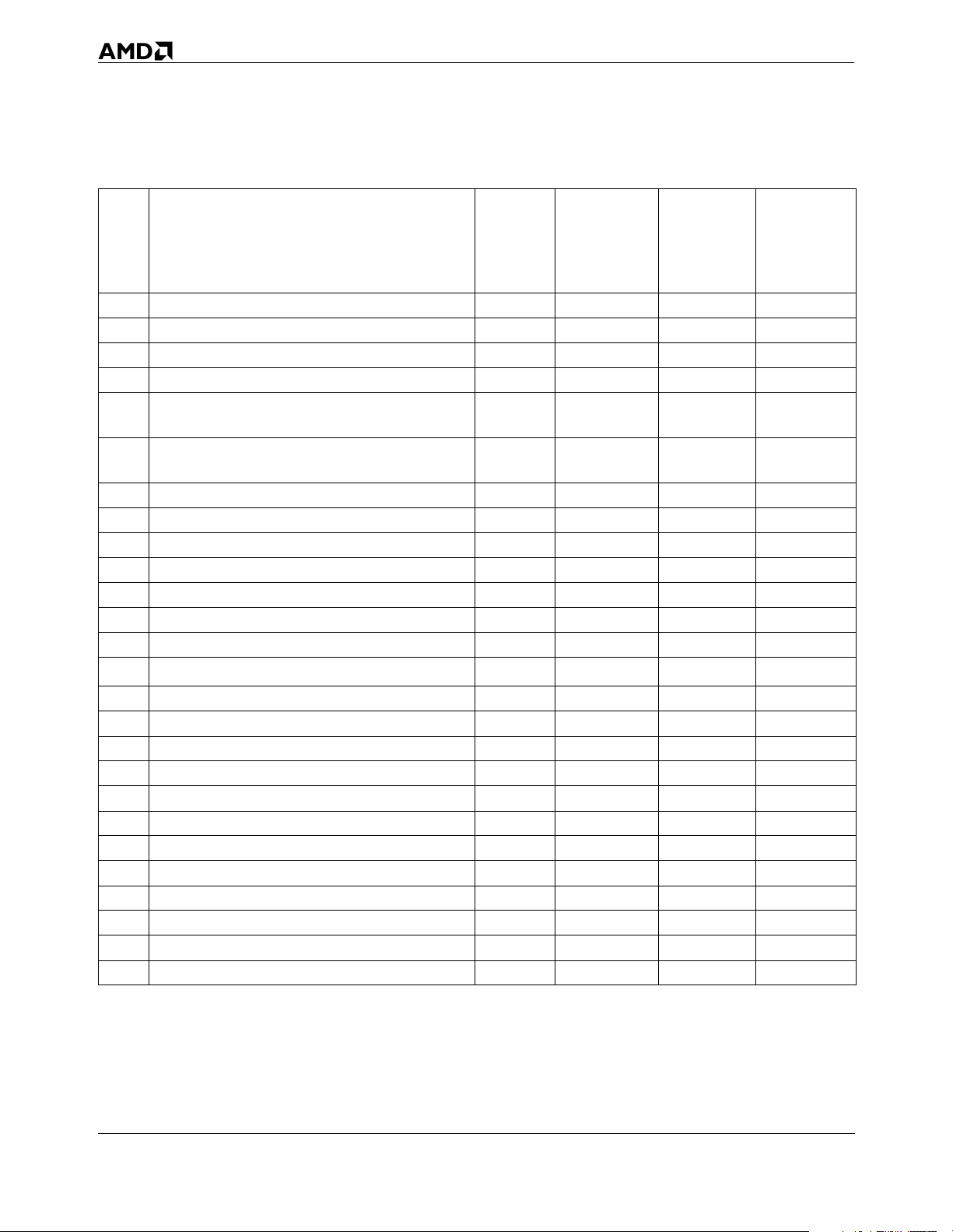

Table 8. Summary by Model of MSR Differences within the AMD-K6™ Family

2

EFER

Standard

Model Stepping

7 All X X X

8 7:0 X X X X

8 F:8 X X X X X X X X X

9 3:0 X X X X X X X X X X X

D

3:0

7:4

MSRs

L2D EWBEC DPE SCE

1

XXXXX XXX

508 MB4092

WHCR

3

MB

STAR UWCCR

PSOR

BF

4X5

X

PBF

VID

PFIR L2AAR EPMR

EBF

Not supported

page 54

XX

5

X

Notes:

1. There are four MSRs that every model and stepping of the AMD-K6 family of processors support identically—MCAR, MCTR, TR12, and

TSC.

2. L2D, EWBEC, and DPE are bits/fields supported in EFER for the indicated models/steppings. All models/steppings support the System

Call Extension (SCE) bit in EFER, even if the corresponding SYSCALL and SYSRET instructions and the STAR register are not supported.

3. Indicates whether the WAELIM field supports 508 Mbytes or 4092 Mbytes of memory. The location of the WAE15M bit and the WAELIM

field within the WHCR register differs between the models/steppings that support 508 Mbytes of memory and those that support 4092

Mbytes of memory.

4. Supported on standard-power versions only.

5. Supported on low-power versions only.

Model-Specific Registers Overview 15

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Standard Model-Specific Registers (All Models)

This section describes the four standard MSRs that every model

and stepping of the AMD-K6 family of processors support

identically. See the appropriate AMD-K6 or AMD-K6E

processor data sheet for more detail on these standard

registers.

Machine-Check

Address Register

(MCAR) and

Machine-Check Type

Register (MCTR)

Test Register 12 (TR12)

Time Stamp Counter (TSC)

The processor does not support the generation of a machine

check exception, but does provide a 64-bit Machine Check

Address Register (MCAR) and a 64-bit Machine Check Type

Register (MCTR) for software compatibility. Because the

processor does not support machine check exceptions, the

contents of the MCAR and MCTR are only affected by the

WRMSR instruction and by RESET being sampled asserted

(where all bits in each register are reset to 0).

The processor also provides the Machine Check Exception

(MCE) bit in Control Register 4 (CR4, bit 6) as a read-write bit.

However, the state of this bit has no effect on the operation of

the processor.

The processor provides the 64-bit Test Register 12 (TR12), but

only the Cache Inhibit (CI) bit (bit 3 of TR12) is supported. All

other bits in TR12 have no effect on the processor’s operation.

Note: The I/O Trap Restart function (bit 9 of TR12) is always

enabled on AMD-K6 processors.

With each processor clock cycle, the processor increments a

64-bit time stamp counter (TSC) MSR. The counter can be

written or read using the WRMSR or RDMSR instructions when

the ECX register contains the value 10h and current privilege

level (CPL) = 0. The counter can also be read using the RDTSC

instruction, but the required privilege level for this instruction

is determined by the Time Stamp Disable (TSD) bit in CR4.

With either of these instructions, the EDX and EAX registers

hold the upper and lower dwords of the 64-bit value to be

written to or read from the TSC, as follows:

■ EDX—Upper 32 bits of TSC

■ EAX—Lower 32 bits of TSC

The TSC can be loaded with any arbitrary value. This feature is

compatible with the Pentium processor.

16 Model-Specific Registers Overview

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Model 7 and Model 8/[7:0] Registers

The AMD-K6E processor Model 7 and the AMD-K6-2 processor

Model 8/[7:0] provide the model-specific registers listed in

Table 9.

The contents of ECX selects the MSR to be addressed by the

RDMSR and WRMSR instruction.

Table 9. Model-Specific Registers Supported by Models 7 and 8/[7:0]

Register Name Mnemonic ECX Value Description Comments

Machine-Check Address Register MCAR 00h page 16 Identical on all models

Machine-Check Type Register MCTR 01h page 16 Identical on all models

Test Register 12 TR12 0Eh page 16 Identical on all models

Time Stamp Counter TSC 10h page 16 Identical on all models

Extended Feature Enable Register EFER C000_0080h page 18

Write Handling Control Register WHCR C000_0082h page 19

SYSCALL/SYSRET Target Address Register STAR C000_0081h page 22 Not supported on Model 7

Model 7 and Model 8/[7:0] Registers 17

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Extended Feature Enable Register (EFER)

The Extended Feature Enable Register (EFER) contains the

control bits that enable the extended features of the AMD-K6

processor. Figure 2 shows the format of the EFER register, and

Table 10 defines the function of each bit of the EFER register.

The EFER register is MSR C000_0080h.

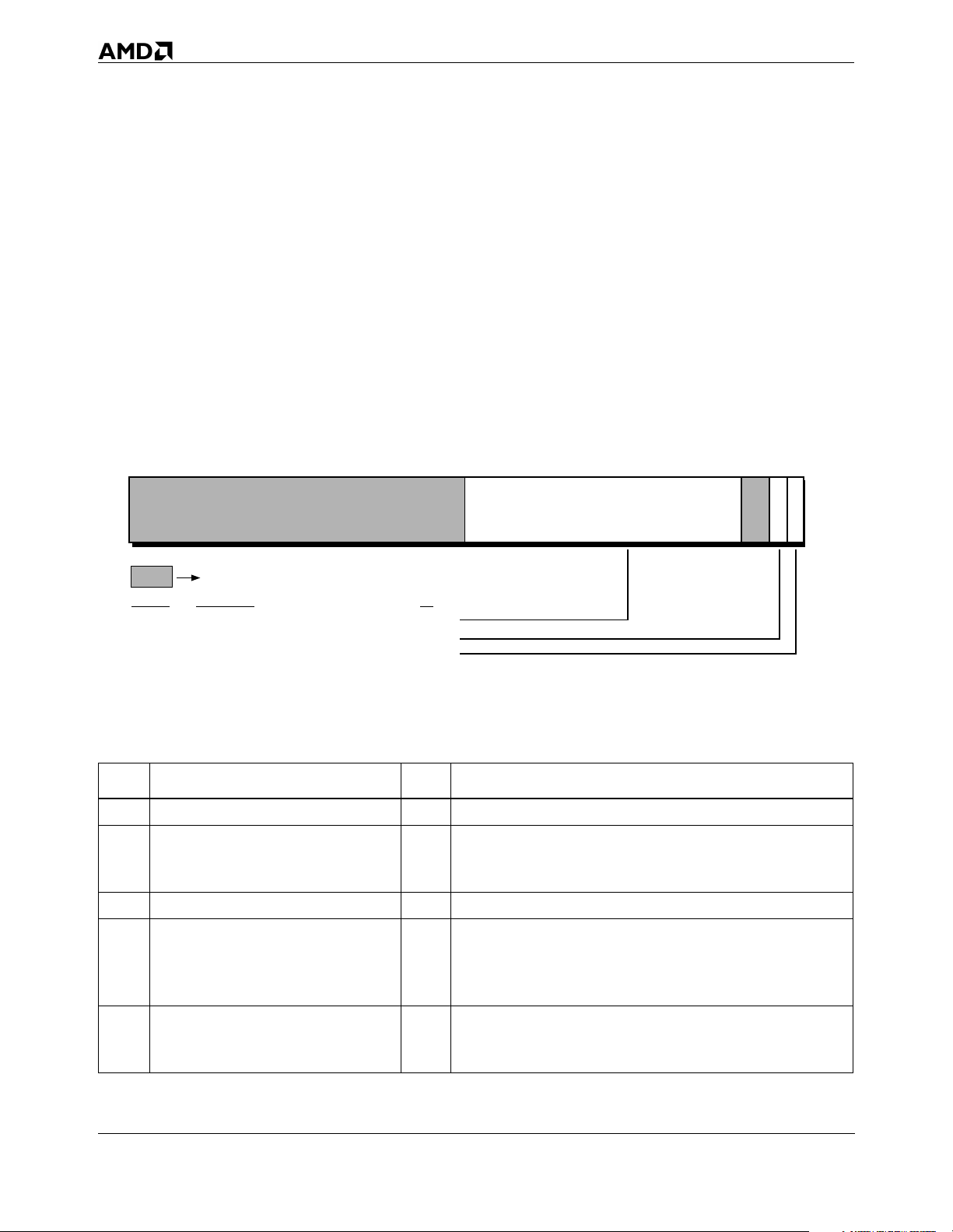

1063

S

C

E

Reserved

Symbol Description Bit

SCE System Call Extension 0

Figure 2. Extended Feature Enable Register (EFER) (Models 7 and 8/[7:0])

Table 10. Extended Feature Enable Register (EFER) Definition (Models 7 and 8/[7:0])

Bit Description R/W Function

Writing a 1 to any reserved bit causes a general protection

63–1

Notes:

1. The AMD-K6E processor Model 7 provides the SCE bit in the EFER register, but this bit does not affect processor operation because the

SYSCALL and SYSRET instructions and the STAR register are not supported in this models.

Reserved

0

System Call Extension (SCE)

1

R

fault to occur. All reserved bits are always read as 0.

SCE must be set to 1 to enable the usage of the SYSCALL and

R/W

SYSRET instructions.

18 Model 7 and Model 8/[7:0] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Write Handling Control Register (WHCR)

The Write Handling Control Register (WHCR) (see Figure 3 on

page 20) is an MSR that contains three fields—the Write

Cacheability Detection Enable (WCDE) bit, the Write Allocate

Enable Limit (WAELIM) field, and the Write Allocate Enable

15-to-16-Mbyte (WAE15M) bit. The WHCR register is MSR

C000_0082h.

AMD-K6 processors contain a split level-1 (L1) 64-Kbyte

writeback cache organized as a separate 32-Kbyte instruction

cache and a 32-Kbyte data cache with two-way set associativity.

The cache line size is 32 bytes and lines are read from memory

using an efficient pipelined burst read cycle. Further

performance gains are achieved by the implementation of a

write allocation scheme.

Write Allocation A write allocate, if enabled, occurs when the processor has a

pending memory write cycle to a cacheable line and the line

does not currently reside in the L1 cache. For more information,

see the Implementation of Write Allocate in the K86™ Processors

Application Note, order# 21326, and the “Cache Organization”

chapter in the appropriate AMD-K6 or AMD-K6E processor

data sheet.

This section describes two programmable mechanisms used by

the processor to determine when to perform write allocate.

When either of these mechanisms indicates that a pending

write is to a cacheable area of memory, a write allocate is

performed.

Before enabling write allocate or changing memory

cacheability/writeability, the BIOS must writeback and

invalidate the internal cache by using the WBINVD instruction.

In addition, write allocate should be enabled only after

performing any memory sizing or typing algorithms.

Model 7 and Model 8/[7:0] Registers 19

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

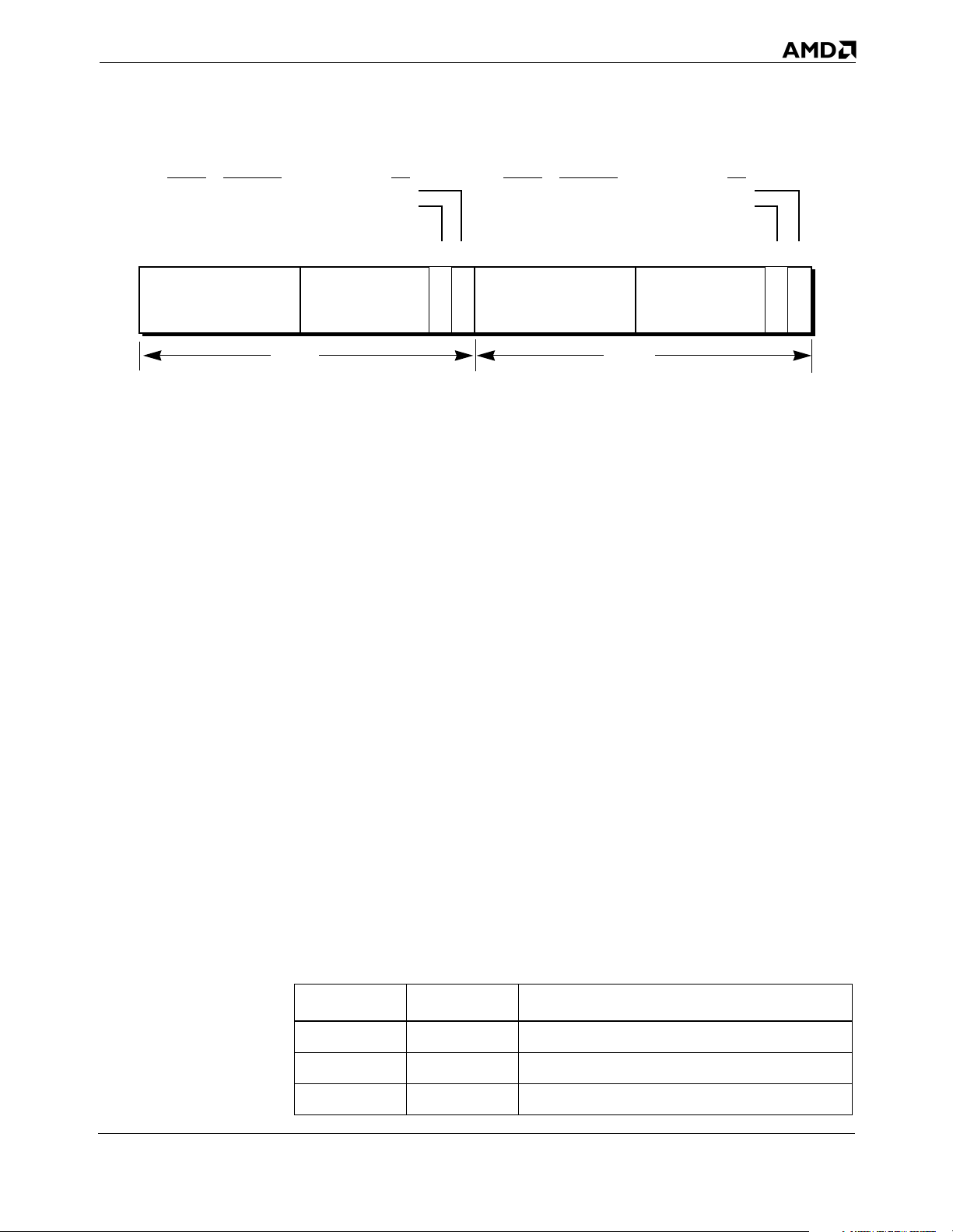

9

71063

8

W

A

E

1

5

M

Reserved

Symbol Description Bits

WCDE Always program to 0 8

WAELIM Write Allocate Enable Limit 7–1

WAE15M Write Allocate Enable 15-to-16-Mbyte 0

Note: Hardware RESET initializes this MSR to all zeros.

0

WAELIM

Figure 3. Write Handling Control Register (WHCR) (Models 7 and 8/[7:0])

Write Cacheability Detection Enable Bit

Write Allocate Enable Limit Field

For proper functionality, always program bit 8 of WHCR to 0.

See “Pipelining Support” on page 69 for more information on

the WCDE bit.

The WAELIM field is 7 bits wide. This field, multiplied by 4

Mbytes, defines an upper memory limit. Any pending write

cycle that misses the L1 cache and that addresses memory

below this limit causes the processor to perform a write

allocate (assuming the address is not within a range where

write allocates are disallowed).

Write allocate is disabled for memory accesses at and above

this limit unless the processor determines a pending write

cycle is cacheable by means of one of the other write allocate

mechanisms—“Write to a Cacheable Page” and “Write to a

Sector” (for more information, see the “Cache Organization”

chapter in the appropriate AMD-K6 or AMD-K6E processor

data sheet.

7

The maximum value of this limit is ((2

–1) · 4 Mbytes) = 508

Mbytes. When all the bits in this field are set to 0, all memory

is above this limit and the write allocate mechanism is

disabled (even if all bits in the WAELIM field are set to 0,

write allocates can still occur due to the “Write to a Cacheable

Page” and “Write to a Sector” mechanisms).

Once the BIOS determines the amount of RAM installed in the

system, this number should also be used to program the

WAELIM field. For example, a system with 32 Mbytes of RAM

would program the WAELIM field with the value 0001000b.

20 Model 7 and Model 8/[7:0] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

This value (8), when multiplied by 4 Mbytes, yields 32 Mbytes

as the write allocate limit.

Write Allocate Enable

15-to-16-Mbyte Field.

The WAE15M bit is used to enable write allocations for the

memory write cycles that address the 1 Mbyte of memory

between 15 Mbytes and 16 Mbytes. This bit must be set to 1 to

allow write allocates in this memory area.

This sub-mechanism of the WAELIM provides a memory hole to

prevent write allocates. This memory hole is provided to

account for a small number of uncommon memory-mapped I/O

adapters that use this particular memory address space. If the

system contains one of these peripherals, the bit should be set

to 0 (even if the WAE15M bit is set to 0, write allocates can still

occur between 15 Mbytes and 16 Mbytes due to the “Write to a

Cacheable Page” and “Write to a Sector” mechanisms). The

WAE15M bit is ignored if the value in the WAELIM field is set

to less than 16 Mbytes.

By definition, write allocations are not performed in the

memory area between 640 Kbytes and 1 Mbyte unless the

processor determines a pending write cycle is cacheable by

means of “Write to a Cacheable Page” or “Write to a Sector.” It

is not safe to perform write allocations between 640 Kbytes and

1 Mbyte (000A_0000h to 000F_FFFFh) because it is considered

a noncacheable region of memory.

Model 7 and Model 8/[7:0] Registers 21

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

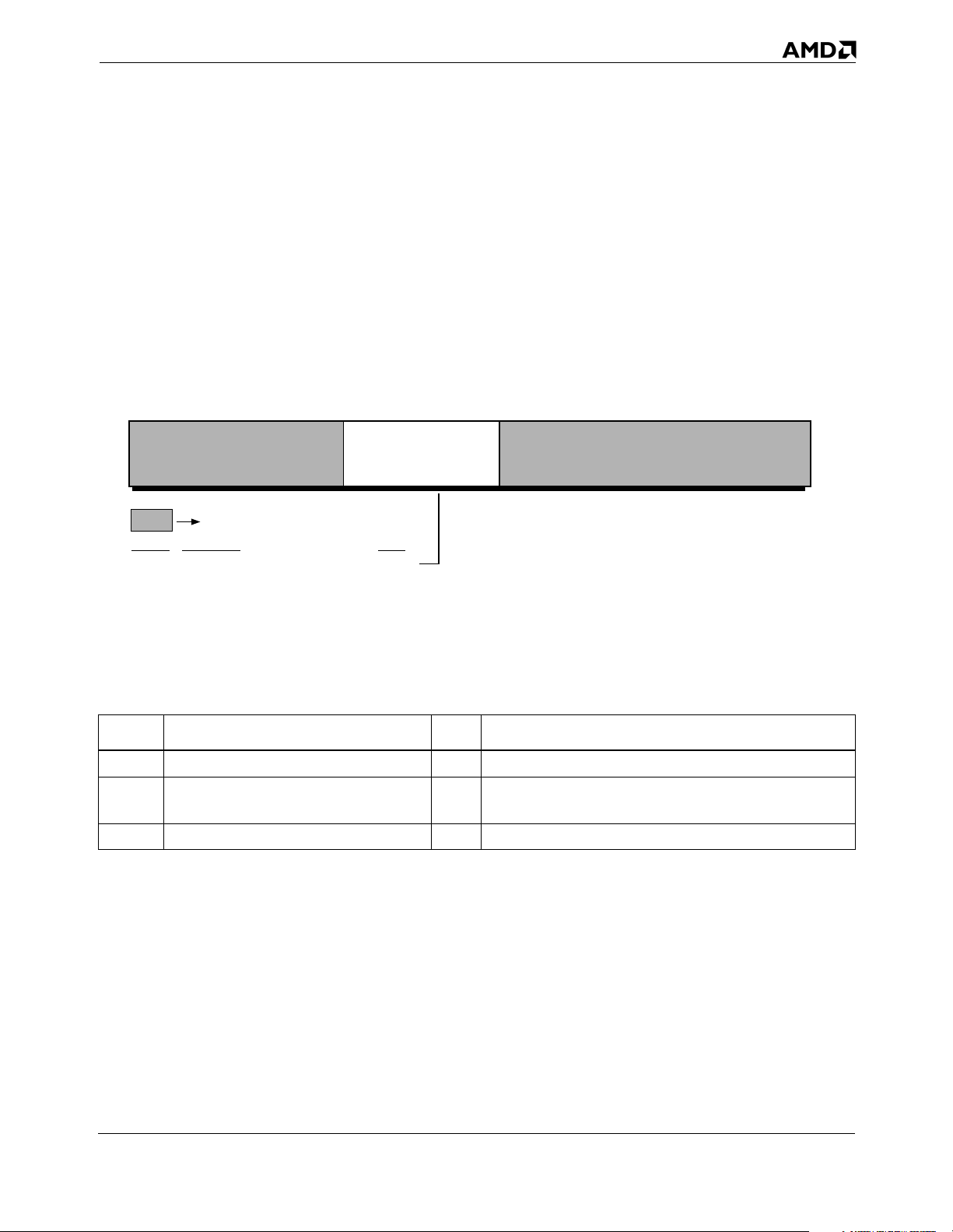

SYSCALL/SYSRET Target Address Register (STAR)

Models 8, 9, and D implement the STAR register. This register

contains the target EIP address used by the SYSCALL

instruction and the 16-bit code and stack segment selector

bases used by the SYSCALL and SYSRET instructions.

Figure 4 shows the format of the STAR register, and Table 11

defines the function of each field of the STAR register. The

STAR register is MSR C000_0081h.

For more information about SYSCALL/SYSRET, see the

SYSCALL and SYSRET Instruction Specification Application Note,

order# 21086.

31 063

32

Target EIP Address

SYSRET CS Selector and SS

Selector Base

47

48

SYSCALL CS Selector and SS

Selector Base

Figure 4. SYSCALL/SYSRET Target Address Register (STAR) (Models 8, 9, and D)

Table 11. SYSCALL/SYSRET Target Address Register (STAR) Definition (Models 8, 9, and D)

Bit Description R/W Function

During the SYSRET instruction, this field is copied into the CS

63–48

47–32

31–0

SYSRET CS and SS Selector Base

SYSCALL CS and SS Selector Base

Target EIP Address

R/W

register and the contents of this field, plus 1000b, are copied

into the SS register.

During the SYSCALL instruction, this field is copied into the

R/W

CS register and the contents of this field, plus 1000b, are

copied into the SS register.

During the SYSCALL instruction, this address is copied into

R/W

the EIP and points to the new starting address.

22 Model 7 and Model 8/[7:0] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Model 8/[F:8] Registers

The AMD-K6-2 processor Model 8/[F:8] and AMD-K6-2E

processor Model 8/[F:8] provides the ten MSRs listed in Table

12.

The contents of ECX select the MSR to be addressed by the

RDMSR and WRMSR instruction.

Table 12. Model-Specific Registers Supported by Model 8/[F:8]

Register Name Mnemonic ECX Value Description Comments

Machine-Check Address Register MCAR 00h page 16 Identical on all models

Machine-Check Type Register MCTR 01h page 16 Identical on all models

Test Register 12 TR12 0Eh page 16 Identical on all models

Time Stamp Counter TSC 10h page 16 Identical on all models

Extended Feature Enable Register EFER C000_0080h page 24 Newly defined for Model 8/[F:8]

Write Handling Control Register WHCR C000_0082h page 27 Newly defined for Model 8/[F:8]

SYSCALL/SYSRET Target Address Register STAR C000_0081h page 22 Identical to Model 8/[7:0]

UC/WC Cacheability Control Register UWCCR C000_0085h page 30 New for Model 8/[F:8]

Processor State Observability Register PSOR C000_0087h page 34 New for Model 8/[F:8]

Page Flush/Invalidate Register PFIR C000_0088h page 36 New for Model 8/[F:8]

Model 8/[F:8] Registers 23

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Extended Feature Enable Register (EFER)

The Extended Feature Enable Register (EFER) contains the

control bits that enable the extended features of the processor.

Figure 5 shows the format of the EFER register, and Table 13

defines the function of each bit of the EFER register. The EFER

register is MSR C000_0080h.

Note: The EFER register as defined in models 7 and 8/[7:0] is

defined differently in Model 8/[F:8]. A complete description

of the newly defined register is included in this section for

Model 8/[F:8].

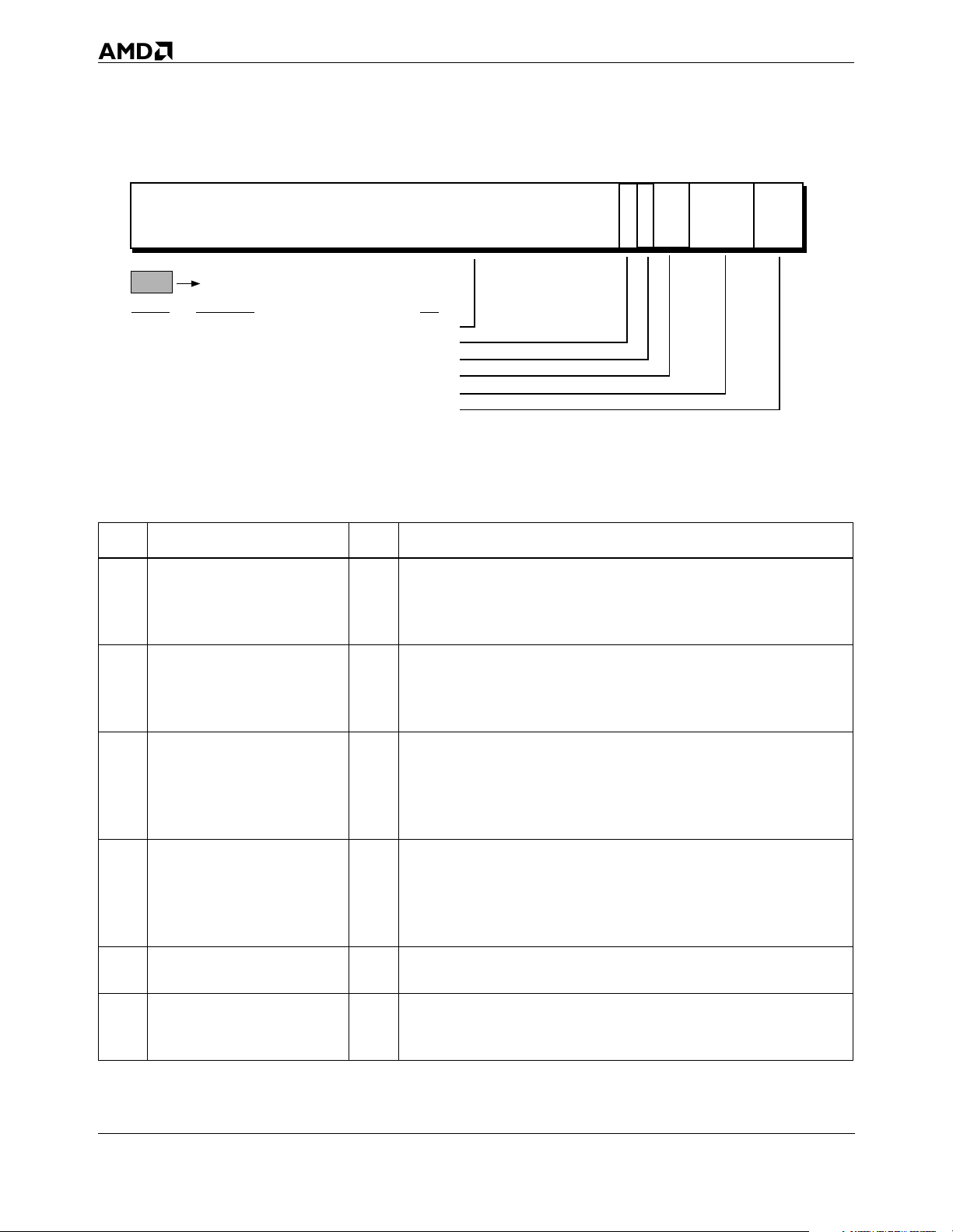

1063

234

S

EWBEC

D

C

P

E

E

Reserved

Symbol Description Bit

EWBEC EWBE Control 3-2

DPE Data Prefetch Enable 1

SCE System Call Extension 0

Figure 5. Extended Feature Enable Register (EFER) (Model 8/[F:8])

Table 13. Extended Feature Enable Register (EFER) Definition (Model 8/[F:8])

Bit Description R/W Function

Writing a 1 to any reserved bit causes a general protection

63–4

3-2

1

0

Reserved

EWBE# Control (EWBEC)

Data Prefetch Enable (DPE)

System Call Extension (SCE)

R

fault to occur. All reserved bits are always read as 0.

This 2-bit field controls the behavior of the processor with

respect to the ordering of write cycles and the EWBE# signal.

R/W

EFER[3] and EFER[2] are Global EWBE# Disable (GEWBED)

and Speculative EWBE Disable (SEWBED), respectively.

DPE must be set to 1 to enable data prefetching (this is the

default setting following reset). If enabled, cache misses initi-

R/W

ated by a memory read within a 32-byte cache line are conditionally followed by cache-line fetches of the other line in

the 64-byte sector.

SCE must be set to 1 to enable the usage of the SYSCALL and

R/W

SYSRET instructions.

External Write Buffer Empty Control Field

Model 8/[F:8] contains an 8-byte write merge buffer that allows

the processor to conditionally combine data from multiple

noncacheable write cycles into this merge buffer. The merge

24 Model 8/[F:8] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

buffer operates in conjunction with the Memory Type Range

Registers (MTRRs). Refer to “UC/WC Cacheability Control

Register (UWCCR)” on page 30 for a description of the MTRRs.

Merging multiple write cycles into a single write cycle reduces

processor bus utilization and processor stalls, thereby

increasing the overall system performance.

Out-of-Order Write Cycles. The presence of the merge buffer

creates the potential to perform out-of-order write cycles

relative to the processor’s cache. In general, the ordering of

write cycles that are driven externally on the system bus and

those that hit the processor’s cache can be controlled by the

EWBE# signal. If EWBE# is sampled negated, the processor

delays the commitment of write cycles to cache lines in the

modified state or exclusive state in the processor’s cache.

Therefore, the system logic can enforce strong ordering by

negating EWBE# until the external write cycle is complete,

thereby ensuring that a subsequent write cycle that hits the

cache does not complete ahead of the external write cycle.

However, the addition of the write merge buffer introduces the

potential for out-of-order write cycles to occur between writes

to the merge buffer and writes to the processor’s cache. Because

these writes occur entirely within the processor and are not

sent out to the processor bus, the system logic is not able to

enforce strong ordering with the EWBE# signal.

The EWBE# control (EWBEC) bits provide a mechanism for

enforcing three different levels of write ordering in the

presence of the write merge buffer:

Best Performance. EFER[3] is defined as the Global EWBE#

Disable (GEWBED). When GEWBED equals 1, the processor

does not attempt to enforce any write ordering internally or

externally (the EWBE# signal is ignored). This is the maximum

performance setting.

Close-to-Best Performance. EFER[2] is defined as the Speculative

EWBE# Disable (SEWBED). SEWBED only affects the

processor when GEWBED equals 0. If GEWBED equals 0 and

SEWBED equals 1, the processor enforces strong ordering for

all internal write cycles with the exception of write cycles

addressed to a range of memory defined as uncacheable (UC) or

write-combining (WC) by the MTRRs. In addition, the processor

Model 8/[F:8] Registers 25

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

samples the EWBE# signal. If EWBE# is sampled negated, the

processor delays the commitment of write cycles to processor

cache lines in the modified state or exclusive state until EWBE#

is sampled asserted.

This setting provides performance comparable to, but slightly

less than, the performance obtained when GEWBED equals 1

because some degree of write ordering is maintained.

Slowest Performance. If GEWBED equals 0 and SEWBED equals 0,

the processor enforces strong ordering for all internal and

external write cycles. In this setting, the processor assumes, or

speculates, that strong order must be maintained between writes

to the merge buffer and writes that hit the processor’s cache.

Once the merge buffer is written out to the processor’s bus, the

EWBE# signal is sampled. If EWBE# is sampled negated, the

processor delays the commitment of write cycles to processor

cache lines in the modified state or exclusive state until EWBE#

is sampled asserted.

This setting is the default after RESET and provides the lowest

performance of the three settings because full write ordering is

maintained.

Write Ordering and Performance. Table 14 summarizes the three

settings of the EWBEC field, along with the effect of write

ordering and performance.

Table 14. Write Ordering and Performance Settings for EFER Register

EFER[3] (GEWBED) EFER[2] (SEWBED) Write Ordering Performance

1 0 or 1

01

0 (Default) 0 (Default)

None Best

All except UC/WC Close-to-Best

All Slowest

Enforcing complete write ordering in a uniprocessor system is

usually not necessary. In order to achieve the highest level of

performance while still maintaining support for the EWBE#

signal, AMD recommends that the BIOS set EFER[3:2] to 01b

(close-to-best performance). Many uniprocessor systems do not

support the EWBE# signal, in which case AMD recommends

that the BIOS set EFER[3:2] to 10b or 11b (best performance).

26 Model 8/[F:8] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Write Handling Control Register (WHCR)

The Write Handling Control Register (WHCR) (see Figure 6 on

page 28) is an MSR that contains two fields—the Write Allocate

Enable Limit (WAELIM) field and the Write Allocate Enable

15-to-16-Mbyte (WAE15M) bit. The WHCR register is MSR

C000_0082h.

Note: The WHCR register as defined in the models 7 and 8/[7:0] is

defined differently in models 8/[F:8], 9, and D. A complete

description of the newly defined register is included in this

section for models 8/[F:8], 9, and D.

AMD-K6 processors contain a split level-1 (L1) 64-Kbyte

writeback cache organized as a separate 32-Kbyte instruction

cache and a 32-Kbyte data cache with two-way set associativity.

The cache line size is 32 bytes, and lines are read from memory

using an efficient pipelined burst read cycle. Further

performance gains are achieved by the implementation of a

write allocation scheme.

Write Allocation A write allocate, if enabled, occurs when the processor has a

pending memory write cycle to a cacheable line and the line

does not currently reside in the L1 cache. For more information

on write allocate, see the Implementation of Write Allocate in the

K86™ Processors Application Note, order# 21326 and see the

“Cache Organization” chapter in the appropriate AMD-K6 or

AMD-K6E processor data sheet.

This section describes two programmable mechanisms used by

the processor to determine when to perform write allocate.

When either of these mechanisms indicates that a pending

write is to a cacheable area of memory, a write allocate is

performed.

Before enabling write allocate or changing memory

cacheability, the BIOS must write back and invalidate the

internal cache by using the WBINVD instruction. In addition,

write allocate should be enabled only after performing any

memory sizing or typing algorithms.

Model 8/[F:8] Registers 27

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

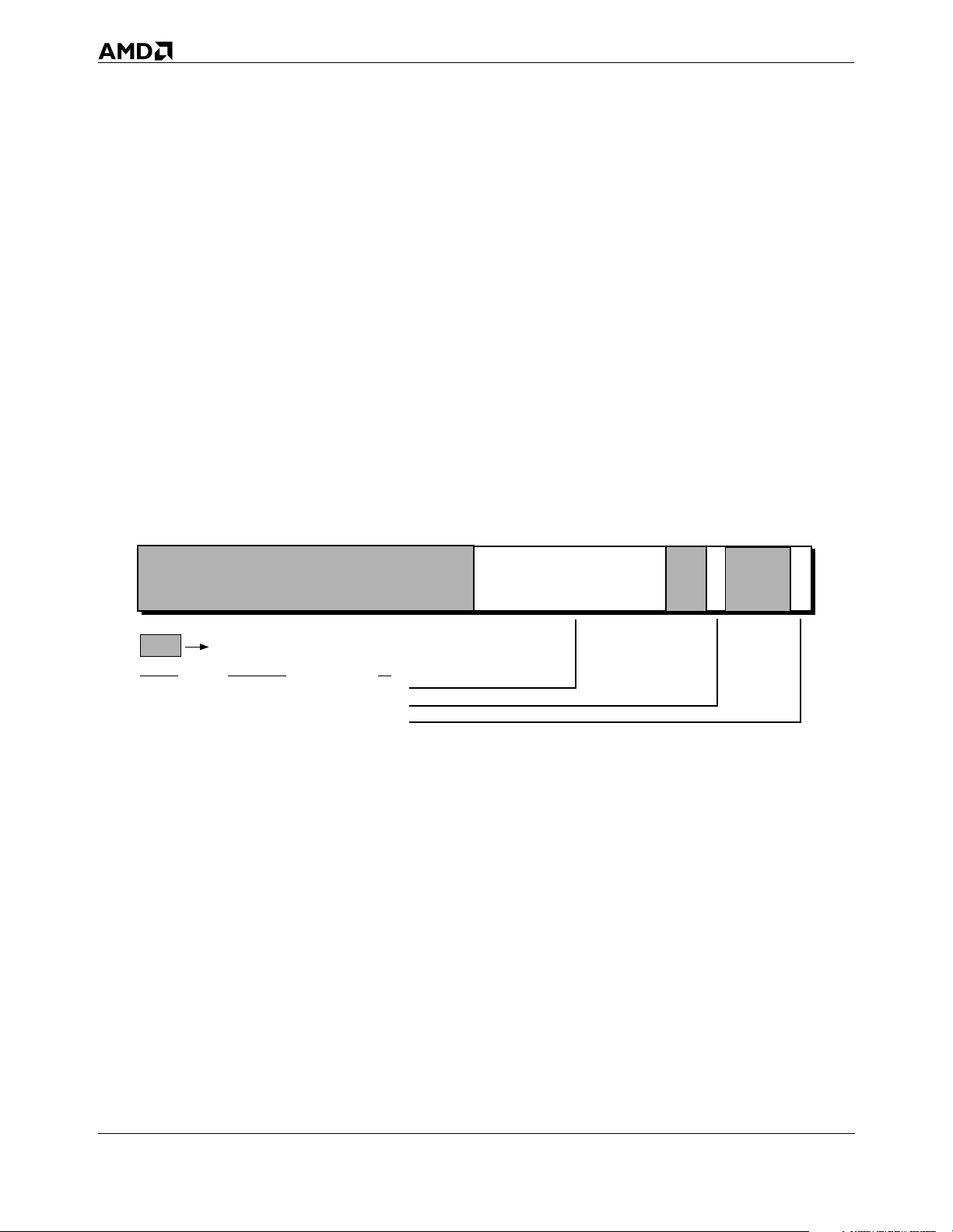

16

17

213132

WAELIM

Reserved

Symbol Description Bits

WAELIM Write Allocate Enable Limit 31-22

WAE15M Write Allocate Enable 15-to-16-Mbyte 16

Note: Hardware RESET initializes this MSR to all zeros.

1522 063

W

A

E

1

5

M

Figure 6. Write Handling Control Register (WHCR) (Models 8/[F:8], 9, and D)

Write Allocate Enable Limit Field

The WAELIM field is 10 bits wide. This field, multiplied by 4

Mbytes, defines an upper memory limit. Any pending write

cycle that misses the L1 cache and that addresses memory

below this limit causes the processor to perform a write allocate

(assuming the address is not within a range where write

allocates are disallowed).

Write allocate is disabled for memory accesses at and above this

limit unless the processor determines a pending write cycle is

cacheable by means of one of the other write allocate

mechanisms—“Write to a Cacheable Page” and “Write to a

Sector” (for more information, see the “Cache Organization”

chapter in the appropriate AMD-K6 or AMD-K6E processor

data sheet.

10

The maximum value of this limit is ((2

–1) · 4 Mbytes) = 4092

Mbytes. When all the bits in this field are set to 0, all memory is

above this limit and the write allocate mechanism is disabled

(even if all bits in the WAELIM field are set to 0, write allocates

can still occur due to the “Write to a Cacheable Page” and

“Write to a Sector” mechanisms).

Once the BIOS determines the amount of RAM installed in the

system, this number should also be used to program the

WAELIM field. For example, a system with 32 Mbytes of RAM

would program the WAELIM field with the value

00_0000_1000b. This value (8), when multiplied by 4 Mbytes,

yields 32 Mbytes as the write allocate limit.

28 Model 8/[F:8] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Write Allocate Enable

15-to-16-Mbyte Field

The WAE15M bit is used to enable write allocations for the

memory write cycles that address the 1 Mbyte of memory

between 15 Mbytes and 16 Mbytes. This bit must be set to 1 to

allow write allocates in this memory area.

This sub-mechanism of the WAELIM provides a memory hole to

prevent write allocates. This memory hole is provided to

account for a small number of uncommon memory-mapped I/O

adapters that use this particular memory address space. If the

system contains one of these peripherals, the bit should be set

to 0 (even if the WAE15M bit is set to 0, write allocates can still

occur between 15 Mbytes and 16 Mbytes due to the “Write to a

Cacheable Page” and “Write to a Sector” mechanisms). The

WAE15M bit is ignored if the value in the WAELIM field is set

to less than 16 Mbytes.

By definition, write allocations are not performed in the

memory area between 640 Kbytes and 1 Mbyte unless the

processor determines a pending write cycle is cacheable by

means of “Write to a Cacheable Page” or “Write to a Sector.” It

is not safe to perform write allocations between 640 Kbytes and

1 Mbyte (000A_0000h to 000F_FFFFh) because it is considered

a noncacheable region of memory. Additionally, if a memory

region is defined as write-combinable or uncacheable by a

MTRR, write allocates are not performed in that region.

Model 8/[F:8] Registers 29

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

UC/WC Cacheability Control Register (UWCCR)

Models 8/[F:8], 9, and D provide two variable-range Memory

Type Range Registers (MTRRs)—MTRR0 and MTRR1—that

each specify a range of memory. Each range can be defined as

one of the following memory types:

■ Uncacheable (UC) Memory—Memory read cycles are sourced

directly from the specified memory address, and the

processor does not allocate a cache line. Memory write

cycles are targeted at the specified memory address, and a

write allocation does not occur.

■ Write-Combining (WC) Memory—Memory read cycles are

sourced directly from the specified memory address, and the

processor does not allocate a cache line. The processor

conditionally combines data from multiple noncacheable

write cycles that are addressed within this range into a

merge buffer. Merging multiple write cycles into a single

write cycle reduces processor bus utilization and processor

stalls, thereby increasing the overall system performance.

This memory type is applicable for linear video frame

buffers.

Note: The MTRRs defined in this document are not software-

compatible to the MTRRs defined by the Pentium Pro and

Pentium II processors.

The programmer accesses the MTRRs by addressing the 64-bit

MSR known as the UC/WC Cacheability Control Register

(UWCCR). The MSR address of the UWCCR is C000_0085h.

Following reset, all bits in the UWCCR register are set to 0.

MTRR0 (lower 32 bits of the UWCCR register) defines the size

and memory type of range 0 and MTRR1 (upper 32 bits) defines

the size and memory type of range 1 (see Figure 7 on page 31).

Prior to programming write-combining or uncacheable areas of

memory in the UWCCR, the software must disable the

processor’s cache, then flush the cache. This can be achieved by

setting the CD bit in CR0 to 1 and executing the WBINVD

instruction. Following the programming of the UWCCR, the

processor’s cache must be enabled by setting the CD bit in CR0

to 0.

30 Model 8/[F:8] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Symbol Description Bits

UC1 Uncacheable Memory Type 32

WC1 Write-Combining Memory Type 33

Physical Address Mask 1Physical Base Address 1

MTRR1 MTRR0

W

C

1

Symbol Description Bits

UC0 Uncacheable Memory Type 0

WC0 Write-Combining Memory Type 1

3233344849

U

Physical Base Address 0

C

1

1731

16 063

Physical Address Mask 0

Figure 7. UC/WC Cacheability Control Register (UWCCR) (Models 8/[F:8], 9, and D)

Physical Base

Address n (n=0, 1)

This address is the 15 most-significant bits of the physical base

address of the memory range. The least-significant 17 bits of the

base address are not needed because the base address is by

definition always aligned on a 128-Kbyte boundary.

Physical Address

Mask n (n=0, 1)

This value is the 15 most-significant bits of a physical address

mask that is used to define the size of the memory range. This

mask is logically ANDed with both the physical base address

field of the UWCCR register and the physical address

generated by the processor. If the results of the two AND

operations are equal, then the generated physical address is

considered within the range. That is, if:

12

U

W

C

C

0

0

Mask & Physical Base Address = Mask & Physical Address Generated

then, the physical address generated by the processor is in the

range.

WCn (n=0, 1) When set to 1, this memory range is defined as write-

combinable (refer to Table 15). Write-combinable memory is

uncacheable.

UCn (n=0, 1) When set to 1, this memory range is defined as uncacheable

(refer to Table 15).

Table 15. WC/UC Memory Type for UWCCR Register

WCn UCn Memory Type

0 0 No effect on cacheability or write-combining

1 0 Write-combining memory range (uncacheable)

0 or 1 1 Uncacheable memory range

Model 8/[F:8] Registers 31

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

Memory-Range Restrictions

The following rules regarding the address alignment and size of

each range must be adhered to when programming the physical

base address and physical address mask fields of the UWCCR

register:

■ The minimum size of each range is 128 Kbytes.

■ The physical base address must be aligned on a 128-Kbyte

boundary.

■ The physical base address must be range-size aligned. For

example, if the size of the range is 1 Mbyte, then the

physical base address must be aligned on a 1-Mbyte

boundary.

■ All bits set to 1 in the physical address mask must be

contiguous. Likewise, all bits set to 0 in the physical address

mask must be contiguous. For example:

111_1111_1100_0000b is a valid physical address mask.

111_1111_1101_0000b is invalid.

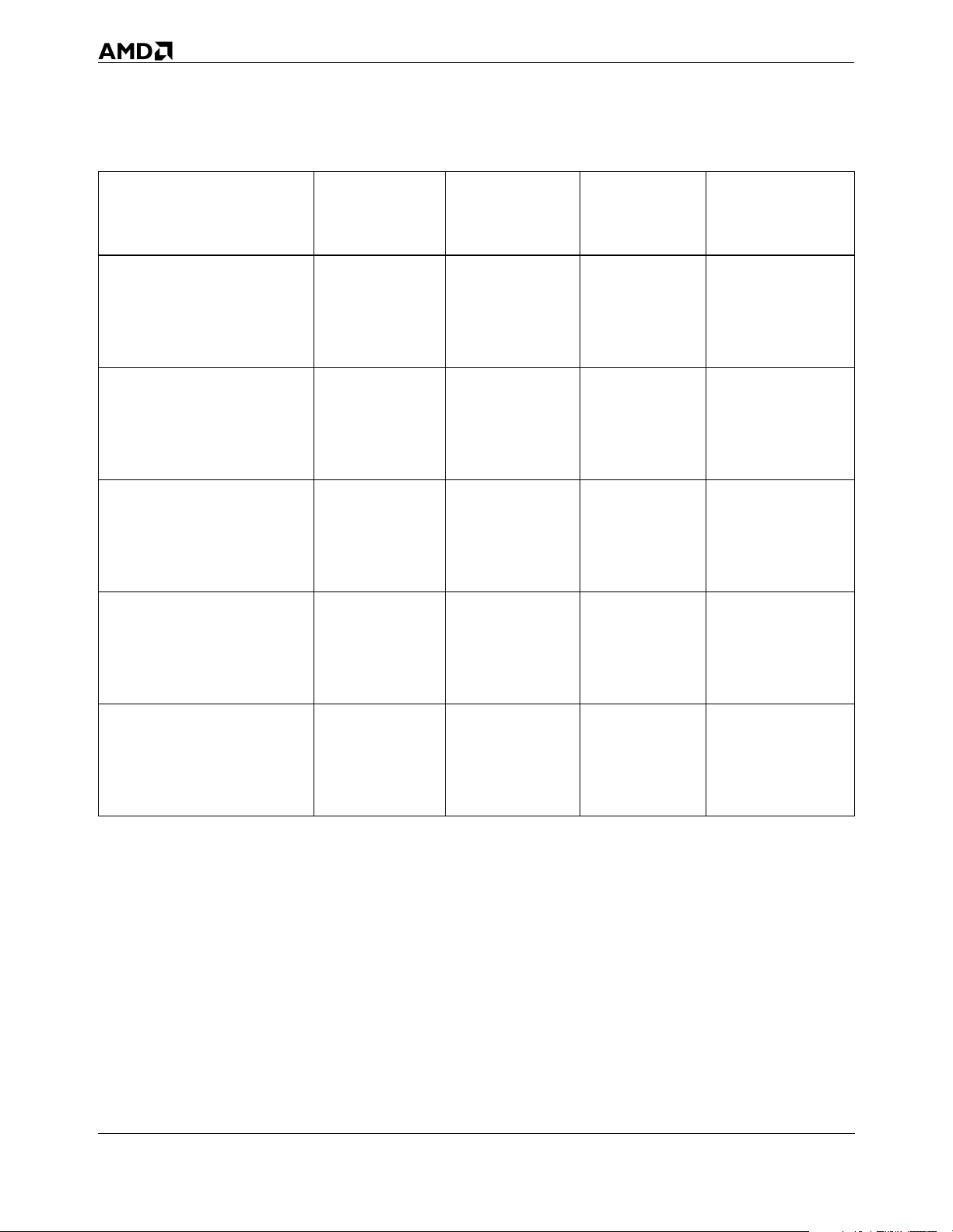

Table 16 lists the valid physical address masks and the resulting

range sizes that can be programmed in the UWCCR register.

Table 16. Valid Masks and Range Sizes for UWCCR Register

Masks Size

111_1111_1111_1111b 128 Kby tes

111_1111_1111_1110b 256 Kby tes

111_1111_1111_1100b 512 Kbytes

111_1111_1111_1000b 1 Mbyte

111_1111_1111_0000b 2 Mbytes

111_1111_1110_0000b 4 Mbytes

111_1111_1100_0000b 8 Mbytes

111_1111_1000_0000b 16 Mbytes

111_1111_0000_0000b 32 Mbytes

111_1110_0000_0000b 64 Mbytes

111_1100_0000_0000b 128 Mbytes

111_1000_0000_0000b 256 Mbytes

111_0000_0000_0000b 512 Mbytes

110_0000_0000_0000b 1 Gbyte

100_0000_0000_0000b 2 Gbytes

000_0000_0000_0000b 4 Gbytes

32 Model 8/[F:8] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Examples Suppose that the range of memory from 16 Mbytes to 32 Mbytes

is uncacheable, and the 8-Mbyte range of memory on top of 1

Gbyte is write-combinable. Range 0 is defined as the

uncacheable range, and range 1 is defined as the writecombining range.

■ Extracting the 15 most-significant bits of the 32-bit physical

base address that corresponds to 16 Mbytes (0100_0000h)

yields a physical base address 0 field of

000_0000_1000_0000b. Because the uncacheable range size

is 16 Mbytes, the physical mask value 0 field is

111_1111_1000_0000b, according to Table 16 on page 32. Bit

1 of the UWCCR register (WC0) is set to 0, and bit 0 of the

UWCCR register is set to 1 (UC0).

■ Extracting the 15 most-significant bits of the 32-bit physical

base address that corresponds to 1 Gbyte (4000_0000h)

yields a physical base address 1 field of

010_0000_0000_0000b. Because the write-combining range

size is 8 Mbytes, the physical mask value 1 field is

111_1111_1100_0000b, according to Table 16. Bit 33 of the

UWCCR register (WC1) is set to 1 and bit 32 of the UWCCR

register is set to 0 (UC1).

Model 8/[F:8] Registers 33

Preliminary Information

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000

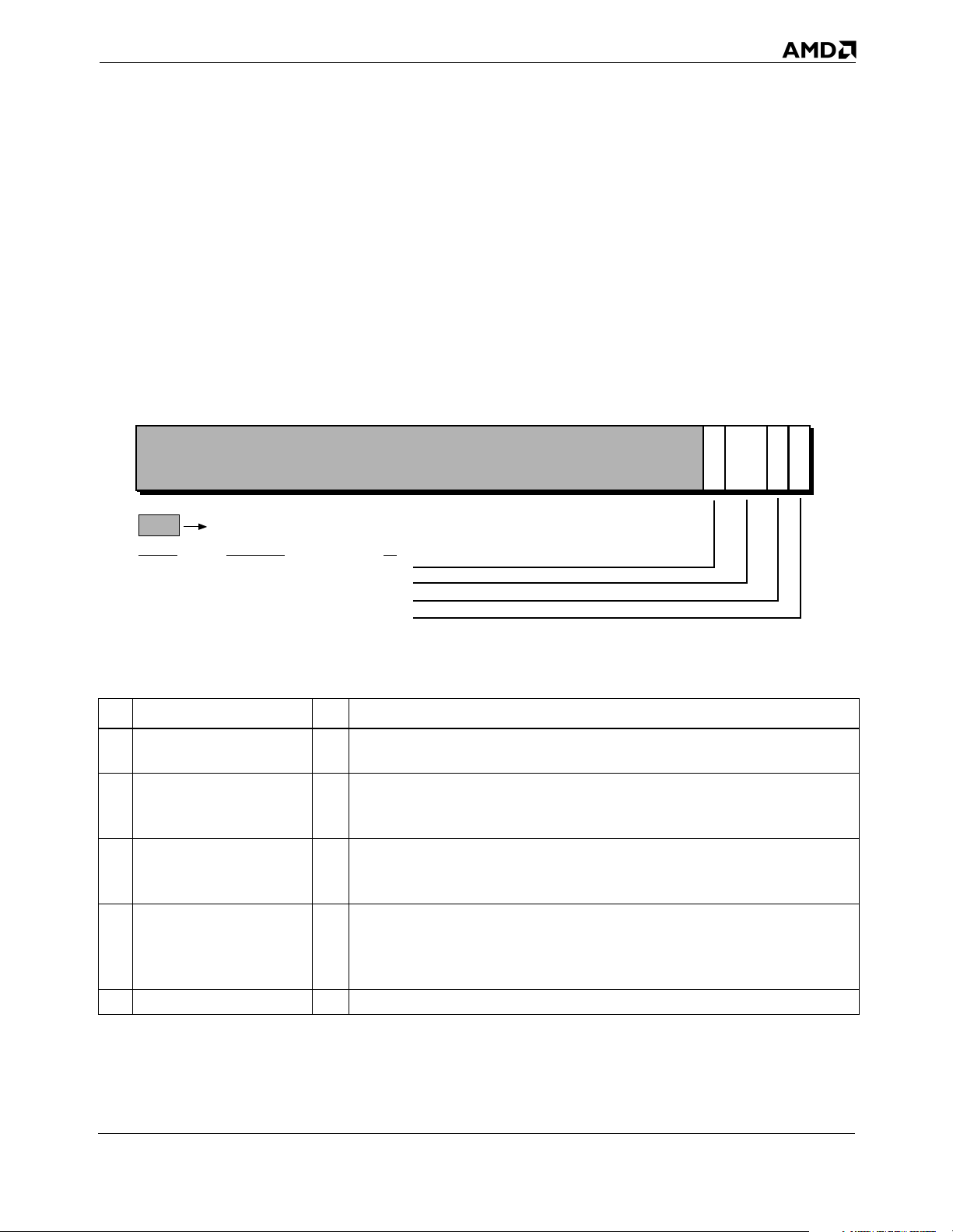

Processor State Observability Register (PSOR)

Models 8/[F:8], 9, and standard-power versions of Model D

provide the Processor State Observability Register (PSOR) as

defined in Figure 8. The PSOR register is MSR C000_0087h.

Note: See page 46 for definitions of the PSOR bit fields for low-

power Model D processors.

.

20

63

Reserved

Symbol Description Bit

NOL2 No L2 Functionality 8

STEP Processor Stepping 7-4

BF Bus Frequency Divisor 2-0

789

N

O

STEP

L

2

34

BF

Figure 8. Processor State Observability Register (PSOR) (Models 8/[F:8], 9, and Standard-Power D)

NOL2 Bit This read-only bit indicates whether the processor contains an

L2 cache.

Note: This bit is always set to 1 for Model 8/[F:8].

Note: This bit is always set to 0 for Models 9 and D.

STEP Field This read-only field contains the stepping ID. This is identical to

the value returned by the CPUID standard function 1 in

EAX[3:0].

BF Field This read-only field contains the value of the BF signals

sampled by the processor during the falling transition of

RESET, which allows the BIOS to determine the frequency of

the host bus.

■ The core frequency must first be known, which can be

determined using the Time Stamp Counter method (See

“Time Stamp Counter (TSC)” on page 16).

■ The core frequency is then divided by the processor-clock to

bus-clock ratio as determined by the BF field of the PSOR

register (see Table 17 and Table 18 on page 35).

■ The result is the frequency of the processor bus.

34 Model 8/[F:8] Registers

Preliminary Information

23913A/0—November 2000 Embedded AMD-K6™ Processors BIOS Design Guide

Table 17. Processor-to-Bus Clock Ratios (Models 8/[F:8] and 9)

State of BF[2:0] Processor-Clock to Bus-Clock Ratio

100b 2.5x

101b 3.0x

110b 6.0x

111b 3.5x

000b 4.5x

001b 5.0x

010b 4.0x

011b 5.5x