Page 1

24888 Rev 3.03 - July 12, 2004 AMD-8151

Cover page

TM

AGP Tunnel Data Sheet

AMD-8151TM HyperTransportTM AGP3.0 Graphics Tunnel

Data Sheet

1Overview

The AMD-8151

HyperTransport™ technology (referred to as link in this document) tunnel developed by AMD that provides an

AGP 3.0 compliant (8x transfer rate) bridge.

1.1 Device Features

• HyperTransport technology tunnel with side A

and side B.

• Side A is 16 bits (input and output); side B is

8 bits.

• Either side may connect to the host or to a

downstream HyperTransport technology

compliant device.

• Each side supports HyperTransport technol-

ogy-defined reduced bit widths: 8-bit, 4-bit,

and 2-bit.

• Side A supports transfer rates of 1600, 1200,

800, and 400 mega-transfers per second.

Side B supports transfer rates of 800 and

400 mega-transfers per second.

• Maximum bandwidth is 6.4 gigabytes per

second across side A (half upstream and half

downstream) and 1.6 gigabytes per second

across side B.

• Independent transfer rate and bit width

selection for each side.

• Link disconnect protocol supported.

TM

HyperTransportTM AGP3.0 Graphics Tunnel (referred to as the IC in this document) is a

• AGP 8x bridge.

• Compliance with AGP 3.0 specification signaling, supporting 4x and 8x transfer rates.

• Compliance with AGP 2.0 specification 1.5volt signaling, supporting 1x, 2x, and 4x

data-transfer modes.

• Supports up to 32 outstanding requests.

• 31 x 31 millimeter, 564-ball BGA package.

• 1.5 volt AGP signaling; some 3.3 volt IO; 1.2

volt link signaling; 1.8 volt core.

TM

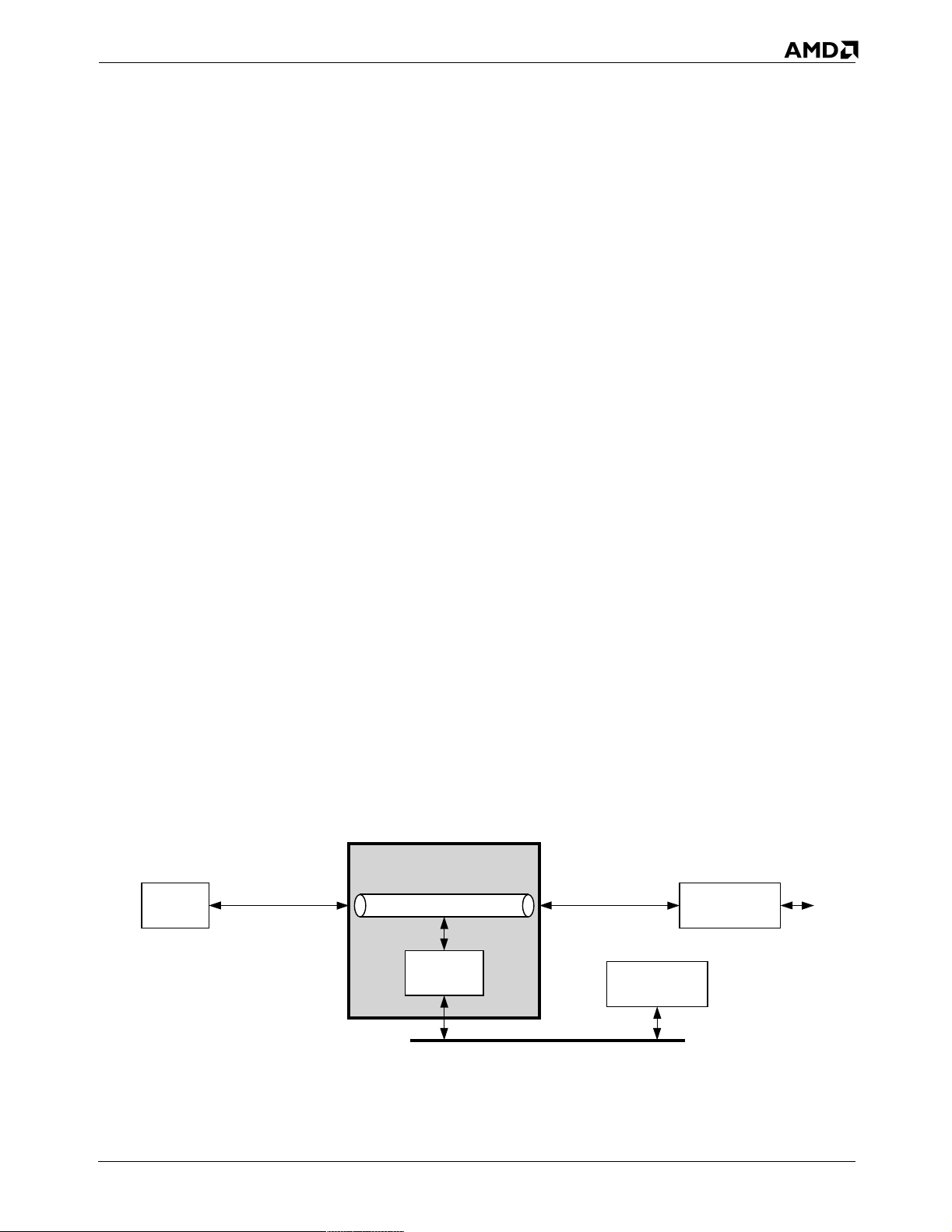

Host

HyperTransport

Link

16 bits upstream,

16 bits downstream

Figure 1: System block diagram.

AMD-8151TM Device

Side A Side B

tunnel

AGP

Bridge

HyperTransport

Link

8 bits upstream,

8 bits downstream

AGP Graphics

Controller

Downstream

Device

1

Page 2

24888 Rev 3.03 - July 12, 2004 AMD-8151

© 2004 Advanced Micro Devices, Inc.

All rights reserved.The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes

no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make

changes to specifications and product descriptions at any time without

notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication.

Except as set forth in AMD's Standard Terms and Conditions of Sale,

AMD assumes no liability whatsoever, and disclaims any express or

implied warranty, relating to its products including, but not limited to, the

implied warranty of merchantability, fitness for a particular purpose, or

infringement of any intellectual property right. AMD's products are not

designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications

intended to support or sustain life, or in any other application in which the

failure of AMD's product could create a situation where personal injury,

death, or severe property or environmental damage may occur. AMD

reserves the right to discontinue or make changes to its products at any

time without notice.

TM

AGP Tunnel Data Sheet

Trademarks

AMD, the AMD Arrow logo, and combinations thereof, and AMD-8151 are trademarks of Advanced Micro

Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Other product names used in this publication are for identification purposes only and may be trademarks of

their respective companies.

2

Page 3

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

Table of Contents

1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Device Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1 Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2 Tunnel Link Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.3 AGP Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.4 Test and Miscellaneous Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.5 Power and Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.5.1 Power Plane Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4 Functional Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.2 Reset And Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.3 Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.3.1 Clock Gating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.4 Tunnel Links . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.4.1 Link PHY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.5 AGP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.5.1 Tags, UnitIDs, And Ordering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.5.2 Various Behaviors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.5.2.1 AGP Compensation And Calibration Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.1 Register Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.1.1 Configuration Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.1.2 Register Naming and Description Conventions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.2 AGP Device Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.3 AGP Bridge Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

6 Electrical Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.1 Absolute Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2 Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.3 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.4 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

7 Ball Designations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8 Package Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

9 Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.1 High Impedance Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.2 NAND Tree Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

10 Appendix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

10.1 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3

Page 4

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

List of Figures

Figure 1: System block diagram................................................................................................................... 1

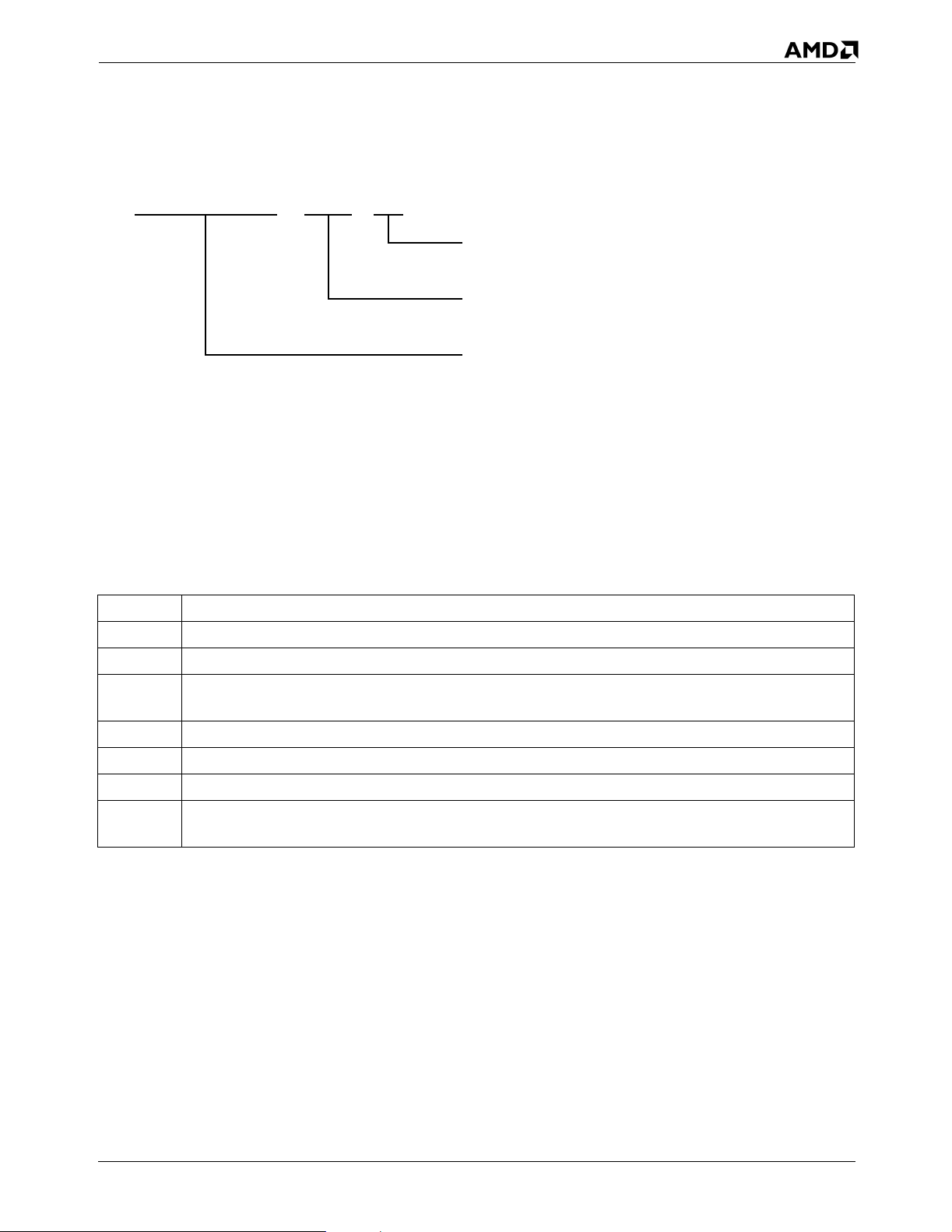

Figure 2: Configuration space. ................................................................................................................... 14

Figure 3: Ball designations......................................................................................................................... 39

Figure 4: Package mechanical drawing...................................................................................................... 42

Figure 5: NAND tree. ................................................................................................................................. 43

4

Page 5

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

List of Tables

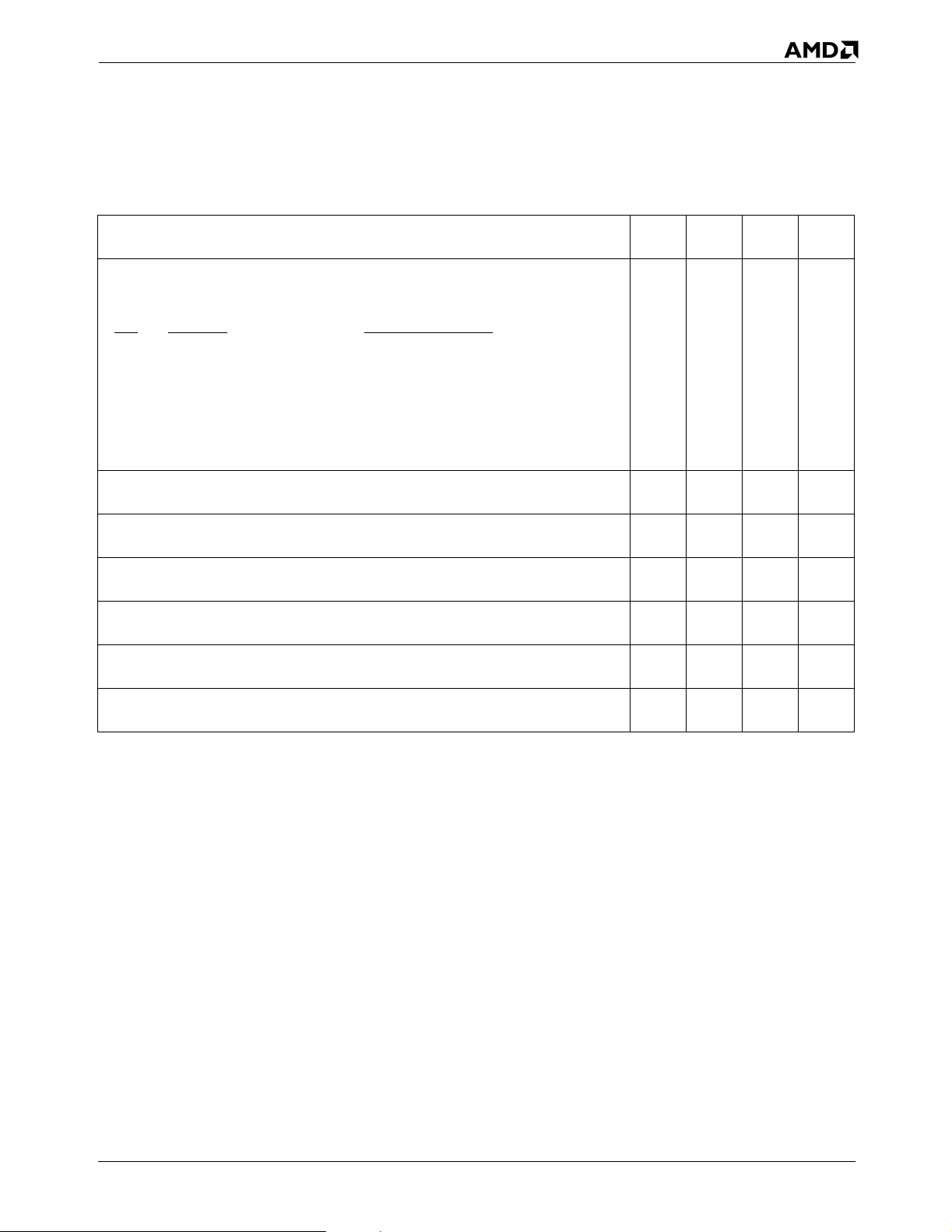

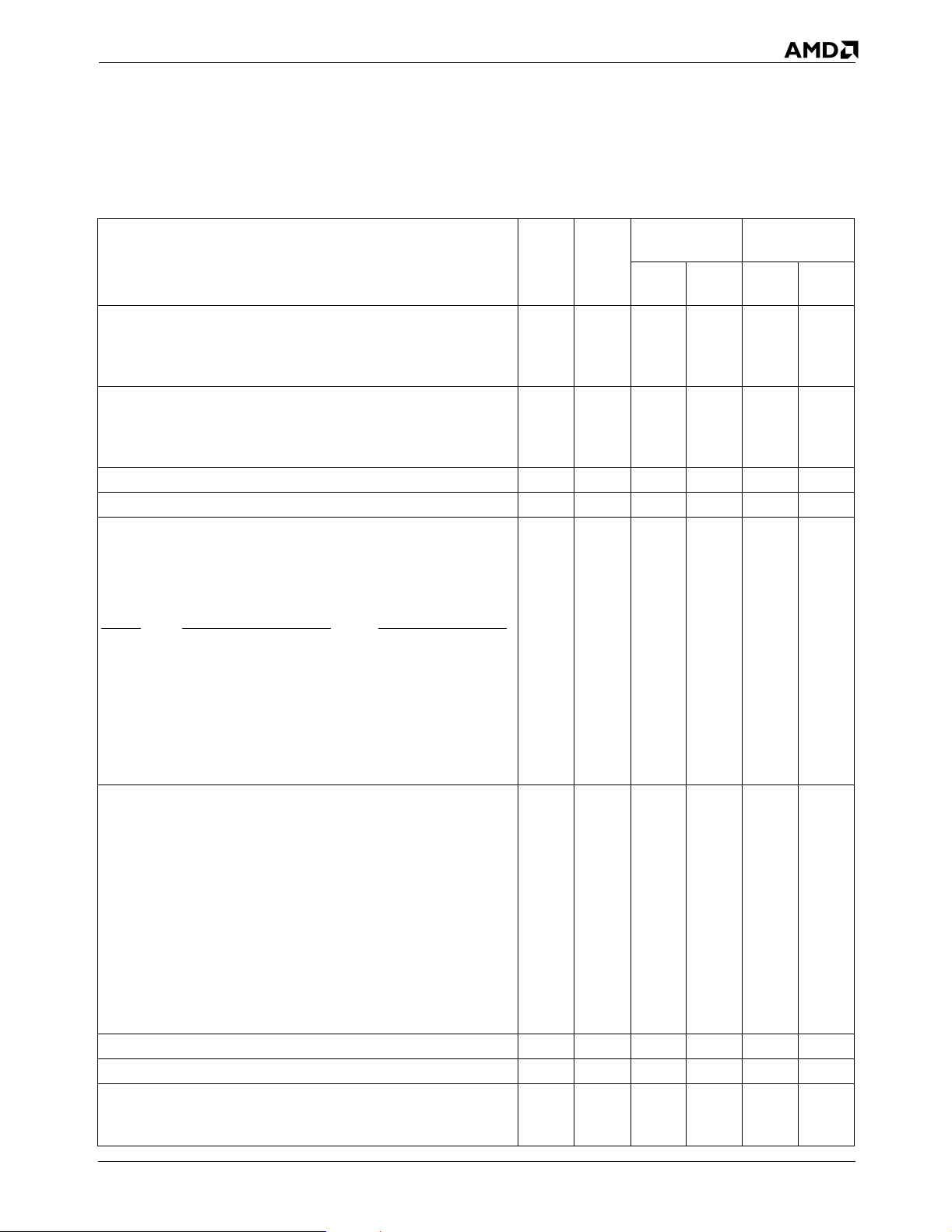

Table 1: IO signal types. ............................................................................................................................. 6

Table 2: Translation from AGP requests to link requests. ........................................................................ 13

Table 3: Configuration spaces................................................................................................................... 15

Table 4: Memory mapped address spaces................................................................................................. 15

Table 5: Register attributes. ...................................................................................................................... 15

Table 6: Absolute maximum ratings......................................................................................................... 34

Table 7: Operating ranges. ........................................................................................................................ 34

Table 8: Current and power consumption................................................................................................. 35

Table 9: DC characteristics for signals on the VDD33 power plane. ....................................................... 35

Table 10: DC characteristics for signals on the VDD15 power plane, AGP 2.0 signaling......................... 36

Table 11: DC characteristics for signals on the VDD15 power plane, AGP 3.0 signaling......................... 36

Table 12: AC data for clocks....................................................................................................................... 37

Table 13: AC data for common clock operation of AGP signals................................................................ 37

Table 14: AC data for clock-forwarded operation of AGP signals............................................................. 38

Table 15: Signal BGA positions.................................................................................................................. 40

Table 16: Power and ground BGA positions. ............................................................................................. 41

Table 17: Test modes................................................................................................................................... 43

5

Page 6

24888 Rev 3.03 - July 12, 2004 AMD-8151

2 Ordering Information

AMD-8151

3 Signal Descriptions

3.1 Terminology

See section 5.1.2 for a description of the register naming convention used in this document. See the

AMD-8151

TM

HyperTransportTM AGP3.0 Graphics Tunnel Design Guide for additional information.

BL C

Case Temperature

C = Commercial temperature range

Package Type

BL = Organic Ball Grid Array with lid

Family/Core

AMD-8151

TM

AGP Tunnel Data Sheet

Signals with a # suffix are active low.

Signals described in this chapter utilize the following IO cell types:

Name Notes

Input Input signal only.

Output Output signal only. This includes outputs that are capable of being in the high-impedance state.

OD Open drain output. These signals are driven low and expected to be pulled high by external cir-

cuitry.

IO Input or output signal.

IOD Input or open-drain output.

Analog Analog signal.

w/PU With pullup. The signal includes a pullup resistor to the signal’s power plane. The resistor value is

nominally 8K ohms.

Table 1: IO signal types.

The following provides definitions and reference data about each of the IC’s pins. “During Reset” provides the

state of the pin while RESET# is asserted. “After Reset” provides the state of the pin immediately after

RESET# is deasserted. “Func.” means that the pin is functional and operating per its defined function.

6

Page 7

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

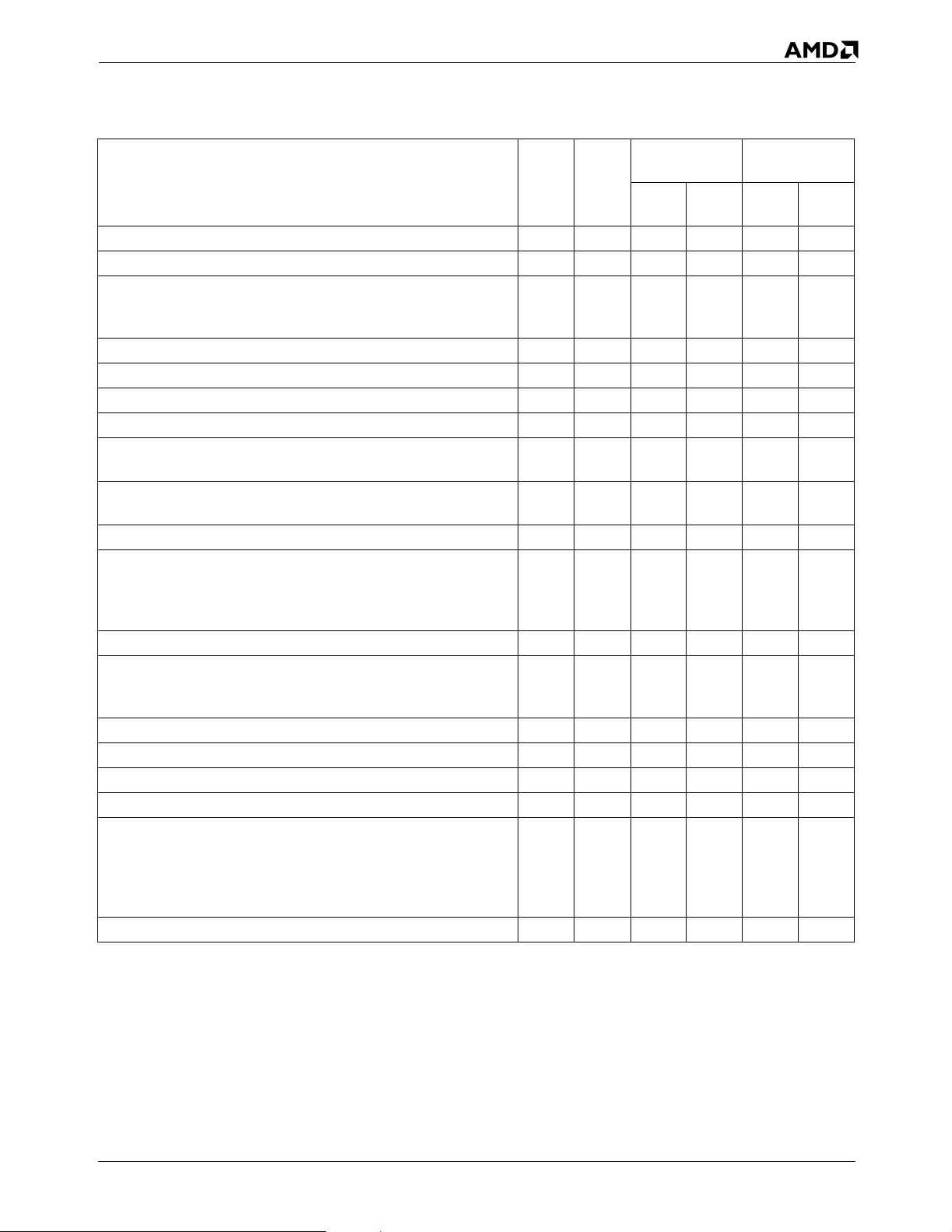

3.2 Tunnel Link Signals

TM

The following are signals associated with the HyperTransport

links. [B, A] in the signal names below refer

to the A and B sides of the tunnel. [P, N] are the positive and negative sides of differential pairs.

Pin name and description IO cell

type

LDTCOMP[3:0].

designed to be connected through resistors as follows:

Bit

[0] Positive receive compensation Resistor to VDD12B

[1] Negative receive compensationResistor to VSS

[3, 2] Transmit compensation Resistor from bit [2] to bit [3]

These resistors are used by the compensation circuit. The output of this circuit is

combined with DevA:0x[E8, E4, E0] to determine compensation values that are

passed to the link PHYs.

LRACAD_[P, N][15:0]; LRBCAD_[P, N][7:0]. Receive link command-address-

data bus.

LRACLK[1, 0]_[P, N]; LRBCLK0_[P, N]. Receive link clock. Link

LR[B, A]CTL_[P, N]. Receive link control signal. Link

LTACAD_[P, N][15:0]; LTBCAD_[P, N][7:0]. Transmit link command-address-

data bus.

LTACLK[1, 0]_[P, N]; LTBCLK0_[P, N]. Transmit link clock. Link

LT[B, A]CTL_[P, N]. Transmit link control signal. Link

Function External Connection

Link compensation pins for both sides of the tunnel. These are

Analog VDD-

Link

input

input

input

Link

output

output

output

Power

plane*

VDD12

VDD12

VDD12

VDD12 Diff

VDD12 Func. Func.

VDD12 Diff

12B

During

reset

High**

Low**

After

reset

Func.

Func.

* The signals connected to the A side of the tunnel are powered by VDD12A and the signals connected to the

B side of the tunnel are powered by VDD12B.

** Diff High and Diff Low for these link pins specifies differential high and low; e.g., Diff High specifies that

the _P signal is high and the _N signal is low.

If one of the sides of the tunnel is not used on a platform then the unconnected link should be treated as follows, for every 10 differential pairs: connect all of the _P differential inputs together and through a resistor to

VSS; connect all the _N differential inputs together and through a resistor to VDD12; leave the differential outputs unconnected. If there are unused link signals on an active link (because the IC is connected to a device

with a reduced bit width), then the unused differential inputs and outputs should also be connected in this way.

7

Page 8

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

3.3 AGP Signals

In the table below, “Term” indicates the standard AGP 3.0 termination impedance to ground; “PU”

indicates a weak pullup resistor; “PD” indicates a weak pulldown resistor.

Pin name and description IO cell

type

A_ADSTB0_[P, N].

A_CBE_L[1:0]. When AGP 3.0 signaling is enabled,

A_ADSTB0_P is the first strobe and A_ADSTB0_N is the second

strobe.

A_ADSTB1_[P, N]. AGP differential strobe for AD[31:16],

A_CBE_L[3:2], and A_DBI[H,L]. When AGP 3.0 signaling is

enabled, A_ADSTB1_P is the first strobe and A_ADSTB1_N is

the second strobe.

A_AD[31:0]. AGP address-data bus. IO VDD15 Term Term PU Low

A_CBE_L[3:0]. AGP command-byte enable bus. IO VDD15 Term Term PU Low

A_CAL[D, S] and A_CAL[D, S]#. Compensation pins for

matching impedance of system board AGP traces. See

DevA:0x[54, 50] for more information. These are designed to be

connected through resistors as follows:

AGP differential strobe for A_AD[15:0] and

Analog VDD15

Power

plane

IO V DD15 Te rm Te rm _P : PU

IO V DD15 Te rm Te rm _P : PU

AGP 3.0

Signaling

During

reset

After

reset

AGP 2.0

Signaling

During

reset

_N: PD

_N: PD

After

reset

_P: PU

_N: PD

_P: PU

_N: PD

Signal

A_CALD Rising edge of data signals Resistor to VSS

A_CALD# Falling edge of data signals Resistor to VDD15

A_CALS Rising edge of strobe signals Resistor to VSS

A_CALS# Falling edge of strobe signals Resistor to VDD15

These resistors are used by the compensation circuit. The output of

this circuit is combined with DevA:0x[54, 50] to determine compensation values that are passed to the link PHYs.

A_DBI[H, L]. Data bus inversion [high, low]. When

DevA:0xA4[AGP3MD]=1, A_DBIL applies to AD[15:0];

A_DBIH applies to AD[31:16]. 1=AD signals are inverted.

0=A_AD signals are not inverted. The IC uses these signals in

determining the polarity of the A_AD signals when they are

inputs. These may also be enabled to support the DBI function of

the IC output signals by DevA:0x40[DBIEN]. Both A_DBIH and

A_DBIL are strobed with A_ADSTB1_[P, N].

When DevA:0xA4[AGP3MD]=0: A_DBIL is pulled low with the

AGP termination value and not used by the IC; A_DBIH is pulled

up to VDD15 through a weak resistor and becomes the AGP 2.0

PIPE# input signal.

A_DEVSEL#. AGP device select. IO VDD15 Term Term PU PU

A_FRAME#. AGP frame signal. IO VDD15 Term Term PU PU

A_GC8XDET#. 0=Specifies that the graphics device supports

AGP 3.0 signaling. The state of this signal is latched on the rising

edge of A_RESET# before being passed to internal logic.

Compensation Function External Connection

IO V DD15 Te rm Te rm PU PU

Input

w/PU

VDD15 PU PU PU PU

8

Page 9

24888 Rev 3.03 - July 12, 2004 AMD-8151

Pin name and description IO cell

type

A_GNT#. AGP master grant signal. Output VDD15 Term Low PU High

A_IRDY#. AGP master ready signal. IO VDD15 Term Term PU PU

A_MB8XDET#. This pin is controlled by DevA:0x40[8XDIS]. It

is designed to be connected to the AGP connector to indicate

support for AGP 3.0 signaling.

A_PAR. AGP parity signal. IO VDD15 Term Term PU Low

A_PCLK. 66 MHz AGP clock. Output VDD33 Func. Func. Func. Func.

A_PLLCLKO. PLL clock output. See section 4.3 for details. Output VDD33 Func. Func. Func. Func.

A_PLLCLKI. PLL clock input. See section 4.3 for details. Input VDD33

A_REFCG. AGP signal reference output. Analog

A_REFGC. AGP signal reference input. Analog

A_REQ#. AGP master request signal. Input VDD15 Term Term PU PU

A_RESET#. AGP bus reset signal. This is asserted whenever

RESET# is asserted or when programmed by

DevB:0x3C[SBRST]. Assertion of this pin does not reset any logic

internal to the IC.

A_RBF#. AGP read buffer full signal. Input VDD15 Term Term PU PU

A_SBSTB_[P, N]. AGP differential side band address strobe. In

AGP 3.0 signaling mode, A_SBSTB_P is the first strobe and

A_SBSTB_N is the second strobe.

A_SBA[7:0]. AGP side band address signals. Input VDD15 Term Term PU PU

A_ST[2:0]. AGP status signals. Output VDD15 Term Low PU Low

A_STOP#. AGP target abort signal. IO VDD15 Term Term PU PU

A_TRDY#. AGP target ready signal. IO VDD15 Term Term PU PU

A_TYPEDET#. AGP IO voltage level type detect. 0=1.5 volts;

1=3.3 volts (not supported by the IC). The state of this pin is

provided in DevA:0x40[TYPEDET]. This pin is also used for testmode selection; see section 9. This signal requires an external

pullup resistor to VDD33 on the systemboard.

A_WBF#. AGP write buffer full signal. Input VDD15 Term Term PU PU

Output VDD15 Low Low Low Low

output

input

Output VDD33 Low High Low High

Inp ut V DD15 Te rm Te rm _P : PU

Input VDD33

Power

plane

VDD15

VDD15

TM

AGP 3.0

Signaling

During

reset

AGP Tunnel Data Sheet

AGP 2.0

Signaling

After

reset

During

reset

_N: PD

After

reset

_P: PU

_N: PD

The SERR# and PERR# signals are not supported on the AGP bridge.

9

Page 10

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

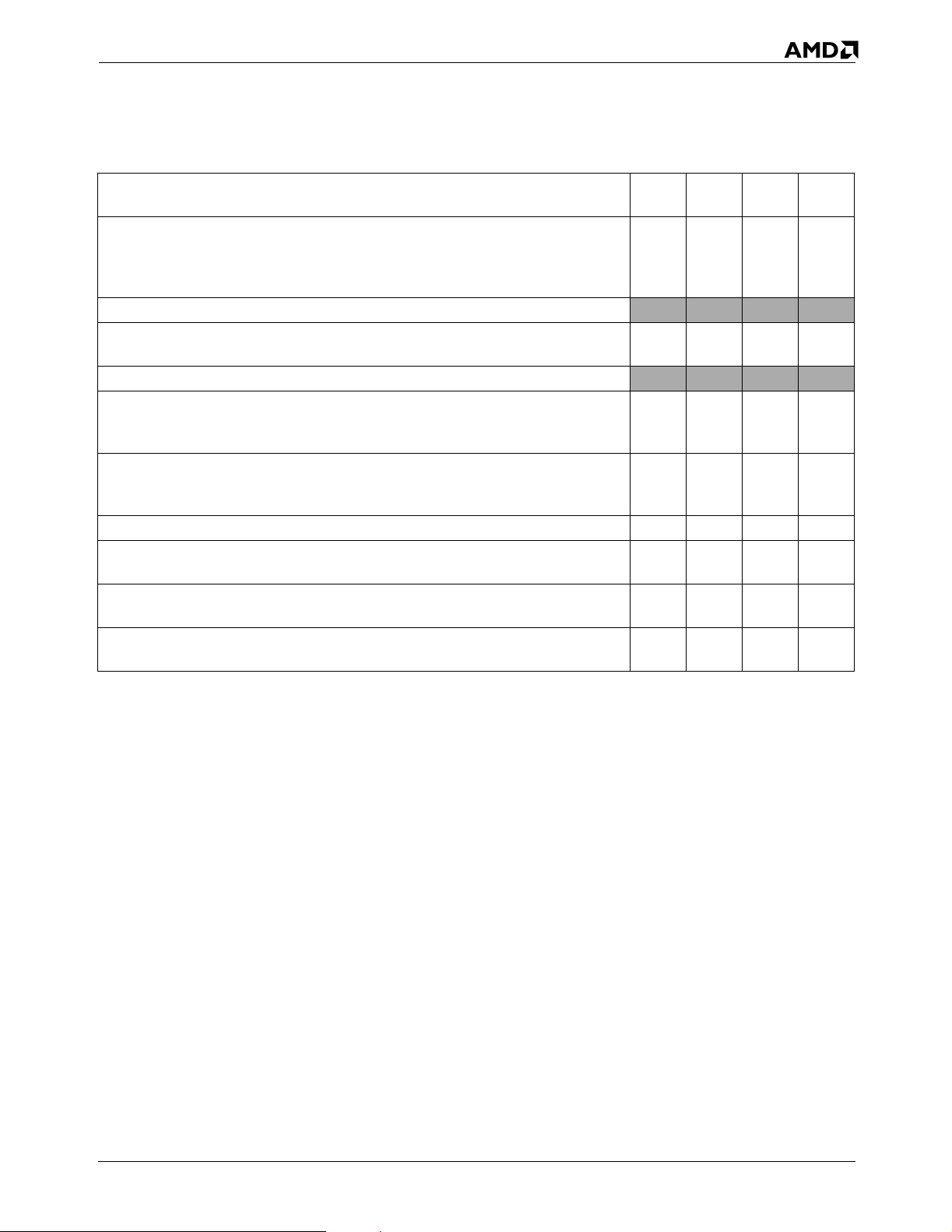

3.4 Test and Miscellaneous Signals

Pin name and description IO cell

type

CMPOVR.

is enabled. 1=The compensation values stored in DevA:0x[E0, E4, E8] control the

compensation circuit. The state of this signal determines the default value for

DevA:0x[E0, E4, E8][ACTL and BCTL] at the rising edge of PWROK.

FREE[7:1]. These should be left unconnected.

LDTSTOP#. Link disconnect control signal. This pin is also used for test-mode

selection; see section 9.

NC[1:0]. These should be left unconnected.

PWROK. Power OK. 1=All power planes are valid. The rising edge of this signal is

deglitched; it is not observed internally until it is high for more than 6 consecutive

REFCLK cycles. See section 4.2 for more details about this signal.

REFCLK. 66 MHz reference clock. This is required to be operational and valid for a

minimum of 200 microseconds prior to the rising edge of PWROK and always while

PWROK is high.

RESET#. Reset input. See section 4.2 for details. Input VDD33

STRAPL[19:13, 11:0]. Strapping option to be tied low. These pins should be tied to

ground. STRAPL0 is used for test-mode selection; see section 9.

STRAPL[22:20]. Strapping option to be tied low. These pins should be tied to

ground.

TEST. This is required to be tied low for functional operation. See section 9 for

details.

Link automatic compensation override. 0=Link automatic compensation

Input VDD33

Input VDD33

Input VDD33

Input VDD33

Input VDD33

Power

plane

IO VDD15 3-State 3-State

IO VDD33 3-State 3-State

During

reset

After

reset

3.5 Power and Ground

VDD12[B, A]. 1.2 volt power plane for the HyperTransport

TM

technology pins. VDD12A provides power to

the A side of the tunnel. VDD12B provides power to the B side of the tunnel.

VDD15. 1.5 volt power plane for AGP.

VDD18. 1.8-volt power plane for the core of the IC.

VDDA18. Analog 1.8-volt power plane for the PLLs in the core of the IC. This power plane is required to be

filtered from digital noise.

VDD33. 3.3-volt power plane for IO.

VSS. Ground.

3.5.1 Power Plane Sequencing

The following are power plane requirements that may imply power supply sequencing requirements.

• VDD33 is required to always be higher than VDD18, VDDA18, VDD15, and VDD12[B, A].

• VDD18 and VDDA18 are required to always be higher than VDD15 and VDD12[B, A].

• VDD15 is required to always be higher than VDD12[B, A].

10

Page 11

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

4 Functional Operation

4.1 Overview

TM

The IC connects to the host through either the side A or side B HyperTransport

link interface. The other side

of the tunnel may or may not be connected to another device. Host-initiated transactions that do not target the

IC or the bridge flow through the tunnel to the downstream device. Transactions claimed by the device are

passed to internal registers or to the AGP bridge.

See section 5.1 for details about the software view of the IC. See section 5.1.2 for a description of the register

naming convention. See the AMD-8151

TM

HyperTransportTM AGP3.0 Graphics Tunnel Design Guide for addi-

tional information.

4.2 Reset And Initialization

RESET# and PWROK are both required to be low while the power planes to the IC are invalid and for at least

1 millisecond after the power planes are valid. Deassertion of PWROK is referred to as a cold reset. After

PWROK is brought high, RESET# is required to stay low for at least 1 additional millisecond. After RESET#

is brought high, the links go through the initialization sequence.

After a cold reset, the IC may be reset by asserting RESET# while PWROK remains high. This is referred to as

a warm reset. RESET# must be asserted for no less than 1 millisecond during a warm reset.

4.3 Clocking

It is required that REFCLK be valid in order for the IC to operate. Also, the LR[B, A]CLK inputs from the

operation links must also be valid at the frequency defined DevA:0xCC[FREQA] and DevA:0xD0[FREQB].

The IC provides A_PCLK as the clock to the AGP device.

The systemboard is required to include a connection from A_PLLCLKO to A_PLLCLKI. The length of this

connection is required to be approximately the same as length of the A_PCLK trace from the IC to the external

AGP devices (including approximately 2.5 inches of etch on the AGP card). The IC uses this loopback to help

match the external trace delay.

4.3.1 Clock Gating

Internal clocks may be disabled during power-managed system states such as power-on suspend. It is required

that all upstream requests initiated by the IC be suspended while in this state.

To enable clock gating, DevA:0xF0[ICGSMAF] is programmed to the values in which clock gating will be

enabled. Stop Grant cycles and STPCLK deassertion link broadcasts interact to define the window in which the

IC is enabled for clock gating during LDTSTOP# assertions. The system is placed into power managed states

by steps that include a broadcast over the links of the Stop Grant cycle that includes the System Management

Action Field (SMAF) followed by the assertion of LDTSTOP#. When the IC detects the Stop Grant broadcast

which is enabled for clock gating, it enables clock gating for the next assertion of LDTSTOP#. While exiting

the power-managed state, the system is required to broadcast a STPCLK deassertion message. The IC uses this

message to disable clock gating during LDTSTOP# assertions. This is important because an LDTSTOP# assertion is not guaranteed to occur after the Stop Grant broadcast is received. The clock gating window must be

closed to insure that clock gating does not occur during Stop Grant for LDTSTOP# assertions that are not associated with the power states specified by DevA:0xF0[ICGSMAF].

11

Page 12

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

In summary, Stop Grant broadcasts with SMAF fields specified by DevA:0xF0[ICGSMAF] enable the clock

gating window and STPCLK deassertion broadcasts disable the window. If LDTSTOP# is asserted while the

clock gating window is enabled, then clock gating occurs.

Also, DevA:0xF0[ECGSMAF] may be used in a similar way to disable A_PCLK and the internal clock grids

associated with the AGP bridge. The same rules for the clock gating window that apply to DevA:0xF0[ICGSMAF] also apply to DevA:0xF0[ECGSMAF]. If clock gating is enabled, then A_PCLK is forced low within

two clock periods after LDTSTOP# is asserted. It becomes active again within two clock periods after LDTSTOP# is deasserted. It is required that there be no AGP-card-initiated upstream or downstream traffic while

A_PCLK is gated. In addition, it is required that there be no host accesses to the bridge or internal registers in

progress from the time that LDTSTOP# is asserted for clock gating until the link reconnects after LDTSTOP#

is deasserted.

4.4 Tunnel Links

HyperTransport link A supports CLK receive and transmit frequencies of 200, 400, 600, and 800 MHz. Link B

supports frequencies of 200 and 400 MHz. The side A and side B frequencies are independent of each other.

4.4.1 Link PHY

The PHY includes automatic compensation circuitry and a software override mechanism, as specified by

DevA:0x[E8, E4, E0]. The IC only implements synchronous mode clock forwarding FIFOs. So only the link

receive and transmit frequencies specified in DevA:0x[D0, CC][FREQB, FREQA] are allowed.

4.5 AGP

The AGP bridge supports AGP 3.0 signaling at 8x and 4x data rates and 1.5-volt AGP 2.0 signaling at 4x, 2x,

and 1x data rates. 64-bit upstream and 32-bit downstream addressing is supported. AGP 3.0 dynamic bus inversion is supported on output signals in 8X mode only, not in 4X mode; dynamic bus inversion on input signals is

supported in both 4X and 8X modes.

4.5.1 Tags, UnitIDs, And Ordering

The IC requires three HyperTransport

TM

technology-defined UnitIDs. They are allocated as follows:

• First UnitID is not used. This is to avoid a potential conflict with the host (because it may be zero; see

DevA:0xC0[BUID]).

• Second UnitID is used for PCI-mode upstream requests and responses to host requests.

• Third UnitID is used for AGP (high priority and low priority) upstream requests.

The SrcTag value that is assigned to upstream non-posted AGP requests increments with each request from 0

to 27 and then rolls over to 0 again; the first SrcTag assigned after reset is 0. Up to 28 non-posted link requests

may be outstanding at a time. The SrcTag value that is assigned to non-posted PCI requests is always 28.

12

Page 13

24888 Rev 3.03 - July 12, 2004 AMD-8151

All AGP transactions are compliant to AGP ordering rules. APG transactions are translated into link transactions as follows:

AGP transaction Link transaction

High priority write WrSized, posted channel, PassPW = 1

High priority read RdSized, PassPW = 1, response PassPW = 1

Low priority write WrSized, posted channel, PassPW = 0

Low priority read RdSized, PassPW = 0, response PassPW = 1

Low priority flush Flush, PassPW = 0

Low priority fence None (wait for all outstanding read responses)

TM

AGP Tunnel Data Sheet

Table 2: Translation from AGP requests to link requests.

4.5.2 Various Behaviors

• The AGP bridge does not claim link special cycles. However, special cycles that are encoded in configura-

tion cycles to device 31 of the AGP secondary bus number (per the PCI-to-PCI bridge specification) are

translated to AGP bus special cycles.

• AGP and PCI read transactions that receive NXA responses from the host complete onto the AGP bus with

the data provided by the host (which is required to be all 1’s, per the link specification).

• In the translation from type 1 link configuration cycles to secondary bus type 0 configuration cycles, the IC

converts the device number to IDSEL AD signal as follows: device 0 maps to AD[16]; device 1 maps to

AD[17]; and so forth. Device numbers 16 through 31 are not valid.

• The compensation values for drive strength and input impedance that are assigned to non-clock forwarded

AGP signals are automatically determined and set by the IC during the first compensation cycle after

RESET#. Once set, they do not change until the next RESET# assertion.

• Per the link protocol, when the COMPAT bit is set in the transaction, the IC does not ever claim the transac-

tion. Such transactions are automatically passed to the other side of the tunnel (or master aborted if the IC is

at the end of the chain). This is true of all transactions within address space that is otherwise claimed by the

IC, including the space defined by DevB:0x3C[VGAEN].

4.5.2.1 AGP Compensation And Calibration Cycles

The AGP PHY includes one compensation circuit for the clock forwarded data signals, A_AD[31:0],

A_CBE_L[3:0], and A_DBI[H, L], and one compensation circuit for the strobes, A_ADSTB[1:0]. Each compensation circuit calculates the required rising-edge (P) and falling-edge (N) signal drive strength through a

free-running state machine that generates a new value approximately every four microseconds. These values

are provided in DevA:0x[50, 54][NCOMP, PCOMP].

Programmable skew values between data signals and strobes are also provided in DevA:0x58.

The compensation values provided to the AGP PHY are software selectable between the calculated compensation values, fixed programmable bypass values, or fixed programmable offsets from the calculated values.

Regardless of which value is selected, the value presented to the PHY is never updated until there is a calibration cycle.

Calibration cycles consist of taking control of the AGP bus, updating the AGP PHY compensation values, and

then releasing (see DevA:0xA8[PCALCYC]). If enabled by DevA:0xB0[CALDIS], they occur periodically

with the period specified by DevA:0xA8[PCALCYC].

13

Page 14

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

The first calibration cycle occurs approximately 4 milliseconds after the deassertion of RESET# (whether AGP

2.0 or 3.0 signaling is enabled).

5 Registers

5.1 Register Overview

The IC includes several sets of registers accessed through a variety of address spaces. IO address space refers

to register addresses that are accessed through x86 IO instructions such as IN and OUT. PCI configuration

space is typically accessed by the host through IO cycles to CF8h and CFCh. There is also memory space and

indexed address space in the IC.

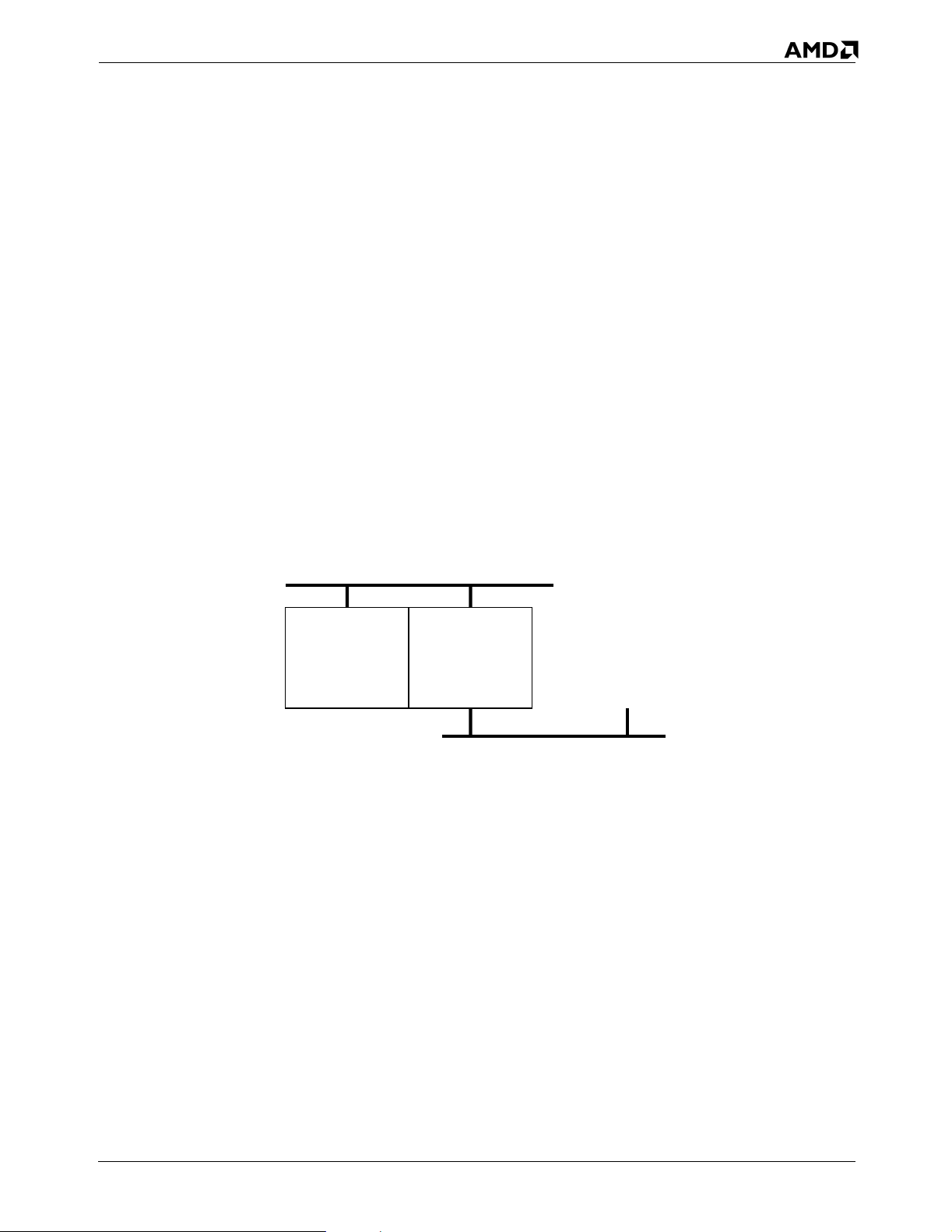

5.1.1 Configuration Space

The address space for the IC configuration registers is broken up into busses, devices, functions, and, offsets, as

defined by the link specification. It is accessed by HyperTransport™ technology-defined type 0 configuration

cycles. The device number is mapped into bits[15:11] of the configuration address. The function number is

mapped into bits[10:8] of the configuration address. The offset is mapped to bits[7:2] of the configuration

address.

The following diagram shows the devices in configuration space as viewed by software.

Primary bus

AGP Device

DevA:0xXX

Device header

First device

Function 0

AGP Bridge

DevB:0xXX

Bridge header

Second device

Function 0

Secondary bus

AGP Slot

Figure 2: Configuration space.

Device A, above, is programmed to be the link base UnitID and device B is the link base UnitID plus 1.

5.1.2 Register Naming and Description Conventions

Configuration register locations are referenced with mnemonics that take the form of Dev[A|B]:[7:0]x[FF:0],

where the first set of brackets contain the device number, the second set of brackets contain the function number, and the last set of brackets contain the offset.

Other register locations (e.g. memory mapped registers) are referenced with an assigned mnemonic that specifies the address space and offset. These mnemonics start with two or three characters that identify the space

followed by characters that identify the offset within the space.

Register fields within register locations are also identified with a name or bit group in brackets following the

register location mnemonic.

14

Page 15

24888 Rev 3.03 - July 12, 2004 AMD-8151

TM

AGP Tunnel Data Sheet

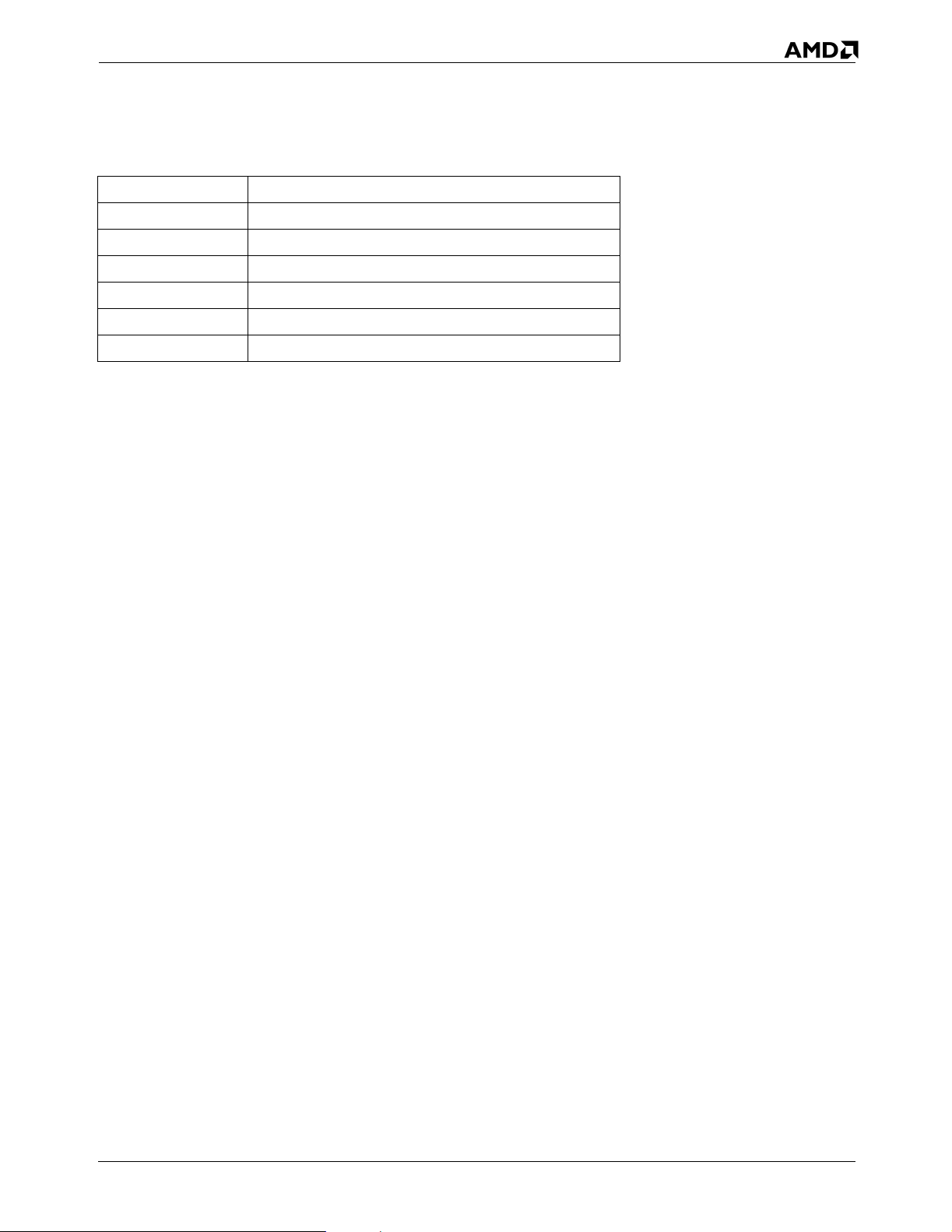

The following are configuration spaces:

Device Function Mnemonic Registers

"A" 0 DevA:0xXX AGP device header; link and AGP capabilities blocks

"B" 0 DevB:0xXX PCI-PCI bridge registers for AGP

Table 3: Configuration spaces.

The IC does not claim configuration-register accesses to unimplemented functions within its devices (they are

forwarded to the other side of the tunnel). Accesses to unimplemented register locations within implemented

functions are claimed; such writes are ignored and reads always respond with all zeros.

The following are memory mapped spaces:

Base address

register

DevA:0x10 Variable None Graphic virtual memory aperture; minimum of 32 megabytes.

DevA:0xB8 4K None GART block in physical memory.

Size

(bytes)

Mnemonic Registers

Table 4: Memory mapped address spaces.

The following are register attributes found in the register descriptions.

Type Description

Read or read-only Capable of being read by software. Read-only implies that the register cannot be written to by

software.

Write Capable of being written by software.

Set by hardware Register bit is set high by hardware.

Write once After RESET#, these registers may be written to once. After being written, they become read only

until the next RESET# assertion. The write-once control is byte based. So, for example, software

may write each byte of a write-once DWORD as four individual transactions. As each byte is

written, that byte becomes read only.

Write 1 to clear Software must write a 1 to the bit in order to clear it. Writing a 0 to these bits has no effect.

Write 1 only Software can set the bit high by writing a 1 to it. However subsequent writes of 0 will have no

effect. RESET# must be asserted in order to clear the bit.

Table 5: Register attributes.

5.2 AGP Device Configuration Registers

These registers are located in PCI configuration space, in the first device (device A), function 0. See section

5.1.2 for a description of the register naming convention.

AGP Vendor And Device ID Register DevA:0x00

Default: 7454 1022h Attribute: Read only.

Bits Description

31:16 AGP device ID.

15:0 Vendor ID.

15

Page 16

24888 Rev 3.03 - July 12, 2004 AMD-8151

AGP Device Status And Command Register DevA:0x04

Default: 0210 0000h Attribute: See below.

Bits Description

31 DPE: detected parity error. Read only. This bit is fixed in the low state.

30 SSE: signaled system error. Read; set by hardware; write 1 to clear. 1=A system error was signaled

(both links were flooded with sync packets) as a result of a CRC error (see

DevA:0x[C8:C4][CRCFEN, CRCERR]). Note: this bit is cleared by PWROK reset but not by

RESET#.

29 RMA: received master abort. Read; set by hardware; write 1 to clear. 1=A request (AGP or PCI)

sent to the host bus received a master abort (an NXA error response). Note: this bit is cleared by

PWROK reset but not by RESET#.

28 RTA: received target abort. Read; set by hardware; write 1 to clear. 1=A request (AGP or PCI) sent

to the host bus received a target abort (a non-NXA error response). Note: this bit is cleared by

PWROK reset but not by RESET#.

27:21 Read only. These bits are fixed in their default state.

20 Capabilities pointer. Read only. This bit is fixed in the high state.

TM

AGP Tunnel Data Sheet

19:3 Read only. These bits are fixed in their default state.

2 MASEN: PCI master enable. Read-write. This bit controls no hardware in the IC.

1 MEMEN: memory enable. Read-write. 1=Enables access to the memory space specified by

DevA:0x10. This bit controls no hardware in the IC.

0 IO enable. Read only. This bit is fixed in the low state.

AGP Device Revision and Class Code Register DevA:0x08

Default: 0600 00??h Attribute: See below.

Bits Description

31:8 CLASSCODE. Read; write once. Provides the AGP bridge class code.

7:0 REVISION. Read only.

AGP Device BIST-Header-Latency-Cache Register DevA:0x0C

Default: 0000 0000h Attribute: Read only.

Bits Description

31:24 BIST. These bits fixed at their default values.

23:16 HEADER. These bits fixed at their default values.

15:8 LATENCY. These bits fixed at their default values.

7:0 CACHE. These bits fixed at their default values.

16

Page 17

24888 Rev 3.03 - July 12, 2004 AMD-8151

AGP Device Graphic Virtual Memory Aperture Register DevA:0x10

It is expected that the state of this register is copied into the host by software. This register controls no hardware in the IC.

Default: 0000 0000 0000 0008h Attribute: See below.

Bits Description

63:32 APBARHI. Read-write. Aperture base address register high. Note: bits[63:40] are required to be

programmed low; setting any of these bits high results in undefined behavior. Note: if

DevA:0x10[64BIT]=0, then these bits are read only, all zero.

31:22 APBARLO. Aperture base address register low. These bits are a combination of read-write and read-

only zero, based on the state of DevA:0xB4[APSIZE]; see that register for details.

21:4 Reserved.

3 Read only. This bit is fixed at its default value to indicate that this register points prefetchable space.

2 64BIT: 64-bit pointer. Read; write once. 1=DevA:0x10 is a 64-bit pointer. 0=DevA:0x10 is a 32-bit

pointer; bits[63:32] are reserved.

1:0 Read only. These bits are fixed at their default value to indicate that this register points memory space.

TM

AGP Tunnel Data Sheet

AGP Device Subsystem ID and Subsystem Vendor ID Register DevA:0x2C

Default: 0000 0000h Attribute: Read; write once.

Bits Description

31:16 Subsystem ID. This field controls no hardware.

15:0 Subsystem vendor ID. This field controls no hardware.

AGP Capabilities Pointer DevA:0x34

Default: 0000 00A0h Attribute: Read only.

Bits Description

31:8 Reserved.

7:0 Capabilities pointer. Specifies the offset in DevA:0 address space for the AGP capabilities block.

17

Page 18

24888 Rev 3.03 - July 12, 2004 AMD-8151

AGP Miscellaneous Control Register DevA:0x40

Default: 0000 0000h Attribute: See below.

Bits Description

31:8 Reserved.

7 Must be low. This bit is required to be low at all times; setting it high results in undefined behavior.

6 Must be low. This bit is required to be low at all times; setting it high results in undefined behavior.

5 Must be low. This bit is required to be low at all times; setting it high results in undefined behavior.

4 Must be low. This bit is required to be low at all times; setting it high results in undefined behavior.

3 FWDIS: fast write disable. Read-write. 1=DevA:0xA4[FWSUP] is low. 0=DevA:0xA4[FWSUP] is

high.

2 8XDIS: AGP 3.0 signaling mode disable. Read-write. 0=The IC drives A_MB8XDET# low to

indicate support for AGP 3.0 signaling. 1=The IC does not drive A_MB8XDET low. This bit may be

used in conjunction with DevB:0x3C[SBRST] to revert back to AGP 2.0 signaling. To do this,

software should (1) set DevB:0x3C[SBRST] in order to reset the AGP card, (2) set 8XDIS to cause

A_MB8XDET# to float high, and (3) clear DevB:0x3C[SBRST].

1 TYPEDET: AGP voltage type detection. Read only. This bit reflects the state of the A_TYPEDET#

pin. 0=The AGP master supports 1.5 volt signaling. 1=The AGP master requires 3.3 volt signaling

and is therefore not compatible with the IC. If this bit is detected high by BIOS, an error should be

signaled.

0 DBIEN: dynamic bus inversion enable. Read-write. 1= A_DBI[H, L] enabled to dynamically invert

the state of the A_AD signals when the IC is driving these. This only applies to AGP 3.0 transfers in

the downstream direction (fast writes and read responses to AGP master requests). For PCI transfers

in the downstream direction, A_DBI[H, L] are held inactive and no inversion takes place. 0=When

the IC drives the A_AD lines, A_DBI[H, L] are driven low. Note: this bit is only valid when 8x

transfer rates are enabled; if (1) DevA:0xA4[AGP3MD]=0 or (2) DevA:0xA4[AGP3MD]=1 and

DevA:0xA8[DRATE] is not 010b, then this field is ignored and the DBI is not enabled.

TM

AGP Tunnel Data Sheet

18

Page 19

24888 Rev 3.03 - July 12, 2004 AMD-8151

AGP PHY Control Register DevA:0x[54, 50]

These registers apply to the compensation values of AGP clock-forwarded data and strobe signals as follows:

• DevA:0x50: data signals A_AD[31:0], A_CBE_L[3:0], A_DBI[H, L], and A_SBA[7:0].

• DevA:0x54: strobe signals A_ADSTB[1:0]_[P, N] and A_SBSTB_[P, N].

NCTL, NDATA, and NCOMP are related to (1) the falling edge drive strength of the signals as outputs and (2)

the impedance of the signals as inputs. PCTL, PDATA, and PCOMP are related to the rising edge drive

strength of the signals as outputs only. For the [N, P]DATA and [N, P]COMP fields of these registers, 00h corresponds to the weakest drive strength and the highest receive impedance. For the [N, P]DATA and [N,

P]COMP fields of these registers, the highest values corresponds to the strongest drive strength and lowest

receive impedance.

External compensation resistors are used by the IC to determine the proper drive strength values. The resistors

correlate the calculated values as follows:

• A_CALD is used to calculate DevA:0x50[PCOMP] (data signal rising edge drive strength).

• A_CALD# is used to calculate DevA:0x50[NCOMP] (data signal falling edge drive strength and receive

impedance).

• A_CALS is used to calculate DevA:0x54[PCOMP] (strobe rising edge drive strength).

• A_CALS# is used to calculate DevA:0x54[NCOMP] (strobe falling edge drive strength and receive impedance).

TM

AGP Tunnel Data Sheet

Note: when new values are written to these registers, new compensation values are not updated to the AGP

PHY automatically; the periodic calibration cycle specified by DevA:0xA8[PCALCYC] must pass in order for

the AGP PHY calibration values to take effect.

Default: 000? 000?h Attribute: See below.

Bits Description

31:30 NCTL: AGP PHY N (falling edge) compensation control. Read-write. These two bits combine to

specify the PHY falling edge compensation value that is applied to AGP signals as follows:

NCTL

00b Apply NCOMP directly as the compensation value.

01b Apply NDATA directly as the compensation value.

10b Apply the sum of NCOMP and NDATA as the compensation value. If the sum

11b Apply the difference of NCOMP minus NDATA as the compensation value. If the dif-

29:28 Reserved.

27:22 NDATA: AGP falling edge drive strength control. Read-write. This value is applied to the falling-

edge (N transistor) PHY compensation as described in NCTL.

21:16 NCOMP: AGP falling edge drive strength. Read only. This provides the calculated value of the

falling-edge (N transistor) drive strength of the AGP signals. The default for this field varies. This

field is updated by the hardware approximately every 8 microseconds.

Description

exceeds 3Fh, then 3Fh is applied.

ference is less than 00h, then 00h is applied.

19

Page 20

24888 Rev 3.03 - July 12, 2004 AMD-8151

15:14 PCTL: AGP PHY P (rising edge) compensation control. Read-write. These two bits combine to

specify the PHY rising edge compensation value that is applied to AGP signals as follows:

PCTL

00b Apply PCOMP directly as the compensation value.

01b Apply PDATA directly as the compensation value.

10b Apply the sum of PCOMP and PDATA as the compensation value. If the sum exceeds

11b Apply the difference of PCOMP minus PDATA as the compensation value. If the dif-

13:12 Reserved.

11 RW: read-write bit. Read-write. This controls no logic.

10:6 PDATA: AGP rising edge drive strength control. Read-write. This value is applied to the rising-

edge (P transistor) PHY compensation as described in PCTL.

5 Reserved.

4:0 PCOMP: AGP rising edge drive strength. Read only. This provides the calculated value of the ris-

ing-edge (P transistor) drive strength of the AGP signals. The default for this field varies. This field is

updated by the hardware approximately every 8 microseconds.

Description

1Fh, then 1Fh is applied.

ference is less than 00h, then 00h is applied.

TM

AGP Tunnel Data Sheet

AGP PHY Skew Control Register DevA:0x58

DSKEW and SSKEW are designed such that when they are both programmed to the same value, the AGP output strobes transition near the center of the data eye. To move the strobe to a later point in the data eye, the

value of SSKEW is increased. To move the strobe to an earlier point in the data eye, DSKEW is increased.

These values translate into skew approximately as follows:

For values 0h to 8h, the skew is about: [D, S]SKEW x 80 picoseconds.

For values 9h to Fh, the skew is about: 800 + ([D, S]SKEW - 8) x 400 picoseconds.

However, these values vary with process, temperature, and voltage. Note that the lower values provide fine resolution and the upper values provide coarse resolution.

Default: 0000 0000h. Attribute: Read-write.

Bits Description

31:8 Reserved.

7:4 DSKEW: AGP data skew. Read-write. This specifies the alignment of the AGP data signal outputs,

A_AD[31:0], A_CBE_L[3:0], and A_DBI[H, L], relative internal clocks. 0h=The strobe transitions

earliest. Fh=The strobe transitions latest.

3:0 SSKEW: AGP strobe skew. Read-write. This specifies the alignment of the AGP strobe signal out-

puts, A_ADSTB[1:0], relative internal clocks. 0h=The strobe transitions earliest. Fh=The strobe transitions latest.

20

Page 21

24888 Rev 3.03 - July 12, 2004 AMD-8151

AGP Most Recent Request Register DevA:0x60

As each PIPE mode or SBA mode AGP request is transferred into the IC, the fields are placed into this register.

Thus, this register provides the fields of the most recent AGP requests. Any sticky bits from prior requests that

have not been updated in the current request are also valid. Note: fences are not captured by this register.

Default: 0000 0000 0000 0000h Attribute: Read only.

Bits Description

63:44 Reserved.

43:40 MRC: most recent command field. Specifies the command field of the most recent AGP request.

0h=LP (low priority) read. 1h=HP (high priority) read. 4h=LP write. 5h=HP write. 8h=LP long read.

9h=HP long read. Ah=Flush.

39:3 MRA: most recent address. Specifies address bits[39:3] of the most recent AGP request.

2:0 MRL: most recent length field. Specifies the length field of the most recent AGP request.

AGP Revision and Capability Register DevA:0xA0

TM

AGP Tunnel Data Sheet

Default: 0030 C002h Attribute: Read only.

Bits Description

31:24 Reserved.

23:16 AGP specification. This field is hardwired to indicate that the IC conforms to AGP specification

revision 3.

15:8 Next capabilities block. Specifies the offset to the next capabilities block.

7:0 Capabilities type. Specifies the AGP capabilities block.

AGP Status Register DevA:0xA4

Default: 1F00 0B2?h (see bit descriptions for bits[3:0])Attribute: Read only.

Bits Description

31:24 RQ: maximum number of outstanding requests. This field is set to indicate support for 32

outstanding requests.

23:18 Reserved.

17 Isochronous support. This bit fixed in the low state to indicate that the IC does not support

isochronous modes.

16:13 Reserved.

12:10 Calibration cycle. This field is set to indicate a requirement for calibration cycles every 64 millisec-

onds.

9 SBA support. This field is set to indicate support for SBA.

8 Coherency. This bit fixed high.

7 64-bit GART support. This bit fixed low.

6 Host translation#. This bit fixed low.

5 Greater-than 4 gigabyte support. This bit fixed high.

21

Page 22

24888 Rev 3.03 - July 12, 2004 AMD-8151

4 FWSUP: fast write support flag. 0=Fast writes are not supported. 1=Fast writes are supported. The

state of this bit is controlled by DevA:0x40[FWDIS].

3 AGP3MD: AGP 3.0 signaling mode detected. 1=The IC detected connection to an AGP 3.0-capable

master and is programmed for AGP 3.0 signaling. 0=The IC detected connection to an AGP 2.0 or

earlier capable master or is not programmed for 1.5-volt, AGP 2.0 signaling. If

DevA:0x40[8XDIS]=0 and the pin A_GC8XDET#=0, then this bit is high. Otherwise, it is low.

2:0 RATE: data rate. When AGP3MD=1, then this field defaults to 011b to indicate support for 4x and

8x data rates. When AGP3MD=0, this field defaults to 111b to indicate support for 4x, 2x, and 1x data

rates.

AGP Command Register DevA:0xA8

Default: 0000 0000h Attribute: Read-write.

Bits Description

31:13 Reserved.

12:10 PCALCYC: periodic calibration cycle. Specifies the period between calibration cycles as follows:

000b=4 milliseconds; 001b=16 milliseconds; 010=64 milliseconds; 011b=256 milliseconds; all other

values are reserved. When DevA:0xA4[AGP3MD]=1, calibration cycles are as specified in the AGP

3.0 specification. When DevA:0xA4[AGP3MD]=0, calibration cycles consist of (1) the internal

calibration logic requests the bus; (2) once granted, the calibration values are update in less than 6

A_PCLK cycles while the AGP bus is in a quiescent state. Note: after changing this value, the IC may

not perform another calibration cycle until the internal counter rolls over as much as 256

microseconds later; in order to avoid this, DevA:0xB0[CALDIS] should be set high before changing

PCALCYC and then DevA:0xB0[CALDIS] should be cleared afterward.

TM

AGP Tunnel Data Sheet

9 SBA_EN: side band address enable. 1=SBA addressing is enabled. Note: when

DevA:0xA4[AGP3MD]=1, SBA addressing is enabled and the state of this bit is ignored.

8 AGPEN: AGP operation enable. 1=The IC accepts master-initiated AGP commands. 0=AGP

commands are ignored.

7:6 Reserved.

5 R4GEN: receive greater-than 4-gigabyte access enable. 1=The IC accepts AGP accesses to

addresses greater than 4 gigabytes.

4 FWEN: fast write enable. 1=Fast writes are enabled. When DevA:0xA4[FWSUP]=0, this bit is

required to be programmed low; if, in this case, this bit is programmed high, then undefined behavior

results.

3 Reserved.

22

Page 23

24888 Rev 3.03 - July 12, 2004 AMD-8151

2:0 DRATE: data transfer mode rate. This field is combined with DevA:0xA4[AGP3MD] to specify

the AGP data rate as follows:

AGP3MD

X 000 No AGP mode selected.

0 001 1x AGP rate; AGP 2.0 signaling.

0 010 2x AGP rate; AGP 2.0 signaling.

0 100 4x AGP rate; AGP 2.0 signaling.

1 001 4x AGP rate; AGP 3.0 signaling.

1 010 8x AGP rate; AGP 3.0 signaling.

1100Reserved.

AGP Control Register DevA:0xB0

Default: 0000 0000h Attribute: Read-write.

Bits Description

31:10 Reserved.

9 CALDIS: calibration cycle disable. 1=Calibration cycles (as defined in DevA:0xA8[PCALCYC])

are disabled.

DRATE

TM

AGP Tunnel Data Sheet

8 APEREN: graphics aperture enable. This bit controls no hardware in the IC. It is expected that the

state of this bit is copied into the host by software.

7 GTLBEN: graphics translation look-aside buffer enable. This bit controls no hardware in the IC. It

is expected that the state of this bit is copied into the host by software.

6:0 Reserved.

AGP Aperture Size Register DevA:0xB4

Default: 0001 0F00h Attribute: See below.

Bits Description

31:28 PGSZSEL: page size select. Read-write. The only legal value for these bits is 0000b, which specifies

a 4-kilobyte page.

27 Reserved.

26:16 Page size support. Read only. These bits are fixed in their default state to indicate that the IC

supports 4-kilobyte pages.

15:12 Reserved.

23

Page 24

24888 Rev 3.03 - July 12, 2004 AMD-8151

11:0 APSIZE: graphic virtual memory aperture size. Read-write (except bits[11, 7:6, and 2:0] which

are read only, fixed at the default value). This field specifies the size of the aperture pointed to by

DevA:0x10. This field also controls read only versus read-write control over several bits in

DevA:0x10. It is encoded as follows:

DevA:0x10 DevA:0x10

Bits[10, 9, 8, 5, 4, 3]

1 1 1 1 1 1 32 MB [63:25] [24:0]

1 1 1 1 1 0 64 MB [63:26] [25:0]

1 1 1 1 0 0 128 MB [63:27] [26:0]

1 1 1 0 0 0 256 MB [63:28] [27:0]

1 1 0 0 0 0 512 MB [63:29] [28:0]

1 0 0 0 0 0 1024 MB [63:30] [29:0]

0 0 0 0 0 0 2048 MB [63:31] [30:0]

It is expected that the state of this field is copied into the host by software. Note: DevA:0x10[2] is

“read; write once,” even though it is shown as read-only above. Also, based on the state of

DevA:0x10[2], DevA:0x10[63:32] may be read-only, all zeros.

Aperture size read-write bits read-only bits

TM

AGP Tunnel Data Sheet

AGP Device GART Pointer DevA:0xB8

This register controls no hardware in the IC. It is expected that the state of this register is copied into the host

by software.

Default: 0000 0000 0000 0000h Attribute: Read-write.

Bits Description

63:32 GARTHI: GART base address register high.

31:12 GARTLO: GART base address register low.

11:0 Reserved.

Link Command Register DevA:0xC0

Default: 0060 0008h Attribute: See below.

Bits Description

31:29 Slave/primary interface type. Read only.

28 DOUI: drop on uninitialized link. Read-write. This specifies the behavior of transactions that are

sent to uninitialized links. 0=Transactions that are received by the IC and forwarded to a side of the

tunnel, when DevA:0x[C4/C8][INITCPLT and ENDOCH] for that side of the tunnel are both low,

remain in buffers awaiting transmission indefinitely (waiting for INITCPLT to be set high). 1=Transactions that are received by the IC and forwarded to a side of the tunnel, when

DevA:0x[C4/C8][INITCPLT and ENDOCH] for that side of the tunnel are both low, behave as if

ENDOCH were high. Note: this bit is cleared by PWROK reset but not by RESET#.

27 DEFDIR: default direction. Read-write. 0=Send AGP master requests to the master link host as

specified by DevA:0xC0[MASHST]. 1=Send AGP master requests to the opposite side of the tunnel.

24

Page 25

24888 Rev 3.03 - July 12, 2004 AMD-8151

26 MASHST: master host. Read; set and cleared by hardware. This bit indicates which link is the path

to the master (or only) host bridge on the HyperTransport™ technology chain. 1=The hardware set

this bit as a result of a write command from the B side of the tunnel to any of the bytes of

DevA:0xC0[31:16]. 0=The hardware cleared this bit as a result of a write command from the A side

of the tunnel to any of the bytes of DevA:0xC0[31:16]. This bit, along with DEFDIR, is used to

determine the side of the tunnel to which AGP master requests are sent.

25:21 UnitID count. Read only. Specifies the number of UnitIDs used by the IC (three).

20:16 BUID: base UnitID. Read-write. This specifies the link-protocol base UnitID. The IC's logic uses

this value to determine the UnitIDs for link request and response packets. When a new value is

written to this field, the response includes a UnitID that is based on the new value in this register.

Note: some legacy operating systems may require that this value be set to zero for normal operation

so that the AGP capability block is part of device 0. Since the IC does not use the base unit ID in any

link transactions, there is no conflict with the host unit ID. However, at boot, BIOS is required to

temporarily change the BUID value of the IC so that the BUID values in downstream devices may be

initialized. After downstream BUID values are initialized, this field may be set to zero to be

compatible with legacy operating systems.

15:8 Reserved.

7:0 Capabilities ID. Read only. Specifies the capabilities ID for link configuration space.

TM

AGP Tunnel Data Sheet

Link Configuration And Control Register DevA:0xC4 and DevA:0xC8

DevA:0xC4 applies side A of the tunnel and DevA:0xC8 applies to side B of the tunnel. The default value for

bit[5] may vary (see the definition).

Default: ??11 0020h for DevA:0xC4 and ??00 0020h for DevA:0xC8.Attribute: See below.

Bits Description

31 Reserved.

30:28 LWO: link width out. Read-write. Specifies the operating width of the outgoing link. Legal values

are 001b (16 bits; DevA:0xC4 only), 000b (8 bits), 101b (4 bits), 100b (2 bits), and 111b (not

connected). Note: this field is cleared by PWROK reset but not by RESET#; the default value of this

field depends on the widths of the links of the connecting device, per the link specification. Note:

after this field is updated, the link width does not change until either RESET# is asserted or a link

disconnect sequence occurs through or LDTSTOP#.

27 Reserved.

26:24 LWI: link width in. Read-write. Specifies the operating width of the incoming link. Legal values are

001b (16 bits; DevA:0xC4 only), 000b (8 bits), 101b (4 bits), 100b (2 bits), and 111b (not connected).

Note: this field is cleared by PWROK reset but not by RESET#; the default value of this field depends

on the widths of the links of the connecting device, per the link specification. Note: after this field is

updated, the link width does not change until either RESET# is asserted or a link disconnect sequence

occurs through an LDTSTOP# assertion.

23 Reserved.

22:20 Max link width out. Read only. This specifies the width of the outgoing link to be 16 bits wide for

side A and 8 bits wide for side B.

19 Reserved.

25

Page 26

24888 Rev 3.03 - July 12, 2004 AMD-8151

18:16 Max link width in. Read only. This specifies the width of the incoming link to be 16 bits wide for

side A and 8 bits wide for side B.

15 Reserved.

14 EXTCTL: extended control time during initialization. Read-write. This specifies the time in

which LT[B, A]CTL is held asserted during the initialization sequence that follows an LDTSTOP#

deassertion, after LR[B, A]CTL is detected asserted. 0=At least 16 bit times. 1=About 50

microseconds. Note: this bit is cleared by PWROK reset but not by RESET#.

13 LDT3SEN: link three-state enable. Read-write. 1=During the LDTSTOP# disconnect sequence, the

link transmitter signals are placed into the high impedance state and the receivers are prepared for the

high impedance mode. For the receivers, this includes cutting power to the receiver differential

amplifiers and ensuring that there are no resultant high-current paths in the circuits. 0=During the

LDTSTOP# disconnect sequence, the link transmitter signals are driven, but in an undefined state,

and the link receiver signals are assumed to be driven. Note: this bit is cleared by PWROK reset but

not by RESET#. AMD recommends that this bit be set high in single-processor systems and be low in

multi-processor systems.

12:10 Reserved.

9:8 CRCERR: CRC Error. Read; set by hardware; write 1 to clear. Bit[9] applies to the upper byte of

the link (DevA:0xC4 only) and bit[8] applies to the lower byte. 1=The hardware detected a CRC error

on the incoming link. Note: this bit is cleared by PWROK reset but not by RESET#.

TM

AGP Tunnel Data Sheet

7 TXOFF: transmitter off. Read; write 1 only. 1=No output signals on the link toggle; the input link

receivers are disabled and the pins may float.

6 ENDOCH: end of chain. Read; write 1 only or set by hardware. 1=The link is not part of the logical

HyperTransport technology chain; packets which are issued or forwarded to this link are either

dropped or result in an NXA error response, as appropriate; packets received from this link are

ignored and CRC is not checked; if the transmitter is still enabled (TXOFF), then it drives only NOP

packets with good CRC. ENDOCH may be set by writing a 1 to it or it may be set by hardware if the

link is determined to be disconnected at the rising edge of RESET#.

5 INITCPLT: initialization complete. Read only. This bit is set by hardware when low-level link

initialization has successfully completed. If there is no device on the other end of the link, or if the

device on the other side of the link is unable to properly perform link initialization, then the bit is not

set. This bit is cleared when RESET# is asserted or after the link disconnect sequence completes after

the assertion of LDTSTOP#.

4 LKFAIL: link failure. Read; set by hardware; write 1 to clear. This bit is set high by the hardware

when a CRC error is detected on the link (if enabled by CRCFEN) or if the link is not used in the

system. Note: this bit is cleared by PWROK reset, not by RESET#.

3 CRCERRCMD: CRC error command. Read-write. 1=The link transmission logic generates

erroneous CRC values. 0=Transmitted CRC values match the values calculated per the link

specification. This bit is intended to be used to check the CRC failure detection logic of the device on

the other side of the link.

2 Reserved.

1 CRCFEN: CRC flood enable. Read-write. 1=CRC errors (in link A for DevA:0xC4[CRCFEN]; in

link B for DevA:0xC8[CRCFEN]) result in sync packets to both outgoing links, DevA:0x04[SSE] is

set, and the LKFAIL bit is set. 0=CRC errors do not result in sync packets, setting of

DevA:0x04[SSE] or the LKFAIL bit.

0 Reserved.

26

Page 27

24888 Rev 3.03 - July 12, 2004 AMD-8151

Link Frequency Capability 0 Register DevA:0xCC

Default: 0035 0022h. Attribute: See below.

Bits Description

31:16 FREQCAPA: link A frequency capability. Read only. These bits indicate that A side of the tunnel

supports 200, 400, 600, and 800 MHz link frequencies.

15:12 Reserved.

11:8 FREQA: link A frequency. Read-write. Specifies the link side A frequency. Legal values are 0h (200

MHz), 2h (400 MHz), 4h (600 MHz), and 5h (800 MHz). Note: this bit is cleared by PWROK reset,

not by RESET#. Note: after this field is updated, the link frequency does not change until either

RESET# is asserted or a link disconnect sequence occurs through LDTSTOP#.

7:0 REVISION. Read only. Revision A of the IC is designed to version 1.02 of the link specification.

Link Frequency Capability 1 Register DevA:0xD0

TM

AGP Tunnel Data Sheet

Default: 0035 0002h. Attribute: See below.

Bits Description

31:16 FREQCAPB: link B frequency capability. Read only. These bits indicate that that B side of the

tunnel supports 200, 400, 600, and 800 MHz link frequencies.

15:12 Reserved.

11:8 FREQB: link B frequency. Read-write. Specifies the link side B frequency. Legal values are 0h (200

MHz), and 2h (400 MHz), 4h (600 MHz), and 5h (800 MHz). Note: although it is possible to program

this field for higher frequencies, the B link of the IC is only designed to support 200 and 400 MHz

operation. Note: this bit is cleared by PWROK reset, not by RESET#. Note: after this field is updated,

the link frequency does not change until either RESET# is asserted or a link disconnect sequence

occurs through LDTSTOP#.

7:0 Link device feature capability indicator. Read only. These bits are set to indicate that the IC

supports LDTSTOP#.

Link Enumeration Scratchpad Register DevA:0xD4

Default: 0000 0000h. Attribute: See below.

Bits Description

31:16 Reserved.

15:0 ESP: enumeration scratchpad. Read-write. This field controls no hardware within the IC. Note: this

bit is cleared by PWROK reset, not by RESET#.

27

Page 28

24888 Rev 3.03 - July 12, 2004 AMD-8151

Link PHY Compensation Control Registers DevA:0x[E8, E4, E0]

The link PHY circuitry includes automatic compensation that is used to adjust the electrical characteristics for

the link transmitters and receivers on both sides of the tunnel. There is one compensation circuit for the receivers and one for each polarity of the transmitters. These registers provide visibility into the calculated output of

the compensation circuits, the ability to override the calculated value with software-controlled values, and the

ability to offset the calculated values with a fixed difference. The overrides and difference values may be different between sides A and B of the tunnel. These registers specify the compensation parameters as follows:

• DevA:0xE0: transmitter rising edge (P) drive strength compensation.

• DevA:0xE4: transmitter falling edge (N) drive strength compensation.

• DevA:0xE8: receiver impedance compensation.

For DevA:0x[E4, E0], higher values represent higher drive strength; the values range from 01h to 13h (19

steps). For DevA:0xE8, higher values represent lower impedance; the values range from 00h to 1Fh (32 steps).

Note: the default state of these registers is set by PWROK reset; assertion of RESET# does not alter any of the

fields.

Default: See below. Attribute: See below.

Bits Description

TM

AGP Tunnel Data Sheet

31 Must be low. Read-write. This bit is required to be low at all times; setting it high results in undefined

behavior.

30:21 Reserved.

20:16 CALCCOMP: calculated compensation value. Read only. This provides the calculated value from

the auto compensation circuitry. The default value of this field is not predictable.

15 Reserved.

14:13 BCTL: link side B PHY control value. Read-write. These two bits combine to specify the PHY

compensation value that is applied to side B of the tunnel as follows:

BCTL

00b Apply CALCCOMP directly as the compensation value.

01b Apply BDATA directly as the compensation value.

10b Apply the sum of CALCCOMP and BDATA as the compensation value. In

11b Apply the difference of CALCCOMP minus BDATA as the compensation value. If the

The default value of this field (from PWROK reset) is controlled by the CMPOVR signal. If

CMPOVR = 0, the default is 00b. If CMPOVR = 1, the default is 01b.

12:8 BDATA: link side B data value. Read-write. This value is applied to the side B of the tunnel PHY

compensation as described in BCTL. The default for DevA:0x[E4, E0] is 08h. The default for

DevA:0xE8 is 0Fh.

Description

DevA:0x[E4, E0], if the sum exceeds 13h, then 13h is applied. In DevA:0x[E8], if the

sum exceeds 1Fh, then 1Fh is applied.

difference is less than 01h, then 01h is applied.

7 Reserved.

28

Page 29

24888 Rev 3.03 - July 12, 2004 AMD-8151

6:5 ACTL: link side A PHY control value. Read-write. These two bits combine to specify the PHY

compensation value that is applied to side A of the tunnel as follows:

ACTL

00b Apply CALCCOMP directly as the compensation value.

01b Apply ADATA directly as the compensation value.

10b Apply the sum of CALCCOMP and ADATA as the compensation value. In

11b Apply the difference of CALCCOMP minus ADATA as the compensation value. If the

The default value of this field (from PWROK reset) is controlled by the CMPOVR signal. If

CMPOVR = 0, the default is 00b. If CMPOVR = 1, the default is 01b.

4:0 ADATA: link side A data value. Read-write. This value is applied to the side A of the tunnel PHY

compensation as described in ACTL. The default for DevA:0x[E4, E0] is 08h. The default for

DevA:0xE8 is 0Fh.

Description

DevA:0x[E4, E0], if the sum exceeds 13h, then 13h is applied. In DevA:0x[E8], if the

sum exceeds 1Fh, then 1Fh is applied.

difference is less than 01h, then 01h is applied.

TM

AGP Tunnel Data Sheet

Clock Control Register DevA:0xF0

See section 4.3.1 for details on clock gating. AMD system recommendations for System Management Action

Field (SMAF) codes are: 0=ACPI C2; 1=ACPI C3; 2=FID/VID change; 3=ACPI S1; 4=ACPI S3; 5=Throttling; 6=ACPI S4/S5. For server and desktop platforms, AMD recommends setting this register to 0004_0008h

(to gate clocks during S1). For mobile platforms, AMD recommends setting this register to 0004_0A0Ah (to

gate clocks during C3 and S1).

Default: 0000 0000h. Attribute: Read-write.

Bits Description

31:19 Reserved.

18 CGEN: clock gate enable. 1=Internal clock gating, as specified by bits[7:0] of this register, is

enabled.

17 Must be low. This bit is required to be low at all times; setting it high results in undefined behavior.

16 Must be low. This bit is required to be low at all times; setting it high results in undefined behavior.

15:8 ECGSMAF: external clock gating system management action fields. Each of the bits of this field

correspond to SMAF values that are captured in Stop Grant cycles from the host. For each bit,

1=When LDTSTOP# is asserted prior to a Stop Grant cycle in which the SMAF field matches the

ECGSMAF bit that is asserted, then A_PCLK and internal clock grids associated with the AGP

bridges are forced low. 0=A_PCLK and the internal clock grids are active while LDTSTOP# is

asserted. For example, if A_PCLK gating is required for SMAF values of 3 and 5, then ECGSMAF[3,

5] must be high. See section 4.3.1 for details.

7:0 ICGSMAF: internal clock gating system management action fields. Each of the bits of this field

correspond to SMAF values that are captured in Stop Grant cycles from the host. For each bit,

1=When LDTSTOP# is asserted prior to a Stop Grant cycle in which the SMAF field matches the

ICGSMAF bit that is asserted, then the IC power is reduced through gating of internal clocks. 0=No

power reduction while LDTSTOP# is asserted. For example, if clock gating is required for SMAF

values of 3 and 5, then ICGSMAF[3, 5] must be high. See section 4.3.1 for details.

29

Page 30

24888 Rev 3.03 - July 12, 2004 AMD-8151

5.3 AGP Bridge Configuration Registers

These registers are located in PCI configuration space, in the second device (device B), function 0. See section

5.1.2 for a description of the register naming convention.

AGP Bridge Vendor And Device ID Register DevB:0x00

Default: 7455 1022h Attribute: See below.

Bits Description

31:16 AGP bridge device ID. Bits[31:20] are read only; bits[19:16] are write-once. When the LSBs are left

at the default value, some operating systems may load a generic graphics driver. System BIOS should

program the LSBs to 6h in order to circumvent the loading of such a driver.

15:0 Vendor ID. Read only.

AGP Bridge Status And Command Register DevB:0x04

TM

AGP Tunnel Data Sheet

Default: 0220 0000h Attribute: See below.

Bits Description

31:9 Read only. These bits are fixed in their default state.

8 SERREN: SERR# enable. Read-write. This bit controls no hardware.

7:3 Special cycle enable. Read only. This bit is hardwired low.

2 MASEN: PCI master enable. Read-write. 1=Enables the AGP bus master to initiate PCI cycles to

the host.

1 MEMEN: memory enable. Read-write. 1=Enables access to the AGP bus memory space.

0 IOEN: IO enable. Read-write. 1=Enables access to the AGP bus IO space.

AGP Bridge Revision and Class Code Register DevB:0x08

Default: 0604 00??h Attribute: Read only.

Bits Description

31:8 CLASSCODE.

7:0 REVISION.

AGP Bridge BIST-Header-Latency-Cache Register DevB:0x0C