Page 1

RapidIO II MegaCore Function v14.0 and v14.0 Arria 10

Edition User Guide

RapidIO II MegaCore Function

User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

UG-01116-2.1

Document last updated for Altera Complete Design Suite version:

Document publication date:

14.0 and 14.0 Arria 10 Edition

August 2014

Feedback Subscribe

Page 2

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 3

Contents

Chapter 1. About The RapidIO II MegaCore Function

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

New Features in the RapidIO II IP Core v14.0 and v14.0 Arria 10 Edition Releases . . . . . . . . . . . . . 1–2

RapidIO II IP Core Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

Supported Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

Device Family Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

IP Core Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–5

Simulation Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–5

Hardware Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–6

Interoperability Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–6

Performance and Resource Utilization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–7

Device Speed Grades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–8

Release Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–8

Installation and Licensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

OpenCore Plus Evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

OpenCore Plus Time-Out Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–10

Chapter 2. Getting Started

Customizing and Generating IP Cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

IFiles Generated for Altera IP Cores (Legacy Parameter Editor) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

IFiles Generated for Altera IP Cores by Qsys (Legacy Parameter Editor) . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Files Generated for Altera IP Cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Simulating IP Cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Simulating the Testbench with the ModelSim Simulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Simulating the Testbench with the VCS Simulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

Integrating Your IP Core in Your Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

Dynamic Transceiver Reconfiguration Controller for Arria V, Arria V GZ, Cyclone V, and Stratix V

Variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

Transceiver PHY Reset Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

Transceiver Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8

Adding Transceiver Analog Settings for Arria V GZ and Stratix V Variations . . . . . . . . . . . . . . . . . 2–8

External Transceiver PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8

Compiling the Full Design and Programming the FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–9

Instantiating Multiple RapidIO II IP Cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–10

Chapter 3. Parameter Settings

Physical Layer Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Supported Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Maximum Baud Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Reference Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Enable Transceiver Dynamic Reconfiguration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Transport Layer Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Enable 16-Bit Device ID Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Enable Avalon-ST Pass-Through Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Disable Destination ID Checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Logical Layer Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Maintenance Configuration Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Doorbell Configuration Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 4

iv Contents

I/O Master Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

I/O Slave Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Capability Registers Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Device Identity CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Device ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Vendor ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Device Information CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Revision ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Assembly Identity CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Assembly ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Assembly Vendor ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Assembly Information CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Revision ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Processing Element Features CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Bridge Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Memory Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Processor Present . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Enable Flow Arbitration Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Enable Standard Route Table Configuration Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Enable Extended Route Table Configuration Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Enable Flow Control Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Enable Switch Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Switch Port Information CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Number of Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Port Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Switch Route Table Destination ID Limit CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Switch Route Table Destination ID Limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Data Streaming Information CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Maximum PDU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Number of Segmentation Contexts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Source Operations CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Destination Operations CAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

Command and Status Registers Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

Data Streaming Logical Layer Control CSR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

Supported Traffic Management Types Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

Traffic Management Mode Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

Maximum Transmission Unit Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

Port General Control CSR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

Host Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Master Enable Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Discovered Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Port 0 Control CSR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Flow Control Participant Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Enumeration Boundary Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Flow Arbitration Participant Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Lane n Status 0 CSR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Transmitter Type Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Receiver Type Reset Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Extended Features Pointer CSR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Error Management Registers Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . 3–12

Chapter 4. Functional Description

Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Avalon Memory Mapped (Avalon-MM) Master and Slave Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 5

Contents v

Avalon-MM Interface Byte Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Avalon Streaming (Avalon-ST) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

RapidIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Clocking and Reset Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

Avalon System Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

Reference Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

Recovered Data Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

Clock Rate Relationships in the RapidIO II IP Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

Clock Domains in Your Qsys System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

Reset for RapidIO II IP Cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

Logical Layer Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–7

Register Access Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–7

Non-Doorbell Register Access Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

Register Access Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

Input/Output Logical Layer Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

Input/Output Avalon-MM Master Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–10

RapidIO Packet Data wdptr and Data Size Encoding in Avalon-MM Transactions . . . . . . . . . . 4–13

Input/Output Avalon-MM Master Module Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–17

Input/Output Avalon-MM Slave Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–19

Initiating Read and Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–20

Avalon-MM Burstcount and Byteenable Encoding in RapidIO Packets . . . . . . . . . . . . . . . . . . . . 4–27

Input/Output Avalon-MM Slave Module Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–31

Maintenance Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–32

Maintenance Interface Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–33

Maintenance Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–33

Initiating MAINTENANCE Read and Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–34

Responding to MAINTENANCE Read and Write Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–35

Handling Port-Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–36

Maintenance Interface Transaction Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–38

Maintenance Packet Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–43

Doorbell Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–44

Doorbell Module Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–44

Preserving Transaction Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–45

Doorbell Module Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–46

Generating a Doorbell Message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–46

Receiving a Doorbell Message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–47

Avalon-ST Pass-Through Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–48

Transaction ID Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–48

Pass-Through Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–49

Pass-Through Interface Usage Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–56

Transport Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–70

Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–71

Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–72

Physical Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–73

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–73

Physical Layer Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–74

Low-level Interface Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–74

Receiver Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–74

CRC Checking and Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–75

Low-Level Interface Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–75

Error Detection and Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–76

Physical Layer Error Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . 4–76

Protocol Violations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–77

Fatal Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–77

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 6

vi Contents

Logical Layer Error Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–77

Maintenance Avalon-MM Slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–78

Maintenance Avalon-MM Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–79

Port-Write Reception Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–80

Port-Write Transmission Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–80

Input/Output Avalon-MM Slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–80

Input/Output Avalon-MM Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–81

Avalon-ST Pass-Through Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–82

Chapter 5. Signals

Global Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

Physical Layer Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

Status Packet and Error Monitoring Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–3

Low Latency Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–3

Multicast Event Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–4

Link-Request Reset-Device Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–4

Transceiver Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–4

Register-Related Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–9

Logical and Transport Layer Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–9

Avalon-MM Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–9

Avalon-ST Pass-Through Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–10

Data Streaming Support Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–10

Packet and Error Monitoring Signal for the Transport Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–11

Error Management Extension Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–11

Error Reporting Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–13

Chapter 6. Software Interface

Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–2

Physical Layer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–6

Transport and Logical Layer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–26

Capability Registers (CARs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–26

Command and Status Registers (CSRs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–32

Maintenance Interrupt Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–34

Transmit Maintenance Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–35

Transmit Port-Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–36

Receive Port-Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–37

Input/Output Master Address Mapping Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–37

Input/Output Master Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–38

Input/Output Slave Mapping Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–39

Input/Output Slave Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–40

Input/Output Slave Pending Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–41

Error Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–42

Doorbell Message Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–53

Chapter 7. Testbench

Testbench Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–1

Testbench Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–3

Reset, Initialization, and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–3

Maintenance Write and Read Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–5

SWRITE Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–6

NREAD Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–6

NWRITE_R Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–7

NWRITE Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–8

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 7

Contents vii

Doorbell Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–8

Port-Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–9

Transactions Across the Avalon-ST Pass-Through Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–10

Testbench Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–10

Transceiver Level Connections in the Testbench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–11

Appendix A. Initialization Sequence

Appendix B. Differences Between RapidIO II MegaCore Function v12.1 and RapidIO MegaCore Function

v12.1

Additional Information

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–5

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–5

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 8

viii Contents

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 9

1. About The RapidIO II

DSP

ASSP

DSP

ASSP

CPU

MemoryMemoryMemory

Memory

DSP

Interface

Bridge

FPGA

Controller

Proprietary,

CPRI, OBSAI,

Ethernet, etc,

RapidIO II

MegaCore

Function

DSP

ASSP

RapidIO

Switch

System Interconnect

MegaCore Function

The RapidIO interconnect—an open standard developed by the RapidIO Trade

Association—is a high-performance packet-switched interconnect technology

designed to pass data and control information between microprocessors, digital signal

processors (DSPs), communications and network processors, system memories, and

peripheral devices.

The Altera

specification and targets high-performance, multi-computing, high-bandwidth, and

co-processing I/O applications. Figure 1–1 shows an example system

implementation.

Figure 1–1. Typical RapidIO Application

®

RapidIO II MegaCore® function complies with the RapidIO v2.2

Features

August 2014 Altera Corporation RapidIO II MegaCore Function

This section outlines the features and supported transactions of the RapidIO II IP core.

User Guide

Page 10

1–2 Chapter 1: About The RapidIO II MegaCore Function

Features

New Features in the RapidIO II IP Core v14.0 and v14.0 Arria 10 Edition Releases

The RapidIO II IP core v14.0 Arria 10 Edition adds the following new feature:

■ Support for Arria 10 devices

For details about changes to the IP core, refer to “Document Revision History” on

page Info–1. For an overview, refer to the RapidIO II IP core chapter in the Altera

MegaCore Library Release Notes. IP core variations that target an Arria 10 device have

additional interfaces and design requirements.

f For information about the new Altera IP design flow in the Quartus II software v14.0

and v14.0 Arria 10 Edition, which impacts all Altera IP cores, refer to the

“Introduction to Altera IP Cores” section in the “Managing Quartus II Projects”

chapter in Volume 1: Design and Synthesis of the Quartus II Handbook and to Introduction

to Altera IP Cores.

The RapidIO II IP core v13.0 and v13.1 do not add any new features.

RapidIO II IP Core Features

The RapidIO II IP core has the following features:

■ Compliant with the RapidIO Trade Association RapidIO Interconnect Specification,

Revision 2.2, June 2011, available from the RapidIO Trade Association website at

www.rapidio.org

■ Supports 8-bit or 16-bit device IDs

■ Supports incoming and outgoing multi-cast events

■ Provides a 128-bit wide Avalon Streaming (Avalon-ST) pass-through interface for

fully integrated implementation of custom user logic

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 11

Chapter 1: About The RapidIO II MegaCore Function 1–3

Features

■ Physical layer features

■ 1×/2×/4× serial with integrated transceivers

■ Fallback to 1× from 4× and 2× modes

■ Fallback to 2× from 4×

■ All five standard serial data rates supported: 1.25, 2.5, 3.125, 5.0 and

6.25 gigabaud (Gbaud)

■ Long control symbol

■ IDLE2 idle sequence

■ Extraction and insertion of command and status (CS) field

■ Support for software control of local and link-partner transmitter emphasis

■ Insertion of clock compensation sequences

■ Receive/transmit packet buffering, scrambling/descrambling, flow control,

error detection and recovery, packet assembly, and packet delineation

■ Automatic freeing of resources used by acknowledged packets

■ Automatic retransmission of retried packets

■ Scheduling of transmission, based on priority

■ Software support for ackID synchronization

■ Virtual channel (VC) 0 support

■ Reliable traffic (RT) support

■ Critical request flow (CRF) support

■ Transport layer features

■ Supports multiple Logical layer modules

■ Supports an Avalon Streaming (Avalon-ST) pass-through interface for custom

implementation of capabilities such as data streaming and message passing

■ A round-robin, priority-supporting outgoing scheduler chooses packets to

transmit from various Logical layer modules

■ Logical layer features

■ Generation and management of transaction IDs

■ Automatic response generation and processing

■ Response Request Timeout checking

■ Capability registers (CARs), command and status registers (CSRs), and Error

Management Extensions registers

■ Direct register access, either remotely or locally

■ Maintenance master and slave Logical layer modules

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 12

1–4 Chapter 1: About The RapidIO II MegaCore Function

Device Family Support

■ Input/Output Avalon

Logical layer modules with 128-bit wide datapath and burst support

■ Doorbell module supporting 16 outstanding

mechanism

■ Optional preservation of transaction order between outgoing

messages and I/O write requests

■ Registers and interrupt indicate NWRITE_R transaction completion

■ Preservation of transaction order between outgoing I/O read requests and I/O

write requests from Avalon-MM interfaces

■ Cycle-accurate simulation models for use in Altera-supported VHDL and Verilog

HDL simulators

■ IEEE-encrypted HDL simulation models for improved simulation efficiency

■ Support for OpenCore Plus evaluation

Supported Transactions

The RapidIO II IP core supports the following RapidIO transactions:

■

NREAD

request and response

■

NWRITE

request

®

Memory-Mapped (Avalon-MM) master and slave

DOORBELL

packets with time-out

DOORBELL

■

NWRITE_R

■

SWRITE

■

MAINTENANCE

■

MAINTENANCE

■

MAINTENANCE

■

DOORBELL

request

Device Family Support

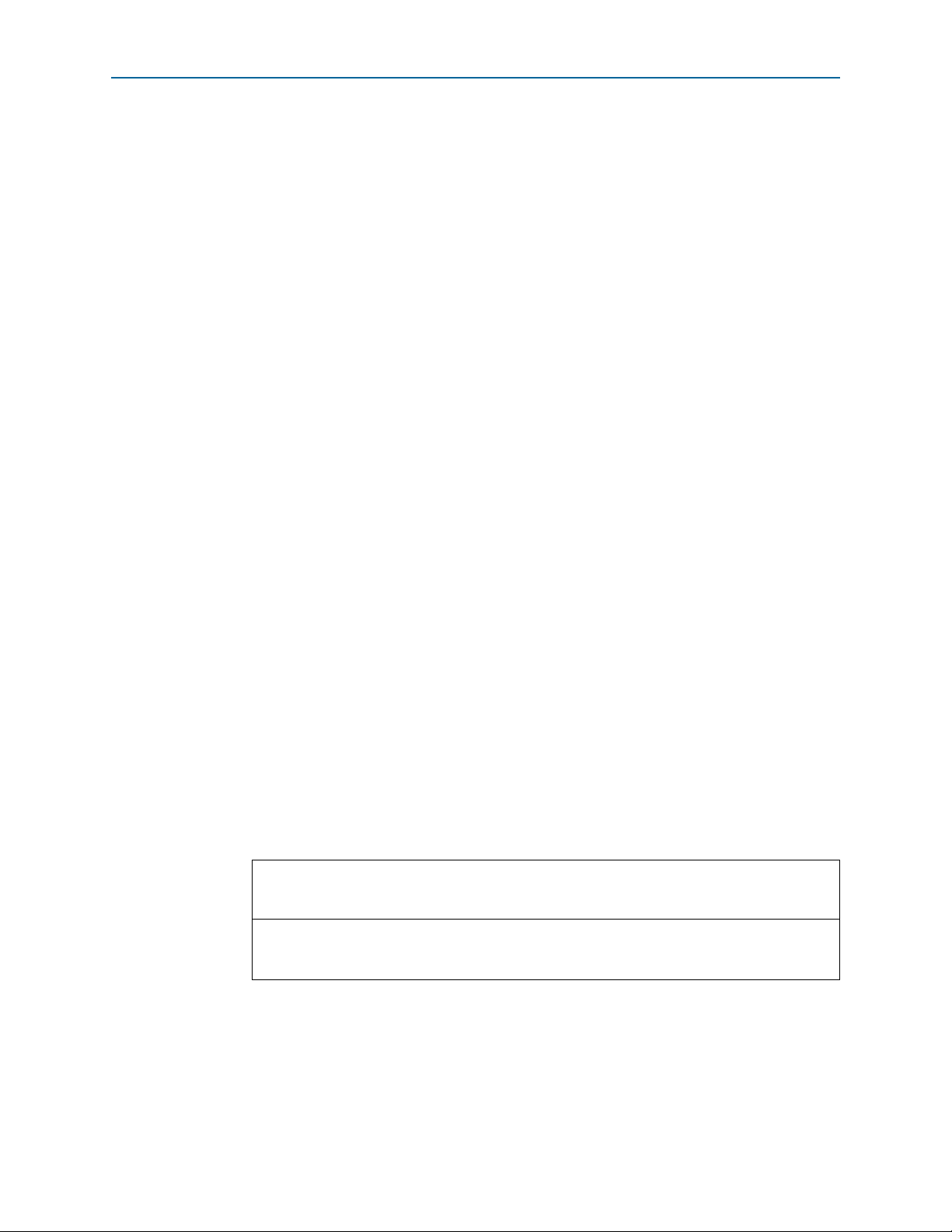

Tab le 1– 1 defines the device support levels for Altera IP cores.

Table 1–1. Altera IP Core Device Support Levels

Preliminary support—The IP core is verified with preliminary timing models for this device family.

The IP core meets all functional requirements, but might still be undergoing timing analysis for the

device family. It can be used in production designs with caution.

Final support—The IP core is verified with final timing models for this device family. The IP core

meets all functional and timing requirements for the device family and can be used in production

designs.

request and response

read request and response

write request and response

port-write request

request and response

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 13

Chapter 1: About The RapidIO II MegaCore Function 1–5

IP Core Verification

Tab le 1– 2 shows the level of support offered by the RapidIO II IP core for each Altera

device family.

Table 1–2. Device Family Support

Device Family Support

Arria 10 Refer to the What’s New in Altera IP page of the Altera website.

Arria V (GX and GT) Final

Arria V GZ Final

Cyclone V Final

Stratix V Final

Other device families No support

IP Core Verification

Before releasing a publicly available version of the RapidIO II IP core, Altera runs a

comprehensive verification suite in the current version of the Quartus

These tests use standalone methods and the Qsys system integration tool to create the

instance files. These files are tested in simulation and hardware to confirm

functionality. Altera tests and verifies the RapidIO II MegaCore function in hardware

for different platforms and environments.

Altera also performs interoperability testing to verify the performance of the IP core

and to ensure compatibility with ASSP devices.

Simulation Testing

Altera verifies the RapidIO II IP core using the following industry-standard

simulators:

■ ModelSim

■ VCS

The test suite contains testbenches that use the Cadence Serial RapidIO Verification IP

(VIP), the Cadence Compliance Management System (CMS) implementation of the

RapidIO Trade Association interoperability checklist, and the RapidIO bus functional

model (BFM) from the RapidIO Trade Association to verify the functionality of the IP

core.

The test suite confirms various functions, including the following functionality:

®

simulator

®

II software.

■ Link initialization

■ Packet format

■ Packet priority

■ Error handling

■ Throughput

■ Flow control

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 14

1–6 Chapter 1: About The RapidIO II MegaCore Function

IP Core Verification

Constrained random techniques generate appropriate stimulus for the functional

verification of the IP core. Functional and code coverage metrics measure the quality

of the random stimulus, and ensure that all important features are verified.

Hardware Testing

Altera tests and verifies the RapidIO II IP core in hardware for different platforms and

environments.

The hardware tests cover serial 1x, 2x, and 4x variations running at 1.25, 2.5, 3.125, 5.0,

and 6.25 Gbaud, and processing the following traffic types:

■

NREAD

s of various payload sizes

■

NWRITE

■

NWRITE_R

■

SWRITE

■

Port-writes

■

DOORBELL

s of various payload sizes

s of various payload sizes

s of various payload sizes

messages

■

MAINTENANCE

reads and writes

The hardware tests also cover the following control symbol types:

■

Status

■

Packet-accepted

■

Packet-retry

■

Packet-not-accepted

■

Start-of-packet

■

End-of-packet

■

Link-request, Link-response

■

Stomp

■

Restart-from-retry

■

Multicast-event

Interoperability Testing

Altera performs interoperability tests on the RapidIO II IP core, which certify that the

RapidIO II IP core is compatible with third-party RapidIO devices.

Altera performs interoperability testing with processors and switches from various

manufacturers including:

■ Texas Instruments Incorporated

■ Integrated Device Technology, Inc. (IDT)

Altera has performed interoperability tests with the IDT CPS-1848 and IDT CPS-1616

switches. Testing of additional devices is an on-going process.

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 15

Chapter 1: About The RapidIO II MegaCore Function 1–7

Performance and Resource Utilization

Performance and Resource Utilization

This section contains tables showing IP core variation sizes in the different device

families. Ta bl e 1– 3 lists the resources and expected performance for selected

variations that use these modules:

■ Minimal variation:

■ Physical layer

■ Transport layer

■ Avalon-ST pass-through interface

■ Full-featured variation:

■ Physical layer

■ Transport layer

■ Maintenance module

■ Doorbell module

■ Input/Output Avalon-MM master

■ Input/Output Avalon-MM slave

■ Error Management Registers block

All variations are configured with the following parameter settings:

■ Transceiver reference clock frequency of 156.25 MHz

■ The maximum RapidIO baud rate supported by the device

■ Support 1×, 2×, and 4× modes of operation

The numbers of ALMs, primary logic registers, and secondary logic registers in

Tab le 1– 3 are rounded up to the nearest 100.

Tab le 1– 3 shows results obtained using the Quartus II software v12.1 SP1 or Quartus

II software v14.0 Arria 10 Edition for the following devices:

■ Arria 10 (10AX048E2F29E2LG) (v14.0 Arria 10 Edition)

■ Arria V (5AGXFB3H4F35I5) (v12.1 SP1)

■ Cyclone V (5CGXFC7C6U19I7) (v12.1 SP1)

■ Stratix V (5SGXEA7H3F35C3) (v12.1 SP1)

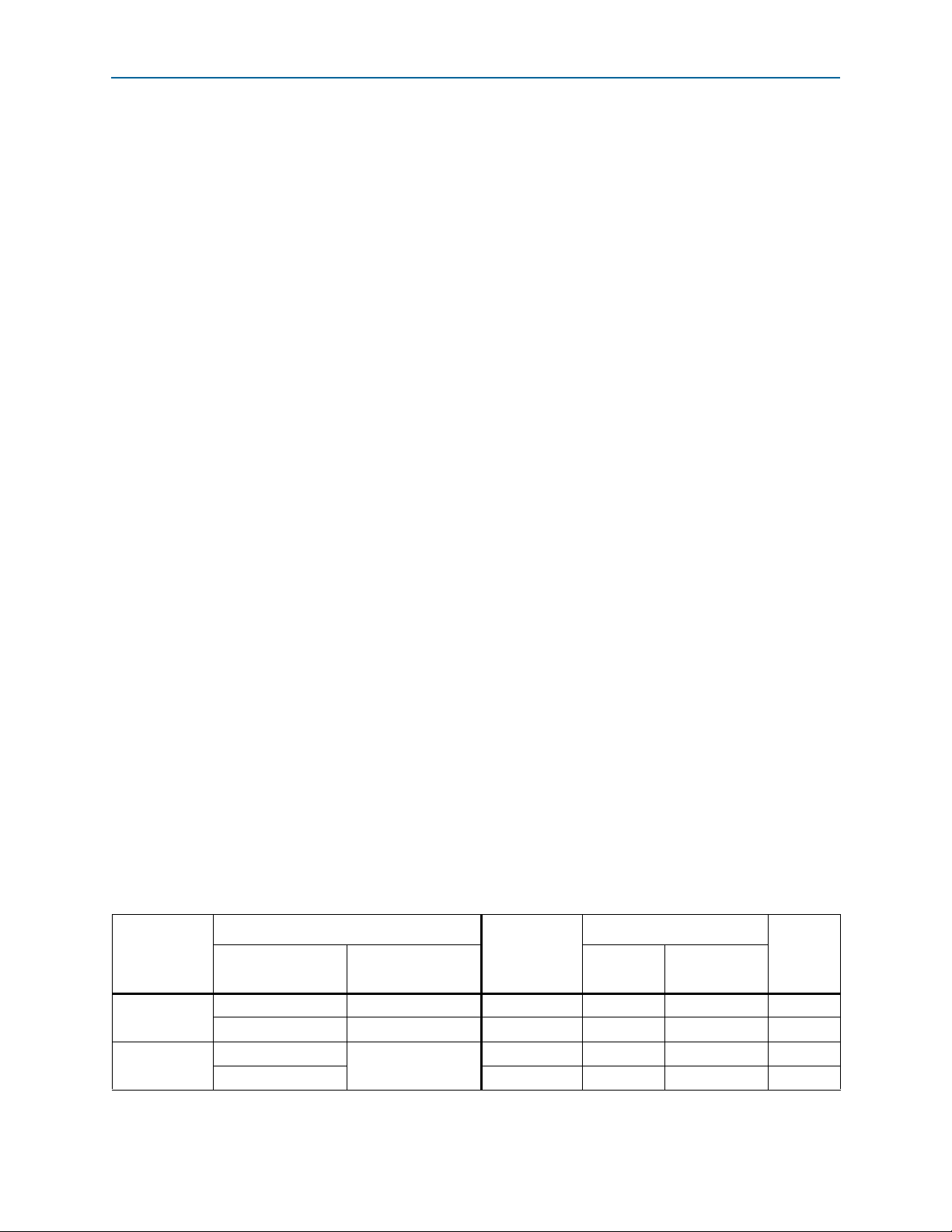

Table 1–3. RapidIO II IP Core FPGA Resource Utilization (Part 1 of 2)

Parameters

Device

ALMs

Variation Baud Rate (Gbaud) Primary Secondary

Minimal 6.25 14300 14300 1100 31

Arria 10

Arria V

Full-featured 6.25 20300 25300 1900 49

Minimal

Full-featured 24400 27500 2700 68

6.25

14800 13800 1700 41

Registers Memory

Blocks

(M10K or

(1)

M20K

)

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 16

1–8 Chapter 1: About The RapidIO II MegaCore Function

Device Speed Grades

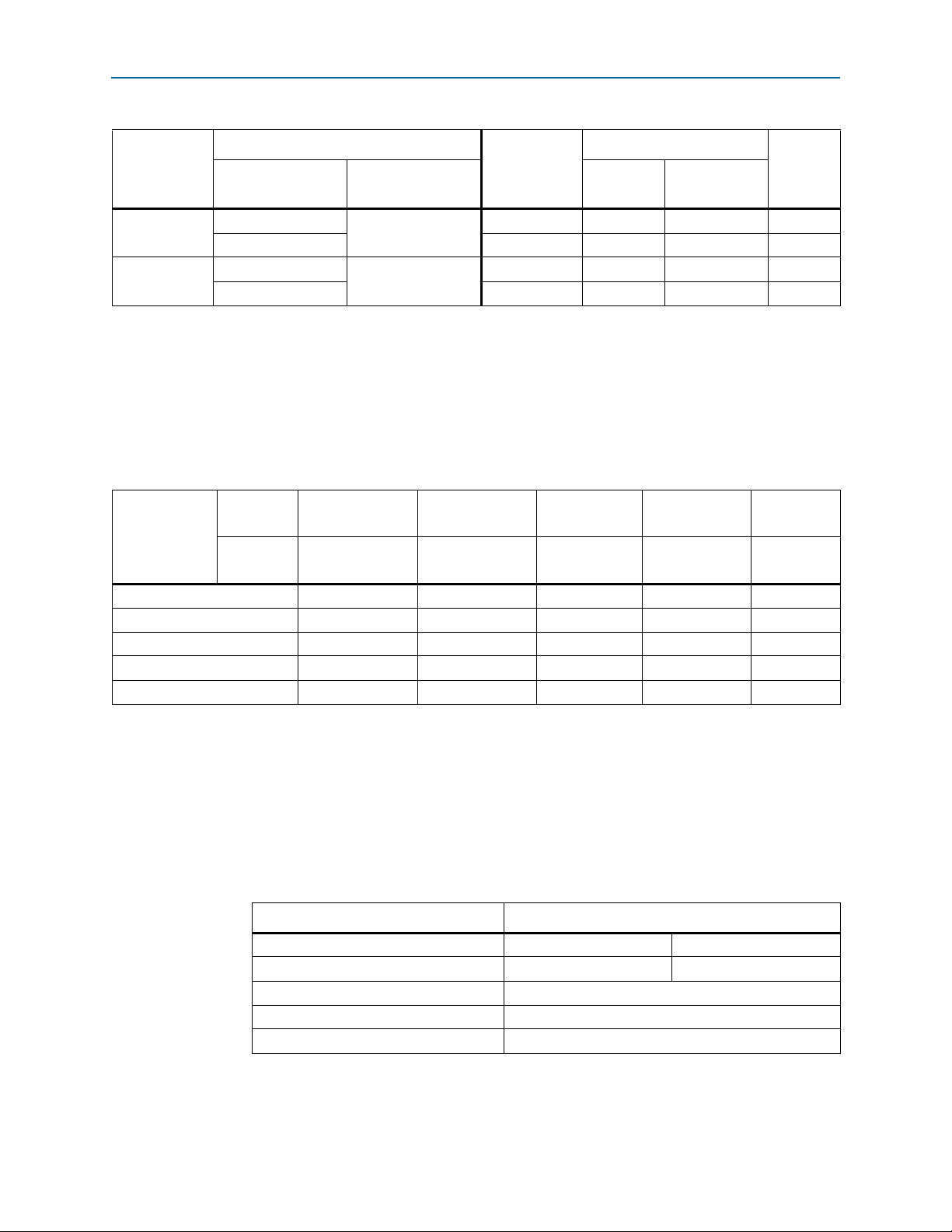

Table 1–3. RapidIO II IP Core FPGA Resource Utilization (Part 2 of 2)

Parameters

Device

Variation Baud Rate (Gbaud) Primary Secondary

Cyclone V

Full-featured 24500 27500 0 68

Minimal

Minimal

Stratix V

Note to Table 1–3:

(1) M10K for Arria V and Cyclone V devices and M20K for Stratix V devices.

Full-featured 24100 28000 2400 55

3.125

6.25

ALMs

14800 13800 0 41

14300 13800 1300 33

Registers Memory

Blocks

(M10K or

M20K

Device Speed Grades

Tab le 1– 4 shows the recommended device family speed grades for the supported link

widths and internal clock frequencies.

Table 1–4. Recommended Device Family and Speed Grades

Rate 1.25 Gbaud

Device Family

f

MAX

31.25 MHz 62.50 MHz 78.125 MHz

Arria 10 –1, –2, –3 –1, –2, –3 –1, –2, –3 –1, –2, –3 –1, –2

Arria V –4, –5, –6 –4, –5, –6 –4, –5, –6 –4, –5 –4, –5

Arria V GZ –3, –4 –3, –4 –3, –4 –3, –4 –3, –4

Cyclone V –6, –7 –6, –7 –6, –7 –7

Stratix V –2, –3, –4 –2, –3, –4 –2, –3, –4 –2, –3, –4 –2, –3, –4

Notes to Table 1–4:

(1) In this table, the entry –n indicates that both the industrial speed grade In and the commercial speed grade Cn are supported for this device

family and baud rate.

(2) In the Cyclone V device family, only Cyclone V GT devices support the 5.0 GBaud rate.

(1)

2.5

Gbaud

3.125 Gbaud

5.0

Gbaud

125

MHz

(2)

6.25

Gbaud

156.25 MHz

—

(1)

)

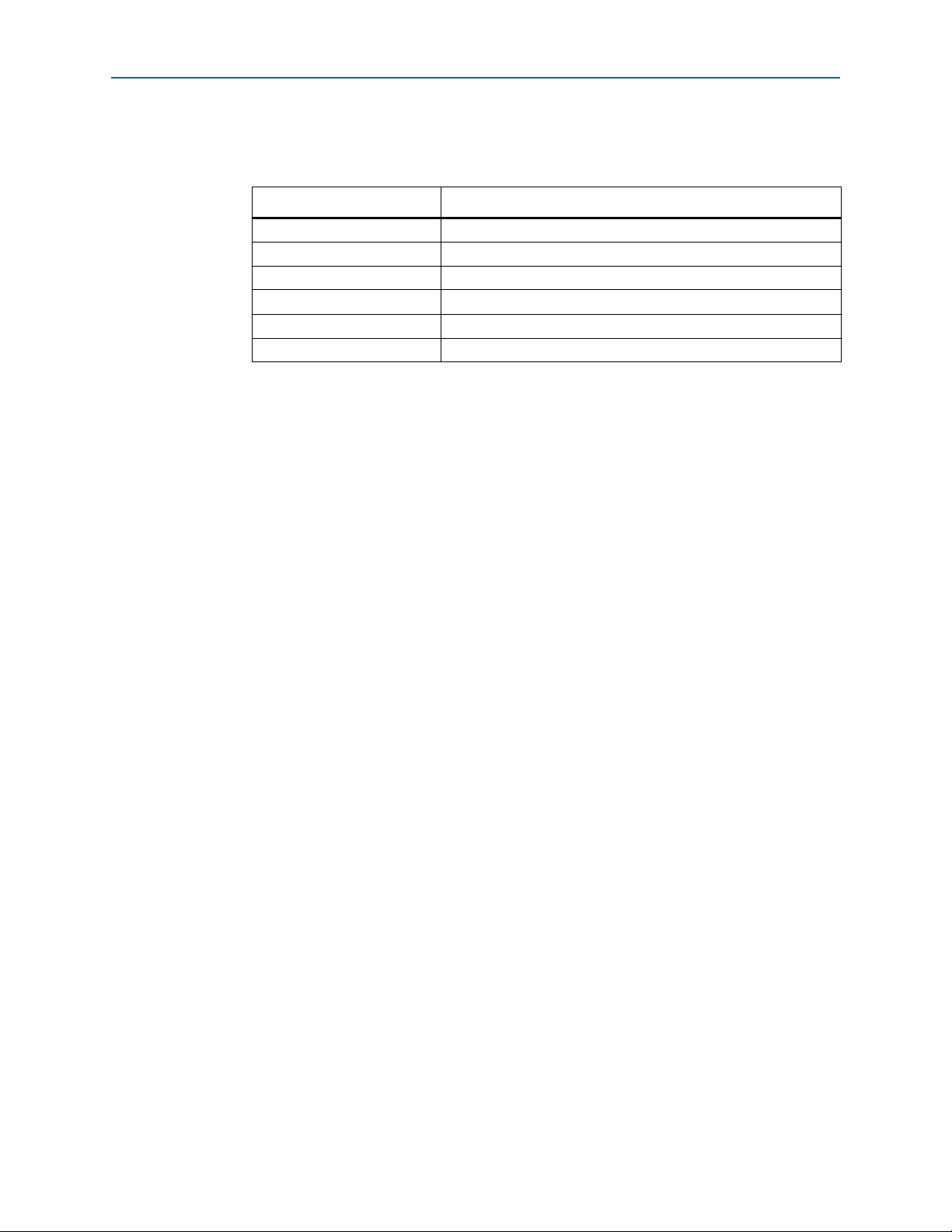

Release Information

Tab le 1– 5 provides information about this release of the RapidIO II IP core.

Table 1–5. RapidIO Release Information

Item Description

Version 14.0 14.0 Arria 10 Edition

Release Date June 2014 August 2014

Ordering Code IP-RAPIDIOII

Product ID 0108

Vendor ID 6AF7

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 17

Chapter 1: About The RapidIO II MegaCore Function 1–9

<path>

common

Contains shared components

altera_rapidio2

Contains the RapidIO II MegaCore function files

Installation directory

ip

Contains the Altera MegaCore IP Library and third-party IP cores

altera

Contains the Altera MegaCore IP Library

Installation and Licensing

Altera verifies that the current version of the Quartus II software compiles the

previous version of each IP core. Any exceptions to this verification are reported in the

MegaCore IP Library Release Notes and in the Altera RapidIO II IP core errata. Altera

does not verify compilation with IP core versions older than the previous release.

Installation and Licensing

The RapidIO II IP core is part of the Altera MegaCore IP Library, which is distributed

with the Quartus II software and downloadable from the Altera website,

www.altera.com.

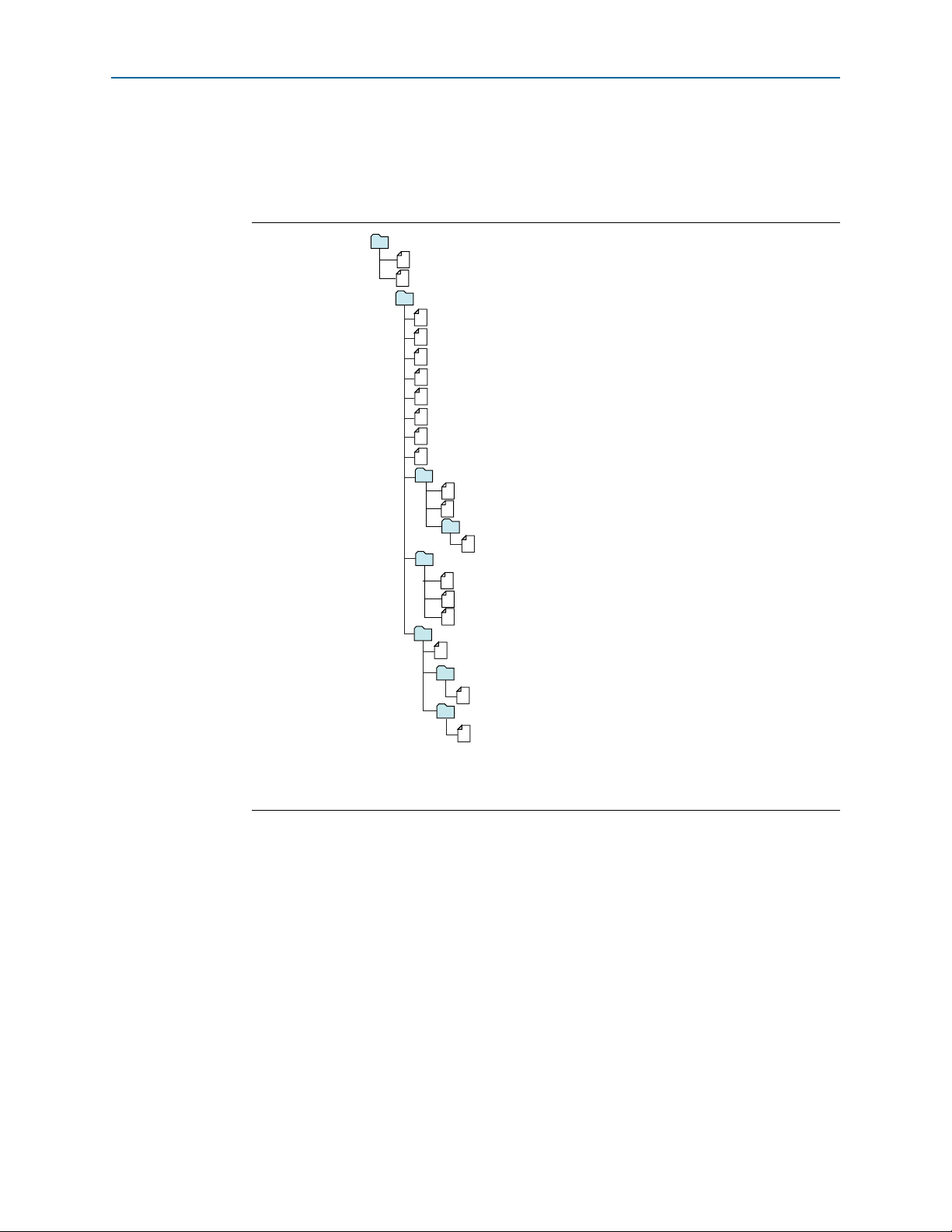

Figure 1–2 shows the directory structure after you install the RapidIO II IP core,

where

<

path> is the installation directory. The default installation directory on

Windows is C:\altera\<version number>; on Linux it is /opt/altera<version number>.

Figure 1–2. Directory Structure

You can use Altera’s free OpenCore Plus evaluation feature to evaluate the IP core in

simulation and in hardware before you purchase a license. You must purchase a

license for the IP core only when you are satisfied with its functionality and

performance, and you want to take your design to production.

After you purchase a license for the RapidIO II IP core, you can request a license file

from the Altera website at www.altera.com/licensing and install it on your computer.

When you request a license file, Altera emails you a license.dat file. If you do not have

internet access, contact your local Altera representative.

OpenCore Plus Evaluation

With the Altera free OpenCore Plus evaluation feature, you can perform the following

actions:

■ Simulate the behavior of a megafunction (Altera IP core or AMPP

megafunction) in your system using the Quartus II software and Altera-supported

VHDL and Verilog HDL simulators.

■ Verify the functionality of your design and evaluate its size and speed quickly and

easily.

■ Generate time-limited device programming files for designs that include IP cores.

■ Program a device and verify your design in hardware.

SM

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 18

1–10 Chapter 1: About The RapidIO II MegaCore Function

Installation and Licensing

OpenCore Plus Time-Out Behavior

OpenCore Plus hardware evaluation supports the following two operation modes:

■ Untethered—the design runs for a limited time.

■ Tethered—requires a connection between your board and the host computer. If

tethered mode is supported by all megafunctions in a design, the device can

operate for a longer time or indefinitely.

All megafunctions in a device time out simultaneously when the most restrictive

evaluation time is reached. If there is more than one megafunction in a design, a

specific megafunction's time-out behavior may be masked by the time-out behavior of

the other megafunctions.

1 For Altera IP cores, the untethered time-out is 1 hour; the tethered time-out value is

indefinite.

After the hardware evaluation time expires, the RapidIO II IP core behaves as if its

reset signal were held asserted, and your design stops working.

f

For Information About Refer To

Installation and licensing Altera Software Installation and Licensing

Open Core Plus AN 320: OpenCore Plus Evaluation of Megafunctions

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 19

You can customize the RapidIO II IP core to support a wide variety of applications.

When you generate the IP core you can choose whether or not to generate a

simulation model. If you generate a simulation model, Altera provides a Verilog

testbench customized for your IP core variation. If you specify a VHDL simulation

model, you must use a mixed-language simulator to run the testbench, or create your

own VHDL-only simulation environment.

Customizing and Generating IP Cores

You can customize IP cores to support a wide variety of applications. The Quartus II

IP Catalog displays IP cores available for the current target device. The parameter

editor guides you to set parameter values for optional ports, features, and output files.

To customize and generate a custom IP core variation, follow these steps:

1. In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP

core to customize. The parameter editor appears.

2. Getting Started

2. Specify a top-level name for your custom IP variation. This name identifies the IP

core variation files in your project. If prompted, also specify the target Altera

device family and output file HDL preference. Click OK.

3. Specify the desired parameters, output, and options for your IP core variation:

■ Optionally select preset parameter values. Presets specify all initial parameter

values for specific applications (where provided).

■ Specify parameters defining the IP core functionality, port configuration, and

device-specific features.

■ Specify options for generation of a timing netlist, simulation model, testbench,

or example design (where applicable).

■ Specify options for processing the IP core files in other EDA tools.

4. Click Finish or Generate to generate synthesis and other optional files matching

your IP variation specifications. The parameter editor generates the top-level .qip

or .qsys IP variation file and HDL files for synthesis and simulation. Some IP cores

also simultaneously generate a testbench or example design for hardware testing.

When you generate the IP variation with a Quartus II project open, the parameter

editor automatically adds the IP variation to the project. Alternatively, click Project >

Add/Remove Files in Project to manually add a top-level .qip or .qsys IP variation

file to a Quartus II project. To fully integrate the IP into the design, make appropriate

pin assignments to connect ports. You can define a virtual pin to avoid making

specific pin assignments to top-level signals.

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 20

2–2 Chapter 2: Getting Started

IFiles Generated for Altera IP Cores (Legacy Parameter Editor)

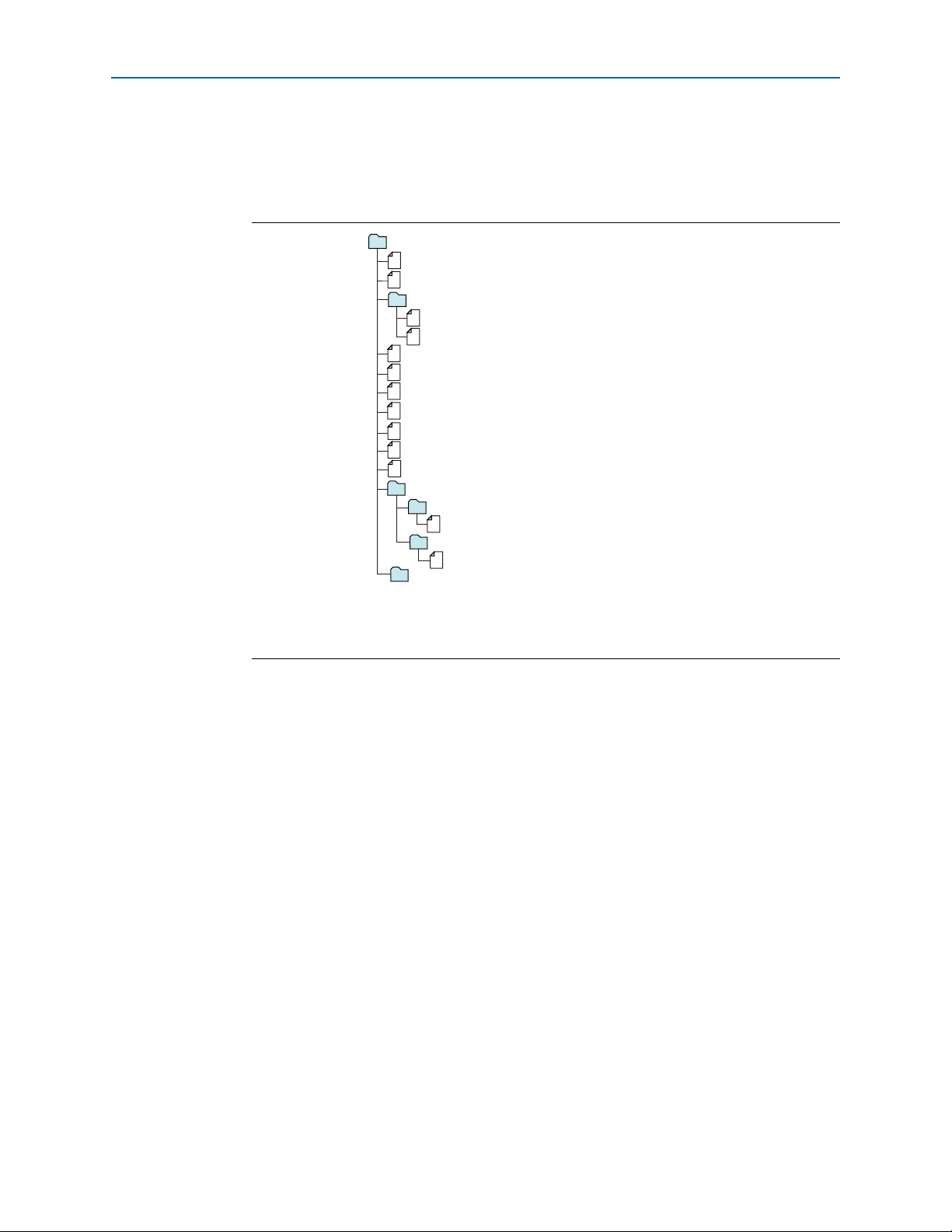

IFiles Generated for Altera IP Cores (Legacy Parameter Editor)

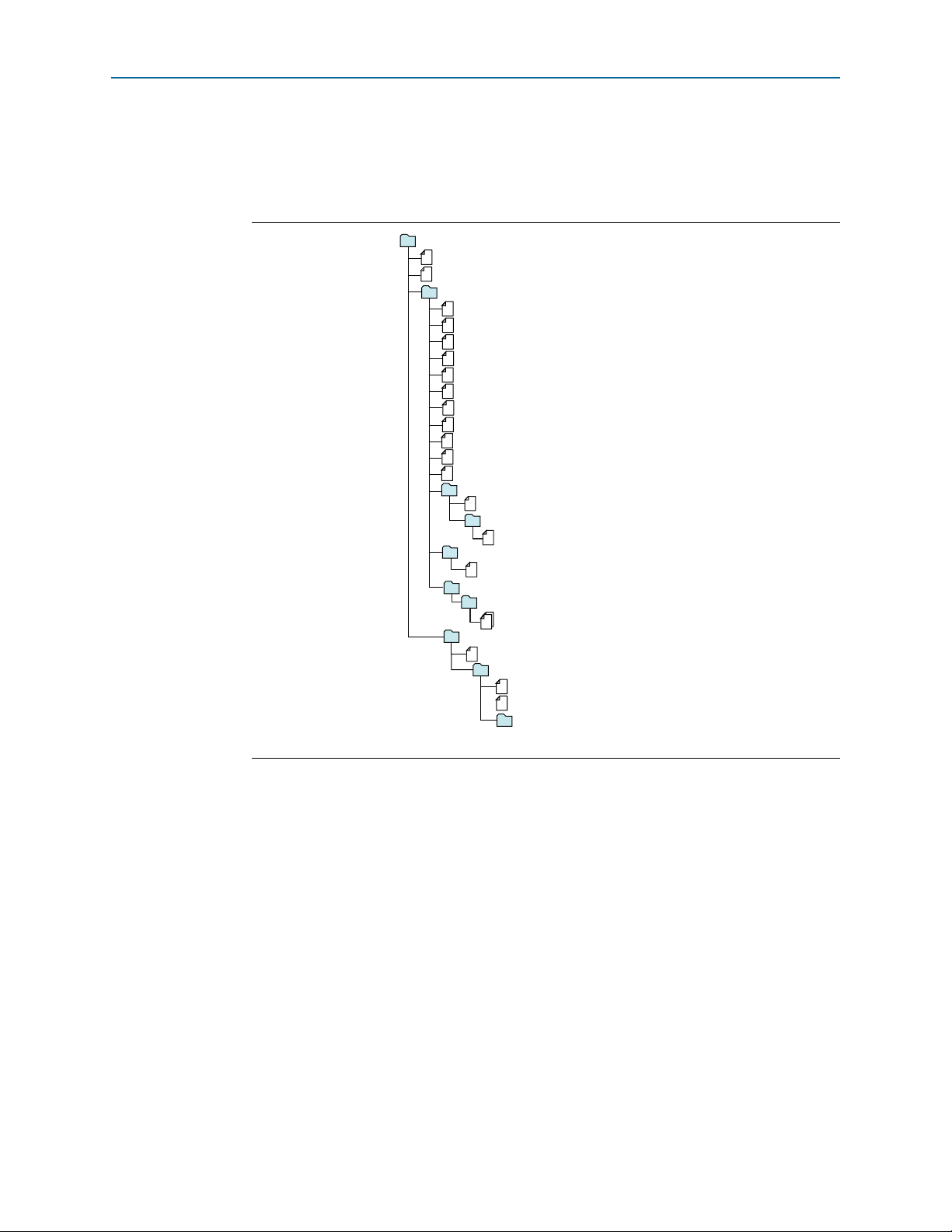

The Quartus II software version 14.0 and previous parameter editor generates the

following output file structure for Altera IP cores:

Figure 2–1. IP Core Generated Files (Legacy Parameter Editor)

<Project Directory>

<your_ip>.qip - Quartus II IP integration file

<your_ip>.v, .sv. or .vhd - Top-level IP synthesis file

<your_ip> - IP core synthesis files

<your_ip>.sv, .v, or .vhd - HDL synthesis files

<your_ip>.sdc - Timing constraints file

<your_ip>.bsf - Block symbol schematic file

<your_ip>.cmp - VHDL component declaration file

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist

<your_ip>.sip - Lists files for simulation

<your_ip>.ppf - XML I/O pin information file

<your_ip>.spd - Combines individual simulation scripts

<your_ip>_sim.f - Refers to simulation models and scripts

<your_ip>_sim

<Altera IP_name>_instance

<your_ip>_testbench or _example - testbench or example design

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

1

<Altera IP>_instance.vo - IPFS model

<simulator_vendor>

<simulator setup scripts>

1

2

1

1

1

1

In the case of the RapidIO II IP core you generate from the Quartus II IP Catalog in the

Quartus II software v14.0 Arria 10 Edition:

■ The testbench script appears in <your_ip>_sim/<vendor>.

■ The testbench files appear in <your_ip>_sim/altera_rapidio2/tb.

■ The IP core simulation files appear in <your_ip>_sim/altera_rapidio2/<vendor>.

The RapidIO II IP core does not generate an example design.

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 21

Chapter 2: Getting Started 2–3

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

<Project Directory>

<your_ip>_bb.v - Verilog HDL black box EDA synthesis file

<your_ip>_inst.v or .vhd - Sample instantiation template

synthesis - IP synthesis files

<your_ip>.qip - Lists files for synthesis

testbench - Simulation testbench files

1

<testbench_hdl_files>

<simulator_vendor> - Testbench for supported simulators

<simulation_testbench_files>

<your_ip>.v or .vhd - Top-level IP variation synthesis file

simulation - IP simulation files

<your_ip>.sip - NativeLink simulation integration file

<simulator vendor> - Simulator setup scripts

<simulator_setup_scripts>

<your_ip> - IP core variation files

<your_ip>.qip or .qsys - System or IP integration file

<your_ip>_generation.rpt - IP generation report

<your_ip>.bsf - Block symbol schematic file

<your_ip>.ppf - XML I/O pin information file

<your_ip>.spd - Combines individual simulation startup scripts

1

<your_ip>.html - Contains memory map

<your_ip>.sopcinfo - Software tool-chain integration file

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist

1

<your_ip>.debuginfo - Lists files for synthesis

<your_ip>.v, .vhd, .vo, .vho - HDL or IPFS models

2

<your_ip>_tb - Testbench for supported simulators

<your_ip>_tb.v or .vhd - Top-level HDL testbench file

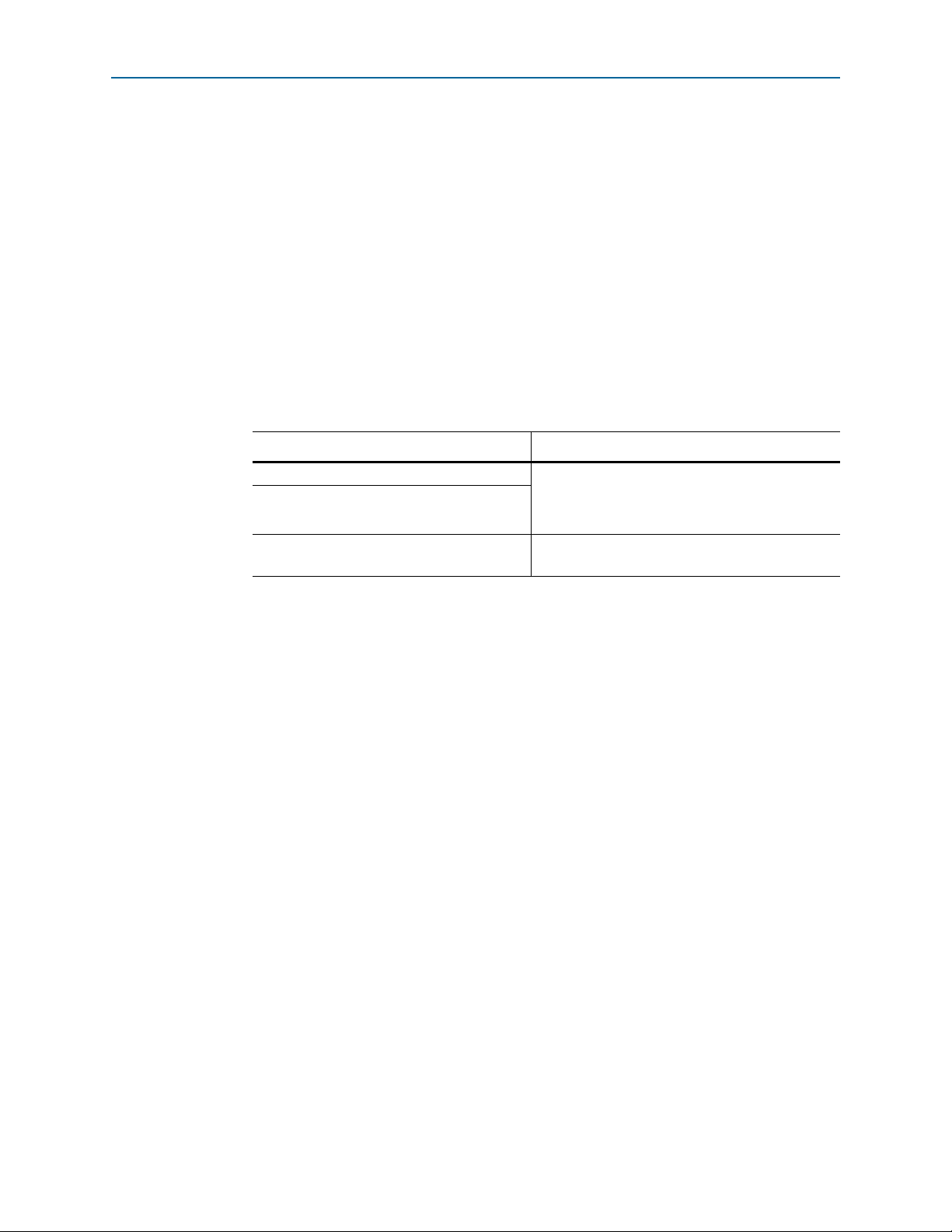

IFiles Generated for Altera IP Cores by Qsys (Legacy Parameter Editor)

IFiles Generated for Altera IP Cores by Qsys (Legacy Parameter Editor)

Generation of the IP core from Qsys produces the following output in Quartus II

software version 14.0 and previous.

Figure 2–2. IP Core Generated Files (Legacy Parameter Editor)

August 2014 Altera Corporation RapidIO II MegaCore Function

In the case of the RapidIO II IP core you generate from the Qsys IP Catalog in the

Quartus II software v14.0:

■ The testbench script appears in <Qsys system>/simulation/<vendor>.

■ The testbench files appear in <Qsys system>/simulation/submodules/tb.

■ The IP core simulation files appear in

The RapidIO II IP core does not generate an example design.

<Qsys system>/simulation/submodules/<vendor>.

User Guide

Page 22

2–4 Chapter 2: Getting Started

Files Generated for Altera IP Cores

Files Generated for Altera IP Cores

The Quartus II software version 14.0 Arria 10 Edition and later generates the

following output file structure for Altera IP cores:

Figure 2–3. IP Core Generated Files

<Project Directory>

<your_ip>.qsys - System or IP integration file

<your_ip>.sopcinfo - Software tool-chain integration file

<your_ip> - IP core variation files

<your_ip>.cmp - VHDL component declaration file

<your_ip>_bb.v - Verilog HDL black box EDA synthesis file

<your_ip>_inst.v or .vhd - Sample instantiation template

<your_ip>.ppf - XML I/O pin information file

<your_ip>.qip - Lists IP synthesis files

<your_ip>.sip - Lists files for simulation

<your_ip>_generation.rpt - IP generation report

<your_ip>.debuginfo - IP generation report

<your_ip>.html - Contains memory map

<your_ip>.bsf - Block symbol schematic

<your_ip>.spd - Combines individual simulation startup scripts

sim - IP simulation files

<your_ip>.v or .vhd - Top-level simulation file

<EDA_tool_name> - Simulator setup scripts

<simulator_setup_scripts>

synth - IP synthesis files

<your_ip>.v or .vhd - Top-level IP synthesis file

<IP subcore library> - IP subcore files

sim

<HDL files>

<your_testbench>_tb - Simulation testbench files

<your_ip>_tb.qsys - Testbench system file

<your_testbench>_tb

1. If supported and enabled for your IP variation

1

<your_testbench>_tb.csv

<your_testbench>_tb.spd

sim - IP core simulation files

1

1

In the case of the RapidIO II IP core you generate in the Quartus II software v14.0

Arria 10 Edition:

■ The testbench script appears in <Qsys_system or your_ip>/sim/<vendor>.

■ The testbench files appear in

<Qsys_system or your_ip>/altera_rapidio2_140/sim/tb.

■ The IP core simulation files appear in

<Qsys_system or your_ip>/altera_rapidio2_140/sim/<vendor>.

The RapidIO II IP core does not generate an example design.

Simulating IP Cores

The Quartus II software supports RTL- and gate-level design simulation of Altera IP

cores in supported EDA simulators. Simulation involves setting up your simulator

working environment, compiling simulation model libraries, and running your

simulation.

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 23

Chapter 2: Getting Started 2–5

Simulating IP Cores

You can use the functional simulation model and the testbench or example design

generated with your IP core for simulation. The functional simulation model and

testbench files are generated in a project subdirectory. This directory may also include

scripts to compile and run the testbench. For a complete list of models or libraries

required to simulate your IP core, refer to the scripts generated with the testbench.

You can use the Quartus II NativeLink feature to automatically generate simulation

files and scripts. NativeLink launches your preferred simulator from within the

Quartus II software.

For more information about simulating Altera IP cores, refer to Simulating Altera

Designs in volume 3 of the Quartus II Handbook.

Simulating the Testbench with the ModelSim Simulator

To simulate the RapidIO II IP core testbench using the Mentor Graphics ModelSim

simulator, perform the following steps:

1. Start the ModelSim simulator.

2. In ModelSim, change directory to the directory where the testbench simulation

script is located:

■ For Arria 10 variations, change directory to <variation>/sim/mentor.

■ For all other variations you generate from the Quartus II IP Catalog, change

directory to <variation>_sim/mentor.

■ For all other variations you generate from the Qsys IP Catalog, change

directory to <Qsys system>/simulation/mentor.

3. To set up the required libraries, compile the generated simulation model, and

exercise the simulation model with the provided testbench, type one of the

following sets of commands:

a. For non-Arria 10 variations, type the following commands:

do msim_setup.tcl

set TOP_LEVEL_NAME <variation>.tb_rio (

ld

run -all

b. For Arria 10 variations, type the following commands:

do msim_setup.tcl

set TOP_LEVEL_NAME <variation>_altera_rapidio2_140.tb_rio

ld

run -all

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 24

2–6 Chapter 2: Getting Started

Integrating Your IP Core in Your Design

Simulating the Testbench with the VCS Simulator

To simulate the RapidIO II IP core testbench using the Synopsys VCS simulator,

perform the following steps:

1. Change directory to the directory where the testbench simulation script is located:

■ For Arria 10 variations, change directory to <variation>/sim/synopsys/vcs.

■ For all other variations you generate from the Quartus II IP Catalog, change

directory to <variation>_sim/synopsys/vcs.

■ For all other variations you generate from the Qsys IP Catalog, change

directory to <Qsys system>/simulation/synopsys/vcs

2. Type the following commands:

sh vcs_setup.sh TOP_LEVEL_NAME="tb_rio"

./simv

f

Quartus II software See the Quartus II Help topics:

IP Catalog

Altera simulation models

For Information About Refer To

Integrating Your IP Core in Your Design

When you integrate your IP core instance in your design, you must pay attention to

some additional requirements. If you generate your IP core from the Qsys IP catalog

and build your design in Qsys, you can perform these steps in Qsys. If you generate

your IP core directly from the Quartus II IP catalog, you must implement these steps

manually in your design.

Dynamic Transceiver Reconfiguration Controller for Arria V, Arria V GZ, Cyclone V, and Stratix V Variations

RapidIO II IP core variations that target an Arria V, Arria V GZ, Cyclone V, or Stratix

V device require an external reconfiguration controller to function correctly in

hardware. RapidIO II IP core variations that target an Arria 10 device include a

reconfiguration controller block and do not require an external reconfiguration

controller. However, you need to control dynamic transceiver reconfiguration in Arria

10 devices through the Arria 10 dynamic reconfiguration interface if you turn on that

interface in the RapidIO II parameter editor.

“About the Quartus II Software”

“About the IP Catalog”

Simulating Altera Designs chapter in volume 3 of

the Quartus II Handbook

Keeping the reconfiguration controller external to the IP core in these devices

provides the flexibility to share the reconfiguration controller among multiple IP cores

and to accommodate FPGA transceiver layouts based on the usage model of your

application. In Arria 10 devices, you can configure individual transceiver channels

flexibly through an Avalon-MM Arria 10 transceiver reconfiguration interface.

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 25

Chapter 2: Getting Started 2–7

Integrating Your IP Core in Your Design

Altera recommends that you implement the reconfiguration controller with an Altera

Transceiver Reconfiguration Controller. The Transceiver Reconfiguration Controller

performs offset cancellation during bring-up of the transceiver channels.

The Transceiver Reconfiguration Controller is available in the IP catalog. You must

add it to your design and connect it to the RapidIO II IP core reconfiguration signals.

In the Transceiver Reconfiguration Controller parameter editor, you select the features

of the transceiver that can be dynamically reconfigured. However, you must ensure

that the following two features are turned on:

■ Enable PLL calibration

■ Enable Analog controls

An informational message in the RapidIO II parameter editor tells you the number of

reconfiguration interfaces you must configure in your dynamic reconfiguration block.

You must configure the Transceiver Reconfiguration Controller Number of

reconfiguration interfaces parameter with this value. For more information, refer to

Table 5–7 on page 5–5.

The Reconfiguration Controller communicates with the RapidIO II IP core on two

busses:

■

reconfig_to_xcvr

■

reconfig_from_xcvr

(output)

(input)

Each of these busses connects to the bus of the same name in the RapidIO II IP core.

You must also connect the following Reconfiguration Controller signals:

■

mgmt_clk_clk

■

mgmt_rst_reset

■

reconfig_busy

f For information about the Altera Transceiver Reconfiguration Controller, refer to the

Altera Transceiver PHY IP Core User Guide.

Transceiver PHY Reset Controller

You must add an Altera Transceiver PHY Reset Controller IP core to your design, and

connect it to the RapidIO II IP core reset signals. This block implements a reset

sequence that resets the device transceivers correctly. The default parameter settings

of the Altera Transceiver PHY Reset Controller IP core are compatible with the

RapidIO II IP core requirements. For more information, refer to “Reset for RapidIO II

IP Cores” on page 4–4.

f For information about the Altera Transceiver PHY Reset Controller IP core, refer to

the Altera Transceiver PHY IP Core User Guide or the Arria 10 Transceiver PHY User

Guide.

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 26

2–8 Chapter 2: Getting Started

Integrating Your IP Core in Your Design

Transceiver Settings

Altera recommends that you maintain the default Native PHY IP core settings

generated for the RapidIO II IP core. If you edit the existing Native PHY IP core, the

regenerated Native PHY IP core does not instantiate correctly in the top-level

RapidIO II IP core. If you must modify transceiver settings, perform the modifications

by editing the project Quartus Settings File (.qsf).

Adding Transceiver Analog Settings for Arria V GZ and Stratix V Variations

In general, Altera recommends that you maintain the default transceiver settings

specified by the RapidIO II IP core. However, Arria V GZ or Stratix V variations

require that you specify some analog transceiver settings.

After you generate your RapidIO II IP core in a Quartus II project that targets an

Arria V GZ or Stratix V device, perform the following steps:

1. In the Quartus II software, on the Assignments tab, click Assignment Editor.

2. In the Assignment Editor, in the Assignment Name column, double click

<<new>> and select Transceiver Analog Settings Protocol.

3. In the To column, type the name of the transceiver serial data input node in your

IP core variation. This name is the variation-specific version of the

rd

signal.

4. In the Va l u e column, click and select SRIO.

5. Repeat steps 2 to 4 to create an additional assignment, with the following

substitution:

In step 3, instead of typing the name of the transceiver serial data input node, type

the name of the transceiver serial data output put node. This name is the

variation-specific version of the

External Transceiver PLL

RapidIO II IP cores that target an Arria 10 device require an external TX transceiver

PLL to compile and to function correctly in hardware. You must instantiate and

connect this IP core to the RapidIO II IP core.

You can create an external transceiver PLL from the IP Catalog. Select the ATX PLL IP

core or the fPLL IP core. In the ATX TX PLL parameter editor, set the following

parameter values:

■ Set PLL output frequency to one half the value you select for the Maximum baud

rate parameter in the RapidIO II parameter editor. The transceiver performs dual

edge clocking, using both the rising and falling edges of the input clock from the

PLL. Therefore, this PLL output frequency setting supports the customer-selected

maximum data rate on the RapidIO link.

■ Set PLL reference clock frequency to the value you select for the Reference clock

frequency parameter in the RapidIO II parameter editor.

td

signal.

■ Turn o n Include Master Clock Generation Block.

■ Turn o n Enable bonding clock output ports.

■ Set PMA interface width to 20.

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 27

Chapter 2: Getting Started 2–9

Compiling the Full Design and Programming the FPGA

When you generate a RapidIO II IP core, the Quartus II software also generates the

HDL code for an ATX PLL, in the file

<variation>/altera_xcvr_atx_pll_a10_140/synth/altera_rapidio2_pll.v. However, the

HDL code for the RapidIO II IP core does not instantiate the ATX PLL. If you choose

to use the ATX PLL provided with the RapidIO II IP core, you must instantiate and

connect the ATX PLL instance with the RapidIO II IP core in user logic.

You must connect the TX PLL IP core to the RapidIO II IP core according to the

following rules.

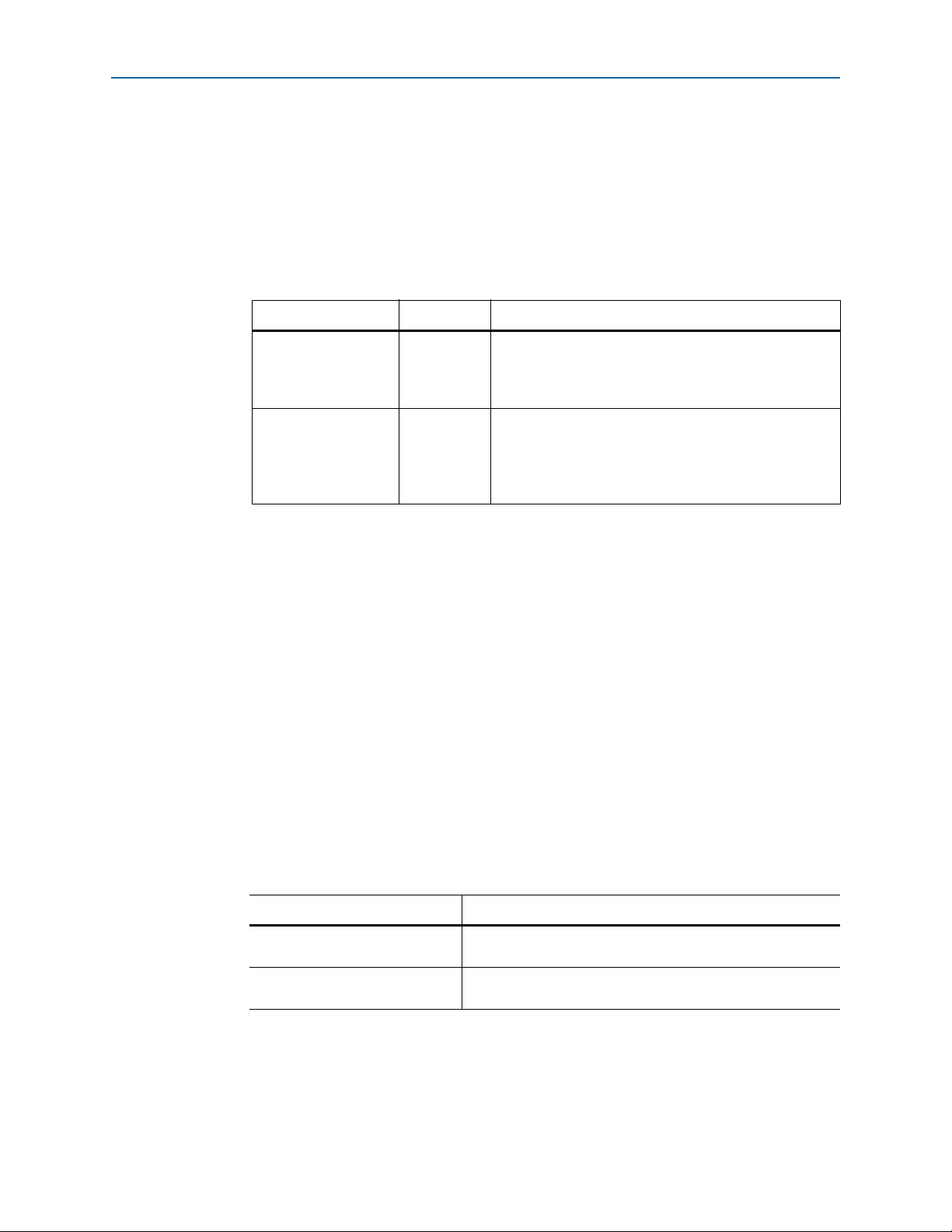

Table 2–1. External Transceiver TX PLL Connections to RapidIO II IP Core

Signal Direction Connection Requirements

pll_refclk0

tx_bonding_clocks

[(6 x <number of

lanes>)–1:0]

Input

Output

Drive the PLL

IP core

source. The minimum allowed frequency for the

pll_refclk0

Connect

tx_bonding_clocks_chN

channel N, for each transceiver channel N that connects to

the RapidIO link. The transceiver channel input ports are

RapidIO II IP core input ports.

pll_refclk0

tx_pll_refclk

clock in an Arria 10 ATX PLL is 100 MHz.

tx_bonding_clocks[6n+5:6n]

input port and the RapidIO II

signal from the same clock

input bus of transceiver

to the

For an example of how to configure and connect a TX PLL IP core to the other system

components, such as the external reset controller, refer to the cleartext testbench files

and Chapter 7, Testbench, especially Figure 7–2.

f For information about the connection requirements and options, refer to the Arria 10

Transceiver PHY User Guide.

Compiling the Full Design and Programming the FPGA

You can use the Start Compilation command on the Processing menu in the

Quartus II software to compile your design. After successfully compiling your design,

program the targeted Altera device with the Programmer and verify the design in

hardware.

1 Before compiling your design in the Quartus II software, you must perform the

modifications described in “Adding Transceiver Analog Settings for Arria V GZ and

Stratix V Variations” on page 2–8.

f

For Information About Refer To

Compiling your design

Programming the device

Quartus II Incremental Compilation for Hierarchical and TeamBased Design chapter in volume 1 of the Quartus II Handbook

Device Programming section in volume 3 of the Quartus II

Handbook

August 2014 Altera Corporation RapidIO II MegaCore Function

User Guide

Page 28

2–10 Chapter 2: Getting Started

Instantiating Multiple RapidIO II IP Cores

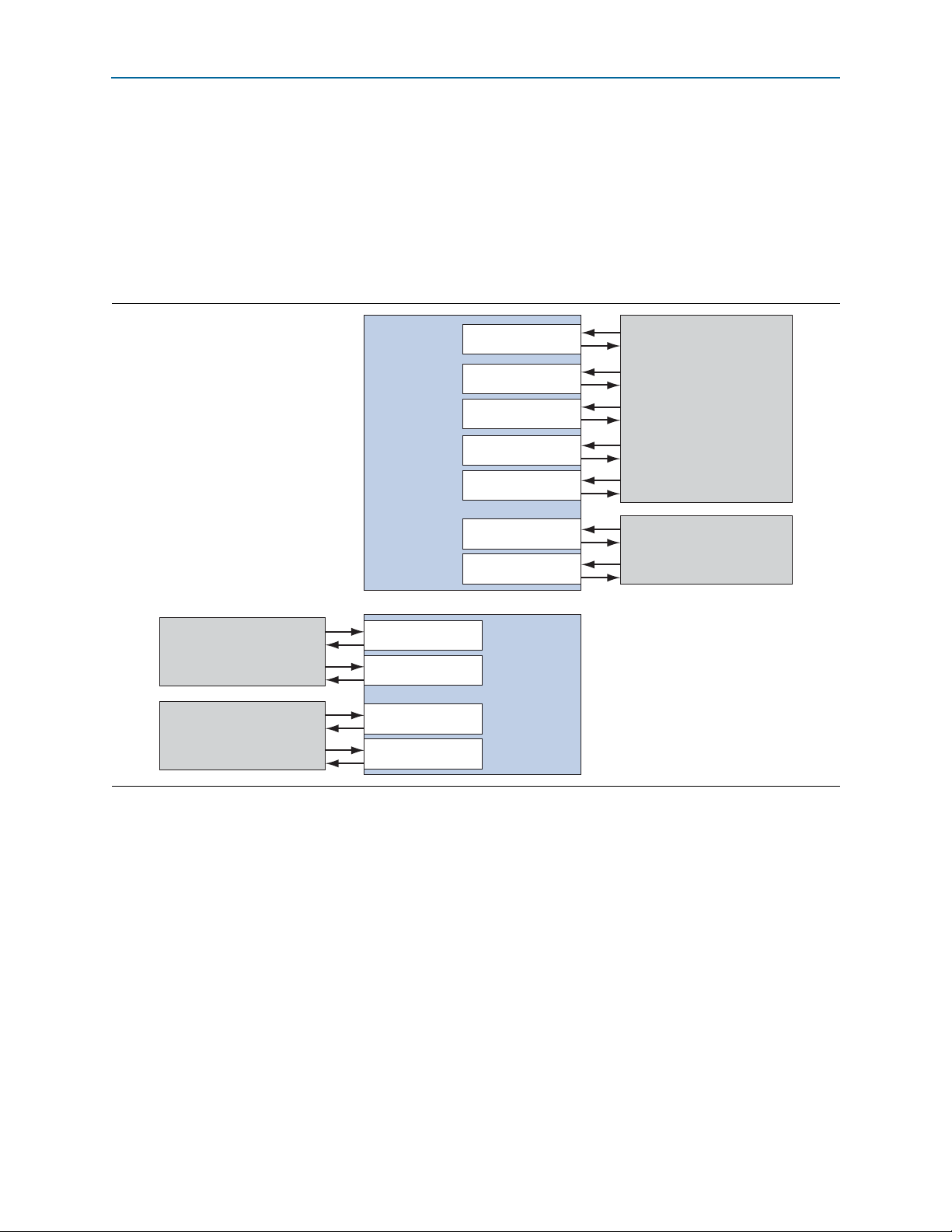

Instantiating Multiple RapidIO II IP Cores

If you want to instantiate multiple RapidIO II IP cores that target an Arria V, Arria V

GZ, Cyclone V, or Stratix V device, a few additional steps are required. These steps are

not relevant for variations that target an Arria 10 device.

The Arria V, Arria V GZ, Cyclone V, and Stratix V transceivers are configured with the

Altera Native PHY IP core. When your design contains multiple RapidIO II IP cores,

the Quartus II Fitter handles the merge of multiple Native PHY IP cores in the same

transceiver block automatically, if they meet the merging requirements specified in

the Altera Transceiver PHY IP Core User Guide.

If you have different RapidIO II IP cores in different transceiver blocks on your

device, you may choose to include multiple Transceiver Reconfiguration Controllers

in your design. However, you must ensure that the Transceiver Reconfiguration

Controllers that you add to your design have the correct number of interfaces to

control dynamic reconfiguration of all your RapidIO II IP core transceivers. The

correct total number of reconfiguration interfaces is the sum of the reconfiguration

interfaces for each RapidIO II IP core; the number of reconfiguration interfaces for

each RapidIO II IP core is the number of channels plus one. You must ensure that the

reconfig_togxb

connect to a single Transceiver Reconfiguration Controller.

and

reconfig_fromgxb

signals of an individual RapidIO II IP core

For example, if your design includes one ×4 RapidIO II IP core and three ×1

RapidIO II IP cores, the Transceiver Reconfiguration Controllers in your design must

include eleven dynamic reconfiguration interfaces: five for the ×4 RapidIO II IP core,

and two for each of the ×1 RapidIO II IP cores. The dynamic reconfiguration interfaces

connected to a single RapidIO II IP core must belong to the same Transceiver

Reconfiguration Controller. In most cases, your design has only a single Transceiver

Reconfiguration Controller, which has eleven dynamic reconfiguration interfaces. If

you choose to use two Transceiver Reconfiguration Controllers, for example, to

accommodate placement and timing constraints for your design, each of the

RapidIO II IP cores must connect to a single Transceiver Reconfiguration Controller.

RapidIO II MegaCore Function August 2014 Altera Corporation

User Guide

Page 29

Chapter 2: Getting Started 2–11

Altera

Transceiver

Reconfiguration

Controller

0

x1 RapidIO II

IP Core

x1 RapidIO II

IP Core

Altera

Transceiver

Reconfiguration

Controller

1

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_fromgxb[N-1:0]

reconfig_togxb[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_fromgxb[2N-1:N]

reconfig_togxb[2M-1:M]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_fromgxb[N-1:0]

reconfig_togxb[M-1:0]

reconfig_from_xcvr[N-1:0]