Page 1

DecemberPOS-PHY Level 4 IP Core User Guide

POS-PHY Level 4 IP Core

User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

c The POS-PHY Level 4 IP Core is scheduled for product obsolescence and discontinued

support as described in PDN1410. Therefore, Altera does not recommend use of this IP

in new designs. For more information about Altera’s current IP offering, refer to Altera’s

Intellectual Property website.

UG-IPPOSPHY4

Document last updated for Altera Complete Design Suite version:

Document publication date:

December 2014

14.1

Subscribe

Page 2

Copyright © 2014 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, and specific device designations

are trademarks and/or service marks of Altera Corporation in the U.S. and other countries. All other words and logos identified as trademarks and/or service marks

are the property of Altera Corporation or their respective owners. Altera products are protected under numerous U.S. and foreign patents and pending applications,

maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard

warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of

the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to

obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 3

The Altera® POS-PHY Level 4 MegaCore® function is an IP core that performs highspeed cell and packet transfers between physical and link-layer devices.

Release Information

Tab le 1– 1 provides information about this release of the Altera® POS-PHY Level 4 IP

core.

Table 1–1. POS-PHY Level 4 IP Core Release Information

Version 14.1

Release Date December 2014

Ordering Code IP-POSPHY4

Product ID 0088

Vendor ID 6AF7

1. About This IP Core

Item Description

f For more information about this release, refer to the MegaCore IP Library Release Notes

and Errata.

Altera verifies that the current version of the Quartus

previous version of each IP core. The MegaCore IP Library Release Notes and Errata

report any exceptions to this verification. Altera does not verify compilation with IP

core versions older than one release.

Device Family Support

IP cores can provide the types of support for target Altera device families described in

Tab le 1– 2.

Table 1–2. Altera IP Core Device Support Levels

Preliminary—The core is verified with preliminary timing models for this device family. The core

meets all functional requirements, but might still be undergoing timing analysis for the device

family. It can be used in production designs with caution.

Final—The core is verified with final timing models for this device family. The core meets all

functional and timing requirements for the device family and can be used in production designs.

FPGA Device Families

®

II software compiles the

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 4

1–2 Chapter 1: About This IP Core

Features

Tab le 1– 3 shows the level of support offered by the POS-PHY Level 4 IP core to each

Altera device family.

Table 1–3. Device Family Support

Device Family Support

®

II GX Preliminary

Arria

Arria II GZ Preliminary

Cyclone IV Preliminary

Stratix IV Full

Stratix V Preliminary

Other device families No support

Features

■ Compliant with all applicable standards, including:

■ Optical Internetworking Forum (OIF), System Packet Interface Level 4 (SPI-4)

Phase 2 Revision 1: OC-192 System Interface for Physical and Link Layer Devices,

OIF-SPI4-02.1, October 2003.

■ PMC-Sierra Inc., POS-PHY

Specification for OC-192 SONET/SDH and 10 GB/s Ethernet Applications, Issue 5

(Draft): June 2000.

TM

Level 4 A Saturn Packet and Cell Interface

■ Stratix III, Stratix IV, and Stratix V device support up to 1,250 Mbps and Stratix II

device support up to 1,040 Mbps, including integrated dynamic phase alignment

(DPA) hardware module

■ Cyclone III, device support up to 622 Mbps for 64 bit data path; support up to 250

Mbps for 32-bit data path width

■ Configurable data path width—affecting the IP core size and speed—for various

performance requirements and applications:

■ 128 bits

■ 64 bits

■ 32 bits (quarter rate)

■ Supports up to 256 ports

■ Fixed start of packet (SOP) alignment to the most significant byte lane eases

subsequent packet processing

■ First-in first-out (FIFO) buffer status management and indications

■ Configurable FIFO buffer modes

■ Shared buffer with embedded addressing

■ Individual buffers

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 5

Chapter 1: About This IP Core 1–3

FPGA

SPI-4.2 Interface

Switch

Interface

User Packet

Processing

OC-192

POS Framer

or

10 GbitE MAC

Switch

Fabri c

Atlantic Interface

POS-PHY Level 4

Receiver

POS-PHY Level 4

Transmitter

OC-192 or

10 GbitE

FPGA

Framer or MAC

Logic

Packet

Classifier

SPI-4.2 InterfaceAtlantic Interface

POS-PHY Level 4

Receiver

POS-PHY Level 4

Transmitter

General Description

■ Error detection and handling

■ Protocol checking—SPI-4.2 datapath state machine check and repair

■ Atlantic FIFO buffer overflow handling

■ Status framing hysteresis (good and bad thresholds)

■ DIP-4 hysteresis (good and bad thresholds)

■ IP functional simulation models for use in Altera-supported VHDL and Verilog

HDL simulators

■ I-Tested certification

General Description

The packet over SONET/SDH physical layer (POS-PHY) Level 4 interface, first

developed by the SATURN

®

Development Group, was adopted by the Optical

Internetworking Forum (OIF) as the System Packet Interface Level 4—Phase 2 (SPI-

4.2). Therefore, POS-PHY Level 4 and SPI-4.2 are synonymous.

The POS-PHY Level 4 IP core uses the SPI-4.2 interface for high-speed cell and packet

transfers between physical (PHY) and link-layer devices. The SPI-4.2 interface

supports a data width of 16 bits (LVDS solution) and can be a PHY-link, link-link, linkPHY, or PHY-PHY connection in multi-gigabit applications, including: asynchronous

transfer mode (ATM) and packet over SONET/SDH (STS-192/STM-64), 10 Gigabit

Ethernet, and multi-channel Gigabit and Fast Ethernet.

In compliance with the SPI-4.2 interface specification, the POS-PHY Level 4 IP core

allows you to implement transmit and receive functions.

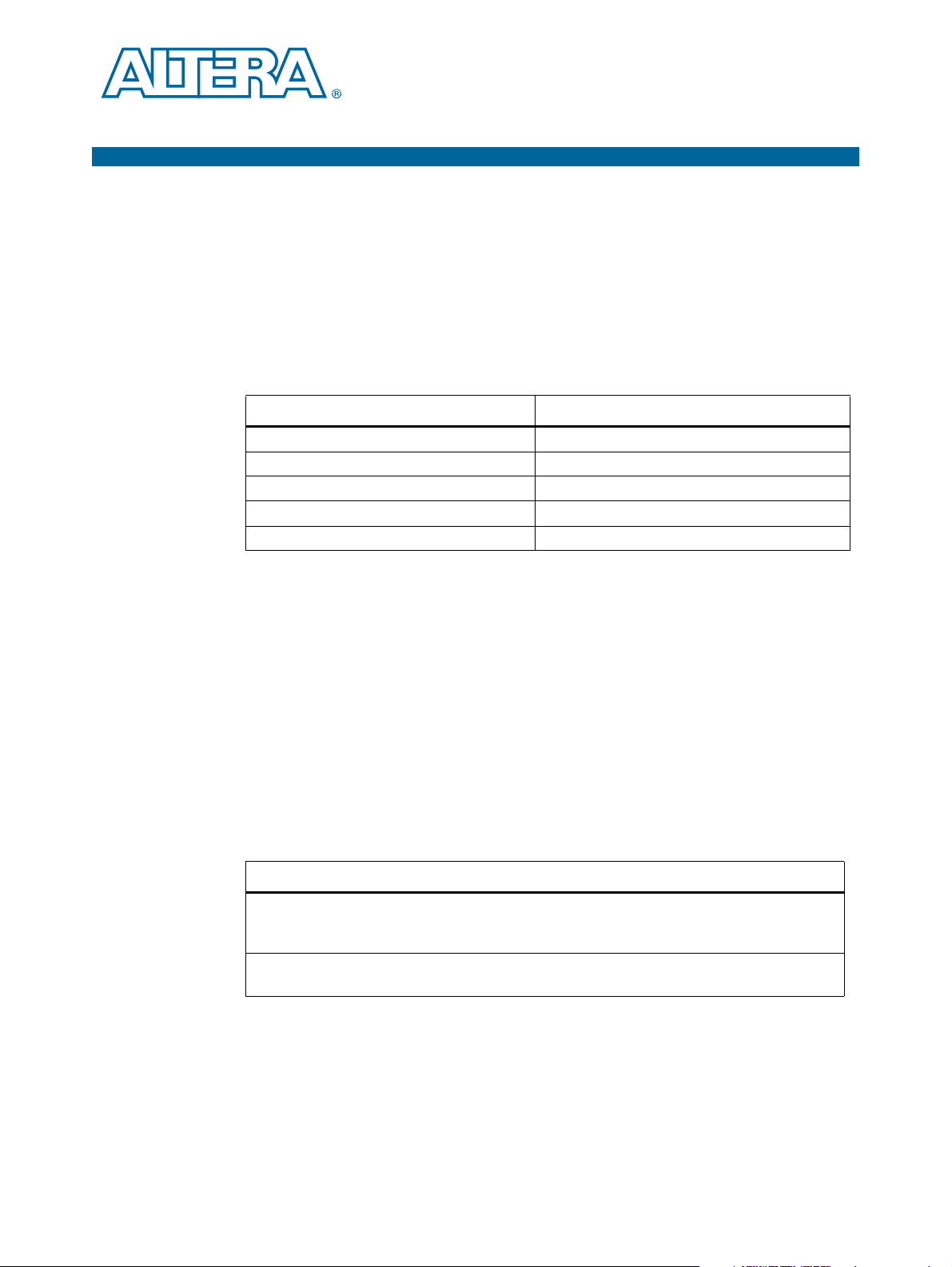

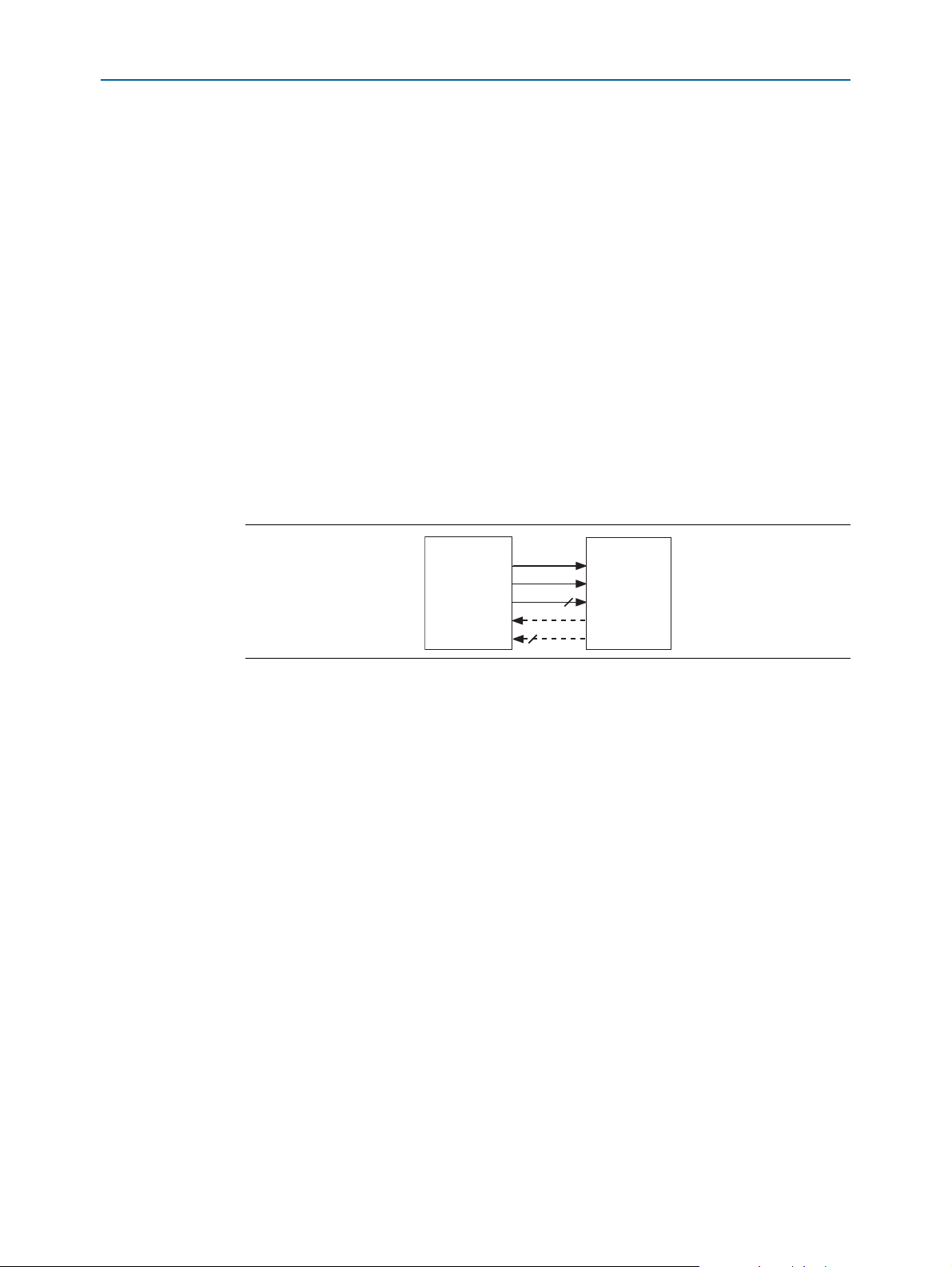

Figure 1–1 shows a full-duplex POS-PHY Level 4 IP core configured for the link layer

in an Altera FPGA device.

Figure 1–1. POS-PHY Level 4 IP Core as Link Layer Configuration

Figure 1–2 shows a full-duplex POS-PHY Level 4 IP core configured for the PHY layer

in an Altera FPGA device.

Figure 1–2. POS-PHY Level 4 IP Core as PHY Layer Configuration

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 6

1–4 Chapter 1: About This IP Core

Transmitter

Source

Receiver

Sink

tsclk

tstat[1:0]

tdclk

tctl

tdat[15:0]

rsclk

rstat[1:0]

rdclk

rctl

rdat[15:0]

General Description

Interfaces & Protocols

The following three interfaces support the POS-PHY Level 4 IP core:

■ SPI-4.2 interface

■ Atlantic

■ Av al on

You can use multiple Atlantic interfaces, but the SPI-4.2 interface only supports a

single transmitter and a single receiver.

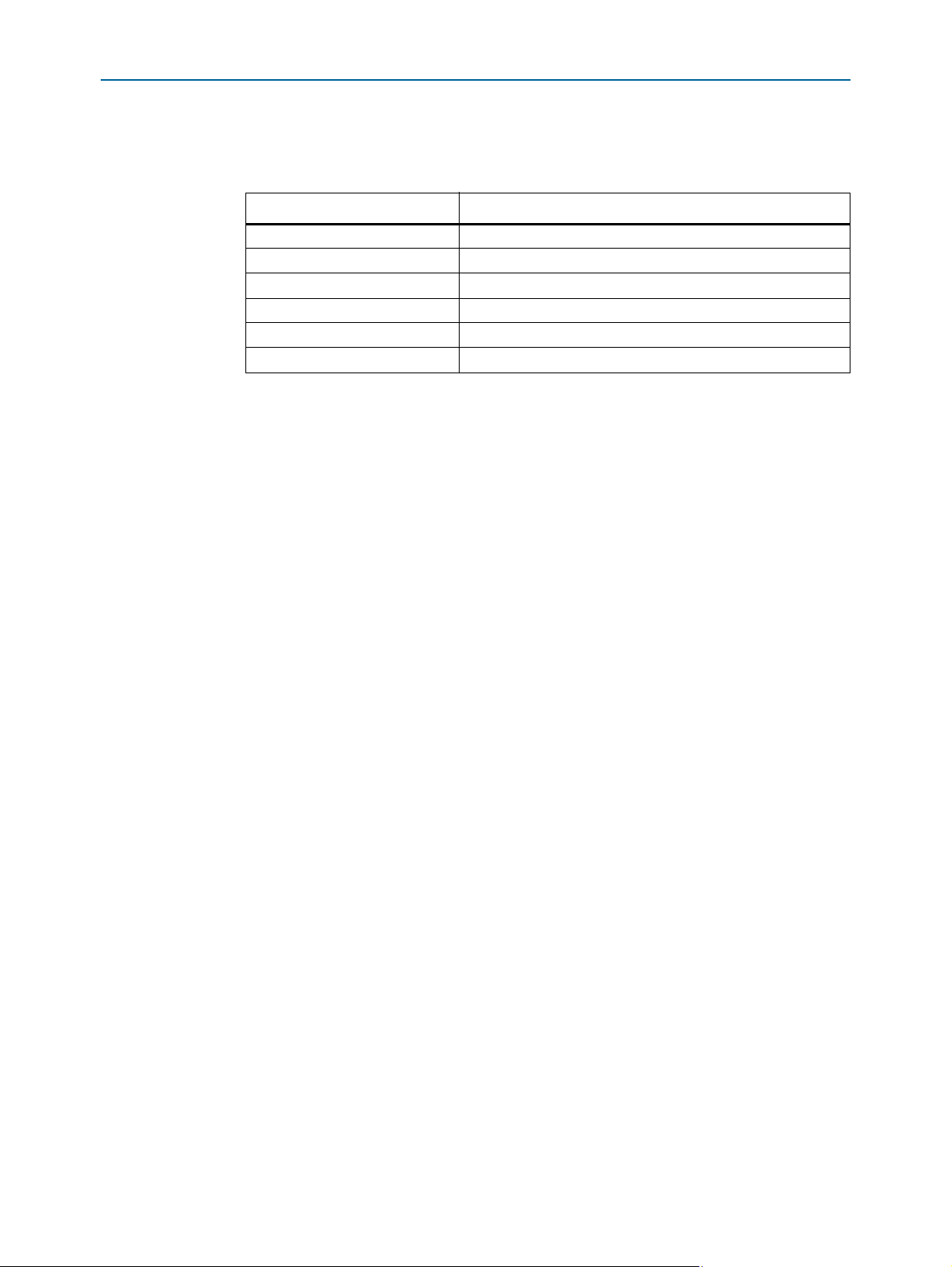

SPI-4.2 Interface

The SPI-4.2 interface is an external interface protocol developed by the Optical

Internetworking Forum (OIF). The SPI-4.2 interface features a high-speed data

portion and a FIFO buffer status portion. The high-speed portion comprises a 16-bit

data bus, a 1-bit control line, and a double data rate (DDR) clock. The FIFO buffer

status portion comprises a 2-bit status channel and a clock.

Figure 1–3 shows a full-duplex SPI-4.2 configuration.

Figure 1–3. SPI-4.2 Top-Level View

™

interface

®

Memory-Mapped (Avalon-MM) interface.

f For further information on this interface, refer to the System Packet Interface Level 4

(SPI-4) Phase 2 Revision 1: OC-192 System Interface for Physical and Link Layer Devices,

available at www.oiforum.com.

Atlantic Interface

The Atlantic interface is an Altera-developed synchronous protocol supporting both

packets and cells. The POS-PHY Level 4 IP core is an Atlantic interface slave that

transfers packets to or from the user-side logic. The Atlantic interface provides a

connection between the FIFO buffer and user logic.

f For further information on this interface, refer to the Atlantic Interface Functional

Specification.

Avalon-MM Interface

The Altera Avalon-MM interface is a simple bus architecture that connects on-chip

processors (or external processor interfaces) and peripherals. The Avalon-MM

interface specifies the port connections between master and slave components, and

specifies the timing by which these components communicate.

All Avalon-MM signals are synchronized to the Avalon-MM clock (

This synchronization simplifies the relevant timing behavior of the Avalon-MM

interface and facilitates integration with high-speed peripherals.

rav_clk/tav_clk

).

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 7

Chapter 1: About This IP Core 1–5

IP Core Verification

In this version of the POS-PHY Level 4 IP core, the Avalon-MM module is a discrete

unit that is instantiated with the parameter editor, when Asymmetric Port Support is

turned on.

f For further information on this interface, refer to the Avalon Interface Specifications.

IP Core Verification

The POS-PHY Level 4 IP core has been rigorously tested and verified in hardware for

different platforms and environments. Each environment has individual test suites

that are designed to cover the following five categories of testability:

■ Sanity

■ Flow Control

■ Error Management

■ Performance

■ Stress

These test suites contain several testbenches that are grouped and focused on testing

specific features of the POS-PHY Level 4 IP core. These individual testbenches set

unique parameters for each specific feature test.

Results of the hardware verification tests are gathered in I-tested reports available for

different ASSP devices. For example, SPI-4.2 Interoperability with PMC-Sierra’s S/UNI

9953 and SPI-4.2 Interoperability with PMC-Sierra’s S/UNI 10×GE (PM3388).

f For these reports, contact your local Altera sales representative or FAE.

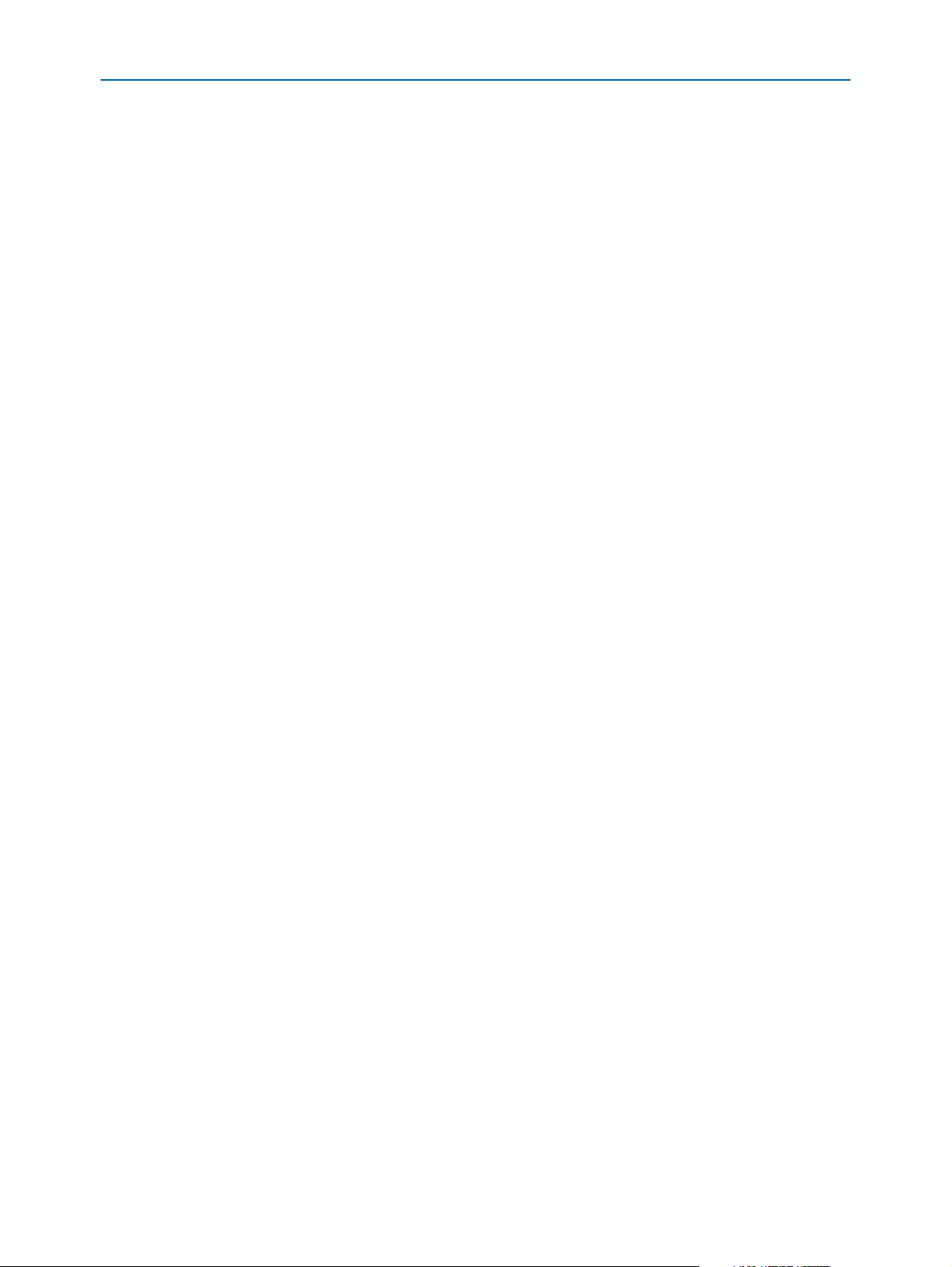

Performance and Resource Utilization

Tab le 1– 4 lists the resources and internal speeds for variations using the shared buffer

with embedded addressing mode.

Tab le 1– 5 lists the resources and internal speeds for a selection of variations using the

individual buffers mode.

All of the results use the Quartus II software version 8.1 for the following devices:

■ Stratix IV GX (EP4SGX70DF29C3 and EP4SGX230DF29C3ES)

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 8

1–6 Chapter 1: About This IP Core

Performance and Resource Utilization

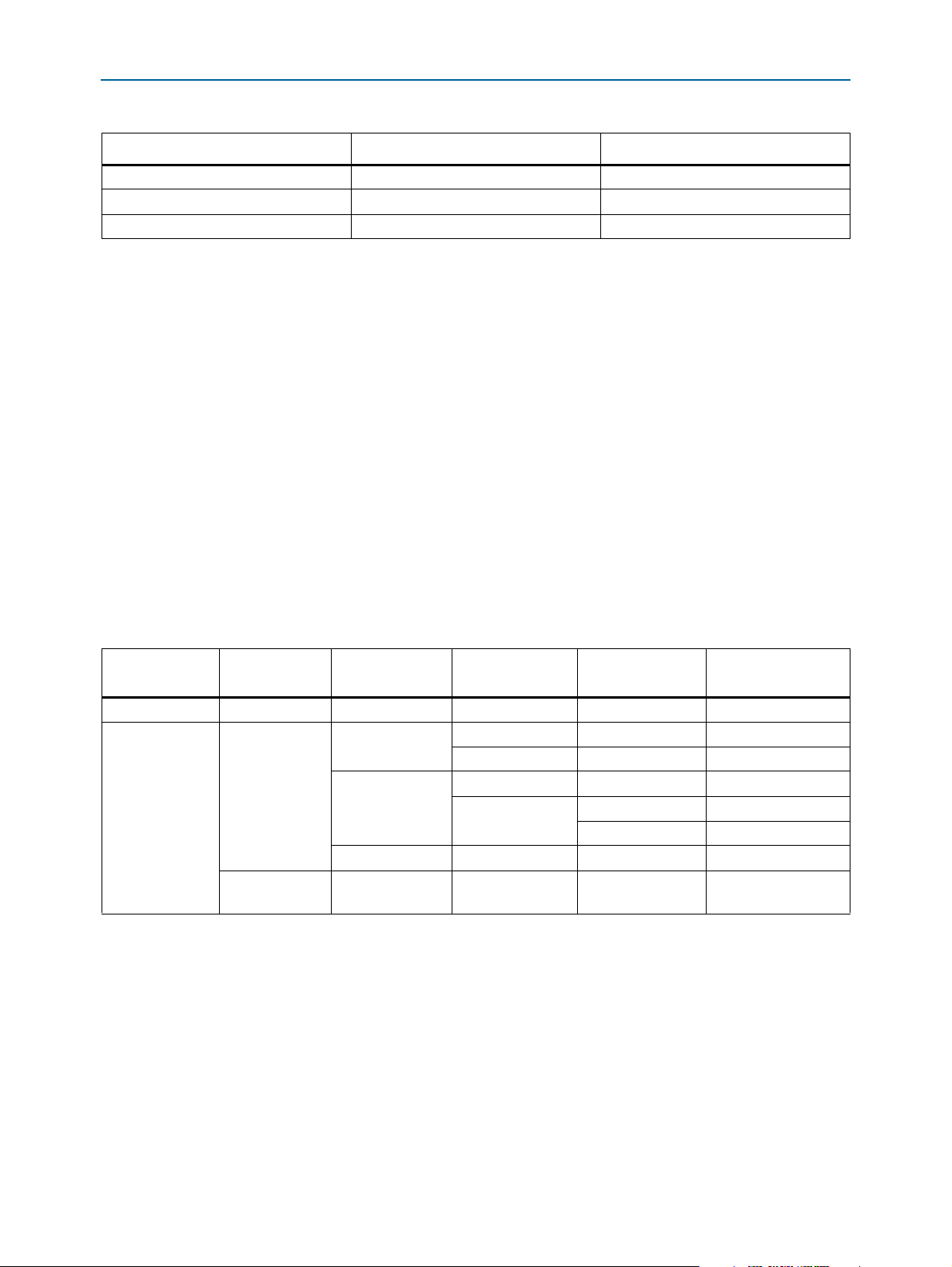

Table 1–4. Performance—Shared Buffer With Embedded Addressing Mode—Stratix IV Devices

Data Flow

Direction

Receiver

Transmitter

Parameters

Data Path

Width (bits)

Number of

Ports

ALUTs

Logic

Registers

Memory

Blocks

(M9K)

EP4SGX70

DF29C3

f

MAX

clk

(MHz)

32 1 1,190 1,294 6 204 195

64 1 1,387 1,820 16 261 284

128 1 2,215 2,741 30 186 207

32 4 1,198 1,300 6 199 156

64 4 1,398 1,826 16 273 273

128 4 2,221 2,742 30 195 195

32 10 1,138 1,249 7 213 163

64 10 1,396 1,782 18 281 270

128 10 2,273 2,709 33 187 160

32 4 1,049 1,085 5 192 185

64 4 1,032 1,454 9 262 232

128 4 1,178 1,464 17 175 181

32 10 1,023 1,119 5 178 163

64 10 1,057 1,601 9 260 225

128 10 1,331 1,770 17 190 166

EP4SGX230

DF29C3ES

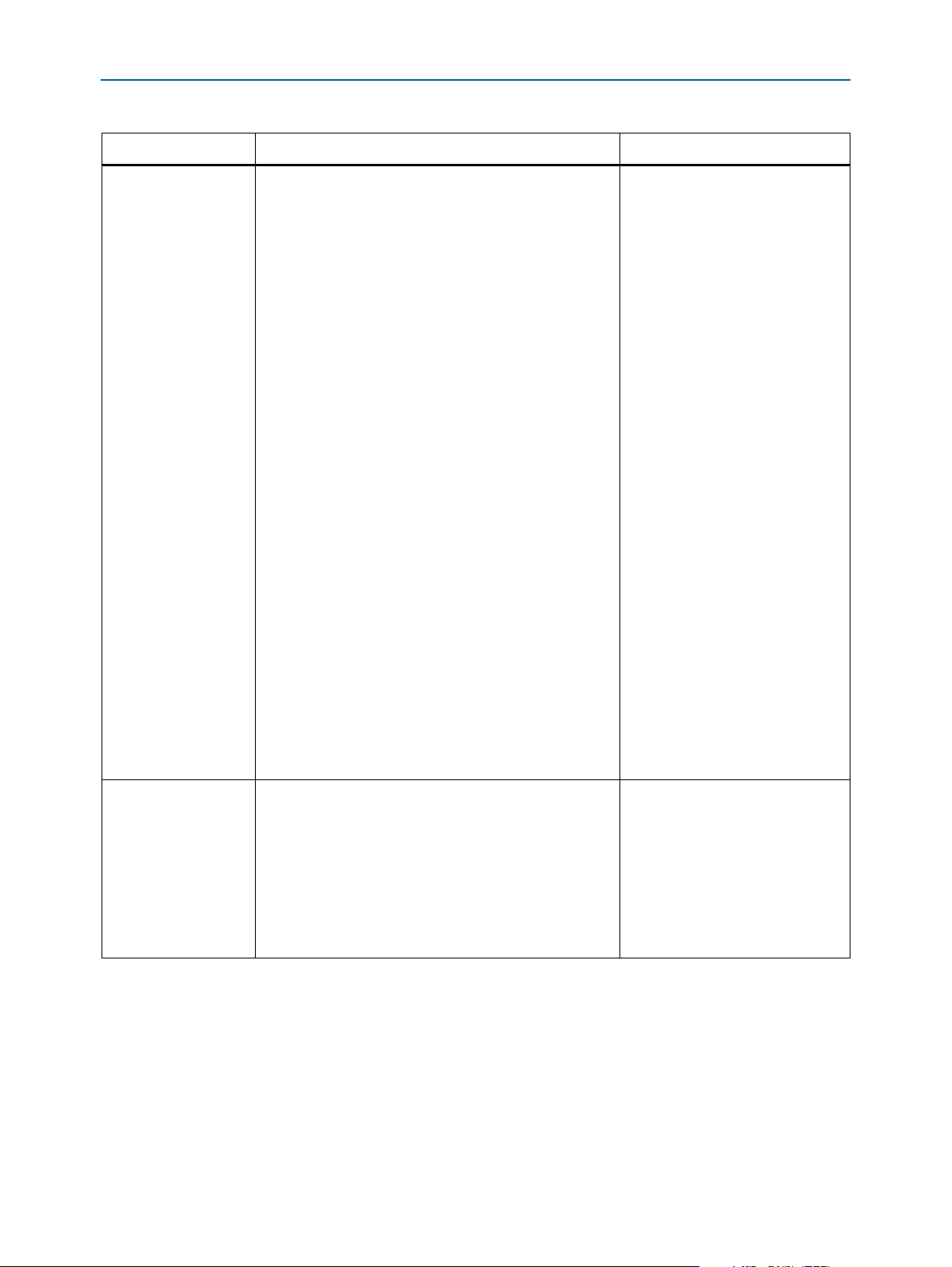

Table 1–5. Performance—Individual Buffers Mode—Stratix IV Devices

Parameters

Logic

Registers

Data Flow

Direction

Data Path

Width (bits)

Number of

ALUTs

Ports

32 4 2,245 2,427 21 182 159

64 4 2,514 2,800 40 270 268

Receiver

128 4 3,833 4,160 78 165 149

32 10 4,070 4,529 45 140 144

64 10 4,823 4,830 88 255 254

32 1 1,155 1,213 6 165 176

64 1 1,309 1,784 10 245 182

128 1 1,710 2,245 18 177 171

Transmitter

32 4 2,563 2,524 18 130 151

64 4 2,726 2,997 34 183 212

128 4 3,430 3,778 66 166 153

32 10 5,210 4,789 42 120 118

64 10 5,733 5,188 82 153 213

Memory

Blocks

(M9K)

EP4SGX70

DF29C3

f

MAX

clk

(MHz)

EP4SGX230

DF29C3ES

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 9

Chapter 1: About This IP Core 1–7

acds

quartus - Contains the Quartus II software

ip - Contains the Altera IP Library and third-party IP cores

altera - Contains the Altera IP Library source code

<IP core name> - Contains the IP core source files

Installing and Licensing IP Cores

Installing and Licensing IP Cores

The Quartus II software includes the Altera IP Library. The library provides many

useful IP core functions for production use without additional license. You can fully

evaluate any licensed Altera IP core in simulation and in hardware until you are

satisfied with its functionality and performance.

Some Altera IP cores, such as MegaCore

separate license for production use. After you purchase a license, visit the Self Service

Licensing Center to obtain a license number for any Altera product. For additional

information, refer to Altera Software Installation and Licensing.

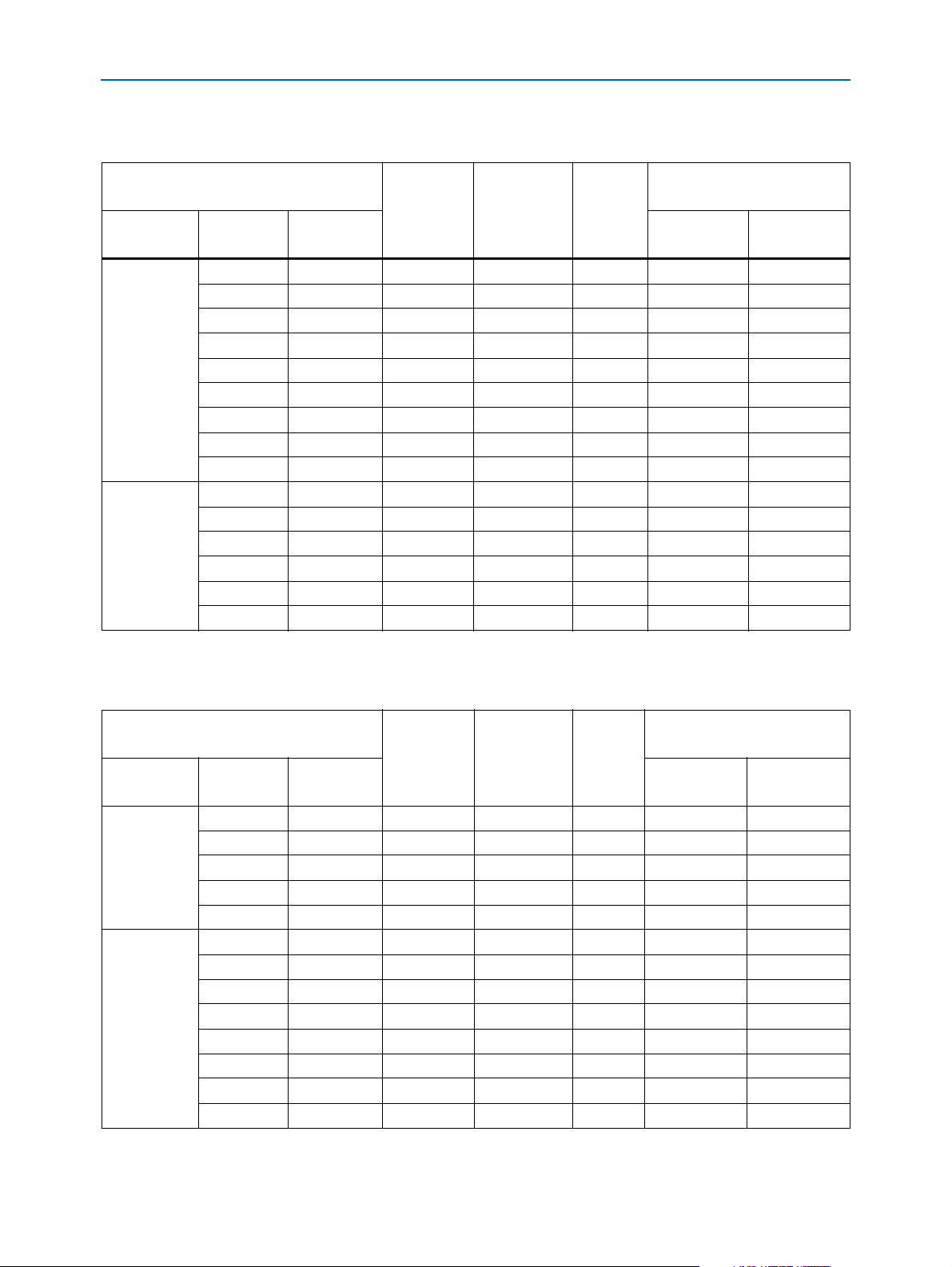

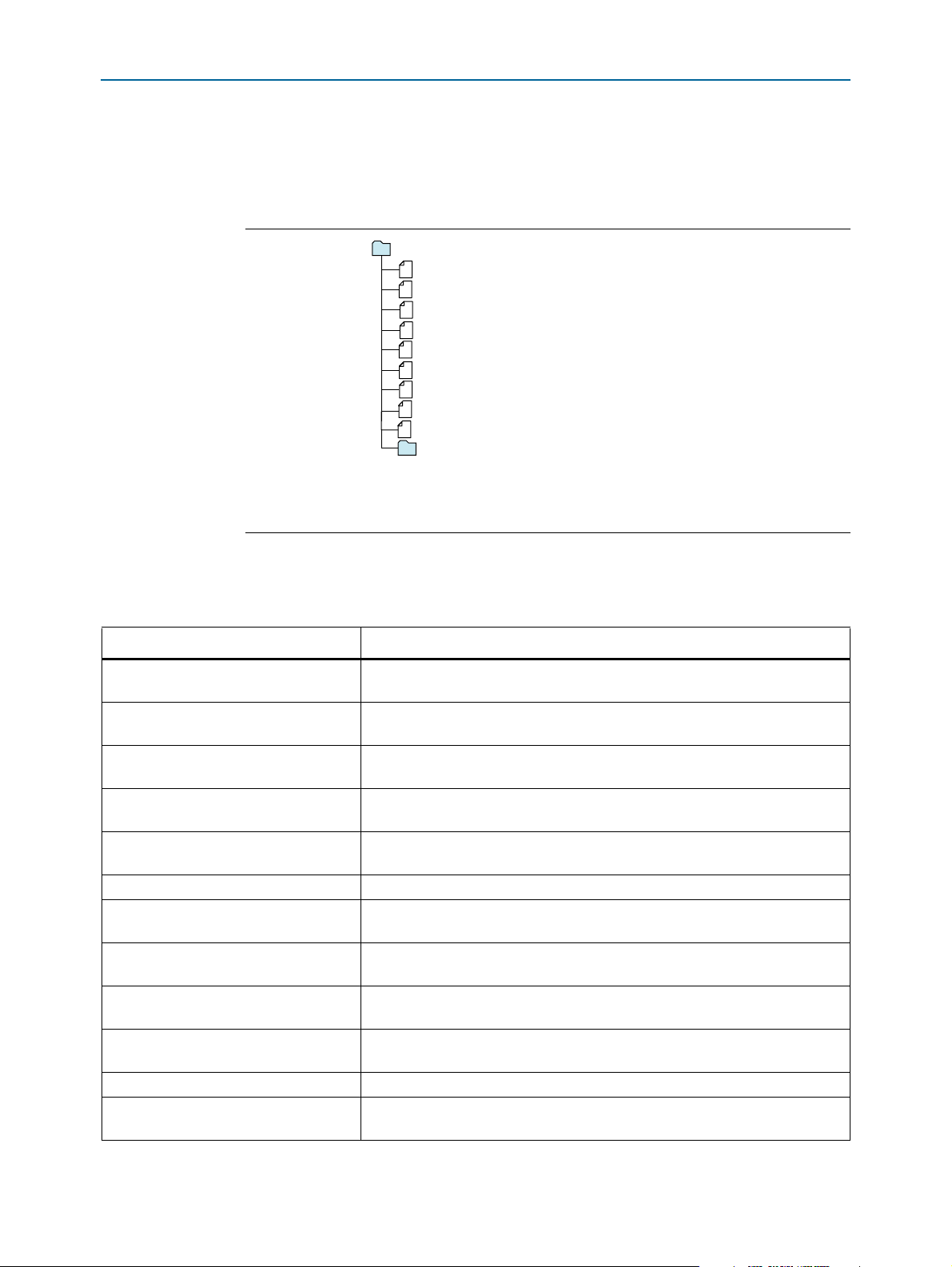

Figure 1–4. IP core Installation Path

1 The default installation directory on Windows is <drive>:\altera\<version number>;

on Linux it is <home directory>/altera/<version number>.

®

functions, require that you purchase a

OpenCore Plus IP Evaluation

Altera's free OpenCore Plus feature allows you to evaluate licensed MegaCore IP

cores in simulation and hardware before purchase. You need only purchase a license

for MegaCore IP cores if you decide to take your design to production. OpenCore Plus

supports the following evaluations:

■ Simulate the behavior of a licensed IP core in your system.

■ Verify the functionality, size, and speed of the IP core quickly and easily.

■ Generate time-limited device programming files for designs that include IP cores.

■ Program a device with your IP core and verify your design in hardware.

OpenCore Plus evaluation supports the following two operation modes:

■ Untethered—run the design containing the licensed IP for a limited time.

■ Tethered—run the design containing the licensed IP for a longer time or

indefinitely. This requires a connection between your board and the host

computer.

All IP cores using OpenCore Plus in a design time out simultaneously when any IP

core times out.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 10

1–8 Chapter 1: About This IP Core

Installing and Licensing IP Cores

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 11

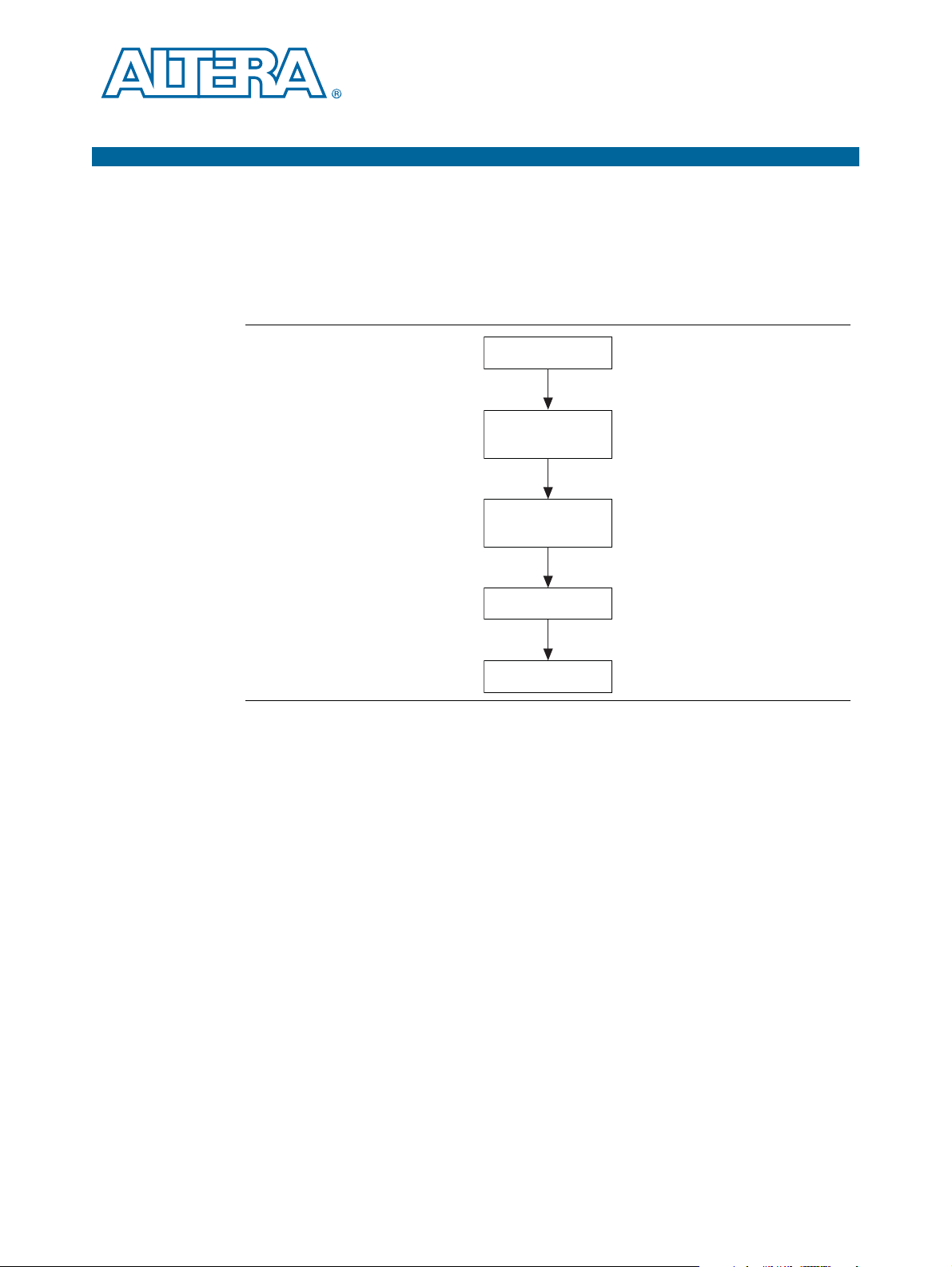

Design Flow

Specify Parameters

Compile Design

Program Device

Simulate with

Te st bench

Apply Timing

Constraints

2. Getting Started

Figure 2–1 shows the stages for creating a system with the POS-PHY Level 4 IP core

and the Quartus

Figure 2–1. Design Flow

®

II software. The sections in this chapter describe each stage.

IP Catalog and Parameter Editor

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

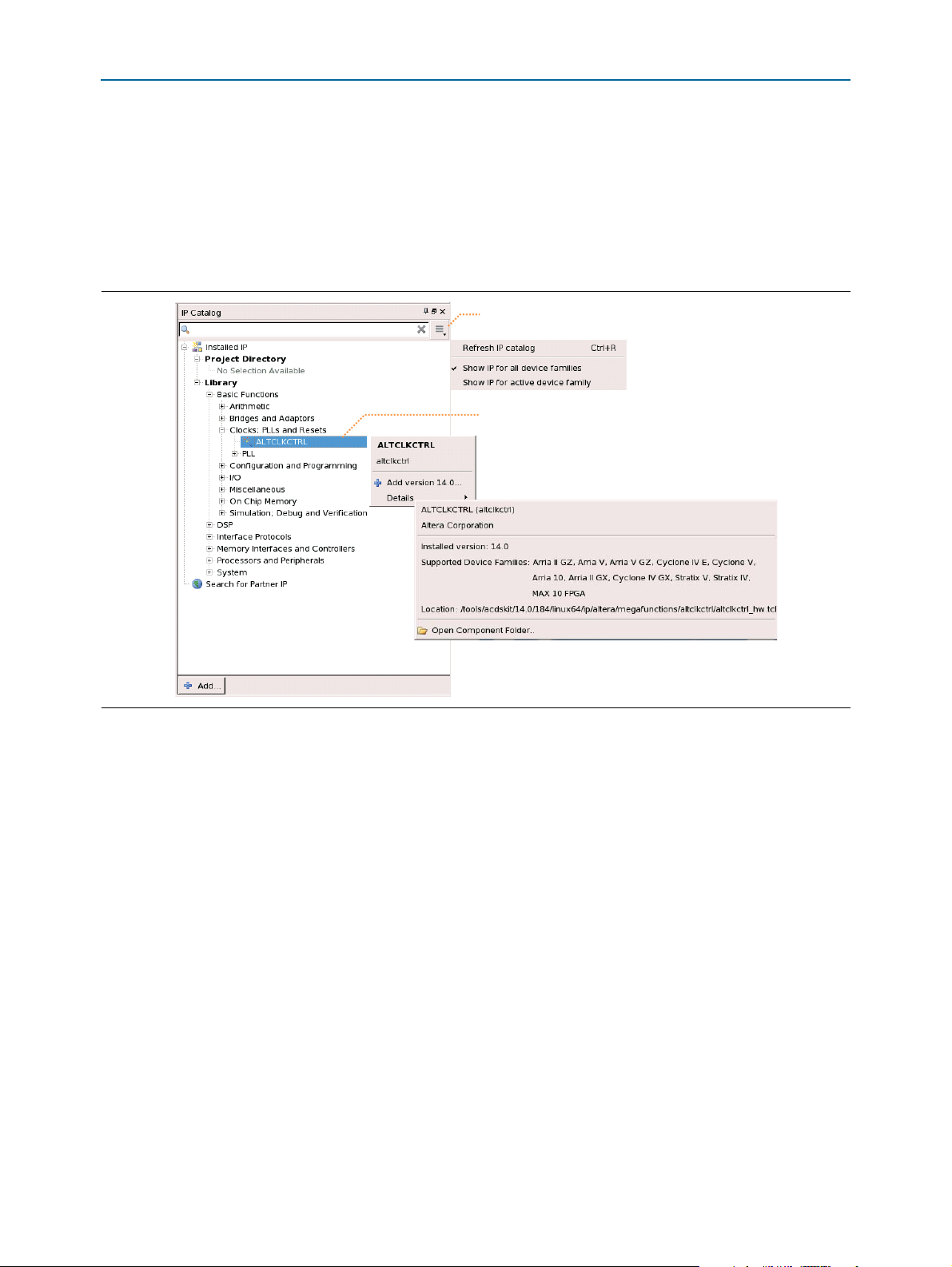

The Quartus II IP Catalog (Too ls > I P C a t a l o g) and parameter editor help you easily

customize and integrate IP cores into your project. You can use the IP Catalog and

parameter editor to select, customize, and generate files representing your custom IP

variation.

The IP Catalog automatically displays the IP cores available for your target device.

Double-click any IP core name to launch the parameter editor and generate files

representing your IP variation. The parameter editor prompts you to specify your IP

variation name, optional ports, architecture features, and output file generation

options. The parameter editor generates a top-level .qsys or .qip file representing the

IP core in your project. Alternatively, you can define an IP variation without an open

Quartus II project. When no project is open, select the Device Family directly in IP

Catalog to filter IP cores by device.

1 The IP Catalog is also available in Qsys (View > IP Catalog). The Qsys IP Catalog

includes exclusive system interconnect, video and image processing, and other

system-level IP that are not available in the Quartus II IP Catalog.

Use the following features to help you quickly locate and select an IP core:

Page 12

2–2 Chapter 2: Getting Started

Using the Parameter Editor

■ Filter IP Catalog to Show IP for active device family or Show IP for all device

families.

■ Search to locate any full or partial IP core name in IP Catalog. Click Search for

Partner IP, to access partner IP information on the Altera website.

■ Right-click an IP core name in IP Catalog to display details about supported

devices, installation location, and links to documentation.

Figure 2–2. Quartus II IP Catalog

Search and filter IP for your target device

Double-click to customize, right-click for information

1 The IP Catalog and parameter editor replace the MegaWizard

the Quartus II software. The Quartus II software may generate messages that refer to

the MegaWizard Plug-In Manager. Substitute “IP Catalog and parameter editor” for

“MegaWizard Plug-In Manager” in these messages.

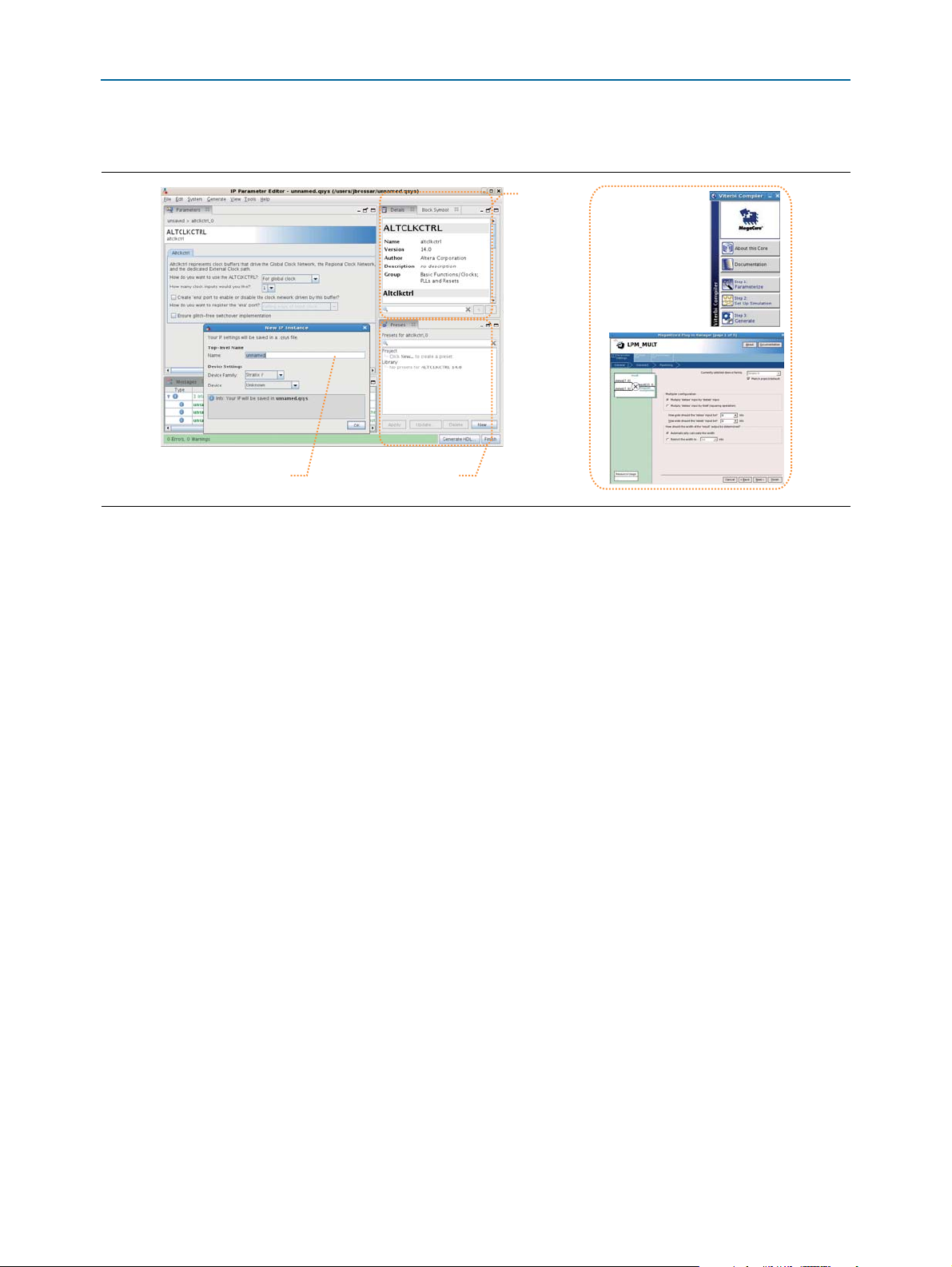

Using the Parameter Editor

The parameter editor helps you to configure your IP variation ports, parameters,

architecture features, and output file generation options:

■ Use preset settings in the parameter editor (where provided) to instantly apply

preset parameter values for specific applications.

■ View port and parameter descriptions and links to detailed documentation.

™

Plug-In Manager in

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 13

Chapter 2: Getting Started 2–3

View IP port

and parameter

details

Apply preset parameters for

specific applications

Specify your IP variation name

and target device

Legacy parameter

editors

Upgrading Outdated IP Cores

■ Generate testbench systems or example designs (where provided).

Figure 2–3. IP Parameter Editors

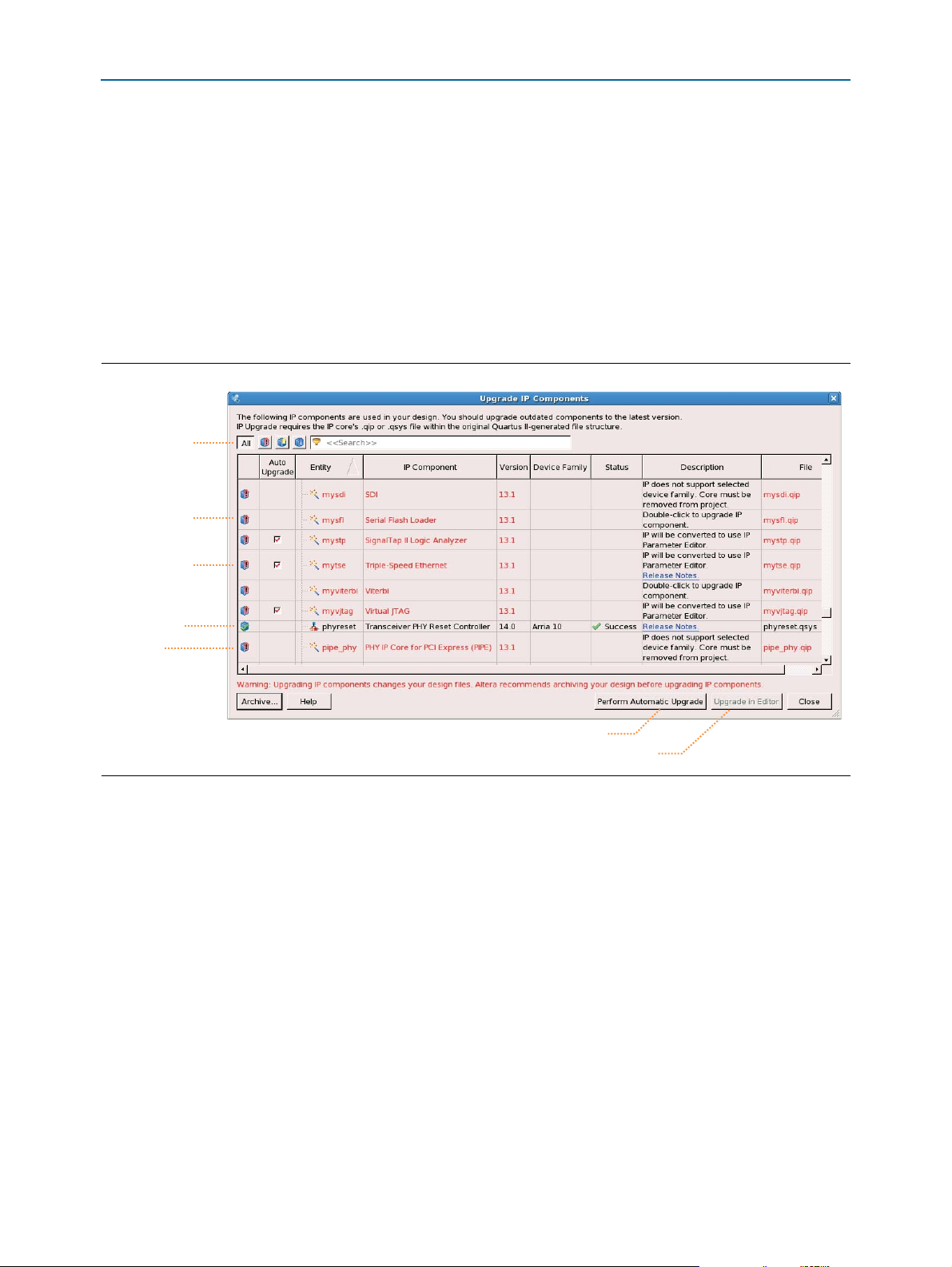

Upgrading Outdated IP Cores

IP cores generated with a previous version of the Quartus II software may require

upgrade before use in the current version of the Quartus II software. Click Project >

Upgrade IP Components to identify and upgrade outdated IP cores.

The Upgrade IP Components dialog box provides instructions when IP upgrade is

required, optional, or unsupported for specific IP cores in your design. Most Altera IP

cores support one-click, automatic simultaneous upgrade. You can individually

migrate IP cores unsupported by auto-upgrade.

The Upgrade IP Components dialog box also reports legacy Altera IP cores that

support compilation-only (without modification), as well as IP cores that do not

support migration. Replace unsupported IP cores in your project with an equivalent

Altera IP core or design logic.Upgrading IP cores changes your original design files.

Before you begin

■ Migrate your Quartus II project containing outdated IP cores to the latest version

of the Quartus II software. In a previous version of the Quartus II software, click

Project > Archive Project to save the project. This archive preserves your original

design source and project files after migration. le paths in the archive must be

relative to the project directory. File paths in the archive must reference the IP

variation .v or .vhd file or .qsys file, not the .qip file.

■ Restore the project in the latest version of the Quartus II software. Click Project >

Restore Archived Project. Click Ok if prompted to change to a supported device

or overwrite the project database.

To upgrade outdated IP cores, follow these steps:

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

1. In the latest version of the Quartus II software, open the Quartus II project

containing an outdated IP core variation.

Page 14

2–4 Chapter 2: Getting Started

Displays upgrade

status for all IP cores

in the Project

Upgrades all IP core that support “Auto Upgrade”

Upgrades individual IP cores unsupported by “Auto Upgrade”

Checked IP cores

support “Auto Upgrade”

Successful

“Auto Upgrade”

Upgrade

unavailable

Double-click to

individually migrate

Upgrading Outdated IP Cores

1 File paths in a restored project archive must be relative to the project

directory and you must reference the IP variation .v or .vhd file or .qsys file,

not the .qip file.

2. Click Project > Upgrade IP Components. The Upgrade IP Components dialog

box displays all outdated IP cores in your project, along with basic instructions for

upgrading each core.

3. To simultaneously upgrade all IP cores that support automatic upgrade, click

Perform Automatic Upgrade. The IP cores upgrade to the latest version. The

Status and Ve rs i on columns reflect the update.

Figure 2–4. Upgrading IP Cores

Upgrading IP Cores at the Command Line

Alternatively, you can upgrade IP cores at the command line. To upgrade a single IP

core, type the following command:

quartus_sh --ip_upgrade -variation_files <my_ip_path> <project>

To upgrade a list of IP cores, type the following command:

quartus_sh --ip_upgrade -variation_files

"<my_ip>.qsys;<my_ip>.<hdl>; <project>"

1 IP cores older than Quartus II software version 12.0 do not support upgrade. Altera

verifies that the current version of the Quartus II software compiles the previous

version of each IP core. The MegaCore IP Library Release Notes reports any verification

exceptions for MegaCore IP. The Quartus II Software and Device Support Release Notes

reports any verification exceptions for other IP cores. Altera does not verify

compilation for IP cores older than the previous two releases.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 15

Chapter 2: Getting Started 2–5

Specify Parameters

Specify Parameters

To specify the parameters, follow these steps:

1. In the Quartus II software, create a new Quartus II project with the New Project

Wizard.

2. In the IP Catalog (Tools > IP Catalog), locate and double-click the POSPHY4 IP

core. The parameter editor appears.

3. Click Step 1: Parameterize.

4. Determine your design’s constraints and performance requirements and then

parameterize the POS-PHY Level 4 IP core in the parameter editor.

1 Not all parameters are supported by, or are relevant for, every IP core variation.

5. Click Step 2: Set Up Simulation.

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL

model produced by the Quartus II software.

c You may only use these simulation model output files for simulation purposes and

expressly not for synthesis or any other purposes. Using these models for synthesis

creates a nonfunctional design.

6. Turn on Generate Simulation Model.

7. Choose the language in the Language list.

8. Some third-party synthesis tools can use a netlist that contains only the structure

of the IP core, but not detailed logic, to optimize performance of the design that

contains the IP core. If your synthesis tool supports this feature, turn on Generate

netlist.

9. Click OK.

10. Click Step 3: Generate in IP Toolbench.

Tab le 2– 1 describes the generated files and other files that may be in your project

directory. The names and types of files specified in the IP Toolbench report vary

based on whether you created your design with VHDL or Verilog HDL

1 If you want to change your project from a receiver to a transmitter, delete all

the HDL files before you regenerate the IP core.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 16

2–6 Chapter 2: Getting Started

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

<Project Directory>

<your_ip>.html - IP core generation report

<your_ip>_testbench.v or .vhd - Testbench file

1

<your_ip>.bsf - Block symbol schematic file

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist1

<your_ip>_bb - Verilog HDL black box EDA synthesis file

<your_ip>.vo or .vho - IP functional simulation model

2

<your_ip>.qip - Quartus II IP integration file

<your_ip>.v or .vhd - Top-level HDL IP variation definition

<your_ip>_block_period_stim.txt - Testbench simulation data

1

<your_ip>-library - Contains IP subcomponent synthesis libraries

Files Generated for Altera IP Cores (Legacy Parameter Editor)

Files Generated for Altera IP Cores (Legacy Parameter Editor)

The Quartus II software version 14.0 and previous parameter editor generates the

following output file structure for Altera IP cores:

Figure 2–5. IP Core Generated Files (Legacy Parameter Editor)

Table 2–1. Generated Files (Part 1 of 2)

File Description

<variation name>_atlfifo_concat.v

<variation name>_dpa_concat.v

<variation

name>_pl4_rx_core_constraints.tcl

<variation name>_refresh_model.tcl

<variation name>_run_modelsim.tcl

<variation name>_rx_data_proc.ocp An OpenCore Plus file, for time limited or tethered hardware evaluation.

<variation name>_rx_modules.v

<variation

name>_rx_data_phy_altlvds.v

<variation name>_rx_core.v

<

variation name>_syn.v or

<

variation name>_syn.vhd

<variation name>_tb.v A Verilog HDL testbench for the requested parameterization.

<variation name>.bsf

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

An encrypted HDL file for Quartus II synthesis. This file is automatically added

to your Quartus II project. You should not modify this file.

A generated HDL file for Quartus II synthesis. This file is automatically added to

your Quartus II project. You should not modify this file.

Constraint settings file for Quartus II synthesis. Use this file to specify

constraints required to achieve performance requirements.

A Tcl script that regenerates the IP functional simulation model, in both Verilog

HDL (.vo) and VHDL (.vho) formats.

A Tcl script that automates the process of running the testbench with the IP

functional simulation model.

An encrypted HDL file for Quartus II synthesis. This file is automatically added

to your Quartus II project. You should not modify this file.

A generated HDL file for Quartus II synthesis. This file is automatically added to

your Quartus II project. You should not modify this file.

A generated HDL file for Quartus II synthesis. This file is automatically added to

your Quartus II project. You should not modify this file.

A timing and resource netlist for use in some third-party synthesis tools.

Quartus II symbol file for the IP core variation. You can use this file in the

Quartus II block diagram editor.

Page 17

Chapter 2: Getting Started 2–7

Simulate the Design

Table 2–1. Generated Files (Part 2 of 2)

File Description

<variation name>.html The IP core report file.

XML file that describes the IP core pin attributes to the Quartus II Pin Planner. IP

<variation name>.ppf

<variation name>.sdc

<variation name>.v or .vhd

<variation_name>.vo or .vho Verilog HDL IP functional simulation model.

core pin attributes include pin direction, location, I/O standard assignments, and

drive strength.

TimeQuest SDC constraint settings file for timing analysis. Use this file to

specify constraints required for TimeQuest analysis.

A IP core variation file, which defines a Verilog HDL top-level description of the

custom IP core. Instantiate the entity defined by this file inside of your design.

Include this file when compiling your design in the Quartus II software.

1. After you review the generation report, click Exit to close the parameter editor.

The custom IP core variation is integrated into your design. You are now ready to

simulate and compile.

Simulate the Design

You can simulate your design using the VHDL and Verilog HDL IP functional

simulation models.

f For more information on IP functional simulation models, including NativeLink, refer

to “Simulate the Design” on page 2–7 and the Simulating Altera IP in Third-Party

Simulation Tools chapter in volume 3 of the Quartus II Handbook.

Altera provides models you can use for functional verification of the POS-PHY Level

4 IP core within your design. A Verilog HDL testbench, including scripts to run it, is

also provided. This testbench, for use with the ModelSim-Altera simulator or other

simulator tools via NativeLink, demonstrates how to instantiate a model in a design.

This section tells you how to use the testbench with the ModelSim simulator or with

other simulators via NativeLink.

f For a list of the simulators that you can use with NativeLink, refer to the Simulating

Altera IP in Third-Party Simulation Tools chapter in volume 3 of the Quartus II Handbook.

c The testbench is in Verilog HDL, so you require a license to run mixed language

simulations to run the testbench with the VHDL model. If you edit any of your

variation’s clear-text Verilog HDL files, you must update the IP functional simulation

model before running the simulator. To update the model, run the quartus_sh -t

<variation_name>_refresh_model.tcl script in the Quartus II software.

Use the Testbench with the ModelSim Simulator

To use the testbench with IP functional simulation models in the ModelSim simulator,

follow these steps:

1. Start the ModelSim simulator.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 18

2–8 Chapter 2: Getting Started

Simulate the Design

2. In the simulator, change the working directory to the location of the

<variation_name>_run_modelsim.tcl file.

3. To run the script type the following command at the simulator command prompt:

source <variation_name>_run_modelsim.tcl

Use the Testbench with NativeLink

To use the testbench with third-party IP functional simulation models using

NativeLink, follow these steps:

1. Create a new custom variation in your Quartus II project. Generate your IP core

for this variation using the parameter editor.

2. Check that the absolute path to your third-party simulation tool is set. Set the path

by clicking Tools > Options > EDA Tool Options.

3. Click Processing > Start > Start Analysis & Elaboration.

1 If the analysis and elaboration is not successful, fix the error before moving

to the next step.

4. Click Assignments > Settings. The Settings dialog box appears. Expand EDA

Tool Settings and select Simulation.

5. In Too l n a m e, select a simulator tool from the list.

6. In EDA Netlist Writer options, select VHDL from the list for Format for output

netlist.

7. In NativeLink settings, select the Compile test bench option and then click Te s t

Benches. The Test Benches dialog box appears.

8. In the Tes t B e n ch es dialog box, click New. The New Test Bench Settings dialog

box appears.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 19

Chapter 2: Getting Started 2–9

Compile the Design and Program a Device

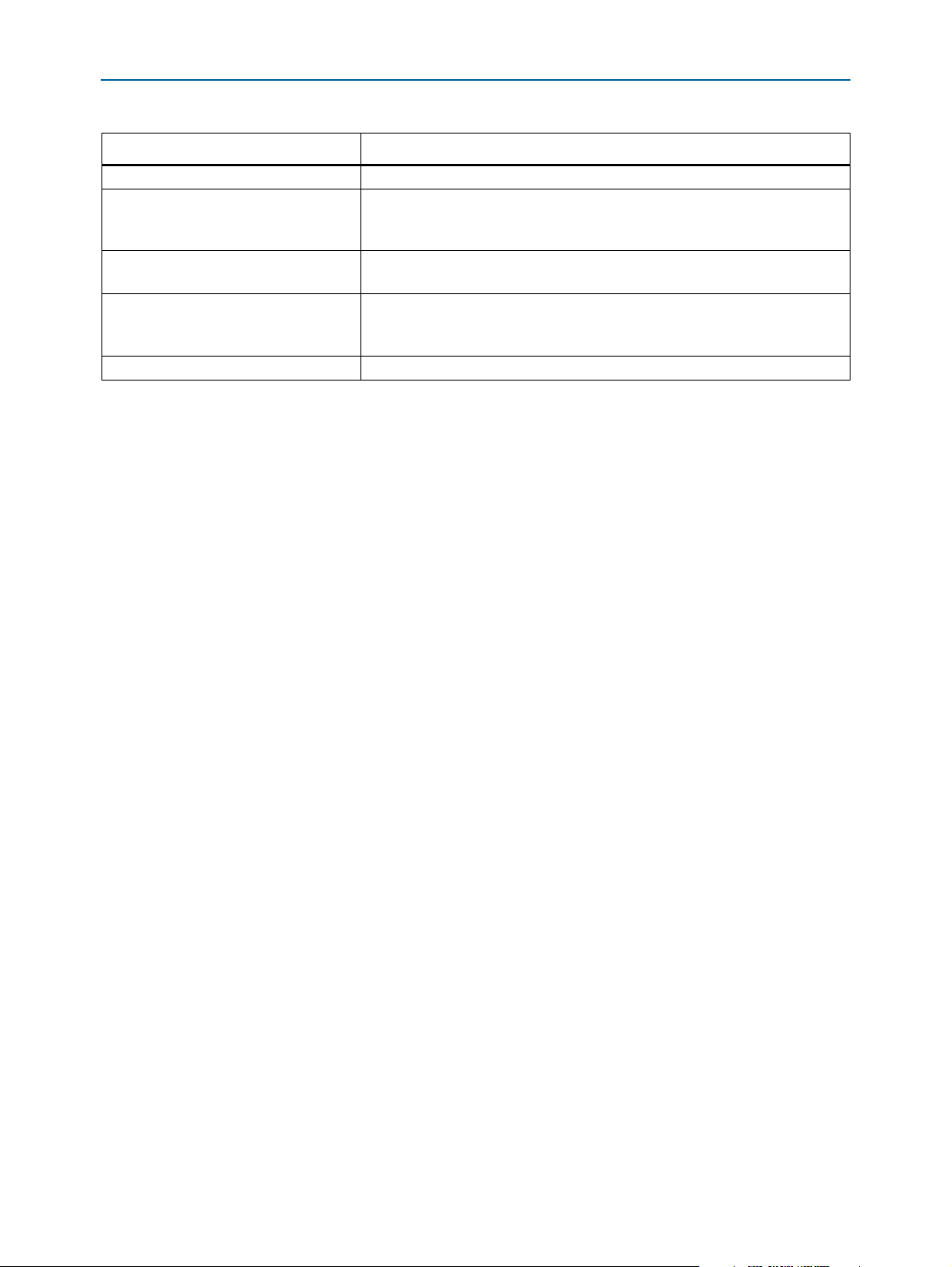

9. In the New Test Bench Settings dialog box, enter the information described in

Table 2–2 on page 2–9 (refer also to Figure 2–6 on page 2–9). To enter the files

described in the table, browse to the files in your project.

Table 2–2. NativeLink Test Bench Settings

Parameter Setting and File Name

Test bench name <any name>

Top-level module in test bench tb

Design instance name in test bench <variation name>

Run for 100 ns

Test bench files <variation name>_tb.v

Figure 2–6 on page 2–9 shows an example of the testbench settings whxen the

<variation_name> is example.

Figure 2–6. Example of New Test Bench Settings for NativeLink

10. When you have entered the required information for your new testbench, click OK

in the New Test Bench Settings dialog box.

11. Click OK in the Test Benches dialog box and then click OK in the Settings dialog

box.

12. Click Tools > EDA Simulation Tool, and then click Run EDA RTL Simulation

Tool. The simulation now begins with your chosen simulation tool.

Compile the Design and Program a Device

You can use the Quartus II software to compile your design. Refer to Quartus II Help

for instructions on compiling your design.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 20

2–10 Chapter 2: Getting Started

Compile the Design and Program a Device

After you have compiled your design, program your targeted Altera device and

verify your design in hardware.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 21

3. Parameter Settings

You customize the POS-PHY Level 4 IP core by specifying parameters using the

parameter editor

c This chapter describes the parameters and how they affect the behavior of the IP core.

Each section corresponds to a tab when you click Parameterize in the parameter

editor.

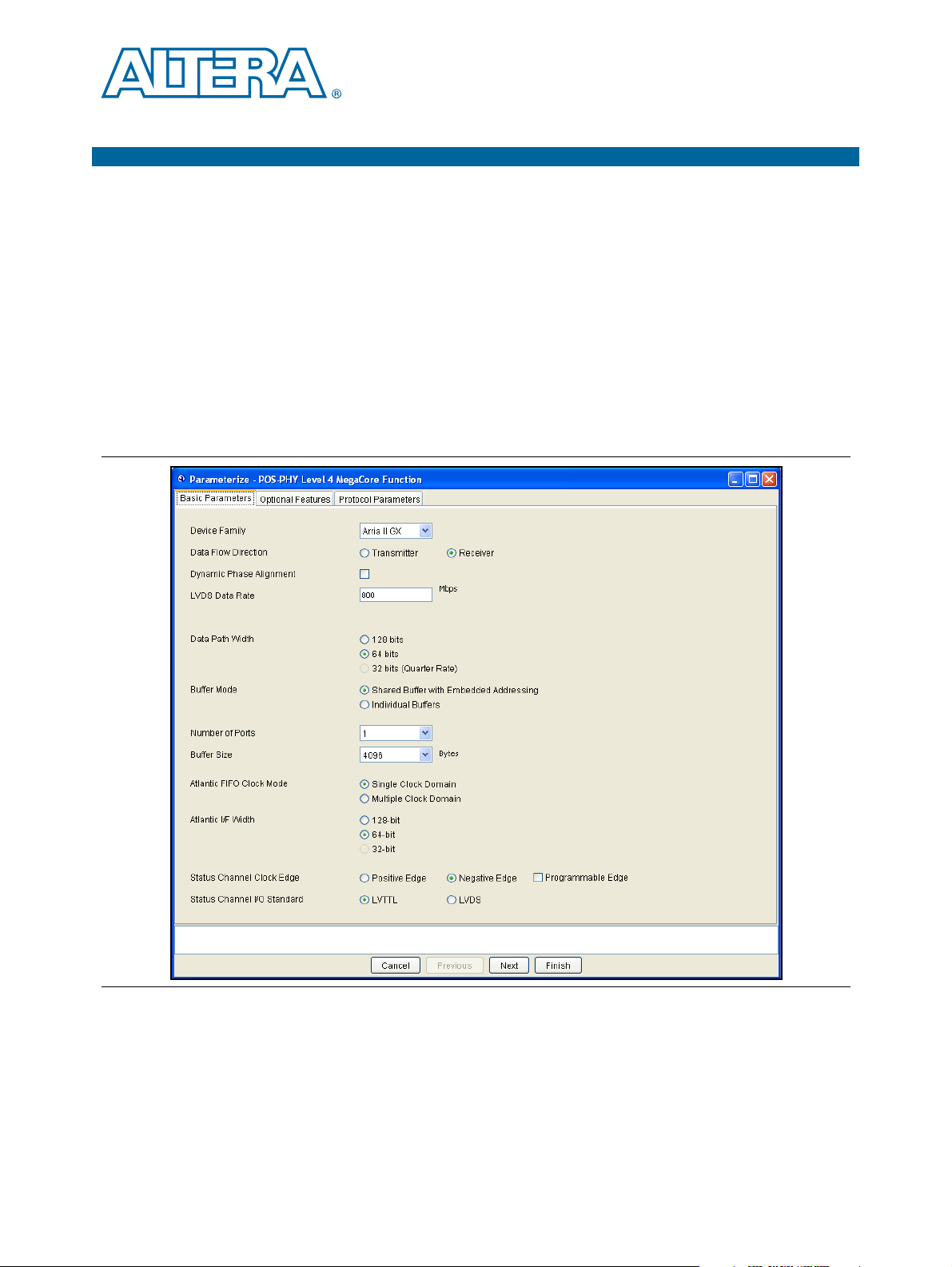

Basic Parameters

Figure 3–1 shows the basic parameters tab.

Figure 3–1. Basic Parameters

in the Quartus®II software.

Device Family

Select the device family. Table 1–3 on page 1–2 shows the device families that the POS-

PHY Level 4 IP core supports.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 22

3–2 Chapter 3: Parameter Settings

Basic Parameters

Tab le 3– 1 shows the maximum LVDS data rates supported by the POS-PHY Level 4 IP

core for each device family.

Table 3–1. Supported LVDS Data Rates

Device Family LVDS Rate (Mbps)

Arria II GX and Arria II GZ 1,000

Cyclone III 622

Cyclone IV 622

Stratix III 1,250

Stratix IV 1,250

Stratix V 1,250

Stratix GX 1,000

The POS-PHY Level 4 IP core operates either as a receiver where data flows from the

SPI-4.2 interface to the Atlantic

™

interface, or as a transmitter where data flows from

the Atlantic interface to the SPI-4.2 interface.

1 The receiver and transmitter variations are separate building blocks in a design, with

no dependency on each other, so you select the parameters independently. For the IP

core to act as a full-duplex, bidirectional transceiver, instantiate one for each direction.

Typical designs may include one or more receivers and one or more transmitters per

FPGA.

1 After you have generated a custom variation, you can re-open the parameter editor

and change the parameters. However, do not change a receiver variation to a

transmitter variation, or a transmitter variation to a receiver variation, otherwise the

Quartus II software generates errors during compilation.

If your receiver design requires dynamic phase alignment (DPA), turn on Dynamic

Phase Alignment.

DPA is recommended for data rates exceeding 622 Mbps, and considered essential for

high-quality signaling above 800 Mbps, or across connectors at 700 Mbps.

DPA is only available in Stratix III, Stratix II, and Stratix GX devices.

f For further information about DPA, refer to “DPA Channel Aligner

(rx_data_phy_dpa)” on page 4–2.

LVDS Data Rate

For a transmitter, the LVDS d ata r ate specifies the data rate out of the FPGA, on each

LVD S pai r.

IP Toolbench uses this parameter to instantiate and configure the ALTLVDS IP core

that includes the fast PLL. For example, to configure a transmitter with a data rate of

700 Mbps on the

This rate corresponds to a 350 MHz DDR clock on

For a receiver, the LVDS data rate specifies the data rate into the FPGA, on each LVDS

pair, and sets the phase-locked loop (PLL) clock rate.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

tdat

line, enter

700

in the LVDS Data Rate field of IP Toolbench.

tdclk

.

Page 23

Chapter 3: Parameter Settings 3–3

Basic Parameters

IP Toolbench uses the LVDS data rate to instantiate and parameterize the ALTLVDS

IP core that includes the fast PLL. For example, for a receiver with a data rate of

700 Mbps on each

350 MHz double-data rate (DDR) clock on

rdat

line, enter

700

in LVDS data rate. This value corresponds to a

rdclk

.

PLL Input Frequency

For a transmitter only, you can enter the PLL input frequency. To enter the PLL

frequency, you must click Import PLL Frequency, to open the ALTLVDS wizard and

view the available input PLL frequencies.

1 When you change the data path width, the PLL input frequency changes.

1 Do not type the PLL frequency into the box.

Data Path Width

The Data path width affects two important aspects of the IP core: size and

performance. The IP core offers the following options:

■ 128 bits running at a frequency of 1/8 the LVDS data rate

■ 64 bits running at 1/4 the LVDS data rate

■ 32 bits (quarter rate) running at 1/2 the LVDS data rate (for non-standard

applications at a maximum of 250 Mbps)

f For approximate resource usage and performance of example POS-PHY Level 4

variations, refer to “Performance and Resource Utilization” on page 1–5.

Buffer Mode

The POS-PHY Level 4 IP core supports the following two buffer modes:

■ Shared buffer with embedded addressing

■ Individual buffers

With Shared buffer with embedded addressing, all ports share a single Atlantic

buffer with an 8-bit address field that supports up to 256 ports. The data is read from

the Atlantic buffer in the same order as it is received. The shared buffer with

embedded addressing mode is smaller than the individual buffers mode, and allows

you to develop your own buffering and status generation implementation.

With Individual buffers, the POS-PHY Level 4 IP core provides an Atlantic first-in

first-out (FIFO) buffer for each port. Therefore, there are as many Atlantic FIFO

buffers of the same depth and width—each with a unique Atlantic interface on the

user end—as the number of ports that you select. The individual buffers supports up

to 16 ports.

1 Timing and routing difficulties may occur when using 16 ports for 128 bit variations;

thus a maximum of 10 ports is recommended for 128-bit variations.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 24

3–4 Chapter 3: Parameter Settings

Basic Parameters

For transmitters for individual buffers variations, a credit-based scheduler is

provided. This scheduler decodes the incoming status channel and decides from

which FIFO buffer (port) to transmit.

The individual buffers for transmitters offer the following advantages:

■ A simple user interface

■ Full scheduler

■ No head-of-line blocking

■ Per-port backpressure

f For further information on individual buffers for transmitters, refer to “Individual

Buffers” on page 5–3.

For receivers, the individual buffers offer the following advantages:

■ A simple user interface

■ No head-of-line blocking

■ The POS-PHY Level 4 IP core handles all of the backpressure automatically

f For further information on individual buffers for receivers, refer to “Individual

Buffers” on page 4–6.

The SPI-4.2 protocol supports from 1 to 256 ports. When you select the number of

ports, you determine the mode of operation. Single-PHY operation for one port; or

multi-PHY for two to 256 ports. For example, when interfacing to a 10-channel Gbit

Ethernet MAC device the number of ports is 10.

When you use the shared buffer with embedded addressing, the Number of ports

determines the number of port addresses supported by the POS-PHY Level 4 protocol

portion of the IP core, such as the status generator and error checker. Port addresses 0

to 255 can always be sent and received when using Shared buffer with embedded

addressing.

For the shared buffer with embedded addressing, the Buffer size defines the size of

the shared embedded address buffer. For the individual buffers, the Buffer size

defines the size of each buffer. The POS-PHY Level 4 IP core supports the following

sizes (per buffer):

■ 512 bytes

■ 1,024 bytes

■ 2,048 bytes

■ 4,096 bytes

■ 8,192 bytes

■ 16,384 bytes

■ 32,768 bytes

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 25

Chapter 3: Parameter Settings 3–5

Basic Parameters

Atlantic FIFO Buffer Clock

The Atlantic FIFO buffer clock sets the clock mode for the Atlantic FIFO buffers. Two

choices are available: Single or Multiple.

With a single Atlantic FIFO buffer clock, the Atlantic FIFO buffers are instantiated as

single clock domain buffers that do not include any clock crossing logic and therefore

consume fewer logic resources.

With a multiple Atlantic FIFO buffer clocks, the Atlantic FIFO buffers are instantiated

as multiple clock domain buffers. Each buffer has two independently operated clock

inputs, thus each Atlantic interface has a separate clock input. Multiple Atlantic FIFO

buffer clocks consume more logic resources.

Atlantic Interface Width

The Atlantic interface width includes 32, 64, or 128 bits, and depends on the internal

data path width. Tab le 3– 2 shows the Atlantic data widths supported for each internal

data path width.

1 For the individual buffers mode, all buffers have the same data path width.

Table 3–2. Atlantic Interface Data Width Limitations

Internal Data Path Width (Bits) Supported Atlantic Data Width (Bits)

128 128

64 64 and 128

32 32 and 64

The Status channel clock edge determines on which clock edge—positive (rising),

negative (falling), or programmable—the 2-bit status channel is transmitted (by the

receiver IP core) in reference to the

tsclk

(for the transmitter) or

rsclk

(for the

receiver) pin. When you turn on Programmable Edge, an input pin,

(

ctl_ts_statedge

for the transmitter;

ctl_rs_statedge

for the receiver), controls the

status channel clocking edge statically at reset.

1 To ensure proper sampling of the status information, you should typically set this

parameter to be the opposite of the sampling clock edge on the adjacent device.

For the Status channel I/O standard, either LVTTL or LV DS , select LVD S to

implement the optional lower bandwidth LVDS status operation (refer to the OIF-

SPI4-02.1 specification).

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 26

3–6 Chapter 3: Parameter Settings

Optional Features

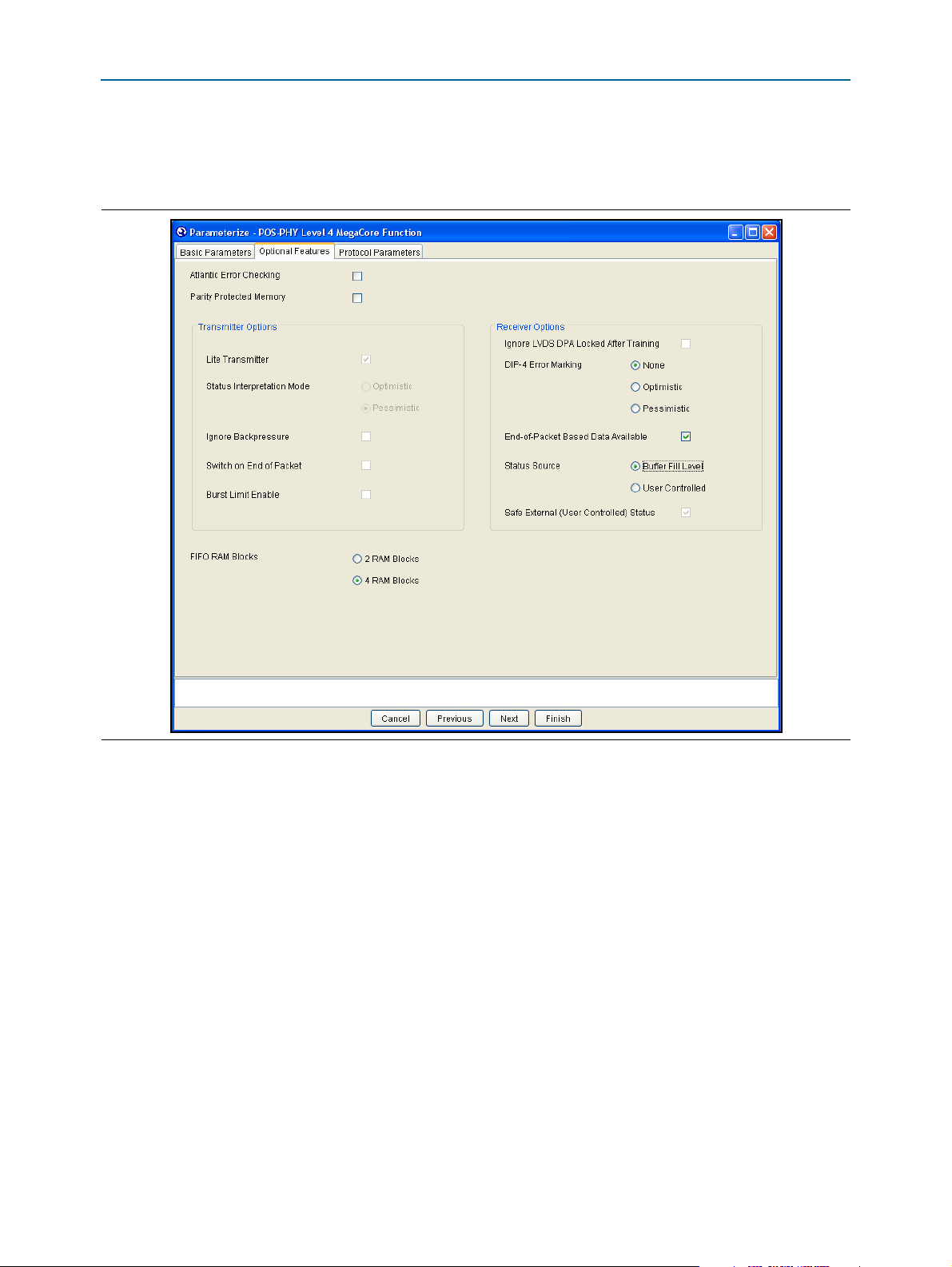

Optional Features

Figure 3–2 on page 3–6 shows the Optional Features tab.

Figure 3–2. Receiver Optional Features

These parameters allow you to enable additional features that the IP core provides.

Each parameter may increase or decrease the number of logic resources.

Turn on Atlantic error checking to add a packet filtering module to the write side of

every Atlantic FIFO buffer. The packet filtering module ensures that only properly

formatted packets are passed through the Atlantic FIFO buffer. When you turn off

Atlantic error checking, the packet filtering module is not added.

The packet filtering module corrects start-of-packet (SOP) and end-of-packet (EOP)

errors before writing packets into the FIFO buffer. For a missing SOP (where data or

an EOP is received for a port without first having received a SOP), an error output is

asserted, and data is not written to the buffer until a SOP is received. For a missing

EOP (where a SOP is received before the previous packet’s EOP), the current packet is

terminated by an EOP, and ERR is asserted. The next packet is stored normally.

For individual buffers variations with a large number of ports, the Atlantic error

checking increases the amount of logic.

Atlantic error checking is often desirable for receivers, but less applicable for

transmitters because the incoming user-Atlantic data may be presumed correct.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 27

Chapter 3: Parameter Settings 3–7

Optional Features

The missing SOP and missing EOP error indicators are always zero if you turn off

Atlantic error checking.

Turn on Parity protected memory to protect all Atlantic FIFO buffers in the IP core by

byte-lane parity. The parity is calculated across every byte of data that is written to

memory in the buffers, and is checked for correctness when it is read. If a parity error

is detected, an error signal is raised. Turn off Parity protected memory, to deactivate

the parity protection.

1 In the receive direction, the parity error signal is 2 clock cycles delayed (compared to

Atlantic FIFO read data). In the transmit direction, the parity error signal is 1 or 2

clock cycles delayed (compared to Atlantic FIFO read data) depending on the

parameters selected.

Transmitter Options

When you turn on Lite transmitter, the transmitter pads packets with

IDLE

characters

to a multiple of 16 bytes for 128-bit variations, or 8 bytes for 64-bit variations.

Although using the lite transmitter feature lowers the effective bandwidth rate on the

SPI-4.2 data bus, it greatly reduces the logic consumption.

When you turn off Lite transmitter, the transmitter packs the packets more tightly

together and pads them with

IDLE

characters to a multiple of 4 bytes. SOP,

continuation of packet (COP) and EOP may be combined into a single control word,

or may be in adjacent control words. Turning off the lite transmitter feature increases

the effective bandwidth rate on the SPI-4.2 data bus, but increases the logic

consumption.

1 COP means no SOP. COP can be pure continuation (control word bits [15:12] =

4'b1000

word bits [15:12] =

, so no SOP and no EOP, but payload follows) or EOP + continuation (control

4'b1xx0

, so end current packet, but continue other packets).

For the transmitter IP core you can select Pessimistic or Optimistic for the Status

interpretation mode.

In the Pessimistic mode, the latest status information is captured and is stored inside

the status processor block until a DIP-2 status is received. If the DIP-2 is valid, the

buffered status is passed on to the scheduler or user logic. If the DIP-2 is invalid, the

scheduler and user logic do not receive an update, and the next incoming status

overwrites the errored buffered status.

In the Optimistic mode, the status information is provided to the user logic and

scheduler through a clock-crossing buffer as it arrives on the status channel. DIP-2

errors cause the

err_ts_dip2

flag to be asserted, but do not affect the status reception.

1 The Pessimistic mode causes the latency in receiving a valid status message to be

calendar multiplier × calendar length

tsclk

cycles longer than the optimistic mode. This

length is significant for systems with large calendar length or large calendar

multiplier values.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 28

3–8 Chapter 3: Parameter Settings

Optional Features

If you turn on Ignore backpressure (only available when you turn on Shared buffer

with embedded addressing), the IP core ignores the backpressure from the receiver

and simply sends data whenever the buffer is not empty. The IP core stops reading

from the buffer only when the status framer is out of synchronization, when a training

pattern is inserted, or when there is not enough data to complete a burst. The user

logic is responsible for using the status outputs from the IP core to schedule data

writes into the buffer appropriately.

If you turn off Ignore backpressure, a simple scheduling algorithm is employed. If

the status received for any port is satisfied, the transmitter stops reading from the

buffer on the next EOP or burst unit size boundary. If all ports are hungry or starving,

the transmitter sends the data in the buffer. So a satisfied status received for one port

prevents transmission for any port, leading to head-of-line blocking.

If you turn on Switch on end-of-packet, the scheduler stops sending from the current

port, and switches ports at the end of burst (that is, when the credits have all been

consumed), as well as when an EOP is sent. If you turn off Switch on end-of-packet,

the scheduler switches ports at the end of the burst (also includes switching when the

buffer is empty).

1 This option applies only to the individual buffers mode, and allows you to

parameterize the port switching capabilities of the transmit scheduler.

f For more information, refer to “Individual Buffers Transmit Scheduler (tx_sched)” on

page 5–3.

Turn on Burst Limit Enable, if you want the transmitter to limit the maximum size of

bursts it sends. Set the maximum burst value with the Burst Limit option (on the

Protocol Parameters tab). At the end of a burst limit a control word is inserted.

Receiver Options

If you turn off Ignore LVDS DPA locked after training, which is only available for

Stratix II devices, a loss of

sends framing, and there is data loss and the possibility of MSOP/EOP errors. If you

turn on Ignore LVDS DPA locked after training, a loss of

trigger stop and framing, and data continues to process normally. You must monitor

the DIP4 error signal to assess if the data is correct or not and trigger a retrain or not.

1 For Stratix III and Stratix IV devices, the

the IP core behaves as if you turned on Ignore LVDS DPA locked after training.

If the signal

stat_rd_lvds_lock

assumes that the lock is lost due to external conditions such as jitter. This signal goes

low if the capture phase of the hardware DPA block changes by two or more phases.

The two phases correspond to a amount that is lower than the accepted threshold for

the SPI4.2 Specification. When the signal goes low, the IP core states it is out of

synchronization and requests a new training sequence.

dpa_lvds_locked

causes the IP core to stop processing data,

dpa_lvds_locked

dpa_lvds_locked

signal never goes low, so

goes low during operation (after training), the IP core

does not

In some cases, it is better to ignore this signal and rely on the error checking

mechanisms or SPI4.2, by checking the DIP4 calculation. You then have to externally

request the retraining and unlock the DPA block.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 29

Chapter 3: Parameter Settings 3–9

Optional Features

It is normal during the normal data transfer in SPI-4.2 that

dpa_locked

signal can

become de-asserted due to some jitter that is still within 0.44 UI of LVDS data. The

DPA has a low pass filter that filters out very high frequency jitter from affecting the

lock signal and phase of

8 jump in one direction),

rx_clk

. If the jitter is detected to be 0.25 UI (two phases out of

dpa_locked

is de-asserted and it is still within 0.44 UI.

The DIP-4 error marking determines how the receiver handles DIP-4 errors. The

receiver uses the following three modes to mark received DIP-4 errors:

■ None—no error marking is performed.

■ Optimistic mode—the receiver IP core marks the preceding and succeeding burst

as errored. If these bursts are payload (that is, if a DIP-4 occurs followed by

IDLE

s),

then only the preceding control word payload is marked as errored. Bursts going

into the Atlantic FIFO buffer are marked with the Atlantic error signal. If a burst is

not an EOP, it is up to the user logic to detect it.

■ Pessimistic mode—the receiver IP core marks all open packets as errored. Packets

going into the Atlantic FIFO buffer are marked with the Atlantic error signal. This

feature increases in resource utilization as the number of ports increases.

End-of-packet-based data available controls the

FIFO buffer. Turn on so the

aN_arxdav

signal is asserted (high) when at least one EOP

is in the buffer, or the fill level is above FIFO threshold low (

the

aN_arxdav

signal is asserted (high) only if the fill level of the FIFO buffer is above

aN_arxdav

signal on the Atlantic

ctl_ax_ftl

). Turn off so

the FIFO threshold low value.

The Status source option applies only to variations using the shared buffer with

embedded addressing mode and provides the following two status channel control

options:

■ Buffer Fill Level—the status for each channel is controlled by the single buffer’s

status. Every calendar time slot contains the result of the almost empty (AE) and

almost full (AF) comparison to the buffer level.

■ User Controlled—to add extra pins, which allows you to directly control the

transmitted buffer status and allows you to send a status irrespective of the fill

level of the internal FIFO buffers, which avoids the situation where the FIFO

buffer is not emptied quickly enough, and if you still request data, the FIFO buffer

overfills.

Turn on Safe External (User Controlled) Status, to ensure the sent status avoids FIFO

buffer overflow (refer to Table 3–3). Turn off Safe External (User Controlled) Status,

to ensure the sent status is always the user status (refer to Table 3–3), irrespective of

buffer fill level.

1 If you turn off Safe External (User Controlled) Status, you can overflow the internal

FIFO buffer.

Table 3–3. User-Controlled Option (Part 1 of 2)

User Status Value FIFO Buffer Status Value Sent Status Value

Starving Starving Starving

Starving Hungry Hungry

Starving Satisfied Satisfied

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 30

3–10 Chapter 3: Parameter Settings

Optional Features

Table 3–3. User-Controlled Option (Part 2 of 2)

User Status Value FIFO Buffer Status Value Sent Status Value

Hungry Starving or Hungry Hungry

Hungry Satisfied Satisfied

Satisfied Any Satisfied

f For more information, refer to “Status Processor” on page 4–7.

FIFO RAM Blocks

The option to select 2 FIFO RAM blocks depends on the parameters you select on the

Basic Parameters tab. These parameters affect the FIFO buffer size and FIFO buffer

width, both of which play a role in memory utilization.

When you select 2 FIFO RAM blocks, the timing performance of the IP core may

decrease (because the memory

4 FIFO RAM blocks). Altera recommends that you do full compilations for both

configurations before deciding which one to choose.

rdata

bus is unregistered, as opposed to registered for

1 Use 2 FIFO RAM block only if it gives an improvement in memory utilization and if

your timing requirements are still met.

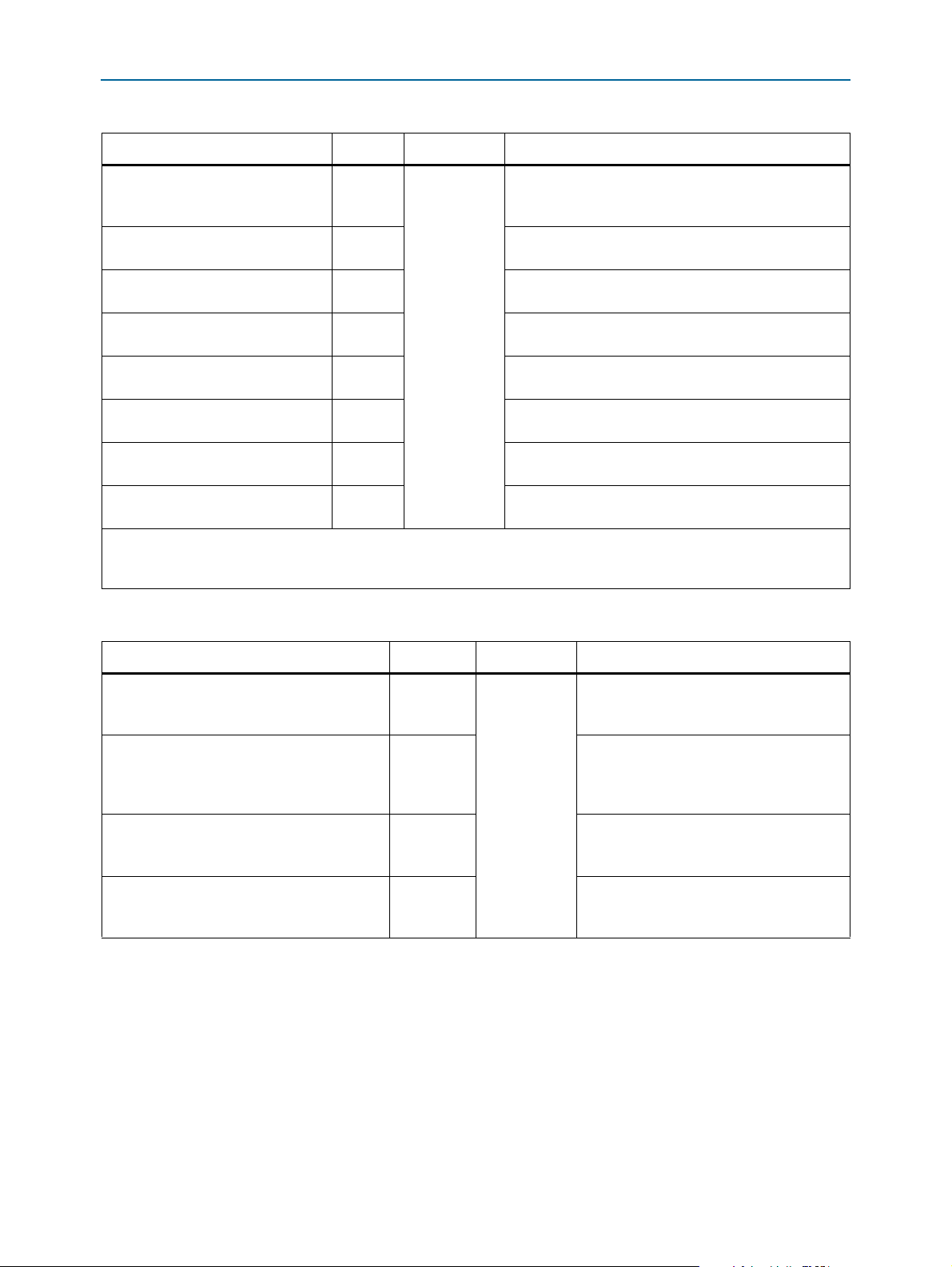

Tab le 3– 3 shows the support for the 2 FIFO RAM block. 4 FIFO RAM block supports

all configuration.

Table 3–4. 2 RAM Block Support

Data Flow

Direction

Receiver Any Any Any — Yes

Transmitter

Buffer Mode Data Path Width

32

Shared Buffer

with Embedded

Addressing

Individual

Buffers

64

128 128 Any No

Any Any Any Yes

Atlantic Interface

Width

32 — No

64 — Yes

64 Any No

128

Lite Transmitter 2 RAM Block Support

Yes Yes

No No

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 31

Chapter 3: Parameter Settings 3–11

Optional Features

Each FIFO RAM block is implemented independently in the available device memory

(for example, with M512, M4K, or M9K blocks) and each device memory has a fixed

number of available configurations. The FIFO RAM block depth for small buffer

configurations (such as 128 × 36 of M4K memory) can be smaller than the minimum

configurable depth of the memory element, meaning that the remainder of the

memory is wasted. By using 2 FIFO RAM blocks instead of 4 you may get better

memory utilization. Figure 3–3 shows the comparison of FIFO RAM blocks.

Figure 3–3. Comparison of FIFO RAM Blocks

4 FIFO RAM Blocks

FIFO Block 0

(size = fifo_size/4)

FIFO Block 1

Write Side

2 FIFO RAM Blocks

(size = fifo_size/4)

FIFO Block 2

(size = fifo_size/4)

FIFO Block 3

(size = fifo_size/4)

Read Side

FIFO Block 0

(size = fifo_size/2)

Write Side

FIFO Block 1

(size = fifo_size/2)

Read Side

Both FIFO buffer width and FIFO buffer size affect memory utilization. The

improvement for a two block FIFO buffer configuration versus a four block FIFO

buffer configuration ranges from half the memory consumption for small buffers, to

the same memory consumption for large buffers.

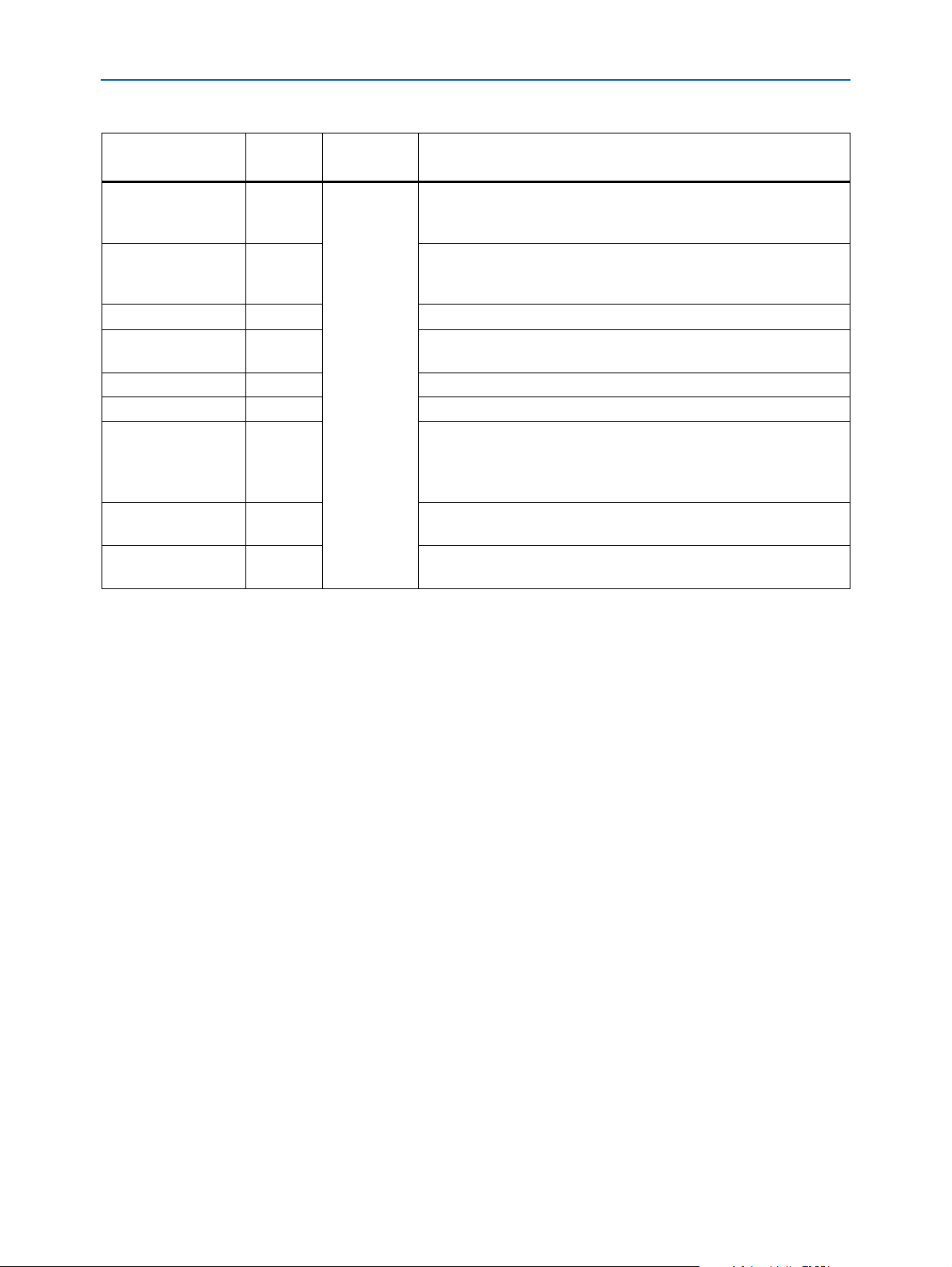

Tab le 3– 5 gives a comparison of the memory utilization for a Stratix II device with 4

FIFO RAM blocks versus 2 FIFO RAM blocks.

Table 3–5. Memory Utilization Comparison (Note 1)

Buffer

Atlantic Interface Width 32 Atlantic Interface Width 64

Size

(bytes)

2 FIFO RAM Blocks 4 FIFO RAM Blocks 2 FIFO RAM Blocks 4 FIFO RAM Blocks

512 4 M4K 4 M4K + 4 M512 4 M4K + 2 M512 8 M4K + 4 M512

1,024 4 M4K 8 M4K 6 M4K 8 M4K + 4 M512

2,048 6 M4K 8 M4K 6 M4K 12 M4K

4,096 12 M4K 12 M4K 10 M4K 12 M4K

8,192 24 M4K 24 M4K 20 M4K 20 M4K

Note to Tab le 3 –5:

(1) Stratix II device, receive (Rx), shared buffer, data path width 32, parity enabled.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 32

3–12 Chapter 3: Parameter Settings

Protocol Parameters

Protocol Parameters

Figure 3–4 on page 3–12 shows the Protocol Parameters tab.

Figure 3–4. Receiver Protocol Parameters

Select Real-Time Programmable, so most of the protocol parameters on this tab

become input pins to the IP core. These input pins allow each parameter to be

connected to a user-implemented register, and controlled at run-time.

Select Fixed Value, to enter values for the protocol parameters on this tab.

IP Toolbench then fixes these values in the IP core, making the parameters static and

the input pins unavailable.

Calendar Options

Turn on Asymmetric Port Support (only available if you select the Real-time

programmable) for the calendar to allow asymmetric weighting of calendar entries to

control the allocation of bandwidth to a given SPI-4.2 port. You must program the

calendar for the IP core to produce the status channel (refer to Appendix E,

Programming the SPI-4.2 Calendar via the Avalon Memory-Mapped Interface).

A port with twice the calendar entries of all other ports nominally uses twice as much

bandwidth on the SPI-4.2 interface depending on the data characteristics. Ports can be

disabled by removing them from the calendar.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 33

Chapter 3: Parameter Settings 3–13

Protocol Parameters

To be effective, the far-end scheduler must handle received status optimistically. As

status is received, credits for each port are topped up to MaxBurst1/MaxBurst2

levels.

Turn on Asymmetric Port Support to instantiate an Avalon

®

Memory-Mapped

(Avalon-MM) interface in the IP core. The Aval on- M M in ter fac e programs the values

of calendar length, calendar multiplier, and the port numbers for each of the calendar

slots.

If you turn on Asymmetric Port Support, the calendar length is programmed from

the Avalon-MM interface (refer to Appendix E).

If you turn on Programmable calendar length, a calendar length input pin is added to

the IP core. This pin allows you to vary the calendar length value from one to the

number of ports without having to recompile. If the programmable calendar length

support parameter is turned off, the calendar length is equal to the number of ports.

The calendar length value cannot be greater than the number of ports (except when

you turn on Asymmetrical Port Support).

The Calendar multiplier determines the number of times the calendar sequence is

repeated before the DIP-2 parity and framing is inserted. Choose a value from 1 to

256.

If the Asymmetric Port Support is turned on, the calendar multiplier value is

programmed via the Avalon-MM interface.

1 The calendar multiplier × calendar length value must be set according to the

instructions in Tab le C–1 o n pag e C– 1 of the “Clock Structure” section, otherwise the

status channel does not operate correctly.

The Maximum calendar length (only available when you turn on Asymmetric Port

Support) defines the maximum number of calendar entries available in the

configurable calendar. Choose a value from 32 to 2,048.

When you turn on Hitless B/W Reprovisioning (only available when you turn on

Asymmetric Port Support), the receiver can transmit a calendar-select word in the

status frame. Active and inactive calendars are tied to the current calendar-select

word in the receiver. When the current calendar-select word changes, the active and

inactive calendars are swapped at the appropriate time, in the following order:

■ The

■ At the beginning of the next status frame, the calendar-select word is toggled.

■ The receiver toggles the used calendar multiplier, calendar length, and calendar to

CALSEL_REQ

register bit is toggled at the receiver (refer to page 4–29).

transmit the next status frame.

■ The transmitter receives the first calendar-select word of the new frame and

detects the toggle.

■ The transmitter toggles the used calendar multiplier, calendar length, and

calendar to interpret the next status frame.

For individual buffers far-end transmitter variations, changing calendars does not

cause the credit table to be flushed, thus a port may not immediately be disabled if it

still has credits. It is up to the user logic to flush the receiver and transmitter buffers

prior to changing the calendar-select word. Otherwise, data may become stranded.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 34

3–14 Chapter 3: Parameter Settings

Protocol Parameters

Each calendar can have independent values for calendar length and calendar

multiplier.

Transmitter Options

The Burst unit size sets the unit size in bytes for burst transfers and controls the

smallest burst transmitted. The valid range for this parameter is from 16 to 1,024

bytes, in 16-byte granularity.

1 The burst unit size multiplier does not limit the maximum burst length, and does not

force control word insertion. Instead, use the Burst limit parameter.

When the data path width is equal to 128 bits and the lite transmitter feature is turned

off, the unit size is 32 bytes, up to 1,024 bytes in 32-byte granularity.

The MaxBurst1 parameter allows you to select the maximum number of credits—

burst unit size to 2,032 bytes—that can be transmitted when the adjacent device’s

FIFO buffer is starving.

The MaxBurst2 parameter allows you to select the maximum number of credits—

burst unit size to 2,032 bytes—that can be transmitted when the adjacent device’s

FIFO buffer is hungry.

The MaxBurst1 and MaxBurst2 parameters do not limit the maximum burst length,

and do not force control word insertion.

The MaxBurst1 and MaxBurst2 parameters are used by the transmit scheduler, thus

they apply only to the individual buffers mode.

1 MaxBurst2 must be less than or equal to MaxBurst1; MaxBurst1 and MaxBurst2 must

be greater than or equal to burst unit size.

f Refer to Figure 3–5 on page 3–16 for the relation of AE and AF.

You c an en ter t he Burst limit only when you turn on Burst Limit Enable. The Burst

limit sets the maximum burst size, in bytes, to be sent by the transmitter, and

guarantees that the transmitter does not send bursts longer than the burst limit (a

control word is inserted at the end of the burst limit). Burst limit values are restricted

to multiples of burst unit size. Depending on other transmitter parameters, the values

may be limited to a minimum value. IP Toolbench only allows valid burst limit

values.

The Maximum training sequence interval (MaxT) allows you to select the interval at

which the training sequence occurs—16 to 65,535 bytes. The training sequence is

scheduled to be inserted after the MaxT counter expires, but is not actually inserted

until the burst that is sent is complete. Therefore, the time between training pattern

insertions is no less than the value of the MaxT parameter, and no more than the value

of the MaxT parameter plus the burst unit size.

If MaxT = 0, periodic training patterns are disabled. If the transmitter status framer is

out of synchronization, the transmitter sends continuous training patterns regardless

of the MaxT

(

tdclk

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

parameter. Training patterns always begin on the rising edge of the clock

).

Page 35

Chapter 3: Parameter Settings 3–15

Protocol Parameters

For the Training pattern repetition value, the training sequence includes one

word, plus

ALPHA(

a) × 20 training words.

ALPHA

is a user-selectable option (0 to 255).

IDLE

Zero (0) is equal to 256 training pattern repetitions.

The training sequence includes one

words are separated into ten consecutive

followed by ten consecutive

tdat

IDLE

control word, plus a × 20 words. The twenty

words of

tdat

words of

16’hF000

16’h0FFF

with

tctl

of

with

1’b0

tctl

.

of

1’b1

,

For the Status sync good and Status sync bad threshold values, two 4-bit inputs,

good_level (ctl_ts_sync_good_theshold)

(

ctl_ts_sync_bad_theshold

The

stat_ts_sync

signal is asserted high when a

), are associated with the

status frames are received without frame or DIP-2 errors. The

deasserted when a

bad_level

number of DIP-2 errors or frame errors have been

and

bad_level

stat_ts_sync

good_level

signal.

number of consecutive

stat_ts_sync

signal is

received since the last error-free frame.

The FIFO buffer threshold high (FTH) for transmitter variations controls when the

aN_atxdav

aN_atxdav

signal is asserted and deasserted for the write side of the FIFO buffer. The

signal indicates when there is room available to write new data into the

FIFO buffer, and is asserted whenever the remaining space in the buffer is greater than

the FTH value.

This threshold is defined in terms of bytes, with a valid range from N to buffer size

bytes, in N-byte increments, where:

■ N = 4 or 8 bytes for 32-bit data path variations

■ N = 8 or 16 bytes for 64-bit data path variations

■ N = 16 or 32 bytes for 128-bit data path variations

The N-byte values depend on the Atlantic interface width and on the Lite transmitter

setting. Ta bl e 3 –6 shows the N-byte values, based on the transmitter's settings.

Table 3–6. N-Byte Values

Datapath Width

32

64

128 128

Atlantic Interface

Width

32 — 4

64 — 8

64

128 On or off 16

Lite Transmitter

On 8

Off 16

On 16

Off 32

N Bytes (FTH

Increment)

1 Although the parameter editor allows you to set FTH values as low as one FIFO

buffer element (translated to bytes), a minimum FTH value is used internally. And,

depending on the core's configuration, up to four FIFO buffer locations are unusable.

For the exact minimum FTH value and number of unusable locations, refer to the

parameter editor message that appears while configuring the core.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 36

3–16 Chapter 3: Parameter Settings

AE AF

Starving Hungry Satisfied

Lmax + ε

Lmax + MaxBurst1+ ε

Lmax + MaxBurst2+ ε

(Empty) (Full)

Protocol Parameters

Receiver Options

The Almost empty (AE) and Almost full (AF) thresholds segregate the receiver FIFO

buffer into three states, depending on the fill levels: starving, hungry, and satisfied.

The SPI-4 Phase 2 specification defines two-bit status values for starving, hungry, and

satisfied. These two-bit values are based on the available space in the FIFO buffer and

on the AE and AF parameter settings:

■ Starving—when the number of elements in the FIFO buffer is less than, or equal to,

the AE threshold

■ Hungry—when the number of elements in the FIFO buffer is between the AE

threshold and the AF threshold

■ Satisfied—when the number of elements in the FIFO buffer is greater than the AF

threshold

The starving, hungry, and satisfied conditions are reported to the adjacent transmitter

on the

rstat

bus, which operates at up to ¼ of the

rdclk

frequency.

These thresholds are defined in terms of bytes, with a valid range from zero to

size

.

1 AE must be lower than or equal to AF.

Figure 3–5 illustrates the relationship between the AE and AF thresholds and the

MaxBurst1 and MaxBurst2 values.

Figure 3–5. FIFO Buffer Thresholds

Notes to Figure 3–5:

(1) L

corresponds to the worst-case response time from sending a status update over the FIFO status channel until

MAX

observing the reaction to that update on the corresponding data path.

corresponds to the difference between the granted credit and the actual data transfer length. This difference arises

(2)

from various protocol overheads.

(3) The MaxBurst1 and MaxBurst2 values are defined by the adjacent device’s transmitter. Determining the optimal

MaxBurst1 and MaxBurst2 values is application-specific, and requires an analysis of the data flows, beyond the

scope of this user guide.

buffer

The FIFO buffer threshold low (FTL) value for receiver variations controls when the

aN_arxdav

signal is asserted for the read side of the FIFO buffer. If the fill level of the

buffer is higher than the FTL value, the

there is a burst of data available.

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

1 There is no requirement to wait for the

from the buffer at any time.

aN_arxdav

aN_arxdav

signal is asserted indicating that

signal to be asserted, you can read

Page 37

Chapter 3: Parameter Settings 3–17

Protocol Parameters

1 FTL must be greater than zero.

This threshold is defined in terms of bytes, with a valid range from: N to

buffer size

in increments of N bytes, where:

■ N = 4 or 8 bytes for 32-bit data path variations

■ N = 8 or 16 bytes for 64-bit data path variations

■ N = 16 bytes for 128-bit data path variations

The N-byte values for the 32-bit and 64-bit variations depend on the Atlantic interface

width. If the Atlantic interface width is greater than the data path width, the larger

value for N is used.

For the DIP-4 good and DIP-4 bad threshold values, two 4-bit inputs are associated

with the DIP-4 OOS state machine:

bad_level (ctl_rd_dip4_bad_threshold

If the

stat_rd_dip4_oos

signal is high, and all of the DIP-4s in the control words

good_level (ctl_rd_dip4_good_threshold

).

) and

received in the current clock cycle (up to 8 in 128-bit mode) are good, the good counter

is incremented by 1; otherwise it is reset to 0. If the good counter reaches the

good_level

threshold, the

stat_rd_dip4_oos

flag is cleared. A

good_level

of 0 is

invalid.

If the

stat_rd_dip4_oos

signal is low, and all of the DIP-4s in the control words

received in the current clock cycle (up to 8 in 128-bit mode) are errored, the bad

counter is incremented by 1; otherwise it is reset to 0. If the bad counter reaches the

bad_level

threshold, the

stat_rd_dip4_oos

flag is asserted. A

bad_level

of 0 is

invalid.

,

1 The receiver may need to receive more control word DIP-4 errors than the DIP-4 bad

threshold parameter set in the wizard, for

stat_rd_dip4_oos

to go high.

f For more information, refer to “DIP-4 Marking” on page 4–16 and “DIP-4 Out of

Service Indication” on page 4–17.

December 2014 Altera Corporation POS-PHY Level 4 IP Core User Guide

Page 38

3–18 Chapter 3: Parameter Settings

Protocol Parameters

POS-PHY Level 4 IP Core User Guide December 2014 Altera Corporation

Page 39

4. Functional Description—Receiver

Data Receiver

And

Serial-to-Parallel

Converter

DPA Channel

Aligner

Status PHY Status FSM

Status

Register

Status Hold

Status

Calculator

Data

Processor

Atlantic

Buffer 0

Atlantic

Interface 0

SPI4.2

Interface

rdclk

rxsys_clk

rdint_clk

rav_clk

rsclk

Atlantic

Buffer N

Atlantic

Interface N

The POS-PHY Level 4 IP core consists of the main SPI-4.2 processing logic, and

configurable Atlantic

core is configured as a receiver, data flows from the SPI-4 interface to the Atlantic

interface.

Features

■ Accepts packets from a SPI-4.2 transmitter

■ Processes control words

■ Detects diagonal interleaved parity (DIP-4) errors

■ Detects SPI-4.2 protocol errors