Page 1

MAX 10 Clocking and PLL User Guide

Subscribe

Send Feedback

UG-M10CLKPLL

2015.05.04

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

Contents

MAX 10 Clocking and PLL Overview................................................................. 1-1

MAX 10 Clocking and PLL Architecture and Features......................................2-1

Clock Networks Overview..........................................................................................................................1-1

Internal Oscillator Overview......................................................................................................................1-1

PLLs Overview..............................................................................................................................................1-1

Clock Networks Architecture and Features.............................................................................................2-1

Global Clock Networks................................................................................................................... 2-1

Clock Pins Introduction..................................................................................................................2-1

Clock Resources............................................................................................................................... 2-2

Global Clock Network Sources...................................................................................................... 2-2

Global Clock Control Block............................................................................................................2-4

Global Clock Network Power Down.............................................................................................2-6

Clock Enable Signals........................................................................................................................2-7

Internal Oscillator Architecture and Features.........................................................................................2-8

PLLs Architecture and Features.................................................................................................................2-8

PLL Architecture..............................................................................................................................2-8

PLL Features................................................................................................................................... 2-10

PLL Locations.................................................................................................................................2-10

Clock Pin to PLL Connections.....................................................................................................2-12

PLL Counter to GCLK Connections...........................................................................................2-12

PLL Control Signals.......................................................................................................................2-13

Clock Feedback Modes..................................................................................................................2-14

PLL External Clock Output..........................................................................................................2-17

ADC Clock Input from PLL.........................................................................................................2-19

Spread-Spectrum Clocking...........................................................................................................2-19

PLL Programmable Parameters...................................................................................................2-19

Clock Switchover........................................................................................................................... 2-22

PLL Cascading................................................................................................................................2-26

PLL Reconfiguration..................................................................................................................... 2-26

MAX 10 Clocking and PLL Design Considerations........................................... 3-1

Altera Corporation

Clock Networks Design Considerations...................................................................................................3-1

Guideline: Clock Enable Signals.................................................................................................... 3-1

Guideline: Connectivity Restrictions............................................................................................ 3-1

Internal Oscillator Design Considerations...............................................................................................3-2

Guideline: Connectivity Restrictions............................................................................................ 3-2

PLLs Design Considerations...................................................................................................................... 3-2

Guideline: PLL Control Signals......................................................................................................3-2

Guideline: Self-Reset........................................................................................................................3-2

Guideline: Output Clocks............................................................................................................... 3-2

Page 3

TOC-3

Guideline: PLL Cascading...............................................................................................................3-3

Guideline: Clock Switchover..........................................................................................................3-3

Guideline: .mif Streaming in PLL Reconfiguration.....................................................................3-4

Guideline: scandone Signal for PLL Reconfiguration.................................................................3-4

MAX 10 Clocking and PLL Implementation Guides......................................... 4-1

ALTCLKCTRL IP Core...............................................................................................................................4-1

IP Catalog and Parameter Editor...................................................................................................4-1

Specifying IP Core Parameters and Options................................................................................4-2

Files Generated for Altera IP Cores (Legacy Parameter Editor)............................................... 4-4

ALTPLL IP Core.......................................................................................................................................... 4-5

IP Catalog and Parameter Editor...................................................................................................4-6

Specifying IP Core Parameters and Options................................................................................4-7

Files Generated for Altera IP Cores (Legacy Parameter Editor).............................................4-17

ALTPLL_RECONFIG IP Core.................................................................................................................4-18

IP Catalog and Parameter Editor.................................................................................................4-18

Specifying IP Core Parameters and Options..............................................................................4-19

Files Generated for Altera IP Cores (Legacy Parameter Editor).............................................4-20

Obtaining the Resource Utilization Report................................................................................4-21

Internal Oscillator IP Core....................................................................................................................... 4-21

IP Catalog and Parameter Editor.................................................................................................4-22

Specifying IP Core Parameters and Options..............................................................................4-23

Files Generated for Altera IP Cores (Legacy Parameter Editor).............................................4-24

ALTCLKCTRL IP Core References.....................................................................5-1

ALTCLKCTRL Parameters.........................................................................................................................5-1

ALTCLKCTRL Ports and Signals..............................................................................................................5-2

ALTPLL IP Core References............................................................................... 6-1

ALTPLL Parameters.................................................................................................................................... 6-1

Operation Modes Parameter Settings........................................................................................... 6-1

PLL Control Signals Parameter Settings.......................................................................................6-2

Programmable Bandwidth Parameter Settings............................................................................6-2

Clock Switchover Parameter Settings........................................................................................... 6-3

PLL Dynamic Reconfiguration Parameter Settings.................................................................... 6-4

Dynamic Phase Configuration Parameter Settings.....................................................................6-4

Output Clocks Parameter Settings.................................................................................................6-5

ALTPLL Ports and Signals..........................................................................................................................6-6

ALTPLL_RECONFIG IP Core References......................................................... 7-1

ALTPLL_RECONFIG Parameters............................................................................................................ 7-1

ALTPLL_RECONFIG Ports and Signals..................................................................................................7-2

ALTPLL_RECONFIG Counter Settings...................................................................................................7-7

Internal Oscillator IP Core References...............................................................8-1

Altera Corporation

Page 4

TOC-4

Internal Oscillator Parameters...................................................................................................................8-1

Internal Oscillator Ports and Signals.........................................................................................................8-1

Additonal Information for MAX 10 Clocking and PLL User Guide................ A-1

Document Revision History for MAX 10 Clocking and PLL User Guide..........................................A-1

Altera Corporation

Page 5

2015.05.04

www.altera.com

101 Innovation Drive, San Jose, CA 95134

MAX 10 Clocking and PLL Overview

1

UG-M10CLKPLL

Subscribe

Clock Networks Overview

MAX® 10 devices support global clock (GCLK) networks.

Clock networks provide clock sources for the core. You can use clock networks in high fan-out global

signal network such as reset and clear.

Internal Oscillator Overview

MAX 10 devices offer built-in internal oscillator up to 116 MHz.

You can enable or disable the internal oscillator.

PLLs Overview

Phase-locked loops (PLLs) provide robust clock management and synthesis for device clock management,

external system clock management, and I/O interface clocking.

You can use the PLLs as follows:

Send Feedback

• Zero-delay buffer

• Jitter attenuator

• Low-skew fan-out buffer

• Frequency synthesizer

• Reduce the number of oscillators required on the board

• Reduce the clock pins used in the device by synthesizing multiple clock frequencies from a single

reference clock source

• On-chip clock de-skew

• Dynamic phase shift

• Counters reconfiguration

• Bandwidth reconfiguration

• Programmable output duty cycle

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 6

1-2

PLLs Overview

• PLL cascading

• Reference clock switchover

• Drive the analog-to-digital converter (ADC) clock

UG-M10CLKPLL

2015.05.04

Altera Corporation

MAX 10 Clocking and PLL Overview

Send Feedback

Page 7

MAX 10 Clocking and PLL Architecture and

www.altera.com

101 Innovation Drive, San Jose, CA 95134

2015.05.04

UG-M10CLKPLL

Subscribe

Send Feedback

Clock Networks Architecture and Features

Global Clock Networks

GCLKs drive throughout the entire device, feeding all device quadrants. All resources in the device, such

as the I/O elements, logic array blocks (LABs), dedicated multiplier blocks, and M9K memory blocks can

use GCLKs as clock sources. Use these clock network resources for control signals, such as clock enables

and clears fed by an external pin. Internal logic can also drive GCLKs for internally-generated GCLKs and

asynchronous clears, clock enables, or other control signals with high fan-out.

Clock Pins Introduction

There are two types of external clock pins that can drive the GCLK networks.

Dedicated Clock Input Pins

Features

2

You can use the dedicated clock input pins (CLK<#>[p,n]) to drive clock and global signals, such as

asynchronous clears, presets, and clock enables for GCLK networks.

If you do not use the dedicated clock input pins for clock input, you can also use them as general-purpose

input or output pins.

The CLK pins can be single-ended or differential inputs. When you use the CLK pins as single-ended clock

inputs, both the CLK<#>p and CLK<#>n pins have dedicated connection to the GCLK networks. When you

use the CLK pins as differential inputs, pair two clock pins of the same number to receive differential

signaling.

Dual-Purpose Clock Pins

You can use the dual-purpose clock (DPCLK) pins for high fan-out control signals, such as protocol signals,

TRDY and IRDY signals for PCI via GCLK networks.

The DPCLK pins are only available on the left and right of the I/O banks.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 8

2-2

Clock Resources

Clock Resources

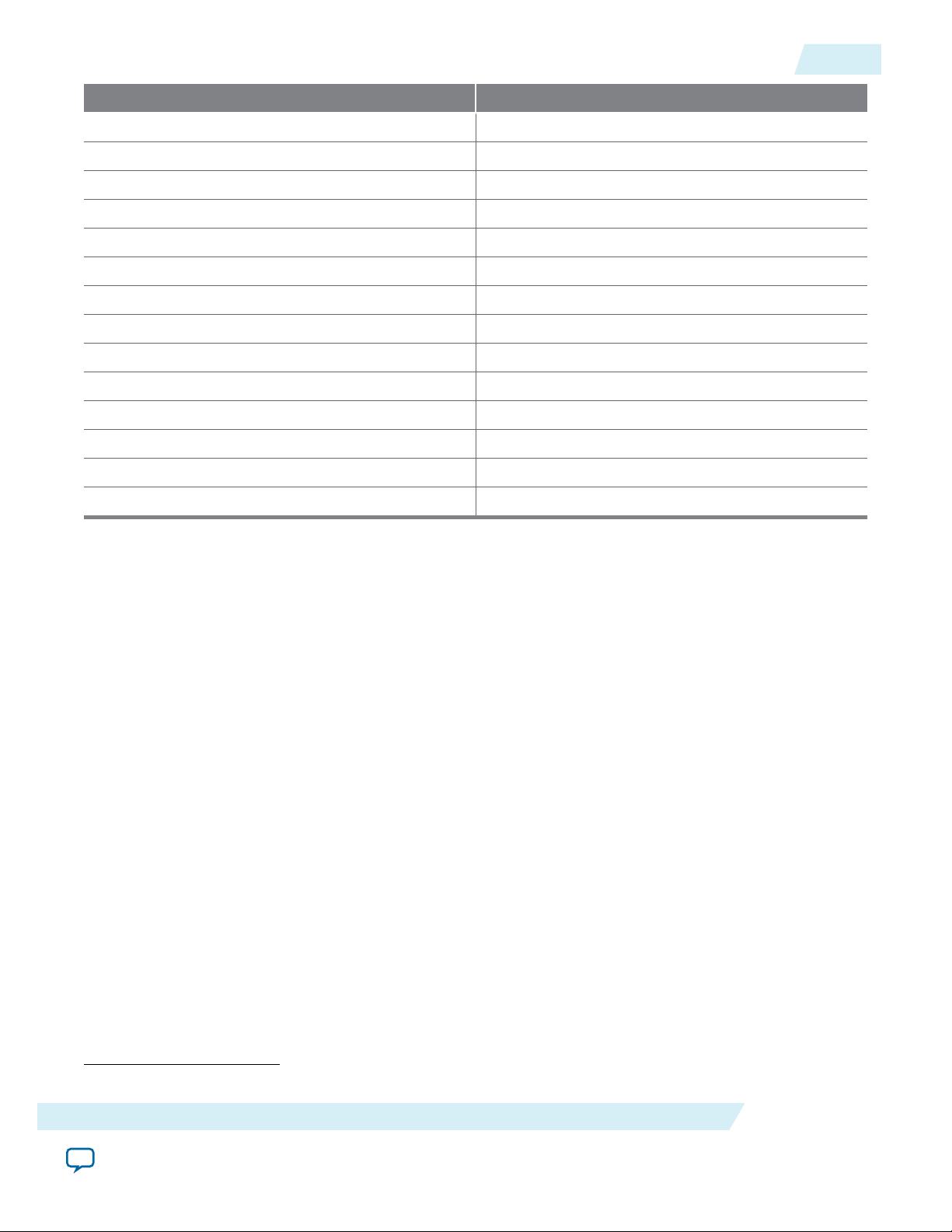

Table 2-1: MAX 10 Clock Resources

UG-M10CLKPLL

2015.05.04

Clock Resource Device Number of Resources

Available

Dedicated clock input pins

• 10M02

• 10M04

• 10M08

• 10M16

• 10M25

• 10M40

8 single-ended or 4

differential

16 single-ended or 8

differential

• 10M50

DPCLK pins All 4

For more information about the clock input pins connections, refer to the pin connection guidelines.

Related Information

MAX 10 FPGA Device Family Pin Connection Guidelines

Global Clock Network Sources

Table 2-2: MAX 10 Clock Pins Connectivity to the GCLK Networks

Source of Clock Resource

CLK[3..0][p,n] pins on the

left and right of the I/O

banks

CLK[7..0][p,n] pins on the

top, left, bottom, and right of

the I/O banks

DPCLK[3..0] pins on the left

and right of the I/O banks

CLK Pin GCLK

CLK0p GCLK[0,2,4]

CLK0n GCLK[1,2]

CLK1p GCLK[1,3,4]

CLK1n GCLK[0,3]

CLK2p GCLK[5,7,9]

CLK2n GCLK[6,7]

CLK3p GCLK[6,8,9]

CLK3n GCLK[5,8]

(1)

CLK4p

(1)

CLK4n

(1)

CLK5p

(1)

CLK5n

(1)

CLK6p

(1)

This only applies to 10M16, 10M25, 10M40, and 10M50 devices.

GCLK[10,12,14]

GCLK[11,12]

GCLK[11,13,14]

GCLK[10,13]

GCLK[15,17,19]

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 9

DPCLK2

DPCLK3

DPCLK0

DPCLK1

CLK[0,1][p,n] CLK[2,3][p,n]

GCLK[0..4] GCLK[5..9]

UG-M10CLKPLL

2015.05.04

CLK6n

CLK7p

CLK7n

DPCLK0 GCLK[0,2]

DPCLK1 GCLK[1,3,4]

DPCLK2 GCLK[5,7]

DPCLK3 GCLK[6,8,9]

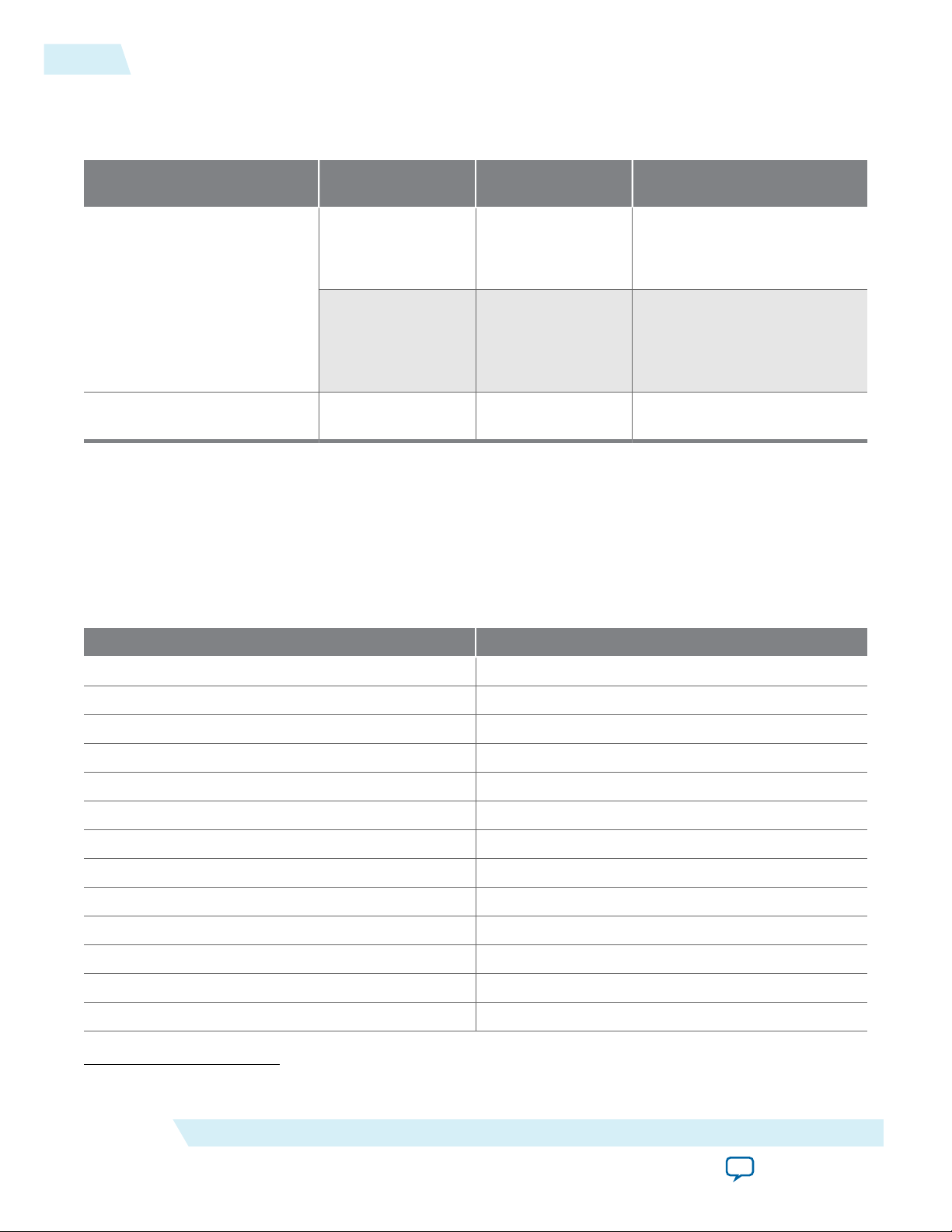

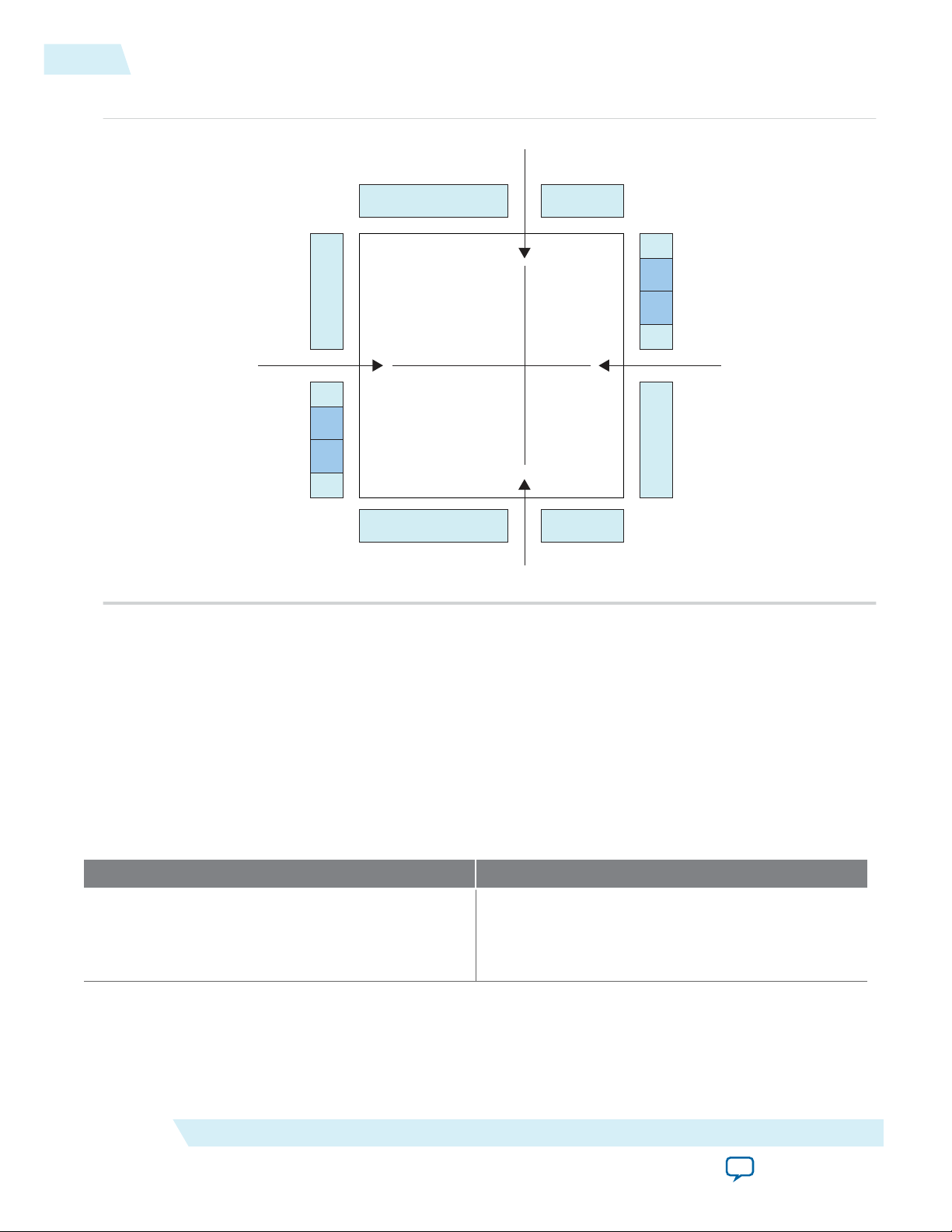

Figure 2-1: GCLK Network Sources for 10M02, 10M04, and 10M08 Devices

(1)

(1)

(1)

Global Clock Network Sources

CLK Pin GCLK

GCLK[16,17]

GCLK[16,18,19]

GCLK[15,18]

2-3

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 10

DPCLK2

DPCLK3

DPCLK0

DPCLK1

CLK[0,1][p,n] CLK[2,3][p,n]

GCLK[0..4] GCLK[5..9]

CLK[4,5][p,n]

CLK[6,7][p,n]

GCLK[15..19]

GCLK[10..14]

2-4

Global Clock Control Block

Figure 2-2: GCLK Network Sources for 10M16, 10M25, 10M40, and 10M50 Devices

UG-M10CLKPLL

2015.05.04

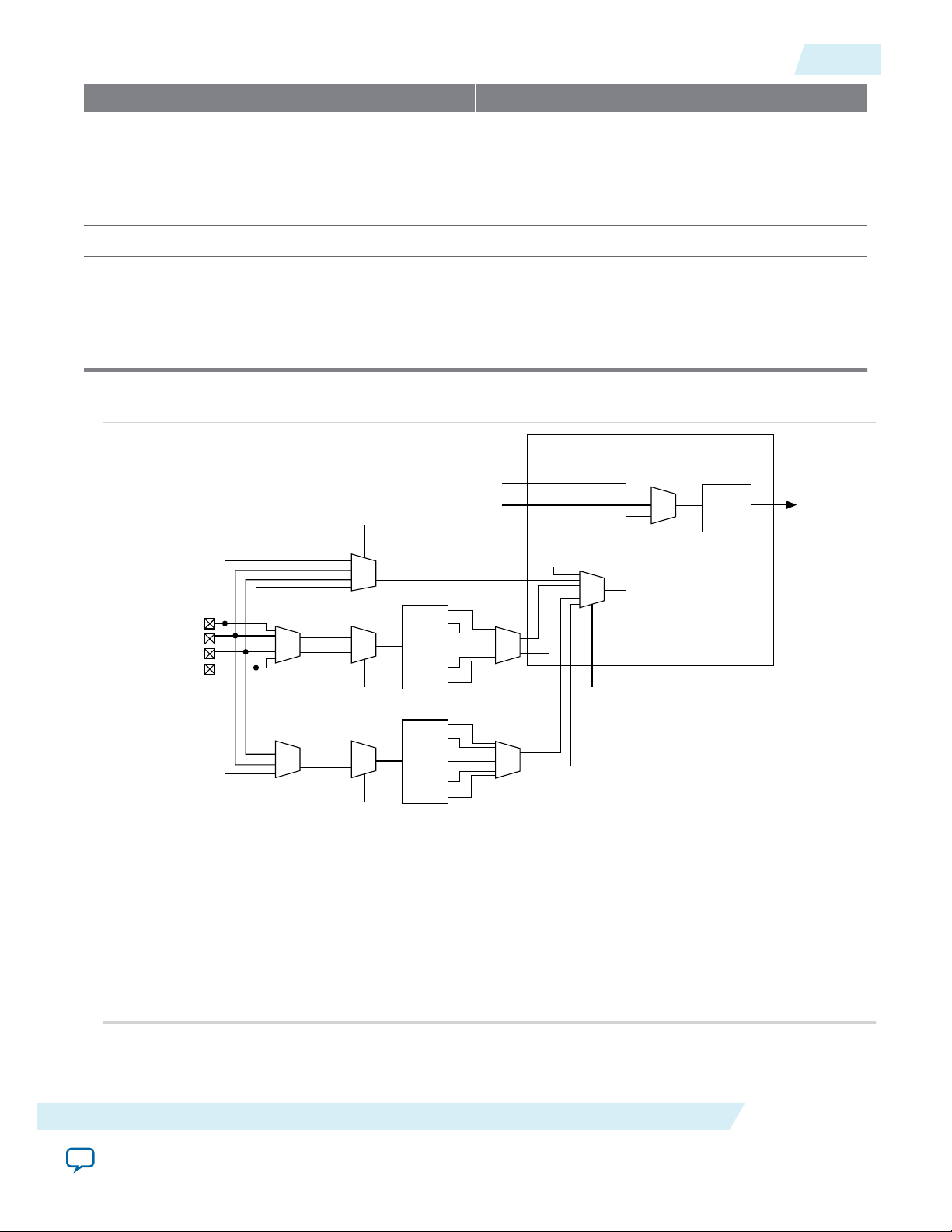

Global Clock Control Block

The clock control block drives GCLKs. The clock control blocks are located on each side of the device,

close to the dedicated clock input pins. GCLKs are optimized for minimum clock skew and delay.

The clock control block has the following functions:

• Dynamic GCLK clock source selection (not applicable for DPCLK pins and internal logic input)

• GCLK multiplexing

• GCLK network power down (dynamic enable and disable)

Table 2-3: Clock Control Block Inputs

Dedicated clock input pins Dedicated clock input pins can drive clocks or

Input Description

global signals, such as synchronous and asynchro‐

nous clears, presets, or clock enables onto given

GCLKs.

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 11

clkswitch (1)

Static Clock Select (3)

Static Clock

Select (3)

Internal Logic

Clock Control Block

DPCLK

clkselect[1..0] (2) Internal Logic (4)

inclk1

inclk0

CLK[n + 3]

CLK[n + 2]

CLK[n + 1]

CLK[n]

f

IN

C0

C1

C2

PLL

Global

Clock

Enable/

Disable

C3

C4

Notes:

(1) The clkswitch signal can either be set through the configuration file or dynamically set when using the manual PLL switchover

feature. The output of the multiplexer is the input clock (fIN) for the PLL.

(2) The clkselect[1..0] signals are fed by internal logic. You can use the clkselect[1..0] signals to dynamically select the clock source for

the GCLK when the device is in user mode. Only one PLL (applicable to PLLs on the same side) can be selected as the clock source to

the GCLK.

(3) The static clock select signals are set in the configuration file. Therefore, dynamic control when the device is in user mode is not

feasible.

(4) You can use internal logic to enable or disable the GCLK in user mode.

clkswitch (1)

inclk1

inclk0

f

IN

C0

C1

C2

PLL

C3

C4

UG-M10CLKPLL

2015.05.04

DPCLK pins DPCLK pins are bidirectional dual function pins that

PLL counter outputs PLL counter outputs can drive the GCLK.

Internal logic You can drive the GCLK through logic array

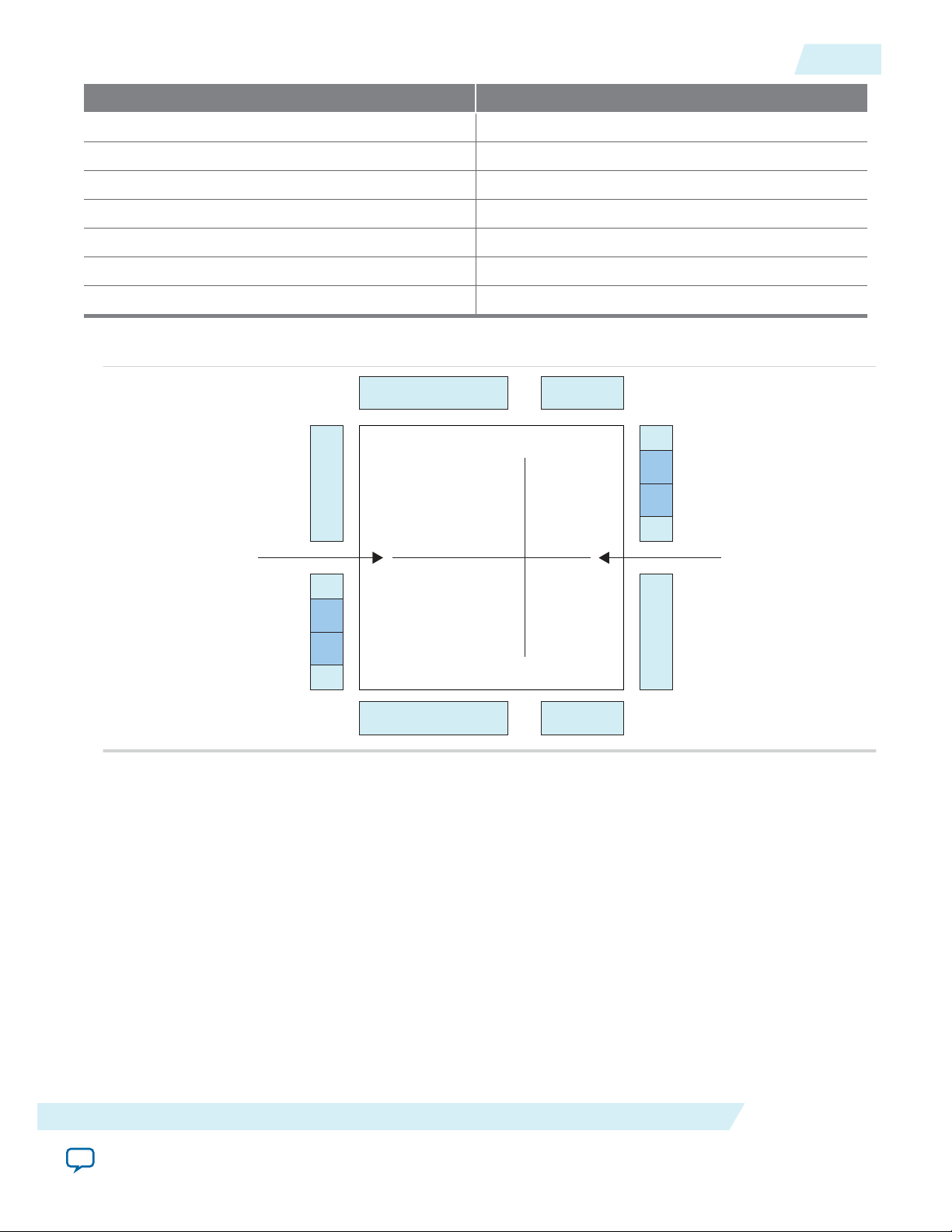

Figure 2-3: Clock Control Block

Global Clock Control Block

Input Description

are used for high fan-out control signals, such as

protocol signals, TRDY and IRDY signals for PCI via

the GCLK. Clock control blocks that have inputs

driven by DPCLK pins cannot drive PLL inputs.

routing to enable the internal logic elements (LEs)

to drive a high fan-out, low-skew signal path. Clock

control blocks that have inputs driven by internal

logic cannot drive PLL inputs.

2-5

Each MAX 10 device has a maximum of 20 clock control blocks. There are five clock control blocks on

each side of the device.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 12

5

GCLK

Clock Input Pins

4

DPCLK

Internal Logic

Clock

Control

Block

5

PLL Outputs

5

4

Five Clock Control

Blocks on Each Side

of the Device

2-6

Global Clock Network Power Down

Each PLL generates five clock outputs through the c[4..0] counters. Two of these clocks can drive the

GCLK through a clock control block.

From the Clock Control Block Inputs table, only the following inputs can drive into any given clock

control block:

• Two dedicated clock input pins

• Two PLL counter outputs

• One DPCLK pin

• One source from internal logic

The output from the clock control block in turn feeds the corresponding GCLK. The GCLK can drive the

PLL input if the clock control block inputs are outputs of another PLL or dedicated clock input pins.

Normal I/O pins cannot drive the PLL input clock port.

Figure 2-4: Clock Control Block on Each Side of the Device

UG-M10CLKPLL

2015.05.04

Altera Corporation

Out of these five inputs to any clock control block, the two clock input pins and two PLL outputs are

dynamically selected to feed a GCLK. The clock control block supports static selection of the signal from

internal logic.

Related Information

• ALTCLKCTRL Parameters on page 5-1

• ALTCLKCTRL Ports and Signals on page 5-2

Global Clock Network Power Down

You can disable the MAX 10 GCLK (power down) by using both static and dynamic approaches. In the

static approach, configuration bits are set in the configuration file generated by the Quartus® II software,

which automatically disables unused GCLKs. The dynamic clock enable or disable feature allows internal

logic to control clock enable or disable of the GCLKs.

When a clock network is disabled, all the logic fed by the clock network is in an off-state, reducing the

overall power consumption of the device. This function is independent of the PLL and is applied directly

on the clock network.

You can set the input clock sources and the clkena signals for the GCLK multiplexers through the

ALTCLKCTRL IP core parameter editor in the Quartus II software.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 13

clkena clkena_out

clk_out

clkin

D Q

clkin

clkena

clk_out

UG-M10CLKPLL

2015.05.04

Related Information

• ALTCLKCTRL Parameters on page 5-1

• ALTCLKCTRL Ports and Signals on page 5-2

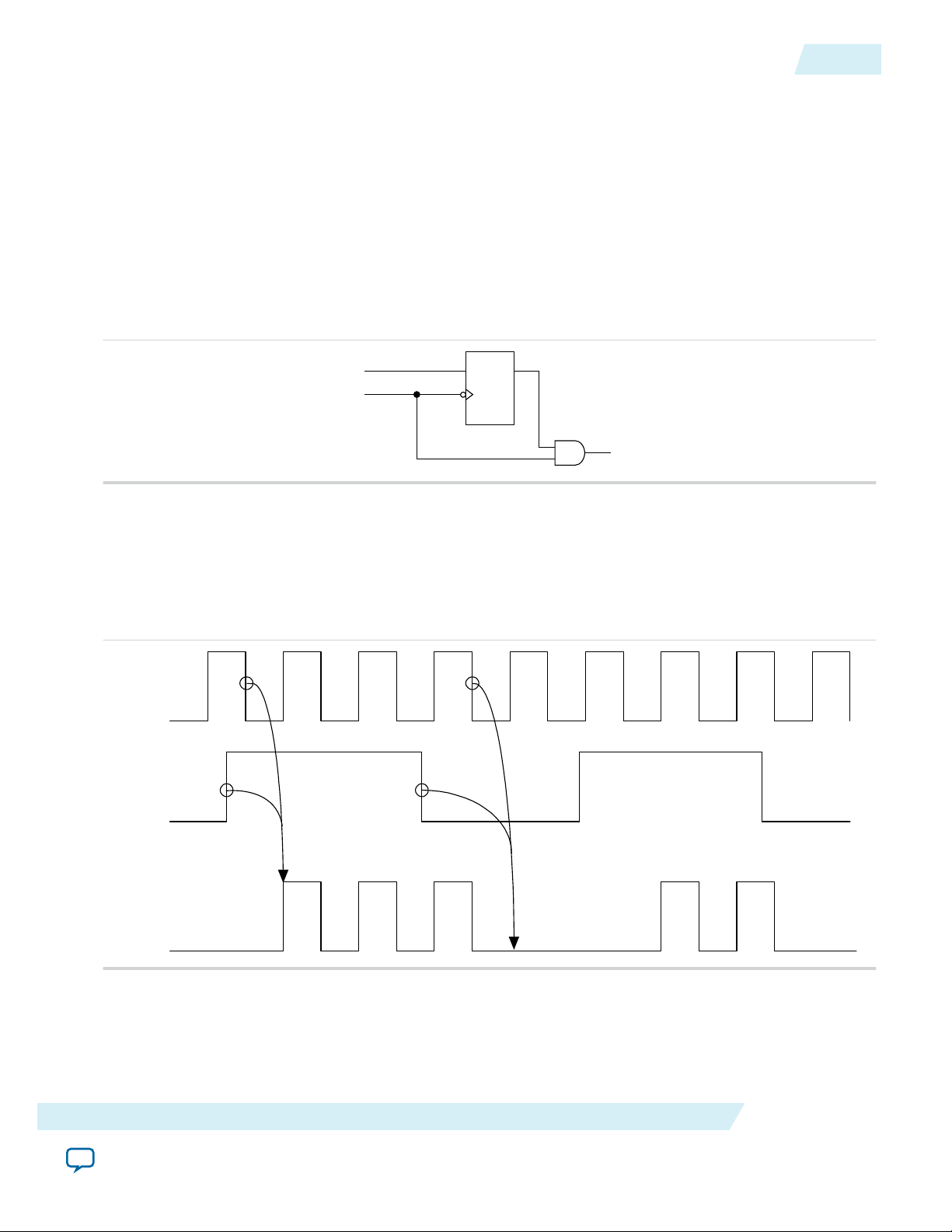

Clock Enable Signals

The MAX 10 devices support clkena signals at the GCLK network level. This allows you to gate off the

clock even when a PLL is used. After reenabling the output clock, the PLL does not need a resynchroniza‐

tion or relock period because the circuit gates off the clock at the clock network level. In addition, the PLL

can remain locked independent of the clkena signals because the loop-related counters are not affected.

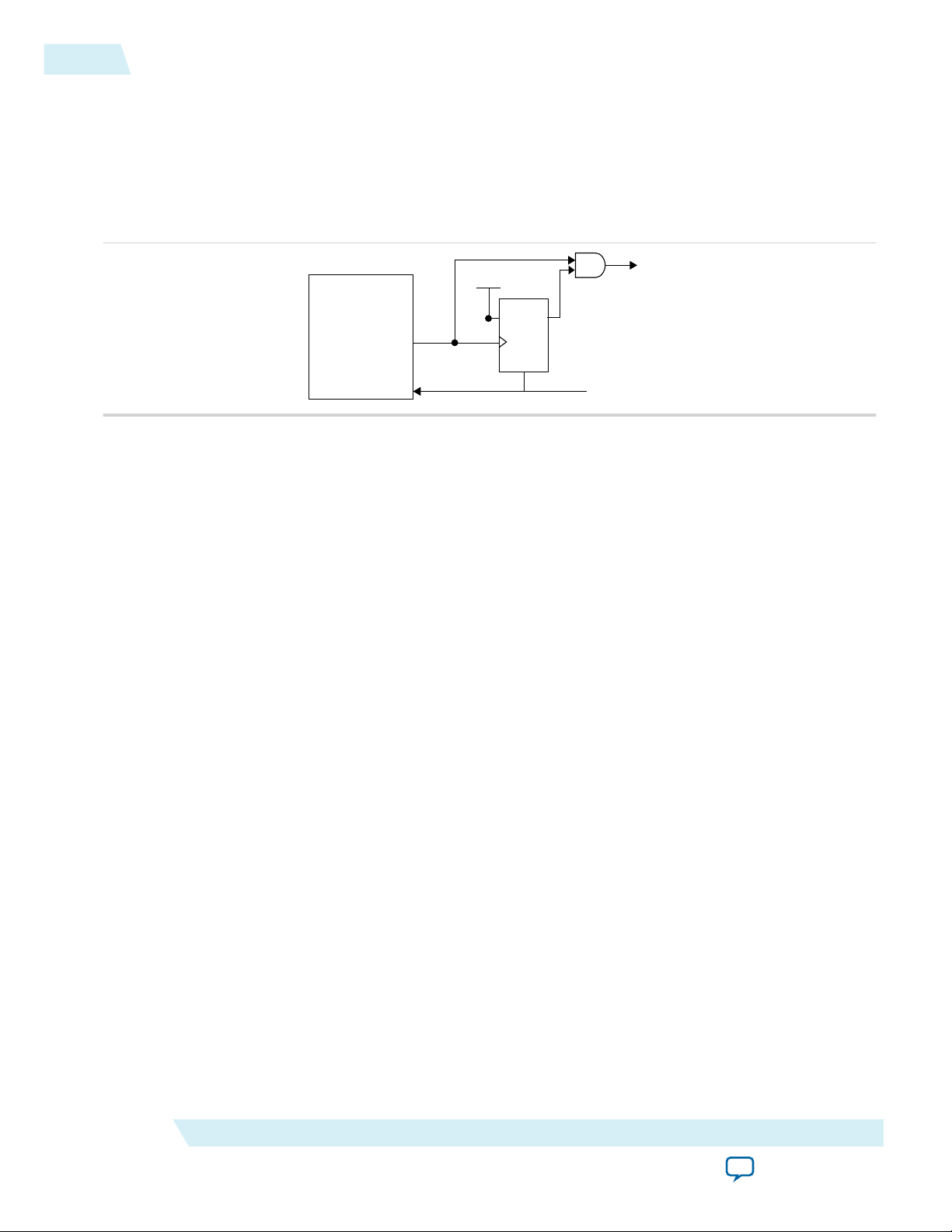

Figure 2-5: clkena Implementation

Clock Enable Signals

2-7

Note: The clkena circuitry controlling the C0 output of the PLL to an output pin is implemented with

two registers instead of a single register.

Figure 2-6: Example Waveform of clkena Implementation with Output Enable

The clkena signal is sampled on the falling edge of the clock (clkin). This feature is useful for

applications that require low power or sleep mode.

The clkena signal can also disable clock outputs if the system is not tolerant to frequency overshoot

during PLL resynchronization.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 14

Clock

Switchover

Block

inclk0

inclk1

pfdena

clkswitch

clkbad0

clkbad1

activeclock

PFD

LOCK

circuit

lock

÷n

CP

LF

VCO

÷2 (1)

÷C0

÷C1

÷C2

÷C3

÷C4

÷M

PLL

output

mux

GCLKs

ADC clock (2)

8

8

GCLK

networks

No Compensation; ZDB Mode

Source-Synchronous; Normal Mode

VCO

Range

Detector

Notes:

(1) This is the VCO post-scale counter K.

(2) Only counter C0 of PLL1 and PLL3 can drive the ADC clock.

PLL

External clock output

4:1

Multiplexer

4:1

Multiplexer

CLKIN

2-8

Internal Oscillator Architecture and Features

Related Information

• Guideline: Clock Enable Signals on page 3-1

• ALTCLKCTRL Parameters on page 5-1

• ALTCLKCTRL Ports and Signals on page 5-2

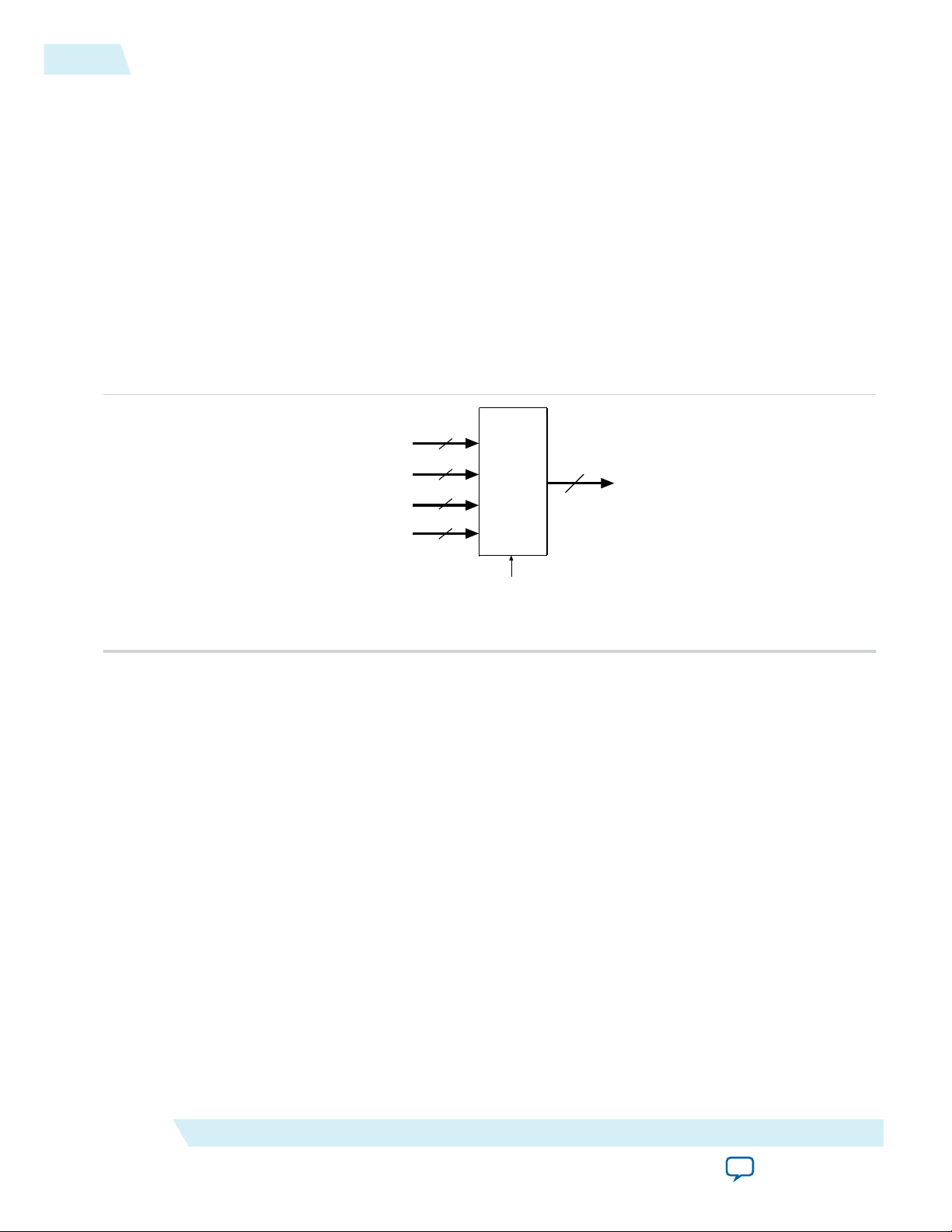

Internal Oscillator Architecture and Features

MAX 10 devices have built-in internal ring oscillator with clock multiplexers and dividers. The internal

ring oscillator operates up to 232 MHz which is not accessible. This operating frequency further divides

down to slower frequencies.

By default internal oscillator is turned off in user mode. You can turn on the oscillator by asserting the

oscena signal in the Internal Oscillator IP core.

When the oscena input signal is asserted, the oscillator is enabled and the output can be routed to the

logic array through the clkout output signal. When the oscena signal is set low, the clkout signal is

constant high. You can analyze this delay using the TimeQuest timing analyzer.

PLLs Architecture and Features

UG-M10CLKPLL

2015.05.04

PLL Architecture

The main purpose of a PLL is to synchronize the phase and frequency of the voltage-controlled oscillator

(VCO) to an input reference clock.

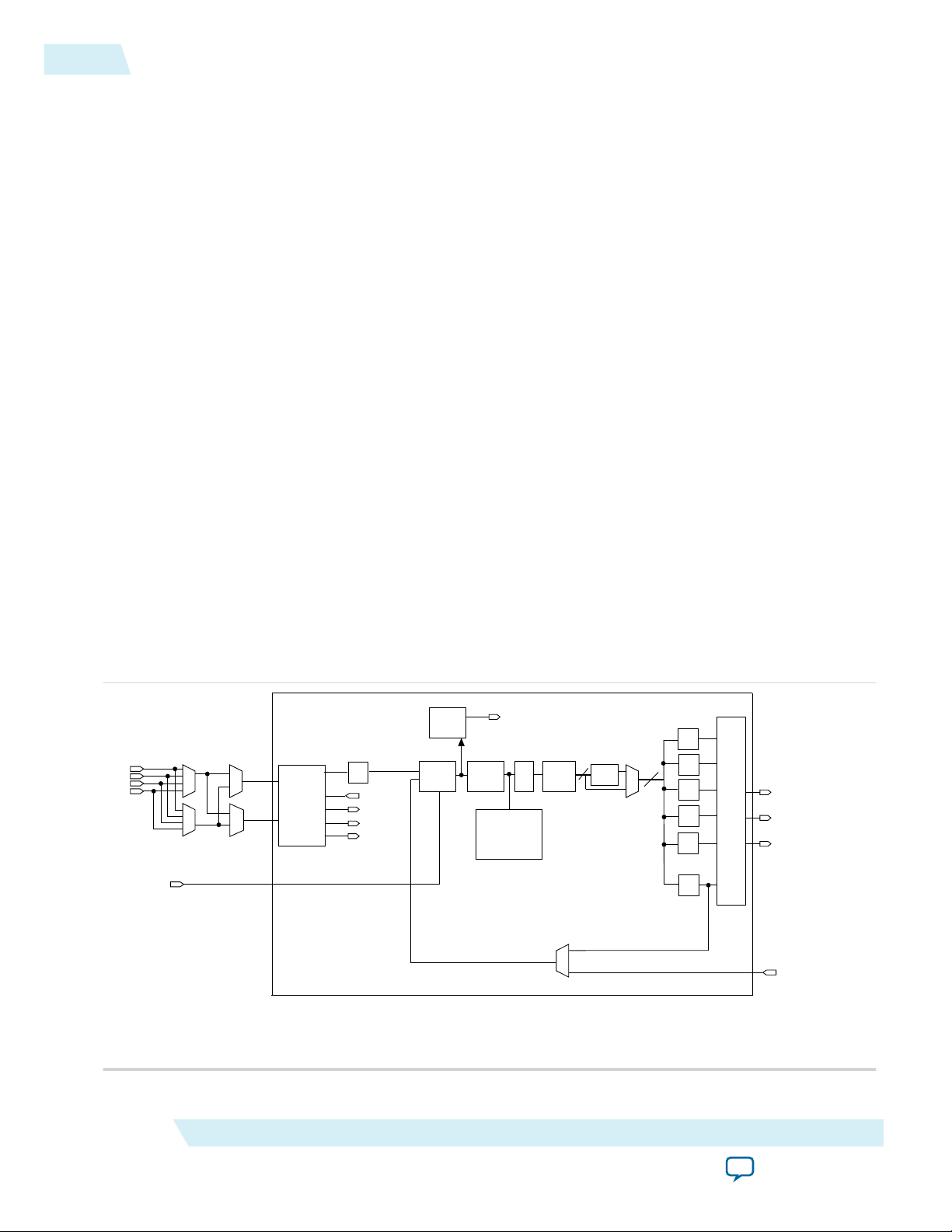

Figure 2-7: MAX 10 PLL High-Level Block Diagram

Each clock source can come from any of the two or four clock pins located on the same side of the device

as the PLL.

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 15

UG-M10CLKPLL

2015.05.04

Phase-Frequency Detector (PFD)

PLL Architecture

2-9

The PFD has inputs from the feedback clock, fFB, and the input reference clock, f

. The PLL compares

REF

the rising edge of the input reference clock to a feedback clock using a PFD. The PFD produces an up or

down signal that determines whether the VCO needs to operate at a higher or lower frequency.

Charge Pump (CP)

If the charge pump receives a logic high on the up signal, current is driven into the loop filter. If the

charge pump receives a logic high on the down signal, current is drawn from the loop filter.

Loop Filter (LF)

The loop filter converts the up and down signals from the PFD to a voltage that is used to bias the VCO.

The loop filter filters out glitches from the charge pump and prevents voltage overshoot, which minimizes

jitter on the VCO.

Voltage-Controlled Oscillator (VCO)

The voltage from the charge pump determines how fast the VCO operates. The VCO is implemented as a

four-stage differential ring oscillator. A divide counter, M, is inserted in the feedback loop to increase the

VCO frequency, f

, above the input reference frequency, f

VCO

REF

.

The VCO frequency is determined using the following equation:

f

= f

VCO

× M = fIN × M/N ,

REF

where fIN is the input clock frequency to the PLL and N is the pre-scale counter.

The VCO frequency is a critical parameter that must be between 600 and 1,300 MHz to ensure proper

operation of the PLL. The Quartus II software automatically sets the VCO frequency within the

recommended range based on the clock output and phase shift requirements in your design.

Post-Scale Counters (C)

The VCO output can feed up to five post-scale counters (C0, C1, C2, C3, and C4). These post-scale counters

allow the PLL to produce a number of harmonically-related frequencies.

Internal Delay Elements

The MAX 10 PLLs have internal delay elements to compensate for routing on the GCLK networks and

I/O buffers. These internal delays are fixed.

PLL Outputs

The MAX 10 PLL supports up to 5 GCLK outputs and 1 dedicated external clock output. The output

frequency, f

, to the GCLK network or dedicated external clock output is determined using the

OUT

following equation:

f

= fIN/N and

REF

f

OUT

= f

VCO

/C = (f

× M)/C = (fIN × M)/(N × C),

REF

where C is the setting on the C0, C1, C2, C3, or C4 counter.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 16

2-10

PLL Features

PLL Features

Table 2-4: MAX 10 PLL Features

Feature Support

C output counters 5

M, N, C counter sizes 1 to 512

Dedicated clock outputs 1 single-ended or 1 differential

Dedicated clock input pins 4 single-ended or 2 differential

Spread-spectrum input clock tracking Yes

PLL cascading Through GCLK

Source synchronous compensation Yes

No compensation mode Yes

Normal compensation Yes

Zero-delay buffer compensation Yes

Phase shift resolution Down to 96 ps increments

(3)

UG-M10CLKPLL

2015.05.04

(2)

(4)

Programmable duty cycle Yes

Output counter cascading Yes

Input clock switchover Yes

User mode reconfiguration Yes

Loss of lock detection Yes

4:1 multiplexer CLK input selection Yes

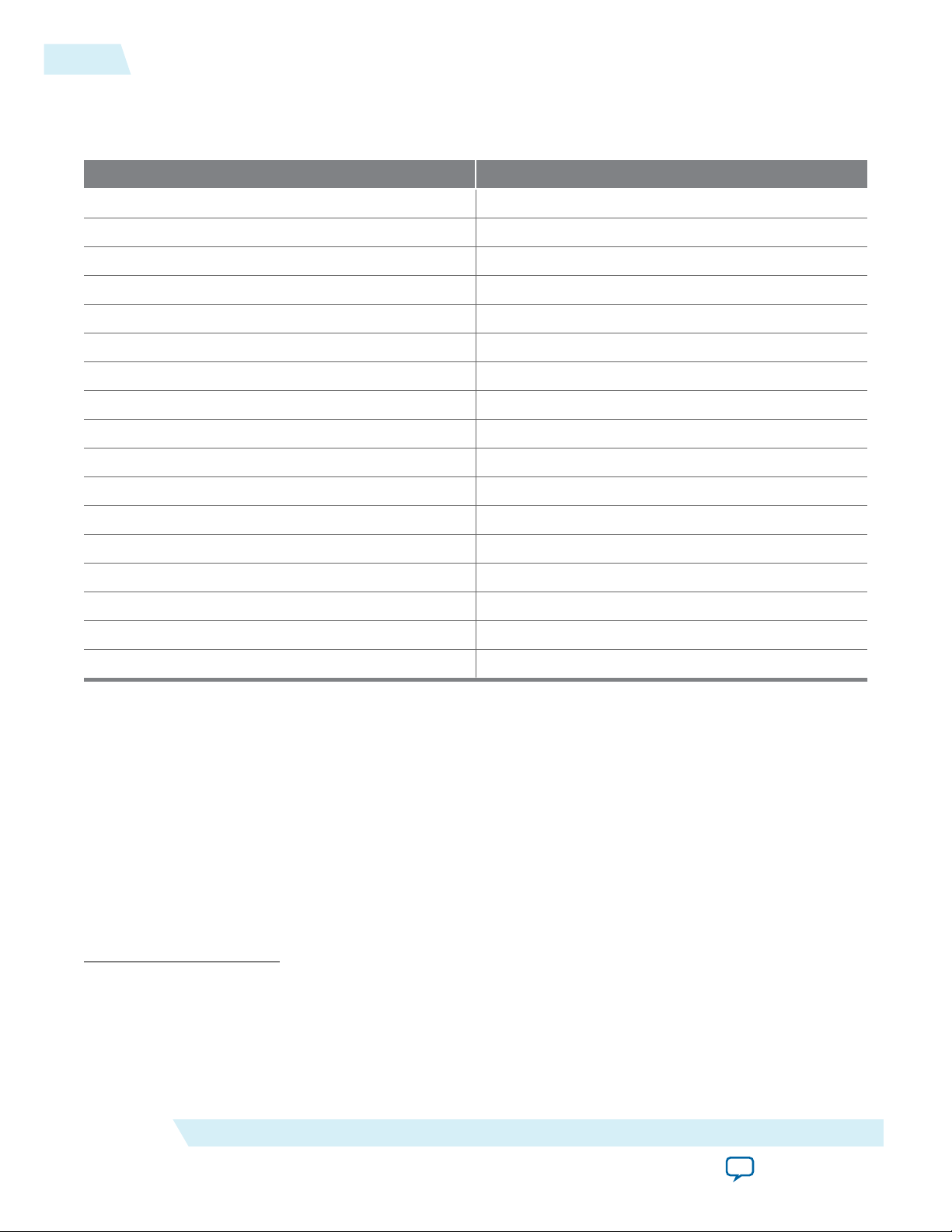

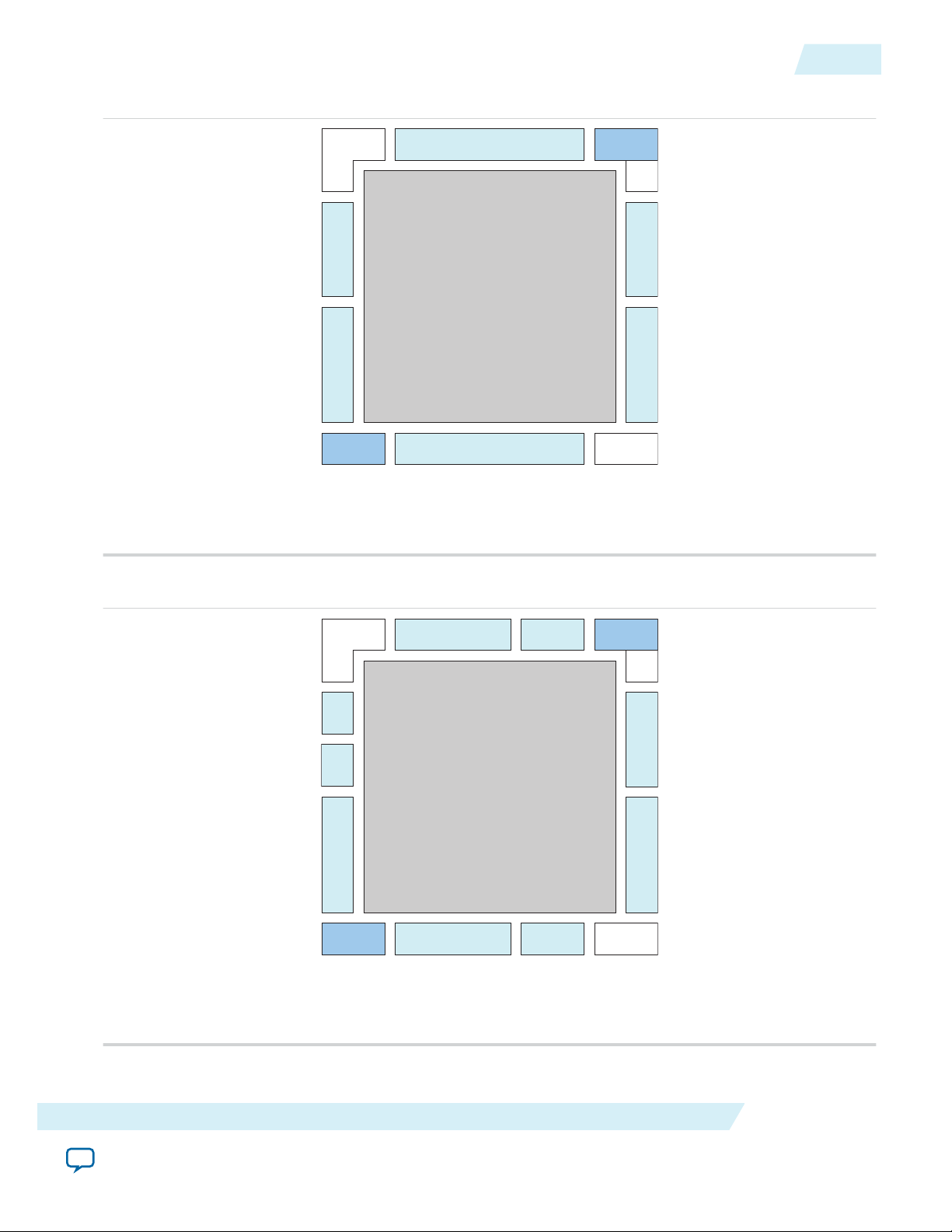

PLL Locations

The following figures show the physical locations of the PLLs. Every index represents one PLL in the

device. The physical locations of the PLLs correspond to the coordinates in the Quartus II Chip Planner.

(2)

C counters range from 1 through 512 if the output clock uses a 50% duty cycle. For any output clocks using a

non-50% duty cycle, the post-scale counters range from 1 through 256.

(3)

Only applicable if the input clock jitter is in the input jitter tolerance specifications.

(4)

The smallest phase shift is determined by the VCO period divided by eight. For degree increments, the

MAX 10 device family can shift all output frequencies in increments of at least 45°. Smaller degree

increments are possible depending on the frequency and divide parameters.

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 17

Bank 8

Bank 3

Bank 1Bank 2

Bank 6Bank 5

PLL 1 (1)

PLL 2 (2)

Notes:

(1) Available on all packages except V36 package.

(2) Available on U324 and V36packages only.

Bank 8

Bank 1A

Bank 2

Bank 6Bank 5

PLL 1 (1)

PLL 2 (2)Bank 7

Bank 3 Bank 4

Bank 1B

Notes:

(1) Available on all packages except V81 package.

(2) Available on F256, F484, U324, and V81 packages only.

UG-M10CLKPLL

2015.05.04

Figure 2-8: PLL Locations for 10M02 Device

PLL Locations

2-11

Figure 2-9: PLL Locations for 10M04 and 10M08 Devices

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 18

Bank 8

Bank 1A

Bank 2

Bank 6Bank 5

PLL 1

PLL 2 (1)Bank 7

Bank 3 Bank 4

Bank 1B

PLL 3 (1)

PLL 4 (1)

OCT

Note:

(1) Available on all packages except E144 and U169 packages.

2-12

Clock Pin to PLL Connections

Figure 2-10: PLL Locations for 10M16, 10M25, 10M40 and 10M50 Devices

UG-M10CLKPLL

2015.05.04

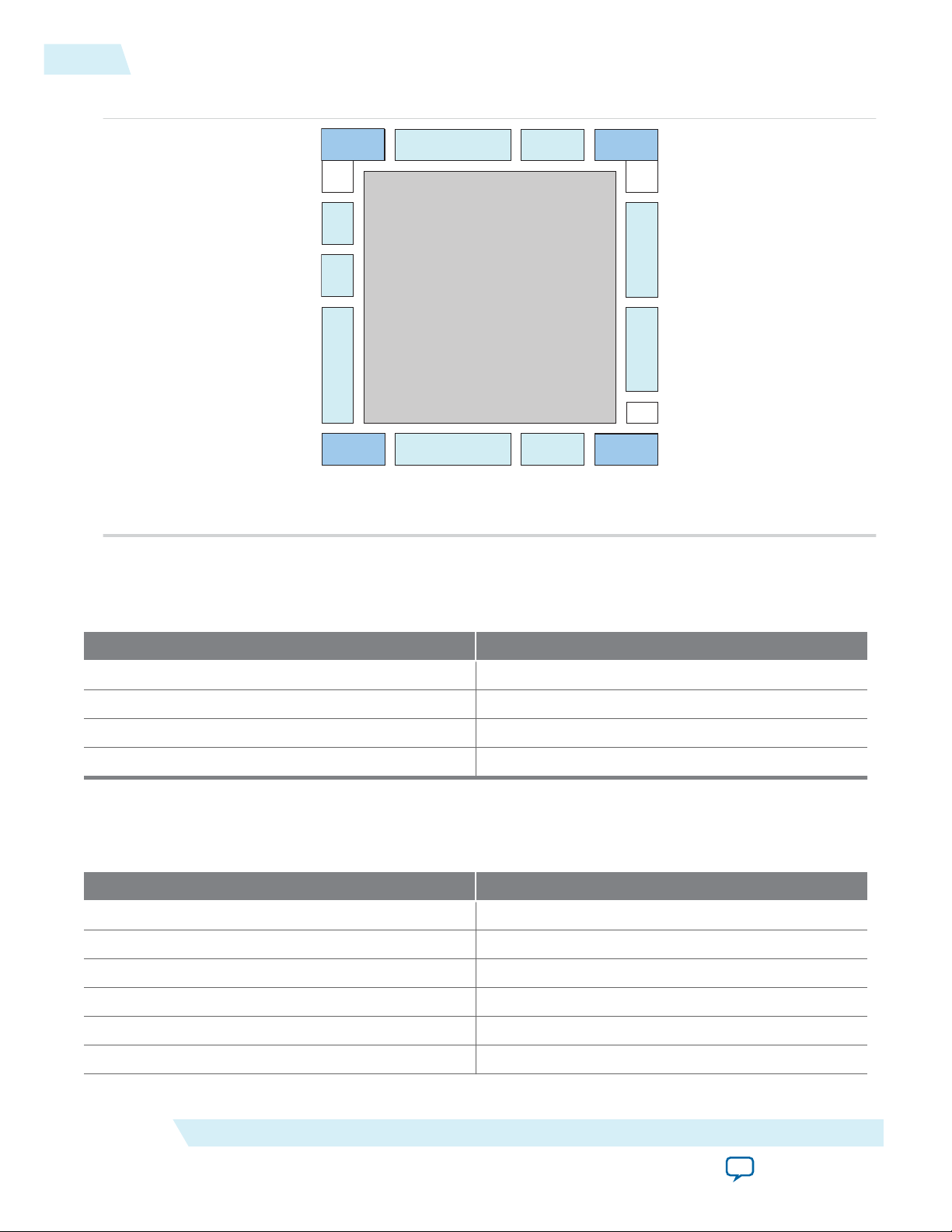

Clock Pin to PLL Connections

Table 2-5: MAX 10 Dedicated Clock Input Pin Connectivity to PLL

Dedicated Clock Pin PLL

CLK[0,1][p,n] PLL1, PLL3

CLK[2,3][p,n] PLL2, PLL4

CLK[4,5][p,n] PLL2, PLL3

CLK[6,7][p,n] PLL1, PLL4

PLL Counter to GCLK Connections

Table 2-6: MAX 10 PLL Counter Connectivity to the GCLK Networks

PLL Counter Output GCLK

PLL1_C0 GCLK[0,3,15,18]

PLL1_C1 GCLK[1,4,16,19]

PLL1_C2 GCLK[0,2,15,17]

PLL1_C3 GCLK[1,3,16,18]

PLL1_C4 GCLK[2,4,17,19]

PLL2_C0 GCLK[5,8,10,13]

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 19

UG-M10CLKPLL

2015.05.04

PLL Control Signals

PLL Counter Output GCLK

PLL2_C1 GCLK[6,9,11,14]

PLL2_C2 GCLK[5,7,10,12]

PLL2_C3 GCLK[6,8,11,13]

PLL2_C4 GCLK[7,9,12,14]

PLL3_C0

PLL3_C1

PLL3_C2

PLL3_C3

PLL3_C4

PLL4_C0

PLL4_C1

PLL4_C2

PLL4_C3

PLL4_C4

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

GCLK[0,3,10,13]

GCLK[1,4,11,14]

GCLK[0,2,10,12]

GCLK[1,3,11,13]

GCLK[2,4,12,14]

GCLK[5,8,15,18]

GCLK[6,9,16,19]

GCLK[5,7,15,17]

GCLK[6,8,16,18]

GCLK[7,9,17,19]

2-13

PLL Control Signals

You can use the following three signals to observe and control the PLL operation and resynchronization.

pfdena

Use the pfdena signal to maintain the last locked frequency so that your system has time to store its

current settings before shutting down.

The pfdena signal controls the PFD output with a programmable gate. The PFD circuit is enabled by

default. When the PFD circuit is disabled, the PLL output does not depend on the input clock, and tends

to drift outside of the lock window.

areset

The areset signal is the reset or resynchronization input for each PLL. The device input pins or internal

logic can drive these input signals.

When you assert the areset signal, the PLL counters reset, clearing the PLL output and placing the PLL

out of lock. The VCO is then set back to its nominal setting. When the areset signal is deasserted, the

PLL resynchronizes to its input as it relocks.

The assertion of the areset signal does not disable the VCO, but instead resets the VCO to its nominal

value. The only time that the VCO is completely disabled is when you do not have a PLL instantiated in

your design.

(5)

This only applies to 10M16, 10M25, 10M40, and 10M50 devices.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 20

DFF

D

Q

PLL

locked

locked

areset

V

CC

2-14

Clock Feedback Modes

locked

The locked output indicates that the PLL has locked onto the reference clock and the PLL clock outputs

are operating at the desired phase and frequency set in the ALTPLL IP core parameter editor.

Altera recommends using the areset and locked signals in your designs to control and observe the status

of your PLL. This implementation is illustrated in the following figure.

Figure 2-11: locked Signal Implementation

Note: If you use the SignalTap® II tool to probe the locked signal before the D flip-flop, the locked

signal goes low only when areset is deasserted. If the areset signal is not enabled, the extra logic

is not implemented in the ALTPLL IP core.

UG-M10CLKPLL

2015.05.04

Related Information

• Guideline: PLL Control Signals on page 3-2

• PLL Control Signals Parameter Settings on page 6-2

• ALTPLL Ports and Signals on page 6-6

Clock Feedback Modes

The MAX 10 PLLs support up to four different clock feedback modes. Each mode allows clock multiplica‐

tion and division, phase shifting, and programmable duty cycle.

The PLL fully compensates input and output delays only when you use the dedicated clock input pins

associated with a given PLL as the clock sources.

For example, when using PLL1 in normal mode, the clock delays from one of the following clock input

pins to the PLL and the PLL clock output-to-destination register are fully compensated:

• CLK0

• CLK1

• CLK2

• CLK3

When driving the PLL using the GCLK network, the input and output delays might not be fully

compensated in the Quartus II software.

Altera Corporation

Related Information

Operation Modes Parameter Settings on page 6-1

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 21

Data pin

PLL reference

clock at input pin

Data at register

Clock at register

UG-M10CLKPLL

2015.05.04

Source Synchronous Mode

If the data and clock arrive at the same time at the input pins, the phase relationship between the data and

clock remains the same at the data and clock ports of any I/O element input register.

You can use this mode for source synchronous data transfers. Data and clock signals at the I/O element

experience similar buffer delays as long as both signals use the same I/O standard.

Figure 2-12: Example of Phase Relationship Between Clock and Data in Source Synchronous Mode

Source Synchronous Mode

2-15

Source synchronous mode compensates for clock network delay, including any difference in delay

between the following two paths:

• Data pin to I/O element register input

• Clock input pin to the PLL PFD input

For all data pins clocked by a source synchronous mode PLL, set the input pin to the register delay chain

in the I/O element to zero in the Quartus II software. All data pins must use the PLL COMPENSATED

logic option in the Quartus II software.

No Compensation Mode

In no compensation mode, the PLL does not compensate for any clock networks. This mode provides

better jitter performance because clock feedback into the PFD does not pass through as much circuitry.

Both the PLL internal and external clock outputs are phase-shifted with respect to the PLL clock input.

MAX 10 Clocking and PLL Architecture and Features

Altera Corporation

Send Feedback

Page 22

PLL Reference

Clock at the Input Pin

PLL Clock at the

Register Clock Port

(1), (2)

External PLL Clock

Outputs (2)

Phase Aligned

Notes:

(1) Internal clocks fed by the PLL are phase-aligned to each other.

(2) The PLL clock outputs can lead or lag the PLL input clocks. The PLL clock outputs lag the

PLL input clocks depending on the routine delays.

PLL Reference

Clock at the Input pin

PLL Clock at the

Register Clock Port

External PLL Clock

Outputs (1)

Phase Aligned

Note:

(1) The external clock output can lead or lag the PLL internal clock signals.

2-16

Normal Mode

Figure 2-13: Example of Phase Relationship Between the PLL Clocks in No Compensation Mode

UG-M10CLKPLL

2015.05.04

Normal Mode

In normal mode, the PLL fully compensates the delay introduced by the GCLK network. An internal clock

in normal mode is phase-aligned to the input clock pin. In this mode, the external clock output pin has a

phase delay relative to the input clock pin. The Quartus II software timing analyzer reports any phase

difference between the two.

Figure 2-14: Example of Phase Relationship Between the PLL Clocks in Normal Compensation Mode

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 23

PLL Reference Clock

at the Input Pin

PLL Clock

at the Register Clock Port

External PLL Clock Output

at the Output Pin

Phase Aligned

UG-M10CLKPLL

2015.05.04

Zero-Delay Buffer Mode

In zero-delay buffer (ZDB) mode, the external clock output pin is phase-aligned with the clock input pin

for zero delay through the device. When using this mode, use the same I/O standard for the input clock

and output clocks to ensure clock alignment at the input and output pins.

Figure 2-15: Example of Phase Relationship Between the PLL Clocks in ZDB Mode

Zero-Delay Buffer Mode

2-17

PLL External Clock Output

Each PLL in the MAX 10 devices supports one single-ended clock output or one differential clock output.

Only the C0 output counter can feed the dedicated external clock outputs without going through the

GCLK. Other output counters can feed other I/O pins through the GCLK.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 24

C0

C1

C2

C4

C3

PLL #

clkena 1 (1)

clkena 0 (1)

PLL #_CLKOUTp (2)

PLL #_CLKOUTn (2)

Notes:

(1) These external clock enable signals are available only when using the ALTCLKCTRL IP core.

(2) PLL#_CLKOUTp and PLL#_CLKOUTn pins are dual-purpose I/O pins that you can use as one single-ended

or one differential clock output.

2-18

PLL External Clock Output

Figure 2-16: PLL External Clock Output

UG-M10CLKPLL

2015.05.04

Each pin of a differential output pair is 180° out of phase. To implement the 180° out-of-phase pin in a

pin pair, the Quartus II software places a NOT gate in the design into the I/O element.

The clock output pin pairs support the following I/O standards:

• Same I/O standard as the standard output pins (in the top and bottom banks)

• LVDS

• LVPECL

• Differential high-speed transceiver logic (HSTL)

• Differential SSTL

The MAX 10 PLLs can drive out to any regular I/O pin through the GCLK. You can also use the external

clock output pins as general-purpose I/O pins if you do not require any external PLL clocking.

Related Information

MAX 10 General Purpose I/O User Guide

Provides more information about the I/O standards supported by the PLL clock output pins.

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 25

UG-M10CLKPLL

2015.05.04

ADC Clock Input from PLL

Only the C0 output counter from PLL1 and PLL3 can drive the ADC clock.

Counter C0 has dedicated path to the ADC clock input.

Spread-Spectrum Clocking

The MAX 10 devices allow a spread-spectrum input with typical modulation frequencies. However, the

device cannot automatically detect that the input is a spread-spectrum signal. Instead, the input signal

looks like deterministic jitter at the input of the PLL.

The MAX 10 PLLs can track a spread-spectrum input clock if the input signal meets the following

conditions:

• The input signal is within the input jitter tolerance specifications.

• The modulation frequency of the input clock is below the PLL bandwidth as specified in the Fitter

report.

MAX 10 devices cannot generate spread-spectrum signals internally.

PLL Programmable Parameters

ADC Clock Input from PLL

2-19

Programmable Duty Cycle

The programmable duty cycle allows PLLs to generate clock outputs with a variable duty cycle. This

feature is supported on the PLL post-scale counters.

The duty cycle setting is achieved by a low and high time-count setting for the post-scale counters. To

determine the duty cycle choices, the Quartus II software uses the frequency input and the required

multiply or divide rate.

The post-scale counter value determines the precision of the duty cycle. The precision is defined as 50%

divided by the post-scale counter value. For example, if the C0 counter is 10, steps of 5% are possible for

duty cycle choices between 5 to 90%.

Combining the programmable duty cycle with programmable phase shift allows the generation of precise

nonoverlapping clocks.

Related Information

Post-Scale Counters (C0 to C4) on page 4-11

Provides more information about configuring the duty cycle of the post-scale counters in real time.

Programmable Bandwidth

The PLL bandwidth is the measure of the PLL’s ability to track the input clock and its associated jitter.

The MAX 10 PLLs provide advanced control of the PLL bandwidth using the programmable characteris‐

tics of the PLL loop, including loop filter and charge pump. The 3-dB frequency of the closed-loop gain in

the PLL determines the PLL bandwidth. The bandwidth is approximately the unity gain point for open

loop PLL response.

Related Information

• Programmable Bandwidth with Advanced Parameters on page 4-10

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 26

2-20

Programmable Phase Shift

• Charge Pump and Loop Filter on page 4-13

Provides more information about the PLL components to update PLL bandwidth in real time.

• Programmable Bandwidth Parameter Settings on page 6-2

Programmable Phase Shift

The MAX 10 devices use phase shift to implement clock delays. You can phase shift the output clocks

from the MAX 10 PLLs using one of the following methods:

• Fine resolution using VCO phase taps

• Coarse resolution using counter starting time

The VCO phase output and counter starting time are the most accurate methods of inserting delays.

These methods are purely based on counter settings, which are independent of process, voltage, and

temperature.

The MAX 10 devices support dynamic phase shifting of VCO phase taps only. The phase shift is configu‐

rable for any number of times. Each phase shift takes about one scanclk cycle, allowing you to implement

large phase shifts quickly.

Fine Resolution Phase Shift

Fine resolution phase shifts are implemented by allowing any of the output counters (C[4..0]) or the M

counter to use any of the eight phases of the VCO as the reference clock. This allows you to adjust the

delay time with a fine resolution. The following equation shows the minimum delay time that you can

insert using this method.

UG-M10CLKPLL

2015.05.04

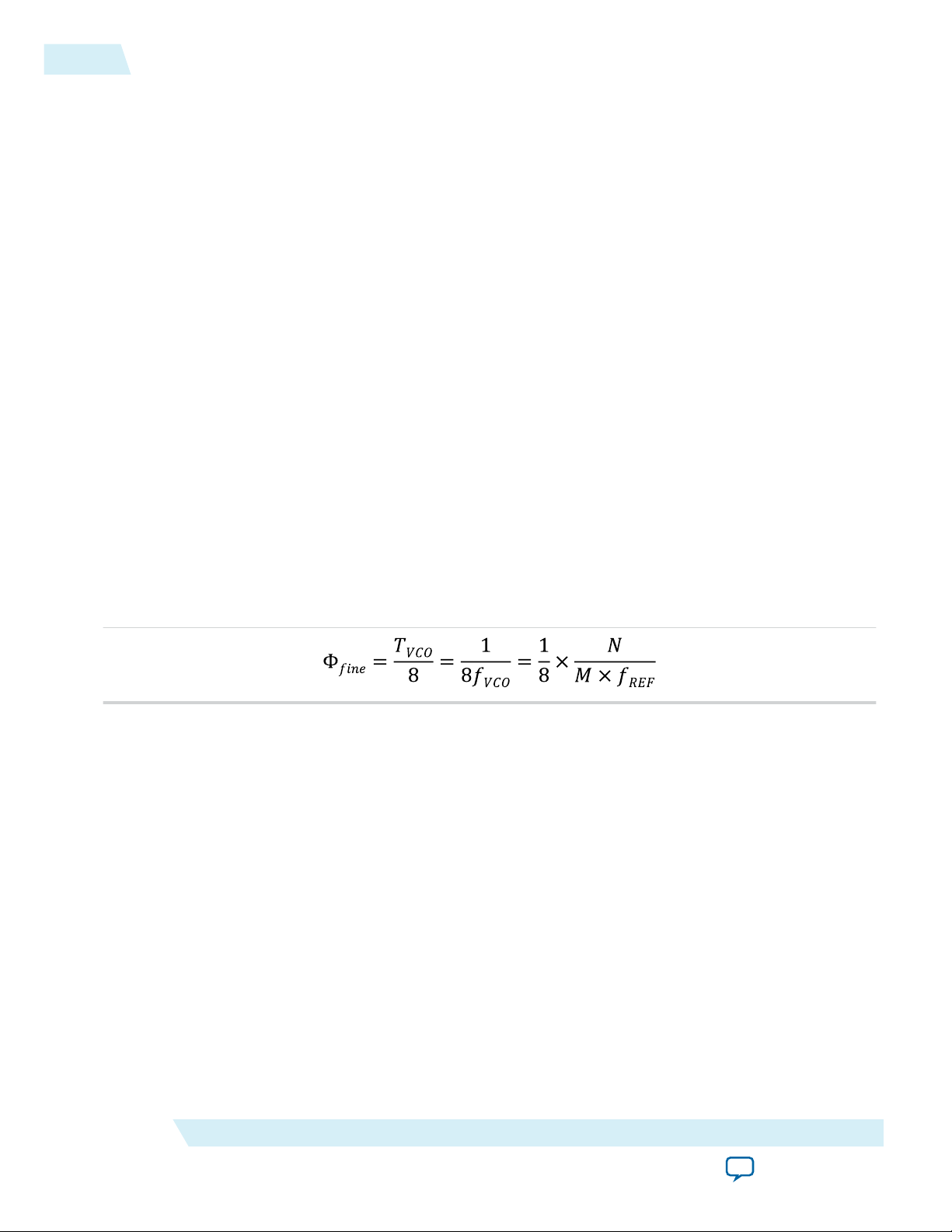

Figure 2-17: Fine Resolution Phase Shift Equation

f

in this equation is the input reference clock frequency

REF

For example, if f

is 100 MHz, N = 1, and M = 8, then f

REF

= 800 MHz, and Φ

VCO

= 156.25 ps. The PLL

fine

operating frequency defines this phase shift, a value that depends on the reference clock frequency and

counter settings.

The following figure shows an example of phase shift insertion using the fine resolution through VCO

phase taps method. The eight phases from the VCO are shown and labeled for reference.

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 27

t

d0-1

t

d0-2

1/8 t

VCO

t

VCO

0

90

135

180

225

270

315

CLK0

CLK1

CLK2

45

UG-M10CLKPLL

2015.05.04

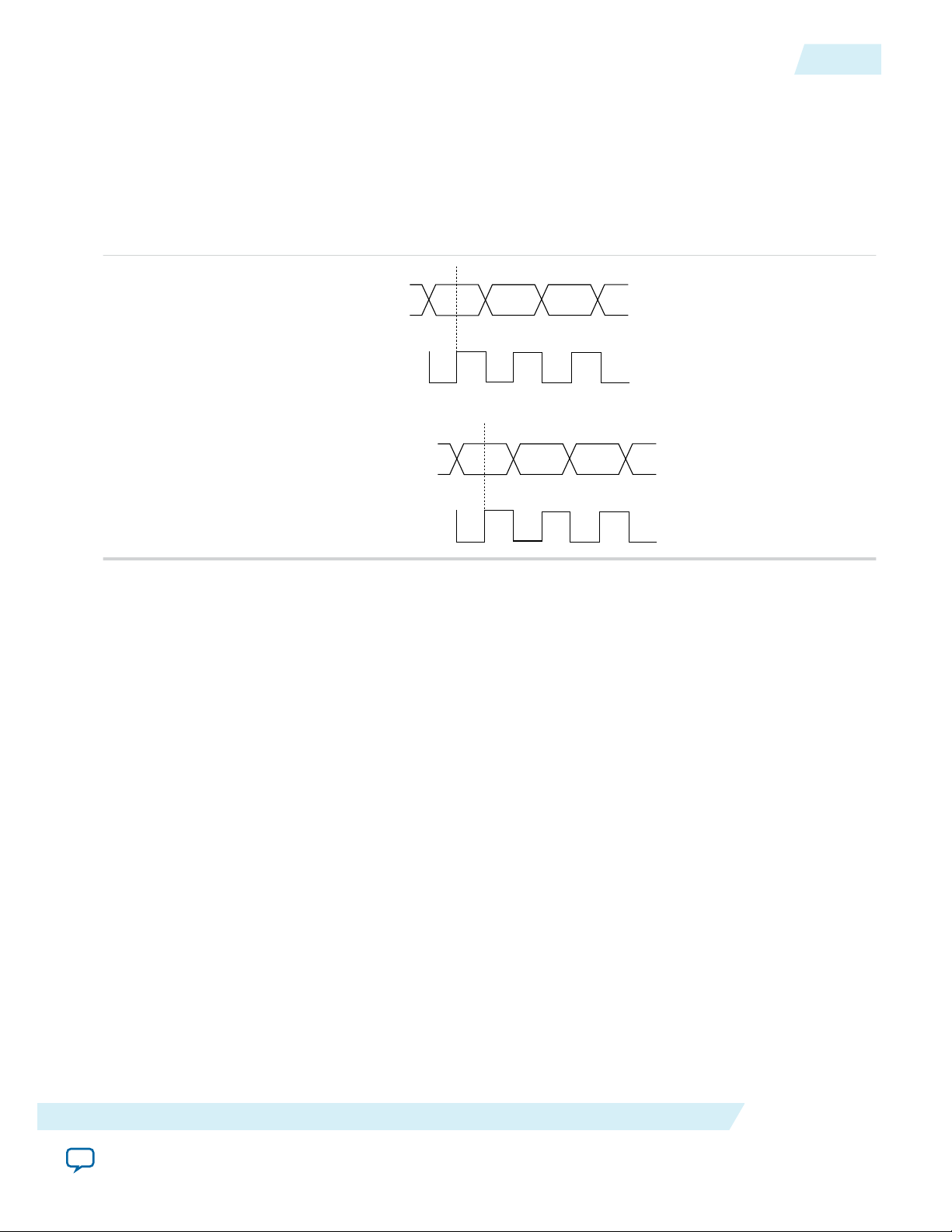

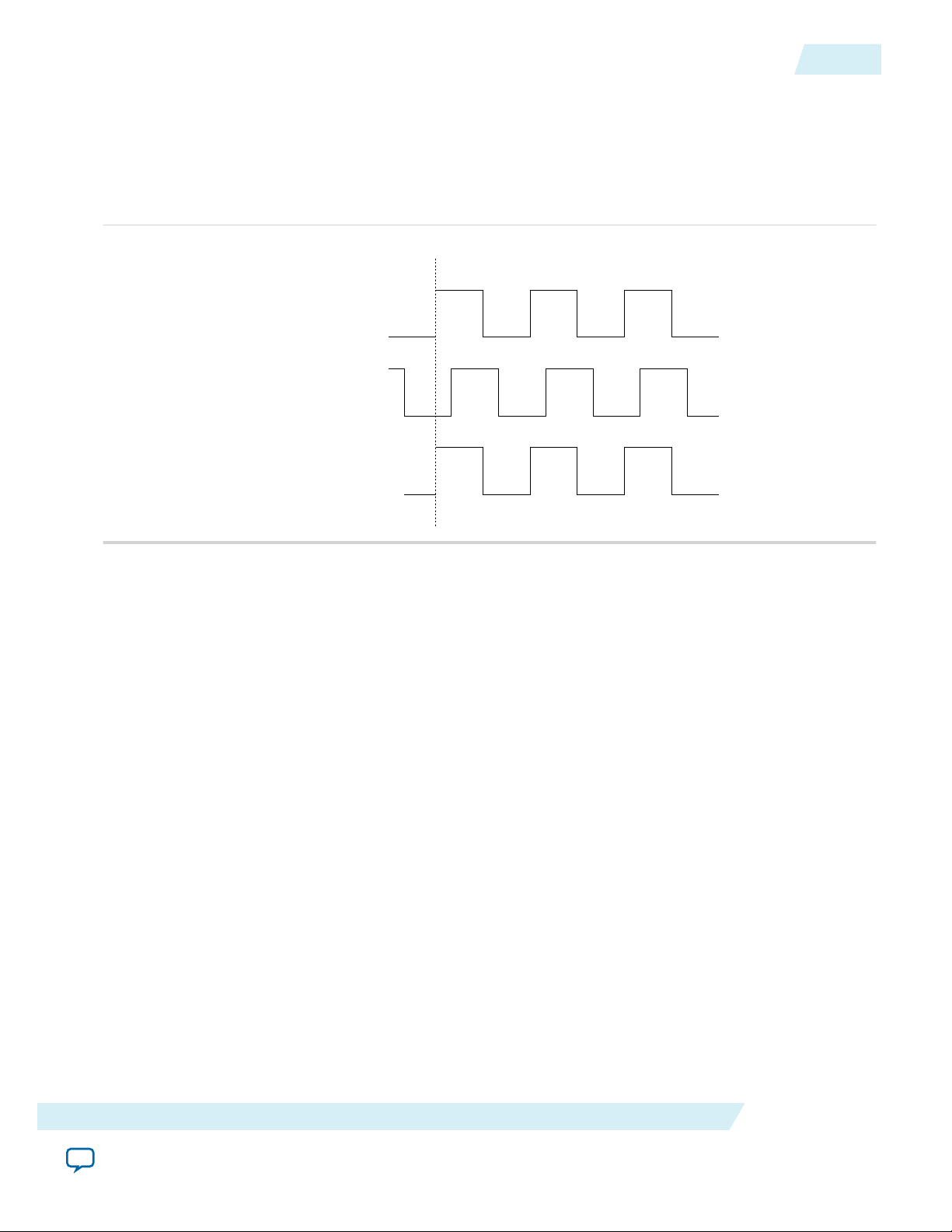

Figure 2-18: Example of Delay Insertion Using VCO Phase Output and Counter Delay Time

Programmable Phase Shift

2-21

The observations in this example are as follows:

• CLK0 is based on 0° phase from the VCO and has the C value for the counter set to one.

• CLK1 signal is divided by four, two VCO clocks for high time and two VCO clocks for low time. CLK1 is

based on the 135° phase tap from the VCO and has the C value for the counter set to one.

• CLK2 signal is also divided by four. In this case, the two clocks are offset by 3 Φ

. CLK2 is based on the

fine

0° phase from the VCO but has the C value for the counter set to three. This creates a delay of two

Φ

(two complete VCO periods).

coarse

Coarse Resolution Phase Shift

Coarse resolution phase shifts are implemented by delaying the start of the counters for a predetermined

number of counter clocks.

Figure 2-19: Coarse Resolution Phase Shift Equation

C in this equation is the count value set for the counter delay time—the initial setting in the PLL usage

section of the compilation report in the Quartus II software. If the initial value is 1, C – 1 = 0° phase shift.

Related Information

• Dynamic Phase Configuration Implementation on page 4-15

• Dynamic Phase Configuration Counter Selection on page 4-16

• Dynamic Phase Configuration with Advanced Parameters on page 4-16

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 28

2-22

Clock Switchover

• Dynamic Phase Configuration Parameter Settings on page 6-4

Provides more information about the ALTPLL IP core parameter settings in the Quartus II software.

• ALTPLL_RECONFIG Parameters on page 7-1

Provides more information about the ALTPLL_RECONFIG IP core parameter settings in the Quartus

II software.

Clock Switchover

The clock switchover feature allows the PLL to switch between two reference input clocks. Use this feature

for clock redundancy or for a dual-clock domain application where a system turns on the redundant clock

if the previous clock stops running. The design can perform clock switchover automatically when the

clock is no longer toggling or based on a user-controlled signal, clkswitch.

The following clock switchover modes are supported in MAX 10 PLLs:

• Automatic switchover—The clock sense circuit monitors the current reference clock. If the current

reference clock stops toggling, the reference clock automatically switches to inclk0 or inclk1 clock.

• Manual clock switchover—The clkswitch signal controls the clock switchover. When the clkswitch

signal goes from logic low to high, and stays high for at least three clock cycles, the reference clock to

the PLL switches from inclk0 to inclk1, or vice-versa.

• Automatic switchover with manual override—This mode combines automatic switchover and manual

clock switchover. When the clkswitch signal goes high, it overrides the automatic clock switchover

function. As long as the clkswitch signal is high, any further switchover action is blocked.

UG-M10CLKPLL

2015.05.04

Related Information

• Guideline: Clock Switchover on page 3-3

• Clock Switchover Parameter Settings on page 6-3

Automatic Clock Switchover

The MAX 10 PLLs support a fully configurable clock switchover capability.

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 29

Switchover

State

Machine

Clock

Sense

N Counter

PFD

clkswitch

(Provides Manual

Switchover Support)

activeclock

clkbad1

clkbad0

muxout

inclk0

inclk1

refclk

fbclk

clksw

UG-M10CLKPLL

2015.05.04

Figure 2-20: Automatic Clock Switchover Circuit Block Diagram

Automatic Clock Switchover

This figure shows a block diagram of the automatic switchover circuit built into the PLL.

2-23

When the current reference clock is not present, the clock sense block automatically switches to the

backup clock for PLL reference. You can select a clock source at the backup clock by connecting it to the

inclk1 port of the PLL in your design.

The clock switchover circuit also sends out three status signals—clkbad[0], clkbad[1], and

activeclock—from the PLL to implement a custom switchover circuit in the logic array.

In automatic switchover mode, the clkbad[0] and clkbad[1] signals indicate the status of the two clock

inputs. When the clkbad[0] and clkbad[1] signals are asserted, the clock sense block detects that the

corresponding clock input has stopped toggling. These two signals are not valid if the frequency difference

between inclk0 and inclk1 is greater than 20%.

The activeclock signal indicates which of the two clock inputs (inclk0 or inclk1) is selected as the

reference clock to the PLL. When the frequency difference between the two clock inputs is more than

20%, the activeclock signal is the only valid status signal.

Note:

Glitches in the input clock may cause the frequency difference between the input clocks to be more

than 20%.

When the current reference clock to the PLL stops toggling, use the switchover circuitry to automatically

switch from inclk0 to inclk1 that runs at the same frequency. This automatic switchover can switch

back and forth between the inclk0 and inclk1 clocks any number of times when one of the two clocks

fails and the other clock is available.

For example, in applications that require a redundant clock with the same frequency as the reference

clock, the switchover state machine generates a signal (clksw) that controls the multiplexer select input.

In this case, inclk1 becomes the reference clock for the PLL.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 30

inclk0

inclk1

muxout

clkbad0

clkbad1

(1)

activeclock

Note:

(1) Switchover is enabled on the falling edge of inclk0 or inclk1, depending on which clock is available. In this figure,

switchover is enabled on the falling edge of inclk1.

2-24

Automatic Switchover with Manual Override

When using automatic clock switchover mode, the following requirements must be satisfied:

• Both clock inputs must be running when the FPGA is configured.

• The period of the two clock inputs differ by no more than 20%.

If the current clock input stops toggling while the other clock is also not toggling, switchover is not

initiated and the clkbad[0..1] signals are not valid. If both clock inputs do not have the same frequency,

but their period difference is within 20%, the clock sense block detects when a clock stops toggling.

However, the PLL might lose lock after the switchover completes and needs time to relock.

Note: Altera recommends resetting the PLL using the areset signal to maintain the phase relationships

between the PLL input and output clocks when using clock switchover.

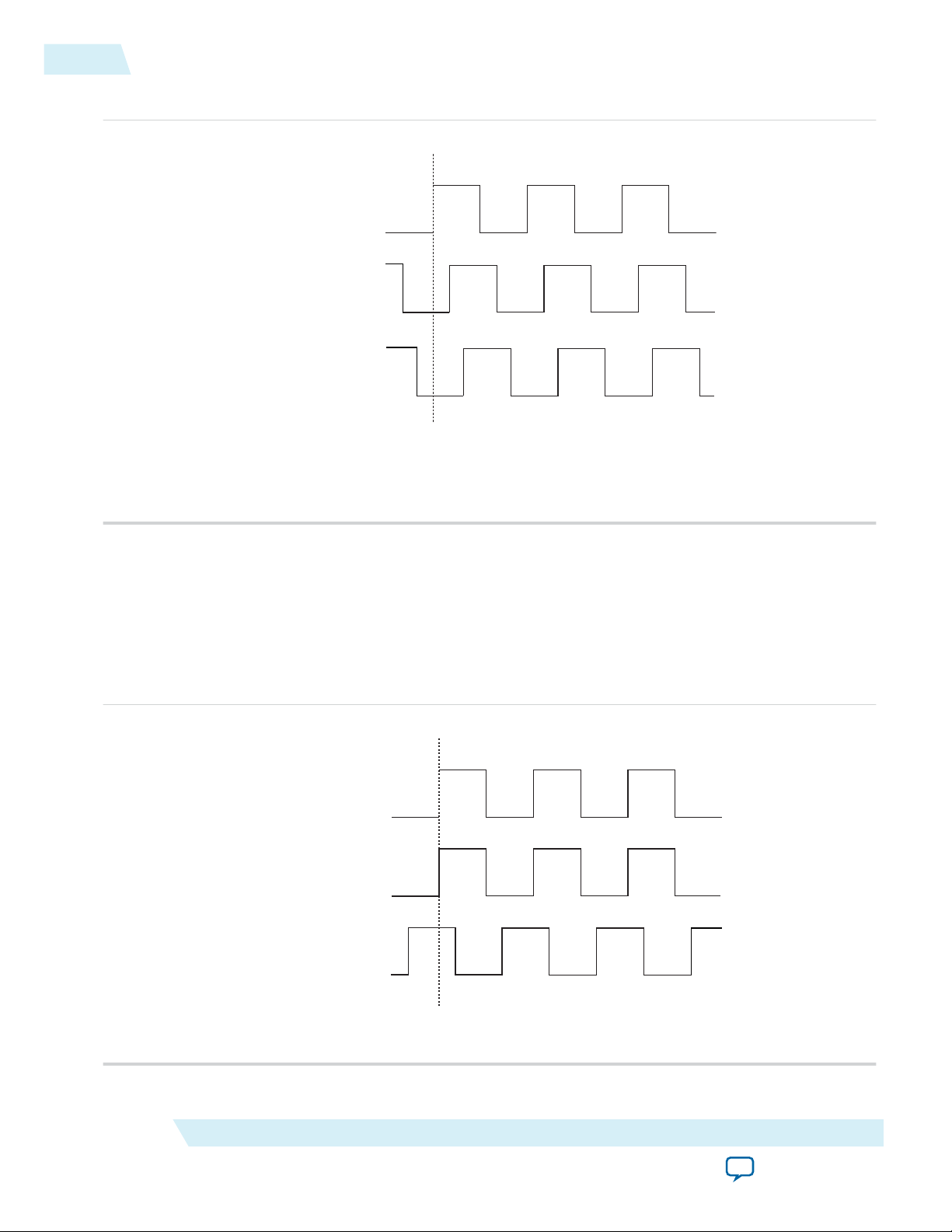

Figure 2-21: Example of Automatic Switchover After Loss of Clock Detection

This figure shows an example waveform of the switchover feature in automatic switchover mode. In this

example, the inclk0 signal remains low. After the inclk0 signal remains low for approximately two clock

cycles, the clock sense circuitry drives the clkbad[0] signal high. Since the reference clock signal is not

toggling, the switchover state machine controls the multiplexer through the clksw signal to switch to the

backup clock, inclk1.

UG-M10CLKPLL

2015.05.04

Automatic Switchover with Manual Override

In automatic switchover with manual override mode, you can use the clkswitch signal for user- or

system-controlled switch conditions. You can use this mode for same-frequency switchover, or to switch

Altera Corporation

between inputs of different frequencies.

For example, if inclk0 is 66 MHz and inclk1 is 200 MHz, you must control the switchover using the

clkswitch signal. The automatic clock sense circuitry cannot monitor clock input (inclk0 and inclk1)

frequencies with a frequency difference of more than 20%.

This feature is useful when clock sources originate from multiple cards on the backplane, requiring a

system-controlled switchover between frequencies of operation.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 31

inclk0

inclk1

muxout

clkswitch

activeclock

clkbad0

clkbad1

To initiate a manual clock switchover event,

both inclk0 and inclk1 must be running when

the clkswitch signal goes high.

UG-M10CLKPLL

2015.05.04

Manual Clock Switchover

2-25

You must choose the backup clock frequency and set the M, N, and C counters so that the VCO operates

within the recommended frequency range.

The following figure shows a clock switchover waveform controlled by the clkswitch signal. In this case,

both clock sources are functional and inclk0 is selected as the reference clock. The clkswitch signal goes

high, which starts the switchover sequence. On the falling edge of inclk0, the counter’s reference clock,

muxout, is gated off to prevent clock glitching. On the falling edge of inclk1, the reference clock

multiplexer switches from inclk0 to inclk1 as the PLL reference. The activeclock signal is asserted to

indicate the clock that is currently feeding the PLL, which is inclk1.

In automatic override with manual switchover mode, the activeclock signal mirrors the clkswitch

signal. Since both clocks are still functional during the manual switch, neither clkbad signal goes high.

Because the switchover circuit is positive-edge sensitive, the falling edge of the clkswitch signal does not

cause the circuit to switch back from inclk1 to inclk0. When the clkswitch signal goes high again, the

process repeats.

Figure 2-22: Example of Clock Switchover Using the

clkswitch signal and automatic switch work only if the clock being switched to is available. If the

The

clkswitch

clock is not available, the state machine waits until the clock is available.

(Manual) Control

Manual Clock Switchover

In manual clock switchover mode, the clkswitch signal controls whether inclk0 or inclk1 is selected as

the input clock to the PLL. By default, inclk0 is selected.

A clock switchover event is initiated when the clkswitch signal transitions from logic low to logic high,

and is being held high for at least three inclk cycles. You must bring the clkswitch signal back to low

again to perform another switchover event. If you do not require another switchover event, you can leave

the clkswitch signal in a logic high state after the initial switch. Pulsing the clkswitch signal high for at

least three inclk cycles performs another switchover event.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 32

C0

C1

C2

C3

C4

VCO Output

VCO Output

VCO Output

VCO Output

VCO Output

VCO Output

2-26

PLL Cascading

If inclk0 and inclk1 have different frequencies and are always running, the minimum amount of time

for which clkswitch signal is high must be greater than or equal to three of the slower-frequency inclk0

and inclk1 cycles.

PLL Cascading

Related Information

Guideline: PLL Cascading on page 3-3

PLL-to-PLL Cascading

Two PLLs are cascaded to each other through the clock network. If your design cascades PLLs, the source

(upstream) PLL must have a low-bandwidth setting and the destination (downstream) PLL must have a

high-bandwidth setting.

Counter-to-Counter Cascading

The MAX 10 PLLs support post-scale counter cascading to create counters larger than 512. This is

implemented by feeding the output of one C counter into the input of the next C counter.

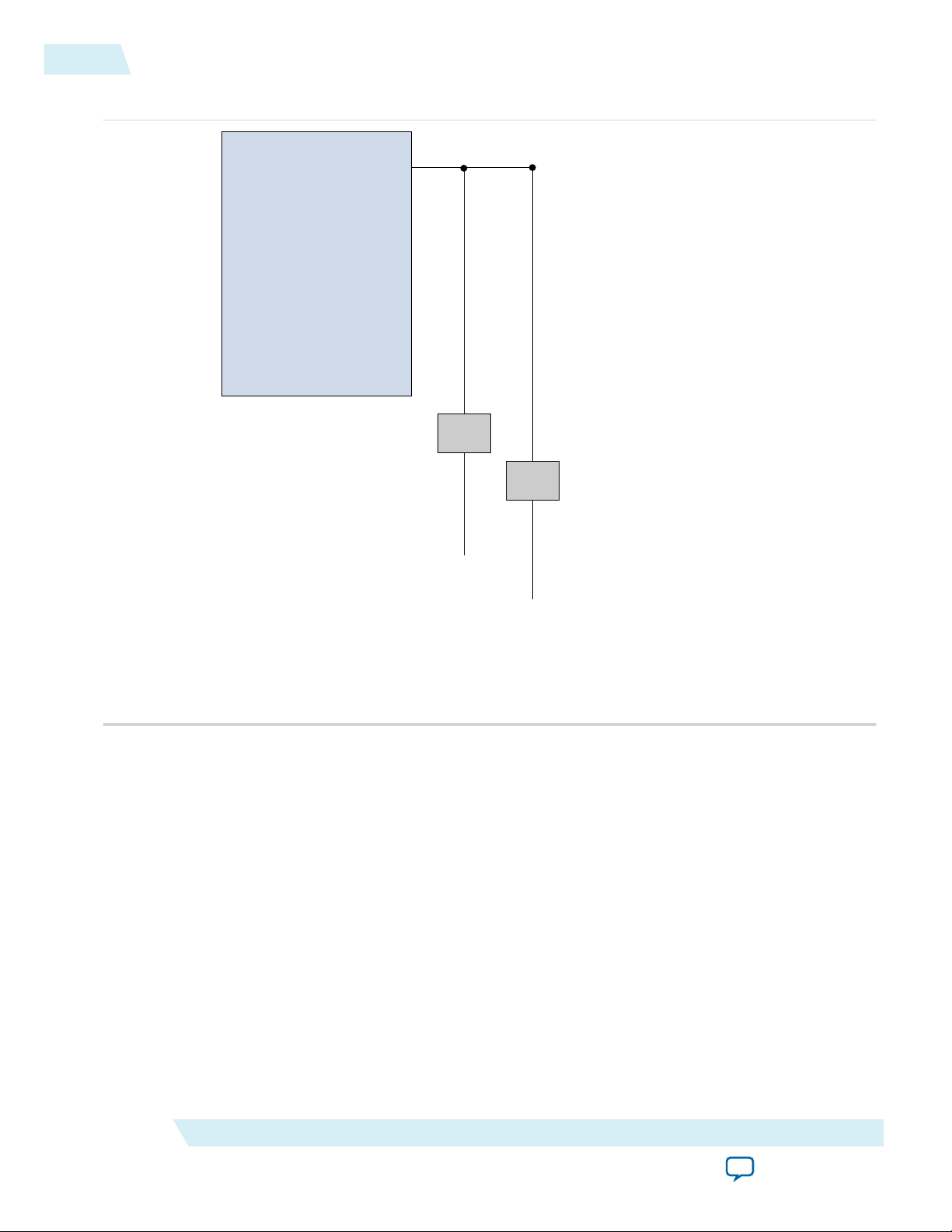

Figure 2-23: Counter-to-Counter Cascading

UG-M10CLKPLL

2015.05.04

Altera Corporation

When cascading counters to implement a larger division of the high-frequency VCO clock, the cascaded

counters behave as one counter with the product of the individual counter settings.

For example, if C0 = 4 and C1 = 2, the cascaded value is C0 x C1 = 8.

The Quartus II software automatically sets all the post-scale counter values for cascading in the configura‐

tion file. Post-scale counter cascading cannot be performed using PLL reconfiguration.

PLL Reconfiguration

The PLLs use several divide counters and different VCO phase taps to perform frequency synthesis and

phase shifts. In MAX 10 PLLs, you can reconfigure both counter settings and phase shift the PLL output

clock in real time. You can also change the charge pump and loop filter components, which dynamically

affects the PLL bandwidth.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 33

/C4 /C3 /C2 /C1 /C0 /M /N

scanclk

scandone

scandata

LF/K/CP

configupdate

inclk

PFD VCO

F

VCO

scanclkena

scandataout

from M counter

from N counter

UG-M10CLKPLL

2015.05.04

PLL Reconfiguration

2-27

The following PLL components are configurable in real time:

• Pre-scale counter (N)

• Feedback counter (M)

• Post-scale output counters (C0-C4)

• Charge pump current (ICP)

• Loop filter components (R, C)

You can use these PLL components to update the following settings in real time without reconfiguring the

entire FPGA:

• Output clock frequency

• PLL bandwidth

• Phase shift

The ability to reconfigure the PLL in real time is useful in applications that may operate in multiple

frequencies. It is also useful in prototyping environments, allowing you to sweep PLL output frequencies

and dynamically adjust the output clock phase.

For instance, a system generating test patterns is required to generate and send patterns at 75 or 150 MHz,

depending on the requirements of the device under test. Reconfiguring the PLL components in real time

allows you to switch between two such output frequencies in a few microseconds.

You can also use this feature to adjust clock-to-out (tCO) delays in real time by changing the PLL output

clock phase shift. This approach eliminates the need to regenerate a configuration file with the new PLL

settings.

Figure 2-24: PLL Reconfiguration Scan Chain

This figure shows the dynamic adjustment of the PLL counter settings by shifting their new settings into a

serial shift register chain or scan chain. Serial data shifts to the scan chain via the scandata port, and shift

registers are clocked by scanclk. The maximum scanclk frequency is 100 MHz. After shifting the last bit

of data, asserting the configupdate signal for at least one scanclk clock cycle synchronously updates the

PLL configuration bits with the data in the scan registers.

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Altera Corporation

Page 34

2-28

PLL Reconfiguration

UG-M10CLKPLL

2015.05.04

The counter settings are updated synchronously to the clock frequency of the individual counters.

Therefore, not all counters update simultaneously.

The dynamic reconfiguration scheme uses configuration files, such as the Hexadecimal-format file (.hex)

or the Memory Initialization file (.mif). These files are used together with the ALTPLL_RECONFIG IP

core to perform the dynamic reconfiguration.

Related Information

• Guideline: .mif Streaming in PLL Reconfiguration on page 3-4

• PLL Dynamic Reconfiguration Implementation on page 4-10

• PLL Dynamic Reconfiguration Parameter Settings on page 6-4

Provides more information about the ALTPLL IP core parameter settings in the Quartus II software.

• ALTPLL_RECONFIG Parameters on page 7-1

Provides more information about the ALTPLL_RECONFIG IP core parameter settings in the Quartus

II software.

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features

Send Feedback

Page 35

MAX 10 Clocking and PLL Design

www.altera.com

101 Innovation Drive, San Jose, CA 95134

2015.05.04

UG-M10CLKPLL

Subscribe

Send Feedback

Clock Networks Design Considerations

Guideline: Clock Enable Signals

Altera recommends using the clkena signals when switching the clock source to the PLLs or GCLK. The

recommended sequence is as follows:

1. Disable the primary output clock by deasserting the clkena signal.

2. Switch to the secondary clock using the dynamic select signals of the clock control block.

3. Allow some clock cycles of the secondary clock to pass before reasserting the clkena signal. The exact

number of clock cycles to wait before enabling the secondary clock depends on your design. You can

build a custom logic to ensure a glitch-free transition when switching between different clock sources.

Related Information

• Clock Enable Signals on page 2-7

• ALTCLKCTRL Parameters on page 5-1

• ALTCLKCTRL Ports and Signals on page 5-2

Considerations

3

Guideline: Connectivity Restrictions

The following guidelines describe the restrictions associated with the signal sources that can drive the

inclk input:

• You must use the inclk ports that are consistent with the clkselect ports.

• When you are using multiple input sources, the inclk ports can only be driven by the dedicated clock

input pins and the PLL clock outputs.

• If the clock control block feeds any inclk port of another clock control block, both clock control

blocks must be able to be reduced to a single clock control block of equivalent functionality.

• When you are using the glitch-free switchover feature, the clock you are switching from must be active.

If the clock is not active, the switchover circuit cannot transition from the clock you originally selected.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 36

3-2

Internal Oscillator Design Considerations

Internal Oscillator Design Considerations

Guideline: Connectivity Restrictions

You cannot drive the PLLs with internal oscillator.

PLLs Design Considerations

Guideline: PLL Control Signals

You must include the areset signal in your designs if one of the following conditions is true:

• PLL reconfiguration or clock switchover is enabled in your design.

• Phase relationships between the PLL input clock and output clocks must be maintained after a loss-oflock condition.

• The input clock to the PLL is toggling or unstable at power-up.

• The areset signal is asserted after the input clock is stable and within specifications.

Related Information

PLL Control Signals on page 2-13

UG-M10CLKPLL

2015.05.04

Guideline: Self-Reset

The lock time of a PLL is the amount of time required by the PLL to attain the target frequency and phase

relationship after device power-up, after a change in the PLL output frequency, or after resetting the PLL.

A PLL might lose lock for a number of reasons, such as the following causes:

• Excessive jitter on the input clock.

• Excessive switching noise on the clock inputs of the PLL.

• Excessive noise from the power supply, causing high output jitter and possible loss of lock.

• A glitch or stopping of the input clock to the PLL.

• Resetting the PLL by asserting the areset port of the PLL.

• An attempt to reconfigure the PLL might cause the M counter, N counter, or phase shift to change,

causing the PLL to lose lock. However, changes to the post-scale counters do not affect the PLL locked

signal.

• PLL input clock frequency drifts outside the lock range specification.

• The PFD is disabled using the pfdena port. When this happens, the PLL output phase and frequency

tend to drift outside of the lock window.

The ALTPLL IP core allows you to monitor the PLL locking process using a lock signal named locked

and also allows you to set the PLL to self-reset on loss of lock.

Guideline: Output Clocks

Each MAX 10 PLL supports up to five output clocks. You can use the output clock port as a core output

clock or an external output clock port. The core output clock feeds the FPGA core and the external output

clock feeds the dedicated pins on the FPGA.

Altera Corporation

MAX 10 Clocking and PLL Design Considerations

Send Feedback

Page 37

UG-M10CLKPLL

2015.05.04

The ALTPLL IP core does not have a dedicated output enable port. You can disable the PLL output using

the areset signal to disable the PLL output counters.

Guideline: PLL Cascading

Consider the following guidelines when cascading PLLs:

• Set the primary PLL to low bandwidth to help filter jitter. Set the secondary PLL to high bandwidth to

track the jitter from the primary PLL. You can view the Quartus II software compilation report file to

ensure the PLL bandwidth ranges do not overlap. If the bandwidth ranges overlap, jitter peaking can

occur in the cascaded PLL scheme.

Note: You can get an estimate of the PLL deterministic jitter and static phase error (SPE) by using the

TimeQuest Timing Analyzer in the Quartus II software. Use the SDC command

derive_clock_uncertainty to generate a report titled PLLJ_PLLSPE_INFO.txt in your

project directory. Then, use set_clock_uncertainty command to add jitter and SPE

values to your clock constraints.

• Keep the secondary PLL in a reset state until the primary PLL has locked to ensure the phase settings

are correct on the secondary PLL.

• You cannot connect any of the inclk ports of any PLLs in a cascaded scheme to the clock outputs

from PLLs in the cascaded scheme.

Guideline: PLL Cascading

3-3

Related Information

PLL Cascading on page 2-26

Guideline: Clock Switchover

Use the following guidelines to design with clock switchover in PLLs:

• Clock loss detection and automatic clock switchover requires that the frequency difference between

inclk0 and inclk1 is within 20% range. Failing to meet this requirement causes the clkbad[0] and

clkbad[1] signals to function improperly.

• When using manual clock switchover, the frequency difference between inclk0 and inclk1 can be

more than 20%. However, differences between the two clock sources (frequency, phase, or both) can

cause the PLL to lose lock. Resetting the PLL ensures that the correct phase relationships are

maintained between the input and output clocks.

• Both inclk0 and inclk1 must be running when the clkswitch signal goes high to start the manual

clock switchover event. Failing to meet this requirement causes the clock switchover to malfunction.

• Applications that require a clock switchover feature and a small frequency drift must use a lowbandwidth PLL. When referencing input clock changes, the low-bandwidth PLL reacts slower than a

high-bandwidth PLL. When the switchover happens, the low-bandwidth PLL propagates the stoppage

of the clock to the output at a slower speed than the high-bandwidth PLL. The low-bandwidth PLL

filters out jitter on the reference clock. However, be aware that the low-bandwidth PLL also increases

lock time.

• After a switchover occurs, there might be a finite resynchronization period for the PLL to lock onto a

new clock. The exact amount of time it takes for the PLL to relock depends on the PLL configuration.

MAX 10 Clocking and PLL Design Considerations

Send Feedback

Altera Corporation

Page 38

ΔF

vco

Primary Clock Stops Running

Switchover Occurs

VCO Tracks Secondary Clock

Frequency Overshoot

3-4

Guideline: .mif Streaming in PLL Reconfiguration

• The phase relationship between the input clock to the PLL and output clock from the PLL is important

in your design. Assert areset for 10 ns after performing a clock switchover. Wait for the locked signal

(or gated lock) to go high before reenabling the output clocks from the PLL.

• Disable the system during switchover if the system is not tolerant of frequency variations during the

PLL resynchronization period. You can use the clkbad[0] and clkbad[1] status signals to turn off the

PFD (pfdena = 0) so that the VCO maintains its last frequency. You can also use the switchover state

machine to switch over to the secondary clock. After enabling the PFD, the output clock enable signals

(clkena) can disable clock outputs during the switchover and resynchronization period. After the lock

indication is stable, the system can reenable the output clock or clocks.

• The VCO frequency gradually decreases when the primary clock is lost and then increases as the VCO

locks onto the secondary clock, as shown in the following figure. After the VCO locks onto the

secondary clock, some overshoot can occur (an over-frequency condition) in the VCO frequency.

Figure 3-1: VCO Switchover Operating Frequency

UG-M10CLKPLL

2015.05.04

Related Information

• Clock Switchover on page 2-22

• Clock Switchover Parameter Settings on page 6-3

Guideline: .mif Streaming in PLL Reconfiguration

Consider the following guidelines when using .mif streaming in PLL reconfiguration:

• 10M02 devices do not support .mif streaming in PLL reconfiguration due to flash size limitation. Altera

recommends using an external flash.

• 10M04, 10M08, 10M16, 10M25, 10M40, and 10M50 devices only support .mif streaming in single

image mode. Altera recommends using an external flash for dual image mode. The MAX 10 devices do

not support using both dual image mode and PLL reconfiguration with .mif simultaneously.

Related Information

PLL Reconfiguration on page 2-26

Guideline: scandone Signal for PLL Reconfiguration

scandone signal must be low before the second PLL reconfiguration. For scandone signal to go low, PLL

areset signal must be asserted.

Altera Corporation

MAX 10 Clocking and PLL Design Considerations

Send Feedback

Page 39

MAX 10 Clocking and PLL Implementation

www.altera.com

101 Innovation Drive, San Jose, CA 95134

2015.05.04