Page 1

JESD204B IP Core User Guide

Last updated for Altera Complete Design Suite: 15.0

Subscribe

Send Feedback

UG-01142

2015.05.04

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

JESD204B IP Core User Guide

Contents

JESD204B IP Core Quick Reference...................................................................1-1

About the JESD204B IP Core..............................................................................2-1

Getting Started.................................................................................................... 3-1

Datapath Modes...........................................................................................................................................2-3

IP Core Variation.........................................................................................................................................2-3

JESD204B IP Core Configuration..............................................................................................................2-4

Run-Time Configuration................................................................................................................2-4

Channel Bonding......................................................................................................................................... 2-5

Performance and Resource Utilization.....................................................................................................2-6

Introduction to Altera IP Cores.................................................................................................................3-1

Installing and Licensing IP Cores..............................................................................................................3-2

Upgrading IP Cores.....................................................................................................................................3-2

IP Catalog and Parameter Editor...............................................................................................................3-5

Design Walkthrough................................................................................................................................... 3-6

Creating a New Quartus II Project................................................................................................3-6

Parameterizing and Generating the IP Core................................................................................3-7

Generating and Simulating the IP Core Testbench.................................................................... 3-8

Compiling the JESD204B IP Core Design..................................................................................3-10

Programming an FPGA Device................................................................................................... 3-11

JESD204B IP Core Design Considerations............................................................................................ 3-11

Integrating the JESD204B IP core in Qsys................................................................................. 3-11

Pin Assignments.............................................................................................................................3-12

Adding External Transceiver PLL............................................................................................... 3-13

Timing Constraints For Input Clocks.........................................................................................3-13

JESD204B IP Core Parameters.................................................................................................................3-16

JESD204B IP Core Component Files......................................................................................................3-21

JESD204B IP Core Testbench.................................................................................................................. 3-21

Testbench Simulation Flow..........................................................................................................3-23

JESD204B IP Core Functional Description........................................................4-1

Altera Corporation

Transmitter...................................................................................................................................................4-4

TX Data Link Layer..........................................................................................................................4-5

TX PHY Layer.................................................................................................................................. 4-8

Receiver......................................................................................................................................................... 4-8

RX Data Link Layer..........................................................................................................................4-9

RX PHY Layer................................................................................................................................ 4-12

Operation....................................................................................................................................................4-13

Operating Modes........................................................................................................................... 4-13

Page 3

JESD204B IP Core User Guide

Scrambler/Descrambler................................................................................................................ 4-14

SYNC_N Signal..............................................................................................................................4-14

Link Reinitialization......................................................................................................................4-16

Link Startup Sequence...................................................................................................................4-17

Error Reporting Through SYNC_N Signal................................................................................4-18

Clocking Scheme........................................................................................................................................4-18

Device Clock...................................................................................................................................4-20

Link Clock.......................................................................................................................................4-21

Local Multi-Frame Clock..............................................................................................................4-22

Clock Correlation...........................................................................................................................4-23

Reset Scheme.............................................................................................................................................. 4-24

Reset Sequence............................................................................................................................... 4-25

Signals..........................................................................................................................................................4-26

Transmitter.....................................................................................................................................4-27

Receiver........................................................................................................................................... 4-36

Registers...................................................................................................................................................... 4-43

Register Access Type Convention............................................................................................... 4-43

TOC-3

JESD204B IP Core Design Guidelines................................................................5-1

JESD204B IP Core Design Example..........................................................................................................5-1

Design Example Components........................................................................................................5-3

System Parameters.........................................................................................................................5-40

System Interface Signals................................................................................................................5-44

Example Feature: Dynamic Reconfiguration.............................................................................5-49

Generating and Simulating the Design Example.......................................................................5-55

Generating the Design Example For Compilation....................................................................5-56

Compiling the JESD204B IP Core Design Example................................................................. 5-57

JESD204B IP Core Deterministic Latency Implementation Guidelines........... 6-1

Constraining Incoming SYSREF Signal....................................................................................................6-1

Programmable RBD Offset.........................................................................................................................6-2

Programmable LMFC Offset......................................................................................................................6-5

JESD204B IP Core Debug Guidelines.................................................................7-1

Clocking Scheme..........................................................................................................................................7-1

JESD204B Parameters................................................................................................................................. 7-1

SPI Programming.........................................................................................................................................7-2

Converter and FPGA Operating Conditions...........................................................................................7-2

Signal Polarity and FPGA Pin Assignment..............................................................................................7-2

Debugging JESD204B Link Using SignalTap II and System Console..................................................7-3

Additional Information...................................................................................... 8-1

JESD204B IP Core Document Revision History..................................................................................... 8-1

How to Contact Altera................................................................................................................................ 8-3

Altera Corporation

Page 4

2015.05.04

www.altera.com

101 Innovation Drive, San Jose, CA 95134

JESD204B IP Core Quick Reference

1

UG-01142

Subscribe

Send Feedback

The Altera® JESD204B MegaCore® function is a high-speed point-to-point serial interface intellectual

property (IP).

The JESD204B MegaCore function is part of the MegaCore IP Library, which is distributed with the

Quartus® II software and downloadable from the Altera website at www.altera.com.

Note:

For system requirements and installation instructions, refer to Altera Software Installation &

Licensing.

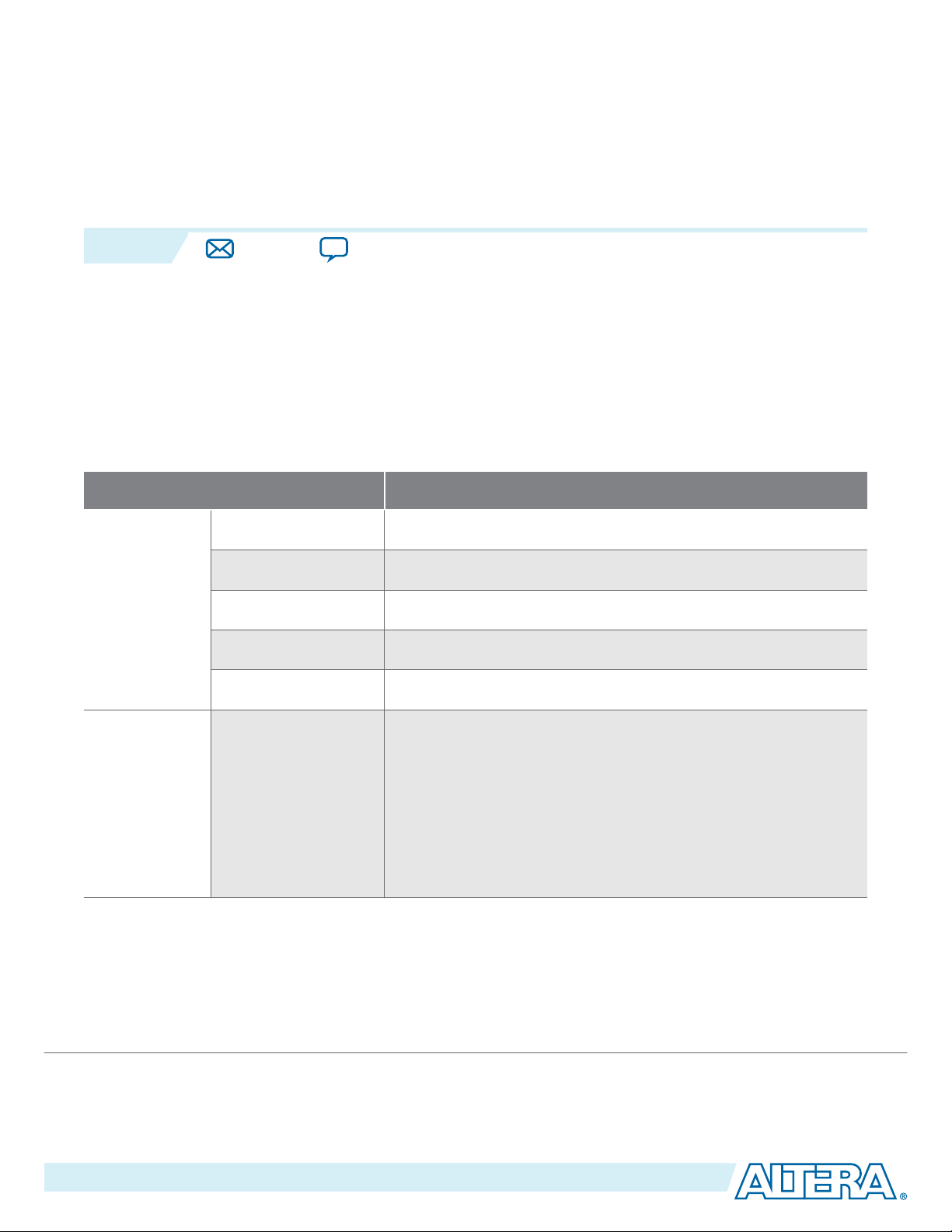

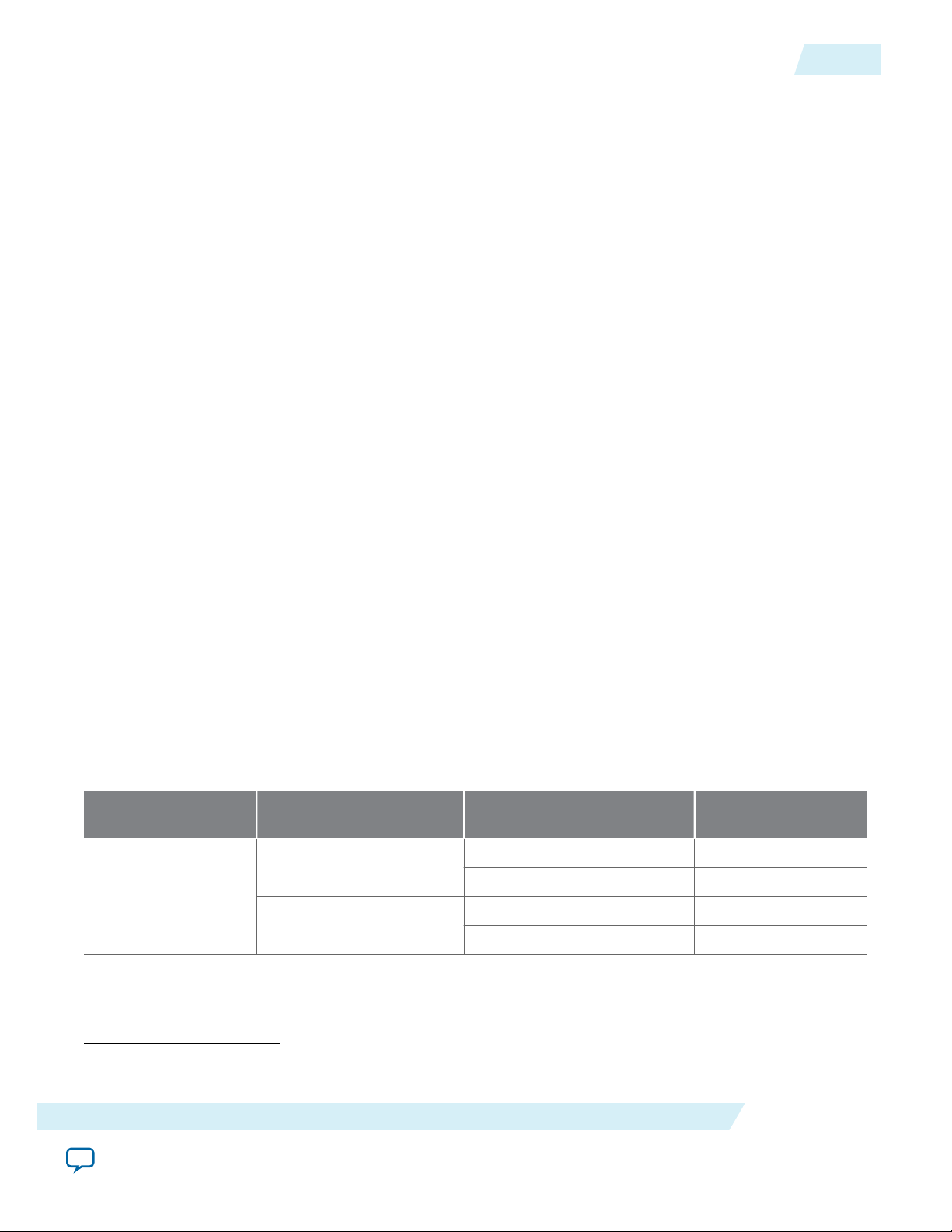

Table 1-1: Brief Information About the JESD204B MegaCore Function

Item Description

Version 15.0

Release Date May 2015

Release

Information

Ordering Code IP-JESD204B

Product ID 0116

Vendor ID 6AF7

• Joint Electron Device Engineering Council (JEDEC)

JESD204B.01, 2012 standard release specification

• Device subclass:

IP Core

Information

Protocol Features

• Subclass 0—Backwards compatible to JESD204A.

• Subclass 1—Uses SYSREF signal to support deterministic

latency.

• Subclass 2—Uses SYNC_N detection to support determin‐

istic latency.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 5

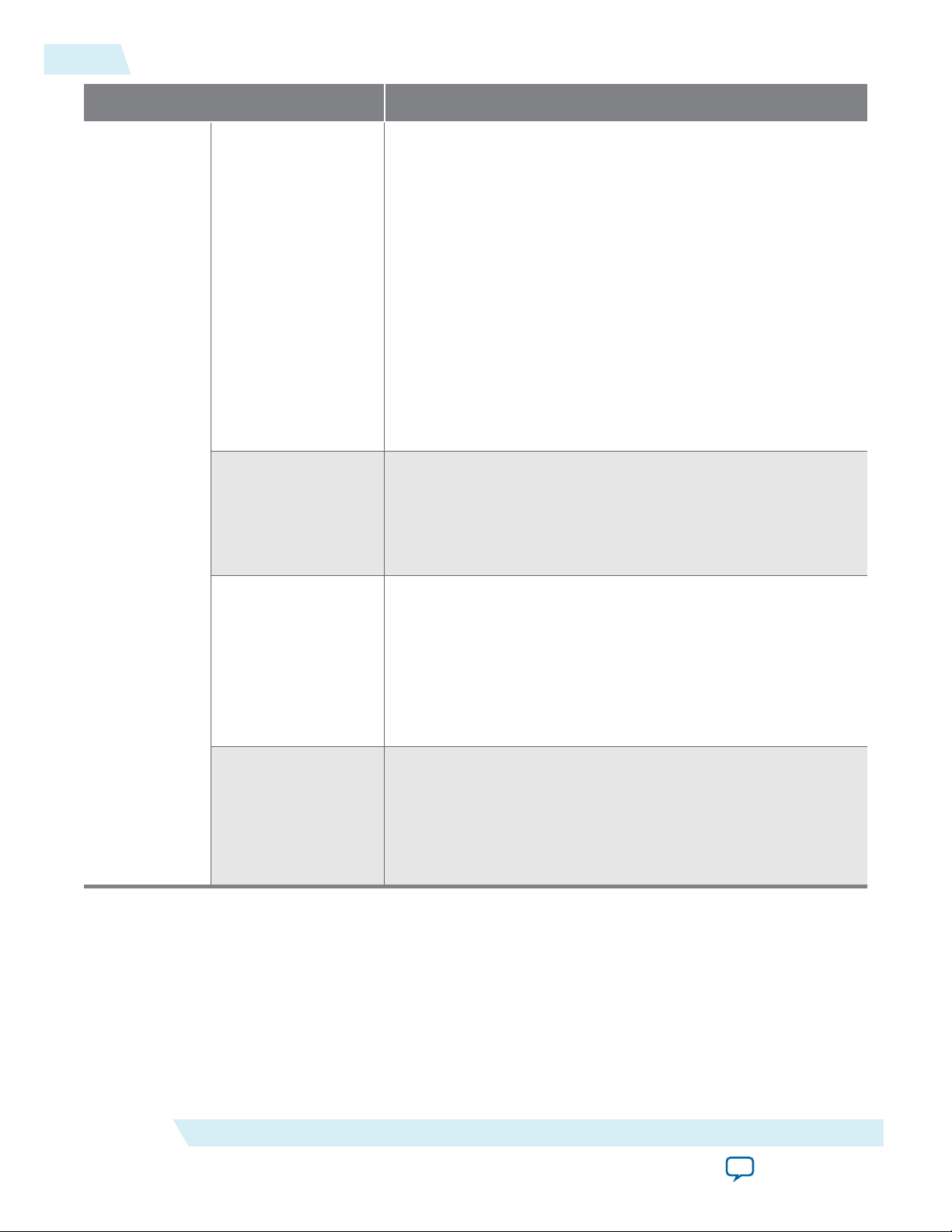

1-2

IP Core

Information

JESD204B IP Core Quick Reference

Item Description

Core Features • Run-time configuration of parameters L,M, and F

Typical Application • Wireless communication equipment

UG-01142

2015.05.04

• Data rates up to 12.5 gigabits per second (Gbps)

• Single or multiple lanes (up to 8 lanes per link)

• Serial lane alignment and monitoring

• Lane synchronization

• Modular design that supports multidevice synchronization

• MAC and PHY partitioning

• Deterministic latency support

• 8B/10B encoding

• Scrambling/Descrambling

• Avalon® Streaming (Avalon-ST) interface for transmit and

receive datapaths

• Avalon Memory-Mapped (Avalon-MM) interface for

Configuration and Status registers (CSR)

• Dynamic generation of simulation testbench

• Broadcast equipment

• Military equipment

• Medical equipment

• Test and measurement equipment

Device Family Support • Cyclone® V FPGA device families

• Arria® V FPGA device families

• Arria V GZ FPGA device families

• Arria 10 FPGA device families

• Stratix® V FPGA device families

Refer to the device support table andWhat’s New in Altera IP

page of the Altera website for detailed information.

Design Tools • Qsys parameter editor in the Quartus II software for design

creation and compilation

• TimeQuest timing analyzer in the Quartus II software for

timing analysis

• ModelSim®-Altera, Aldec Riviera-Pro, VCS/VCS MX, and

NCSim software for design simulation or synthesis

Related Information

• Altera Software Installation and Licensing

• What's New in Altera IP

Altera Corporation

JESD204B IP Core Quick Reference

Send Feedback

Page 6

2015.05.04

www.altera.com

101 Innovation Drive, San Jose, CA 95134

About the JESD204B IP Core

2

UG-01142

Subscribe

Send Feedback

The Altera JESD204B IP core is a high-speed point-to-point serial interface for digital-to-analog (DAC) or

analog-to-digital (ADC) converters to transfer data to FPGA devices. This unidirectional serial interface

runs at a maximum data rate of 12.5 Gbps. This protocol offers higher bandwidth, low I/O count and

supports scalability in both number of lanes and data rates. The JESD204B IP core addresses multi-device

synchronization by introducing Subclass 1 and Subclass 2 to achieve deterministic latency.

The JESD204B IP core incorporates:

• Media access control (MAC)—data link layer (DLL) block that controls the link states and character

replacement.

• Physical layer (PHY)—physical coding sublayer (PCS) and physical media attachment (PMA) block.

The JESD204B IP core does not incorporate the Transport Layer (TL) that controls the frame assembly

and disassembly. The TL and test components are provided as part of a design example component where

you can customize the design for different converter devices.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 7

JESD204B TX

IP Core

FPGA

M Converters

1 Link, L Lanes

SYNC_N

M Converters

M Converters

SYNC_N

SYNC_N

M Converters

SYNC_N

JESD204B RX

IP Core

1 Link, L Lanes

1 Link, L Lanes

1 Link, L Lanes

DAC Device

Clock 1

ADC Device

Clock 1

Multi-Device

Synchronization

through Subclass 1

or Subclass 2

Multi-Device

Synchronization

through Subclass 1

or Subclass 2

Logic Device (TX)

Device Clock 2

Logic Device (RX)

Device Clock 2

JESD204B TX

IP Core

JESD204B RX

IP Core

2-2

About the JESD204B IP Core

Figure 2-1: Typical System Application for JESD204B IP Core

The JESD204B IP core utilizes the Avalon-ST source and sink interfaces, with unidirectional flow of data,

to transmit and receive data on the FPGA fabric interface.

UG-01142

2015.05.04

Key features of the JESD204B IP core:

• Data rate of up to 12.5 Gbps

• Run-time JESD204B parameter configuration (L, M, F, S, N, K, CS, CF)

• MAC and PHY partitioning for portability

• Subclass 0 mode for backward compatibility to JESD204A

• Subclass 1 mode for deterministic latency support (using SYSREF) between the ADC/DAC and logic

• Subclass 2 mode for deterministic latency support (using SYNC_N) between the ADC/DAC and logic

Altera Corporation

• Multi-device synchronization

device

device

About the JESD204B IP Core

Send Feedback

Page 8

UG-01142

2015.05.04

Datapath Modes

The JESD204B IP core supports TX-only, RX-only, and Duplex (TX and RX) mode. The IP core is a

unidirectional protocol where interfacing to ADC utilizes the transceiver RX path and interfacing to DAC

utilizes the transceiver TX path.

The JESD204B IP core generates a single link with a single lane and up to a maximum of 8 lanes. If there

are two ADC links that need to be synchronized, you have to generate two JESD204B IP cores and then

manage the deterministic latency and synchronization signals, like SYSREF and SYNC_N, at your custom

wrapper level.

The JESD204B IP core supports duplex mode only if the LMF configuration for ADC (RX) is the same as

DAC (TX) and with the same data rate. This use case is mainly for prototyping with internal serial

loopback mode. This is because typically as a unidirectional protocol, the LMF configuration of converter

devices for both DAC and ADC are not identical.

IP Core Variation

The JESD204B IP core has three core variations:

Datapath Modes

2-3

• JESD204B MAC only

• JESD204B PHY only

• JESD204B MAC and PHY

In a subsystem where there are multiple ADC and DAC converters, you need to use the Quartus II

software to merge the transceivers and group them into the transceiver architecture. For example, to

create two instances of the JESD204B TX IP core with four lanes each and four instances of the JESD204

RX IP core with two lanes each, you can apply one of the following options:

• MAC and PHY option

1. Generate JESD204B TX IP core with four lanes and JESD204B RX IP core with two lanes.

2. Instantiate the desired components.

3. Use the Quartus II software to merge the PHY lanes.

• MAC only and PHY only option—based on the configuration above, there are a total of eight lanes in

duplex mode.

1. Generate the JESD204B Duplex PHY with a total of eight lanes. (TX skew is reduced in this

configuration as the channels are bonded).

2. Generate the JESD204B TX MAC with four lanes and instantiate it two times.

3. Generate the JESD204B RX MAC with two lanes and instantiate it four times.

4. Create a wrapper to connect the JESD204B TX MAC and RX MAC with the JESD204B Duplex

PHY.

Note:

If the data rate for TX and RX is different, the transceiver does not allow duplex mode to generate a

duplex PHY. In this case, you have to generate a RX-only PHY on the RX data rate and a TX-only

PHY on the TX data rate.

About the JESD204B IP Core

Send Feedback

Altera Corporation

Page 9

2-4

JESD204B IP Core Configuration

JESD204B IP Core Configuration

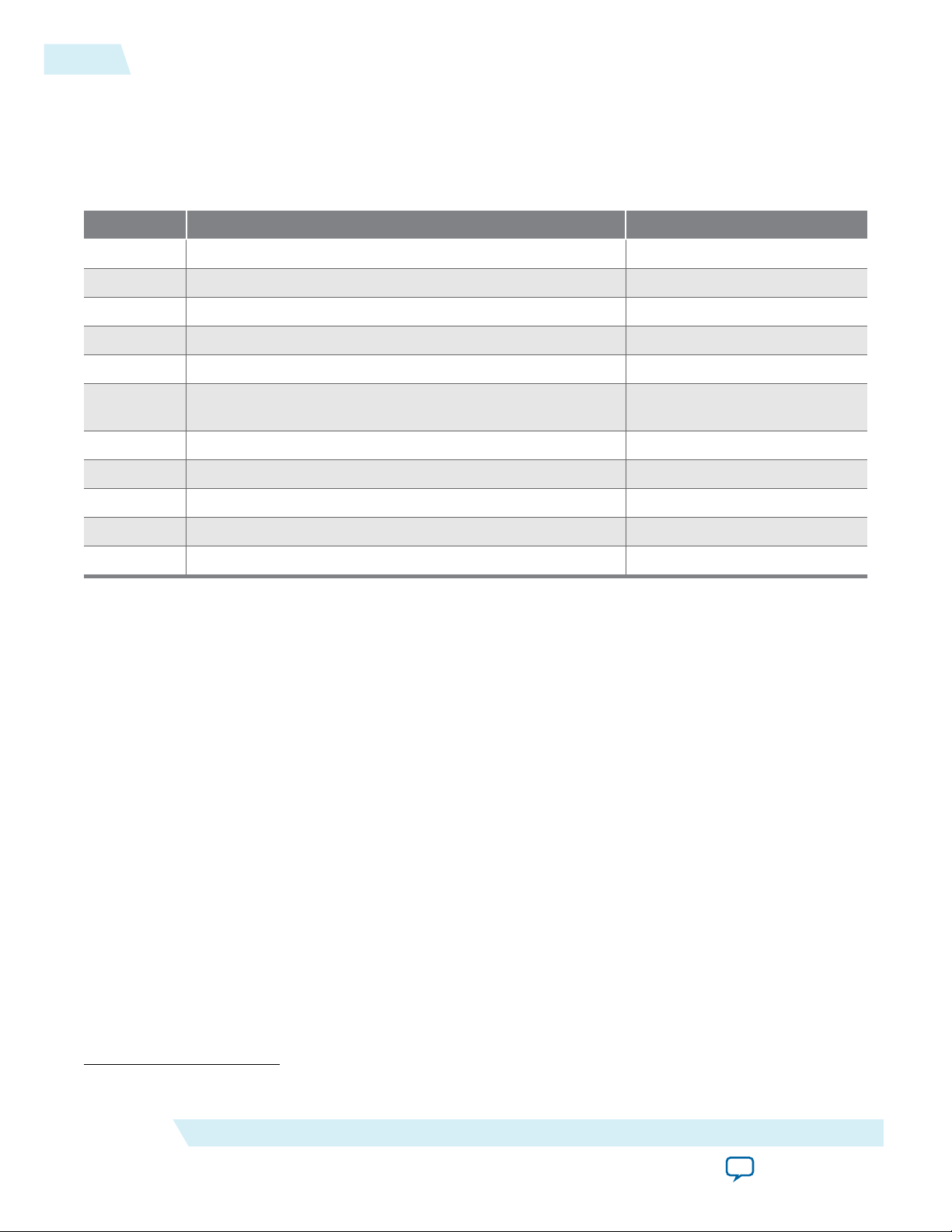

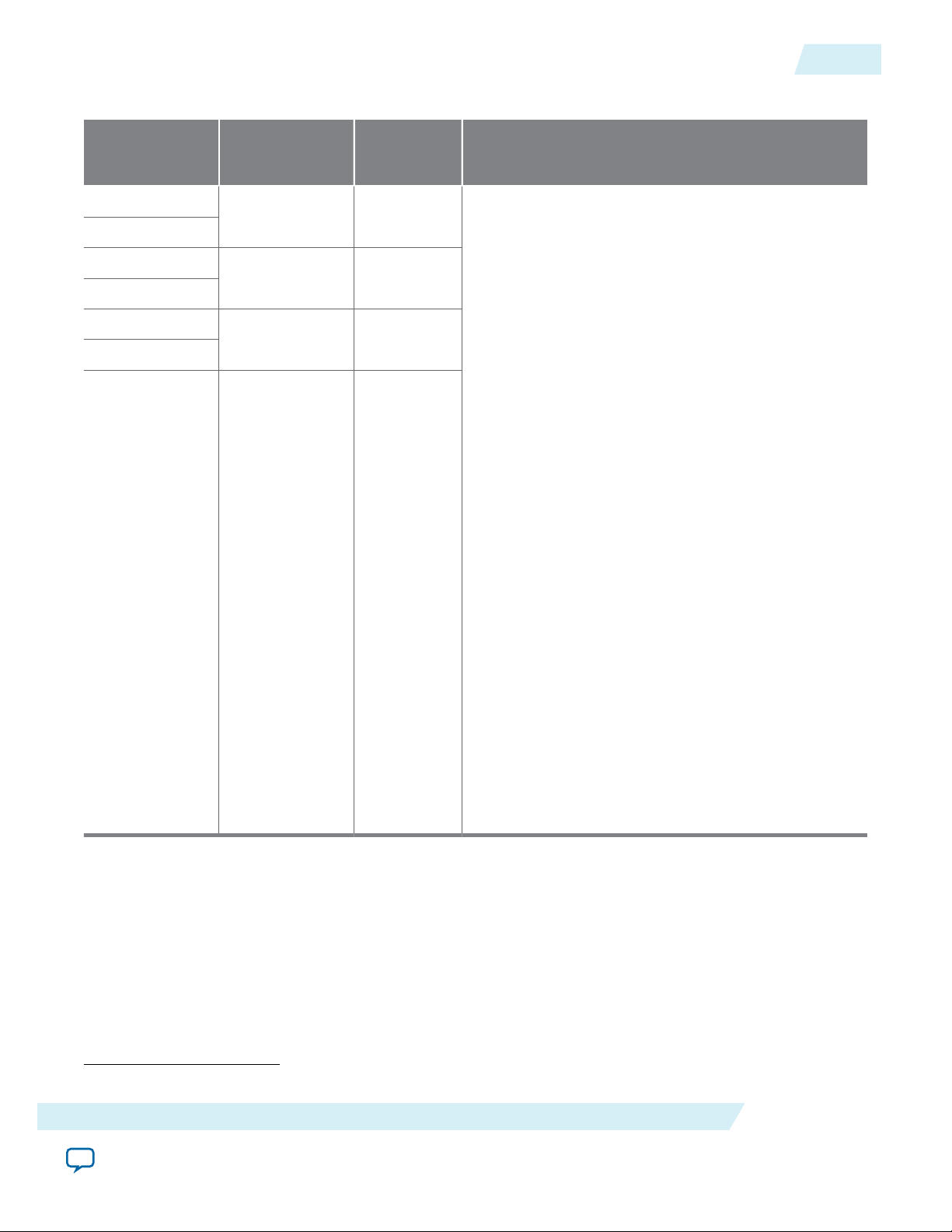

Table 2-1: JESD204B IP Core Configuration

Symbol Description Value

L Number of lanes per converter device 1-8

M Number of converters per device 1-256

F Number of octets per frame 1, 2, 4-256

S Number of transmitted samples per converter per frame 1-32

N Number of conversion bits per converter 1-32

UG-01142

2015.05.04

N' Number of transmitted bits per sample (JESD204 word size,

1-32

which is in nibble group)

K Number of frames per multiframe 17/F ≤ K ≤ 32 ; 1-32

CS Number of control bits per conversion sample 0-3

CF Number of control words per frame clock period per link 0-32

HD High Density user data format 0 or 1

LMFC Local multiframe clock (F × K /4) link clock counts

Run-Time Configuration

The JESD204B IP core allows run-time configuration of LMF parameters.

The most critical parameters that must be set correctly during IP generation are the L and F parameters.

Parameter L denotes the maximum lanes supported while parameter F denotes the size of the deskew

buffer needed for deterministic latency. The hardware generates during parameterization, which means

that run-time programmability can only fall back from the parameterized and generated hardware, but

not beyond the parameterized IP core.

You can use run-time configuration for prototyping or evaluating the performance of converter devices

with various LMF configurations. However, in actual production,Altera recommends that you generate

the JESD204B IP core with the intended LMF to get an optimized gate count.

For example, if a converter device supports LMF = 442 and LMF = 222, to check the performance for both

configurations, you need to generate the JESD204B IP core with maximum F and L, which is L = 4 and F

= 2. During operation, you can use the fall back configuration to disable the lanes that are not used in

LMF = 222 mode. You must ensure that other JESD204B configurations like M, N, S, CS, CF, and HD do

not violate the parameter F setting. You can access the Configuration and Status Register (CSR) space to

modify other configurations such as:

(1)

• K (multi-frame)

• device and lane IDs

• enable or disable scrambler

• enable or disable character replacement

(1)

The value of F x K must be divisible by 4.

Altera Corporation

About the JESD204B IP Core

Send Feedback

Page 10

UG-01142

2015.05.04

F Parameter

This parameter indicates how many octets per frame per lane that the JESD204B link is operating in. You

must set the F parameter according to the JESD204B IP Specification for a correct data mapping.

To support the High Density (HD) data format, the JESD204B IP core tracks the start of frame and end of

frame because F can be either an odd or even number. The start of frame and start of multi-frame wrap

around the 32-bits data width architecture. The RX IP core outputs the start of frame (sof[3:0]) and

start of multiframe (somf[3:0]), which act as markers, using the Avalon-ST data stream. Based on these

markers, the transport layer build the frames.

In a simpler system where the HD data format is set to 0, the F will always be 1, 2, 4, 6, 8, and so forth.

This simplifies the transport layer design, so you do not need to use the sof[3:0] and somf[3:0]

markers.

Channel Bonding

The JESD204B IP core supports channel bonding—bonded and non-bonded modes.

The channel bonding mode that you select may contribute to the transmitter channel-to-channel skew. A

bonded transmitter datapath clocking provides low channel-to-channel skew as compared to non-bonded

channel configurations.

Channel Bonding

2-5

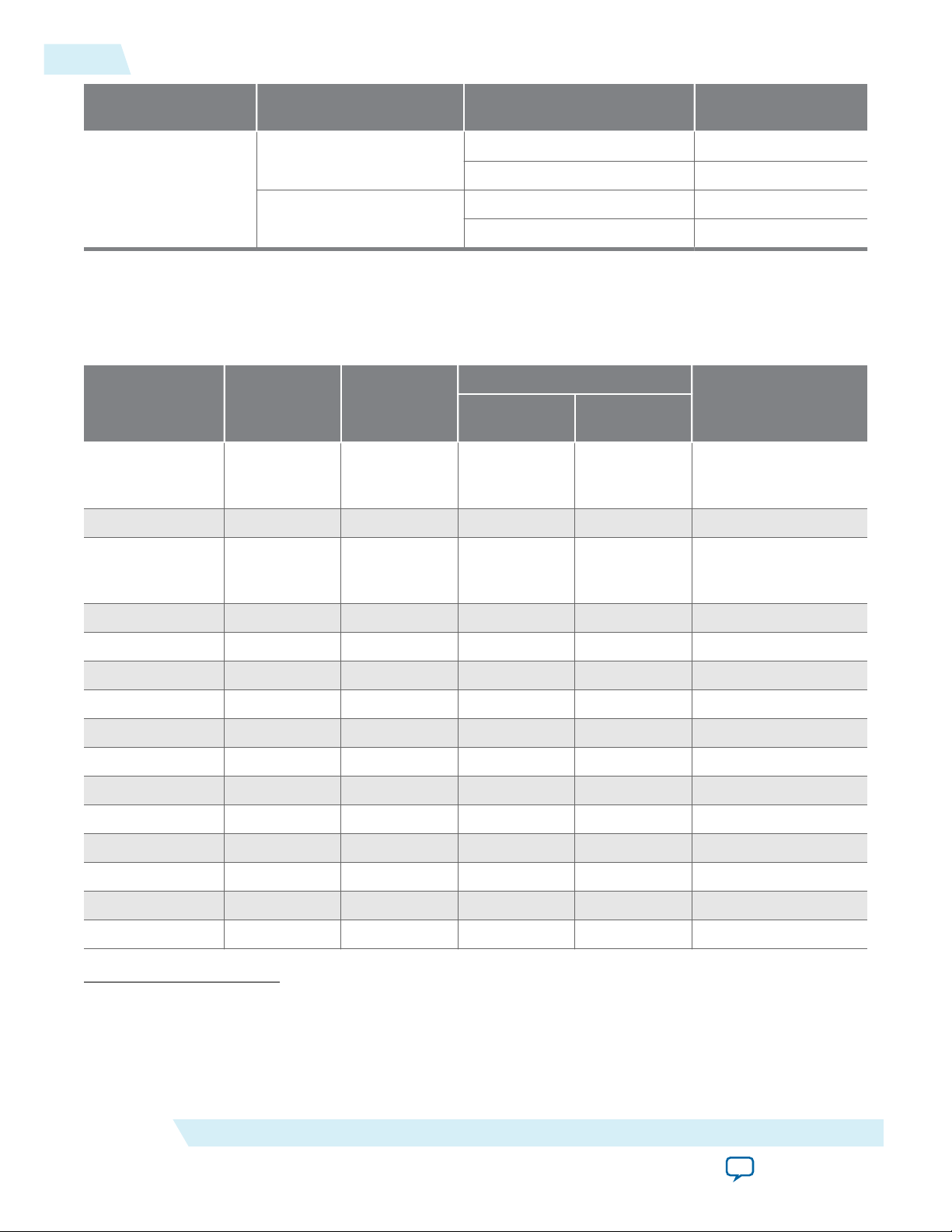

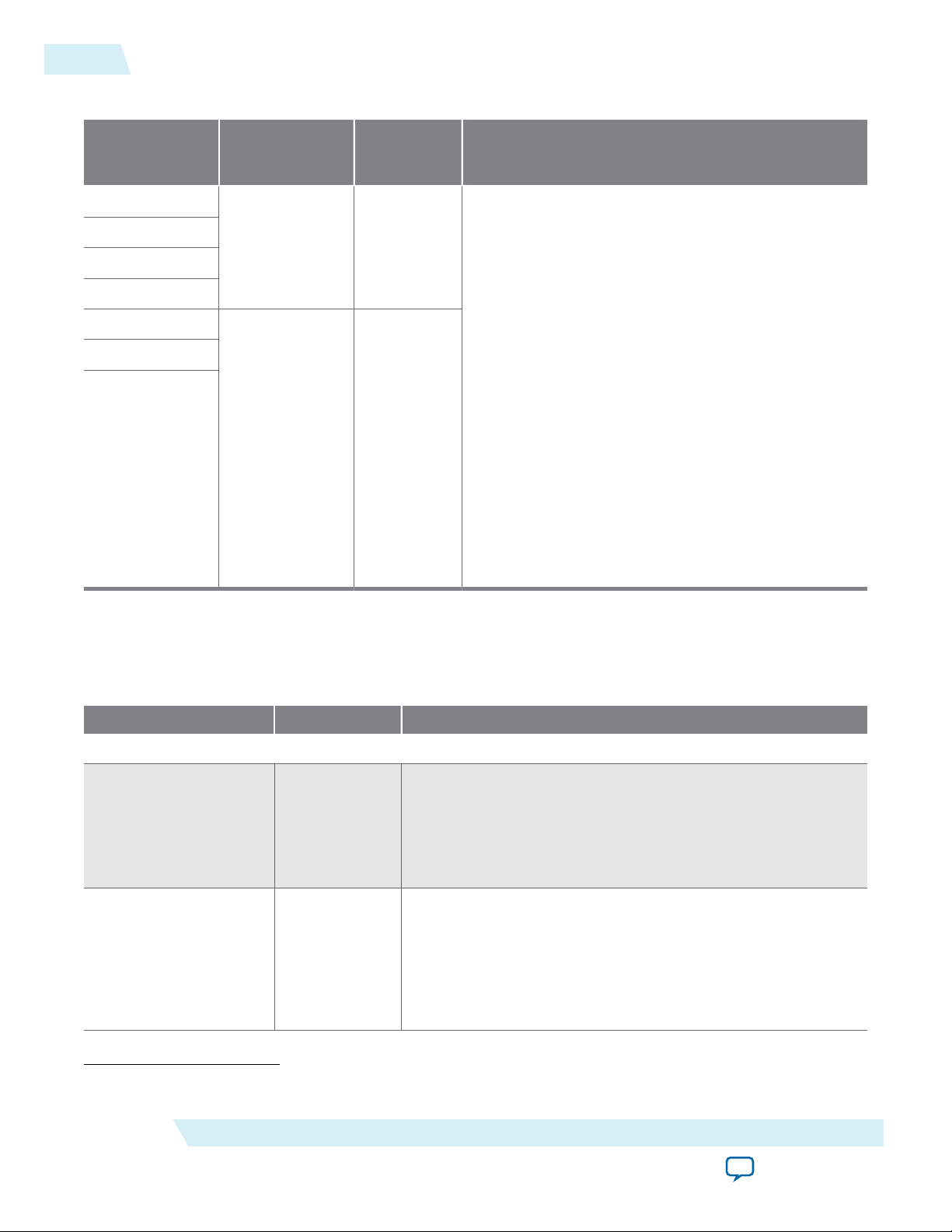

Table 2-2: Maximum Number of Lanes (L) Supported in Bonded and Non-Bonded Mode

• In PHY-only mode, you can generate up to 32 channels, provided that the channels are on the same side. In

MAC and PHY integrated mode, you can generate up to 8 channels.

• In bonded channel configuration, the lower transceiver clock skew and equal latency in the transmitter phase

compensation FIFO for all channels result in a lower channel-to-channel skew. You must use adjacent

channels when you select ×6 bonding. You must also place logical channel 0 in either physical channel 1 or 4.

Physical channels 1 and 4 are indirect drivers of the ×6 clock network. The JESD204B IP core automatically

selects between xN or feedback compensation (fb_compensation) bonding depending on the number of

transceiver channels you set.

• When you select bonded channel and L<6, the IP core automatically selects xN/x6 bonding mode for the

transceiver. When you select bonded channel and L≥6, the IP core automatically selects x6 PLL fb_compensa‐

tion bonding mode for the transceiver

• In non-bonded channel configuration, the transceiver clock skew is higher and latency is unequal in the

transmitter phase compensation FIFO for each channel. This may result in a higher channel-to-channel skew.

Device Family Core Variation Bonding Mode Configuration Maximum Number of

Lanes (L)

PHY only

Bonded 32

Non-bonded 32

(2)

(2)

Arria V

Bonded 6

MAC and PHY

Non-bonded 8

(2)

The maximum lanes listed here is for configuration simplicity. Refer to the Altera Transceiver PHY User

Guide for the actual number of channels supported.

About the JESD204B IP Core

Send Feedback

Altera Corporation

Page 11

2-6

Performance and Resource Utilization

Device Family Core Variation Bonding Mode Configuration Maximum Number of

Bonded 32

Arria V GZ

PHY only

Non-bonded 32

Arria 10

Bonded 8

Stratix V

MAC and PHY

Non-bonded 8

Performance and Resource Utilization

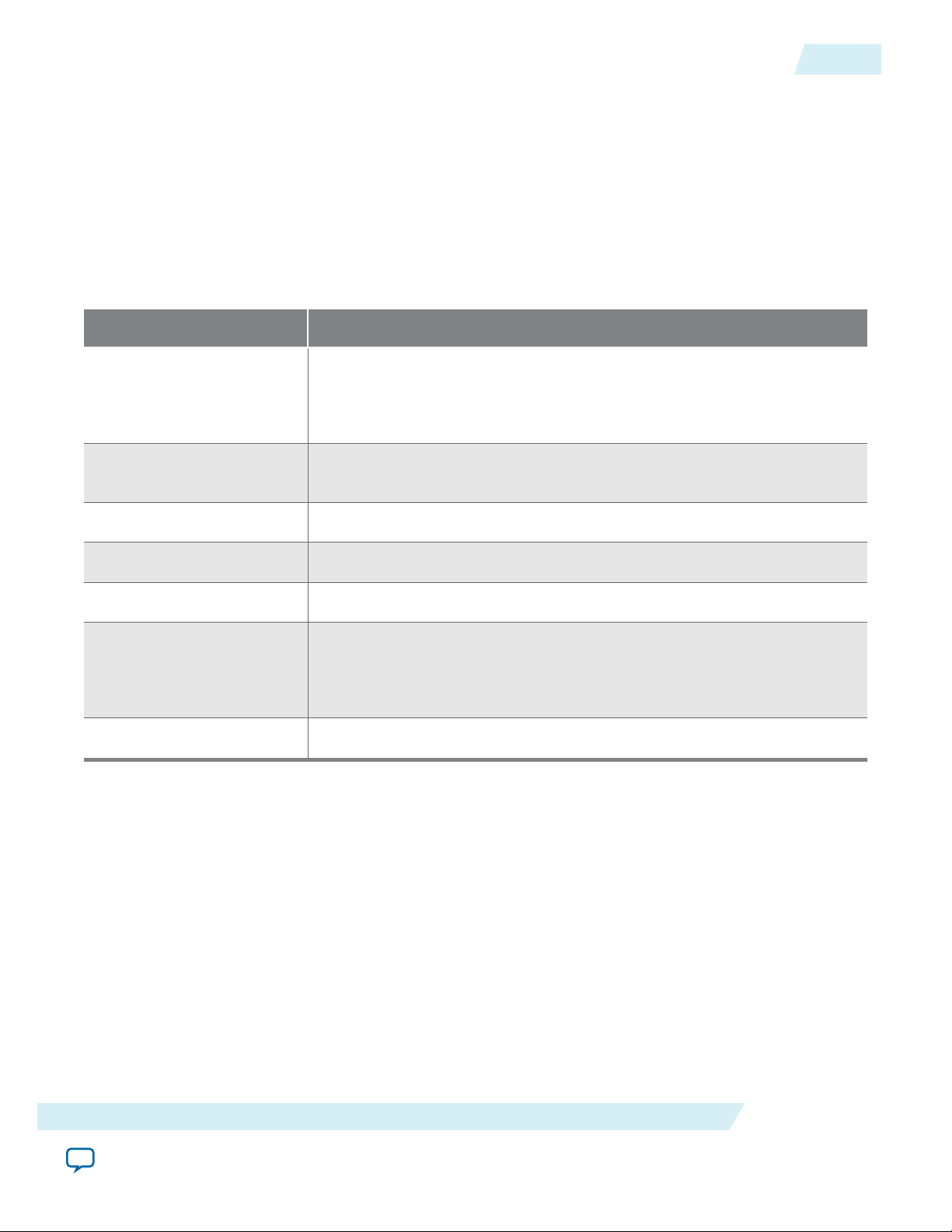

Table 2-3: JESD204B IP Core FPGA Performance

UG-01142

2015.05.04

Lanes (L)

(2)

(2)

Data Rate

Enable Soft PCS

(Gbps)

Link Clock F

(3)

Device Family

PMA Speed

Grade

FPGA Fabric

Speed Grade

Cyclone V 5 <Any

Enable Hard

PCS (Gbps)

1.0 to 5.0 — 125.00

supported

speed grade>

Cyclone V 6 6 or 7 1.0 to 3.125 — 78.125

Arria V <Any

supported

speed grade>

<Any

supported

speed grade>

1.0 to 6.55 —

Arria V GZ 2 3 2.0 to 9.9 —

Arria V GZ 3 4 2.0 to 8.8 —

(4)

(4)

(4)

163.84

247.50

220.00

Arria 10 1 1 2.0 to 12.0 2.0 to 12.5 312.50

Arria 10 2 1 2.0 to 12.0 2.0 to 12.5 312.50

Arria 10 2 2 2.0 to 9.83 2.0 to 12.5 312.50

Arria 10 3 1 2.0 to 12.0 2.0 to 12.5 312.50

Arria 10 3 2 2.0 to 9.83 2.0 to 12.5 —

Arria 10 4 3 2.0 to 8.83 2.0 to 12.5 312.50

MAX

(MHz)

Arria 10 5 3 2.0 to 8.0 2.0 to 8.0 312.50

Stratix V 1 1 or 2 2.0 to 12.2 2.0 to 12.5 312.50

Stratix V 2 1 or 2 2.0 to 12.2 2.0 to 12.5 312.50

Stratix V 2 3 2.0 to 9.8 2.0 to 12.5

(3)

Select Enable Soft PCS to achieve maximum data rate. For the TX IP core, enabling soft PCS incurs an

additional 3–8% increase in resource utilization. For the RX IP core, enabling soft PCS incurs an additional

10–20% increase in resource utilization.

(4)

Enabling Soft PCS does not increase the data rate for the device family and speed grade. You are

recommended to select the Enable Hard PCS option.

Altera Corporation

(5)

312.50

About the JESD204B IP Core

Send Feedback

Page 12

UG-01142

2015.05.04

Performance and Resource Utilization

2-7

Data Rate

Enable Soft PCS

(Gbps)

(3)

Device Family

PMA Speed

Grade

FPGA Fabric

Speed Grade

Enable Hard

PCS (Gbps)

Stratix V 3 1, 2, 3, or 4 2.0 to 8.5 2.0 to 8.5 312.50

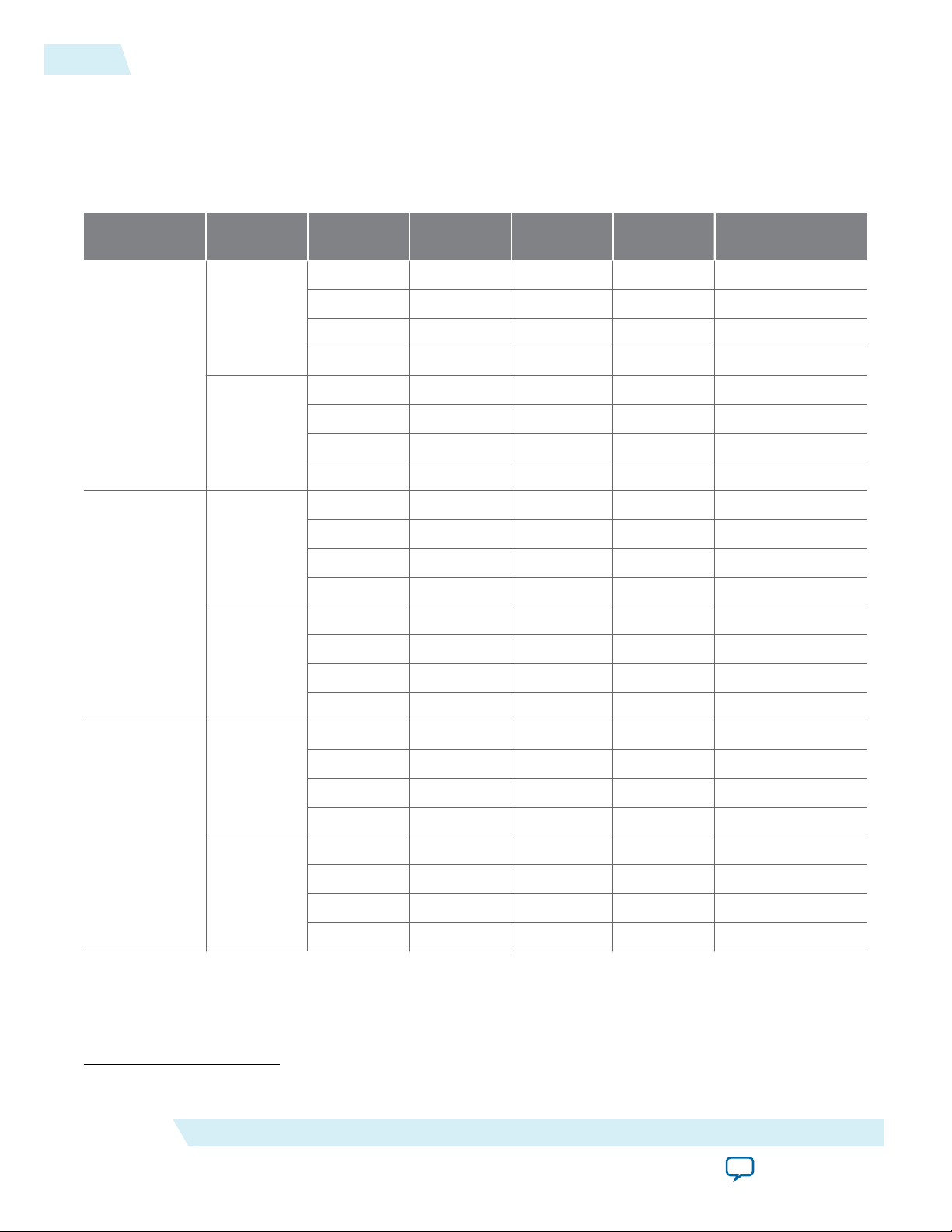

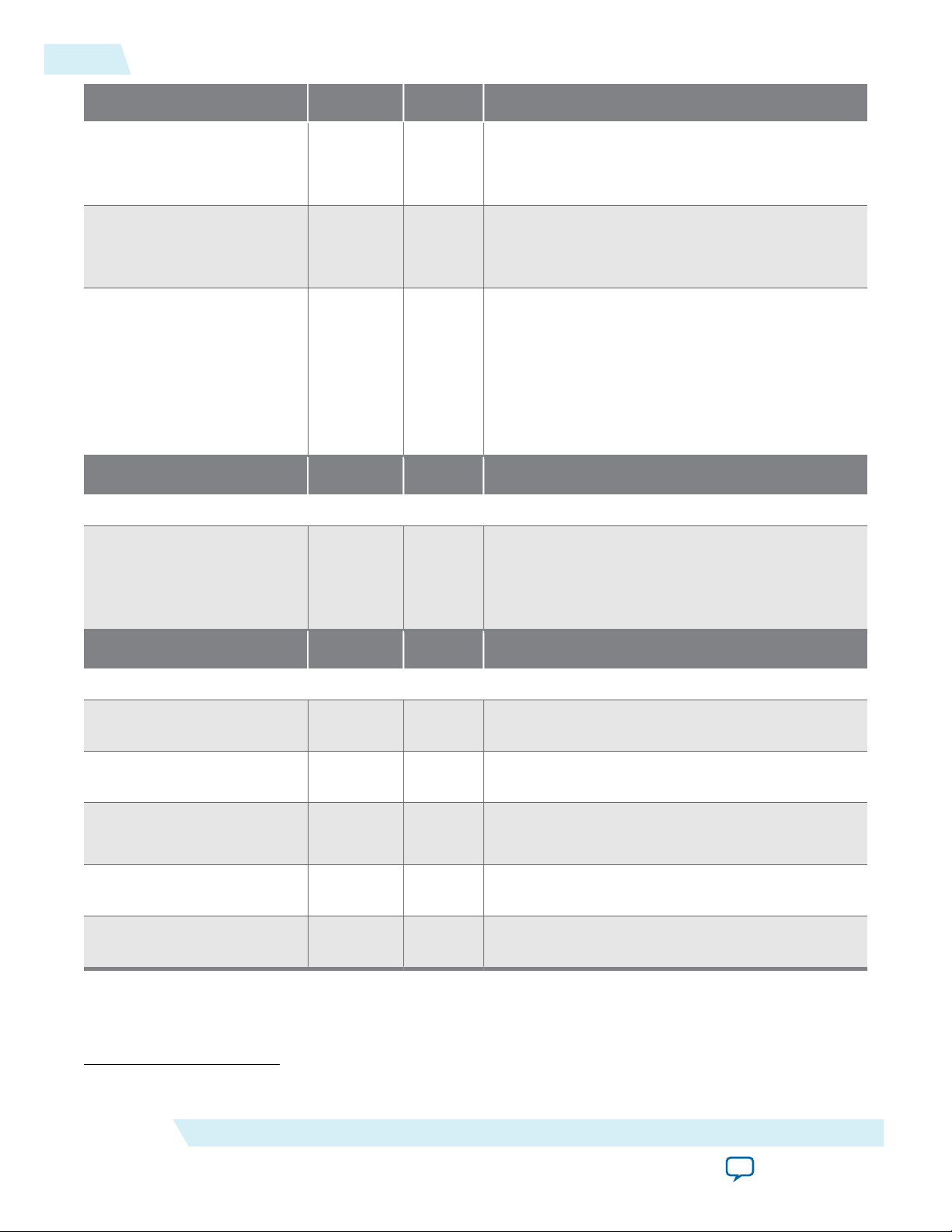

The following table lists the resources and expected performance of the JESD204B IP core. These results

are obtained using the Quartus II software targeting the following Altera FPGA devices:

• Cyclone V : 5CGTFD9E5F31I7

• Arria V : 5AGXFB3H4F35C5

• Arria V GZ : 5AGZME5K2F40C3

• Arria 10 : 10AX115H2F34I2SGES

• Stratix V : 5SGXEA7H3F35C3

All the variations for resource utilization are configured with the following parameter settings:

Table 2-4: Parameter Settings To Obtain the Resource Utilization Data

Parameter Setting

JESD204B Wrapper Base and PHY

JESD204B Subclass 1

Data Rate 5 Gbps

Link Clock F

MAX

(MHz)

PCS Option Enabled Hard PCS

PLL Type

• ATX (for 10 series devices)

• CMU (for V series devices)

Bonding Mode Non-bonded

Reference Clock Frequency 125.0 MHz

Octets per frame (F) 1

Enable Scrambler (SCR) Off

Enable Error Code Correction (ECC_EN) Off

(3)

Select Enable Soft PCS to achieve maximum data rate. For the TX IP core, enabling soft PCS incurs an

additional 3–8% increase in resource utilization. For the RX IP core, enabling soft PCS incurs an additional

10–20% increase in resource utilization.

(5)

When using Soft PCS mode at 12.5 Gbps, the timing margin is very limited. You are advised to enable

HIGH fitter effort, register duplication, and register retiming to improve timing performance.

About the JESD204B IP Core

Send Feedback

Altera Corporation

Page 13

2-8

Performance and Resource Utilization

Table 2-5: JESD204B IP Core Resource Utilization

The numbers of ALMs and logic registers in this table are rounded up to the nearest 10.

Note: The resource utilization data are extracted from a full design which includes the Altera Transceiver PHY

Reset Controller IP Core. Thus, the actual resource utilization for the JESD204B IP core should be smaller

by about 15 ALMs and 20 registers.

UG-01142

2015.05.04

Device Family Data Path Number of

Lanes

1 1047 1543 1200 1

2 1594 2325 1825 2

RX

4 2832 4043 3080 4

8 5354 7525 5585 8

Cyclone V

1 728 1148 948 0

2 889 1424 1066 0

TX

4 1218 1941 1293 0

8 1715 2837 1757 0

1 1052 1543 1197 1

2 1586 2325 1823 2

RX

4 2830 4043 3077 4

8 5330 7525 5584 8

Arria V

1 719 1148 947 0

2 887 1424 1062 0

TX

4 1208 1941 1292 0

ALMs ALUTs Logic

Registers

Memory Block

(M10K/M20K)

(6) (7)

Arria V GZ

(6)

M10K for Arria V device, M20K for Arria V GZ, Stratix V and Arria 10 devices.

Altera Corporation

8 1724 2853 1754 0

1 1062 1542 1215 0

2 1634 2363 1858 0

RX

4 2934 4097 3141 0

8 5526 7697 5711 0

1 728 1150 948 0

2 937 1488 1083 0

TX

4 1365 2114 1354 0

8 2141 3417 1895 0

About the JESD204B IP Core

Send Feedback

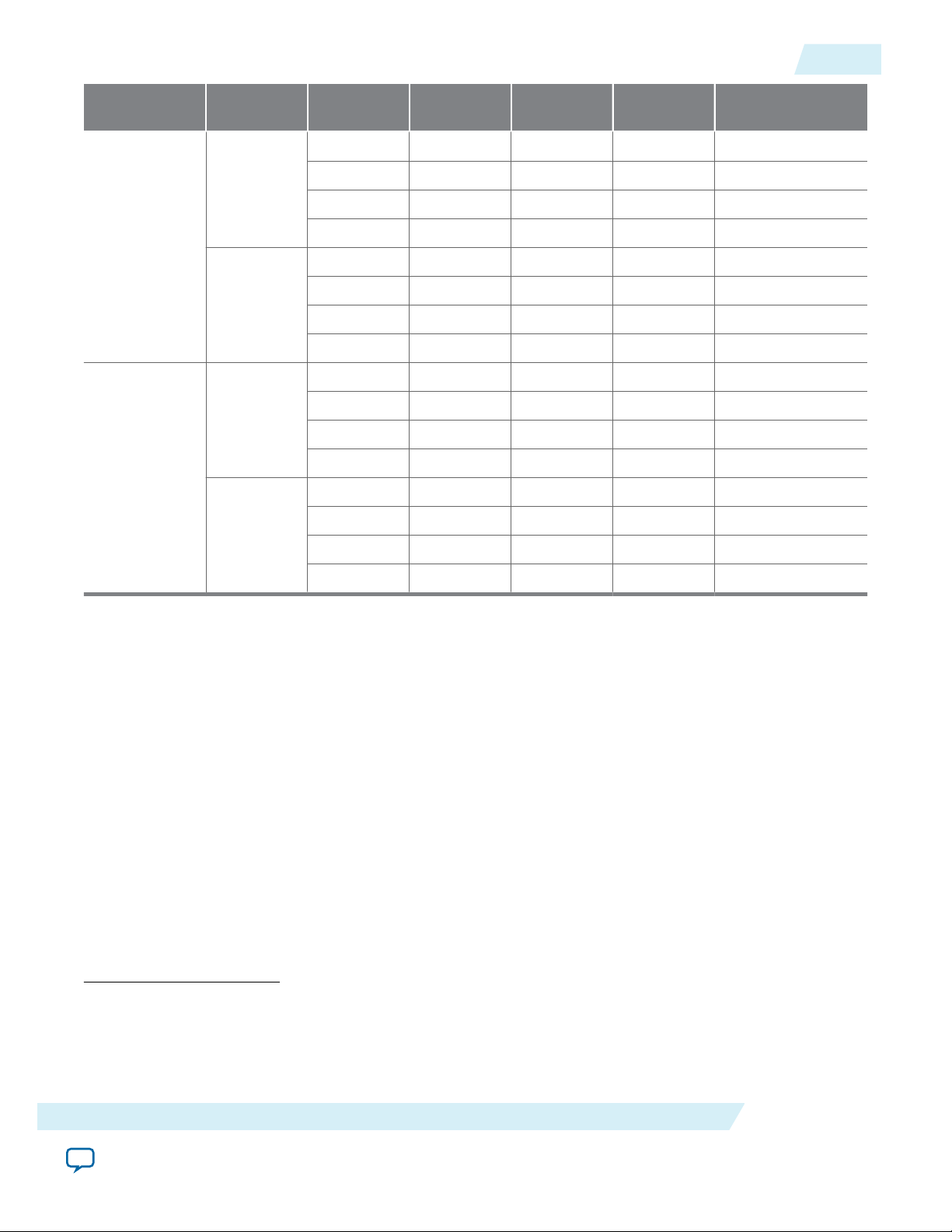

Page 14

UG-01142

2015.05.04

Performance and Resource Utilization

2-9

Device Family Data Path Number of

Lanes

1 1043 1504 1194 0

2 1575 2265 1815 0

RX

4 2828 3927 3060 0

8 5356 7347 5546 0

Arria 10

1 695 1092 931 0

2 878 1373 1049 0

TX

4 1240 1888 1285 0

8 1908 2969 1757 0

1 1056 1542 1215 0

2 1642 2363 1857 0

RX

4 2936 4097 3140 0

8 5546 7697 5712 0

Stratix V

1 719 1150 948 0

2 937 1488 1083 0

TX

4 1358 2114 1353 0

ALMs ALUTs Logic

Registers

Memory Block

(M10K/M20K)

(6) (7)

8 2137 3417 1894 0

Related Information

• JESD204B IP Core Parameters on page 3-16

• Fitter Resources Reports in the Quartus II Help

Information about the Quartus II resource utilization reporting, including ALMs needed.

(6)

M10K for Arria V device, M20K for Arria V GZ, Stratix V and Arria 10 devices.

(7)

The Quartus II software may auto-fit to use MLAB when the memory size is too small. Conversion from

MLAB to M20K or M10K was performed for the numbers listed above.

(7)

The Quartus II software may auto-fit to use MLAB when the memory size is too small. Conversion from

MLAB to M20K or M10K was performed for the numbers listed above.

About the JESD204B IP Core

Send Feedback

Altera Corporation

Page 15

2015.05.04

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Getting Started

3

UG-01142

Subscribe

Send Feedback

The JESD204B IP core is part of the MegaCore IP Library distributed with the Quartus II software and

downloadable from the Altera website at www.altera.com.

Related Information

Altera Software Installation & Licensing

Introduction to Altera IP Cores

Altera and strategic IP partners offer a broad portfolio of off-the-shelf, configurable IP cores optimized for

Altera devices. The Quartus II software installation includes the Altera IP library. You can integrate

optimized and verified Altera IP cores into your design to shorten design cycles and maximize

performance. You can evaluate any Altera IP core in simulation and compilation in the Quartus II

software. The Quartus II software also supports integration of IP cores from other sources. Use the IP

Catalog to efficiently parameterize and generate synthesis and simulation files for a custom IP variation.

The Altera IP library includes the following categories of IP cores:

• Basic functions

• DSP functions

• Interface protocols

• Low power functions

• Memory interfaces and controllers

• Processors and peripherals

Note:

The IP Catalog (Tools > IP Catalog) and parameter editor replace the MegaWizard™ Plug-In

Manager for IP selection and parameterization, beginning in Quartus II software version 14.0. Use

the IP Catalog and parameter editor to locate and paramaterize Altera and other supported IP

cores.

Related Information

• IP User Guide Documentation

• Altera IP Release Notes

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 16

acds

quartus - Contains the Quartus II software

ip - Contains the Altera IP Library and third-party IP cores

altera - Contains the Altera IP Library source code

<IP core name> - Contains the IP core source files

3-2

Installing and Licensing IP Cores

Installing and Licensing IP Cores

The Altera IP Library provides many useful IP core functions for your production use without purchasing

an additional license. Some Altera MegaCore IP functions require that you purchase a separate license for

production use. However, the OpenCore® feature allows evaluation of any Altera IP core in simulation

and compilation in the Quartus II software. After you are satisfied with functionality and perfformance,

visit the Self Service Licensing Center to obtain a license number for any Altera product.

Figure 3-1: IP Core Installation Path

Note: The default IP installation directory on Windows is <drive>:\altera\<version number>; on Linux it is

<home directory>/altera/ <version number>.

UG-01142

2015.05.04

Related Information

• Altera Licensing Site

• Altera Software Installation and Licensing Manual

Upgrading IP Cores

IP core variants generated with a previous version of the Quartus II software may require upgrading

before use in the current version of the Quartus II software. Click Project > Upgrade IP Components to

identify and upgrade outdated IP core variants.

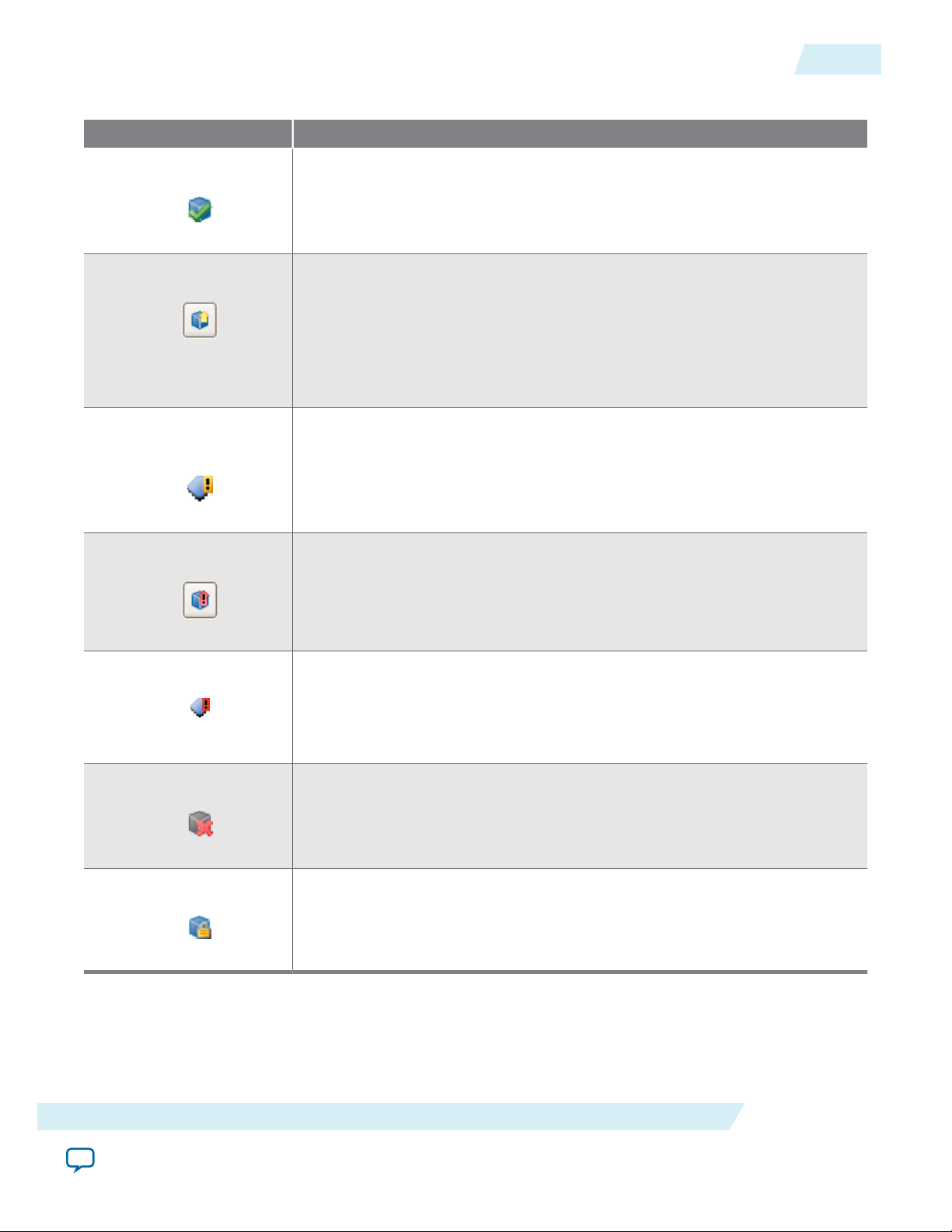

Icons in the Upgrade IP Components dialog box indicate when IP upgrade is required, optional, or

unsupported for IP cores in your design. This dialog box may open automatically when you open a

project containing upgradeable IP variations. You must upgrade IP cores that require upgrade before you

can compile the IP variation in the current version of the Quartus II software.

The upgrade process preserves the original IP variation file in the project directory as <my_variant>_

BAK.qsys for IP targeting Arria 10 and later devices, and as <my_variant>_BAK.v, .sv, or .vhd for legacy IP

targeting 28nm devices and greater.

Upgrading IP cores for Arria 10 and later devices may append a unique identifier to the original IP

Note:

core entity name(s), without similarly modifying the IP instance name. There is no requirement to

update these entity references in any supporting Quartus II file; such as the Quartus II Settings File

(.qsf), Synopsys Design Constraints File (.sdc), or SignalTap File (.stp), if these files contain instance

names. The Quartus II software reads only the instance name and ignores the entity name in paths

that specify both names. Use only instance names in assignments.

Altera Corporation

Getting Started

Send Feedback

Page 17

UG-01142

2015.05.04

Table 3-1: IP Core Upgrade Status

IP Core Status Description

Upgrading IP Cores

3-3

IP Upgraded

IP Upgrade Optional

IP Upgrade Mismatch

Warning

IP Upgrade Required

Your IP variation uses the lastest version of the IP core.

Upgrade is optional for this IP variation in the current version of the Quartus

II software. You can upgrade this IP variation to take advantage of the latest

development of this IP core. Alternatively you can retain previous IP core

characteristics by declining to upgrade. Refer to the Description for details

about IP core version differences. If you do not upgrade the IP, the IP variation

synthesis and simulation files are unchanged and you cannot modify

parameters until upgrading.

Warning of non-critical IP core differences in migrating IP to another device

family.

You must upgrade the IP variation before compiling in the current version of

the Quartus II software. Refer to the Description for details about IP core

version differences.

IP Upgrade Unspported

Upgrade of the IP variation is not supported in the current version of the

Quartus II software due to incompatibility with the current version of the

Quartus II software. You are prompted to replace the unsupported IP core

with a supported equivalent IP core from the IP Catalog. Refer to the Descrip‐

tion for details about IP core version differences and links to Release Notes.

IP End of Life

Altera designates the IP core as end-of-life status. You may or may not be able

to edit the IP core in the parameter editor. Support for this IP core

discontinues in future releases of the Quartus II software.

Encrypted IP Core

The IP variation is encrypted.

Follow these steps to upgrade IP cores:

1. In the latest version of the Quartus II software, open the Quartus II project containing an outdated IP

core variation. The Upgrade IP Components dialog automatically displays the status of IP cores in

Getting Started

Send Feedback

Altera Corporation

Page 18

Runs “Auto Upgrade” on all supported outdated cores

Opens editor for manual IP upgrade

“Auto Upgrade”

supported

Upgrade required

Upgrade

optional

Upgrade details

“Auto Upgrade”

successful

3-4

Upgrading IP Cores

your project, along with instructions for upgrading each core. Click Project > Upgrade IP

Components to access this dialog box manually.

2. To upgrade one or more IP cores that support automatic upgrade, ensure that the Auto Upgrade

option is turned on for the IP core(s), and then click Perform Automatic Upgrade. The Status and

Version columns update when upgrade is complete. Example designs provided with any Altera IP core

regenerate automatically whenever you upgrade an IP core.

3. To manually upgrade an individual IP core, select the IP core and then click Upgrade in Editor (or

simply double-click the IP core name. The parameter editor opens, allowing you to adjust parameters

and regenerate the latest version of the IP core.

Figure 3-2: Upgrading IP Cores

UG-01142

2015.05.04

Altera Corporation

Note: IP cores older than Quartus II software version 12.0 do not support upgrade. Altera verifies that

the current version of the Quartus II software compiles the previous version of each IP core.

The Altera IP Release Notes reports any verification exceptions for Altera IP cores. Altera does

not verify compilation for IP cores older than the previous two releases.

Related Information

Altera IP Release Notes

Getting Started

Send Feedback

Page 19

UG-01142

2015.05.04

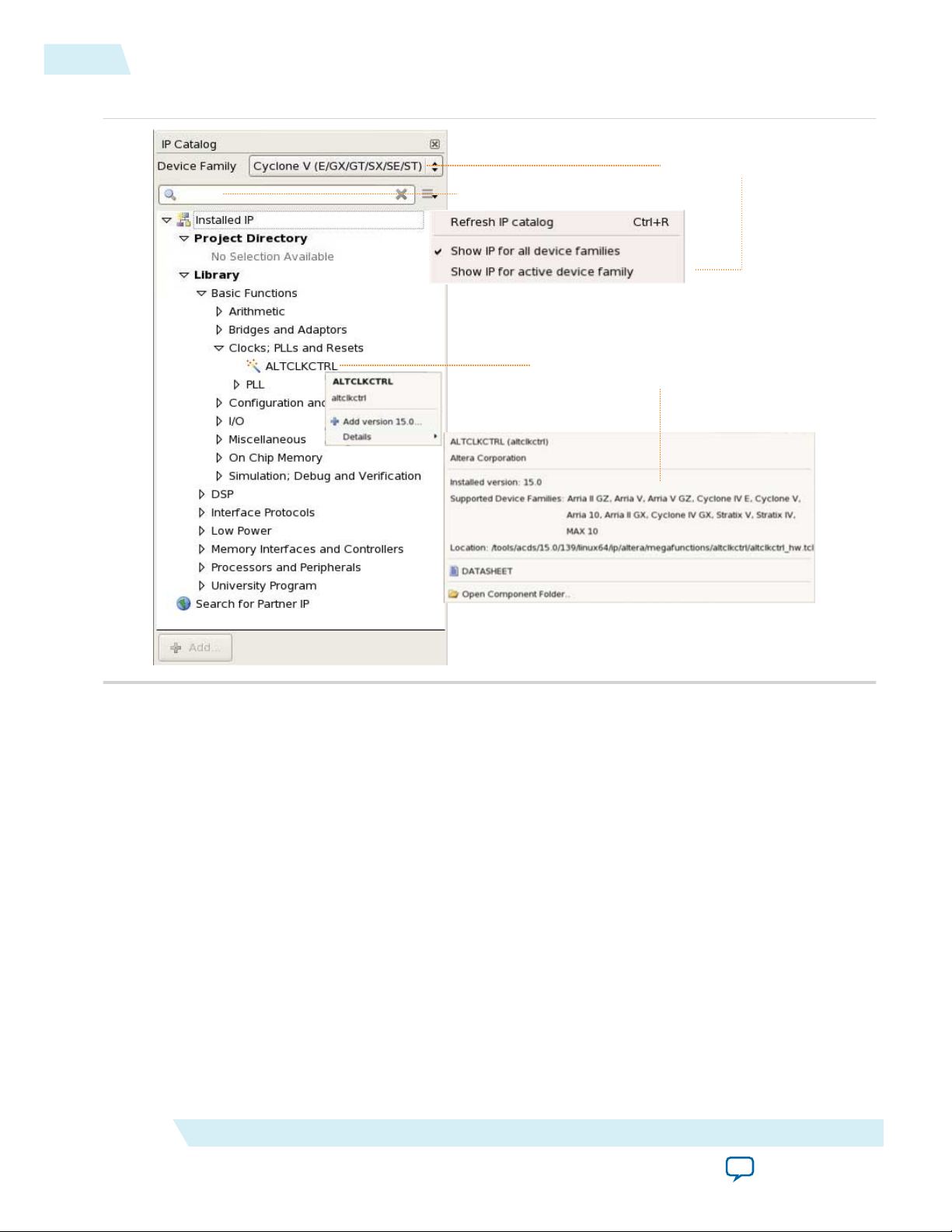

IP Catalog and Parameter Editor

The Quartus II IP Catalog (Tools > IP Catalog) and parameter editor help you easily customize and

integrate IP cores into your project. You can use the IP Catalog and parameter editor to select, customize,

and generate files representing your custom IP variation.

Note: The IP Catalog (Tools > IP Catalog) and parameter editor replace the MegaWizard™ Plug-In

Manager for IP selection and parameterization, beginning in Quartus II software version 14.0. Use

the IP Catalog and parameter editor to locate and paramaterize Altera IP cores.

The IP Catalog lists installed IP cores available for your design. Double-click any IP core to launch the

parameter editor and generate files representing your IP variation. The parameter editor prompts you to

specify an IP variation name, optional ports, and output file generation options. The parameter editor

generates a top-level Qsys system file (.qsys) or Quartus II IP file (.qip) representing the IP core in your

project. You can also parameterize an IP variation without an open project.

Use the following features to help you quickly locate and select an IP core:

• Filter IP Catalog to Show IP for active device family or Show IP for all device families. If you have no

project open, select the Device Family in IP Catalog.

• Type in the Search field to locate any full or partial IP core name in IP Catalog.

• Right-click an IP core name in IP Catalog to display details about supported devices, open the IP core's

installation folder, and view links to documentation.

• Click Search for Partner IP, to access partner IP information on the Altera website.

IP Catalog and Parameter Editor

3-5

Getting Started

Send Feedback

Altera Corporation

Page 20

Search for installed IP cores

Double-click to customize, right-click for

detailed information

Show IP only for target device

3-6

Design Walkthrough

Figure 3-3: Quartus II IP Catalog

UG-01142

2015.05.04

Note: The IP Catalog is also available in Qsys (View > IP Catalog). The Qsys IP Catalog includes

exclusive system interconnect, video and image processing, and other system-level IP that are not

available in the Quartus II IP Catalog. For more information about using the Qsys IP Catalog, refer

to Creating a System with Qsys in the Quartus II Handbook.

Design Walkthrough

This walkthrough explains how to create a JESD204B IP core design using Qsys in the Quartus II

software. After you generate a custom variation of the JESD204B IP core, you can incorporate it into your

overall project.

Creating a New Quartus II Project

You can create a new Quartus II project with the New Project Wizard. This process allows you to:

Altera Corporation

Getting Started

Send Feedback

Page 21

UG-01142

2015.05.04

• specify the working directory for the project.

• assign the project name.

• designate the name of the top-level design entity.

1. From the Windows Start menu, select Programs > Altera > Quartus II <version> to launch the

Quartus II software. Alternatively, you can use the Quartus II Web Edition software.

2. On the File menu, click New Project Wizard.

3. In the New Project Wizard: Directory, Name, Top-Level Entity page, specify the working directory,

project name, and top-level design entity name. Click Next.

4. In the New Project Wizard: Add Files page, select the existing design files (if any) you want to include

in the project.

(8)

Click Next.

5. In the New Project Wizard: Family & Device Settings page, select the device family and specific

device you want to target for compilation. Click Next.

6. In the EDA Tool Settings page, select the EDA tools you want to use with the Quartus II software to

develop your project.

7. Review the summary of your chosen settings in the New Project Wizard window, then click Finish to

complete the Quartus II project creation.

Parameterizing and Generating the IP Core

Parameterizing and Generating the IP Core

3-7

Before you begin

Refer to Table 3-6 for the IP core parameter values and description.

1. In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core you want to

customize.

2. Specify a top-level name for your custom IP variation. This name identifies the IP core variation files

in your project. If prompted, also specify the target Altera device family and output file HDL

preference. Click OK.

3. In the Main tab, set the following options:

• Jesd204b wrapper

• Data path

• Jesd204b subclass

• Data Rate

• PCS Option

• PLL Type

• Bonding Mode

• PLL/CDR Reference Clock Frequency

• Enable Bit reversal and Byte reversal

• Enable Transceiver Dynamic Reconfiguration

• Enable Altera Debug Master Endpoint

• Enable Capability Registers

(8)

To include existing files, you must specify the directory path to where you installed the JESD204B IP core.

You must also add the user libraries if you installed the MegaCore IP Library in a different directory from

where you installed the Quartus II software.

Getting Started

Send Feedback

Altera Corporation

Page 22

3-8

Generating and Simulating the IP Core Testbench

UG-01142

2015.05.04

• Set user-defined IP identifier

• Enable Control and Status Registers

• Enable Prbs Soft Accumulators

4. In the Jesd204b Configurations tab, select the following configurations:

• Common configurations (L, M, Enable manual F configuration, F, N, N', S, K)

• Advanced configurations (SCR, CS, CF, HD, ECC_EN, PHADJ, ADJCNT, ADJDIR)

5. In the Configurations and Status Registers tab, set the the following configurations:

• Device ID

• Bank ID

• Lane ID

• Lane checksum

6. After parameterizing the core, click Generate Example Design to create the simulation testbench. Skip

to step 8 if you do not want to generate the design example.

7. Set a name for your <example_design_directory> and click OK to generate supporting files and scripts.

The testbench and scripts are located in the <example_design_directory>/ip_sim folder.

The Generate Example Design option generates supporting files for the following entities:

• IP core for simulation—refer to Generating and Simulating the IP Core Testbench on page 3-8

• IP core design example for simulation—refer to Generating and Simulating the Design Example

on page 5-55

• IP core design example for synthesis—refer to Compiling the JESD204B IP Core Design Example

on page 5-57

8. Click Finish or Generate HDL to generate synthesis and other optional files matching your IP

variation specifications. The parameter editor generates the top-level .qip or .qsys IP variation file and

HDL files for synthesis and simulation.

The top-level IP variation is added to the current Quartus II project. Click Project > Add/Remove

Files in Project to manually add a .qip or .qsys file to a project. Make appropriate pin assignments to

connect ports.

Some parameter options are grayed out if they are not supported in a selected configuration or it is

Note:

a derived parameter.

Generating and Simulating the IP Core Testbench

You can simulate your JESD204B IP core variation by using the provided IP core demonstration

testbench.

To use the JESD204B IP core testbench, follow these steps:

1. Generate the simulation model. Refer to Generating the Testbench Simulation Model on page 3-9.

2. Simulate the testbench using the simulator-specific scripts that you have generated. Refer to

Simulating the IP Core Testbench on page 3-9.

Note:

Some configurations are preset and are not programmable in the JESD204B IP core testbench. For

more details, refer to JESD204B IP Core Testbench on page 3-21 or the README.txt file located

in the <example_design_directory>/ip_sim folder.

Altera Corporation

Getting Started

Send Feedback

Page 23

UG-01142

2015.05.04

Generating the Testbench Simulation Model

To generate the testbench simulation model, execute the generated script (gen_sim_verilog.tcl or

gen_sim_vhdl.tcl) located in the <example_design_directory>/ip_sim folder.

To run the Tcl script using the Quartus II sofware, follow these steps:

1. Launch the Quartus II software.

2. On the View menu, click Utility Windows > Tcl Console.

3.

In the Tcl Console, type cd <example_design_directory>/ip_sim to go to the specified

directory.

4.

Type source gen_sim_verilog.tcl (Verilog) or source gen_sim_vhdl.tcl (VHDL)

to generate the simulation files.

To run the Tcl script using the command line, follow these steps:

1. Obtain the Quartus II software resource.

2.

Type cd <example_design_directory>/ip_sim to go to the specified directory.

3.

Type quartus_sh -t gen_sim_verilog.tcl (Verilog) or quartus_sh -t

gen_sim_vhdl.tcl (VHDL) to generate the simulation files.

Simulating the IP Core Testbench

Generating the Testbench Simulation Model

3-9

The JESD204B IP core simulation supports the following simulators:

• ModelSim-Altera SE/AE

• VCS

• VCS MX

• Cadence

• Aldec Riviera

VHDL is not supported in ModelSim-Altera AE, VCS simulators, and Aldec Riviera (for Arria 10

Note:

devices only).

Table 3-2: Simulation Setup Scripts

This table lists the simulation setup scripts and run scripts.

Simulator File Directory Script

ModelSim®-Altera

SE/AE

<example_design_directory>/ip_sim/testbench/setup_

scripts/mentor

VCS <example_design_directory>/ip_sim/testbench/setup_

scripts/synopsys/vcs

VCS MX <example_design_directory>/ip_sim/testbench/setup_

scripts/synopsys/vcsmx

msim_setup.tcl

vcs_setup.sh

vcsmx_setup.sh

synopsys_sim.setup

Aldec Riviera <example_design_directory>/ip_sim/testbench/setup_

Cadence <example_design_directory>/ip_sim/testbench/setup_

Getting Started

Send Feedback

rivierapro_setup.tcl

scripts/aldec

ncsim_setup.sh

scripts/cadence

Altera Corporation

Page 24

3-10

Compiling the JESD204B IP Core Design

Table 3-3: Simulation Run Scripts

Simulator File Directory Script

UG-01142

2015.05.04

ModelSim-Altera

<example_design_directory>/ip_sim/testbench/mentor run_altera_jesd204_tb.tcl

SE/AE

VCS <example_design_directory>/ip_sim/testbench/synopsys/vcs run_altera_jesd204_tb.sh

VCS MX <example_design_directory>/ip_sim/testbench/synopsys/

vcsmx

run_altera_jesd204_tb.sh

Aldec Riviera <example_design_directory>/ip_sim/testbench/aldec run_altera_jesd204_tb.tcl

Cadence <example_design_directory>/ip_sim/testbench/cadence run_altera_jesd204_tb.sh

To simulate the testbench design using the ModelSim-Altera or Aldec Riviera-PRO simulator, follow

these steps:

1. Launch the ModelSim-Altera or Aldec Riviera-PRO simulator.

2. On the File menu, click Change Directory > Select <example_design_directory>/ip_sim/testbench/

<simulator name>.

3. On the File menu, click Load > Macro file. Select run_altera_jes204_tb.tcl. This file compiles the

design and runs the simulation automatically, providing a pass/fail indication on completion.

To simulate the testbench design using the VCS, VCS MX (in Linux), or Cadence simulator, follow these

steps:

1. Launch the VCS, VCS MX, or Cadence simulator.

2. On the File menu, click Change Directory > Select <example_design_directory>/ip_sim/testbench/

<simulator name>.

3. Run the run_altera_jes204_tb.sh file. This file compiles the design and runs the simulation automati‐

cally, providing a pass/fail indication on completion.

Related Information

Simulating Altera Designs

More information about Altera simulation models.

Compiling the JESD204B IP Core Design

Before you begin

Refer to the JESD204B IP Core Design Considerations on page 3-11 before compiling the JESD204B

IP core design.

To compile your design, click Start Compilation on the Processing menu in the Quartus II software. You

can use the generated .qip file to include relevant files into your project.

Related Information

• JESD204B IP Core Design Considerations on page 3-11

• Quartus II Help

More information about compilation in Quartus II software.

Altera Corporation

Getting Started

Send Feedback

Page 25

UG-01142

2015.05.04

Programming an FPGA Device

After successfully compiling your design, program the targeted Altera device with the Quartus II

Programmer and verify the design in hardware. For instructions on programming the FPGA device, refer

to the Device Programming section in volume 3 of the Quartus II Handbook.

Related Information

Device Programming

JESD204B IP Core Design Considerations

You must be aware of the following conditions when integrating the JESD204B IP core in your design:

• Intergrating the IP core in Qsys

• Pin assignments

• Adding external transceiver PLL

• Timing constraints for the input clock

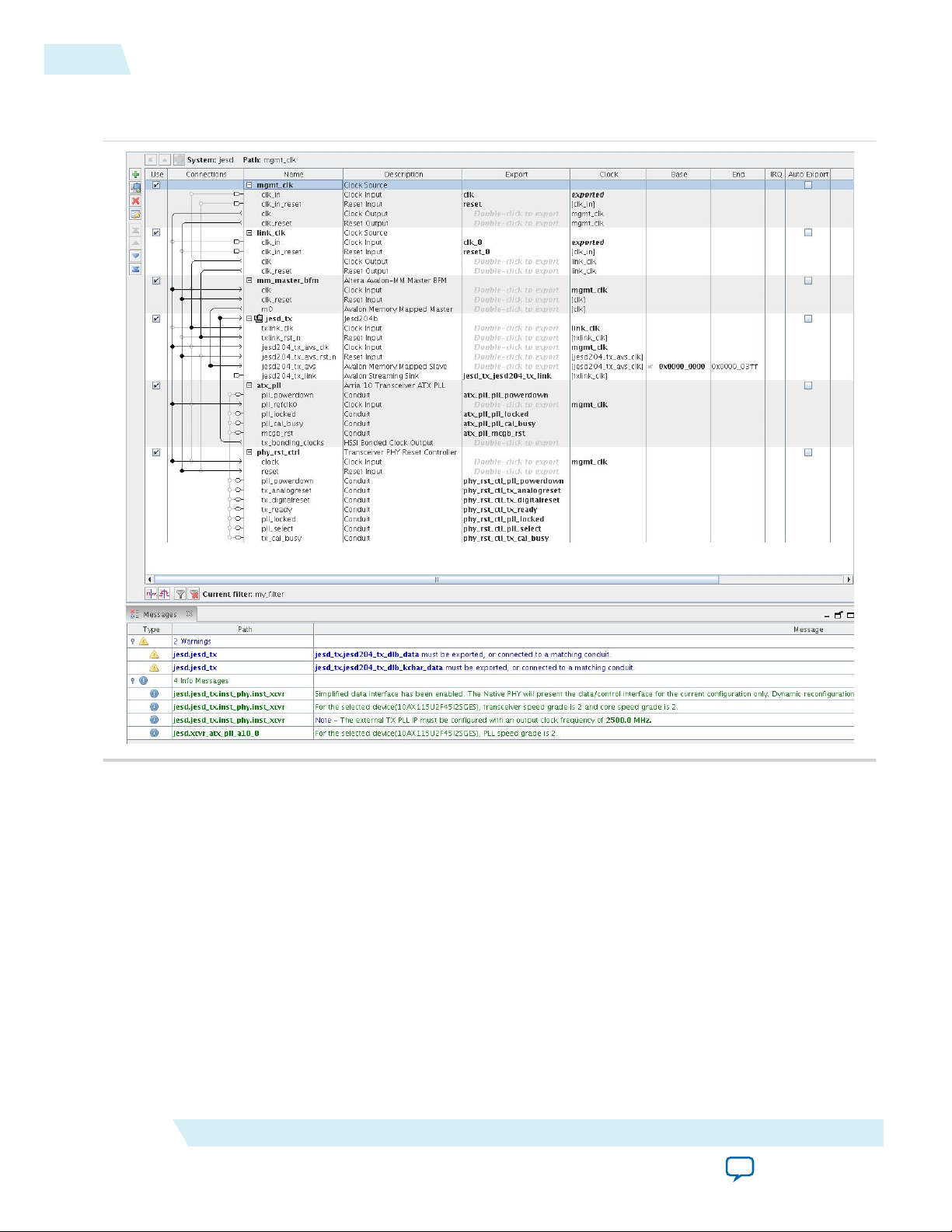

Integrating the JESD204B IP core in Qsys

You can integrate the JESD204B IP core with other Qsys components within Qsys.

Programming an FPGA Device

3-11

You can connect standard interfaces like clock, reset, Avalon-MM, Avalon-ST, HSSI bonded clock, HSSI

serial clock, and interrupt interfaces within Qsys. However, for conduit interfaces, you are advised to

export all those interfaces and handle them outside of Qsys.

(9)

This is because conduit interfaces are not

part of the standard interfaces. Thus, there is no guarantee on compatibility between different conduit

interfaces.

The Transport Layer provided in this JESD204B IP core design example is not supported in Qsys.

Note:

Therefore, you must export all interfaces that connect to the Transport Layer (for example,

jesd204_tx_link interface) and connect them to a transport layer outside of Qsys.

(9)

You can also connect conduit interfaces within Qsys but you must create adapter components to handle all

the incompatibility issues like incompatible signal type and width.

Getting Started

Send Feedback

Altera Corporation

Page 26

3-12

Pin Assignments

Figure 3-4: Example of Connecting JESD204B IP Core with Other Qsys Components in Qsys

Figure shows an example of how you can connect the IP core with other Qsys components in Qsys.

UG-01142

2015.05.04

Related Information

Transport Layer on page 5-8

Pin Assignments

Set the pin assignments before you compile to provide direction to the Quartus II software Fitter tool. You

must also specify the signals that should be assigned to device I/O pins.

You can create virtual pins to avoid making specific pin assignments for top-level signals. This is useful

when you want to perform compilation, but are not ready to map the design to hardware. Altera

recommends that you create virtual pins for all unused top-level signals to improve timing closure.

Note:

Altera Corporation

Do not create virtual pins for the clock or reset signals.

Getting Started

Send Feedback

Page 27

UG-01142

2015.05.04

Adding External Transceiver PLL

The JESD204B IP core variations that target an Arria 10 FPGA device require external transceiver PLLs

for compilation.

JESD204B IP core variations that target a V-series FPGA device contain transceiver PLLs. Therefore, no

external PLLs are required for compilation.

You are recommend to use an ATX PLL or CMU PLL to get a better jitter performance.

Note: The PMA width is 20 bits for Hard PCS and 40 bits for Soft PCS.

Related Information

Arria 10 Transceiver PHY User Guide

More information about the Arria 10 transceiver PLLs and clock network.

Timing Constraints For Input Clocks

When you generate the JESD204B IP core variation, the Quartus II software generates a Synopsys Design

Constraints File (.sdc) that specifies the timing constraints for the input clocks to your IP core.

When you generate the JESD204B IP core, your design is not yet complete and the JESD204B IP core is

not yet connected in the design. The final clock names and paths are not yet known. Therefore, the

Quartus II software cannot incorporate the final signal names in the .sdc file that it automatically

generates. Instead, you must manually modify the clock signal names in this file to integrate these

constraints with the timing constraints for your full design.

Adding External Transceiver PLL

3-13

This section describes how to integrate the timing constraints that the Quartus II software generates with

your IP core into the timing constraints for your design.

The Quartus II software automatically generates the altera_jesd204.sdc file that contains the JESD204B IP

core's timing constraints.

Three clocks are created at the input clock port:

• JESD204B TX IP core:

• txlink_clk

• reconfig_to_xcvr[0] (for Arria V, Cyclone V, and Stratix V devices only)

• reconfig_clk (for Arria 10 device only)

• tx_avs_clk

• JESD204B RX IP core:

• rxlink_clk

• reconfig_to_xcvr[0] (for Arria V, Cyclone V, and Stratix V devices only)

• reconfig_clk (for Arria 10 device only)

• rx_avs_clk

In a functional system design, these clocks (except for reconfig_to_xcvr[0] clock) are typically

provided by the core PLL.

Getting Started

Send Feedback

Altera Corporation

Page 28

3-14

Timing Constraints For Input Clocks

UG-01142

2015.05.04

In the .sdc file for your project, make the following command changes:

• Specify the PLL clock reference pin frequency using the create_clock command.

• Derive the PLL generated output clocks from the Altera PLL IP Core (for Arria V, Cyclone V and

Stratix V) or Altera I/O PLL IP Core (for Arria 10) using the derive_pll_clocks command.

• Comment out the create_clock commands for the txlink_clk, reconfig_to_xcvr[0] or

reconfig_clk, and tx_avs_clk, rxlink_clk, and rx_avs_clk clocks in the altera_jesd204.sdc file.

• Identify the base and generated clock name that correlates to the txlink_clk, reconfig_clk, and

tx_avs_clk, rxlink_clk, and rx_avs_clk clocks using the report_clock command.

• Describe the relationship between base and generated clocks in the design using the

set_clock_groups command.

After you complete your design, you must modify the clock names in your .sdc file to the full-design clock

names, taking into account both the IP core instance name in the full design, and the design hierarchy. Be

careful when adding the timing exceptions based on your design, for example, when the JESD204B IP

core handles asynchronous timing between the txlink_clk, rxlink_clk, pll_ref_clk, tx_avs_clk,

rx_avs_clk, and reconfig_clk (for Arria 10 only) clocks.

The table below shows an example of clock names in the altera_jesd204.sdc and input clock names in the

user design. In this example, there is a dedicated input clock for the transceiver TX PLL and CDR at the

refclk pin. The device_clk is the input to the core PLL clkin pin. The IP core and transceiver Avalon-

MM interfaces have separate external clock sources with different frequencies.

Altera Corporation

Getting Started

Send Feedback

Page 29

UG-01142

2015.05.04

Table 3-4: Example A

Timing Constraints For Input Clocks

3-15

Original clock

names in altera_

jesd204.sdc

tx_pll_ref_clk

rx_pll_ref_clk

txlink_clk

rxlink_clk

tx_avs_clk

rx_avs_clk

reconfig_clk

(10)

User design input

clock names

xcvr_tx_rx_refclk 250

device_clk 125

jesd204_avs_clk 100

phy_mgmt_clk 75

Frequency

(MHz)

Recommended SDC timing constraint

create_clock -name xcvr_tx_rx_refclk -period 4.0

[get_ports xcvr_tx_rx_refclk ]

create_clock -name device_clk -period 8.0 [get_ports

device_clk]

create_clock -name jesd204_avs_clk -period 10.0

[get_ports jesd204_avs_clk]

create_clock -name phy_mgmt_clk -period 13.3 [get_

ports phy_mgmt_clk]

derive_pll_clocks

set_clock_groups -asynchronous \

-group {xcvr_tx_rx_refclk \

<base and generated clock names as reported by

report_clock commands> \

} \

-group {device_clk \

<base and generated clock names as reported by

report_clock commands> \

} \

-group {jesd204_avs_clk} \

-group {phy_mgmt_clk \

<base and generated clock names as reported by

report_clock commands> \

}

However, if your design requires you to connect the

rx_avs_clk and reconfig_clk to the same clock,

you need to put them in the same clock group.

The table below shows an example where the device_clk in this design is an input into the transceiver

refclk pin. The IP core's Avalon-MM interface shares the same clock source as the transceiver

management clock.

(10)

For Arria 10 device only.

Getting Started

Send Feedback

Altera Corporation

Page 30

3-16

JESD204B IP Core Parameters

Table 3-5: Example B

UG-01142

2015.05.04

Original clock

names in altera_

jesd204.sdc

tx_pll_ref_clk

rx_pll_ref_clk

txlink_clk

rxlink_clk

tx_avs_clk

rx_avs_clk

reconfig_clk

(11)

User design input

clock names

device_clk 125

mgmt_clk 100

Frequency

(MHz)

Recommended SDC timing constraint

create_clock -name device_clk -period 8.0 [get_ports

device_clk]

create_clock -name mgmt_clk -period 10.0 [get_ports

mgmt_clk]

derive_pll_clocks

set_clock_groups -asynchronous \

-group {device_clk \

<base and generated clock names as reported by

report_clock commands> \

} \

-group {mgmt_clk \

<base and generated clock names as reported by

report_clock commands> \

}

JESD204B IP Core Parameters

Table 3-6: JESD204B IP Core Parameters

Parameter Value Description

Main Tab

Device Family

JESD204B Wrapper

(11)

For Arria 10 device only.

• Arria V

• Arria V GZ

• Arria 10

• Cyclone V

• Stratix V

• Base Only

• PHY Only

• Both Base

and PHY

Select the targeted device family.

Select the JESD204B wrapper.

• Base Only—generates the DLL only.

• PHY Only—generates the transceiver PHY layer only (soft

and hard PCS).

• Both Base and PHY—generates both DLL and transceiver

PHY layers.

Altera Corporation

Getting Started

Send Feedback

Page 31

UG-01142

2015.05.04

JESD204B IP Core Parameters

Parameter Value Description

3-17

Data Path

• Receiver

• Transmitter

• Duplex

Select the operation modes. This selection enables or disables

the receiver and transmitter supporting logic.

• RX—instantiates the receiver to interface to the ADC.

• TX—instantiates the transmitter to interface to the DAC.

• Duplex—instantiates the receiver and transmitter to

interface to both the ADC and DAC.

JESD204B Subclass • 0

• 1

• 2

Select the JESD204B subclass modes.

• 0—Set subclass 0

• 1—Set subclass 1

• 2—Set subclass 2

Data Rate 1.0–12.5 Set the data rate for each lane.

• Cyclone V—1.0 Gbps to 5.0 Gbps

• Arria V—1.0 Gbps to 6.55 Gbps

• Arria V GZ—2.0 Gbps to 9.9 Gbps

• Arria 10—2.0 Gbps to 12.5 Gbps

• Stratix V—2.0 Gbps to 12.5 Gbps

PCS Option • Enabled

Hard PCS

• Enabled Soft

PCS

Select the PCS modes.

• Enabled Hard PCS—utilize Hard PCS components. Select

this option to minimize resource utilization with data rate

that supports up to the limitation of the Hard PCS.

(12)

Note: For this setting, you will utilize 8G PCS mode

with 20 bits PMA width and 32 bits PCS width.

• Enabled Soft PCS—utilize Soft PCS components. Select this

option to allow higher supported data rate but increase in

resource utilization.

Note: For this setting, you will utilize 10G PCS mode

with 40 bits PMA width and 40 bits PCS width.

PLL Type • CMU

• ATX

Select the Phase-Locked Loop (PLL) types, depending on the

FPGA device family.

• Cylone V—CMU

• Arria V—CMU

• Stratix V—CMU, ATX

(12)

The maximum data rate is limited by different device speed grade, transceiver PMA speed grade, and

PCS options. Refer to Table 3-4 for the maximum data rate support.

Getting Started

Send Feedback

Altera Corporation

Page 32

3-18

JESD204B IP Core Parameters

Parameter Value Description

UG-01142

2015.05.04

Bonding Mode

PLL/CDR Reference

Clock Frequency

Enable Bit reversal and

Byte reversal

Enable Transceiver

Dynamic Reconfigura‐

tion

Enable Altera Debug

Master Endpoint

(14)

• Bonded

• Non-bonded

Select the bonding modes.

• Bonded—select this option to minimize inter-lanes skew

for the transmitter datapath.

• Non-bonded—select this option to disable inter-lanes skew

control for the transmitter datapath.

Note: The bonding type is automatically selected based on

the device family and number of lanes that you set.

50.0–625.0 Set the transceiver reference clock frequency for PLL or CDR.

On, Off Turn on this option to set the data transmission order in MSB-

first serialization. If this option is off, the data transmission

order is in LSB-first serialization.

On, Off

Turn on this option to enable dynamic data rate change. When

you enable this option, you need to connect the reconfigura‐

tion interface to the transceiver reconfiguration controller.

(13)

For Arria 10 devices, turn on this option to enable the

Transceiver Native PHY reconfiguration interface with "Share

Reconfiguration Interface" enabled for multiple channels.

On, Off Turn on this option for the Transceiver Native PHY IP core to

include an embedded Altera Debug Master Endpoint (ADME).

This ADME connects internally to the Avalon-MM slave

interface of the Transceiver Native PHY and can access the

reconfiguration space of the transceiver. It can perform certain

test and debug functions via JTAG using System Console.

Enable Capability

Registers

Set user-defined IP

identifier

(13)

To perform dynamic reconfiguration, you have to instantiate the Transceiver Reconfiguration Controller

from the IP Catalog and connect it to the JESD204B IP core through the reconfig_to_xcvr and

reconfig_from_xcvr interface.

(14)

To support the Transceiver Toolkit in your design, you must turn on this option.

Altera Corporation

(14)

This parameter is valid only for Arria 10 devices and when you

turn on the Enable Transceiver Dynamic Reconfiguration

parameter.

On, Off Turn on this option to enable capability registers, which

provides high level information about the transceiver channel's

configuration.

0–255 Set a user-defined numeric identifier that can be read from the

user identifer offset when you turn on the Enable Capability

Registers parameter.

Getting Started

Send Feedback

Page 33

UG-01142

2015.05.04

JESD204B IP Core Parameters

Parameter Value Description

3-19

Enable Control and

Status Registers

(14)

On, Off Turn on this option to enable soft registers for reading status

signals and writing control signals on the PHY interface

through the embedded debug. Signals include rx_is_

locktoref, rx_is_locktodata, tx_cal_busy, rx_cal_busy,

rx_serial_loopback, set_rx_locktodata, set_rx_

locktoref, tx_analogreset, tx_digitalreset, rx_

analogreset, and rx_digitalrest. For more information,

refer to the Arria 10 Transceiver User Guide.

Enable Prbs Soft

Accumulators

(14)

On, Off Turn on this option to set the soft logic to perform PRBS bit

and error accumulation when using the hard PRBS generator

and checker.

JESD204B Configurations Tab

Lanes per converter device

1–8 Set the number of lanes per converter device.

(15)

(L)

Converters per device (M) 1–256 Set the number of converters per converter device.

Enable manual F configu‐

ration

On, Off

Turn on this option to set parameter F in manual mode

and enable this parameter to be configurable. Otherwise,

the parameter F is in derived mode.

You have to enable this parameter and configure the

appropriate F value if the transport layer in your design is

supporting Control Word (CF) and/or High Density

format(HD).

Note: The auto derived F value using formula

F=M*S*N\'/(8*L) may not apply if parameter

CF and/or parameter HD are enabled.

Octets per frame (F) 1, 2, 4–256 The number of octets per frame derived from the formula

of F= M*N'*S/(8*L).

Converter resolution (N) 1–32 Set the number of conversion bits per converter.

Transmitted bits per

sample (N')

1–32 Set the number of transmitted bits per sample (JESD204B

word size).

Note: If parameter CF equals to 0 (no control word),

parameter N' must be larger than or equal to

sum of parameter N and parameter CS (N' ≥ N

+ CS). Otherwise, parameter N' must be larger

than or equal to parameter N (N'≥N).

Samples per converter per

frame (S)

(15)

Refer to the Table 3-6 table for the supported range for L.

1–32 Set the number of transmitted samples per converter per

frame.

Getting Started

Send Feedback

Altera Corporation

Page 34

3-20

JESD204B IP Core Parameters

UG-01142

2015.05.04

Frames per multiframe

(K)

1–32 Set the number of frames per multiframe. This value is

dependent on the value of F and is derived using the

following constraints:

• The value of K must fall within the range of 17/F <= K

<= min(32, floor (1024/F))

• The value of F*K must be divisible by 4

Enable scramble (SCR) On, Off Turn on this option to scramble the transmitted data or

descramble the receiving data.

Control Bits (CS) 0–3 Set the number of control bits per conversion sample.

Control Words (CF) 0–32 Set the number of control words per frame clock period

per link.

High density user data

format (HD)

On, Off Turn on this option to set the data format. This parameter

controls whether a sample may be divided over more

lanes.

• On: High Density format

• Off: Data should not cross the lane boundary

Enable Error Code

Correction (ECC_EN)

On, Off Turn on this option to enable error code correction (ECC)

for memory blocks.

Phase adjustment request

(PHADJ)

On, Off Turn on this option to specify the phase adjustment

request to the DAC.

• On: Request for phase adjustment

• Off: No phase adjustment

This parameter is valid for Subclass 2 mode only.

Adjustment resolution

0–15 Set the adjustment resolution for the DAC LMFC.

step count (ADJCNT)

This parameter is valid for Subclass 2 mode only.

Direction of adjustment

(ADJDIR)

• Advance

• Delay

Select to adjust the DAC LMFC direction.

This parameter is valid for Subclass 2 mode only.

Configurations and Status Registers Tab

Device ID 0–255 Set the device ID number.

Bank ID 0–15 Set the device bank ID number.

Lane# ID 0–31 Set the lane ID number.

Lane# checksum 0–255 Set the checksum for each lane ID.

Altera Corporation

Getting Started

Send Feedback

Page 35

UG-01142

2015.05.04

Related Information

Performance and Resource Utilization on page 2-6

JESD204B IP Core Component Files

The following table describes the generated files and other files that may be in your project directory. The

names and types of generated files specified may vary depending on whether you create your design with

VHDL or Verilog HDL.

Table 3-7: Generated Files

Extension Description

<variation name>.v or .vhd IP core variation file, which defines a VHDL or Verilog HDL description of

the custom IP core. Instantiate the entity defined by this file inside of your

design. Include this file when compiling your design in the Quartus II

software.