Page 1

Interlaken MegaCore Function User Guide

Interlaken MegaCore Function

User Guide

c The Interlaken MegaCore function is scheduled for product

obsolescence and discontinued support as described in

PDN1410. Therefore, Altera does not recommend use of this IP

in new designs. For more information about Altera’s current IP

offering, refer to Altera’s Intellectual Property website.

101 Innovation Drive

San Jose, CA 95134

www.altera.com

UG-01092-1.3

Document last updated for Altera Complete Design Suite version:

Document publication date:

12.0

June 2012

Feedback Subscribe

Page 2

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 3

Contents

Chapter 1. About This MegaCore Function

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Device Family Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

MegaCore Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Performance and Resource Utilization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Release Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

Installation and Licensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

Interlaken MegaCore Function Licenses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–5

OpenCore Evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–6

Chapter 2. Getting Started

Design Flows . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

MegaWizard Plug-In Manager Design Flow Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Qsys Design Flow Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

MegaWizard Plug-in Manager Design Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Specifying Parameters and Generating the MegaCore Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Simulating the Interlaken MegaCore Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Instantiating the MegaCore Function in Your Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Qsys Design Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Specifying Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Completing the Qsys System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

Simulating the System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

Specifying Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

Hard PLL Assignment Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

I/O Standard Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8

Compiling the Full Design and Programming the FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–9

Chapter 3. Parameter Settings

General Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Operational Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Number of Lanes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Lane Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Number of Words in Meta Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Exclude Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Enable Out-of-Band Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

In-Band Flow Control Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Expose Calendar Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Number of Sixteen-Bit Calendar Pages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Burst Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Enable Dynamic Configuration of BurstMax and BurstShort Parameters . . . . . . . . . . . . . . . . . . . . . 3–4

Parameterized Static BurstMax Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Parameterized Static BurstShort Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Chapter 4. Functional Description

Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Interfaces Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Interlaken Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Application Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 4

iv Contents

Avalon-ST Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

Optional In-Band Flow Control and Dynamic Configuration Signals . . . . . . . . . . . . . . . . . . . . . . 4–4

Out-of-Band Flow Control Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

Clocking and Reset Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–5

MegaCore Function MAC Clock Domains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–5

Interlaken Interface Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–5

Out-of-Band Flow Control Block Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–6

Clock Diagrams for the Interlaken MegaCore Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–6

Interlaken MegaCore Function Recommended Clock Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

MAC Clock Verified Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

PCS Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–10

Transceiver Reference Clock Recommended Frequency and Source . . . . . . . . . . . . . . . . . . . . . . 4–10

Out-of-Band Flow Control Block Recommended Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . 4–11

Reset for Interlaken MegaCore Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–11

Transmit Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–11

Arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–12

Arbiter and Application Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–12

Application Data Transfer Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–13

TX MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–16

TX PCS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–16

Receive Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–17

RX PCS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–17

RX MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–18

Channel Filtering Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–19

Packet Regrouper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–19

Calendar and Status Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–20

Lane Status Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–21

TX Calendar Control Block and In-Band Flow Control Calendar Bits . . . . . . . . . . . . . . . . . . . . . . . . 4–21

Behavior with Hidden Calendar Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–21

Behavior with Exposed Calendar Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–22

Status Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–22

High-Speed I/O Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–22

FIFO Buffers and Pipeline Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–23

Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–23

Out-of-Band Flow Control Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–24

RX Out-of-Band Flow Control Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–24

TX Out-of-Band Flow Control Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–25

Out-of-Band Flow Control Block Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–25

Chapter 5. Signals

Interlaken Interface and External Transceiver Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

Interlaken Interface Data and Clock Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

Interlaken Interface Status Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–3

Interlaken MegaCore Function Reset Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–4

Application Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–5

RX Application Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–5

TX Application Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–6

Out-of-Band Flow Control Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–8

RX Out-of-Band Flow Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–8

TX Out-of-Band Flow Control Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–10

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 5

Contents v

Chapter 6. Qsys Design Examples

Design Examples Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–1

Interlaken Sample Channel Client Component . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–2

Design Example Simulation Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

Running a Design Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

Setting Up the Design Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–4

Creating the Quartus II Project and Generating the Qsys System . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–4

Simulating the System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–4

Compiling and Programming the Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–5

Appendix A. Initializing the Interlaken MegaCore Function

Configuration and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1

Expected Behavior at Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1

Troubleshooting an Interlaken Link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–2

Appendix B. Excluding Transceivers for Faster Simulation

External Transceiver Interface Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–2

External Transceiver Interface Data and Clock Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–5

Reset in Interlaken MegaCore Functions Without Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–6

Reset Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–7

Required Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–8

Appendix C. Closing Timing on 10- and 20-lane Designs

Appendix D. Porting an Interlaken Design from the Previous Version of the Software

Additional Information

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 6

vi Contents

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 7

1. About This MegaCore Function

Interlaken is a high-speed serial communication protocol for chip-to-chip packet

transfers. The Altera

Protocol Specification, Revision 1.2. It supports specific combinations of number of lanes

from 4 to 20, and lane rates from 3.125 to 10.3125 gigabits per second (Gbps), on

®

Stratix

IV GT devices, and lane rates from 3.125 to 6.375 Gbps on Stratix IV GX

devices, providing raw bandwidth of 12.50 Gbps to 127.50 Gbps.

Interlaken provides low I/O count compared to earlier protocols, supporting

scalability in both number of lanes and lane speed. Other key features include flow

control, low overhead framing, and extensive integrity checking. The Interlaken

MegaCore function incorporates a physical coding sublayer (PCS), a physical media

attachment (PMA), and a media access control (MAC) block. The MegaCore function

transmits and receives Avalon

interface.

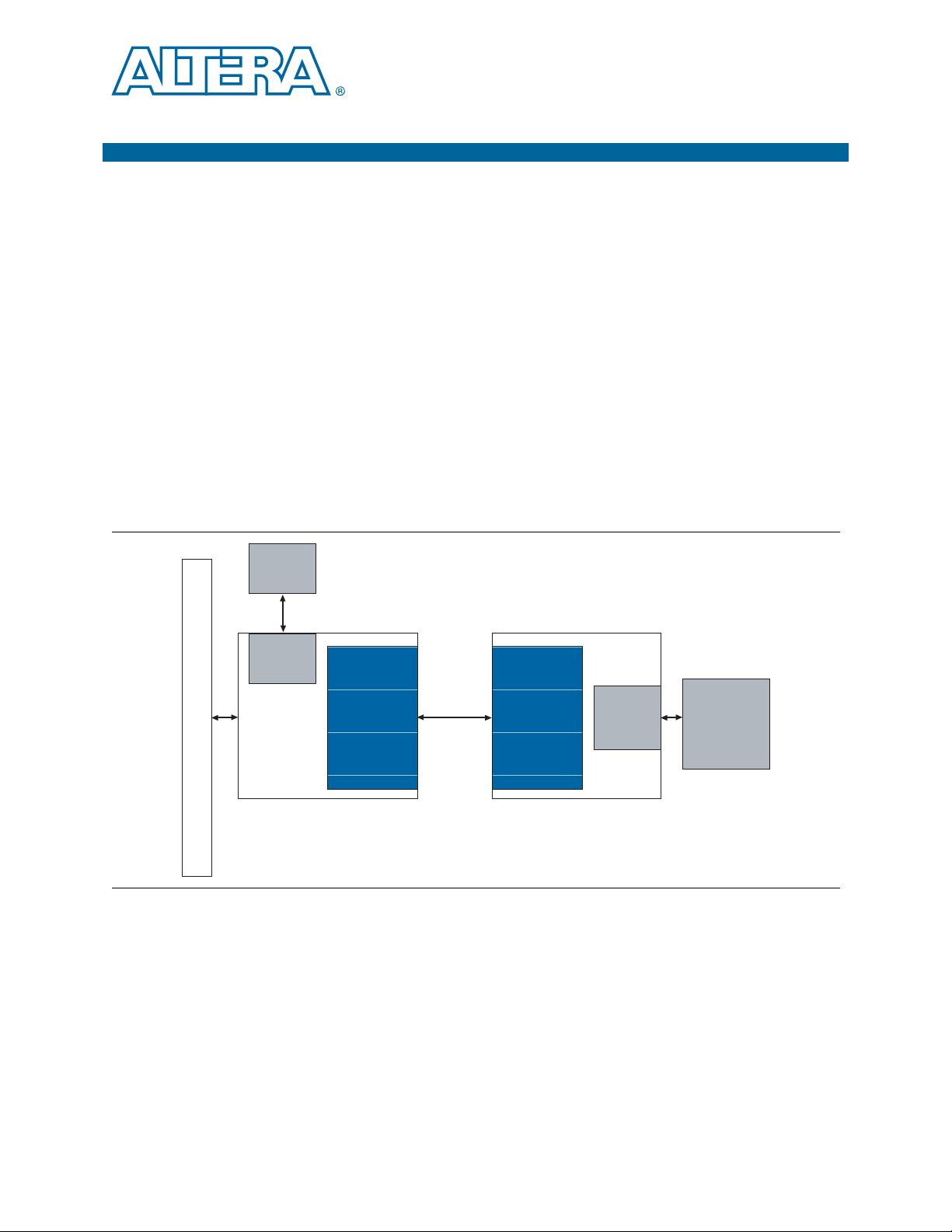

Figure 1–1 shows an example system implementation.

Figure 1–1. Typical Interlaken Application

High-Speed

Memory

Memory

Controller

®

Interlaken MegaCore® function implements the Interlaken

®

Streaming (Avalon-ST) data on its FPGA fabric

Features

Swuitch Fabric or Backplane

Stratix IV GX

FPGA

Interlaken

MegaCore

Function

Interlaken Link

Interlaken

MegaCore

Function

Ethernet MAC

Stratix IV GT

FPGA

Optical

Module

The Interlaken MegaCore function has the following features:

■ Compliant with the Interlaken Protocol Specification, Rev 1.2

■ Supports 4, 8, 10, 12, and 20 serial lanes in configurations that provide nominal

bandwidths of 20 Gbps, 40 Gbps, and 100 Gbps

■ Supports per-lane data rates of 3.125, 6.25, 6.375, and 10.3125 Gbps using Altera

on-chip high-speed transceivers

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 8

1–2 Chapter 1: About This MegaCore Function

■ Supports fast simulation by allowing configuration without high-speed

Device Family Support

transceivers

■ Supports up to 127.5 Gbps raw bandwidth

■ Supports dynamically configurable BurstMax and BurstShort values

■ Provides Avalon-ST interfaces on the transmit and receive datapaths

■ Supports two logical channels in out-of-the-box configuration

■ Supports optional user-controlled in-band flow control with 1, 8, or 16 16-bit

calendar pages

■ Supports optional out-of-band flow control blocks for lane status, link status, and

one calendar page

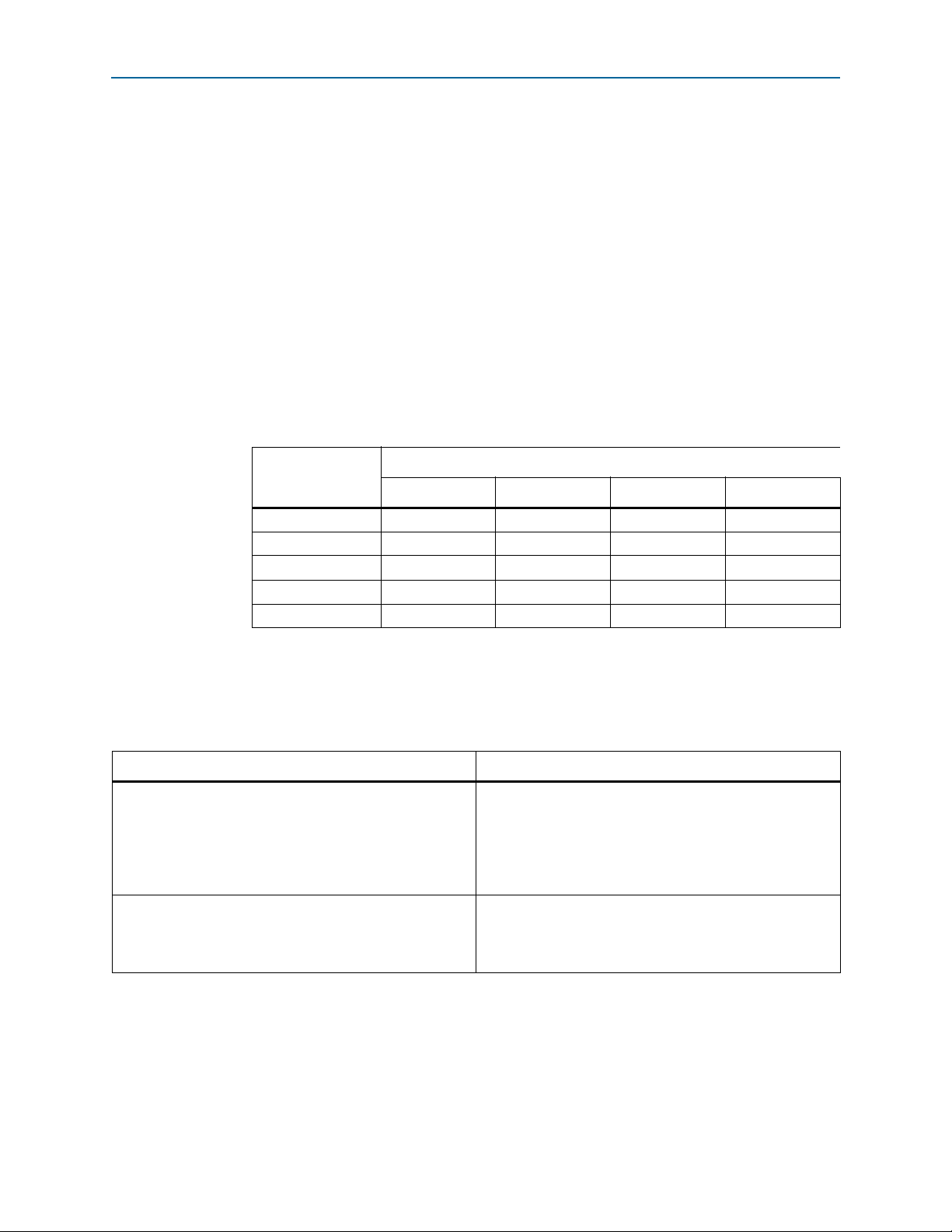

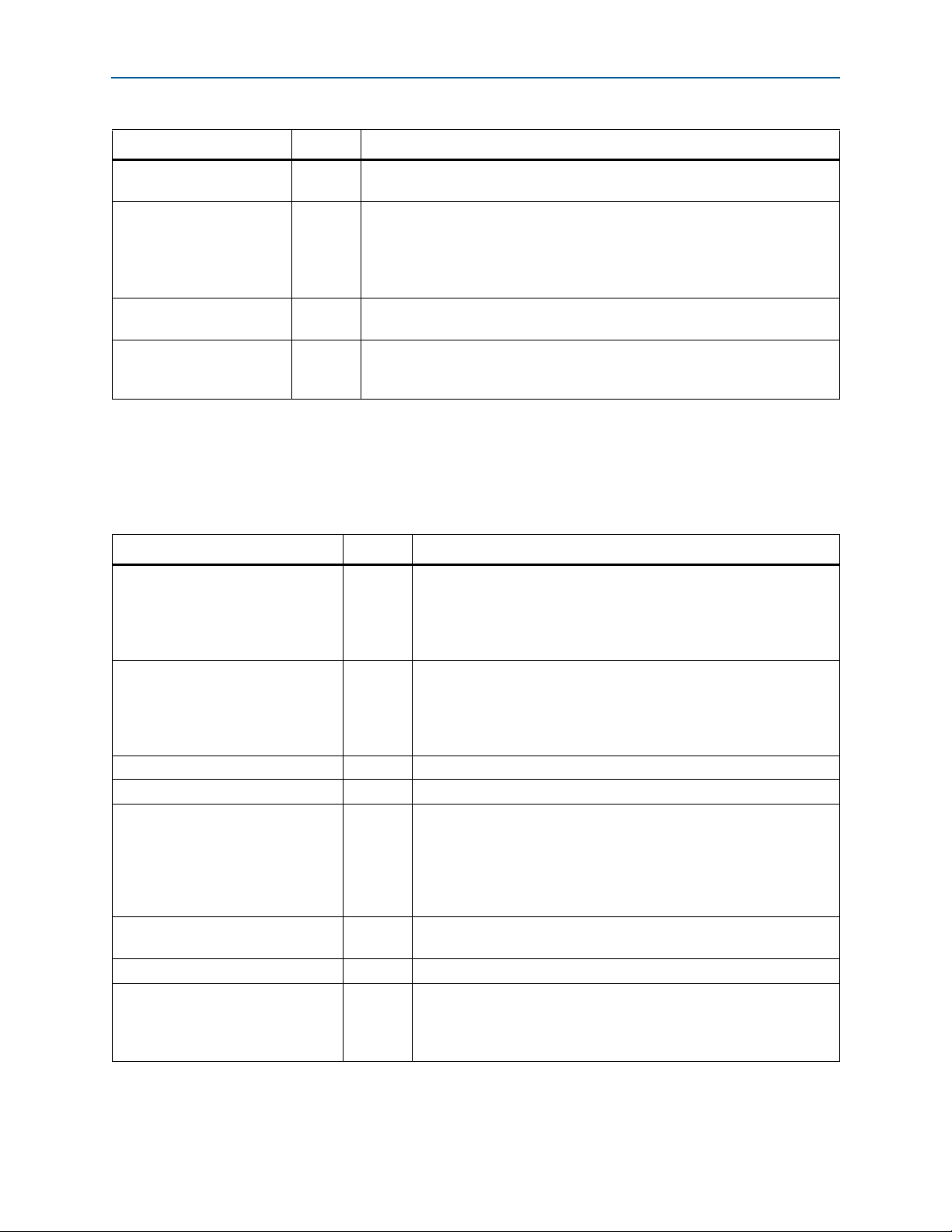

Tab le 1 –1 lists the theoretical raw bandwidth of the Interlaken MegaCore function in

the supported combinations of lane rate and number of lanes.

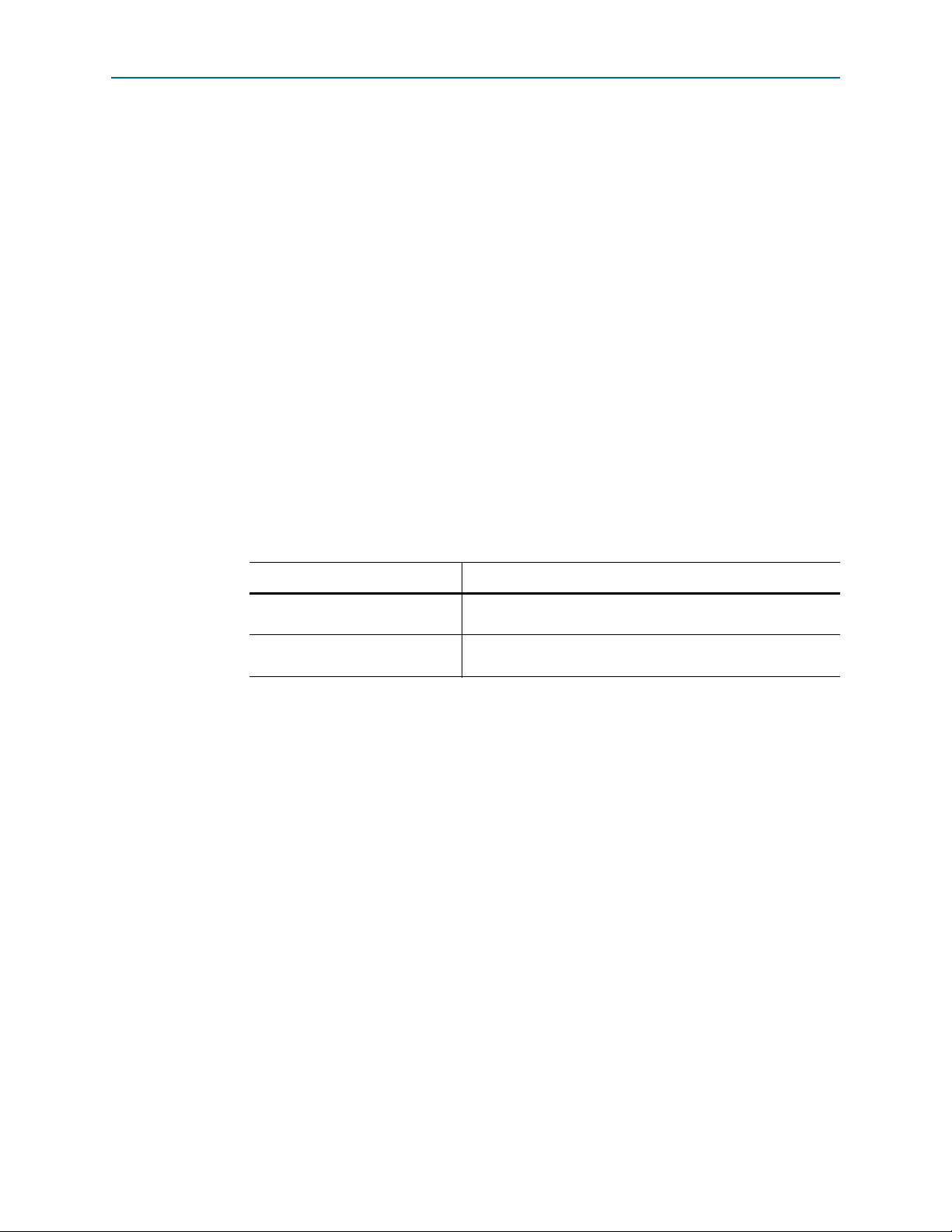

Table 1–1. Theoretical Raw Aggregate Bandwidth in Gbps

Number of Lanes

3.125 6.25 6.375 10.3125

4 12.50 25.00 25.50 —

8 25.00 50.00 51.00 —

10 — 62.50 63.75 —

12 — 75.00 76.50 123.75

20 — 125.00 127.50 —

Device Family Support

Tab le 1 –2 defines the device support levels for Altera IP cores.

Table 1–2. Altera IP Core Device Support Levels

FPGA Device Families HardCopy Device Families

Preliminary support—The core is verified with preliminary

timing models for this device family. The IP core meets all

functional requirements, but might still be undergoing timing

analysis for the device family. It can be used in production

designs with caution.

Final support—The IP core is verified with final timing

models for this device family. The IP core meets all

functional and timing requirements for the device family and

can be used in production designs.

Lane Rate (Gbps)

HardCopy Companion—The IP core is verified with

preliminary timing models for the HardCopy companion

device. The IP core meets all functional requirements, but

might still be undergoing timing analysis for the HardCopy

device family. It can be used in production designs with

caution.

HardCopy Compilation—The IP core is verified with final

timing models for the HardCopy device family. The IP core

meets all functional and timing requirements for the device

family and can be used in production designs.

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 9

Chapter 1: About This MegaCore Function 1–3

MegaCore Verification

Tab le 1 –3 shows the level of support offered by the Interlaken MegaCore function for

each Altera device family.

Table 1–3. Device Family Support

Device Family Support

Stratix IV GT

Stratix IV GX Final

Note to Tab le 1–3:

(1) Altera supports the 12-lane, 10-Gbps configuration in Stratix IV GT devices only.

(1)

Final

MegaCore Verification

Before releasing a version of the Interlaken MegaCore function, Altera runs

comprehensive regression tests in the current version of the Quartus

These tests use standalone methods and the Qsys system integration tool to create the

instance files. These files are tested in simulation and hardware to confirm

functionality. Altera tests and verifies the Interlaken MegaCore function in hardware

for different platforms and environments.

Constrained random techniques generate appropriate stimulus for the functional

verification of the MegaCore function. Functional coverage metrics measure the

quality of the random stimulus, and ensure that all important features are verified.

Performance and Resource Utilization

Tab le 1 –4 lists the resources and expected performance for different Interlaken

MegaCore function variations.

Tab le 1 –4 shows results obtained using the Quartus II software for the following

devices:

■ Stratix IV GT device EP4S100G5F45I1

■ Stratix IV GX devices EP4SGX530NF45C2 and EP4SGX530KH40C2

Resource utilization is shown for variations that include the transceiver and do not

include the out-of-band flow control block.

®

II software.

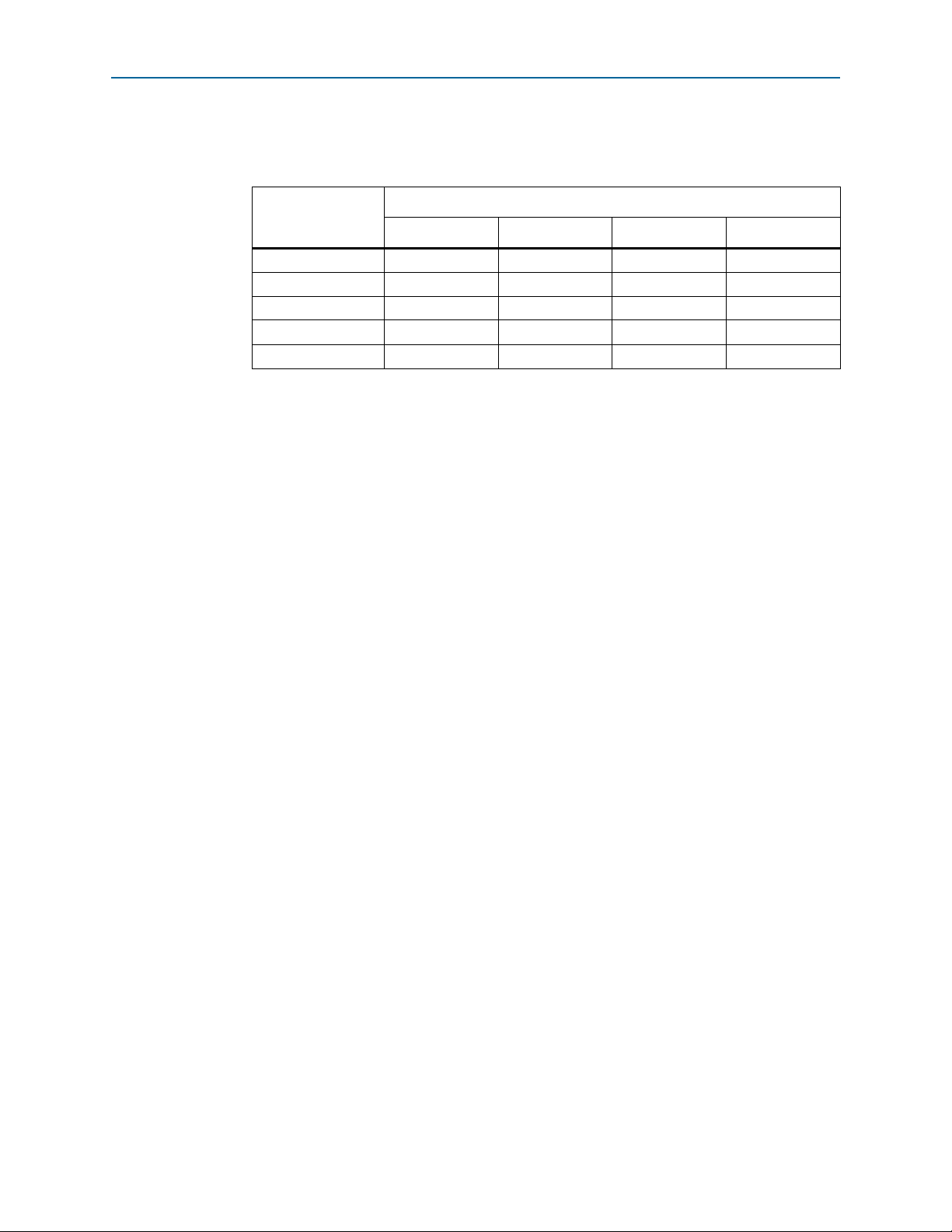

Table 1–4. Interlaken MegaCore Function FPGA Resource Utilization

Parameters Resource Utilization

Device

Stratix IV GX

EP4SGX530NF45C2

Stratix IV GX

EP4SGX530KH40C2

Stratix IV GT

EP4S100G5F45I1

June 2012 Altera Corporation Interlaken MegaCore Function

Number of

Lanes

4 6.25 12,229 16,774 52

8 6.25 24,825 31,776 68

10 6.25 29,949 38,033 96

20 6.25 63,033 77,806 159

12 10.3125 50,164 56,948 84

Per-Lane Data Rate

(Gbps)

Combinational

ALUTs

Logic Registers

M9K

Blocks

User Guide

Page 10

1–4 Chapter 1: About This MegaCore Function

Release Information

For all Interlaken MegaCore function variations that target a Stratix IV GX device,

Altera recommends that you target a C2 speed grade device. For all variations that

target a Stratix IV GT device, Altera recommends you target an I1 speed grade device.

In all cases, Altera recommends that you set the Optimization Technique in the

Analysis & Synthesis Settings dialog box to Speed.

f For information about how to apply the Speed setting, refer to volume 1 of the

Quartus II Handbook.

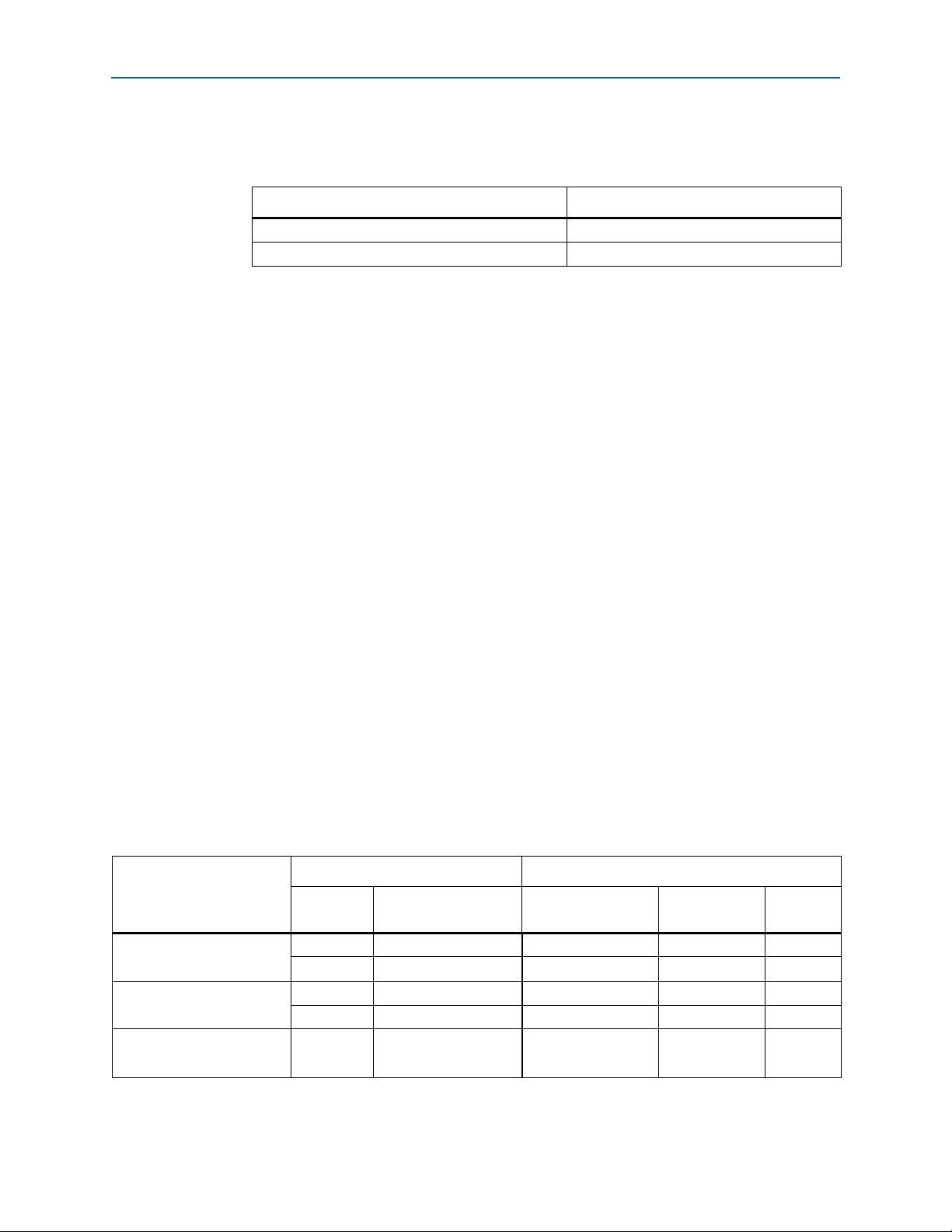

Release Information

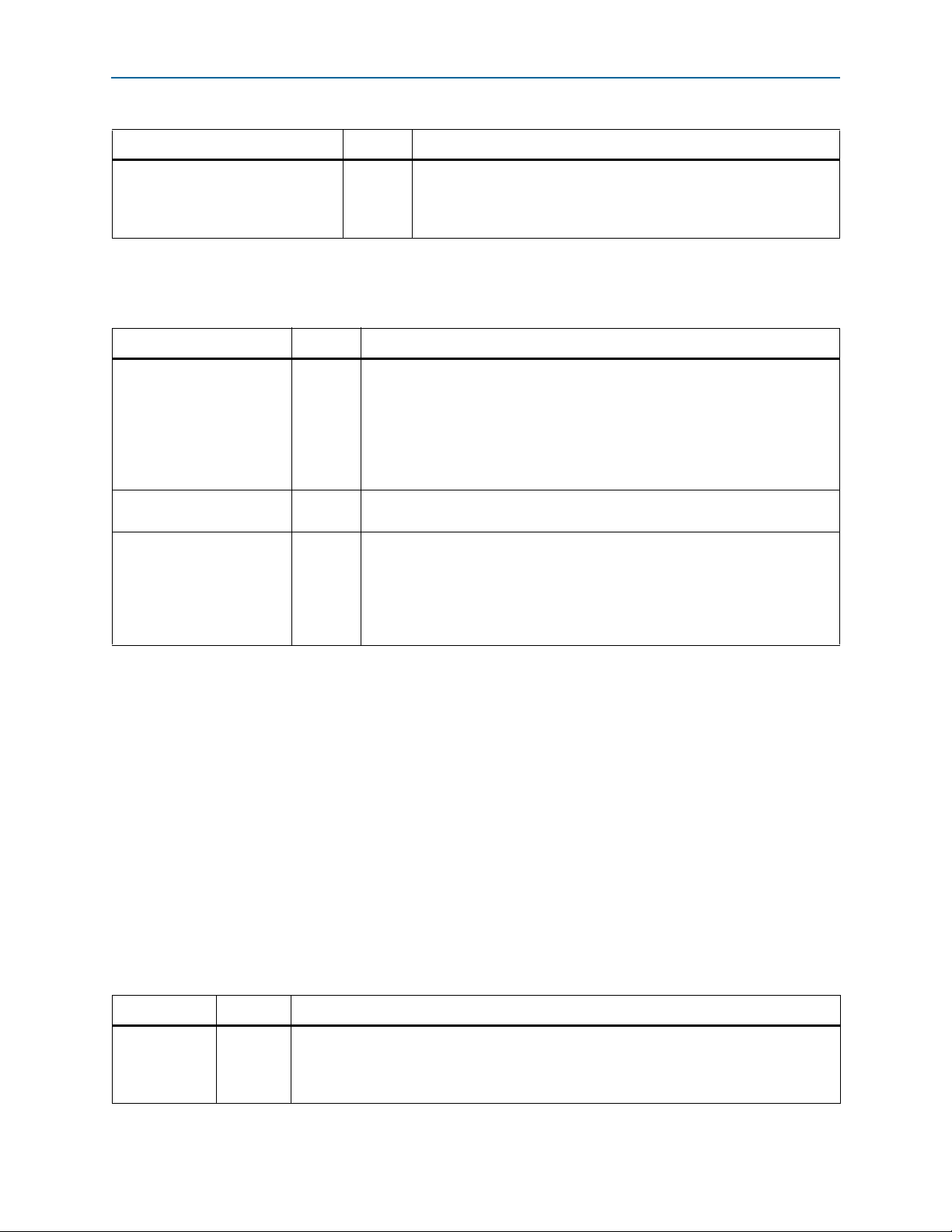

Tab le 1 –5 and Tab le 1 –6 provide information about this release of the Interlaken

MegaCore function. Tab le 1 –5 lists the release information common to all Interlaken

MegaCore function licenses.

Table 1–5. Interlaken MegaCore Function Release Information

Item Value

Version 12.0

Release Date June 2012

Vendor ID 6AF7

License Ordering Codes and Product IDs are listed in Table 1–6

Tab le 1 –6 lists the license information for this release of the Interlaken MegaCore

function.

Table 1–6. Interlaken MegaCore Function License Ordering Codes and Product IDs

License

20G License IP-INTLKN/20G/4L 00DA

40G License IP-INTLKN/40G/8L 00D5

100G Licenses

Note to Tab le 1–6:

(1) For information about the different licenses, refer to “Interlaken MegaCore Function Licenses” on page 1–5.

(1)

Altera verifies that the current version of the Quartus II software compiles the

previous version of each MegaCore function. Any exceptions to this verification are

reported in the MegaCore IP Library Release Notes and Errata. Altera does not verify

compilation with MegaCore function versions older than the previous release.

Installation and Licensing

The Interlaken MegaCore function is part of the MegaCore IP Library, which is

distributed with the Quartus II software and downloadable from the Altera website,

www.altera.com.

Ordering Code Product ID

IP-INTLKN/100G/20L 00D6

IP-INTLKN/100G/12L 00D4

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 11

Chapter 1: About This MegaCore Function 1–5

<path>

alt_interlaken

Contains the Interlaken MegaCore function files

common

Contains shared components

Installation directory

ip

Contains the Altera MegaCore IP Library and third-party IP cores

altera

Contains the Altera MegaCore IP Library

Installation and Licensing

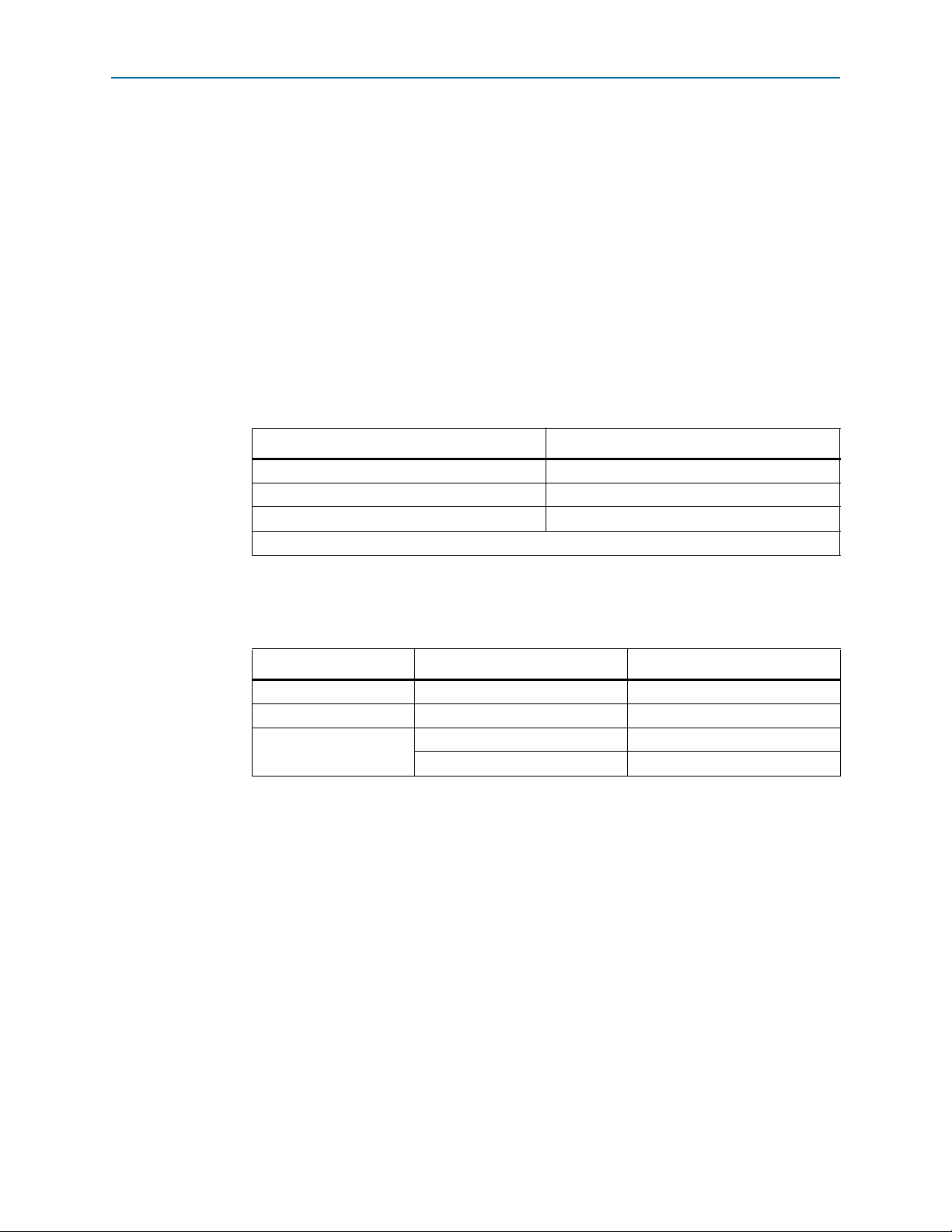

Figure 1–2 shows the directory structure after you install the Interlaken MegaCore

function, where

<

path> is the installation directory. The default installation directory

on Windows is C:\altera\<version number>; on Linux it is

/opt/altera<version number>.

Figure 1–2. Directory Structure

You can use Altera’s free OpenCore evaluation feature to evaluate the MegaCore

function in simulation before you purchase a license. You must purchase a license for

the MegaCore function only when you are satisfied with its functionality, and you

want to check performance in hardware and take your design to production.

After you purchase a license for the Interlaken MegaCore function, you can request a

license file from the Altera website at www.altera.com/licensing and install it on your

computer. When you request a license file, Altera emails you a license.dat file. If you

do not have internet access, contact your local Altera representative.

Interlaken MegaCore Function Licenses

The Altera Interlaken MegaCore function is available to you through several different

licenses, depending on the variation you wish to generate. Licensing is based

primarily on aggregate bandwidth. Tabl e 1– 7 shows the license required to program a

device with each supported variation.

Table 1–7. Interlaken MegaCore Function License Support

Number of

Lanes

4 IP-INTLKN/20G/4L IP-INTLKN/20G/4L IP-INTLKN/20G/4L —

8 IP-INTLKN/20G/4L IP-INTLKN/40G/8L IP-INTLKN/40G/8L —

10 — IP-INTLKN/40G/8L IP-INTLKN/40G/8L —

12 — IP-INTLKN/40G/8L IP-INTLKN/40G/8L IP-INTLKN/100G/12L

20 — IP-INTLKN/100G/20L IP-INTLKN/100G/20L —

3.125 6.25 6.375 10.3125

After you acquire a license, you can compile and program your device with all the

variations that require that license. However, to program a variation that requires a

different license, you must acquire the additional license. You can generate, simulate,

and compile all MegaCore function-supported variations without a license, because

the Interlaken MegaCore function supports the Altera OpenCore evaluation feature.

Lane Rate (Gbps)

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 12

1–6 Chapter 1: About This MegaCore Function

Installation and Licensing

OpenCore Evaluation

The Altera OpenCore evaluation feature allows you to generate RTL files and

simulation models, to simulate, and to compile to validate timing, but requires that

you acquire a license to generate a programming file with which to configure an

FPGA. Therefore, without a license for the variation your design includes, you cannot

create an SRAM Object File (.sof) or Programmer Object File (.pof) for programming a

device with your design. With the free OpenCore evaluation feature, you can perform

the following actions:

■ Simulate the behavior of a megafunction (Altera MegaCore function or AMPP

megafunction) in your system using the Quartus II software and Altera-supported

VHDL and Verilog HDL simulators.

■ Verify the functionality of your design and evaluate its size and speed quickly and

easily.

f For more information about installation and licensing, refer to Altera Software

Installation and Licensing.

SM

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 13

Design Flows

2. Getting Started

1 You can customize the Interlaken MegaCore

applications. You use the MegaWizard Plug-In Manager or the Qsys system

integration tool to instantiate this MegaCore function.

The MegaWizard Plug-In Manager flow offers the following advantages:

■ Allows you to parameterize the MegaCore function to create a variation that you

can instantiate manually in your design.

The Qsys flow offers the following advantages:

■ Allows you to integrate other Altera-provided custom components such as DMA

controllers, on-chip memories, and FIFOs in your design.

■ Provides visualization of hierarchical designs.

■ Allows customization of interconnect elements and pipelining.

function to support a wide variety of

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 14

2–2 Chapter 2: Getting Started

Design Flows

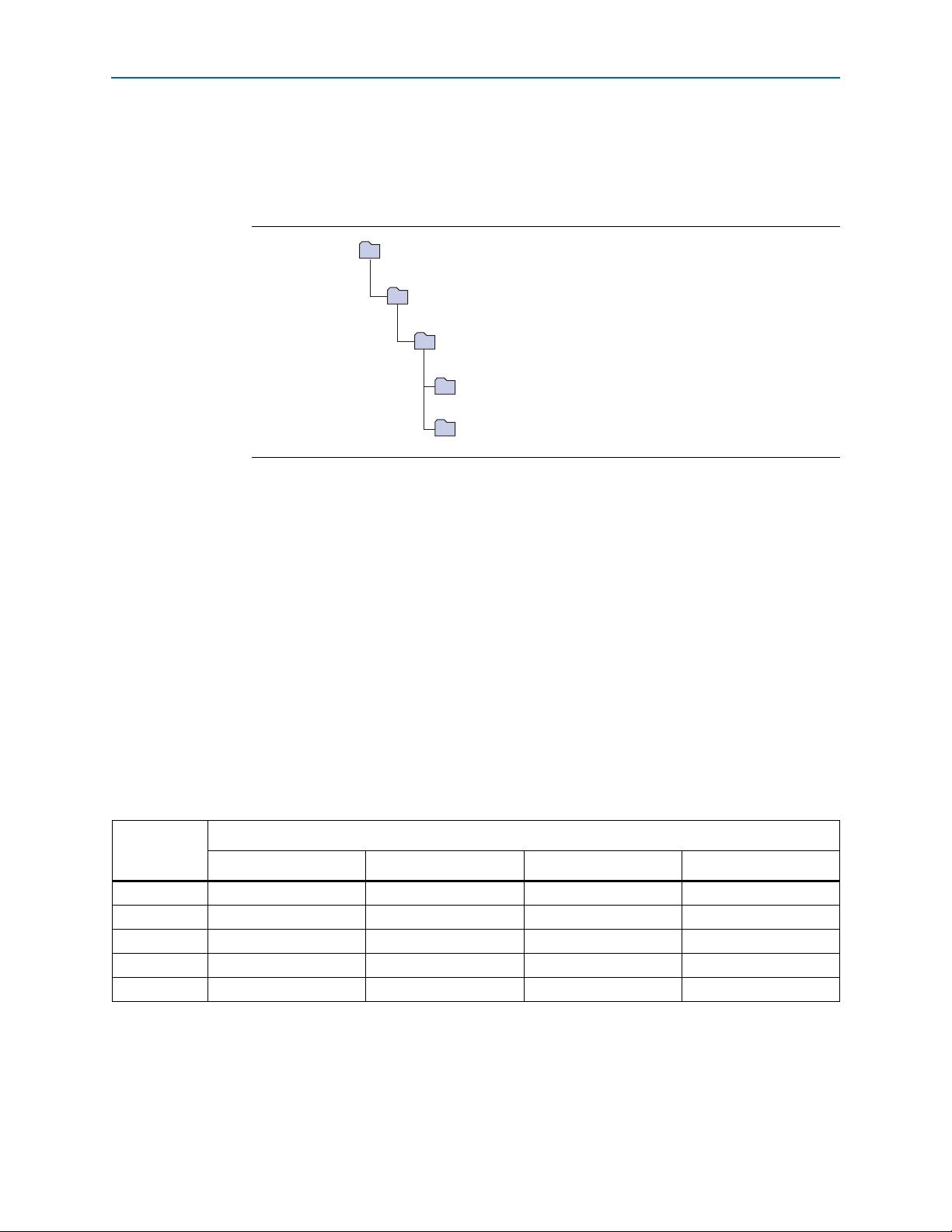

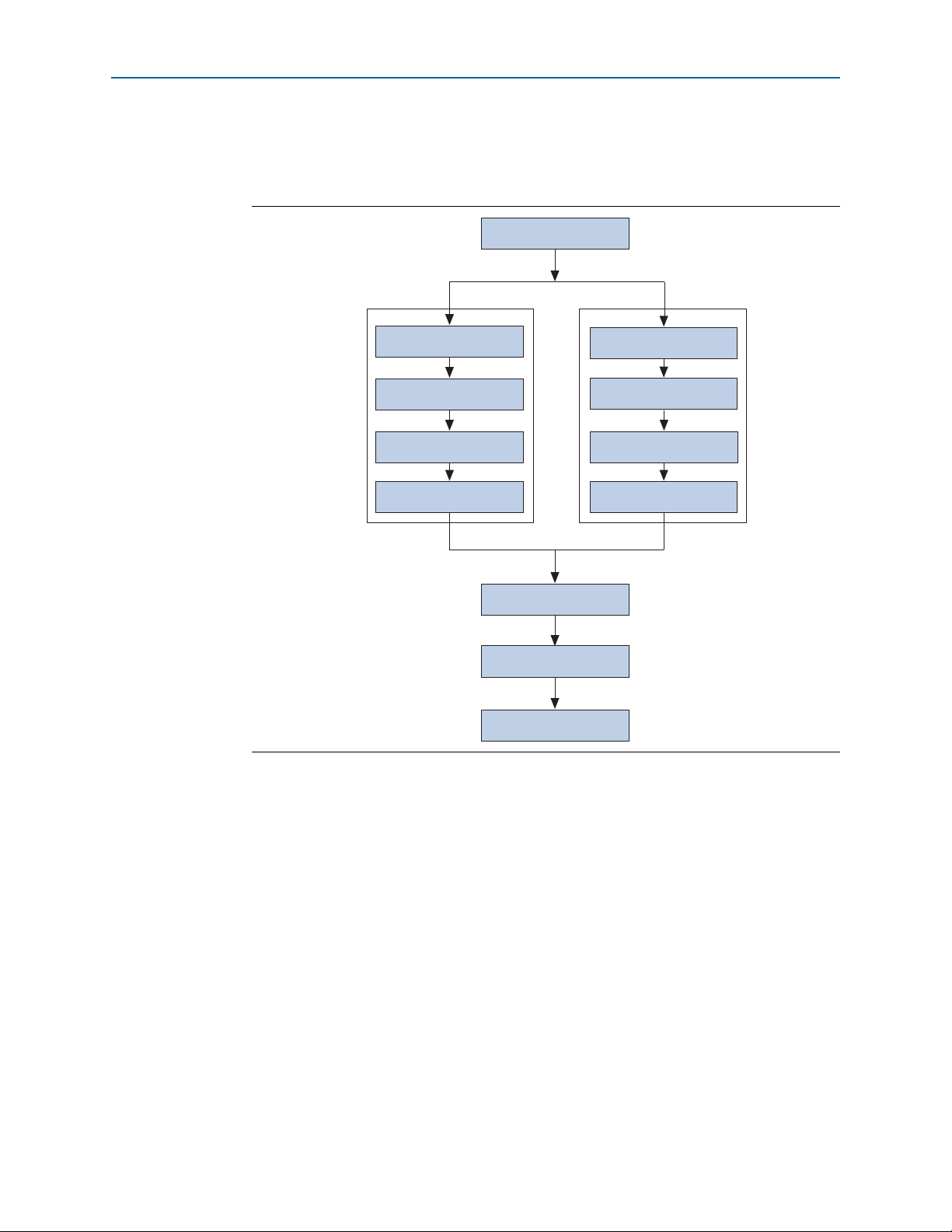

Figure 2–1 shows the stages for creating a system with the Interlaken MegaCore

function and the Quartus II software. Each stage is described in detail in subsequent

sections.

Figure 2–1. Interlaken MegaCore Function Design Flow

Select Design Flow

MegaWizard Plug-in

Manager Flow

Qsys Flow

Specify Parameters

Generate

MegaCore Function

Simulate with

Testbench

Instantiate MegaCore

In Design

Specify Constraints

Compile Design

Program Device

Specify Parameters

Complete Qsys System

Generate Qsys System

Simulate System

MegaWizard Plug-In Manager Design Flow Summary

You can use the MegaWizard Plug-In Manager in the Quartus II software to

parameterize a custom MegaCore function variation. The Interlaken parameter editor

lets you interactively set parameter values and select optional ports. This flow is best

for manual instantiation of a MegaCore function in your design.

Qsys Design Flow Summary

The Qsys design flow enables you to integrate an Interlaken component in a Qsys

system. The Qsys design flow allows you to connect component interfaces with the

system interconnect, eliminating the requirement to design low-level interfaces and

significantly reducing design time. When you add an Interlaken MegaCore function

instance to your design, an Interlaken parameter editor guides you in selecting the

properties of the Interlaken MegaCore function instance.

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 15

Chapter 2: Getting Started 2–3

MegaWizard Plug-in Manager Design Flow

MegaWizard Plug-in Manager Design Flow

The MegaWizard Plug-in Manager flow allows you to customize the Interlaken

MegaCore function, and manually integrate the function in your design.

Specifying Parameters and Generating the MegaCore Function

To specify Interlaken MegaCore function parameters using the MegaWizard Plug-In

Manager, perform the following steps:

1. Create a Quartus II project using the New Project Wizard available from the File

menu. Ensure that you target a device family supported by the Interlaken

MegaCore function.

2. Launch the MegaWizard Plug-in Manager from the Tools menu, and follow the

prompts in the MegaWizard Plug-In Manager interface to create a custom

megafunction variation.

1 To select the Interlaken MegaCore function, click

Installed Plug-Ins > Interfaces > Interlaken > Interlaken v<version>.

3. Specify the parameters in the Interlaken parameter editor. For details about these

parameters, refer to Chapter 3, Parameter Settings.

4. Click Finish to generate the MegaCore function and supporting files.

IEEE encrypted functional simulation models for the simulators listed in the

Simulating Altera Designs chapter in volume 3 of the Quartus II Handbook are

included in the supporting files. The models appear in a set directory hierarchy in

the project directory. The functional simulation model is a cycle-accurate VHDL or

Verilog HDL model produced by the Quartus II software.

c Use the simulation models only for simulation and not for synthesis or any

other purposes. Using these models for synthesis creates a nonfunctional

design.

5. If you generate the Interlaken MegaCore function instance in a Quartus II project,

you are prompted to add the Quartus II IP File (.qip) to the current Quartus II

project. You can also turn on Automatically add Quartus II IP Files to all projects.

The .qip contains information about the generated IP core. In most cases, the .qip

contains all of the necessary assignments and information required to process the

MegaCore function or system in the Quartus II compiler. The MegaWizard Plug-In

Manager generates a single .qip for each MegaCore function.

6. Click Exit to close the MegaWizard Plug-In Manager.

You can now simulate your custom MegaCore function variation, integrate it in your

design, and compile.

Simulating the Interlaken MegaCore Function

You can simulate your Interlaken MegaCore function variation using any of the

vendor-specific IEEE encrypted functional simulation models which are generated in

the new <instance name>_sim subdirectory of your project directory.

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 16

2–4 Chapter 2: Getting Started

Qsys Design Flow

You cannot simulate the Interlaken MegaCore function in the ModelSim-Altera

(ModelSim-AE) simulator. ModelSim-AE is the simulation tool provided with the

Quartus II software.

f

Quartus II software See the Quartus II Help topics:

MegaWizard Plug-In Manager

Functional simulation models for Altera IP

cores

For Information About Refer To

“About the Quartus II Software”

“About the MegaWizard Plug-In Manager”

Simulating Altera Designs chapter in volume 3 of

the Quartus II Handbook

Instantiating the MegaCore Function in Your Design

After you generate your Interlaken MegaCore function variation, you can instantiate

it in the RTL for your design.

When you integrate your Interlaken MegaCore function variation in your design, note

the following connection and assignment requirements and recommendations:

■ If you turn off Exclude transceiver when you parameterize your Interlaken

MegaCore function, you must ensure that you connect the calibration clock

cal_blk_clk

10–125 MHz. The

transceiver block must be connected to the same clock signal.

■ If you turn off Exclude transceiver when you parameterize your Interlaken

MegaCore function, you should set the RTL parameter

improve your transceiver simulation time. In this version of the Interlaken

MegaCore function, you must modify your RTL files to set the parameter. Add this

parameter to the parameter list in your HSIO bank instances with the value 1’b1.

The HSIO bank instances for the different variations are instantiations of the

modules

alt_ntrlkn_hsio_bank_bpcs_3g

to a clock signal with the appropriate frequency range of

cal_blk_clk

ports on other components that use the same

alt_ntrlkn_hsio_bank_bpcs4, alt_ntrlkn_hsio_bank_10g

, or

alt_ntrlkn_hsio_bank_pmad5

SIM_FAST_RESET

,

.

to 1 to

Qsys Design Flow

You can use Qsys to build a system that contains your customized Interlaken

MegaCore function. You can easily add other components and quickly create a Qsys

system. Qsys can automatically generate HDL files that include all of the specified

components and interconnections. The HDL files are ready to be compiled by the

Quartus II software to produce output files for programming an Altera device.

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 17

Chapter 2: Getting Started 2–5

Qsys Design Flow

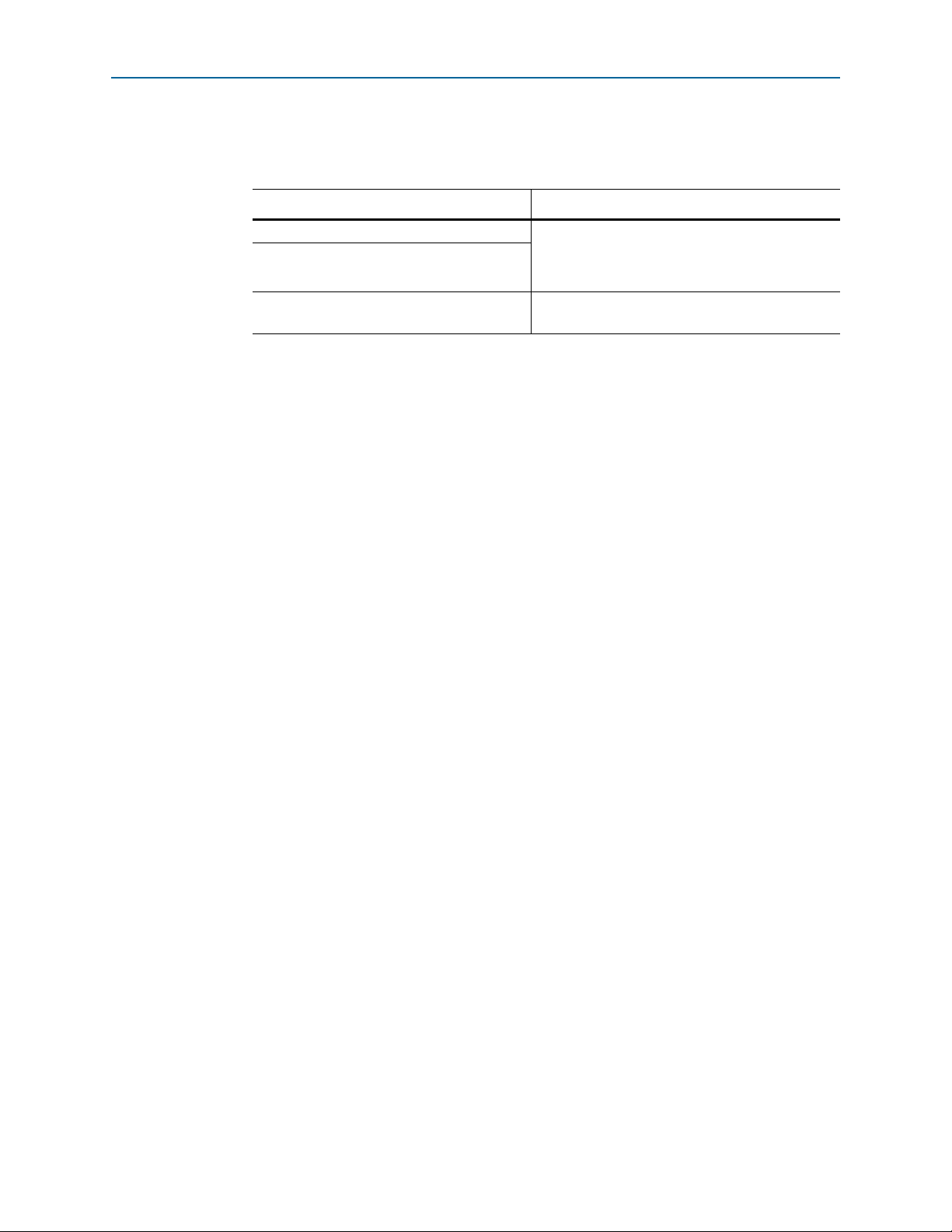

Figure 2–2 shows a block diagram of an example Qsys system.

Figure 2–2. Qsys System

Interlaken

Link Partner

Interlaken

MegaCore Function

Avalon Streaming Connection Avalon Streaming Connection

f

DMA

Controller

Interlaken

Client

System Interconnect

On-Chip

FIFO Buffer

Qsys System

Interlaken

Client

For Information About Refer To

System interconnect

Qsys tool

Qsys Interconnect chapter in volume 1 of the Quartus II

Handbook and the Avalon Interface Specifications

Creating a System with Qsys in volume 1 of the Quartus II

Handbook

Quartus II software Quartus II Help

On-Chip

Memory

Specifying Parameters

To specify Interlaken MegaCore function parameters using the Qsys flow, perform the

following steps:

1. Create a new Quartus II project using the New Project Wizard available from the

File menu.

2. On the Tools menu, click Qsys.

3. On the Component Library tab, expand Interface Protocols > Interlaken and

highlight Interlaken.

4. Click Add to add an Interlaken MegaCore function to your system. The Interlaken

parameter editor appears.

5. Specify the parameters in the Interlaken parameter editor. For detailed

explanations of these parameters, refer to Chapter 3, Parameter Settings.

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 18

2–6 Chapter 2: Getting Started

6. Click Finish to complete the Interlaken MegaCore function and add it to the

system.

Qsys Design Flow

Completing the Qsys System

To complete the Qsys system, perform the following steps:

1. Add and parameterize any additional components.

2. Connect the components using the Connection panel on the System Contents tab.

3. If some signals are not displayed, click the Filter icon to display the Filters dialog

box. In the Filter list, click All Interfaces.

4. Ensure your Qsys system meets the connection and assignment requirements

listed in “Specifying Parameters and Generating the MegaCore Function” on

page 2–3.

5. If you intend to simulate your Qsys system, on the Generation tab, set Generate

simulation model to Ve r il o g to generate a functional simulation model in Verilog

HDL.

6. Click Generate to generate the system. Qsys generates the system and produces a

system .qip file, <system name>.qip, that contains the assignments and information

required to process the IP cores and system in the Quartus II Compiler. The file is

located in the <project name>/synthesis subdirectory.

7. In the Quartus II software, in the Project menu, click Add/Remove Files in Project

and add the

<system name>.qip file to the project.

Simulating the System

During system generation, Qsys optionally generates various IEEE encrypted

functional simulation models for the Interlaken MegaCore function and functional

simulation models for other components in the Qsys system. You can use these

simulation models to simulate your system with your supported simulation tool.

In addition, you can simulate the static design example that is provided in Verilog

HDL. The static design example is available for several Interlaken MegaCore function

variations. Refer to Chapter 6, Qsys Design Examples.

The design examples are located in the design_examples subdirectory of the

alt_interlaken installation directory. Each testbench provides some basic stimulus to

the user interfaces of the Interlaken MegaCore function. You can use the example as a

basis for your own system simulation.

f For information about simulating Qsys systems, refer to the Creating a System with

Qsys chapter in volume 1 of the Quartus II Handbook.

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 19

Chapter 2: Getting Started 2–7

Specifying Constraints

Specifying Constraints

Altera provides a Synopsys Design Constraints (.sdc) file that you must apply to

ensure that the Interlaken MegaCore function meets design timing requirements. The

script automatically constrains the system clocks and the reference clock based on the

data rate you specify. If your design includes multiple instances of the Interlaken

MegaCore function, you must edit the .sdc file to ensure that each instance name

appears correctly in the file.

The Quartus II software v12.0 requires that you add the following additional

constraints manually:

■ Hard PLL Assignment Constraints

■ I/O Standard Constraints

The following sections describe the constraints you must add manually.

Hard PLL Assignment Constraints

The .sdc script provided with the Quartus II software v12.0 requires that you add

hard PLL assignment constraints to the Quartus Settings File (.qsf) before you

compile your design. You can add these constraints directly to the .qsf, or you can use

the Quartus II Assignment Editor.

You must add the following hard transceiver PLL assignments before compilation:

set_location_assignment IOBANK_<quad_location> -to <PLL_path>

where

■

<quad_location>

is any valid quad location on your device. It may be any of QLn

or QRn, for n in {0,1,2,3}, depending on the device

■

<PLL_path>

for any valid high-speed I/O (HSIO) bank number

is

"*|lt_ntrlkn_hsio_bank_*:alt_ilk_hsio_bank_<n>|*|tx_pll*0"

<n>

The valid HSIO bank numbers depend on the number of lanes in your Interlaken

MegaCore function variation. Table 2–1 shows the valid HSIO bank numbers.

Table 2–1. Valid HSIO Bank Numbers Depending on Number of Lanes

Number of Lanes

0123

4 v ———

8 vv——

10 vv——

12 vvv—

20 vvvv

Valid HSIO Bank Numbers

To add the constraint using the Assignment Editor, perform the following steps:

1. Open your Quartus II project in the Quartus II software.

2. On the Processing menu, point to Start and click Start Analysis & Elaboration.

The analysis and elaboration process might take several minutes to complete.

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 20

2–8 Chapter 2: Getting Started

Specifying Constraints

3. On the Assignments menu, click Assignment Editor.

4. Click <<new>> to edit a new assignment.

5. Double-click the new row in the Assignment Name column and select Location.

6. Double-click the new row in the To column.

7. Click the Node Finder icon. The Node Finder dialog box appears.

8. Ensure that Filter is set to Design Entry (all names).

9. To fill the Named field, follow one of these steps:

■ If the number of lanes in your Interlaken MegaCore function is 10 or 20, in the

Named field, type

■ If the number of lanes in your Interlaken MegaCore function is 4, 8, or 12, in the

Named field, type

*tx_pll_edge0

*tx_pll0

10. Click List.

11. Highlight each node found and click the right-arrow icon to move it from the

Nodes Found list to the Selected Nodes list.

12. Click OK. All the selected nodes appear in separate rows in the Assignment

Editor, with Assignment Name set to Location.

13. For each new row, perform the following steps:

a. Double-click the new row in the Va l u e column and click the Browse icon. A

Location dialog box appears.

b. For Element, select I/O bank.

c. For Location, select IOBANK_Q<m> for your preferred value <m>.

You must preserve the lane order in assigning IO banks, keeping in mind the

requirement that 10- and 20-lane variations use five transceivers in each

transceiver block, and the other variations use four transceivers in each

transceiver block. Refer to “High-Speed I/O Block” on page 4–22.

d. Click OK. The value you selected appears in the Va l ue column.

f For more information about timing analyzers, refer to the Quartus II Help and The

Quartus II TimeQuest Timing Analyzer chapter in volume 3 of the Quartus II Handbook.

I/O Standard Constraints

The Interlaken MegaCore function implements the transceivers with the

programmable transmitter output buffer power (VCCH TX) set to 1.4 V. Therefore, the

MegaCore function requires that you connect the Interlaken interface signals to pins

that implement the 1.4-V PCML I/O standard. This setting increases the data rate

range of the Interlaken interface. On a Stratix IV GX device, this requirement might

not be implemented automatically. If your design includes high-speed transceivers,

you should enforce this requirement manually.

To enforce this requirement, after you generate the system, perform the following

steps:

1. In the Quartus II window, on the Assignments menu, click Assignment Editor.

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 21

Chapter 2: Getting Started 2–9

Compiling the Full Design and Programming the FPGA

2. For each N, perform the following steps:

a. In the <<new>> cell in the To column, type the top-level signal name for your

Interlaken MegaCore function instance

rx_serial_dataN_export

signal.

b. Double-click in the Assignment Name column and click I/O Standard.

c. Double-click in the Va l ue column and click 1.4-V PCML.

3. Repeat step 2 for your Interlaken MegaCore function instance

tx_serial_dataN_export

signals.

Compiling the Full Design and Programming the FPGA

You can use the Start Compilation command on the Processing menu in the

Quartus II software to compile your design.

The 10- and 20-lane Interlaken MegaCore function variations require fine tuning to

achieve timing closure. Refer to Appendix C, Closing Timing on 10- and 20-lane

Designs for a list of steps you can implement to improve timing.

After successfully compiling your design, program the target Altera device with the

Programmer and verify the design in hardware. Programming the device requires

that you have a license for your Interlaken MegaCore function variation. Refer to

“Interlaken MegaCore Function Licenses” on page 1–5.

f

For Information About Refer To

Compiling your design

Programming the device

Quartus II Incremental Compilation for Hierarchical and TeamBased Design chapter in volume 1 of the Quartus II Handbook

Quartus II Programmer chapter in volume 3 of the Quartus II

Handbook

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 22

2–10 Chapter 2: Getting Started

Compiling the Full Design and Programming the FPGA

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 23

3. Parameter Settings

Customize the Interlaken MegaCore function by specifying parameters in the

Interlaken parameter editor, which you access from the MegaWizard Plug-In Manager

or from the Qsys tool in the Quartus II software.

This chapter describes the parameters and how they affect the behavior of the

MegaCore function. To customize your Interlaken MegaCore function, you can

modify parameters to specify the following properties:

■ Operational mode

■ Number of lanes

■ Lane rate

■ Meta frame length

■ Whether the MegaCore function includes or excludes the transceiver

■ Whether the MegaCore function enables out-of-band flow control

■ Number of pages of in-band flow control calendar bits

■ Whether the BurstMax and BurstShort parameters are dynamically configurable

■ BurstMax value, if not dynamically configurable

■ BurstShort value, in variations with a datapath width of 512 bits, if not

dynamically configurable

General Parameters

This section lists the basic parameters that affect the configuration of the Interlaken

MegaCore function.

Operational Mode

The Operational mode parameter specifies whether the MegaCore function is

configured to support simultaneous bidirectional communication. The operational

mode with simultaneous bidirectional communication is called duplex mode. The

current version of the MegaCore function supports only Duplex mode.

Number of Lanes

The Number of lanes parameter specifies the number of lanes available for Interlaken

communication. Supported values are 4, 8, 10, 12, and 20.

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 24

3–2 Chapter 3: Parameter Settings

General Parameters

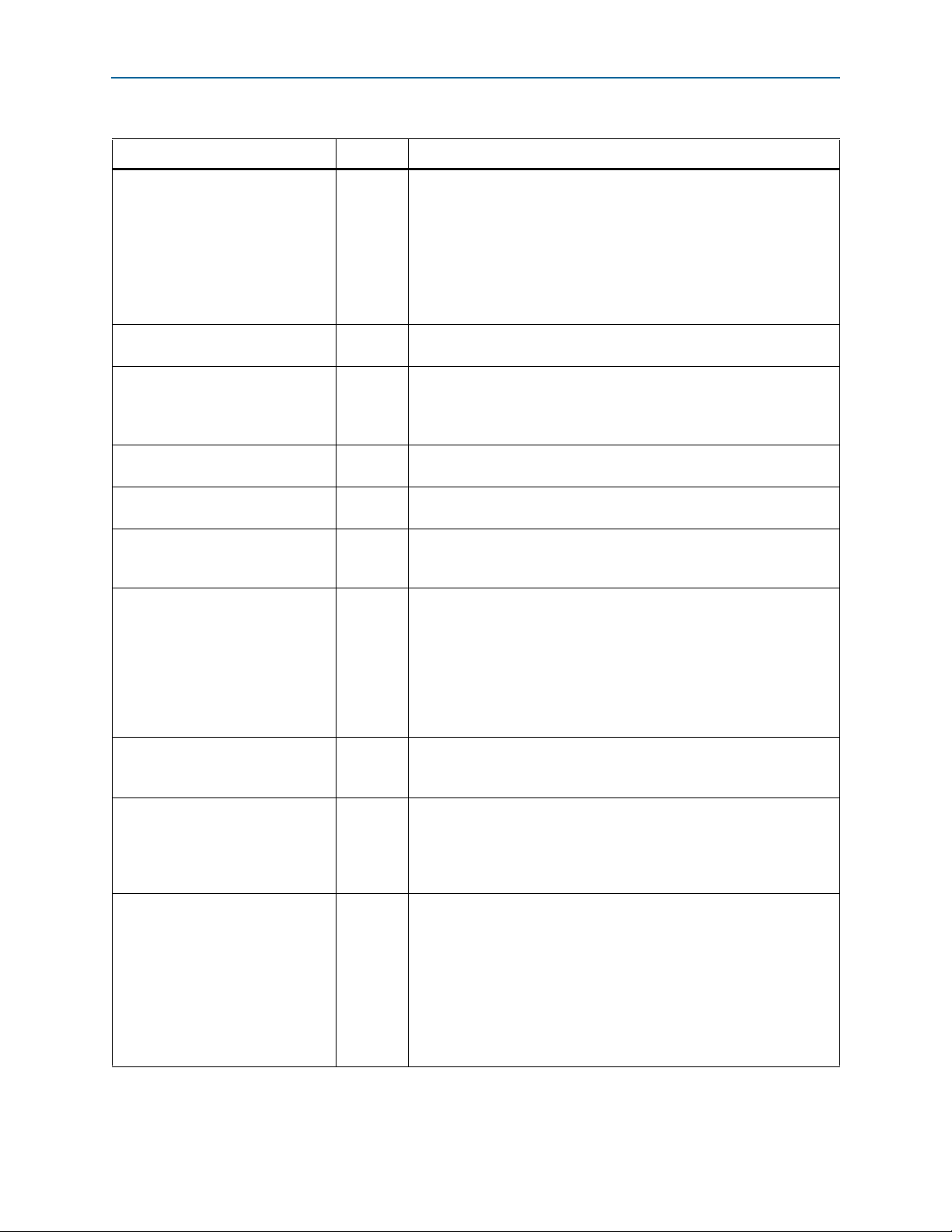

The Interlaken MegaCore function supports only some combinations of number of

lanes and lane rate. Tab le 3 –1 shows the supported combinations.

Table 3–1. Supported Combinations of Number of Lanes and Lane Rate

Number of Lanes

3.125 6.25 6.375 10.3125

4 vvv—

8 v v v —

10 — vv—

12 — vvv

20 — vv—

Lane Rate (Gbps)

1 The Interlaken parameter editor does not enforce the license restrictions. If you

specify a supported combination that your set of licenses does not allow, compilation

does not generate a programming file.

For information about the lane number and lane rate combinations supported by the

different Interlaken IP licenses, refer to “Installation and Licensing” on page 1–4.

Lane Rate

The Lane rate parameter specifies the data rate on each lane. All lanes have the same

data rate.

The Interlaken MegaCore function supports only certain combinations of number of

lanes and lane rate. Refer to Table 3–1. For information about the device support for

different combinations, refer to Table 1–3 on page 1–3.

1 The Interlaken parameter editor does not enforce the license restrictions. If you

specify a supported combination that your set of licenses does not allow, compilation

does not generate a programming file.

For information about the lane number and lane rate combinations supported by the

different Interlaken IP licenses, refer to “Installation and Licensing” on page 1–4.

Number of Words in Meta Frame

The Meta frame length in words parameter specifies the length of the meta frame, in

64-bit (8-byte) words. In the Interlaken specification, this parameter is called the

MetaFrameLength parameter.

Smaller values for this parameter shorten the time to achieve lock. Larger values

reduce overhead while transfering data, after lock is achieved. For information about

achieving lock, refer to Appendix A, Initializing the Interlaken MegaCore Function.

Exclude Transceiver

Turn o n th e Exclude transceiver parameter to specify that your Interlaken MegaCore

function does not include an HSIO block. By default, this parameter is turned off.

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 25

Chapter 3: Parameter Settings 3–3

In-Band Flow Control Parameters

If this parameter is turned on, the Interlaken MegaCore function simulation model

and the Interlaken MegaCore function generated RTL both exclude the transceivers.

This option is available to you for faster simulation. However, if you exclude the

transceivers from your Interlaken MegaCore function, you must regenerate and

compile with the parameter turned off to create your programming file.

Enable Out-of-Band Flow Control

Turn o n th e Enable out-of-band flow control parameter to specify that your

Interlaken MegaCore function includes out-of-band flow control functionality. By

default, this parameter is not turned on.

Turning off out-of-band flow control decreases the resource utilization of your

Interlaken MegaCore function, and excludes this optional specification feature.

For more information about the out-of-band flow control block, refer to “Out-of-Band

Flow Control Block” on page 4–24.

In-Band Flow Control Parameters

This section lists the parameters that affect the in-band flow control configuration.

Expose Calendar Ports

Turn o n th e Expose calendar ports parameter to specify that the in-band flow control

calendar bits are available on input and output signals of the Interlaken MegaCore

function. If you expose the calendar ports, you are able to view the in-band flow

control RX calendar bits, and you are responsible for specifying the values of the

in-band flow control TX calendar bits that appear in bits [55:40] of the control words

you transmit on the Interlaken link.

If you turn off the Expose calendar ports parameter, a single 16-bit page of in-band

flow control calendar information is included in the Interlaken control words, and the

Interlaken MegaCore function uses only two of those bits. For more information about

the Interlaken MegaCore function behavior when calendar ports are configured and

when they are not, refer to “Calendar and Status Block” on page 4–20.

For information about the calendar port signals, refer to Table 5–6 on page 5–5 and

Table 5–8 on page 5–7.

Number of Sixteen-Bit Calendar Pages

The Width of calendar ports, in 16-bit pages parameter specifies the number of 16-bit

pages of in-band flow control data your Interlaken MegaCore function supports.

Supported values are 1, 8, and 16. You can modify this number from its default value

of 1 only if you turn on the Expose calendar ports parameter.

Burst Parameters

This section lists the parameters that affect the value and dynamic configurability of

the BurstMax and BurstShort Interlaken parameters.

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 26

3–4 Chapter 3: Parameter Settings

Burst Parameters

Enable Dynamic Configuration of BurstMax and BurstShort Parameters

Turn o n th e Enable dynamic burst parameters parameter to enable dynamic

configuration of the BurstMax and BurstShort Interlaken parameters. If you turn on

this option, your Interlaken MegaCore function has additional input ports you set

dynamically to the desired values of the two Interlaken parameters. Supported values

are BurstMax values of 128 and 256 bytes and BurstShort values of 32 and 64 bytes.

Dynamic configuration of BurstShort is restricted to 12-lane, 10.3125 Gbps and 20-lane

Interlaken MegaCore function variations, that is, the variations with a 512-bit wide

channel datapath. In other variations, whether you turn on Enable dynamic burst

parameters or not, BurstShort has a static value.

Refer to Table 5–8 on page 5–7 for information about the input ports for dynamic

configuration of BurstMax and BurstShort.

Parameterized Static BurstMax Value

If you disable dynamic configuration of the BurstMax and BurstShort parameters, you

can specify the static value of BurstMax that is configured in your Interlaken

MegaCore function with the BURST MAX length in bytes parameter. This parameter

is available if you turn off Enable dynamic burst parameters. Supported static

BurstMax length values are 128 bytes and 256 bytes.

Parameterized Static BurstShort Value

If you turn off Enable dynamic burst parameters, you can specify the static value of

BurstShort that is configured in your 12-lane, 10.3125 Gbps or 20-lane Interlaken

variation. In these Interlaken variations, the default value of the BurstShort Interlaken

parameter is 32 bytes, but you can specify with the BURST SHORT length in bytes

parameter that it be set to 64 bytes instead.

In other Interlaken MegaCore variations, if you turn off Enable dynamic burst

parameters, the static value of BurstShort is 16 bytes in variations with a 128-bit

datapath, and 32 bytes in variations with a 256-bit datapath, as shown in Table 4–1 on

page 4–3.

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 27

4. Functional Description

The Interlaken MegaCore function provides the functionality described in the

Interlaken Protocol Definition, Revision 1.2, and arbitration between two incoming

user-defined channels, and regroups received data to two outgoing user-defined

channels. This chapter describes the individual interfaces and main blocks of the

Interlaken MegaCore function and how data passes between them.

This chapter contains the following sections:

■ “Architecture Overview”

■ “Interfaces Overview”

■ “Clocking and Reset Structure” on page 4–5

■ “Transmit Path” on page 4–11

■ “Receive Path” on page 4–17

■ “Calendar and Status Block” on page 4–20

■ “High-Speed I/O Block” on page 4–22

■ “Out-of-Band Flow Control Block” on page 4–24

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 28

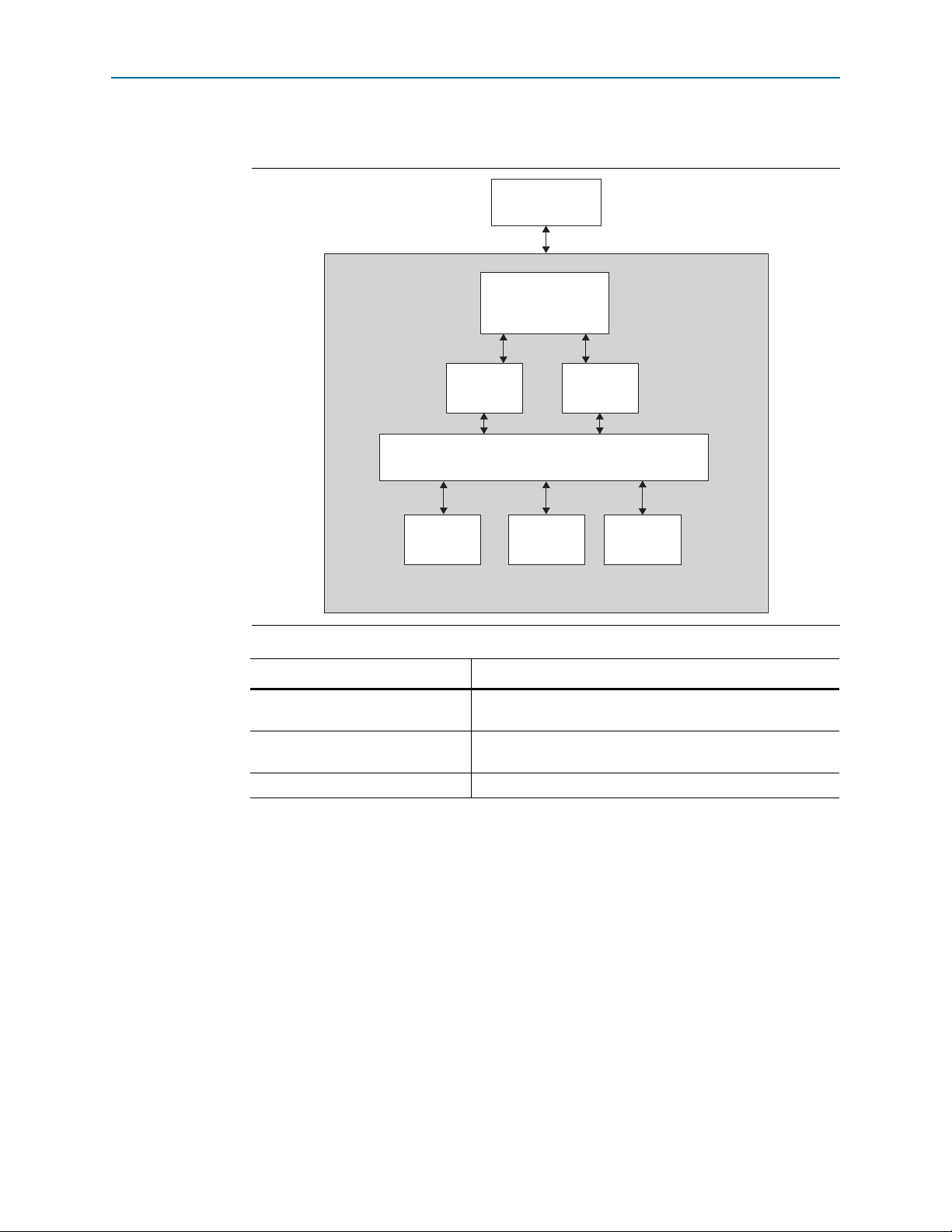

4–2 Chapter 4: Functional Description

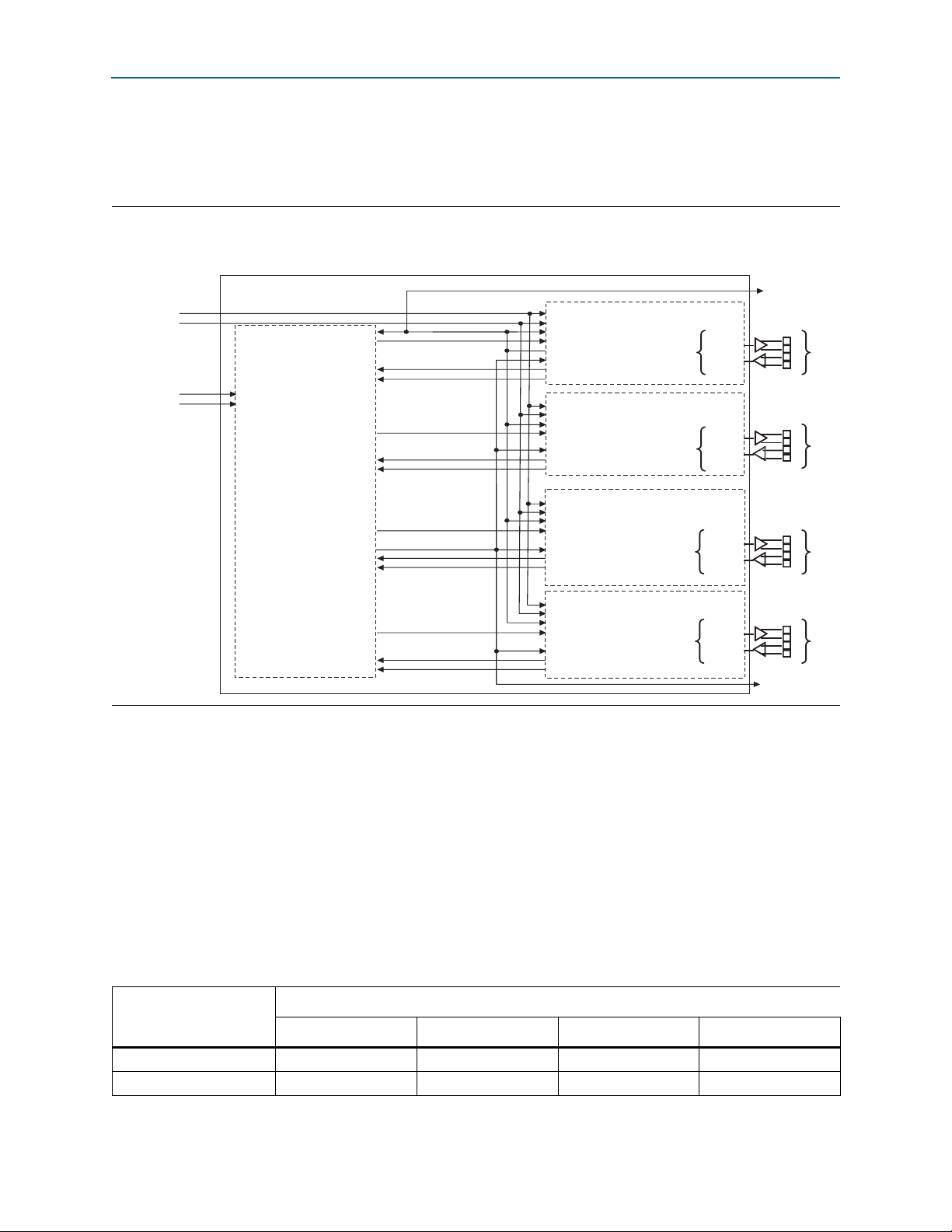

HSIO Block

Interlaken MegaCore Function

Application

Interface

FIFO and Pipeline Registers (10- and 20-lane variations only)

Transceiver Blocks

TX

PCS

TX

MAC

RX

PCS

RX

MAC

TX Out-of-Band

Flow Control

RX Out-of-Band

Flow Control

Calendar

and

Status

Filter

and

Buffer

Filter

and

Buffer

Packet

Regroup

Packet

Regroup

Arbiter

Channel 0

Channel 1

Channel 0

Channel 1

Calendar and

lane, link status

Out-of-Band Flow Control Block

Interlaken Interface

Out-of-Band

Flow Control

Interface

Architecture Overview

Architecture Overview

Figure 4–1 shows the main blocks of the Interlaken MegaCore function.

Figure 4–1. Interlaken MegaCore Function Block Diagram

The following sections describe the individual interfaces, clocks, and blocks.

Interfaces Overview

The Altera Interlaken MegaCore function supports the following interfaces:

■ Interlaken Interface

■ Application Interface

■ Out-of-Band Flow Control Interface

Interlaken Interface

The Interlaken interface complies with the Interlaken Protocol Definition, Revision 1.2. It

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

provides a high-speed transceiver interface to an Interlaken link.

Page 29

Chapter 4: Functional Description 4–3

Interfaces Overview

The Interlaken MegaCore function value for the Interlaken BurstMax parameter is

configurable. You can specify BurstMax to be dynamically configurable or you can

configure a static value in the Interlaken parameter editor, as described in Chapter 3,

Parameter Settings. The Interlaken MegaCore function supports two values for

BurstMax, 128 bytes and 256 bytes. The default static value is 128 bytes for all

variations.

The default value of BurstShort in Interlaken MegaCore function variations with a

512-bit wide datapath is 32 bytes. However, for these variations, you can specify

BurstShort to be dynamically configurable to 32 bytes or 64 bytes, or you can

configure a static value of 32 bytes or 64 bytes, as described in Chapter 3, Parameter

Settings.

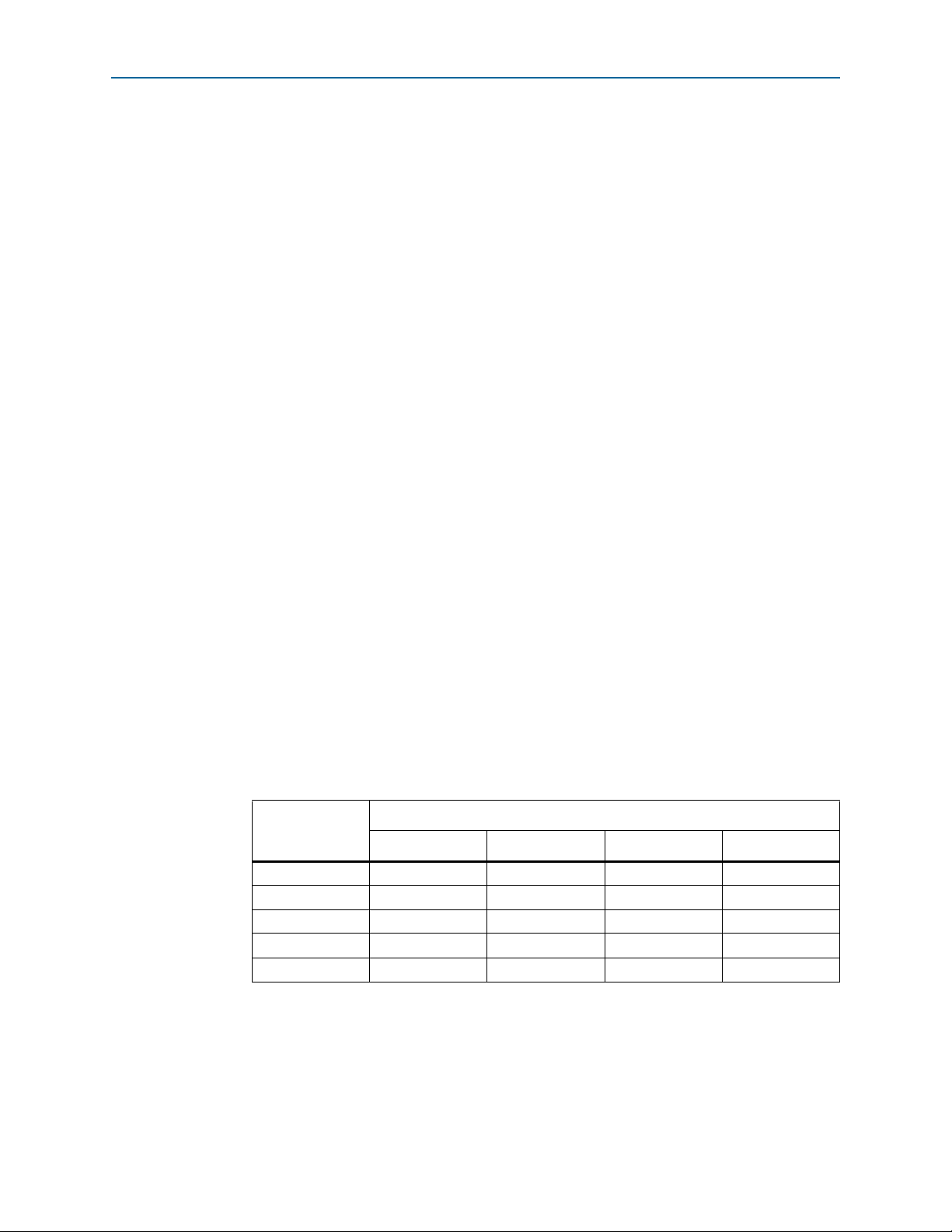

Tab le 4 –1 shows the Interlaken MegaCore function values for the Interlaken

BurstShort parameter.

Table 4–1. BurstShort Value in Bytes

Number of Lanes

Lane Rate (Gbps)

3.125 6.25 6.375 10.3125

416

816

(1)

(1)

16

(1)

16

(1)

32 32 —

—

10—3232—

12 — 32 32 32 or 64

20 — 32 or 64 32 or 64 —

Note to Tab le 4–1:

(1) The BurstShort value for Interlaken MegaCore function variations with a 128-bit wide datapath increases link

utilization while preventing multiple burst control words in the same clock cycle.

The Interlaken MegaCore function does not support BurstMin.

If you do not expose the in-band flow control calendar bits, the Interlaken MegaCore

function supports the following in-band flow control format for the RX and TX

calendar bits:

■ Bit 0: XON/XOFF bit for Channel 0

■ Bit 1: XON/XOFF bit for Channel 1

If you expose the calendar ports, the application determines the use of the in-band

flow control bits the MegaCore function receives on the incoming Interlaken link, and

the application is responsible for specifying the values of the in-band flow control bits

the MegaCore function transmits on the outgoing Interlaken link. In this case, you can

configure your MegaCore function to use 1, 8, or 16 pages of 16 calendar bits. For

more information, refer to “Calendar and Status Block” on page 4–20.

f The Interlaken Protocol Definition, Revision 1.2 is available from the Interlaken Alliance

website at www.interlakenalliance.com.

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 30

4–4 Chapter 4: Functional Description

If you turn on the Exclude transceiver parameter to generate a faster simulation

model, your functional simulation model’s interface to and from the Interlaken link

transceivers presents the data in slightly different format and exposes different clocks.

In addition, the application or testbench must implement the reset sequence. For more

information, refer to Appendix B, Excluding Transceivers for Faster Simulation.

Interfaces Overview

Application Interface

The application interface provides two channels of communication to and from the

Interlaken link. Each channel in each direction is implemented as an Avalon-ST

interface with one modification. The width of the Avalon-ST interfaces depends on

the number of lanes in the Interlaken MegaCore function instance.

Depending on the parameter values you set in the Interlaken parameter editor,

additional signals may be available to the application.

Avalon-ST Interface

The Avalon-ST interface provides a standard, flexible, and modular protocol for data

transfers from a source interface to a sink interface. The Avalon-ST interface protocol

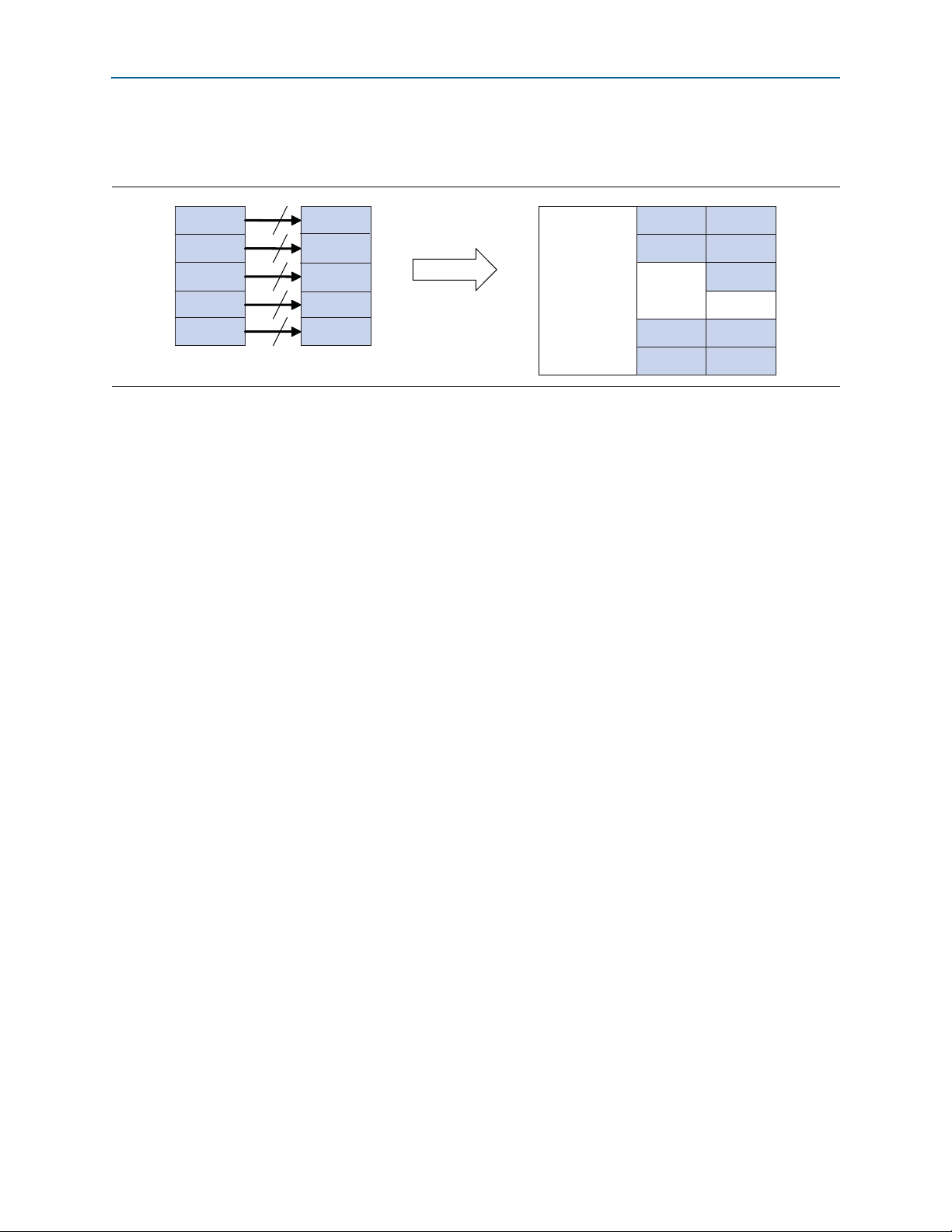

allows you to easily connect components to the Interlaken MegaCore function.

The application interface implements an Avalon-ST interface with a modification in

how the empty signal is used and monitored. In the Avalon-ST interface, the empty

signal is monitored only when end-of-packet is asserted. However, the application

interface asserts and monitors this signal during other data-valid clock cycles as well.

This modification allows the application to provide data in incomplete words,

mirroring the same capability on the Interlaken link.

For more information about the application interface, refer to “Arbiter” on page 4–12

and “Packet Regrouper” on page 4–19.

f For more information about the Avalon-ST interface, refer to Avalon Interface

Specifications.

Optional In-Band Flow Control and Dynamic Configuration Signals

Depending on the parameter values you set in the Interlaken parameter editor, the

application interface may include additional signals that the application controls to

dynamically configure the BurstMax and BurstShort signals, or receives and controls

to manage the in-band flow control bits on the Interlaken link. For more infomation

about BurstMax and BurstShort configuration, refer to “Interlaken Interface” and to

Table 5–8 on page 5–7. For more information about the in-band flow control signals,

refer to “Calendar and Status Block” on page 4–20 and to Table 5–6 on page 5–5 and

Table 5–8 on page 5–7.

Out-of-Band Flow Control Interface

The out-of-band flow control interface conforms to the out-of-band requirements in

Section 5.3.4.2, Out-of-Band Flow Control, of the Interlaken Protocol Definition, Revision

1.2. This interface is included in the Interlaken MegaCore function if you turn on the

Enable out-of-band flow control parameter.

For more information, refer to “Out-of-Band Flow Control Block” on page 4–24.

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 31

Chapter 4: Functional Description 4–5

Clocking and Reset Structure

Clocking and Reset Structure

The Interlaken MegaCore function has a variable number of clock domains,

depending on whether the MegaCore function includes or excludes transceivers, and

on whether it includes or excludes the out-of-band flow control block.

In addition to the high-speed clock domains inside the device transceivers, some of

which also clock the PCS lanes, the Interlaken MegaCore function contains two MAC

clock domains for the receive and transmit directions, four out-of-band flow control

block clocks, and clocks for the Interlaken interface.

For information about the clocks visible in your Interlaken IP core functional

simulation model if you turn on Exclude transceivers, refer to Appendix B, Excluding

Transceivers for Faster Simulation.

For recommended clock rates, refer to “Interlaken MegaCore Function Recommended

Clock Rates” on page 4–9.

MegaCore Function MAC Clock Domains

The Interlaken MegaCore function MAC blocks have the following two clock

domains:

■

rx_mac_c_clk

■

tx_mac_c_clk

—clocks the RX MAC block.

—clocks the TX MAC block.

Altera recommends that the same clock drive the

clocks.

Interlaken Interface Clocks

If you turn off Exclude transceiver, your Interlaken MegaCore function has the

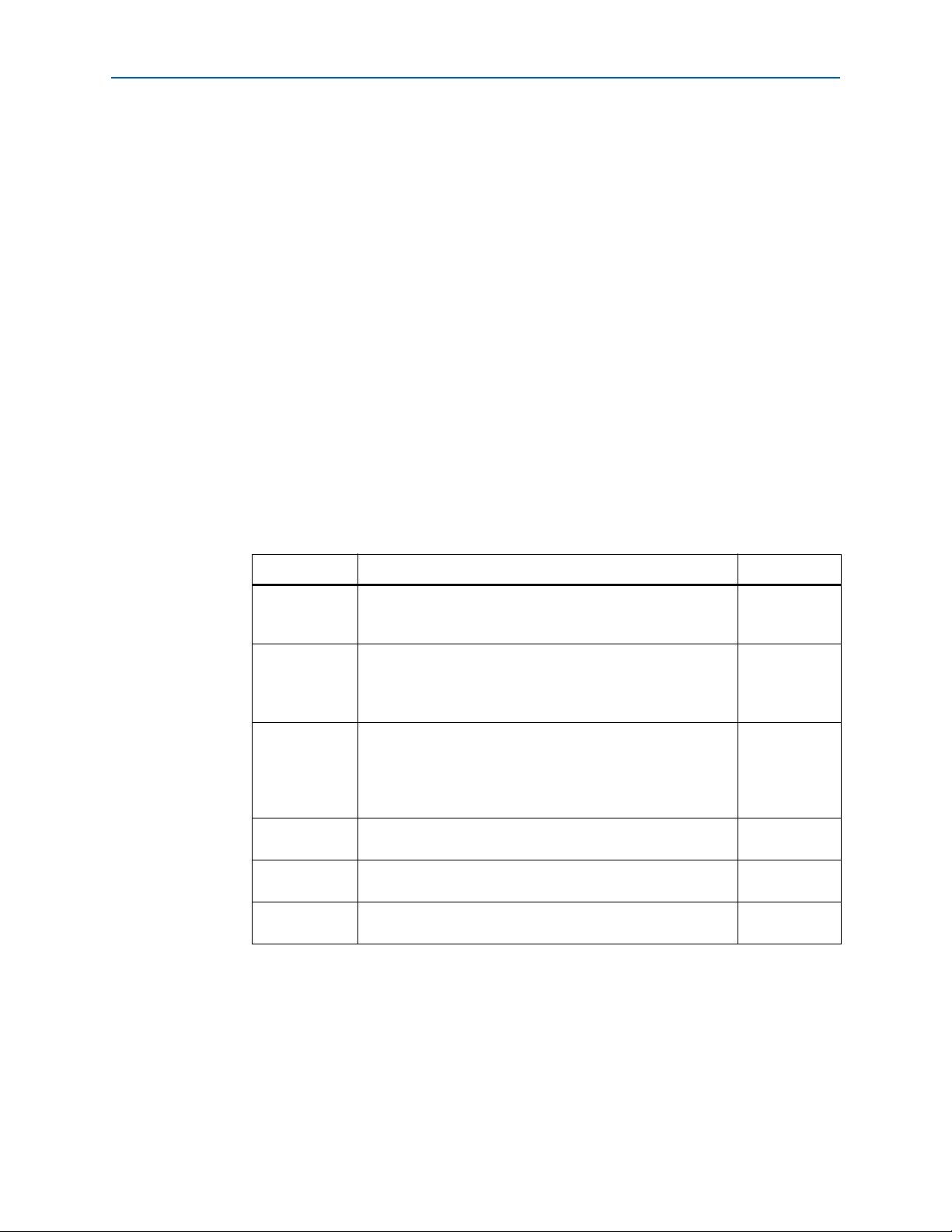

Interlaken interface clocks shown in Table 4–2.

Table 4–2. Interlaken Interface Clocks

Clock Name Description

ref_clk

cal_blk_clk

rx_coreclkout

tx_coreclkout

1 For all Interlaken MegaCore variations except the 8-lane, 3.125-Gbps variation, Altera

Reference clock for the RX and TX transceiver PLLs

Transceiver calibration-block clock

Clocks the RX PCS block. This clock is derived from the physically central RX lane clock.

Clocks the TX PCS block. This clock is derived from the master TX clock from transceiver block 0.

It drives all the transceiver block

block to the HSIO block.

recommends that you drive the

tx_coreclkout

clock. Refer to “Interlaken MegaCore Function Recommended Clock

clk_in

rx_mac_c_clk

Rates” on page 4–9.

rx_mac_c_clk

clocks, as well as the transmit lanes from the TX PCS

and

tx_mac_c_clk

and

tx_mac_c_clk

clocks with the

For information about the Interlaken link facing clocks if you turn on Exclude

transceiver, refer to Appendix B, Excluding Transceivers for Faster Simulation.

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 32

4–6 Chapter 4: Functional Description

Clocking and Reset Structure

Out-of-Band Flow Control Block Clocks

If you turn on Enable out-of-band flow control, your Interlaken MegaCore function

has the following four additional clock domains:

■

rx_oob_in_fc_clk

described in the Interlaken specification. This clock is received from an upstream

TX out-of-band flow control block associated with the Interlaken link partner.

■

tx_oob_out_clk

described in the Interlaken specification. This clock is generated by the

out-of-band flow control block and sent to a downstream RX out-of-band flow

control block associated with the Interlaken link partner.

■

rx_oob_in_sys_clk

application side of the block. The frequency of this clock must be at least double

the frequency of

■

tx_oob_in_double_fc

the application side of the block. The frequency of this clock must be double the

frequency of

—clocks the incoming out-of-band flow control interface signals

—clocks the outgoing out-of-band flow control interface signals

—clocks the outgoing calendar and status information on the

rx_oob_in_fc_clk

.

—clocks the incoming calendar and status information on

tx_oob_out_clk

.

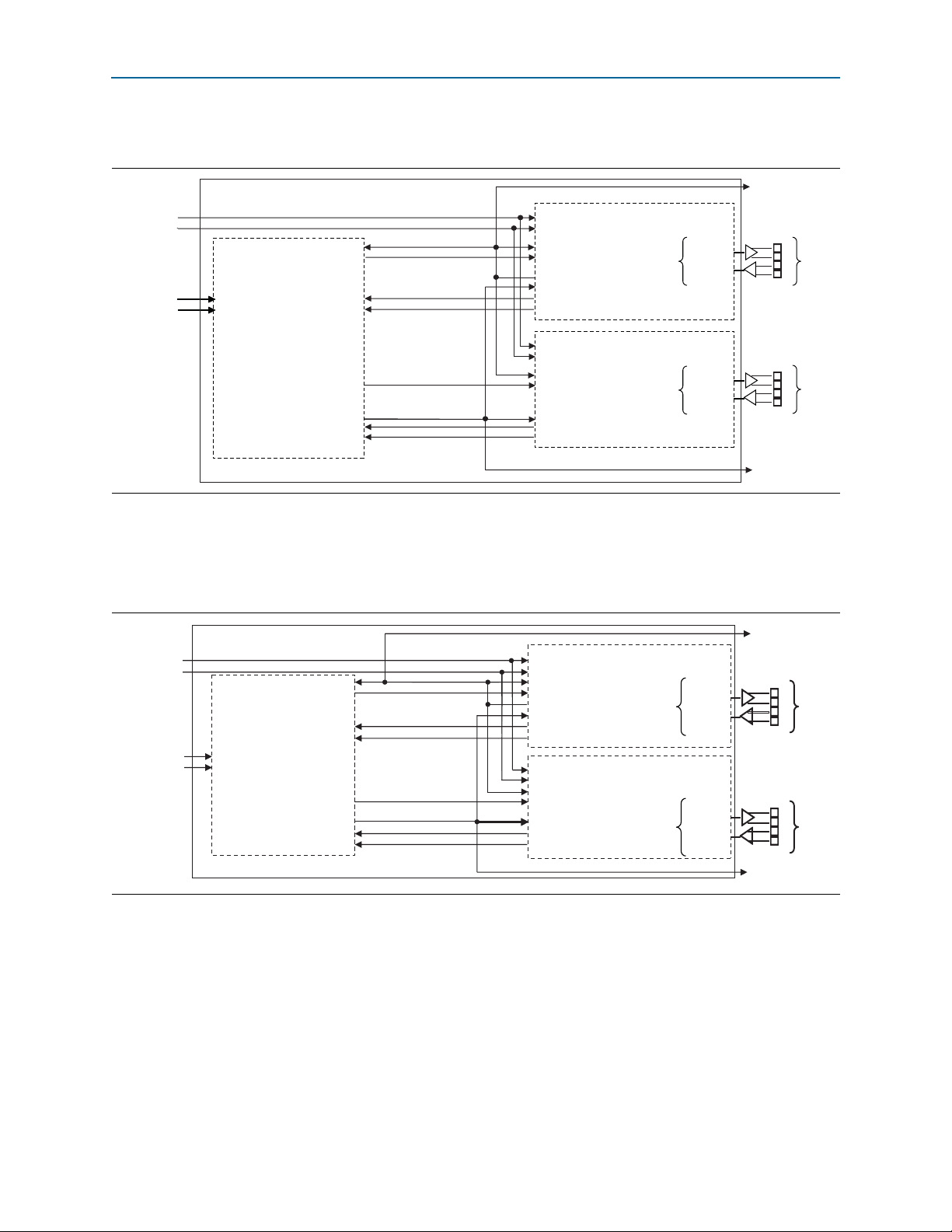

Clock Diagrams for the Interlaken MegaCore Function

Figure 4–2 to Figure 4–6 show the clock diagrams for the Interlaken MegaCore

function variations with the supported numbers of lanes. The figures show variations

with transceivers. For figures that show variations without transceivers, refer to

Appendix B, Excluding Transceivers for Faster Simulation.

The 10-lane and 20-lane variations use the transceivers in PMA Direct mode. These

variations incorporate five lanes in a single transceiver block. The other variations use

the transceivers in low latency PCS mode, incorporating four lanes in each transceiver

block.

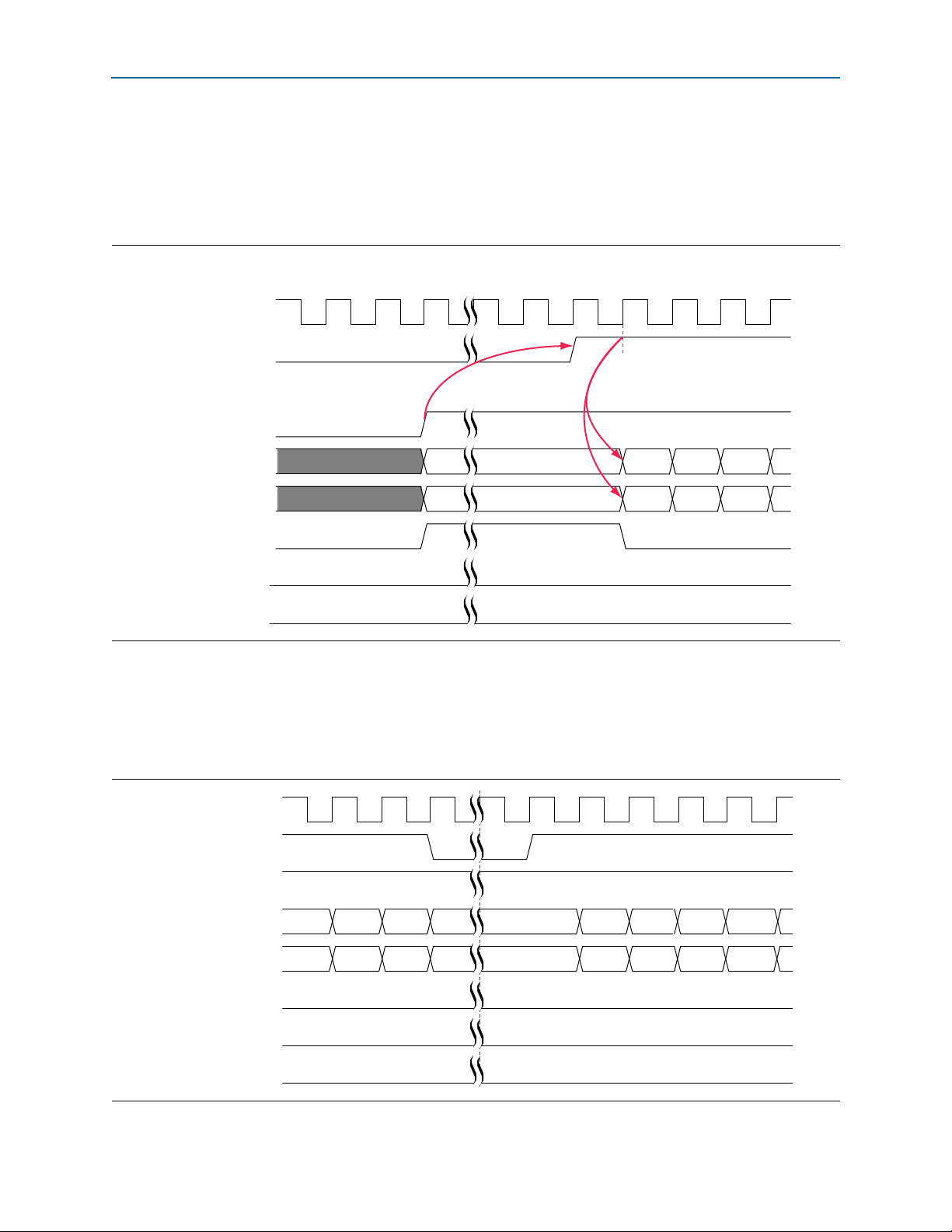

Figure 4–2 shows the clock diagram for a four-lane Interlaken MegaCore function.

Figure 4–2. Clock Diagram for 4-Lane Interlaken MegaCore Function

cal_blk_clk

ref_clk

tx_mac_clk

rx_mac_c lk

TX MAC and PCS

RX MAC and PCS

tx_mac_clk

rx_mac_c lk

tx_lane_clk

tx_data [79:0]

rx_data [79:0]

rx_lane_c lk [3:0]

common_rx_coreclk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

clk_out (master TX clock)

common_r x_c lk

rx_dat aout[79:0]

rx_clk[3:0]

HSIO Bank 0

(low latency PCS mode)

tx_pin[3:0]

rx_pin[3:0]

tx_c orec lkout

x4

rx_c oreclkout

Interlaken MegaCore Function June 2012 Altera Corporation

User Guide

Page 33

Chapter 4: Functional Description 4–7

cal_blk_clk

ref_clk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

clk_out (master TX clock)

common_r x_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

tx_lane_clk

tx_data [79:0]

tx_data [159:80]

rx_data [79:0]

rx_lane_clk [3:0]

rx_data [159:80]

rx_lane_clk [7:4]

common_rx_coreclk

HSIO Bank 0

(low latency PCS mode)

tx_cor eclkout

rx_c oreclkout

x4

tx_mac_clk

rx_mac_clk

tx_mac_clk

rx_mac_clk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

common_r x_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

HSIO Bank 1

(low latency PCS mode)

x4

TX MAC and PCS

RX MAC and PCS

Lanes 4 to 7

Lanes 0 to 3

Clocking and Reset Structure

Figure 4–3 shows the clock diagram for an eight-lane Interlaken MegaCore function.

Figure 4–3. Clock Diagram for 8-Lane Interlaken MegaCore Function

Figure 4–4 shows the clock diagram for a 10-lane Interlaken MegaCore function. This

variation uses the transceivers in PMA Direct mode. For more information, refer to

“High-Speed I/O Block” on page 4–22.

Figure 4–4. Clock Diagram for 10-Lane Interlaken MegaCore Function

cal_blk_clk

ref_clk

tx_lane_clk

tx_data[99:0]

rx_data[99:0]

rx_c lk[4:0]

tx_data[199:100]

common_r x_corec lk

rx_data[199: 100]

rx_c lk[9:5]

tx_mac_c_c lk

rx_mac_c _clk

TX MAC

and PCS

tx_mac_clk

rx_mac_c lk

RX MAC

and PCS

cal_blk_clk

ref_clk

clk_in

tx_datain[99:0]

clk_out (master TX clock)

common_r x_clk

rx_dataout[99:0]

rx_clk[4:0]

cal_blk_clk

ref_clk

clk_in

tx_datain[99:0]

common_r x_clk

rx_dataout[ 99:0]

rx_c lk[4:0]

HSIO Bank 0

(in PMA Dir ect mode)

Lanes 5 to 9

HSIO Bank 1

(in PMA Dir ect mode)

Lanes 0 to 4

tx_pin[4:0]

rx_pin[4:0]

tx_pin[4:0]

rx_pin[4:0]

tx_coreclkout

x5

x5

rx_coreclkout

June 2012 Altera Corporation Interlaken MegaCore Function

User Guide

Page 34

4–8 Chapter 4: Functional Description

cal_blk_clk

ref_clk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

clk_out (master TX clock)

common_r x_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

tx_lane_clk

tx_data [79:0]

tx_data [159:80]

rx_data [79:0]

rx_lane_clk [3:0]

rx_data [159:80]

rx_lane_clk [7:4]

common_rx_coreclk

tx_data [239:160]

rx_data [239:160]

rx_lane_clk [11:8]

HSIO Bank 0

(low latency PCS mode)

tx_cor eclkout

rx_c oreclkout

x4

tx_mac_clk

rx_mac_clk

tx_mac_clk

rx_mac_clk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

common_r x_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

HSIO Bank 1

(low latency PCS mode)

x4

cal_blk_clk

ref_clk

clk_in

Lanes 0 to 3

tx_datain[79:0]

common_r x_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

HSIO Bank 2

(low latency PCS mode)

Lanes 4 to 7

Lanes 8 to 11

x4

TX MAC and PCS

RX MAC and PCS

Clocking and Reset Structure

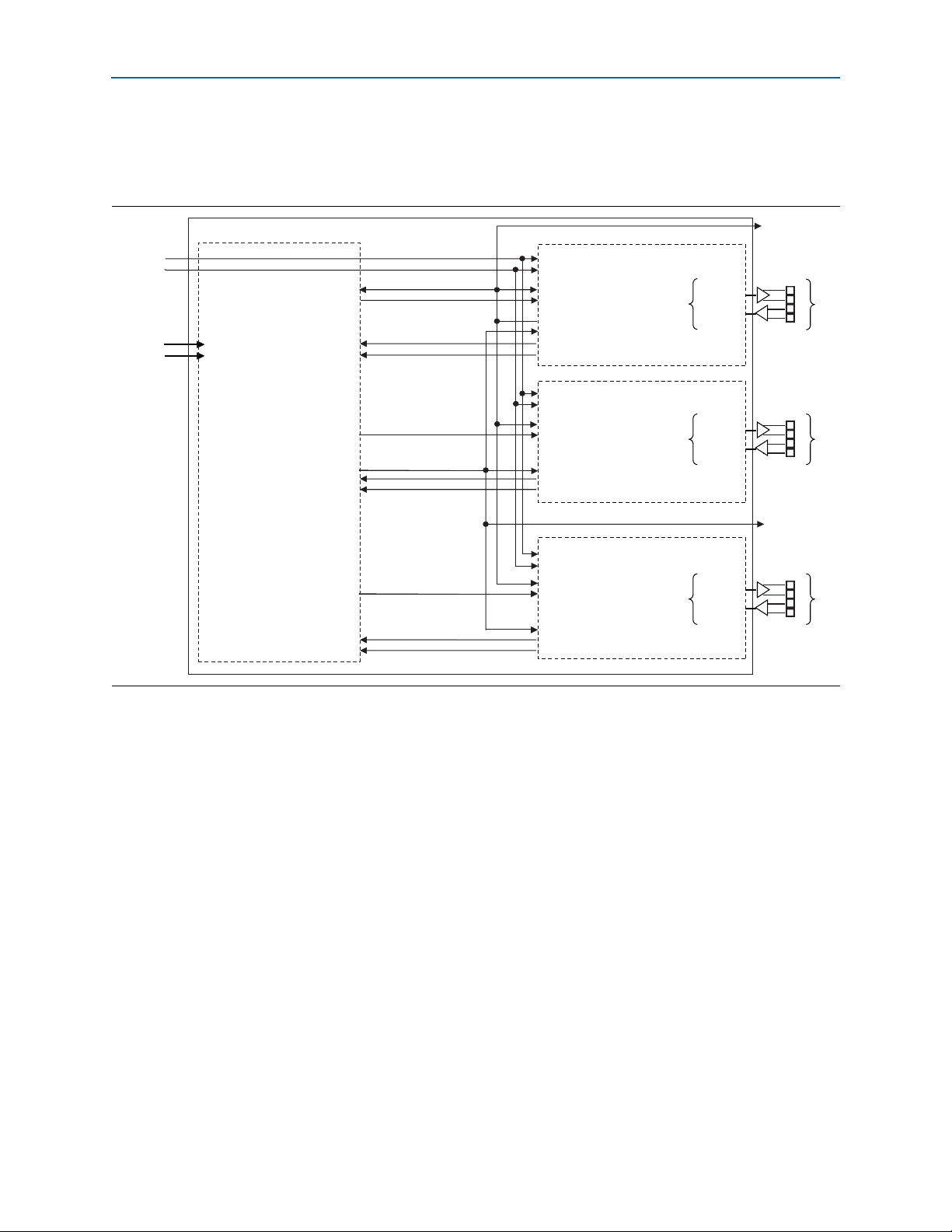

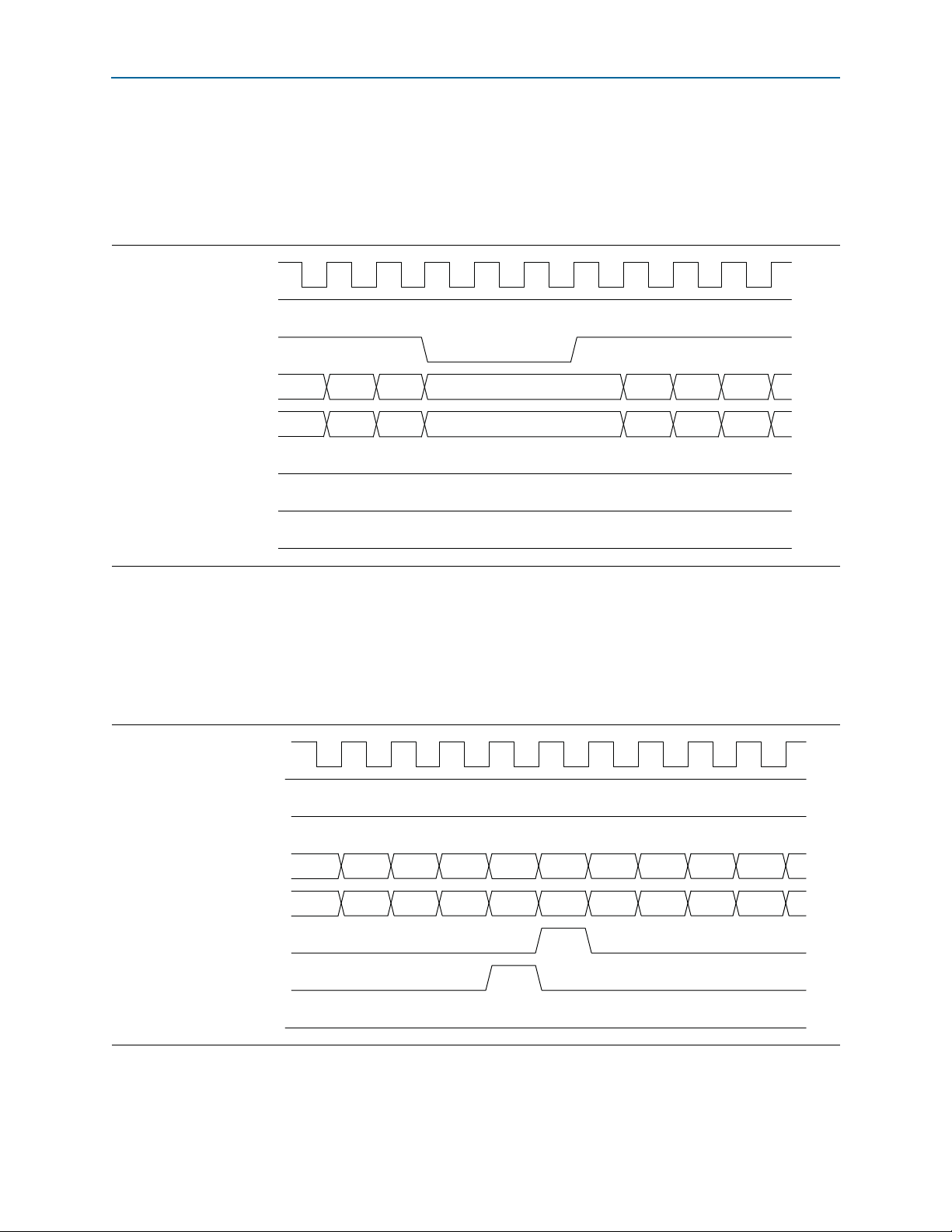

Figure 4–5 shows the clock diagram for a 12-lane, 6-Gbps variation. In this variation,

the transceiver datapath width is 20. The clock diagram for a 12-lane, 10-Gbps