Page 1

2014.12.17

www.altera.com

101 Innovation Drive, San Jose, CA 95134

ALTDQ_DQS2 IP Core User Guide

UG-01089

Subscribe

The Altera ALTDQ_DQS2 megafunction IP core controls the double data rate (DDR) I/O elements

(IOEs) for the data (DQ) and data strobe (DQS) signals in Arria® V, Cyclone® V, and Stratix® V devices.

A DQ group is composed of one DQS, one optional complementary DQS, and up to 36 configurable DQ

I/Os.

Related Information

Introduction to Altera IP Cores

ALTDQ_DQS2 Features

The ALTDQ_DQS2 IP core has the following features:

• Access to dynamic on-chip termination (OCT) controls to switch between parallel termination during

reads and series termination during writes.

• High-performance support for DDR interface standards.

• 4- to 36-bit programmable DQ group widths.

• Half-rate registers to enable successful data transfers between the I/O registers and the core logic.

• Access to I/O delay chains to fine-tune delays on the data or strobe signals.

• Access to hard read FIFO.

• Access to latency shifter FIFO and data valid FIFO for efficient control of DQS gating and read

operations (Arria V and Cyclone V devices only).

Send Feedback

ALTDQ_DQS2 Device Support

The ALTDQ_DQS2 IP core supports the following devices:

• Arria V devices

• Cyclone V devices

• Stratix V devices

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 2

acds

quartus - Contains the Quartus II software

ip - Contains the Altera IP Library and third-party IP cores

altera - Contains the Altera IP Library source code

<IP core name> - Contains the IP core source files

2

Resource Utilization and Performance

Resource Utilization and Performance

To view the compilation reports in the Quartus II software, follow these steps:

1. On the Processing menu, click Start Compilation to run a full compilation.

2. After compiling the design, on the Processing menu, click Compilation Report.

3. In the Table of Contents browser, expand the Fitter folder by clicking the “+” icon.

4. Expand Resource section, and select Resource Usage Summary to view the resource usage informa‐

tion.

5. Expand Resource section, and select Resource Utilization by Entity to view the resource utilization

information.

Installing and Licensing IP Cores

The Altera IP Library provides many useful IP core functions for production use without purchasing an

additional license. You can evaluate any Altera® IP core in simulation and compilation in the Quartus® II

software using the OpenCore® evaluation feature. Some Altera IP cores, such as MegaCore® functions,

require that you purchase a separate license for production use. You can use the OpenCore Plus feature to

evaluate IP that requires purchase of an additional license until you are satisfied with the functionality and

performance. After you purchase a license, visit the Self Service Licensing Center to obtain a license

number for any Altera product.

UG-01089

2014.12.17

Figure 1: IP Core Installation Path

Note:

Related Information

• Altera Licensing Site

• Altera Software Installation and Licensing Manual

The default IP installation directory on Windows is <drive>:\altera\<version number>; on Linux it is

<home directory>/altera/ <version number>.

Customizing and Generating IP Cores

You can customize IP cores to support a wide variety of applications. The Quartus II IP Catalog and

parameter editor allow you to quickly select and configure IP core ports, features, and output files.

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 3

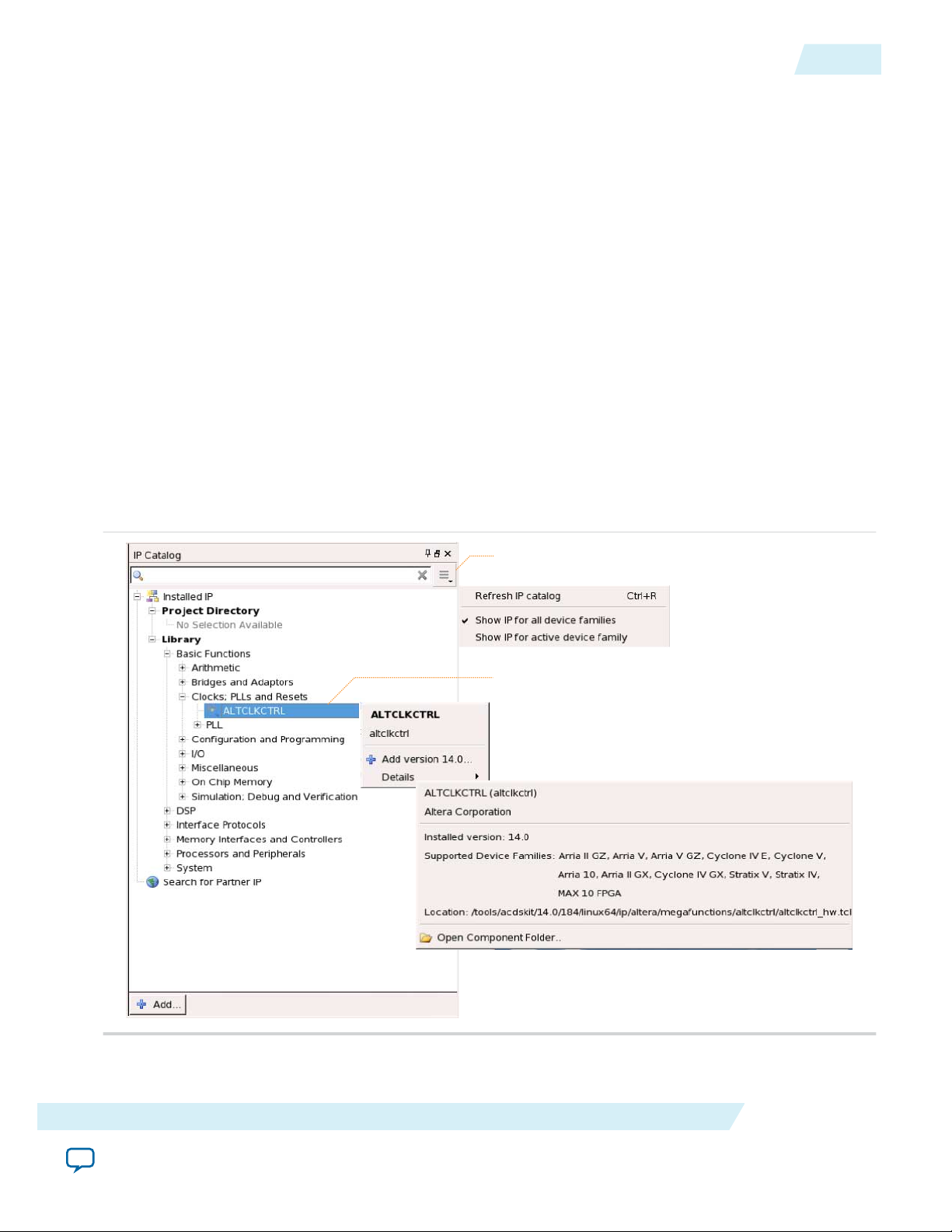

Search and filter IP for your target device

Double-click to customize, right-click for information

UG-01089

2014.12.17

IP Catalog and Parameter Editor (replaces MegaWizard Plug-In Manager)

IP Catalog and Parameter Editor (replaces MegaWizard Plug-In Manager)

The Quartus II IP Catalog (Tools > IP Catalog) and parameter editor help you easily customize and

integrate IP cores into your project. You can use the IP Catalog and parameter editor to select, customize,

and generate files representing your custom IP variation.

Note: The IP Catalog (Tools > IP Catalog) and parameter editor replace the MegaWizard™ Plug-In

Manager for IP selection and parameterization, beginning in Quartus II software version 14.0. Use

the IP Catalog and parameter editor to locate and paramaterize Altera IP cores.

The IP Catalog lists IP cores available for your design. Double-click any IP core to launch the parameter

editor and generate files representing your IP variation. The parameter editor prompts you to specify an

IP variation name, optional ports, and output file generation options. The parameter editor generates a

top-level Qsys system file (.qsys) or Quartus II IP file (.qip) representing the IP core in your project. You

can also parameterize an IP variation without an open project.

Use the following features to help you quickly locate and select an IP core:

• Filter IP Catalog to Show IP for active device family or Show IP for all device families.

• Search to locate any full or partial IP core name in IP Catalog. Click Search for Partner IP, to access

partner IP information on the Altera website.

• Right-click an IP core name in IP Catalog to display details about supported devices, open the IP core's

installation folder, andor view links to documentation.

3

Figure 2: Quartus II IP Catalog

Note:

The IP Catalog is also available in Qsys (View > IP Catalog). The Qsys IP Catalog includes

exclusive system interconnect, video and image processing, and other system-level IP that are not

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 4

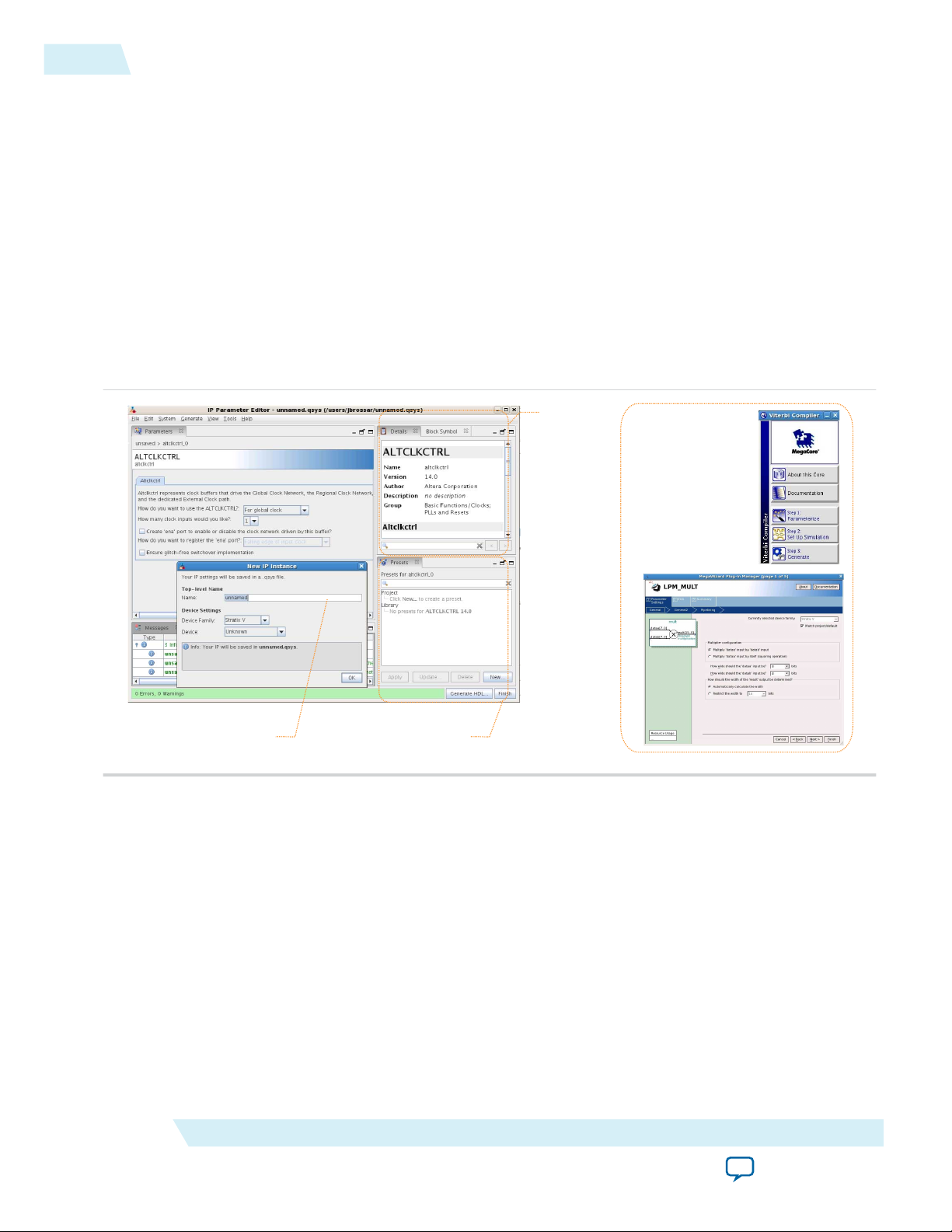

View IP port

and parameter

details

Apply preset parameters for

specific applications

Specify your IP variation name

and target device

Legacy parameter

editors

4

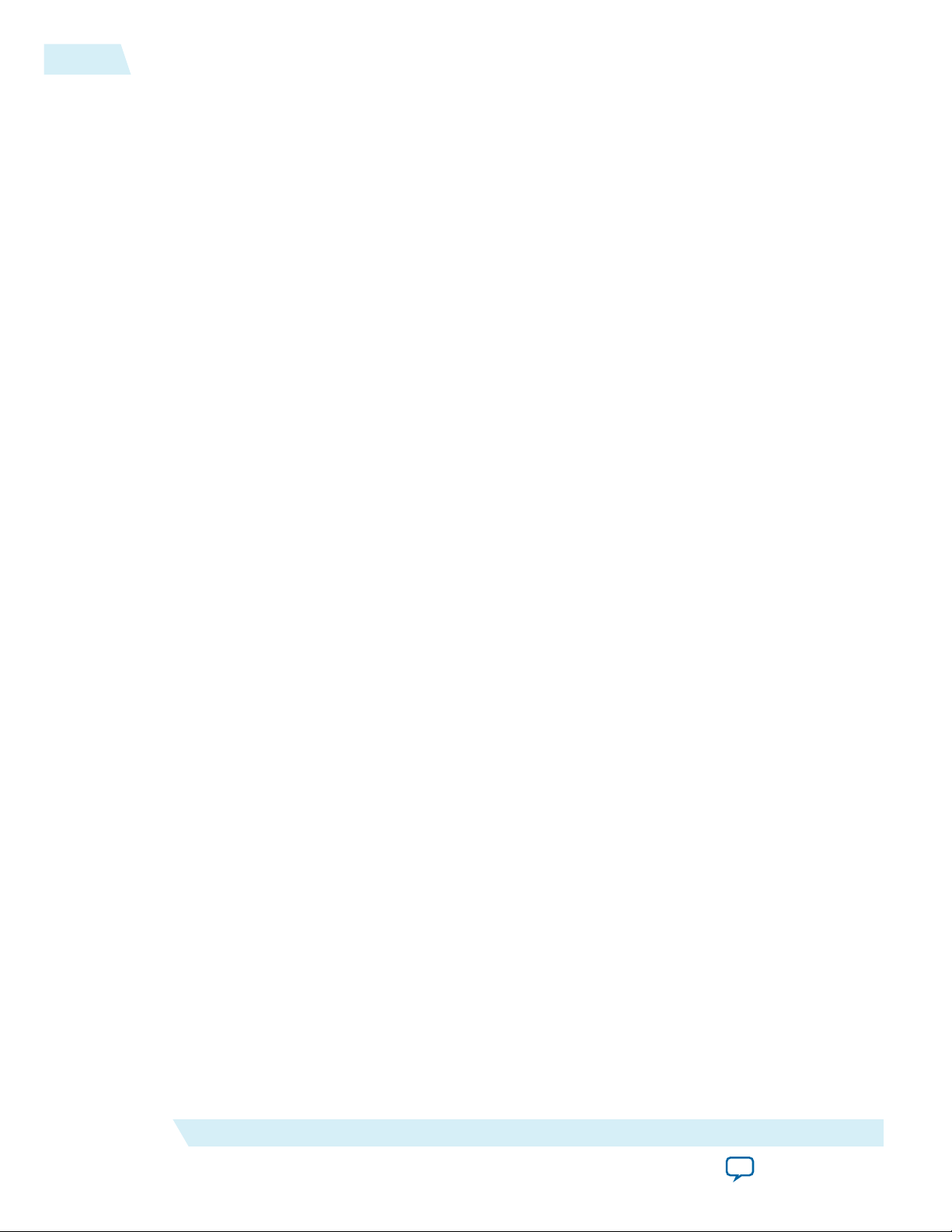

Using the Parameter Editor

available in the Quartus II IP Catalog. For more information about using the Qsys IP Catalog, refer

to Creating a System with Qsys in the Quartus II Handbook.

Related Information

• Creating a System with Qsys

Using the Parameter Editor

The parameter editor helps you to configure IP core ports, parameters, and output file generation options.

• Use preset settings in the parameter editor (where provided) to instantly apply preset parameter values

for specific applications.

• View port and parameter descriptions, and links to documentation.

• Generate testbench systems or example designs (where provided).

Figure 3: IP Parameter Editors

UG-01089

2014.12.17

Adding IP Cores to IP Catalog

Altera Corporation

The IP Catalog automatically displays Altera IP cores found in the project directory, in the Altera

installation directory, and in the defined IP search path. The IP Catalog can include Altera-provided IP

components, third-party IP components, custom IP components that you provide, and previously

generated Qsys systems.

You can use the IP Search Path option (Tools > Options) to include custom and third-party IP

components in the IP Catalog. The IP Catalog displays all IP cores in the IP search path. The Quartus

software searches the directories listed in the IP search path for the following IP core files:

• Component Description File (_hw.tcl)—Defines a single IP core.

• IP Index File (.ipx)—Each .ipx file indexes a collection of available IP cores, or a reference to other

directories to search. In general, .ipx files facilitate faster searches.

The Quartus software searches some directories recursively and other directories only to a specific depth.

When the search is recursive, the search stops at any directory that contains an _hw.tcl or .ipx file.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

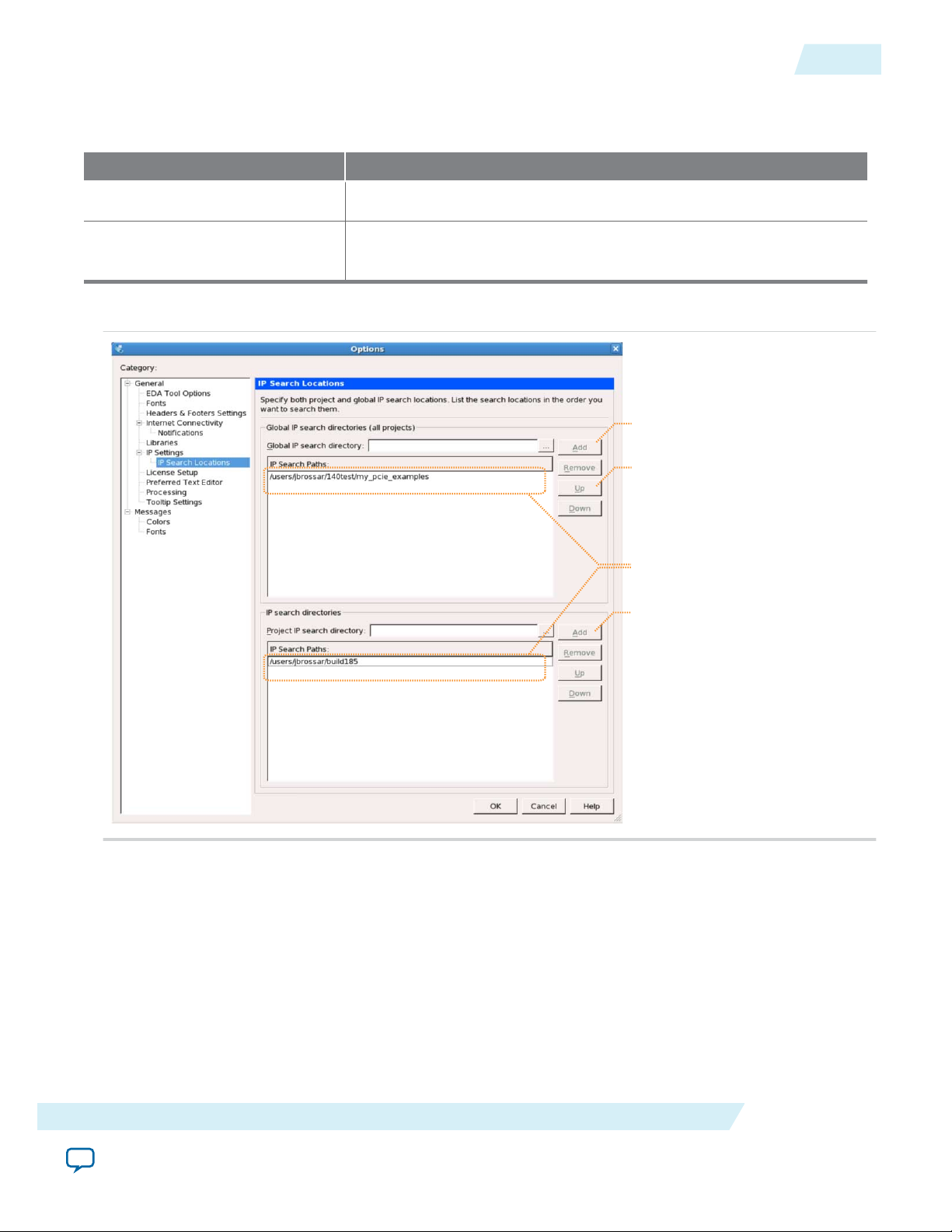

Page 5

Adds new global IP search paths

Changes search path order

Adds new project-specific IP search paths

Lists current project and global search paths

UG-01089

2014.12.17

In the following list of search locations, a recursive descent is annotated by **. A single * signifies any file.

Table 1: IP Search Locations

Location Description

Adding IP Cores to IP Catalog

5

PROJECT_DIR/*

PROJECT_DIR/ip/**/*

Finds IP components and index files in the Quartus project directory.

Finds IP components and index files in any subdirectory of the /ip

subdirectory of the Quartus project directory.

Figure 4: Specifying IP Search Locations

If the Quartus software recognizes two IP cores with the same name, the following search path precedence

rules determine the resolution of files:

1. Project directory.

2. Project database directory.

3. Project IP search path specified in IP Search Locations, or with the SEARCH_PATH assignment in the

Quartus Settings File ( .qsf) for the current project revision.

4. Global IP search path specified in IP Search Locations, or with the SEARCH_PATH assignment in the

quartus2.ini file.

5. Quartus software libraries directory, such as <Quartus Installation>\libraries.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 6

6

Specifying IP Core Parameters and Options

Note: If you add a component to the search path, you must refresh your system by clicking File > Refresh

to update the IP Catalog.

Specifying IP Core Parameters and Options

The parameter editor GUI allows you to quickly configure your custom IP variation. You specify IP core

options and parameters in the Quartus II software.

1. In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize.

The parameter editor appears.

2. Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation

settings in a file named <your_ip>.qsys. Click OK.

3. Specify the parameters and options for your IP variation in the parameter editor, including one or

more of the following. Refer to your IP core user guide for information about specific IP core

parameters.

• Optionally select preset parameter values if provided for your IP core. Presets specify initial

parameter values for specific applications.

• Specify parameters defining the IP core functionality, port configurations, and device-specific

features.

• Specify options for processing the IP core files in other EDA tools.

4. Click Generate HDL, the Generation dialog box appears.

5. Specify output file generation options, and then click Generate. The IP variation files generate

according to your specifications.

6. To generate a simulation testbench, click Generate > Generate Testbench System.

7. To generate an HDL instantiation template that you can copy and paste into your text editor, click

Generate > HDL Example.

8. Click Finish. The parameter editor adds the top-level .qsys file to the current project automatically. If

you are prompted to manually add the .qsys file to the project, click Project > Add/Remove Files in

Project to add the file.

9. After generating and instantiating your IP variation, make appropriate pin assignments to connect

ports.

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 7

View IP port

and parameter

details

Apply preset parameters for

specific applications

Specify your IP variation name

and target device

UG-01089

2014.12.17

Figure 5: IP Parameter Editor

Files Generated for Altera IP Cores (version 14.0 and previous)

7

Files Generated for Altera IP Cores (version 14.0 and previous)

The Quartus II software version 14.0 and previous generates the following output for your IP core.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 8

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

<Project Directory>

<your_ip>_sim

1

<Altera IP>_instance.vo - IPFS model

2

<simulator_vendor>

<simulator setup scripts>

<your_ip>.qip - Quartus II IP integration file

<your_ip>.sip - Lists files for simulation

<your_ip>_testbench or _example - Testbench or example

1

<your_ip>.v, .sv. or .vhd - Top-level IP synthesis file

<AlteraIP_name>_instance

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist

1

<your_ip>.cmp - VHDL component declaration file

<your_ip>.bsf - Block symbol schematic file

<your_ip> - IP core synthesis files

<your_ip>.sv, .v, or .vhd - HDL synthesis files

<your_ip>.sdc - Timing constraints file

<your_ip>.ppf - XML I/O pin information file

<your_ip>.spd - Combines individual simulation scripts

1

<your_ip>_sim.f - Refers to simulation models and scripts

1

8

Upgrading IP Cores

Figure 6: IP Core Generated Files

UG-01089

2014.12.17

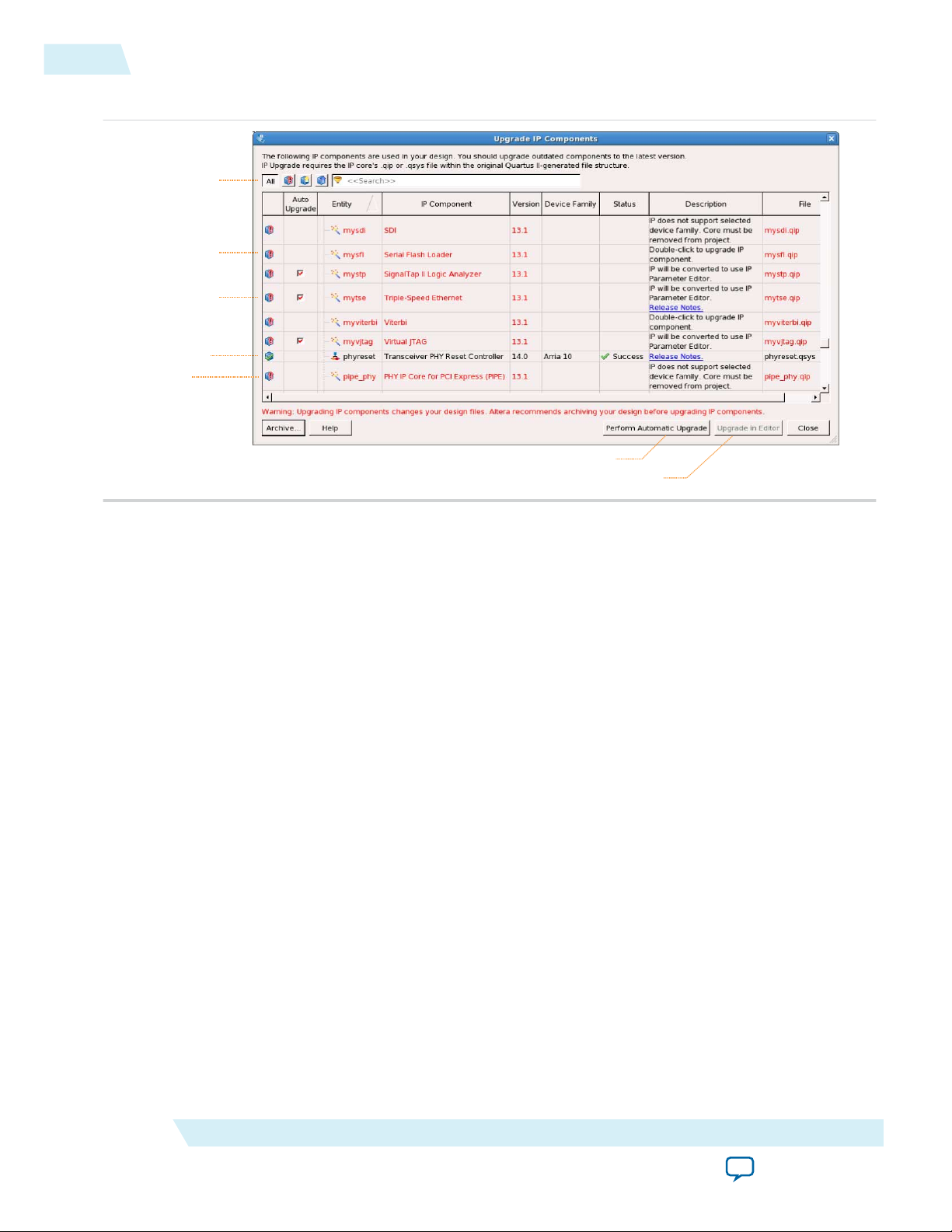

Upgrading IP Cores

IP core variants generated with a previous version of the Quartus II software may require upgrading

before use in the current version of the Quartus II software. Click Project > Upgrade IP Components to

identify and upgrade IP core variants.

The Upgrade IP Components dialog box provides instructions when IP upgrade is required, optional, or

unsupported for specific IP cores in your design. You must upgrade IP cores that require it before you can

compile the IP variation in the current version of the Quartus II software. Many Altera IP cores support

automatic upgrade.

The upgrade process renames and preserves the existing variation file (.v, .sv, or .vhd) as <my_variant>_

BAK.v, .sv, .vhd in the project directory.

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 9

UG-01089

2014.12.17

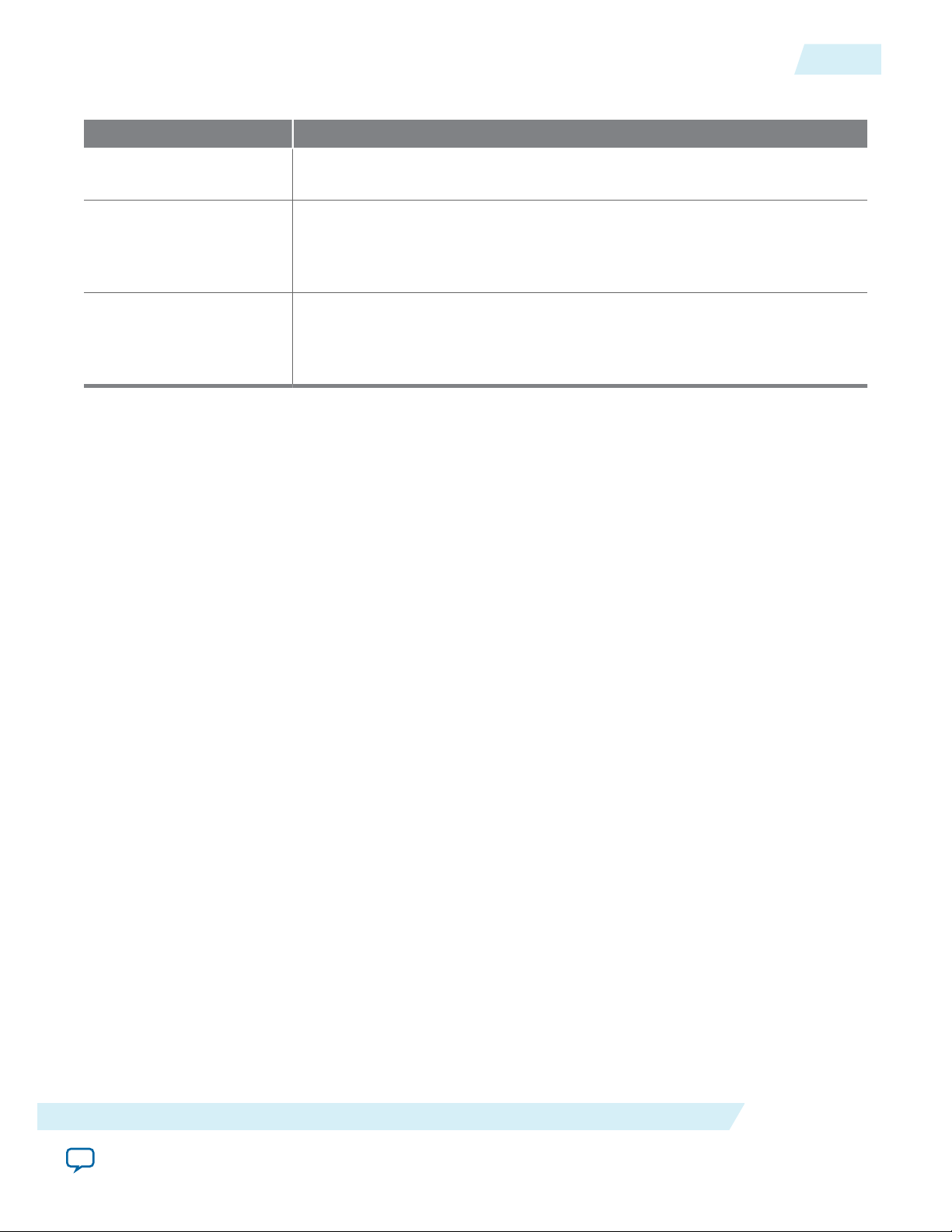

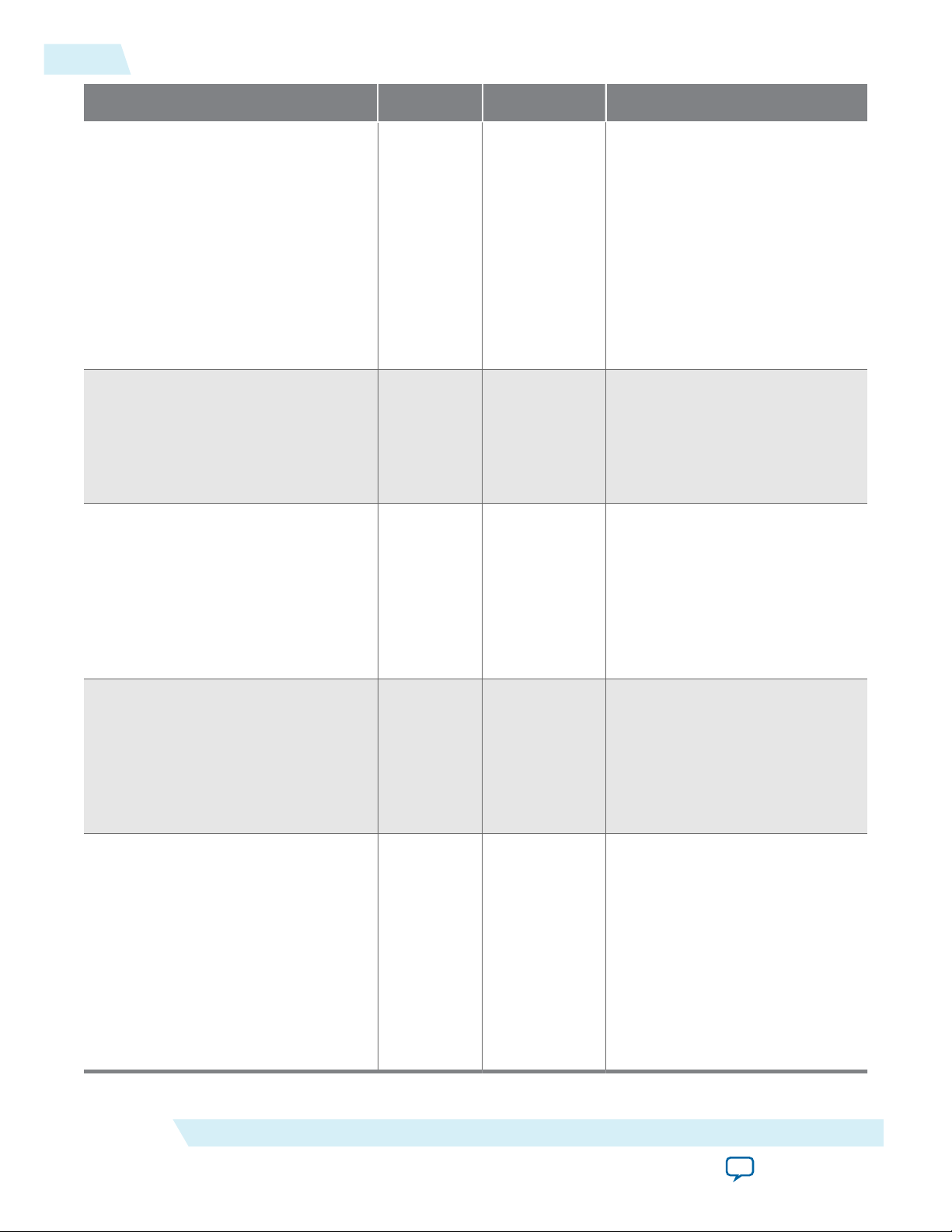

Table 2: IP Core Upgrade Status

IP Core Status Corrective Action

Upgrading IP Cores

9

Required Upgrade IP

Components

Optional Upgrade IP

Components

You must upgrade the IP variation before compiling in the current version of

the Quartus II software.

Upgrade is optional for this IP variation in the current version of the Quartus

II software. You can upgrade this IP variation to take advantage of the latest

development of this IP core. Alternatively you can retain previous IP core

characteristics by declining to upgrade.

Upgrade Unsupported Upgrade of the IP variation is not supported in the current version of the

Quartus II software due to IP core end of life or incompatibility with the

current version of the Quartus II software. You are prompted to replace the

obsolete IP core with a current equivalent IP core from the IP Catalog.

Before you begin

• Archive the Quartus II project containing outdated IP cores in the original version of the Quartus II

software: Click Project > Archive Project to save the project in your previous version of the Quartus II

software. This archive preserves your original design source and project files.

• Restore the archived project in the latest version of the Quartus II software: Click Project > Restore

Archived Project. Click OK if prompted to change to a supported device or overwrite the project

database. File paths in the archive must be relative to the project directory. File paths in the archive

must reference the IP variation .v or .vhd file or .qsys file (not the .qip file).

1. In the latest version of the Quartus II software, open the Quartus II project containing an outdated IP

core variation. The Upgrade IP Components dialog automatically displays the status of IP cores in

your project, along with instructions for upgrading each core. Click Project > Upgrade IP

Components to access this dialog box manually.

2. To simultaneously upgrade all IP cores that support automatic upgrade, click Perform Automatic

Upgrade. The Status and Version columns update when upgrade is complete. Example designs

provided with any Altera IP core regenerate automatically whenever you upgrade the IP core.

ALTDQ_DQS2 IP Core User Guide

Altera Corporation

Send Feedback

Page 10

Displays upgrade

status for all IP cores

in the Project

Upgrades all IP core that support “Auto Upgrade”

Upgrades individual IP cores unsupported by “Auto Upgrade”

Checked IP cores

support “Auto Upgrade”

Successful

“Auto Upgrade”

Upgrade

unavailable

Double-click to

individually migrate

10

Upgrading IP Cores

Figure 7: Upgrading IP Cores

UG-01089

2014.12.17

Example 1: Upgrading IP Cores at the Command Line

You can upgrade IP cores that support auto upgrade at the command line. IP cores that do not

support automatic upgrade do not support command line upgrade.

• To upgrade a single IP core that supports auto-upgrade, type the following command:

quartus_sh –ip_upgrade –variation_files <my_ip_filepath/my_ip>.<hdl>

<qii_project>

Example:

quartus_sh -ip_upgrade -variation_files mega/pll25.v hps_testx

• To simultaneously upgrade multiple IP cores that support auto-upgrade, type the following

command:

quartus_sh –ip_upgrade –variation_files “<my_ip_filepath/my_ip1>.<hdl>;

<my_ip_filepath/my_ip2>.<hdl>” <qii_project>

Example:

quartus_sh -ip_upgrade -variation_files "mega/pll_tx2.v;mega/pll3.v"

hps_testx

Note:

IP cores older than Quartus II software version 12.0 do not support upgrade.

Altera verifies that the current version of the Quartus II software compiles the

previous version of each IP core. The Altera IP Release Notes reports any verifica‐

tion exceptions for Altera IP cores. Altera does not verify compilation for IP cores

older than the previous two releases.

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 11

UG-01089

2014.12.17

Related Information

Altera IP Release Notes

ALTDQ_DQS2 Parameter Settings

You can instantiate and parameterize using the IP Catalog and parameter editor GUI, or the ip-generate

command through the command-line interface (CLI).

The following table lists the ALTDQ_DQS2 parameter settings.

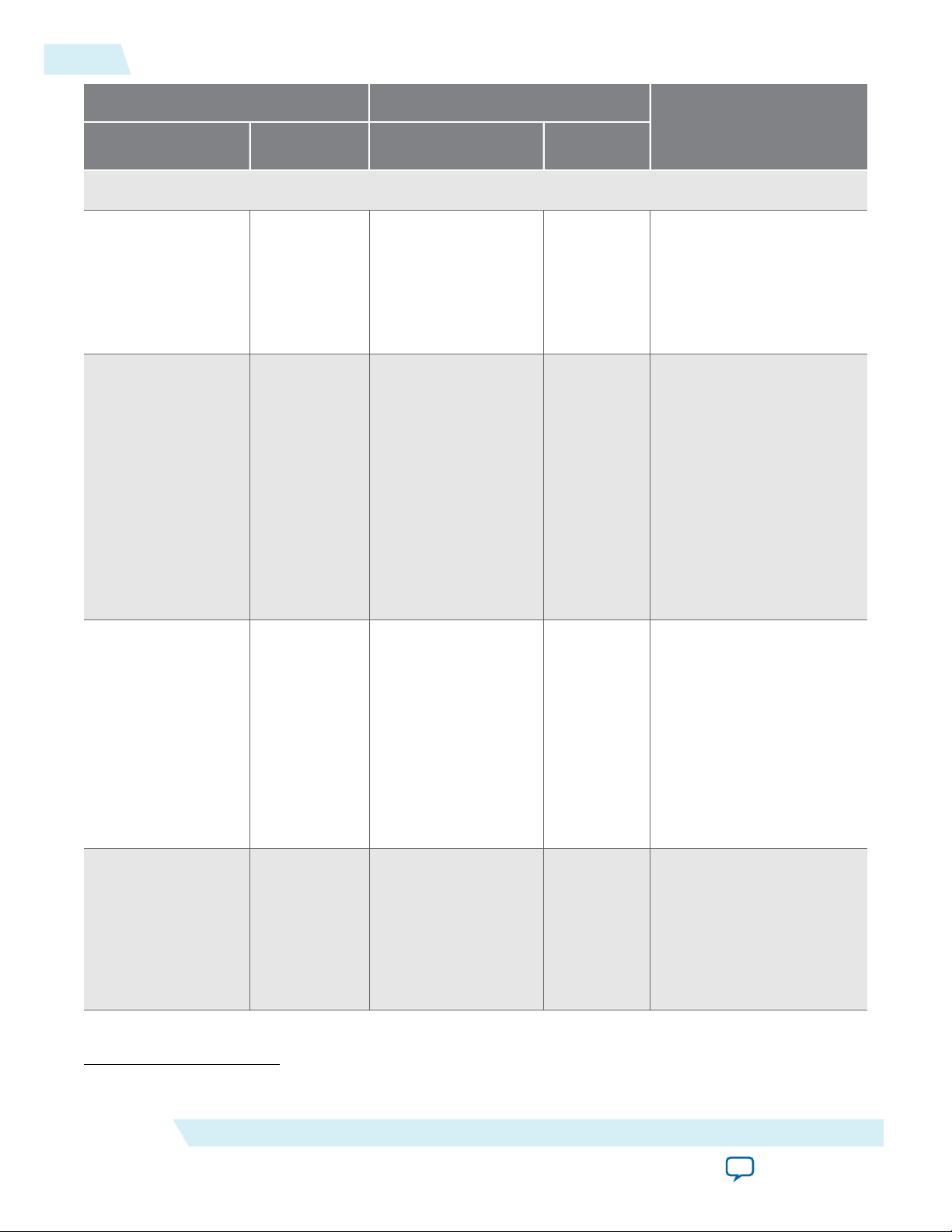

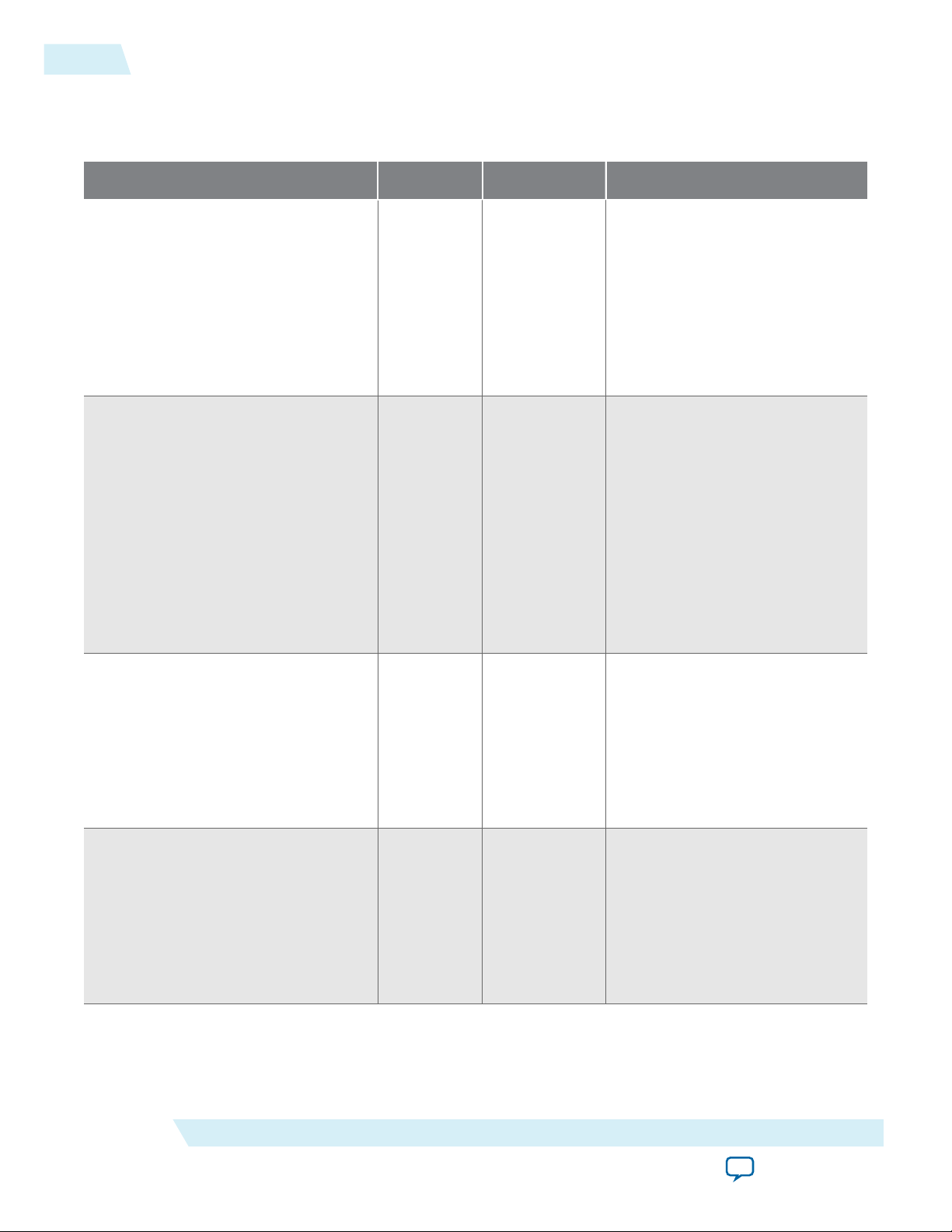

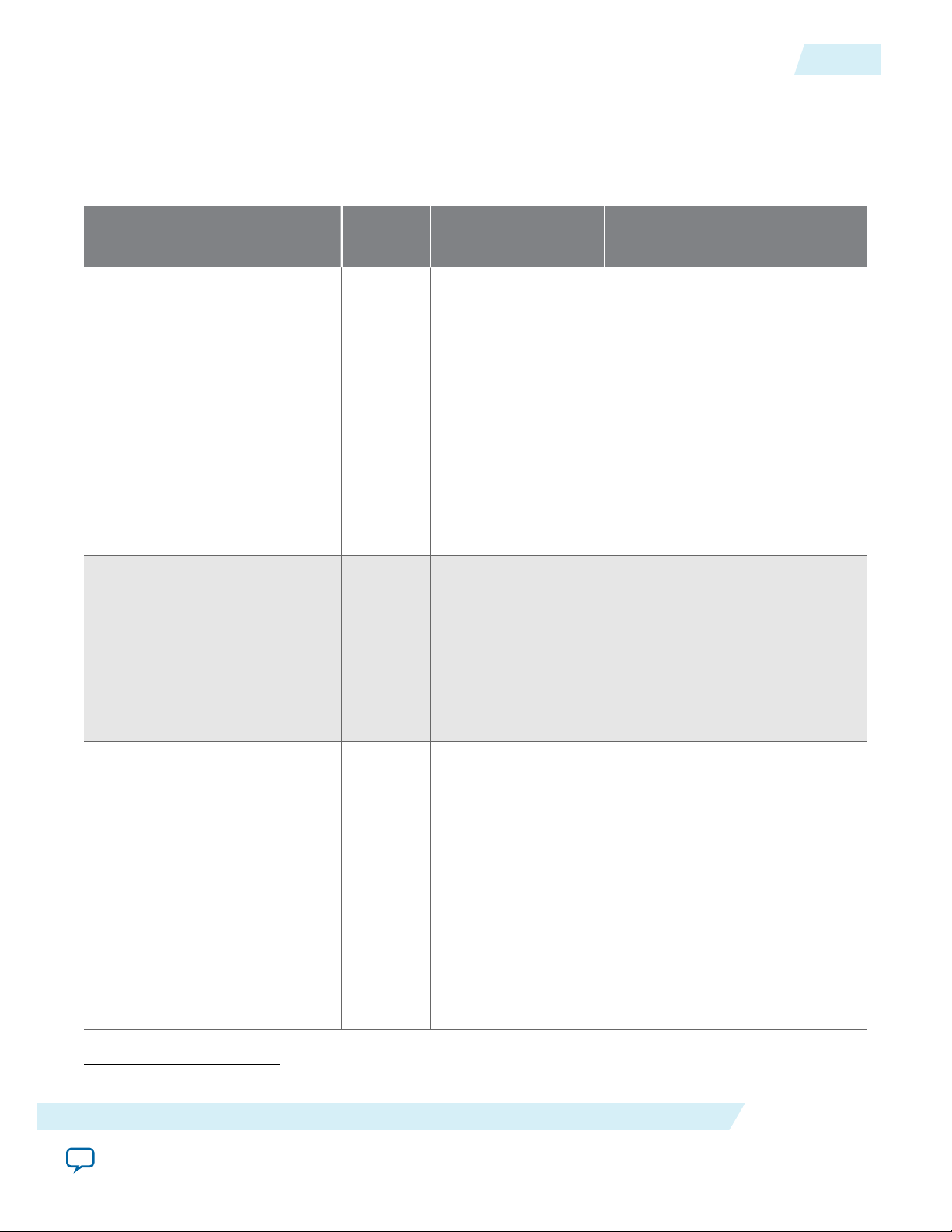

Table 3: ALTDQ_DQS2 Parameter Settings

ALTDQ_DQS2 Parameter Settings

11

Parameter Editor GUI Setting

Name

Legal Values

General Settings

Pin width 1 to 36

Pin type input

output

bidir

Extra output-only

0 – 36

pins

CLI Parameter

Name

PIN_WIDTH 1 to 36

PIN_TYPE

EXTRA_OUTPUT_WIDTH 0 to 36

Legal

Values

input

output

bidir

(1)

Description

This setting specifies the

number of data (DQ) pins

to make as part of this

DQS group.

The default value is 9 (9).

This setting specifies the

direction of the data pins

(input, output, or bidirec‐

tional).

The default value is bidir

(bidir).

This setting specifies the

extra output pins that you

need as part of a DQS

group.

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

A common use for this

setting is to add datamask

pins.

The default value is 0 (0).

Altera Corporation

Page 12

12

ALTDQ_DQS2 Parameter Settings

UG-01089

2014.12.17

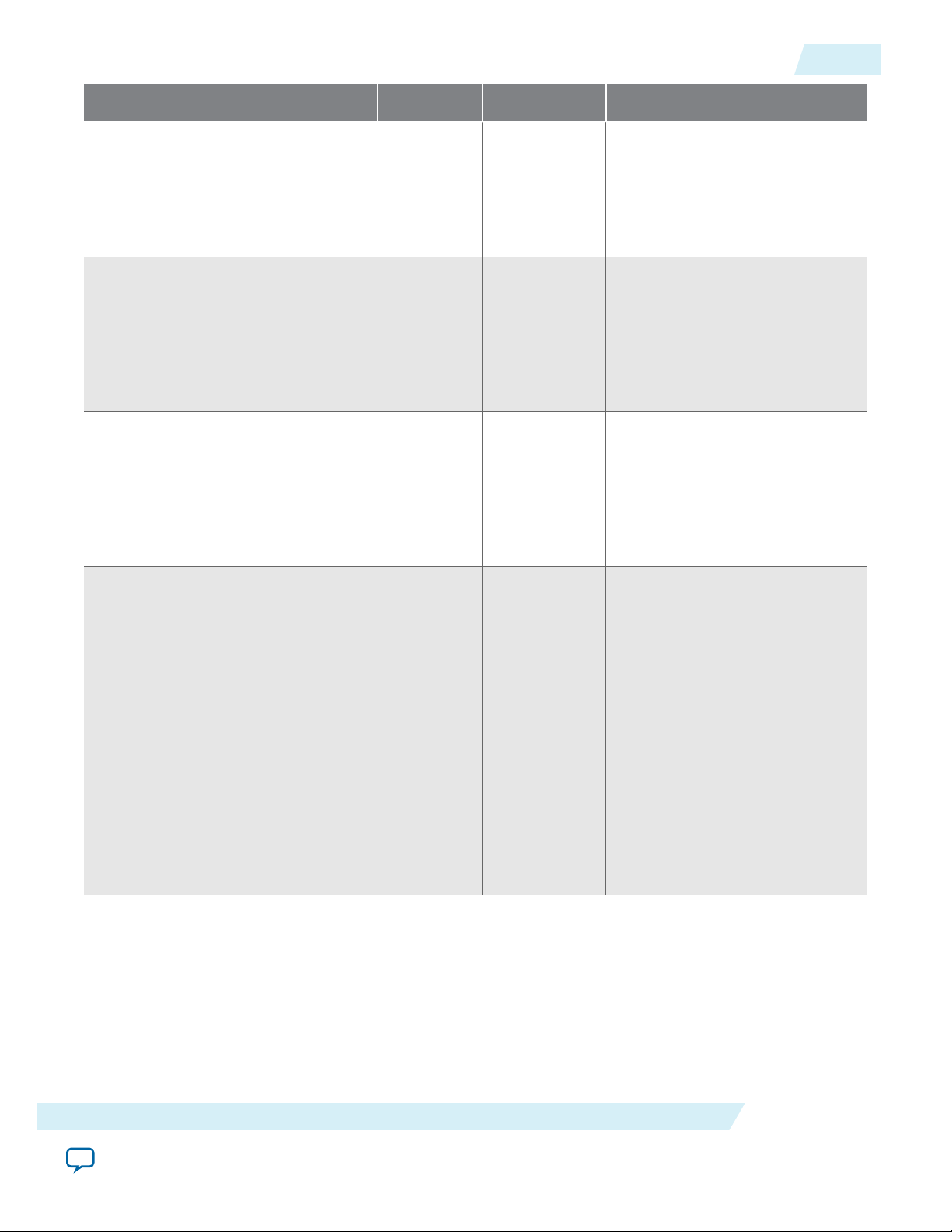

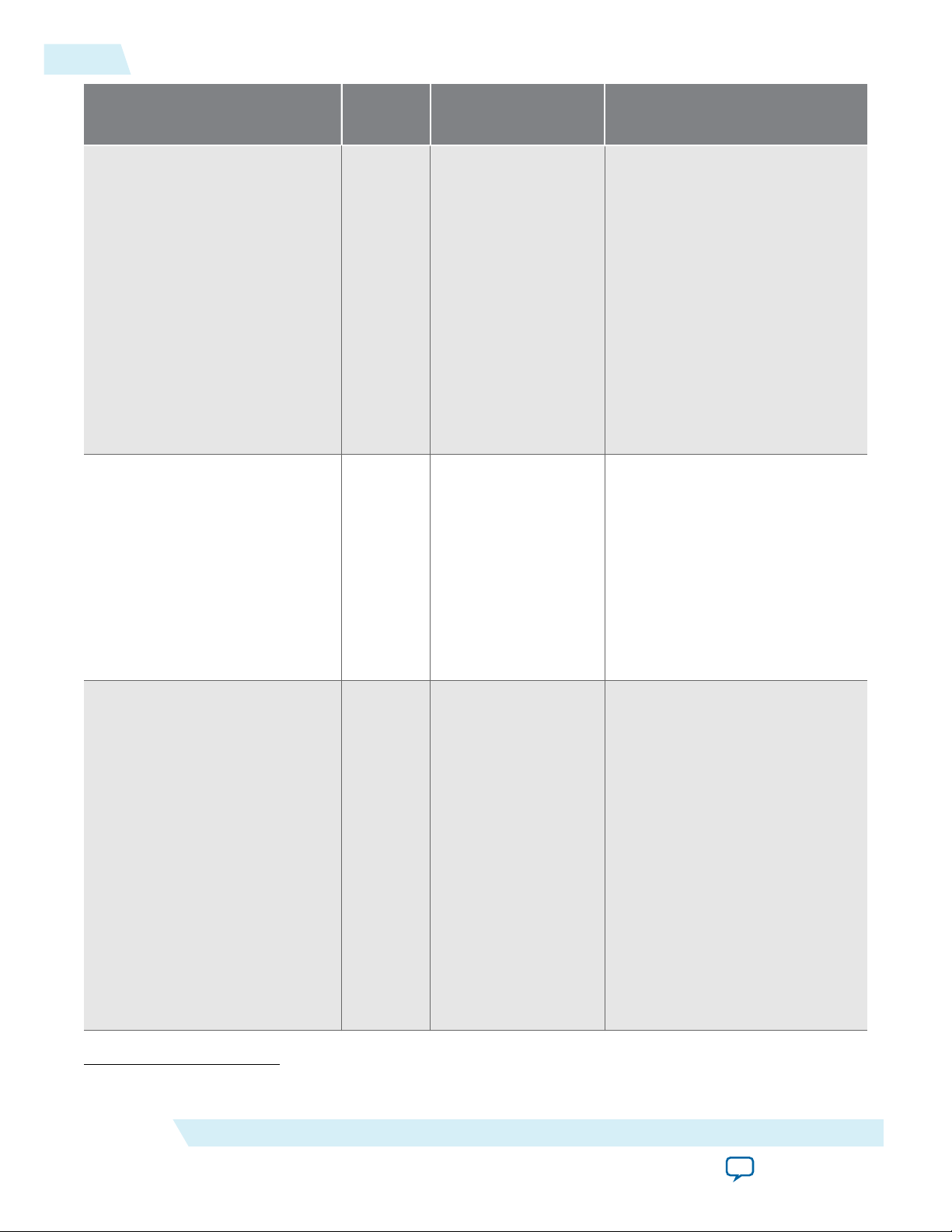

Parameter Editor GUI Setting

Name

Legal Values

Memory frequency 1–1068

Use DLL Offset

—

Control

Enable hard FIFOs —

CLI Parameter

Name

INPUT_FREQ 120–1068

USE_OFFSET_CTRL

USE_HARD_FIFOS

Legal

Values

true

false

true

false

(1)

Description

This setting specifies the

full-rate clock frequency

of the incoming DQS

group signal from the

external device in MHz.

The default value is

300 MHz (300).

This setting enables

dynamic control of the

DLL offset.

Altera recommends using

this setting for test

purposes only. For DQS

data capture calibration,

use the D1, D2, D3, and

D4 delay chains.

This setting enables the

hard FIFOs (read FIFO for

Stratix V devices and read

FIFO, latency shifter FIFO

and data valid FIFO for

Arria V and Cyclone V

devices) as part of the

ALTDQ_DQS2 IP core.

Use Capture Clock

to clock the read

Side of the Hard

VFIFO

Enable dual write

clocks

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

Altera Corporation

—

—

USE_DQSIN_FOR_

VFIFO_READ

DUAL_WRITE_CLOCK

true

false

true

false

Turn on this setting when

you use the hard data valid

FIFO and when the

capture clock is not gated.

This setting is available

only for Arria V and

Cyclone V devices.

This setting enables the

use of separate output

clocks for data and strobe.

This setting is disabled by

default for Arria V and

Cyclone V devices.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 13

UG-01089

2014.12.17

ALTDQ_DQS2 Parameter Settings

13

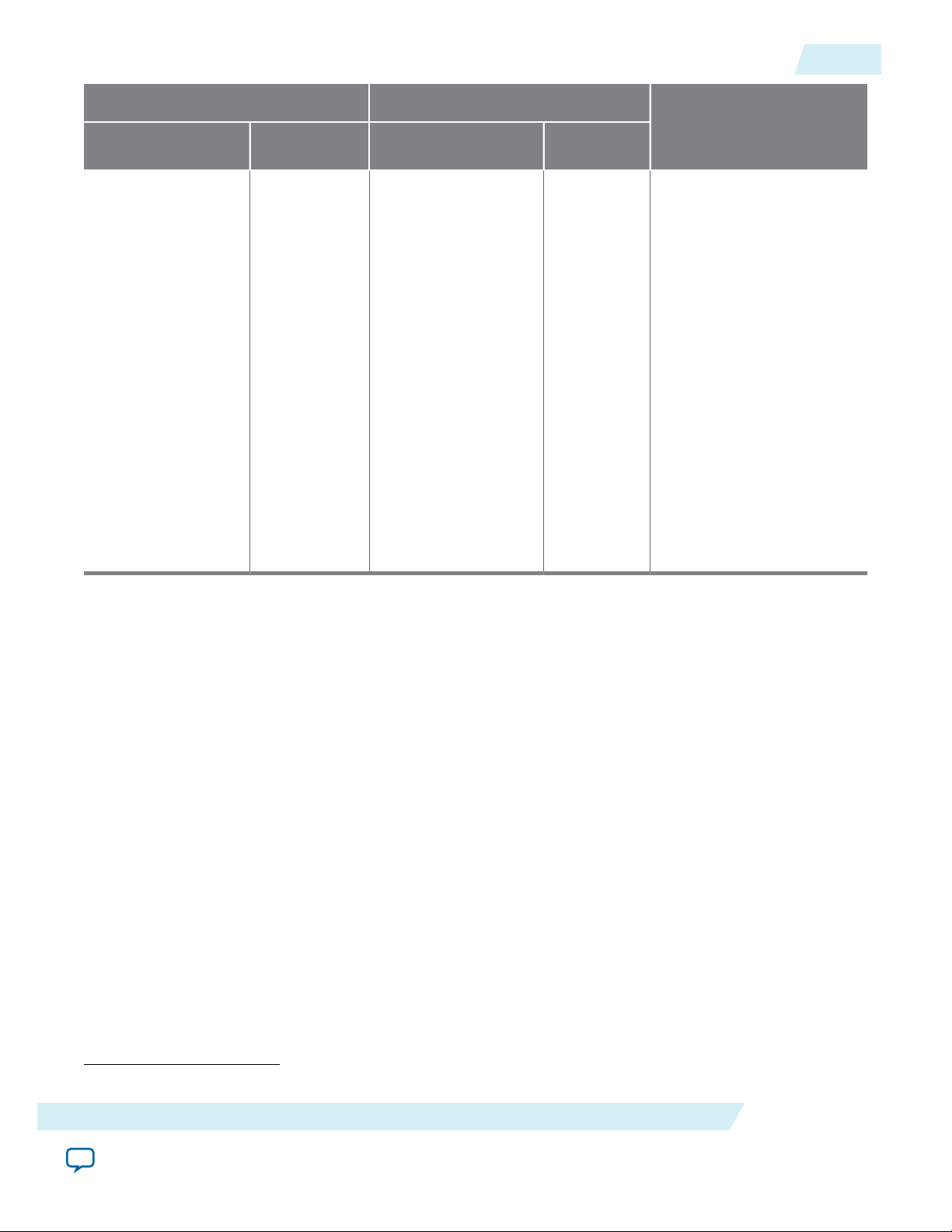

Parameter Editor GUI Setting

Name

Use dynamic

Legal Values

—

configuration scan

chains

Output Path

CLI Parameter

Name

USE_DYNAMIC_CONFIG

Legal

Values

true

false

Description

(1)

This setting enables

run-time configuration of

multiple delay chains,

phase shifts, and transfer

registers.

Requires a correctly

formatted bitstream.

For more information,

refer to DQS Configura‐

tion Block Bit Sequence

for Arria V GZ and

Stratix V Devices on page

42 and DQS Configura‐

tion Block Bit Sequence

for Arria V and Cyclone

V Devices on page 56.

Use half-rate

output path

Use output phase

alignment blocks

—

—

HALF_RATE_OUTPUT

USE_OUTPUT_PHASE_

ALIGNMENT

true

false

true

false

This setting doubles the

width of the data bus on

the FPGA side and clocks

the FPGA side interface

using the half-rate clock

input.

If this setting is enabled,

drive the hr_clock_in

port with the half-rate

clock signal.

When enabling hard read

FIFO in a Stratix V device,

you must set this

parameter to true.

This setting is enabled by

default.

This setting enables phase

shift on the output path

based on the delay settings

from the DLL.

This setting is disabled by

default.

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 14

14

ALTDQ_DQS2 Parameter Settings

UG-01089

2014.12.17

Parameter Editor GUI Setting

Name

Legal Values

Capture Strobe

Capture strobe

type

Single

Differential

Complemen‐

tary

Use inverted

—

capture strobe

CLI Parameter

Name

CAPTURE_STROBE_TYPE

INVERT_CAPTURE_

STROBE

Legal

(1)

Values

single

differential

complementary

true

false

Description

This setting specifies the

type of capture strobe

(DQS signal from the

external device).

The default value is Single

(single).

When enabled, this

parameter captures data

with an inverted capture

strobe.

Strobe inversion occurs

from dqsbusout (an

output port from the DQS

delay chain block) to the

clock input of the DDIO_

IN block.

DQS phase shift 0 degrees

45 degrees

90 degrees

135 degrees

Use capture strobe

—

enable block

DQS_PHASE_SETTING

USE_DQS_ENABLE

0

1

2

3

true

false

This setting is enabled by

default.

This setting specifies the

phase shift value for the

DQS delay chain to shift

the incoming strobe in the

data valid window during

read and write operations.

The default value is 90

degrees (2).

This setting is for Stratix V

devices only.

This setting enables the

capture strobe enable

block, which allows

control over the preamble

state of the capture strobe.

This setting is disabled by

default.

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 15

UG-01089

2014.12.17

ALTDQ_DQS2 Parameter Settings

15

Parameter Editor GUI Setting

Name

Treat the capture

Legal Values

—

strobe enable as a

half-rate signal

DQS enable phase

setting

0 degrees

45 degrees

90 degrees

135 degrees

Output Strobe

Generate output

—

strobe

CLI Parameter

Name

USE_HALF_RATE_DQS_

ENABLE

DQS_ENABLE_PHASE_

SETTING

USE_OUTPUT_STROBE

Legal

Values

true

false

0

1

2

3

true

false

Description

(1)

This setting doubles the

width of the capture

strobe enable bus on the

FPGA side and clocks the

FPGA side interface using

the half-rate clock input.

This setting specifies the

value of phase shift to shift

the full-rate clock signal

that drives the capture

strobe enable block.

The default value is 0

degrees (0).

This setting generates an

output strobe signal based

on the OE signal and the

full-rate clock. This setting

is enabled by default.

Make capture

strobe bidirec‐

tional

—

USE_BIDIR_STROBE

true

false

This setting enables the

bidirectional capture

strobe (capture strobe and

output strobe is on the

same port).

This setting is disabled by

default.

Differential/

complementary

output strobe

—

DIFFERENTIAL_

OUTPUT_STROBE

true

false

This setting enables either

the differential or

complementary output

strobe.

This setting is disabled by

default.

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 16

16

ALTDQ_DQS2 Parameter Settings

UG-01089

2014.12.17

Parameter Editor GUI Setting

Name

Use reset signal to

Legal Values

—

stop output strobe

OCT Source Output Strobe

Enable

Data Write

Enable

Dedicated

OCT Enable

CLI Parameter

Name

USE_OUTPUT_STROBE_

RESET

OCT_SOURCE

Legal

Values

true

false

0

1

2

Description

(1)

This setting stops the

unidirectional output

strobe using a userprovided reset signal. The

core_clock_in and the

reset_n_core_clock_in

signals are required.

This setting specifies the

type of input signal to

toggle the OCT control:

• Output Strobe Enable

—Uses the output_

strobe_ena input as

the OCT control signal.

• Data Write Enable—

Uses the write_oe_in

input as the OCT

control signal.

• Dedicated OCT

Enable—Adds a oct_

ena_in input to the

interface, which is used

as the OCT control

signal.

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

Altera Corporation

The availability of the

Output Strobe Enable,

Data Write Enable,and

Dedicated OCT Enable

are dependent on PIN_

TYPE and USE_BIDIR_

STROBE parameters.

Default value is Data

Write Enable.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 17

UG-01089

2014.12.17

ALTDQ_DQS2 Data Paths

17

Parameter Editor GUI Setting

Name

Legal Values

Preamble type high

low

none

CLI Parameter

Name

PREAMBLE_TYPE

Legal

Values

high

low

none

Description

(1)

This setting sets the DQS

preamble to high (DDR3),

low (DDR2), or none:

• When you select low

and the strobe is

bidirectional, the

output strobe is held

low for the first full

rate cycle.

• When you select high

or none, the strobe is

driven high for the first

full rate cycle.

• Default value is low.

Note:

The ALTDQ_

DQS2 IP core

does not

support DQS

tracking.

Related Information

• DQS Configuration Block Bit Sequence for Arria V and Cyclone V Devices on page 56

• DQS Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices on page 42

• IP-Generate Command on page 96

ALTDQ_DQS2 Data Paths

Describes the read and write data paths and using other IP cores with the ALTDQ_DQS2 IP core.

DQ and DQS Input Path

The DQ and DQS input paths receive the DQ and DQS signals from the external device during read

operations.

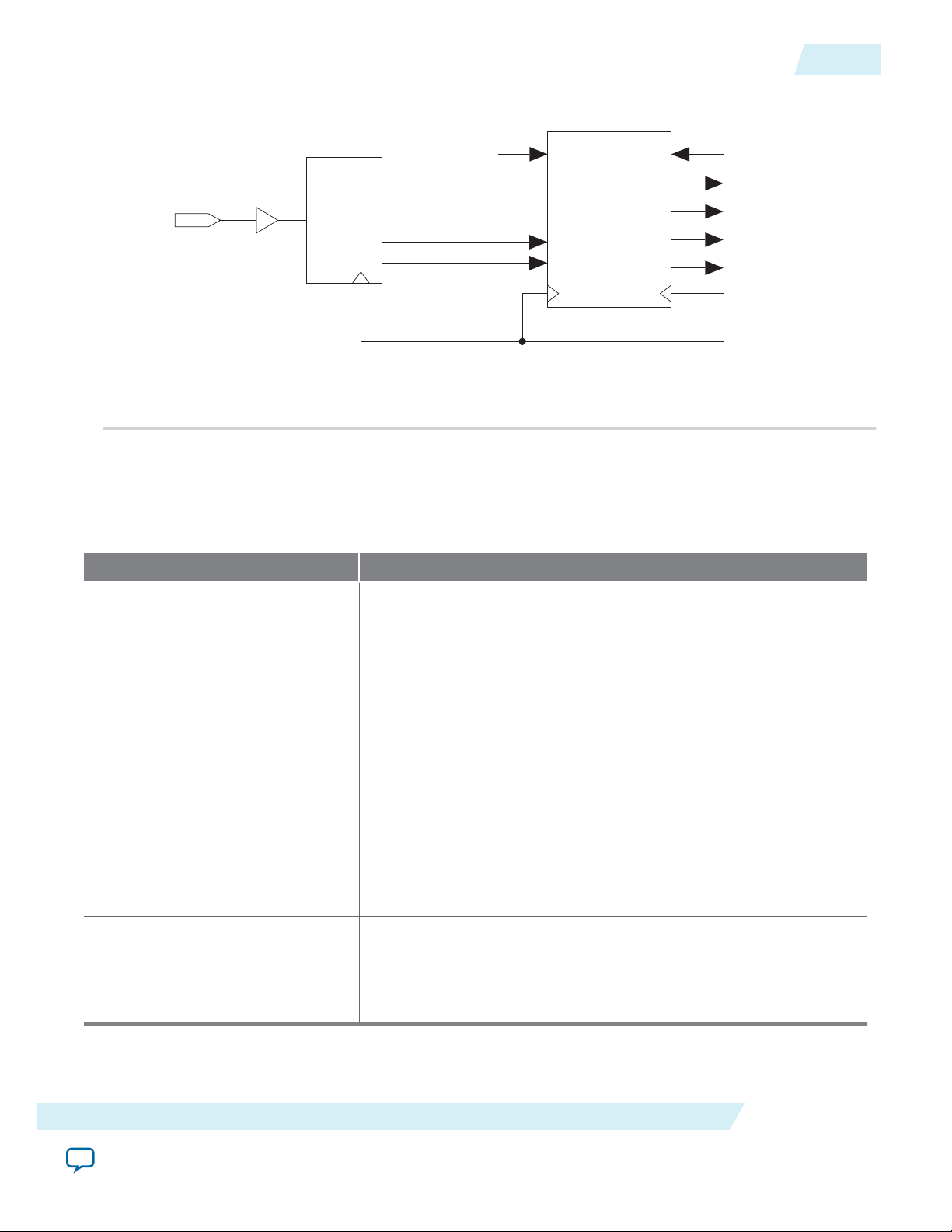

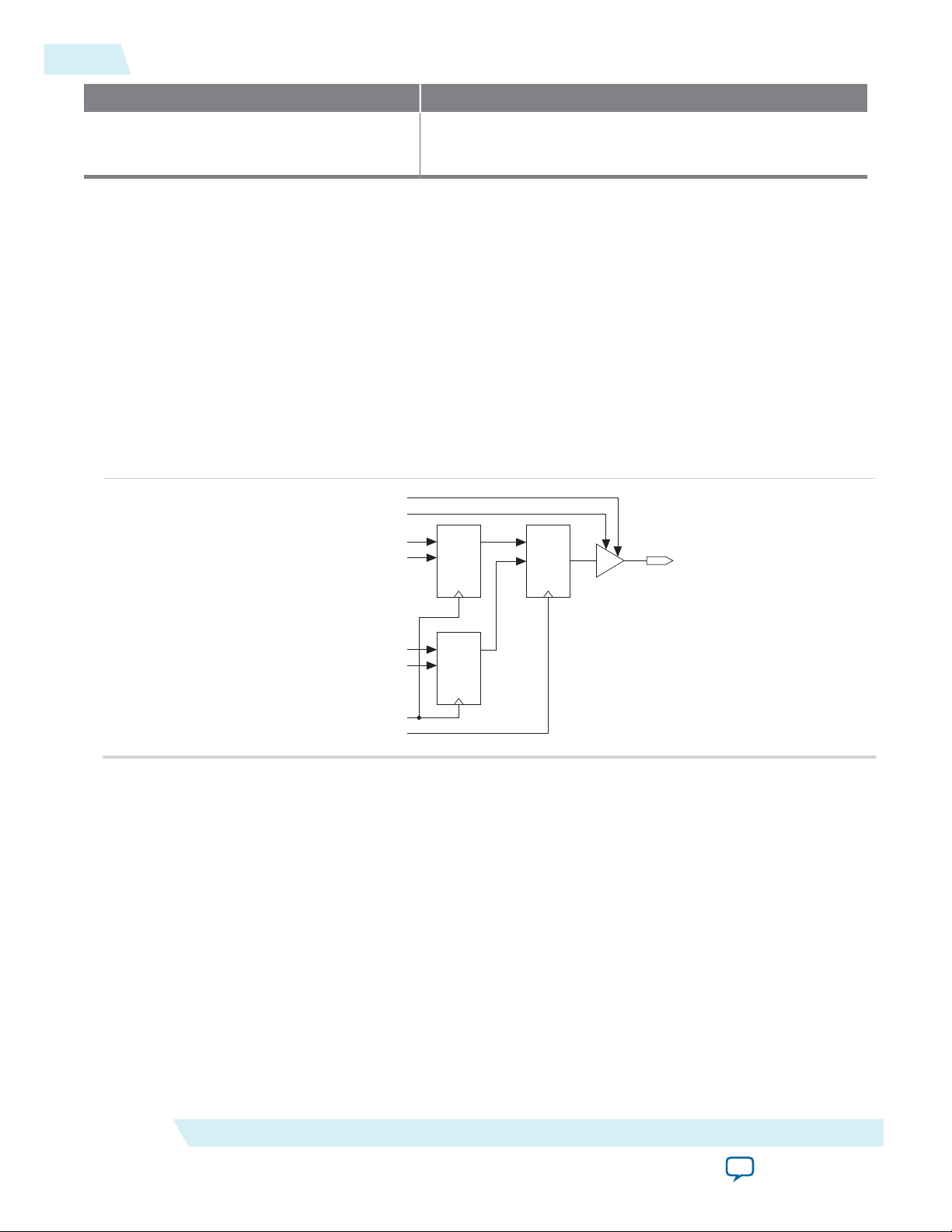

DQ and DQS Input Paths for Stratix V Devices

The following figure shows the input paths where x = 0 to (n-1) and n = the number of DQ pins.

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 18

capture_strobe_ena

PRE

D

Q

IN

LO

strobe_ena_clock_in

DQS Enable Control

DQS Delay Chain

HI

DQSIN

DQSBUSOUT

IN

OUT

capture_strobe_in

DQS Enable

read_data_in[x]

capture_strobe_out

read_data_out[x]

read_data_out[n+x]

(from DQS pin)

(from DQ pin)

DDIO_IN

You can use the DDIO_IN block with a soft or

hard read FIFO in Stratix V devices. However,

you can use this block with only a hard read

FIFO in Arria V and Cyclone V devices.

When the hard read FIFO block is not present,

the DQ and DQS path ends at the DDIO_IN

block.

For bidirectional DQS, the input of the

buffer connects to the strobe_io port.

For bidirectional DQ, the input of the buffer

connects to the read_write_data_io[x] port.

Optional inversion occurs from dqsbusout

(output port from the DQS delay chain block) to

the clock input of the DDIO_IN block.

CLK

18

Data Input Path for Arria V, Cyclone V, and Stratix V Devices

Figure 8: DQ and DQS Input Paths for Stratix V Devices

UG-01089

2014.12.17

Data Input Path for Arria V, Cyclone V, and Stratix V Devices

Altera Corporation

Note: For more information about the DQ and DQS input path with a hard read FIFO block, refer to

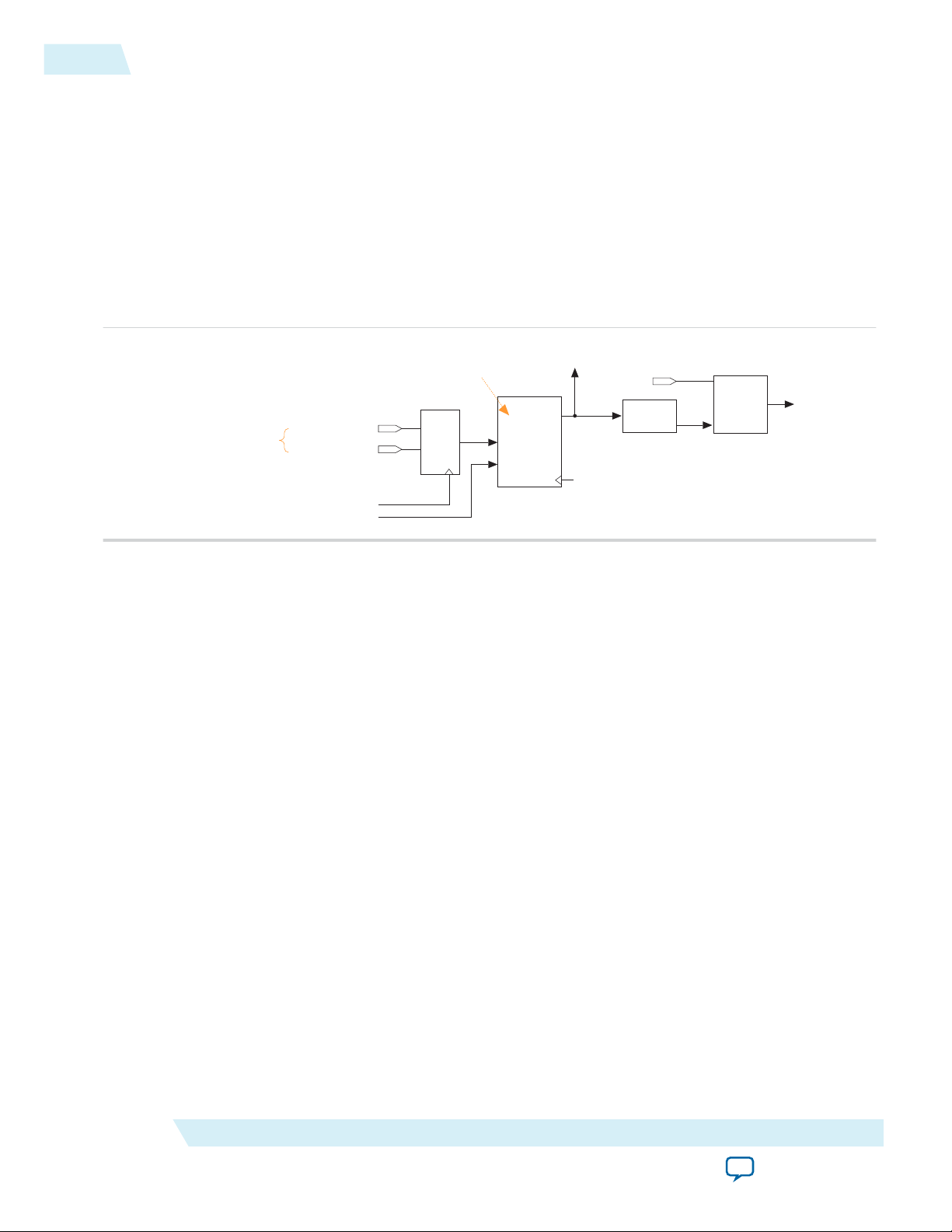

The DQ and DQS input paths in Arria V and Cyclone V devices are the same, except for an additional

read FIFO block to implement the second-stage rate conversion DDIO. The high-speed 4 x 8 read FIFO,

Figure 9 and Figure 10.

clocked by the DQS clock, implements the half-rate to full-rate conversion, if necessary.

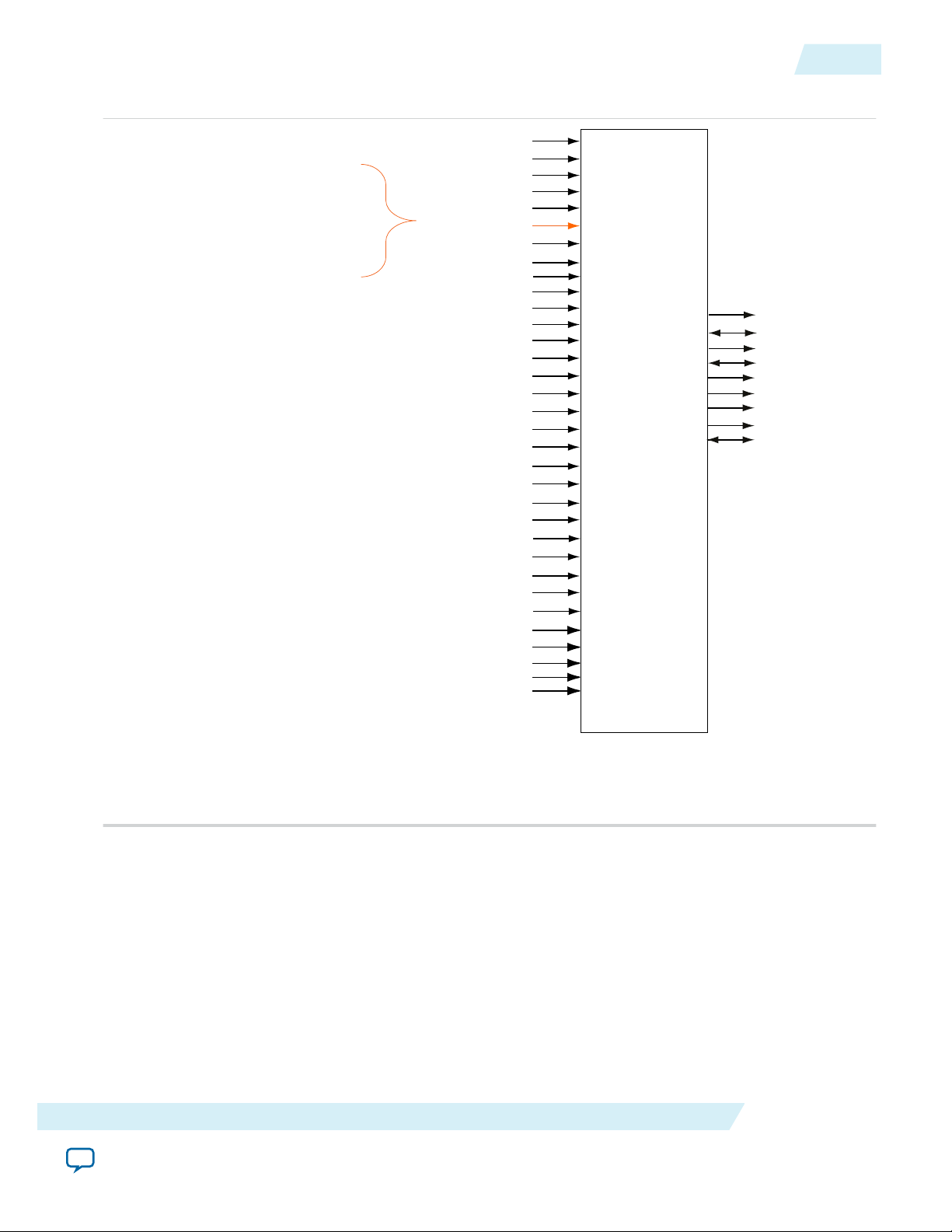

The following figure shows the data input path (when you enable the hard read FIFO) for Arria V,

Cyclone V, and Stratix V devices.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 19

DATAIN

Delay

Chain

DDIO

In

FIFO REN Logic

DATAOUT[0]

DATAOUT[1]

DATAOUT[2]

DATAOUT[3]

HR or FR Clock

DQS from DQS Logic

FIFO WREN

Logic

Read

FIFO

WREN REN

This figure is applicable to Stratix V devices because Stratix V devices support optional hard read FIFO.

UG-01089

2014.12.17

Figure 9: Data Input Path for Arria V, Cyclone V, and Stratix V Devices

Blocks in DQ and DQS Data Input Path

The following table lists the blocks in the DQ and DQS input paths.

Blocks in DQ and DQS Data Input Path

19

Table 4: Blocks in DQ and DQS Input Path

Block Name Description

DQS enable • Represents the AND-gate control on the DQS input that grounds

the DQS input strobe when the strobe goes to Hi-Z after a DDR

read postamble. The DQS enable block enables the registers to

allow enough time for the DQS delay settings to travel from the

DQS phase-shift circuitry or core logic to all the DQS logic blocks

before the next change.

• For more information about the DQS enable block, refer to the

“Update Enable Circuitry” in the External Memory Interfaces

chapter in the respective device handbook.

DQS enable control • Represents the circuitry that controls the DQS enable block. A

DQS enable control block controls each DQS enable block.

• For more information about the DQS enable control block, refer

to the “DQS Postamble Circuitry” in the External Memory

Interfaces chapter in the respective device handbook.

DQS delay chain • Represents the delay chains that delay signals.

• For more information about the DQS delay chain block, refer to

“DQS Delay Chain” in the External Memory Interfaces chapter in

the respective device handbook.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 20

capture_strobe_ena[0]

DDIO

Out

FR Clock

capture_strobe_ena[1]

strobe_ena_hr_clock_in

vfifo_inc_wr_ptr

inc_wr_ptr

capture_strobe_in

Data Valid

FIFO

DQS Enable

Control

DQS Delay

Chain

DQS Clock Tree

These ports are 2-bit wide because the

DDIO_OUT block is driven by a half-rate

clock, allowing you to enable DQS during

a half-rate cycle.

The data valid FIFO is a hard FIFO

in Arria V and Cyclone V devices.

Read FIFO

Write Enable

20

DQS Logic

DQS Logic

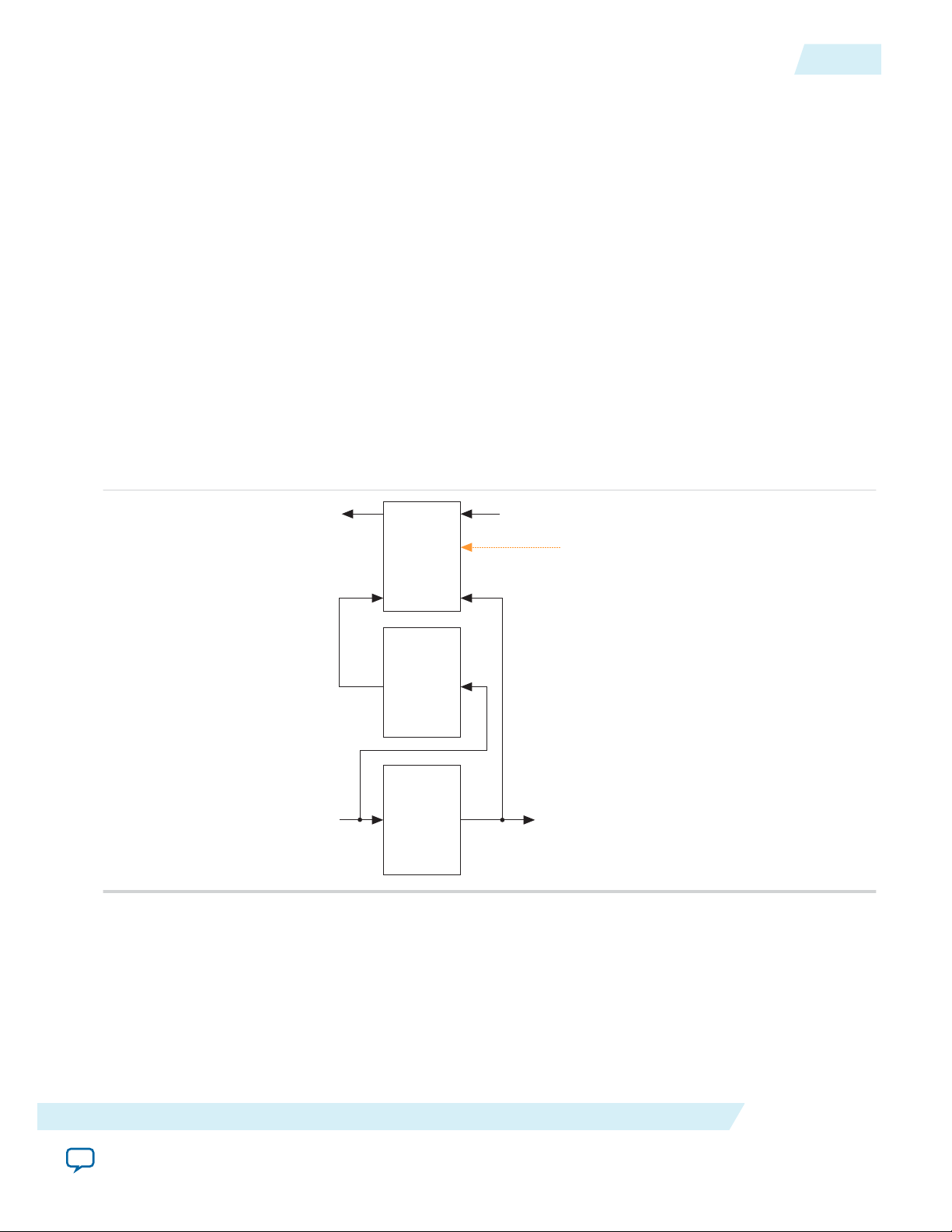

The DQS input path in Arria V and Cyclone V devices has the following differences from Stratix V and

earlier versions of the device families:

• A data valid FIFO delays the DQS enable path by up to 16 full-rate cycles. During a required calibra‐

tion process, you can increase the unknown delay, which the data valid FIFO implements, by 1, by

pulsing the INC_WR_PTR port. The delay wraps around after 16 increments.

• The DQS delay chain implements a static non-programmable phase shift of 90°.

The following figure shows the DQS input path in Arria V and Cyclone V devices.

Figure 10: DQS Input Path in Arria V and Cyclone V Devices

UG-01089

2014.12.17

Capture DDIO to Read FIFO Path

The capture DDIO block captures input data (DQ) on the rising and falling edges of the capture clock or

strobe (DQS).

For Stratix V devices, the capture DDIO block feeds the hard read FIFO or bypasses the hard read FIFO

and goes directly to the core. If the capture DDIO block connects directly to the core, the data is

transmitted at full rate. For protocols with bidirectional DQS, only an exact number of DQS edge is

available for both capturing data in the capture DDIO block and then either in the read FIFO or in the

core. The data transfer from the capture DDIO block and the next stage is referred to as zero-cycle

transfer. This means that the transfer must happen on the same clock edge.

The hard read FIFO always changes the data rate from full-rate to half-rate, so if you choose to use fullrate, then you cannot use the Read FIFO.

For Arria V and Cyclone V devices, the capture DDIO block to Read FIFO path is similar, with the

following exceptions:

• The read FIFO must always be used and cannot be bypassed.

• The read FIFO supports both half-rate and full-rate.

For Arria V, Cyclone V, and Stratix V devices, the hard read FIFO implements the functionality of a

generic asynchronous FIFO. You can locate the hard read FIFO in a true dual-ported RAM. Data is

written to the write side of the DQS clock domain and read from the read side of the core clock domain.

For Arria V and Cyclone V devices, the core clock domain can run at half the frequency and implements a

full-rate to half-rate transformation. You can use the write enable and read enable signals to control when

to write and read data from the read FIFO. The same signal controls the increment of the write and read

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 21

The read FIFO block is a hard FIFO in Arria V,

Cyclone V, and Stratix V devices. The latency

shifter FIFO and data valid FIFO are hard

FIFO in Arria V and Cyclone V devices.

Read

FIFO

DOUT

DIN

REN WREN

Latency

Shifter

FIFO

Data

Valid

FIFO

Data to Core Data from DQ

To DQS Enable

Read Data Enable from Core

UG-01089

2014.12.17

FIFO Control

pointers. For protocols using a bidirectional strobe, the write enable signal is tied to VCC and DQS

gating/ungating implements the write enable functionality.

For Arria V and Cyclone V devices, the hard data valid FIFO internally generates the write enable (or

gating/ungating) signal, while the hard latency FIFO internally generates the read enable signal.

FIFO Control

For Arria V and Cyclone V devices, in addition to the read FIFO and the data valid FIFO, the location of

the latency shifter FIFO is in each DQS group. The latency shifter FIFO takes in a read-enable command

from the core and implements a programmable latency of up to 32 cycles before feeding into the readenable port of the read FIFO.

You can use the output of the data valid FIFO to perform the following tasks:

• To ungate the DQS logic when a strobe signal is capturing the data. In this case, the write-enable port

must always be '1' on the read FIFO.

• To enable the read FIFO write-enable port when a clock is in use.

The following figure shows the three FIFOs interconnection.

Figure 11: Data Valid FIFO, Latency Shifter FIFO, and Read FIFO Interconnection

21

ALTDQ_DQS2 IP Core User Guide

Send Feedback

When a read command is sent to the memory device, a read-data-enable token is pushed through the data

valid FIFO and the latency shifter FIFO. The data valid FIFO implements a latency equal to the read

command to data latency. When the token comes out of the data valid FIFO, the DQS signal is ungated.

The latency shifter FIFO then creates enough space between write and read pointers in the read FIFO to

ensure that the data read on the read side is correct. If the read FIFO is read at half-rate, the read FIFO

also implements a full-rate to half-rate conversion.

Altera Corporation

Page 22

write_oe_in[2x]

hr_clock_in

datain

dataout

LO

OUT

write_oe_in[2x+1]

D

Q

write_data_in[3n+x]

hr_clock_in

HI

OUT

write_data_in[n+x]

HI

OUT

hr_clock_in

write_data_in[2n+x]

datain

dataout

HI

Q

write_data_in[x]

LO

HI

Half-rate to

single-rate output

enable registers

Output phase

alignment registers

Alignment

clock

Write

clock

0

1

LO

0

1

datain

dataout

0

1

DDR output registers

Write

clock

Alignment

clock

write_data_out[x]

Half-rate to

single-rate

output registers

Alignment

clock

Half-rate to

single-rate

output registers

Output phase

alignment registers

Output phase

alignment registers

0

1

0

1

0

1

Series termination

control

LO

write_oe_in[x]

(to DQ pin)

write_data_in[x]

write_data_in[n+x]

DFF

Alignment

clock

Write

clock

Series termination

control

The alignment clock comes from the write-leveling delay chains. For more information, refer to “Leveling Circuitry”

section in the External Memory Interfaces in Stratix V Devices chapter in the Stratix V Device Handbook.

The write clock comes from the PLL or the write-leveling delay chains. For more information, refer to “Leveling

Circuitry” section in the External Memory Interfaces in Stratix V Devices chapter in the Stratix V Device Handbook.

The series termination control connects to the ALTOCT megafunction.

For bidirectional DQ, the output of the buffer

connects to the read_write_data_io[x] port.

22

DQ and DQS Output Path

The determination of the correct latencies to implement at each of these FIFOs is important and cannot

be done during compilation. When you attempt to implement your own custom memory solution, you

must also implement some form of calibration algorithm.

To determine if the data coming from the read FIFO is valid, you must implement the read data valid

latency in soft logic.

Related Information

UniPHY External Memory Interface Debug Toolkit

DQ and DQS Output Path

The DQ and DQS output path sends the DQ and DQS signal to the external device during write

operations.

DQ and DQS Output Path for Stratix V Devices

The following figure shows the output path where n = the number of DQ pins and x = 0 to (n-1). is only

applicable for Stratix V devices.

Note: This figure is only applicable for Stratix V devices. For Arria V and Cyclone V DQ and DQS output

path, refer to Figure 14.

UG-01089

2014.12.17

Figure 12: DQ and DQS Output Path for Stratix V Devices

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 23

extra_write_data_in[3m+y]

hr_clock_in

datain

dataout

HI

OUT

extra_write_data_in[2m+y]

HI

OUT

hr_clock_in

extra_write_data_in[m+y]

datain

dataout

HI

OUT

extra_write_data_in[y]

LO

Half-rate to

single-rate output

enable registers

Output phase

alignment registers

Alignment

clock

0

1

Alignment

clock

Half-rate to

single-rate

output registers

Output phase

alignment registers

0

1

0

1

0

1

VCC

DDR output registers

extra_write_data_out[y]

Write clock

LO

LO

extra_write_data_in[y]

(to DQ pin)

Alignment

clock

Write clock

The alignment clock comes from the write-leveling delay chains.

The write clock comes from the PLL or the write-leveling delay chains.

UG-01089

2014.12.17

Blocks in DQ and DQS Output Path

The following figure shows the DQ and DQS output path for additional DQ pins usage, where y = 0 to

(m-1) and m= the number of DQ pins

Figure 13: DQ and DQS Output Path (for Additional DQ Pins Usage) for Stratix V Devices

23

Blocks in DQ and DQS Output Path

Table 5: Blocks in the DQ and DQS Output Path

ALTDQ_DQS2 IP Core User Guide

Related Information

• External Memory Interfaces in Stratix V Devices

The following table lists the blocks in the DQ and DQS output path.

Block Name Description

Half-rate to single-rate output enable

registers

Output phase alignment registers Represents the circuitry required to phase shift the DQ-

Represents a group of registers that convert half-rate data to

single-rate data.

output signals. Use this block for write-leveling purposes in

DDR3 SDRAM interfaces.

Altera Corporation

Send Feedback

Page 24

DATAOUT

DDIO

Out

DATAOUT[0]

DATAOUT[1]

DATAOUT[2]

DATAOUT[3]

DDIO

Out

DDIO

Out

CLK_HR

CLK_FR

OCT from DQS Logic

OE from Output Enable Path

24

DQ and DQS Output Path for Arria V and Cyclone V Devices

Block Name Description

DDR output registers Represents the DDIO registers that transfer DDR signals

from the core to the DQ/DQS pins.

Related Information

• External Memory Interfaces in Arria V Devices

• External Memory Interfaces in Cyclone V Devices

• External Memory Interfaces in Stratix V Devices

DQ and DQS Output Path for Arria V and Cyclone V Devices

The data output path for Arria V and Cyclone V families is similar to the output paths for Stratix V and

earlier families, except for the output phase alignment registers. These registers are not available in Arria

V and Cyclone V devices and do not support leveled interfaces.

The following figure shows the DQ and DQS output path for Arria V and Cyclone V devices.

Figure 14: DQ and DQS Output Path for Arria V and Cyclone V Devices

UG-01089

2014.12.17

ALTDQ_DQS2 Ports

Altera Corporation

You must connect the ALTDQ_DQS2 IP core to the ALTOCT, ALTDLL, and ALTERA_PLL IP cores to

utilize their features.

Related Information

• Instantiating IP cores

The following figure shows the data strobe, data, termination control, PLL, DLL, hard FIFO, and dynamic

configuration ports of the IP core.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 25

-

ALTDQ_DQS2

config_clock_in

config_data_in

config_dqs_ena

config_dqs_io_ena

config_update

core_clock_in

fr_clock_in

hr_clock_in

lfifo_rden

reset_n_core_clock_in

rfifo_reset_n

strobe_ena_hr_clock_in

vfifo_reset_n

write_strobe_clock_in

dll_delayctrl_in[]

capture_strobe_ena[]

output_strobe_ena[]

oct_ena_in[]

parallelterminationcontrol_in[]

seriesterminationcontrol_in[]

write_oe_in[]

output_strobe_n_out

output_strobe_out

extra_write_data_out[]

write_data_out[]

strobe_n_io

capture_strobe_out

read_data_out[]

strobe_io

read_write_data_io[]

write_data_in[]

config_io_ena[]

lfifo_rdata_en_full[]

lfifo_rd_latency[]

vfifo_qvld[]

vfifo_inc_wr_ptr[]

capture_strobe_n_in

extra_write_data_in[]

read_data_in[]

config_extra_io_ena[]

lfifo_reset_n

capture_strobe_in

This signal is used for QDRII. This clock, unlike

other clocks, can be held at zero during initialization,

which is a requirement for QDRII. Use the core

clock signal for internal purposes. In a half-rate

application, the core clock signal is unconnected. In

a full-rate application, you must connect the core

clock signal to the full-rate clock.

UG-01089

2014.12.17

Figure 15: ALTDQ_DQS2 Block Diagram by Port Types

ALTDQ_DQS2 Ports

25

ALTDQ_DQS2 IP Core User Guide

Altera Corporation

Send Feedback

Page 26

26

ALTDQ_DQS2 Data Strobe Ports

ALTDQ_DQS2 Data Strobe Ports

Table 6: ALTDQ_DQS2 Data Strobe Ports

Port Name Type Width Description

UG-01089

2014.12.17

capture_strobe_ena

capture_strobe_n_in

Input 1 Controls the DQS enable control

block by acting as the gating

signal for signals coming from

the input registers (capture_

strobe_in) to reach the DQS

delay chain block.

This port is only supported in

Stratix V devices.

Input 1 Receives the negative polarity

clock signal from the external

device. For example, a DQSn

signal from the external

memory. This port is available

when the capture strobe type is

set to differential or complemen‐

tary.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

capture_strobe_in

capture_strobe_out

Input 1 Receives the clock signal from

the external device, for example,

a DQS signal from the external

memory.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Output 1 Sends the delayed clock signal to

the core. For example, a delayed

DQS signal from the DQS delay

chain.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 27

UG-01089

2014.12.17

ALTDQ_DQS2 Data Strobe Ports

Port Name Type Width Description

27

output_strobe_ena

oct_ena_in

reset_n_core_clock_in

write_strobe_clock_in

Input 2 = half-rate

1 = full-rate

The gating signal for the

output_strobe_out port.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input 2 = half-rate

1 = full-rate

Controls the dynamic on-chiptermination signal for all data

and strobe ports.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input 1 Asynchronous reset used in

QDRII-like interfaces to reset the

write strobe.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input 1 Receives the clock signal from

the core. For example, a DQS

signal from the core. Clocks the

DDIO that generates the output

strobe signal.

ALTDQ_DQS2 IP Core User Guide

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Note: This signal is the

main full-rate input

clock when you set

the IP type to Input

for Arria V and

Cyclone V devices.

Altera Corporation

Send Feedback

Page 28

28

ALTDQ_DQS2 Data Strobe Ports

Port Name Type Width Description

UG-01089

2014.12.17

strobe_ena_hr_clock_in

strobe_io

strobe_n_io

Input 1 Receives the clock signal from

the clock pin or the PLL to clock

the DQS enable control block.

Also a half-rate signal that, after

going through the DQS_ENABLE_

CTRL input, controls the gating of

the input strobe.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Bidirectional 1 Sends and receives the bidirec‐

tional clock signal.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Bidirectional 1 Sends and receives the negative

polarity clock signal for differen‐

tial or complementary strobe

configuration.

output_strobe_out

output_strobe_n_out

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Output 1 Sends clock signal to the external

device. For example, a DQS

signal to the external memory.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Output 1 Sends the negative polarity clock

signal to the external device (For

example, DQSn signal to the

external memory). This port is

available when you set the

output strobe type to differential

or complementary.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 29

UG-01089

2014.12.17

ALTDQ_DQS2 Data Ports

The following table lists the ALTDQ_DQS2 data ports where n= number of DQ pins, m= number of

additional output-only DQ pins, x = 0 to (n-1), and y= 0 to (m-1).

Table 7: ALTDQ_DQS2 Data Ports

ALTDQ_DQS2 Data Ports

29

Port Name Type Width

extra_write_data_in[]

extra_write_data_out[]

Description

(2)

Input 2m = full-rate

4m = half-rate

Receives data signal from the

core.

This port connects to the input

port of the half-rate data to

single-rate data output registers

block (Figure 13). In full-rate

mode, only the extra_write_

data_in[y] and extra_write_

data_in[m+y] ports are used.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Output m Sends data to the external device.

This port connects to the output

port of the output buffer (Figure

13).

read_data_in[]

(2)

The port width applies to full-rate mode, unless otherwise specified.

ALTDQ_DQS2 IP Core User Guide

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input n Receives data from the external

device.

This port connects to the input

port of the input buffer located

between the DQ pin and the

DDR input registers block. This

is an input-only DQ port that

receives data from the external

device (Figure 8).

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Altera Corporation

Send Feedback

Page 30

30

ALTDQ_DQS2 Data Ports

UG-01089

2014.12.17

Port Name Type Width

read_data_out[]

read_write_data_io[]

(2)

Output 2n = full-rate

4n = half-rate

Bidirec‐

n Receives and sends data between

tional

Description

Sends the captured data from the

external device to the core.

This port connects to the output

port of the DDR input register

block (Figure 8). The read_

data_out[x] port outputs the

positive-edge triggered data, and

the read_data_out[n+x] port

outputs the negative-edge

triggered data.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

the core and the external device.

You must assign the bidirec‐

tional DQ port with the output

termination and input termina‐

tion assignments.

write_data_in[]

Input 2n = full-rate

4n = half-rate

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Receives DDR data signal from

the core to be sent out to the

external device. For example,

data to be written to the external

memory during write operation.

This port connects to the input

port of the half-rate data to

single-rate data output registers

block (Figure 12). In full-rate

mode, the IP core uses only the

write_data_in[x] and write_

data_in[n+x] ports.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

(2)

The port width applies to full-rate mode, unless otherwise specified.

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 31

UG-01089

2014.12.17

ALTDQ_DQS2 Data Ports

31

Port Name Type Width

write_data_out[]

write_oe_in[]

Description

(2)

Output n Sends the DDR data signal to the

external device. For example,

data to be written to the external

memory during write operation.

This port connects to the output

port of the output buffer located

between the DDR output

registers block and the DQ-out

pin (Figure 12).

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input n = full-rate

2n = half-rate

Receives the gating signal from

the core to control the output

buffer. For example, gating

control when writing data to the

external memory during write

operation.

This port connects to the input

port of the half-rate data to

single-rate data output-enable

registers block (Figure 12). In

full-rate mode, the IP core uses

only the write_oe_in[x] port.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Note: To understand how these ports connect to the IOEs, refer to “I/O Elements” in the External

Memory Interfaces in Stratix V Devices chapter of the Stratix V Device Handbook.

(2)

The port width applies to full-rate mode, unless otherwise specified.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 32

32

ALTDQ_DQS2 Termination Control Ports

ALTDQ_DQS2 Termination Control Ports

Table 8: ALTDQ_DQS2 Termination Control Ports

Port name Type Width Description

UG-01089

2014.12.17

parallelterminationcontrol_in[]

seriesterminationcontrol_in[]

Input 16 Controls the calibrated

parallel termination ports

of the input buffers.

You must connect this port

to the paralleltermina-

tioncontrol[15:0] port

of the ALTOCT IP core.

Ensure that the termination

block located in the

ALTOCT instance is

assigned with the termina‐

tion control block

assignment.

This port is supported in

Arria V, Cyclone V, and

Stratix V devices.

Input 16 Controls the calibrated

series termination ports of

the output buffers.

You must connect this port

to the seriestermina-

tioncontrol[15:0] port

of the ALTOCT IP core.

Ensure that the termination

block located in the

ALTOCT instance is

assigned with the termina‐

tion control block

assignment.

Related Information

• DC and Switching Characteristics for Stratix V Devices

Altera Corporation

This port is supported in

Arria V, Cyclone V, and

Stratix V devices.

Describes the dynamic OCT control in Stratix V devices.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 33

UG-01089

2014.12.17

ALTDQ_DQS2 PLL and DLL Ports

Table 9: ALTDQ_DQS2 PLL and DLL Ports

Port name Type Width Description

ALTDQ_DQS2 PLL and DLL Ports

33

dll_delayctrl_in[]

fr_clock_in

hr_clock_in

Input 7 Receives the 7-bit delay settings

from the dll_delayctrlout port of

the ALTDLL instance. This 7-bit

signal controls delay through the

DQS delay chains. Compilation

error occurs if this port is not

connected to a DLL.

This port is supported in Arria V,

Cyclone V, and Stratix V devices.

Input 1 Receives the full-rate clock signal

from a clock pin, or the PLL clock

output port.

This port is supported in Arria V,

Cyclone V, and Stratix V devices.

Input 1 Receives the half-rate clock signal

from a clock pin, or the PLL clock

output port.

This port is supported in Arria V,

Cyclone V, and Stratix V devices.

Note: For more information about DLL in Stratix V device, refer to “Delay-Locked Loop” in the External

Memory Interfaces in Stratix V Devices chapter of the Stratix V Device Handbook.

Note: For more information about PLL in Stratix V devices, refer to “PLL Specifications” in DC and

Switching Characteristics for Stratix V Devices chapter of the Stratix V Device Handbook.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 34

34

ALTDQ_DQS2 Hard FIFO Ports

ALTDQ_DQS2 Hard FIFO Ports

Table 10: Hard FIFO Ports

Ports Type Width Description

UG-01089

2014.12.17

lfifo_rdata_en_full

lfifo_rden Input

Input 2 Data input to the latency shifter

FIFO. This signal is the full read

enable token generated by user

logic and is asserted for the

length of the desired read burst.

This token is delayed by a

variable number of integer cycles

inside the latency shifter FIFO

and used to feed the read enable

signal of the read FIFO.

This port is only supported in

Arria V and Cyclone V devices.

1 Data input to the Read FIFO

Read Enable. This signal is the

full read enable token generated

by user logic and is asserted for

the length of the desired read

burst.

This port is only supported in

Stratix V devices.

lfifo_reset_n

lfifo_rd_latency[]

Altera Corporation

Input 1 Active high reset to the latency

shifter FIFO

This port is only supported in

Arria V and Cyclone V devices.

Input 5 The number of cycles to delay

data inputs feeding the latency

shifter FIFO. A maximum of 31

cycles is supported.

This port is only supported in

Arria V and Cyclone V devices.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 35

UG-01089

2014.12.17

ALTDQ_DQS2 Dynamic Configuration Ports

Ports Type Width Description

35

vfifo_qvld

vfifo_inc_wr_ptr

vfifo_reset_n

Input Arria V and

Cyclone V

devices: 2

Stratix V

devices: 1

Data input to the data valid

FIFO. This signal is the full read

enable token generated by user

logic and is asserted for the

length of the desired read burst.

This signal is driven by the same

user logic that drives the lfifo_

rdata_en_full signal.

In general applications, you can

leave this port unconnected.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input 2 Increments the latency

implemented by the data valid

FIFO by one cycle.

This port is only supported in

Arria V and Cyclone V devices.

Input 1 Active high reset to the data

valid FIFO

rfifo_reset_n

Input 1 Active high reset to the read

The I/O and DQS configuration blocks represent a set of serial-to-parallel shift registers that dynamically

changes the settings of various device configuration bits. The I/O and DQS configuration blocks shift a

serial configuration data stream into the shift registers, and then load the data stream into the configura‐

tion registers. The shift registers power-up low. Every I/O pin contains an I/O configuration block. Every

DQS group contains a DQS configuration block and an I/O configuration block.

ALTDQ_DQS2 Dynamic Configuration Ports

The following table lists the dynamic configuration ports where n= number of DQ pins and m= number

of additional DQ pins.

This port is only supported in

Arria V and Cyclone V devices.

FIFO .

This port is only supported in

Arria V and Cyclone V devices.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 36

36

ALTDQ_DQS2 Dynamic Configuration Ports

Table 11: ALTDQ_DQS2 Dynamic Configuration Ports

Port name Type Width Description

UG-01089

2014.12.17

config_clock_in

config_data

Input 1 The ALTDQ_DQS2 dynamic

configuration interface consists

of this input port.

Receives the clock signal to

clock all dynamic configuration

blocks. You can connect this

port to a clock pin, or the PLL

clock output port.

This is the clock signal. All other

input signals must be treated as

synchronous to this clock.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input 1 The ALTDQ_DQS2 dynamic

configuration interface consists

of this input port.

The 1-bit serial input through

which data is scanned into the

calibration blocks. It is common

to all configuration blocks, but it

will only be scanned into

calibrations blocks whose enable

input is asserted.

config_io_ena[]

Altera Corporation

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input n An input port that controls the

enable input on the DQ I/O

configurations. Receives the

clock enable signal for the I/O

configuration block.

Refer to Dynamic Reconfigura‐

tion for ALTDQ_DQS2 on

page 38

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 37

UG-01089

2014.12.17

ALTDQ_DQS2 Dynamic Configuration Ports

Port name Type Width Description

37

config_dqs_io_ena

config_dqs_ena

Input 1 An input port that controls the

enable input on the DQS I/O

configurations. Receives the

clock enable signal for the DQS

I/O configuration block.

Refer to Dynamic Reconfigura‐

tion for ALTDQ_DQS2 on

page 38

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input 1 An input port that controls the

enable input on the DQS logic.

Receives the clock enable signal

for the DQS configuration

block.

Refer to Dynamic Reconfigura‐

tion for ALTDQ_DQS2 on

page 38

config_update

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Input 1 The ALTDQ_DQS2 dynamic

configuration interface consists

of this input port.

Receives the signal to load the

bits from the serial-to-parallel

shift registers to the configura‐

tion registers.

After scanning all the bits into

the desired scan chain blocks,

the bits can be copied at once

into the configuration register

by asserting the config_update

signal for one clock cycle.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 38

38

Dynamic Reconfiguration for ALTDQ_DQS2

Port name Type Width Description

UG-01089

2014.12.17

config_data_in

config_extra_io_ena[]

Input 1 Receives the serial configuration

Input m Receives the clock enable signal

Note: For more information about the dynamic configuration blocks in Stratix V device, refer to “I/O

Configuration Block and DQS Configuration Block” in the External Memory Interfaces in Stratix

V Devices chapter of the Stratix V Device Handbook.

Dynamic Reconfiguration for ALTDQ_DQS2

data stream that shifts into the

serial-to-parallel shift registers.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

for the additional I/O configura‐

tion block.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

When static timing closure is challenging (for example, high frequency, high board trace skew, and high

timing uncertainty), dynamically reconfiguring the ALTDQ_DQS2 IP core may provide additional timing

margin. Arria V, Cyclone V, and Stratix V devices contain reconfigurable logic, allowing you to adjust the

delay of several datapaths at runtime.

The I/O configuration block and the DQS configuration block are shift registers that you can use to

dynamically change the settings of various device configuration bits. The shift registers are configured

with the rest of the device when the Programmer Object File (.pof). In dynamic mode, you can override

the static values at runtime with a scan chain. You can reconfigure the I/Os by turning on the Use

dynamic configuration scan chains option.

The following figure shows the Use dynamic configuration scan chains option.

Figure 16: Use Dynamic Configuration Scan Chains Option

The following figure shows the dynamic reconfiguration scan chain implementation.

Altera Corporation

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 39

din

update

enable

clk

DQ0

din

update

enable

clk

DQ1

din

update

enable

clk

DQS

config_data

config_update

config_clock_in

config_io_ena[0] config_io_ena[1] config_dqs_ena

UG-01089

2014.12.17

Dynamic Reconfiguration for ALTDQ_DQS2

Figure 17: Reconfiguration Scan Chain

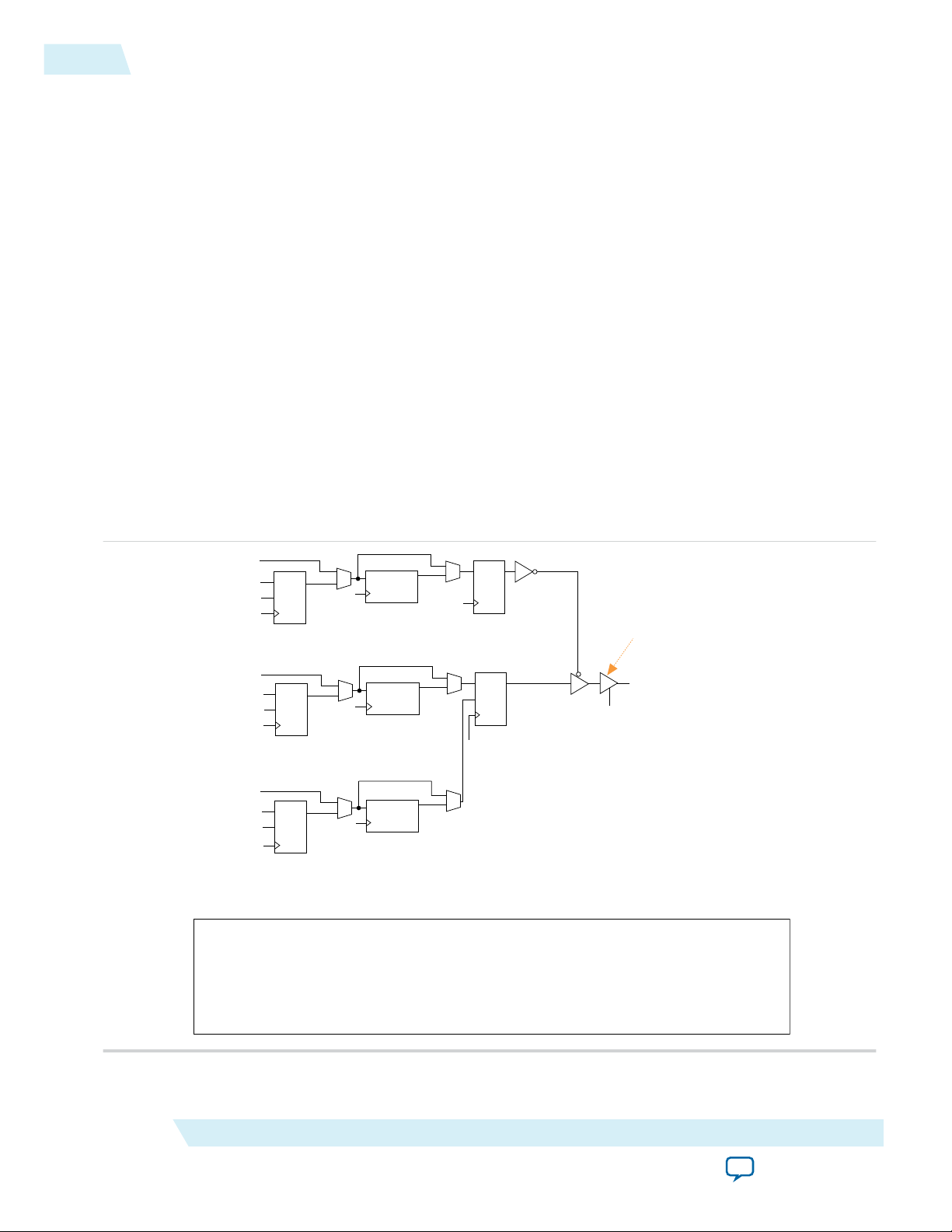

Each I/O contains a scan chain block. The DQS logic also contains its own scan chain block. You can use

I/O scan chain blocks to configure DQ and DQS I/O configuration registers (for example, delay chain)

and you can use the DQS logic scan chain to configure DQS logic configuration (for example, DQS

postamble phase). You can serially scan configuration bits into each scan chain block with the following

operating sequence:

39

The ALTDQ_DQS2 dynamic configuration interface is made of four input ports:

• config_clock_in—This is the clock signal. All other input signals must be treated as synchronous to

this clock. The typical frequency is 25 MHz.

• config_data—This is the 1-bit serial input through which data is scanned into the calibration blocks.

This is common to all configuration blocks, but it will only be scanned into calibrations blocks whose

enable input is asserted. Configuration data must be input in LSB first ordering. For example, the

Stratix V I/O configuration block data must start with padtoinputregisterdelaysetting[0].

• config_enable—In a generic ALTDQ_DQS2 IP core, the following three config_enable inputs are

available:

• config_io_ena[]—Controls the enable input on the DQ I/Os

• config_dqs_io_ena[]—Controls the enable input on the DQS I/Os

• config_dqs_ena[]—Controls the enable input on the DQS logic

Note:

Each of these inputs is wide to control all the scan chain blocks instantiated in the

ALTDQ_DQS2 IP core. In a general application, you must assert only one enable input at a

time to scan the desired data in the corresponding scan chain block. The enable input must be

held high for the entire duration of the scanning process. All other inputs must be held at 0.

Note: You must deassert the config_enable signal after the last bit of config_data to prevent

further data from scanning in. Then, assert the update signal whenever you are ready to copy

the scanned in data to the configuration registers.

• config_update—After scanning all the bits into the desired scan chain blocks, copy them into the

configuration register by asserting the config_update signal for one clock cycle.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Altera Corporation

Page 40

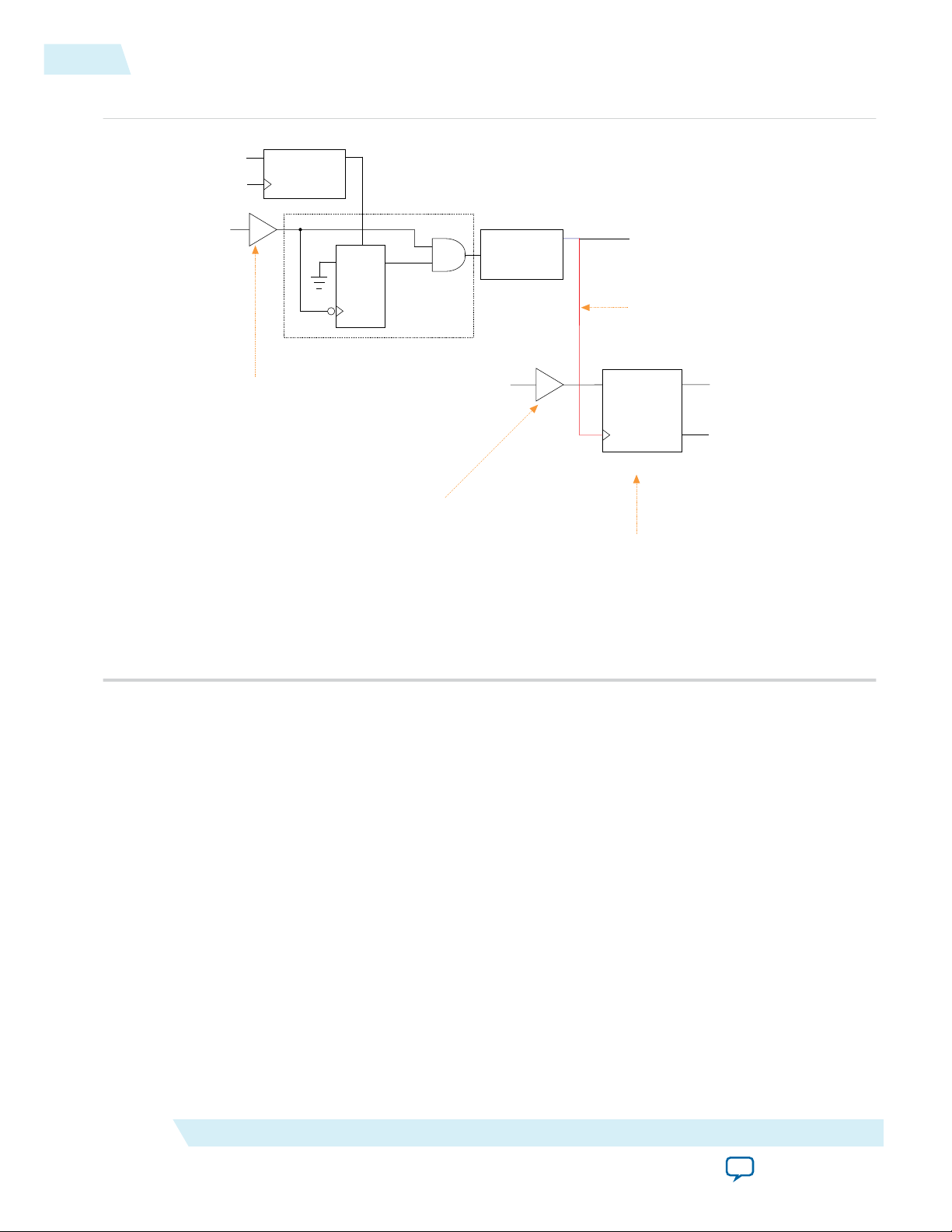

1

0

DQ

D1

Delay

Chain

D1

Delay

Chain

AB

Positive Edge

Read Data

Negative Edge

Read Data

D4

Delay

Chain

D4

Delay

Chain

EF

DQS

Delay

Chain

T

DQS

T11

Delay

Chain

T11

Delay

Chain

R

To dqsenable

Port

To dqsdisablen

Port

DQS

Enable

Control

Q

S

From

dqsenableout

Port

Clock Phase

Select

Clock Phase

Select (0 Degree)

To

levelingclk

Port

To

zerophaseclk

Port

M N

X V

Output

Alignment

Clock Phase

Select (0 Degree)

Output

Alignment

W U

Output

Alignment

Output

Alignment

Negative Edge

Write Data

Positive Edge

Write Data

W U

Output

Alignment

1

0

Negative Edge

Write Data

Positive Edge

Write Data

X V

Output

Alignment

Output Enable

Signal

Clock Phase

Select

Clock Phase

Select (0 Degree)

I J

Leveling

Delay

Chain

Clock Signal

from Core

Clock Phase

Select

K L

Output Enable

Signal

O P

Output

Alignment

OCT Control

Signal

DQ

D5

Delay

Chain

D5

Delay

Chain

D6 OCT

Delay

Chain

D6 OE

Delay

Chain

D5 OCT

Delay

Chain

D5 OE

Delay

Chain

DQS

D5

Delay

Chain

D5

Delay

Chain

D5 OCT

Delay

Chain

D5 OE

Delay

Chain

D6 OCT

Delay

Chain

D6 OE

Delay

Chain

C

D

G

H

D2

Delay

Chain

D3

Delay

Chain

-

D6

Delay

Chain

D6

Delay

Chain

D5 OCT

Delay

Chain

D5 OE

Delay

Chain

D5 OCT

Delay

Chain

D5 OE

Delay

Chain

Use the combination of D1, D2, D3, and D4 delay chains for calibration. Use D1, D2, and D3 to delay

DQ, and D4 delay chain to delay DQS. D5 and D6 delay chains are the output delay chains.

The D2 and D3 delay chains are static input delay chains. The D6 delay chain is static output delay

chain. You can only set the settings in the Q uartus II Settings File (.qsf) or the Fitter sets the settings

automatically based on the timing constraints. You cannot dynamically set the settings.

40

I/O Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

I/O Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

Figure 18: I/O and DQS Delay Chains for Arria V GZ and Stratix V Devices

UG-01089

2014.12.17

The following tables lists the I/O configuration block bit sequence, description, and settings for Arria V

GZ and Stratix V devices.

Table 12: I/O Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

Bit

Legend

in

Figure

18

A 5..0 padtoinputregisterdelaysetting Connects to the delayctrlin port of

Altera Corporation

Bit Name Description

the D1 delay chain to control the first I/

O buffer-to-input register delay chain

(D1).

Sets to tune the DQ delay (read calibra‐

tion) for DDR applications.

For delay values, refer to the “Program‐

mable IOE Delay” section in the Stratix

V Device Datasheet.

ALTDQ_DQS2 IP Core User Guide

Send Feedback

Page 41

UG-01089

2014.12.17

I/O Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

41

Legend

in

Figure

18

Bit

Bit Name Description

B 11..6 padtoinputregisterrisefalldelaysetting Connects to the delayctrlin port of

the second D1 delay chain to control the

second pad-to-input register delay chain

(D1).

For delay values, refer to the “Program‐

mable IOE Delay” section in the Stratix

V Device Datasheet.