Acer TravelMate 292 Schematics Rev0.3

5

4

3

2

1

COMPAL CONFIDENTIAL

COVER SHEET

MODEL NAME :

D D

COMPAL P/N :

PCB NO :

Revision :

DATE :

DA8CL56L100

2.0

2004/03/02

History :

(1) 12/05 : Modify ATI trapping value page 03

(2) 12/06 : VRAM Channel A&B swap page 08 & 09

(3) 12/08 : ADD R82 for SPWG function verify page11

(4) 12/10 : (a) ADD R83 R84 to detect Graphic chip type page 10

C C

(5) 12/11 : ADD R85 R86 pull down for ATI suggest page 4,5

(6) 12/12 : ADD power play function page 12

(7) 01/30 : ADD L13 L14 L15 & L5 from 0603 to 0805 page 10

(8) 01/30 : ADD C128 page 11

(9) 03/02 : Change C21,C72,C96 to 100U page 06,08,09

(b) Change JP4 connecter to Match LS-2201 T/P Board page 10

DCL56 VGA/B

LS-2231

DCL56 Schematics Document

ATI Mobility Radeon M10/M11P Graphics Controller

B B

A A

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SE CRET INFO RMATI ON. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

2

Size Document Number Rev

A3

Date: Sheet

COVER SHEET

DCL56 VGA/B LS-2231

1

2.0

112Thursday, March 04, 2004

of

5

4

3

2

1

BLOCK DIAGRAM

ATI MOBILITY RADEON M10-P

D D

ATI M10-P

LVDS

AGP CONN.

AGP, DAC & LVDS

AGP,

PAGE 10

RGB,

TMDS

C C

INTERFACE

ATI M10-P

PAGE 3

POWER REGULATOR

K/B CONN.

POWER INTERFACE

PAGE 10

T/B FPC CONN.

PAGE 6,7

ATI M10-P

PAGE 10

B B

MEMORY INTERFACE

PAGE 4,5

LCD CONN.

PAGE 11

+1.2V and +2.5V

PAGE 12

POWER CONN.

PAGE 10

CHANNEL A,B

4M32x4

64MB DDR SDRAM

A A

5

4

(BGA144)

PAGE 8,9

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SE CRET INFO RMATI ON. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

3

2

Compal Electronics, Inc.

Title

Size Document Number Rev

A3

Date: Sheet

BLOCK DIAGRAM

DCL56 VGA/B LS-2231

1

2

12Tuesday, March 02, 2004

of

2.0

5

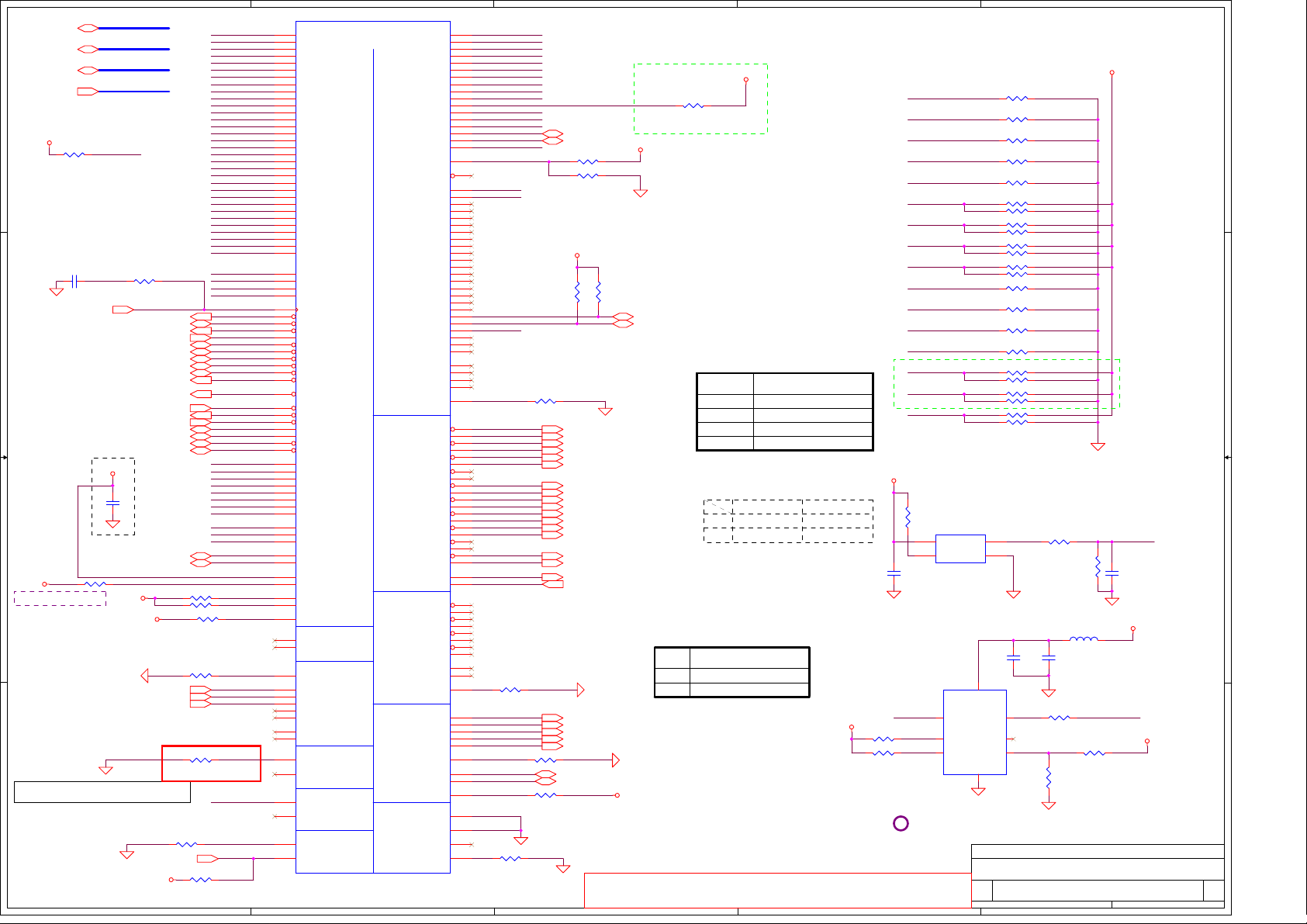

AGP_AD[0..31]<10>

AGP_SBA[0..7]<10>

AGP_C/BE#[0..3]<10>

AGP_ST[0..2]<10>

D D

+3VS

1 2

R26 10K_0402_5%

C1 @10P_0402_50V8K

CLK_AGP_66M<10>

C C

Source form MCH (+0.75V)

B B

+1.5VS

If M10+P POP 47_0603_1%

If M9+P POP 137_0603_1%

Leave SSIN & SSOUT No Connect, When

Using M10-P Internal Spread Spectrum

A A

AGP_AD[0..31]

AGP_SBA[0..7]

AGP_C/BE#[0..3]

AGP_ST[0..2]

AGP_STP#

1 2

12

R18 @10_0402_5%

+AGPREF

1

C2

0.1U_0402_16V4Z

2

(Closed to M26)

(15mil)

1 2

R32 47_0603_1%

+1.5VS

5

B_PCIRST#<10,11>

AGP_REQ#<10>

AGP_GNT#<10>

AGP_PAR<10>

AGP_STOP#<10>

AGP_DEVSEL#<10>

AGP_TRDY#<10>

AGP_IRDY#<10>

AGP_FRAME#<10>

PCI_PIRQA#<10>

AGP_WBF#<10>

C3_STAT#<10>

AGP_BUSY#<10>

AGP_RBF#<10>

AGP_ADSTB0<10>

AGP_ADSTB1<10>

AGP_ADSTB0#<10>

AGP_ADSTB1#<10>

AGP_SBSTB<10>

AGP_SBSTB#<10>

R33 1K_0402_5%

1 2

R34 1K_0402_5%

1 2

1 2

+3VS

AGP8X_DET#

High: AGP2.0

R35 10K_0402_5%

(15mil)

R36 715_0603_1%

CRMA<10>

LUMA<10>

COMPS<10>

R44 @4.7K_0402_5%

R48 1K_0402_5%

+3VS

SUS_STAT#<10>

1 2

R50 10K_0402_5%

12

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

CLK_AGP_66M

B_PCIRST#

AGP_REQ#

AGP_GNT#

AGP_PAR

AGP_STOP#

AGP_DEVSEL#

AGP_TRDY#

AGP_IRDY#

AGP_FRAME#

AGP_STP#

AGP_BUSY#

AGP_RBF#

AGP_ADSTB0

AGP_ADSTB1

AGP_ADSTB0#

AGP_ADSTB1#

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

AGP_SBSTB

AGP_SBSTB#

(25mil)

DAC2_RSET

12

CRMA

LUMA

COMPS

SSIN

12

XTALIN

U1A

H29

AD0

H28

AD1

J29

AD2

J28

AD3

K29

AD4

K28

AD5

L29

AD6

L28

AD7

N28

AD8

P29

AD9

P28

AD10

R29

AD11

R28

AD12

T29

AD13

T28

AD14

U29

AD15

N25

AD16

R26

AD17

P25

AD18

R27

AD19

R25

AD20

T25

AD21

T26

AD22

U25

AD23

V27

AD24

W26

AD25

W25

AD26

Y26

AD27

Y25

AD28

AA26

AD29

AA25

AD30

AA27

AD31

N29

C/BE#0

U28

C/BE#1

P26

C/BE#2

U26

C/BE#3

AG30

PCICLK

AG28

RST#

AF28

REQ#

AD26

GNT#

M25

PAR

N26

STOP#

V29

DEVSEL#

V28

TRDY#

W29

IRDY#

W28

FRAME#

AE26

INTA#

AC26

WBF#

AH30

STP_AGP#

AH29

AGP_BUSY#

AE29

RBF#

M28

AD_STBF_0

V25

AD_STBF_1

M29

AD_STBS_0

V26

AD_STBS_1

AD28

SBA0

AD29

SBA1

AC28

SBA2

AC29

SBA3

AA28

SBA4

AA29

SBA5

Y28

SBA6

Y29

SBA7

AF29

ST0

AD27

ST1

AE28

ST2

AB29

SB_STBF

AB28

SB_STBS

M26

AGPREF

M27

AGPTEST

AB25

DBI_HI

AB26

DBI_LO

AC25

AGP8X_DET#

AE11

DMINUS

AF11

DPLUS

AK21

R2SET

AJ23

C_R

AJ22

Y_G

AK22

COMP_B

AJ24

H2SYNC

AK24

V2SYNC

AG23

DDC3CLK

AG24

DDC3DATA

AK25

SSIN

AJ25

SSOUT

AH28

XTALIN

AJ29

XTALOUT

AH27

TESTEN

AG26

SUS_STAT#

SA002160E00(0301021300)

4

M10-P/(M9+X)

(1/6)

ZV_LCDDATA0

ZV_LCDDATA1

ZV_LCDDATA2

ZV_LCDDATA3

ZV_LCDDATA4

ZV_LCDDATA5

ZV_LCDDATA6

ZV_LCDDATA7

ZV_LCDDATA8

ZV_LCDDATA9

ZV_LCDDATA10

ZV_LCDDATA11

ZV_LCDDATA12

ZV_LCDDATA13

ZV_LCDDATA14

ZV_LCDDATA15

ZV PORT / EXT TMDS / GPIO / ROMLVDSTMDSDA C1

ZV_LCDDATA16

ZV_LCDDATA17

ZV_LCDDATA18

ZV_LCDDATA19

ZV_LCDDATA20

ZV_LCDDATA21

ZV_LCDDATA22

ZV_LCDDATA23

ZV_LCDCNTL0

ZV_LCDCNTL1

ZV_LCDCNTL2

ZV_LCDCNTL3

PCI/AGPAGP8XCLK

BLON/(BLON#)

THRM

SSC DAC2

TEST_MCLK/(NC)

TEST_YCLK/(NC)

PLLTEST/(NC)

RSTB_MSK/(NC)

4

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

VREFG/(NC)

ROMCS#

DVOMODE

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

TXCLK_LN

TXCLK_LP

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXCLK_UN

TXCLK_UP

DIGON

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TXCM

TXCP

DDC2CLK

DDC2DATA

HPD1

HSYNC

VSYNC

RSET

DDC1DATA

DDC1CLK

AUXWIN

AJ5

AH5

AJ4

AK4

AH4

AF4

AJ3

AK3

AH3

AJ2

AH2

AH1

AG3

AG1

AG2

AF3

AF2

AG4

AF5

AH6

AJ6

AK6

AH7

AK7

AJ7

AH8

AJ8

AH9

AJ9

AK9

AH10

AE6

AG6

AF6

AE7

AF7

AE8

AG8

AF8

AE9

AF9

AG10

AF10

AJ10

AK10

AJ11

AH11

AE10

AK16

AH16

AH17

AJ16

AH18

AJ17

AK19

AH19

AK18

AJ18

AG16

AF16

AG17

AF17

AF18

AE18

AH20

AG20

AF19

AG19

AE12

AG12

AJ13

AH14

AJ14

AH15

AJ15

AK15

AH13

AK13

AE13

AE14

AF12

AK27

R

AJ27

G

AJ26

B

AG25

AH25

AH26

AF25

AF24

AF26

B6

E8

AE25

AG29

STRAP_G

STRAP_H

STRAP_J

STRAP_K

STRAP_D

STRAP_E

STRAP_F

STRAP_B

STRAP_A

STRAP_O

GPIO10

STRAP_L

STRAP_M

STRAP_N

M_SEN#

POWER_SEL

MCLK_SPREAD

VREFG

(25 mil)

STRAP_R

STRAP_S

R40

4.7K_0402_5%

LCD_DATA

LCD_CLK

STRAP_T

DVOMODE

1 2

R25 0_0402_5%

TXOUT0TXOUT0+

TXOUT1TXOUT1+

TXOUT2TXOUT2+

TXCLKTXCLK+

TZOUT0TZOUT0+

TZOUT1TZOUT1+

TZOUT2TZOUT2+

TZCLKTZCLK+

ENVDD

1 2

R37 100K_0402_5%

R

G

B

HSYNC

VSYNC

(15mil)

AGP_RSET

DDC_DATA

DDC_CLK

1 2

R49

1 2

R45 499_0603_1%

DDC_DATA <10>

DDC_CLK <10>

1 2

R47 10K_0402_5%

1K_0402_5%

3

Memory Config.

GPIO10=Hinh, 128MB

GPIO10=Low, 64MB

2

AGP, DAC & LVDS INTERFACE

+3VS

GPIO8

GPIO7

GPIO4

GPIO5

GPIO6

GPIO0

M_SEN# <10>

POWER_SEL <12>

R4 1K_0603_1%

1 2

1 2

R7 1K_0603_1%

+3VS

R1 @10K_0402_5%

1 2

Modify (12/05)

GPIO1

GPIO2

+3VS

12

12

R38

4.7K_0402_5%

LCD_DATA <11>

LCD_CLK <11>

GPIO3

GPIO9

GPIO11

GPIO12

GPIO13

Vedio Memory Config.

Size Vendor

4Mx32 Samsung

4Mx32 Hynix

8Mx32 Samsung

8Mx32 Hynix

180_0603_5%

150_0402_5%

+3VS

M10-PM9+X

150_0402_5%

1

2

TXOUT0- <11>

TXOUT0+ <11>

TXOUT1- <11>

TXOUT1+ <11>

TXOUT2- <11>

TXOUT2+ <11>

TXCLK- <11>

TXCLK+ <11>

TZOUT0- <11>

TZOUT0+ <11>

TZOUT1- <11>

TZOUT1+ <11>

TZOUT2- <11>

TZOUT2+ <11>

TZCLK- <11>

TZCLK+ <11>

ENVDD <11>

ENBKL <10,11>

R S

0 0

*

0 1

1 0

1 1

Ra 261_0603_1%

Rb

For VGA DDR spread sprum

R<10>

G<10>

B<10>

HSYNC <10>

VSYNC <10>

Selection Table For W180

+3VS

SS%

0

1

Spread % Setting for

Freq. Range

Fin>Fout>Fin-1.25%

Fin>Fout>Fin-3.75%

+3VS

1 2

R41 10K_0402_5%

1 2

R42 10K_0402_5%

L

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

1

+3VS

ID_Disable

STRAP_A

VGA_Disable

STRAP_B

STRAP_D

STRAP_E

STRAP_F

STRAP_G

STRAP_H

STRAP_J

STRAP_K

STRAP_O

STRAP_L

STRAP_M

STRAP_N

STRAP_R

STRAP_S

STRAP_T

R2 @10K_0402_5%

R3 @10K_0402_5%

R5 @10K_0402_5%

R6 @10K_0402_5%

R8 @10K_0402_5%

R9 10K_0402_5%

R10 @10K_0402_5%

R11 10K_0402_5%

R12 @10K_0402_5%

R14 @10K_0402_5%

R15 @10K_0402_5%

R16 @10K_0402_5%

R17 @10K_0402_5%

R19 @10K_0402_5%

R20 @10K_0402_5%

R21 @10K_0402_5%

R22 @10K_0402_5%

R23 @10K_0402_5%

R13 10K_0402_5%

R24 @10K_0402_5%

R81 10K_0402_5%

R27 @10K_0402_5%

R28 @10K_0402_5%

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

Modify (12/05)

Divider Circuit for 1.2V/(1.5)dc XTALIN from 3.3Vdc OSC out

12

R29

10K_0402_5%

X1

4

VDD

1

OE

27MHZ_15P

C3

0.1U_0402_16V4Z

U2

1

X1/CLK

7

FS1

8

FS2

3.3V OSC out for W18 0

FREQOUT

3

OUT

GND

6

VDD

CLKOUT

GND

W180-01GT_SO8

3

2

1

C126

2

0.1U_0402_16V4Z

5

2

X2

4

SS%

SS%

R30 261_0603_1%

R39

Ra

1 2

R31

150_0402_5%

Rb

L12

1 2

1

FCM2012C-800_0805

C127

2

2.2U_0603_6.3V4Z

1 2

22_0402_5%

1 2

R43 @10K_0402_5%

12

R46

10K_0402_5%

1.5V OSC out for M9+X

1.2V OSC out for

M10-P

XTALIN

12

C4

@15P_0402_50V8J

+3VS

MCLK_SPREADFREQOUT

+3VS

Note: PLACE CLOSE TO U6 (VGA M9+X/M10-P)

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

ATI M10-P & M9+X (AGP BUS)

DCL56 VGA/B LS-2231

1

312Tuesday, March 02, 2004

2.0

of

5

4

3

2

1

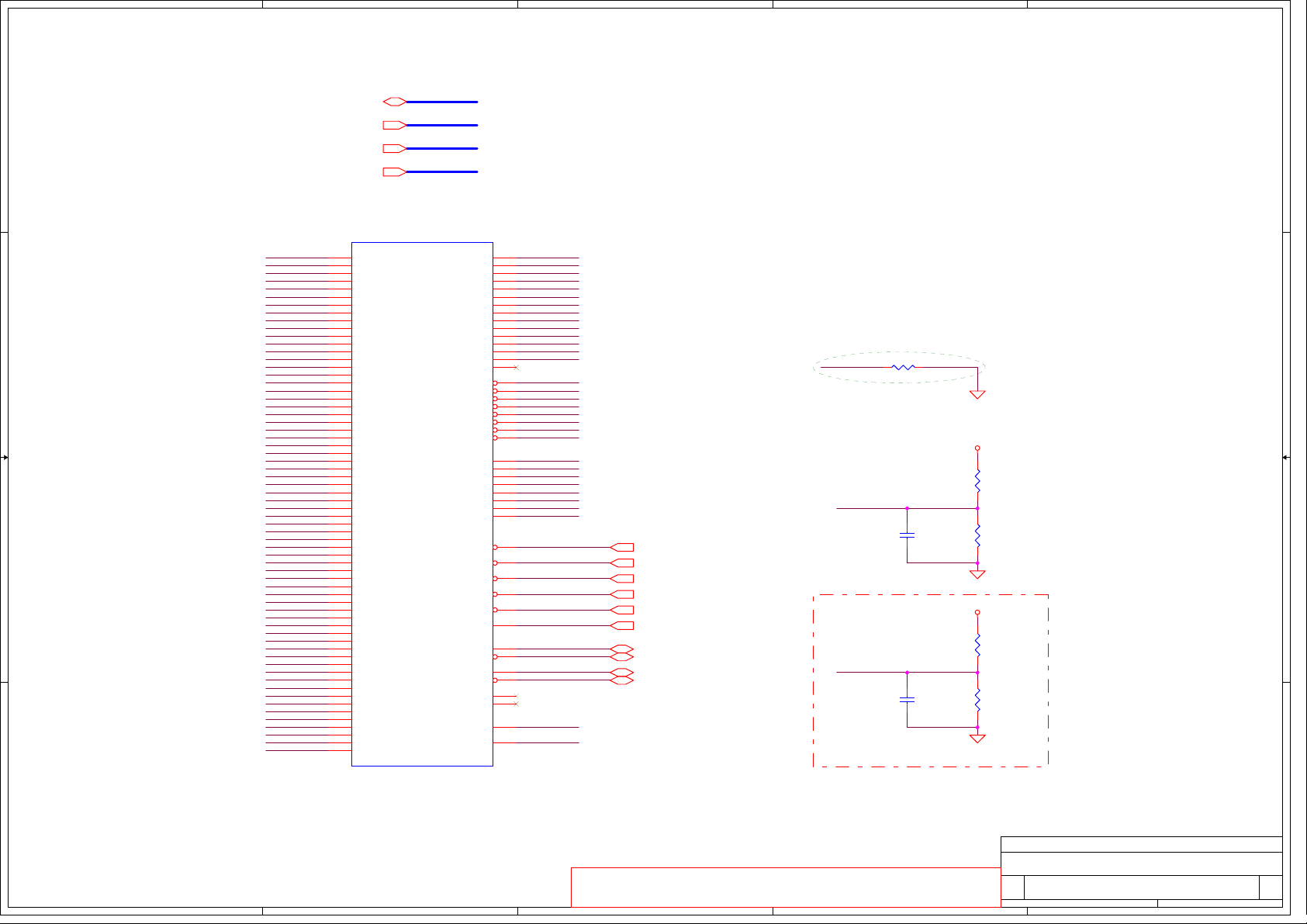

MEMORY INTERFACE A

NMDA[0..63]<8>

D D

NMDA0

NMDA1

NMDA2

NMDA3

NMDA4

NMDA5

NMDA6

NMDA7

NMDA8

NMDA9

NMDA10

C C

B B

NMDA11

NMDA12

NMDA13

NMDA14

NMDA15

NMDA16

NMDA17

NMDA18

NMDA19

NMDA20

NMDA21

NMDA22

NMDA23

NMDA24

NMDA25

NMDA26

NMDA27

NMDA28

NMDA29

NMDA30

NMDA31

NMDA32

NMDA33

NMDA34

NMDA35

NMDA36

NMDA37

NMDA38

NMDA39

NMDA40

NMDA41

NMDA42

NMDA43

NMDA44

NMDA45

NMDA46

NMDA47

NMDA48

NMDA49

NMDA50

NMDA51

NMDA52

NMDA53

NMDA54

NMDA55

NMDA56

NMDA57

NMDA58

NMDA59

NMDA60

NMDA61

NMDA62

NMDA63

NMAA[0..13]<8>

NDQMA[0..7]<8>

NDQSA[0..7]<8>

U1B

L25

DQA0

L26

DQA1

K25

DQA2

K26

DQA3

J26

DQA4

H25

DQA5

H26

DQA6

G26

DQA7

G30

DQA8

D29

DQA9

D28

DQA10

E28

DQA11

E29

DQA12

G29

DQA13

G28

DQA14

F28

DQA15

G25

DQA16

F26

DQA17

E26

DQA18

F25

DQA19

E24

DQA20

F23

DQA21

E23

DQA22

D22

DQA23

B29

DQA24

C29

DQA25

C25

DQA26

C27

DQA27

B28

DQA28

B25

DQA29

C26

DQA30

B26

DQA31

F17

DQA32

E17

DQA33

D16

DQA34

F16

DQA35

E15

DQA36

F14

DQA37

E14

DQA38

F13

DQA39

C17

DQA40

B18

DQA41

B17

DQA42

B15

DQA43

C13

DQA44

B14

DQA45

C14

DQA46

C16

DQA47

A13

DQA48

A12

DQA49

C12

DQA50

B12

DQA51

C10

DQA52

C9

DQA53

B9

DQA54

B10

DQA55

E13

DQA56

E12

DQA57

E10

DQA58

F12

DQA59

F11

DQA60

E9

DQA61

F9

DQA62

F8

DQA63

SA002160E00(0301021300)

NMDA[0..63]

NMAA[0..13]

NDQMA[0..7]

NDQSA[0..7]

M10-P/(M9+X)

(2/6)

AA12/(AA13)

AA13/(AA12)

AA14/(NC)

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

MEMORY INTERFACE

A

MVREFD

MVREFS/(NC)

AA0

AA1

AA2

AA3

AA4

AA5

AA6

AA7

AA8

AA9

AA10

AA11

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

RASA#

CASA#

WEA#

CSA0#

CSA1#

CKEA

CLKA0

CLKA0#

CLKA1

CLKA1#

DIMA0

DIMA1

E22

B22

B23

B24

C23

C22

F22

F21

C21

A24

C24

A25

E21

B20

C19

J25

F29

E25

A27

F15

C15

C11

E11

J27

F30

F24

B27

E16

B16

B11

F10

A19

E18

E19

E20

F20

B19

B21

C20

C18

A18

D30

B13

B7

B8

NMAA0

NMAA1

NMAA2

NMAA3

NMAA4

NMAA5

NMAA6

NMAA7

NMAA8

NMAA9

NMAA10

NMAA11

NMAA12

NMAA13

NDQMA0

NDQMA1

NDQMA2

NDQMA3

NDQMA4

NDQMA5

NDQMA6

NDQMA7

NDQSA0

NDQSA1

NDQSA2

NDQSA3

NDQSA4

NDQSA5

NDQSA6

NDQSA7

MVREFD

MVREFS

NMRASA#

NMCASA#

NMWEA#

NMCSA0#

NMCSA1#

NMCKEA

NMCLKA0

NMCLKA0#

NMCLKA1

NMCLKA1#

NMRASA# <8>

NMCASA# <8>

NMWEA# <8>

NMCSA0# <8>

NMCSA1# <8>

NMCKEA <8>

NMCLKA0 <8>

NMCLKA0# <8>

NMCLKA1 <8>

NMCLKA1# <8>

NMCKEA

R85 10K_0402_5%

Modify (12/11)

MVREFD

C5

0.1U_0402_16V4Z

MVREFS

C6

0.1U_0402_16V4Z

1

2

1

2

12

(25 mil)

(25 mil)

+2.5VS

12

R51

1K_0603_1%

12

R52

1K_0603_1%

+2.5VS

12

R53

1K_0603_1%

12

R54

1K_0603_1%

A A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

ATI M10-P/M9+X DDR-A

DCL56 VGA/B LS-2231

1

2.0

of

412Tuesday, March 02, 2004

Loading...

Loading...