Acer CHROMEBOOK 13 Schematics

A

ompal Confidential

C

M

odel Name : Z3ENN

File Name : LA-B551PR10

OM P/N : 4319TUBOL01~10

B

1

2

AX

AX

D

D

DA@

DA@

P

P

CB

CB

DAZ17600100

DAZ17600100

P

P

CB Z3ENN LA-B551P LS-B551P

CB Z3ENN LA-B551P LS-B551P

B

C

D

Compal Confidential

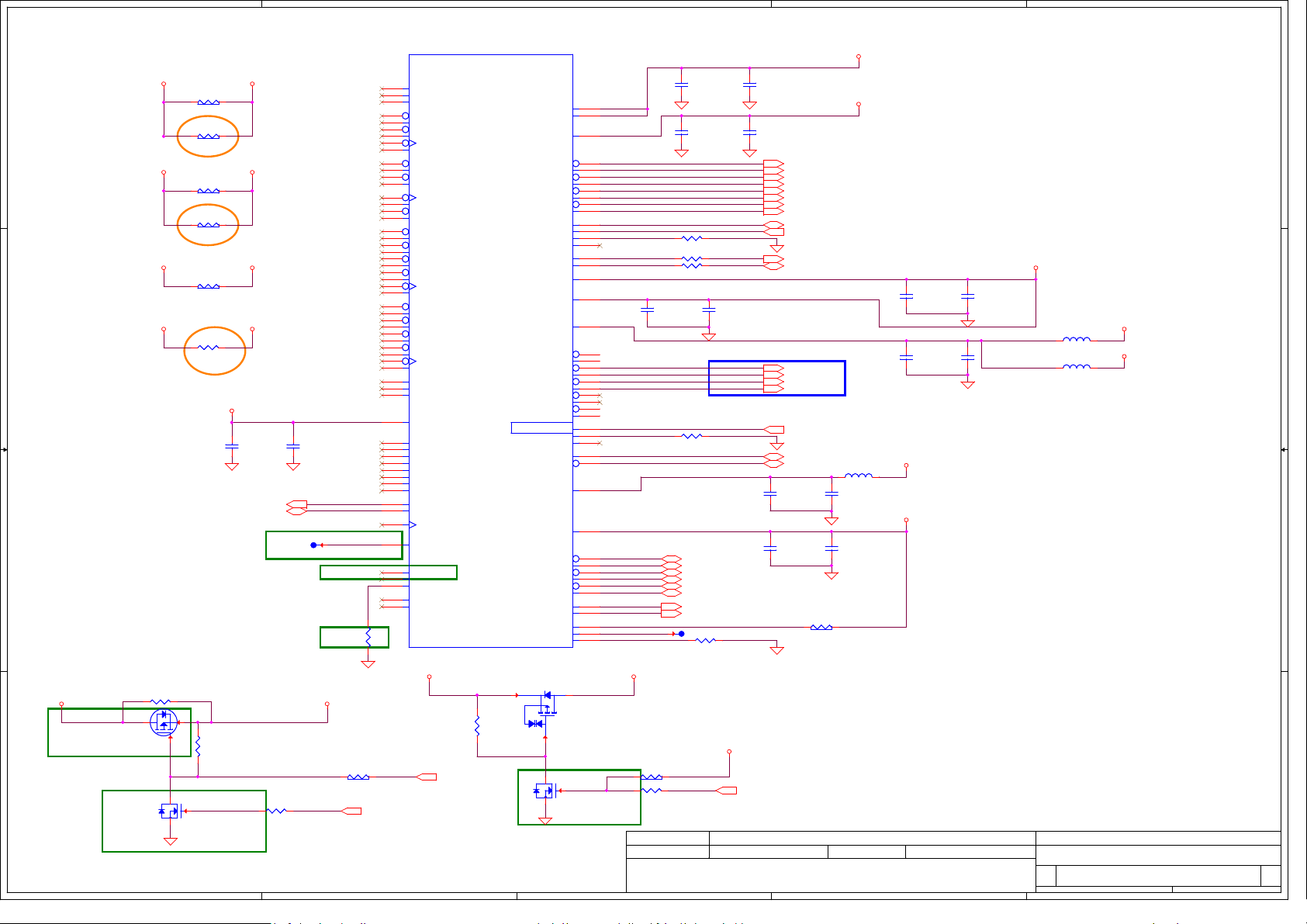

NIKE MB LA-B551P

E

1

2

Nvidia LOGAN Processor

2014-05-28

3

3

REV: 1.0

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2013/11/20 2014/11/09

2013/11/20 2014/11/09

2013/11/20 2014/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

E

of

1 42Thursday, June 19, 2014

of

1 42Thursday, June 19, 2014

of

1 42Thursday, June 19, 2014

4

1.0

1.0

1.0

A

ompal Confidential

C

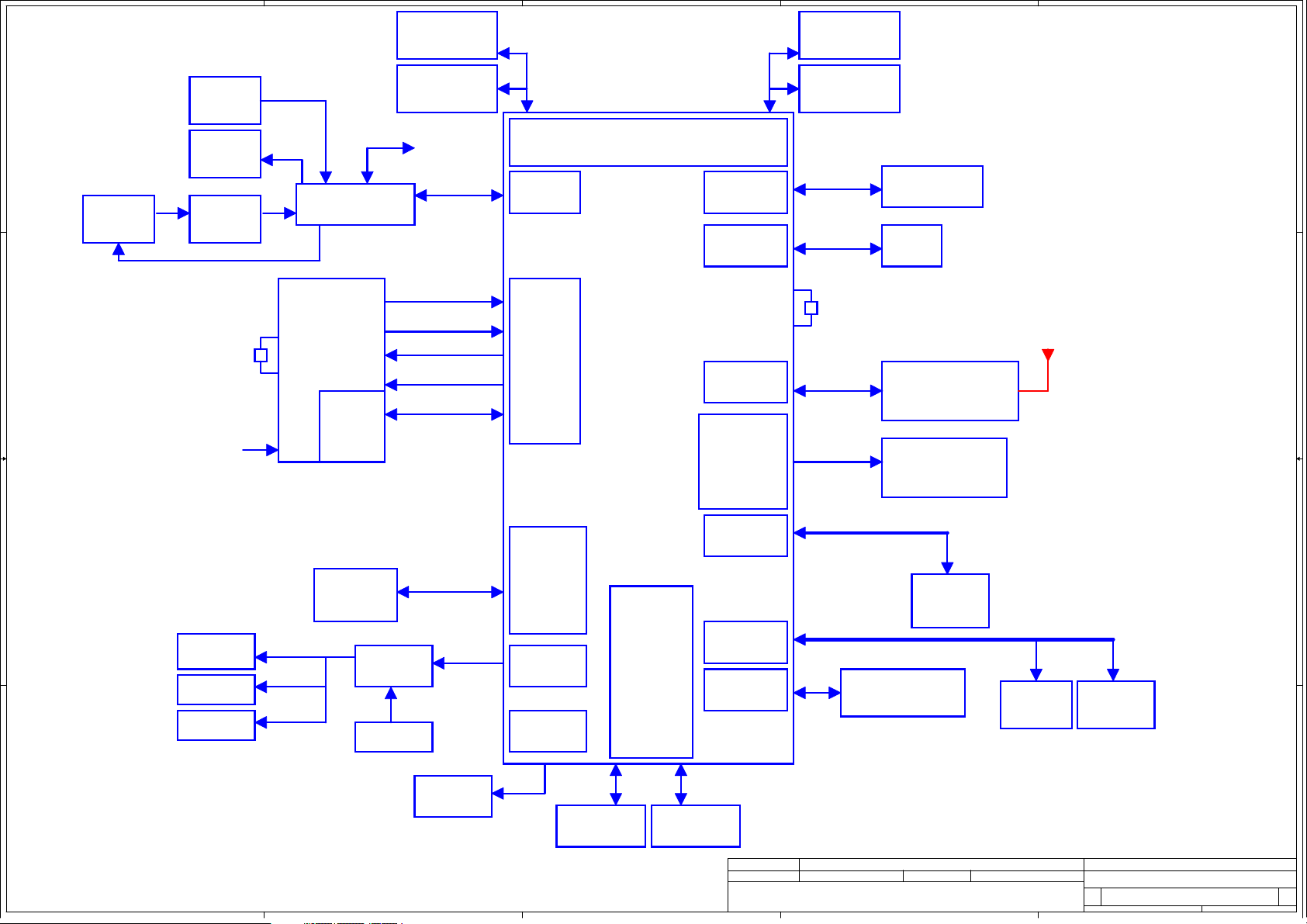

odel Name : LOGAN Block Diagram

M

D

MIC * 1

1

S

peaker * 2

(2W)

Audio JACK

HP + MIC

P.23

2

HEADSET SW

TS3A225E

PWR_ON

P.23

P.23

P.23

B

DDR3L

256/512Mb*16

D

DR3L

256/512Mb*16

P

.04

C

DDR3L Bus

D

DDR3L

256/512Mb*16

P.05

DDR3L

256/512Mb*16

E

P.04 P.05

1

Audio Codec

MAX9809X

P.22

G

EN1_I2C

CH0 DDR CH1

VDDIO_DDR

(1.35V)

DAP2

VDDIO_AUDIO

(1.8V)

SDMMC4

VDDIO_SDMMC4

(1.8V)

SDMMC3

VDDIO_SDMMC3

(1.8V & 3.3V)

8 bits

eMMC 16G/32G

P.25

SD Card4 bits

P.27

PMU_32K_IN

PMIC

AS3722

32KHz

AS3728

SYS_RESET#

CORE_PWR_REQ

CPU_PWR_REQ

PWR_I2C

VDDIO_SYS

(1.8V)

Nvidia

Logan

SDMMC1

VDDIO_SDMMC1

(1.8V)

LVDS/DP

AVDD_LVDS0_IO

(1.05V)

AVDD_PLL_UD2DPD

(1.05V)

AVDD_LVDS0_PLL

12MHz

BT/WLAN Antenna

WIFI/BT

AW-CM389NF

FOXCONN T77H526.01

P.20

13.3" LCD Panel

1366*768

eDP I/F

P.14

2

GEN1_I2C

HDMI

3

HDMI CONN.

HDMI & DDC

P.16

Charger

BQ24735

BATT CONN.

P.31

CHARGER_I2C

EC

STM32L100

P.29

AVDD_HDMI

(3.3V)

AVDD_HDMI_PLL

(1.05V)

SPI

VDDIO_BB

(1.8V)

USB2.0

AVDD_USB

(3.3V)

USB3.0

P.31

THEM Sensor

G781

P.29

LID SW IC

P.24

SPI ROM

4

W25Q32DW

P.18

SPI

VDDIO_GMI

(1.8V)

USB3.0

USB3.0 * 2 Port

Camera Module

VDDIO_UART

(1.8V)

GEN2_I2C

VDDIO_HV

(3.3V)

CAM_I2C

VDDIO_CAM

(1.8V)

USB2.0

THEM Sensor

TMP451

TPM

SLB9645TT1.2

(FW:133.32Goog)

P.21

P.21

P.27

3

Touch ScreenTouch PAD

Design reserve

P.28

4

www.schematic-x.blogspot.com

P.17 P.14

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

A

B

C

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

2013/11/20 2014/11/09

2013/11/20 2014/11/09

2013/11/20 2014/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

SYSTEM BLOCK

SYSTEM BLOCK

SYSTEM BLOCK

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

E

of

2 42Thursday, June 1 9, 2014

of

2 42Thursday, June 1 9, 2014

of

2 42Thursday, June 1 9, 2014

0.1

0.1

0.1

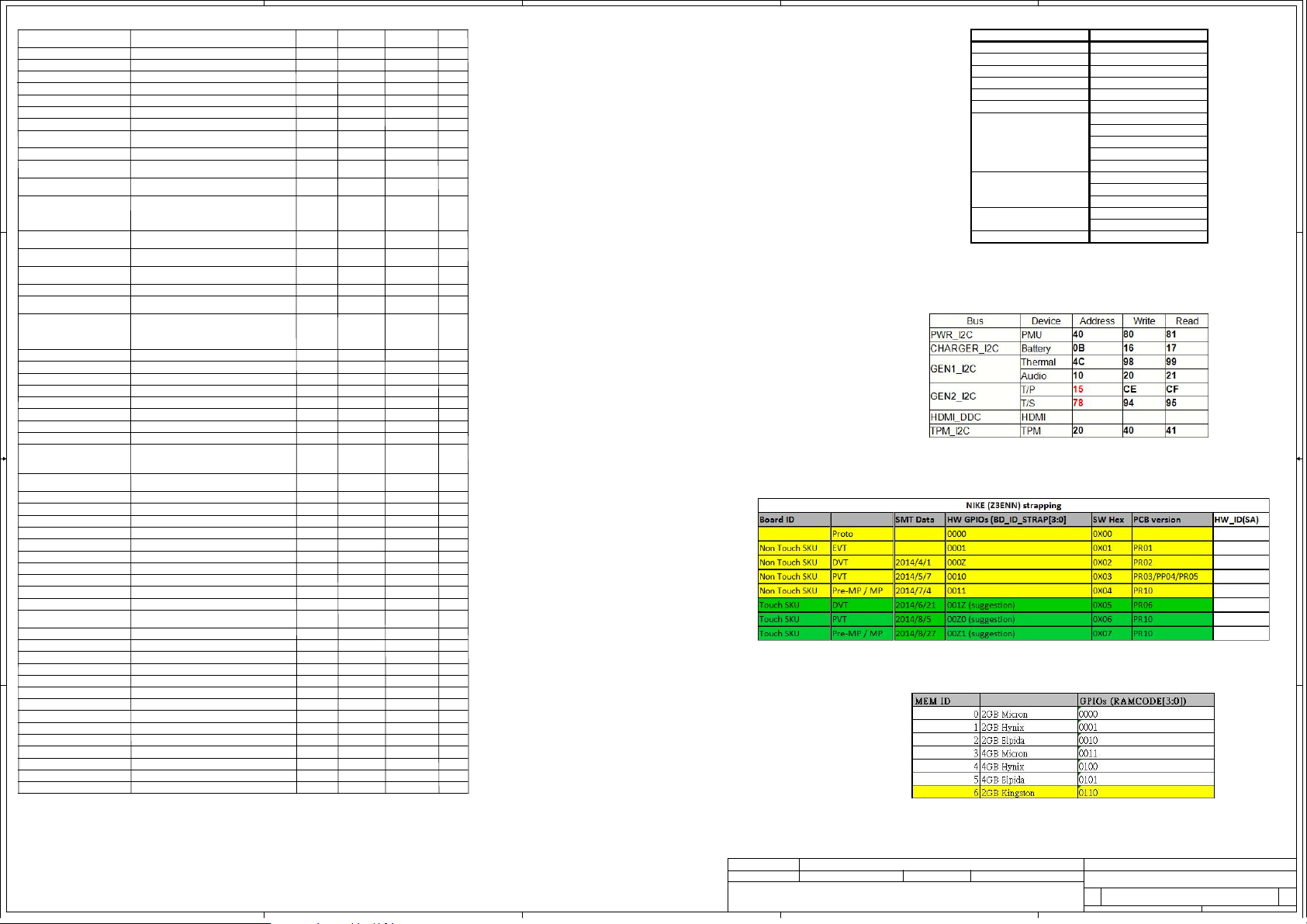

A

V

oltage Rails

Power Plane Description

VIN

BATT+ Battery power supply

B+

VDD_5V0_SYS For All Device standby mode

VDD_3V3_SYS For All Device standby mode

VDD_1V8_PMU

1

V_RTC_1V8

+VDD_1V35_MEM

VDD_0V675_DDR3_VREF For DDR VREFDQ & VREF CA

VDD_1V2_CORE_AP

VDD_1V0_CPU For TEGRA CPU VDD

VDD_1V05_PLL_AP

VDD_1V8_PMU For TEGRA AVDD_OSC, VDDIO_SYS

VDD_1V05_PLL_AP For TEGRA VDDIO_DDR_HS

VDD_1V8_PMU For TEGRA VDDIO_GMI,

VDD_1V05_PLL_AP

V_USB_3V3

VDD_1V8_PMU

2

VDD_3V3_HV_AP For TEGRA VDDIO_HV

VDD_1V05_PLL_AP For TEGRA AVDD_HDMI_PLL

VDD_1V05_PLL_AP

VDD_1V8_PMU For TEGRA VDDIO_BB

VDD_1V8_PMU

VDD_1V8_PMU For eMMC VCCQ Power rail

VDD_2V85_EMMC For eMMC Power rail

VDD_5V0_SYS For CODEC AMP Power

+MICBIAS For MIC signal

VDD_1V8_PMU For CODEC Power

V_MIPI_1V2 For eDP bridge Power

VDDC_1V8_EDP For eDP bridge Power

3

VDD_3V3_SYS For Cap sensor Power rail

BL_12V For LCD backlight Power rail

VDD_3V3_LCM For LCD Power rail

VDD_3V3_LCM For Touch Control Power rail

V_SENSOR_2V85 For GYRO & COMPASS rail

VDD_3V3_SYS For Wireless KB Power rail

V_CAM_2V8

VDD_1V8_PMU

V_VCM_2V8

VDD_3V3_SYS

VDD_1V8_PMU

VDD_3V3_SYS For NFC VBAT Power rail

VDD_1V8_PMU For NFC PVDD Power rail

VDD_3V3_SYS For GPS VDD Power rail

VDD_1V8_PMU

+GPS_AUX_OUT

VDD_3V3_SBY_EC(EC_AVCC) For MCU Power

4

Adapter power supply (12V)

AC or battery power rail for power circuit.

For All Device standby mode

PMU RTC power rail

DDR3L power rail & TEGRA DDR power rail

For TEGRA core logic

AVDD_PLL_P_C, AVDD_PLL_X,

AVDD_PLL_M, AVDD_PLL_U, AVDD_PLL_E

For TEGRA AVDDIO_USB3, AVDD_USB3_PLL

For TEGRA AVDD_USB, HVDD_USB3

For TEGRA VDDIO_CAM, VDDIO_SDMMC4,

AVDD_USB_PLL

For TEGRA AVDD_HDMIAVDD_3V3_HDMI_TEGRA_S

For TEGRA AVDD_DSI_CSI_PLL

For TEGRA AVDD_DSI_CSIV_MIPI_1V2

For SD card PowerVDD_3V3_SD_CARD

For TEGRA VDDIO_SDMMC3V_MICROSD_IO

For TEGRA VDDIO_Audio,VDDIO_SDMMC1,

VDDIO_UART

For eMMC VCC Power railVDD_2V85_EMMC

For 2M Front Camera & ALS Power railVDD_3V3_SYS

For 8M Rear CAMERA AVDD

For 8M Rear CAMERA VDDIO

For 8M Rear CAMERA VCM_VDD

For WIFI VBAT Power rail

For WIFI VIO Power rail

For GPS VDDIO Power rail

For GPS LNA Power

A

CTIVE SUSPEND

B

DEEP SLEEP OFF

C

OM Config

B

on-Touch

N

4

319TUBOL01 (SMT MB AB551 Z3ENN HYN 2G KIN 16G HDMI)

EMI@/DA@/HYN2G@/HYN16G@/AZURE@

4

319TUBOL02 (SMT MB AB551 Z3ENN T50 2G/16G HDMI)

EMI@/DA@/HYN2G@/HYN16G@/AZURE@

4319TUBOL03 (SMT MB AB551 Z3ENN T50 4G/32G HDMI)

EMI@/DA@/HYN4G@/HYN32G@/AZURE@

4319TUBOL04 (SMT MB AB551 Z3ENN T50 2G/32G HDMI)

EMI@/DA@/HYN2G@/HYN32G@/AZURE@

4319TUBOL05 (SMT MB AB551 Z3ENN T50 4G/16G HDMI)

EMI@/DA@/HYN4G@/HYN16G@/AZURE@

4319TUBOL06 (SMT MB AB551 Z3ENN HYN 2G KIN 16G P2 HDMI)

EMI@/DA@/HYN2G@/KIN16G@/AZURE@

Touch

4319TUBOL07 (SMT MB AB551 Z3ENN T50 2G/16G T HDMI)

TS@/EMI@/DA@/HYN2G@/KIN16GA@/AZURE@

4319TUBOL08 (SMT MB AB551 Z3ENN T50 4G/32G T HDMI)

TS@/EMI@/DA@/HYN4G@/HYN32G@/FOXCO@

4319TUBOL09 (SMT MB AB551 Z3ENN T50 2G/32G T HDMI)

TS@/EMI@/DA@/HYN2G@/HYN32G@/FOXCO@

4319TUBOL10 (SMT MB AB551 Z3ENN T50 4G/16G T HDMI)

TS@/EMI@/DA@/HYN4G@/KIN16G@/FOXCO@

@EMI@

DA@PCB

@

KIN16G@

HYN16G@

KIN32G@

HYN32G@

KIN16GA@

HYN2G@

HYN4G@

KIN2G@

AZURE@

FOXCO@

E

1

2

3

4

D

B

TO Option Table

B

TO Item BOM Structure

EMI Part EMI@

EMI Reserve Part

ESD Reserve Part @ESD@

Connector CONN@

UN-MOUNT

eMMC

DDR3L

WIFI/BT

Touch Screen TS@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

A

B

C

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

2013/11/20 2014/11/09

2013/11/20 2014/11/09

2013/11/20 2014/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Notes List

Notes List

Notes List

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

E

of

3 42Thursday, June 1 9, 2014

of

3 42Thursday, June 1 9, 2014

of

3 42Thursday, June 1 9, 2014

0.1

0.1

0.1

A

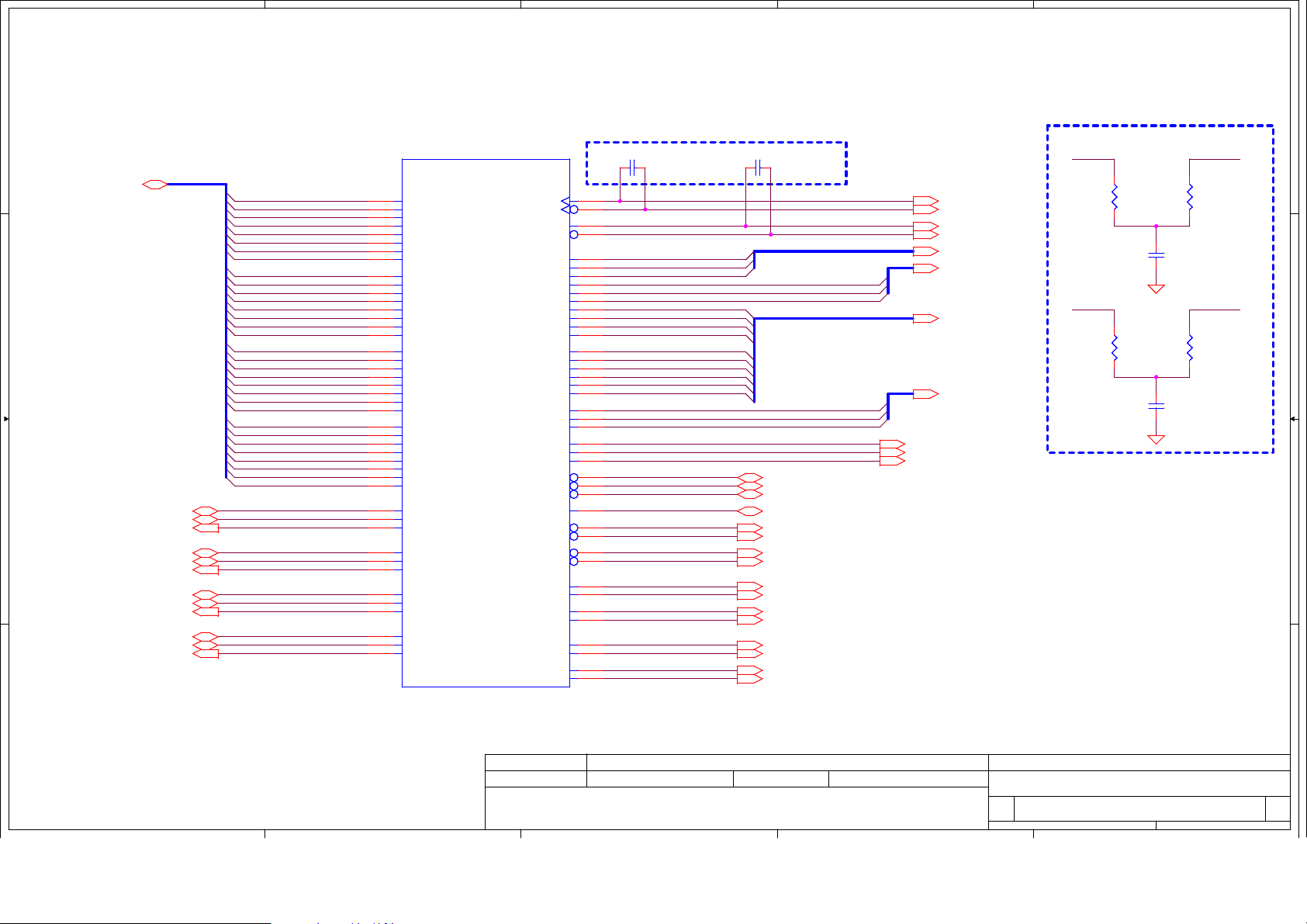

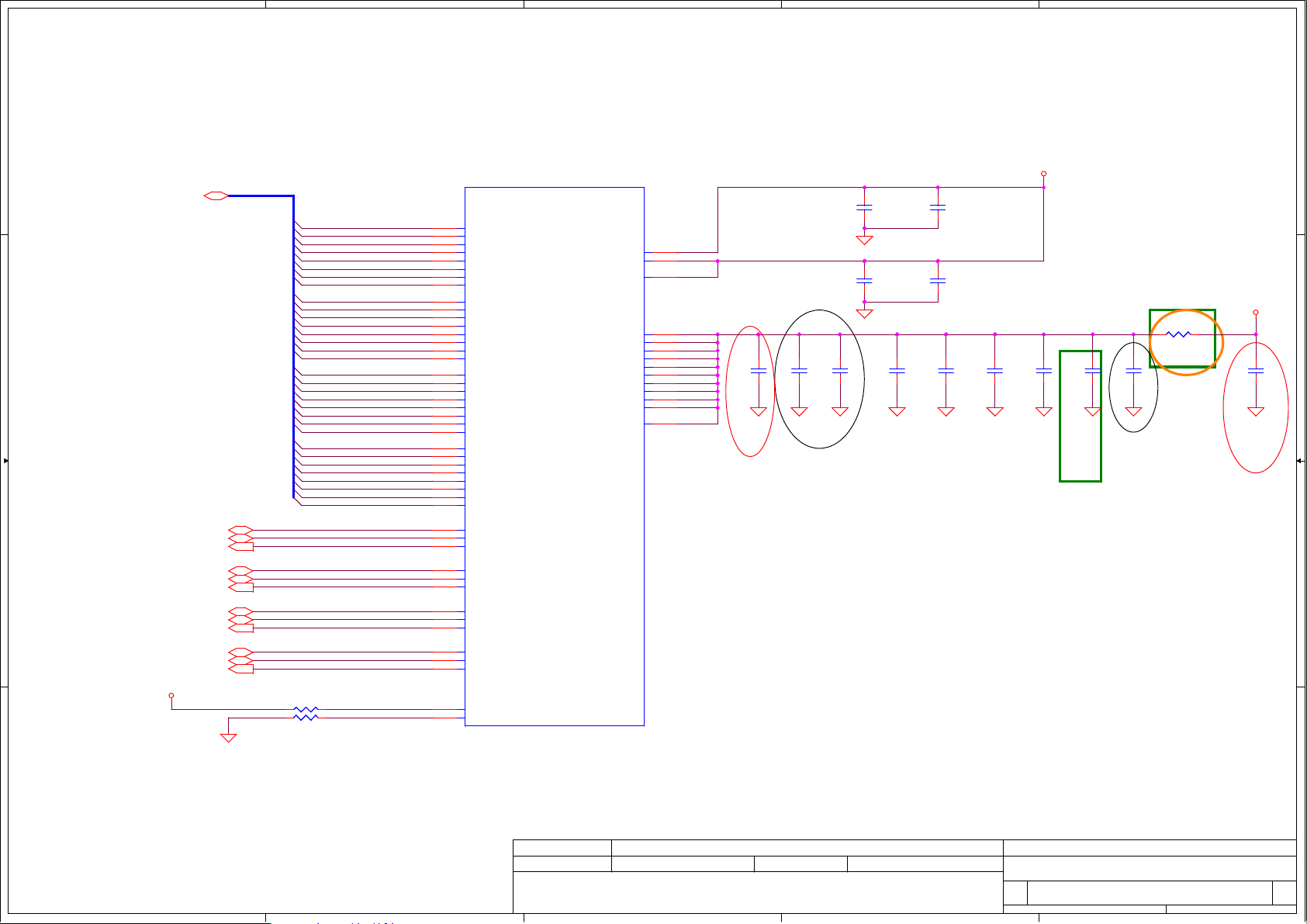

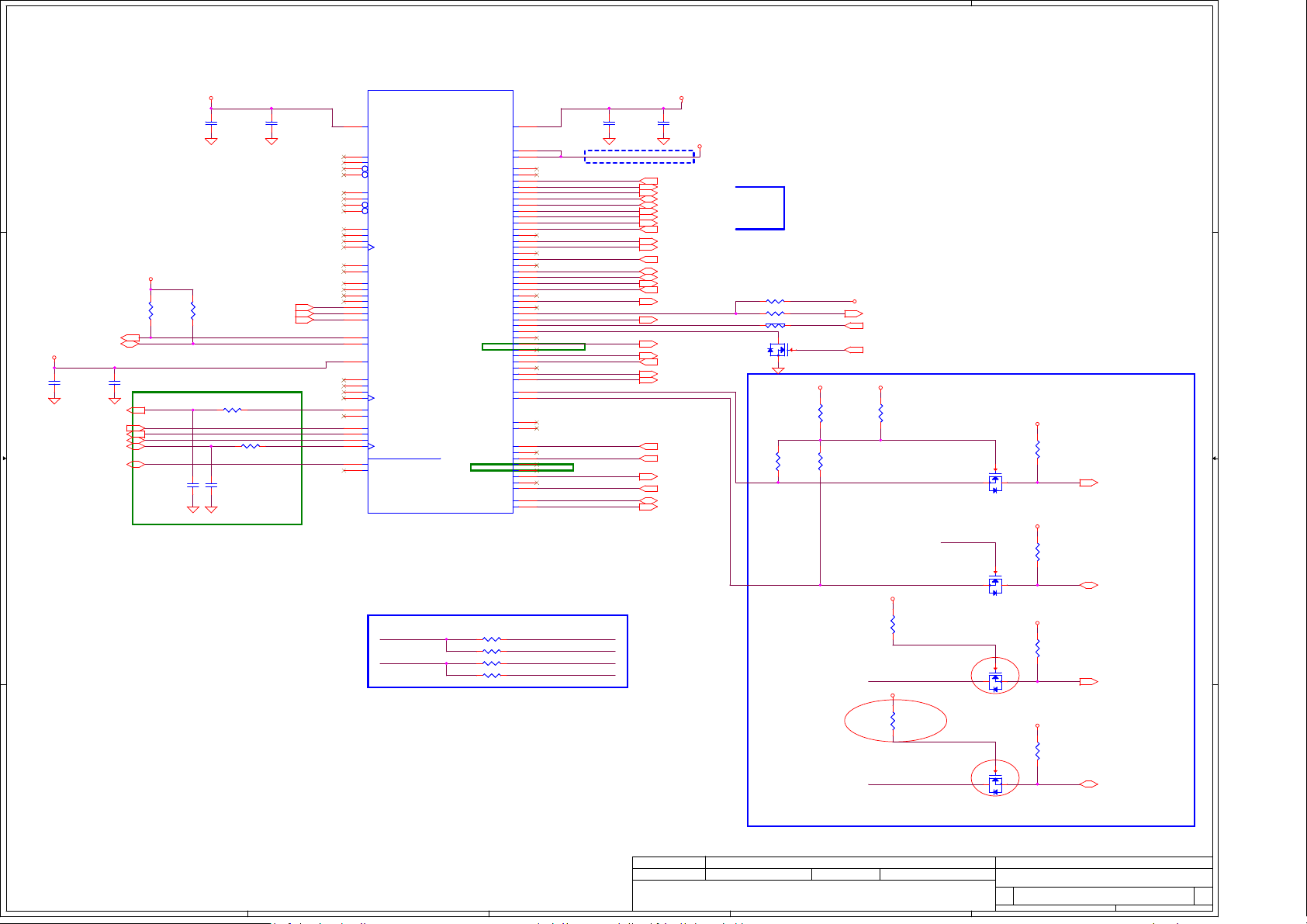

D580M: CH0 MEMORY I/F

C

1

DDR_DQ[0..31](6)

BYTE 0

BYTE 2

2

BYTE 1

BYTE 3

DDR_DQS0P(6)

3

DDR_DQS0N(6)

DDR_DM0(6)

DDR_DQS2P(6)

DDR_DQS2N(6)

DDR_DM2(6)

DDR_DQS1P(6)

DDR_DQS1N(6)

DDR_DM1(6)

DDR_DQS3P(6)

DDR_DQS3N(6)

DDR_DM3(6)

DDR_DQS0P

DDR_DQS0N

DDR_DQS2P

DDR_DQS2N

DDR_DQS1P

DDR_DQS1N

DDR_DQS3P

DDR_DQS3N

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

DDR_DM0

DDR_DM2

DDR_DM1

DDR_DM3

B

U1E

U1E

BGA

BGA

SEC 5 OF 8

B5

DDR_DQ0

B2

DDR_DQ1

A5

DDR_DQ2

C2

DDR_DQ3

B3

DDR_DQ4

C3

DDR_DQ5

A4

DDR_DQ6

A3

DDR_DQ7

E9

DDR_DQ8

A9

DDR_DQ9

G8

DDR_DQ10

C9

DDR_DQ11

E8

DDR_DQ12

F9

DDR_DQ13

F8

DDR_DQ14

D9

DDR_DQ15

B8

DDR_DQ16

C6

DDR_DQ17

A8

DDR_DQ18

A6

DDR_DQ19

F6

DDR_DQ20

D6

DDR_DQ21

A7

DDR_DQ22

E6

DDR_DQ23

D11

DDR_DQ24

A11

DDR_DQ25

E11

DDR_DQ26

B11

DDR_DQ27

F11

DDR_DQ28

G12

DDR_DQ29

A10

DDR_DQ30

H12

DDR_DQ31

C5

DDR_DQS0P

D5

DDR_DQS0N

C1

DDR_DM0

G9

DDR_DQS1P

H9

DDR_DQS1N

B9

DDR_DM1

C8

DDR_DQS2P

D8

DDR_DQS2N

B6

DDR_DM2

H11

DDR_DQS3P

G11

DDR_DQS3N

C11

DDR_DM3

SA00007KT00

S IC CD580M-R-A1 FCBGA 813P GPU

SEC 5 OF 8

CD580M

CD580M

DDR_CLK

DDR_CLK_N

DDR_CLKB

DDR_CLKB_N

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_A15

DDR_A_B3

DDR_A_B4

DDR_A_B5

DDR_BA0

DDR_BA1

DDR_BA2

DDR_CAS_N

DDR_RAS_N

DDR_WE_N

DDR_RESET_N

DDR_CS0_N

DDR_CS1_N

DDR_CS_B0_N

DDR_CS_B1_N

DDR_CKE0

DDR_CKE1

DDR_CKE_B0

DDR_CKE_B1

DDR_ODT0

DDR_ODT1

DDR_ODT_B0

DDR_ODT_B1

C

Capacitor need close to SOC < 100mil.

1

1

C1 2.2P_0402_50V

C1 2.2P_0402_50V

G14

H14

H18

G18

C14

D12

E14

G15

E12

D14

B12

F14

C12

F12

H15

D20

F18

D18

C20

A16

G17

E20

H17

E17

E18

F17

C15

D15

E15

F15

A12

B14

A19

A18

A13

A14

A20

B20

A15

B15

C18

B18

2

DDR0_CLKP

DDR0_CLKN

DDR1_CLKP

DDR1_CLKN

DDR_A0

DDR_A1

DDR_A2

DDR0_A3

DDR0_A4

DDR0_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_A15

DDR1_A3

DDR1_A4

DDR1_A5

DDR_BA0

DDR_BA1

DDR_BA2

DDR_CAS#

DDR_RAS#

DDR_WE#

DDR_RESET#

DDR0_CS0#

DDR0_CS1#

DDR1_CS0#

DDR1_CS1#

DDR0_CKE0

DDR0_CKE1

DDR1_CKE0

DDR1_CKE1

DDR0_ODT0

DDR0_ODT1

DDR1_ODT0

DDR1_ODT1

C2 2.2P_0402_50V

C2 2.2P_0402_50V

2

DDR_CAS# (6,7)

DDR_RAS# (6,7)

DDR_WE# (6,7)

DDR_RESET# (6,7)

DDR0_CS0# (6)

DDR0_CS1# (6)

DDR1_CS0# (7)

DDR1_CS1# (7)

DDR0_CKE0 (6)

DDR0_CKE1 (6)

DDR1_CKE0 (7)

DDR1_CKE1 (7)

DDR0_ODT0 (6)

DDR0_ODT1 (6)

DDR1_ODT0 (7)

DDR1_ODT1 (7)

D

DDR_BA0 (6,7)

DDR_BA1 (6,7)

DDR_BA2 (6,7)

DDR0_CLKP (6)

DDR0_CLKN (6)

DDR1_CLKP (7)

DDR1_CLKN (7)

DDR_A[0..2] (6,7)

DDR0_A[5..3] (6)

DDR_A[6..15] (6,7)

DDR1_A[5..3] (7)

E

N

ote:Place at the T-point

DDR0_CLKN

R1

R1

45.3_0402_1%

45.3_0402_1%

1

45.3_0402_1%

45.3_0402_1%

2

DDR0_CLK_TERM

R2

R2

DDR0_CLKP

1

2

1

C3

C3

0.01U_0402_16V7K

0.01U_0402_16V7K

2

DDR1_CLKN

R3

R3

45.3_0402_1%

45.3_0402_1%

1

45.3_0402_1%

45.3_0402_1%

2

DDR1_CLK_TERM

R4

R4

DDR1_CLKP

1

2

1

C4

C4

0.01U_0402_16V7K

0.01U_0402_16V7K

2

1

2

3

4

Security Classification

Security Classification

Security Classification

2013/11/20 2014/11/09

2013/11/20 2014/11/09

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2013/11/20 2014/11/09

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

DDR3L (Channel 0)

DDR3L (Channel 0)

DDR3L (Channel 0)

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

E

of

4 42Thursday, June 19, 2014

of

4 42Thursday, June 19, 2014

of

4 42Thursday, June 19, 2014

4

0.1

0.1

0.1

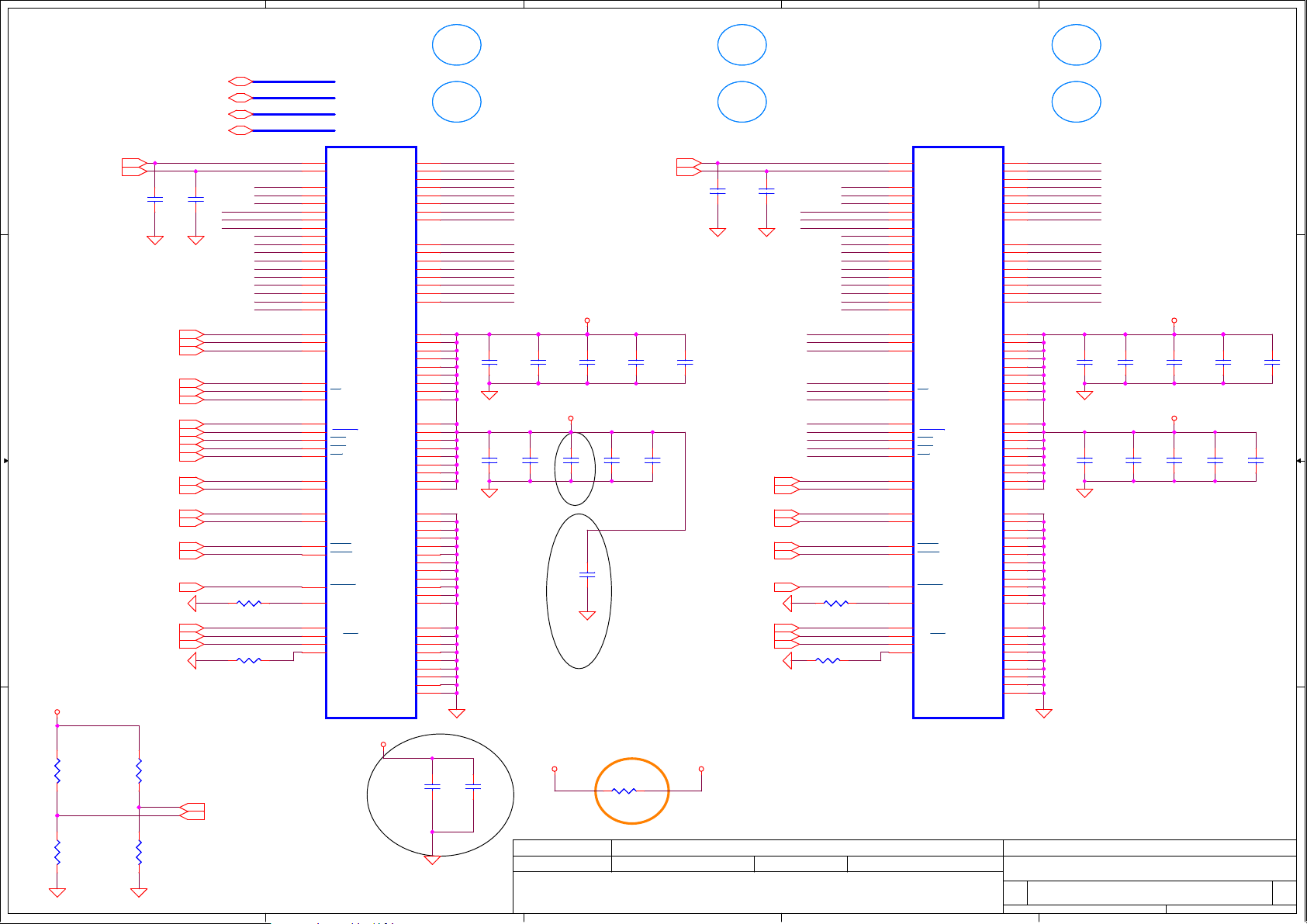

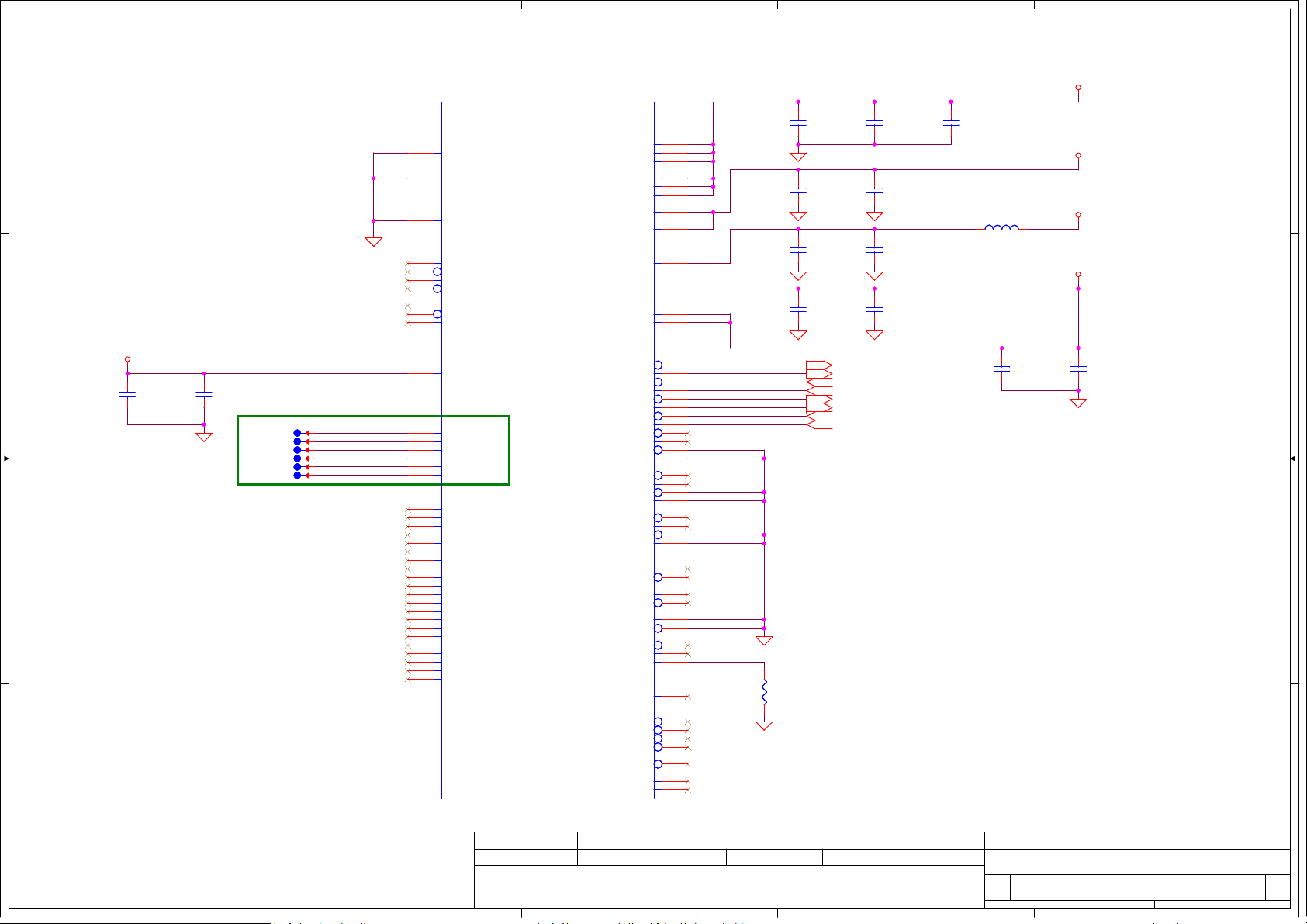

A

D580M: CH1 MEMORY I/F

C

B

C

D

E

1

C13

C13

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

+1.05V_RUN_AVDD

1

C14

C14

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

2

Change R5 to 0.01 ohm,

follow nV comment, 12/23

R5

R5

1

0.01_1206_ 1%

0.01_1206_ 1%

1

47P_0402_50V8J

47P_0402_50V8J

2

C326

C326

1

C342

C342

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

2

1

2

+1.35V_LP0

2

C347

C347

33P_0402_50V8K

33P_0402_50V8K

5/04 EMI ADD

Add C347 33P to +1.35V_LP0 for EMI, 05/22

U1F

U1F

BGA

BGA

DDR_DQ[32..63](7)

E21

B21

G21

A21

G20

D21

F20

C21

B26

C24

A26

A24

E26

D24

E27

A25

B23

G23

A23

H23

C23

F24

A22

E24

C31

C27

C30

A27

C29

D27

A29

A28

H21

H20

F21

C26

D26

B24

E23

D23

F23

B30

B29

B27

C17

D17

DDR_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ44

DDR_DQ45

DDR_DQ46

DDR_DQ47

DDR_DQ48

DDR_DQ49

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ53

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ57

DDR_DQ58

DDR_DQ59

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ63

DDR_DQS4P

DDR_DQS4N

DDR_DM4

DDR_DQS5P

DDR_DQS5N

DDR_DM5

DDR_DQS6P

DDR_DQS6N

DDR_DM6

DDR_DQS7P

DDR_DQS7N

DDR_DM7

DDR_COMP_PU

DDR_COMP_PD

1

1

DDR_DM4

DDR_DM6

DDR_DM5

DDR_DM7

R634_0402_1%

R634_0402_1%

R734_0402_1%

R734_0402_1%

DDR_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ48

DDR_DQ49

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ53

DDR_DQ54

DDR_DQ55

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ44

DDR_DQ45

DDR_DQ46

DDR_DQ47

DDR_DQ56

DDR_DQ57

DDR_DQ58

DDR_DQ59

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ63

DDR_COMP_PU

DDR_COMP_PD

BYTE 4

BYTE 6

2

BYTE 5

BYTE 7

DDR_DQS4P(7 )

DDR_DQS4N(7)

DDR_DM4(7)

3

+1.35V_LP0_ VDDIO_DDR

DDR_DQS6P(7 )

DDR_DQS6N(7)

DDR_DM6(7)

DDR_DQS5P(7 )

DDR_DQS5N(7)

DDR_DM5(7)

DDR_DQS7P(7 )

DDR_DQS7N(7)

DDR_DM7(7)

DDR_DQS4P

DDR_DQS4N

DDR_DQS6P

DDR_DQS6N

DDR_DQS5P

DDR_DQS5N

DDR_DQS7P

DDR_DQS7N

2

2

CD580M

CD580M

SEC 6 OF 8

SEC 6 OF 8

(1.05V)

(1.05V)

AVDD_PLL_APC2C3

VDDIO_DDR_HS

(1.2 - 1.5V)

(1.2 - 1.5V)

VDDIO_DDR 10

VDDIO_DDR_MCLK

AVDD_PLL_M

VDDIO_DDR 1

VDDIO_DDR 2

VDDIO_DDR 3

VDDIO_DDR 4

VDDIO_DDR 5

VDDIO_DDR 6

VDDIO_DDR 7

VDDIO_DDR 8

VDDIO_DDR 9

C5

C5

0.1U_0402_1 0V6K

0.1U_0402_1 0V6K

K16

B17

A17

J9

J12

J14

J11

J17

J18

J20

J21

K10

K11

J15

Add C346 33P to +1.35V_LP0_VDDIO_DDR for EMI, 05/22

C346

C346

33P_0402_50V8K

33P_0402_50V8K

1

C9

C9

0.47U_0402_16V4Z

0.47U_0402_16V4Z

2

1/18 follow nvidia suggestion for PDN

C7

C7

0.1U_0402_1 0V6K

0.1U_0402_1 0V6K

1

1

C10

C10

0.47U_0402_16V4Z

0.47U_0402_16V4Z

2

2

1

C6

C6

2.2U_0402_6 .3V6M

2.2U_0402_6 .3V6M

2

1

C8

C8

2.2U_0402_6 .3V6M

2.2U_0402_6 .3V6M

2

+1.35V_LP0_ VDDIO_DDR

1

C11

C11

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

2

1

2

1

2

1

C12

C12

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

2

Add C326 4.7uF, follow nV comment, 01/13

1

2

1

2

3

4

Security Classification

Security Classification

Security Classification

2013/11/20 2014/11/09

2013/11/20 2014/11/09

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIA L

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIA L

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIA L

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAI NS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAI NS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAI NS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CO NSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CO NSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CO NSENT OF COMPAL ELECTRONICS, INC.

2013/11/20 2014/11/09

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Doc ument Number Rev

Size Doc ument Number Rev

Size Doc ument Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

DDR3L (Channel 1)

DDR3L (Channel 1)

DDR3L (Channel 1)

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

E

of

5 42Thursday, June 19, 201 4

of

5 42Thursday, June 19, 201 4

of

5 42Thursday, June 19, 201 4

4

0.1

0.1

0.1

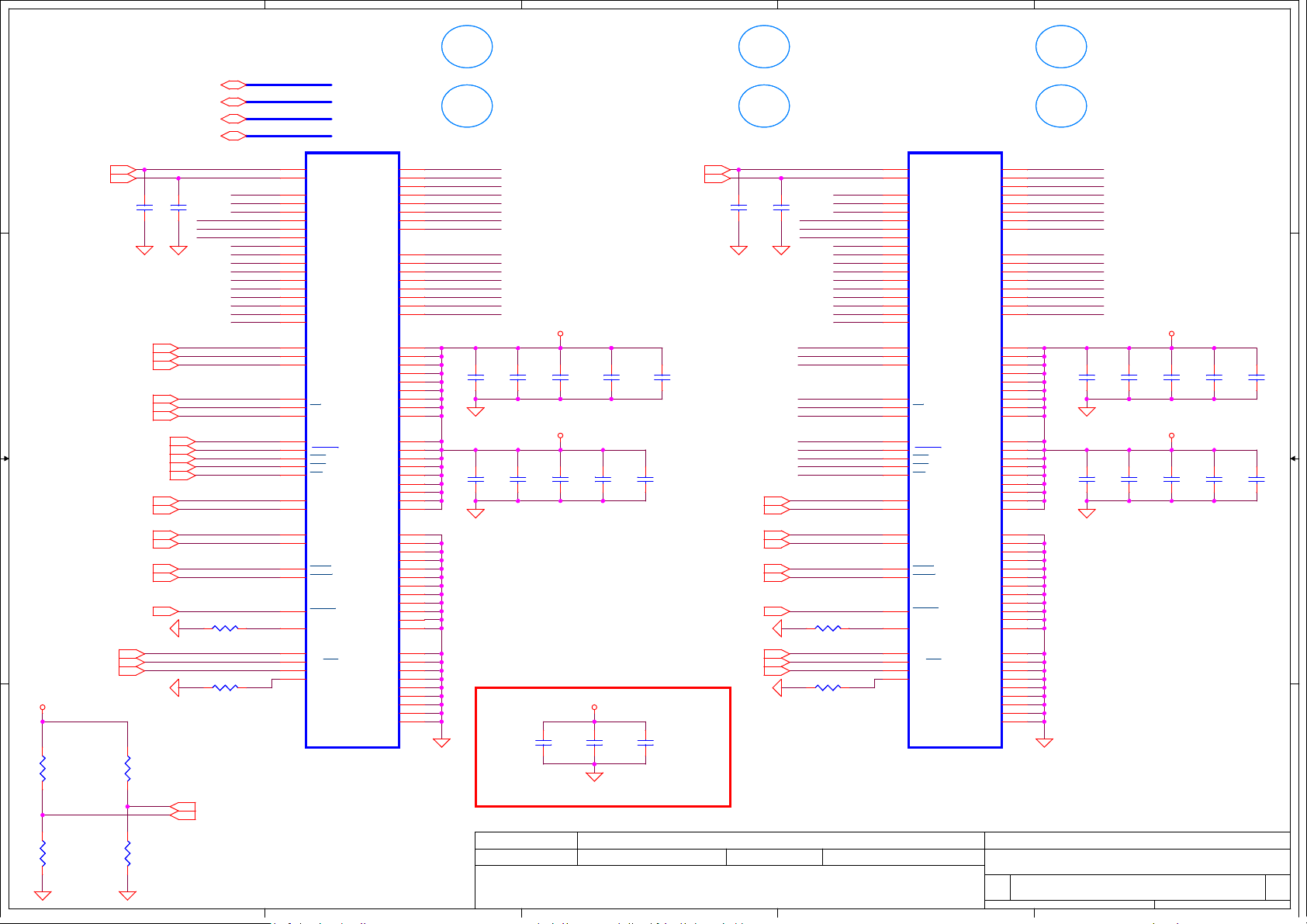

1

2

3

4

MEM_0_VREFCA(6)

MEM_0_VREFDQ(6)

+VDDIO_DRAM

1

R12

R12

5.49K_0402_ 1%

5.49K_0402_ 1%

2

1

R15

R15

5.49K_0402_ 1%

5.49K_0402_ 1%

2

A

2

56Mx16 DDR3 *4==>2048MB

512Mx16 DDR3 *4==>4096MB

DR_DQ[0..31](4)

D

DR_A[0..2](4,7)

D

DR0_A[5..3](4)

D

DR_A[6..15](4,7)

D

M8

H1

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

K1

L2

J3

K3

L3

F3

C7

E7

D3

G3

B7

T2

2

L8

J1

L1

J9

L9

2

C15

C15

DDR_BA0(4,7)

DDR_BA1(4,7)

DDR_BA2(4,7)

DDR0_CLKP(4)

DDR0_CLKN(4)

DDR0_CKE0(4)

DDR0_ODT0(4)

DDR0_CS0#(4)

DDR_RAS#(4,7)

DDR_CAS#(4,7)

DDR_WE#(4,7)

DDR_DQS0P(4)

DDR_DQS2P(4)

DDR_DM0(4 )

DDR_DM2(4 )

DDR_DQS0N(4)

DDR_DQS2N(4)

DDR_RESET#(4,6,7)

DDR0_ODT1(4,6)

DDR0_CS1#(4,6)

DDR0_CKE1(4,6)

1

R13

R13

5.49K_0402_ 1%

5.49K_0402_ 1%

2

1

R16

R16

5.49K_0402_ 1%

5.49K_0402_ 1%

2

A

1

1

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

C16

C16

2

2

DDR_A0

DDR_A1

DDR_A2

DDR0_A3

DDR0_A4

DDR0_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_A15

DDR_BA0

DDR_BA1

DDR_BA2

DDR0_CLKP

DDR0_CLKN

DDR0_CKE0

DDR0_ODT0

DDR0_CS0#

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_DQS0P

DDR_DQS2P

DDR_DM0

DDR_DM2

DDR_DQS0N

DDR_DQS2N

DDR_RESET#

1

R8

R8

240_0402_1 %

240_0402_1 %

DDR0_ODT1

DDR0_CS1#

DDR0_CKE1

1

R10

R10

240_0402_1 %

240_0402_1 %

MEM_0_VREFCA (6)

MEM_0_VREFDQ (6)

U

U

19

19

VREFCA

VREFDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15/BA3

BA0

BA1

BA2

CK

CK

CKE/CKE0

ODT/ODT0

CS/CS0

RAS

CAS

WE

DQSL

DQSU

DML

DMU

DQSL

DQSU

RESET

ZQ/ZQ0

NC/ODT1

NC/CS1

NC/CE1

NCZQ1

96-BALL

96-BALL

SDRAM DDR3

SDRAM DDR3

H5TC4G63MFR-PBA 9 6P

H5TC4G63MFR-PBA 9 6P

SA00005AV50

SA00005AV50

+VDDIO_DRAM

@

@

5/04 EMI ADD

B

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

B

C340

C340

47P_0402_50V8J

47P_0402_50V8J

C

19

19

U

U

U

U

19

19

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

1

2

YN2G@

YN2G@

H

H

S

S

A00005AV50

A00005AV50

S

S

IC D3 256M16/1600 H5TC4G6 3AFR-PBA ABO!

IC D3 256M16/1600 H5TC4G6 3AFR-PBA ABO!

H

H

YN4G@

YN4G@

S

S

A00006WZ40

A00006WZ40

S

S

IC D3 512M16/1600 H5TC8G6 3AMR-PBA ABO!

IC D3 512M16/1600 H5TC8G6 3AMR-PBA ABO!

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

+VDDIO_DRAM

MEM_0_VREFCA( 6)

MEM_0_VREFDQ(6)

205mA 205mA

0.1U_0402_10V6K

4.7U_0603_6.3V6M

C19

C19

C29

C29

4.7U_0603_6.3V6M

1

2

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

1

2

1

C341

C341

47P_0402_50V8J

47P_0402_50V8J

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C20

C20

C30

C30

1/18 follow nvidia suggestion for PDN

C21

C21

2

+VDDIO_DRAM

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C31

C31

2

C331

C331

+VDDIO_DRAM

820mA

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIA L

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIA L

THIS SHEET OF ENGINEERI NG DRAWING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIA L

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERE D FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAI NS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAI NS

DEPARTMENT EXCEPT AS A UTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAI NS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CO NSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CO NSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CO NSENT OF COMPAL ELECTRONICS, INC.

0.1U_0402_10V6K

0.1U_0402_10V6K

1

2

0.47U_0402_16V4Z

0.47U_0402_16V4Z

1

C32

C32

2

0.47U_0402_16V4Z

0.47U_0402_16V4Z

1

2

0.1U_0402_10V6K

1

C22

C22

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C33

C33

2

R14

R14

1

2

0.01_0805_ 1%

0.01_0805_ 1%

0612 modified.

C23

C23

0.1U_0402_10V6K

0.1U_0402_10V6K

1

2

+1.35V_LP0

2013/11/20 2014/11/09

2013/11/20 2014/11/09

2013/11/20 2014/11/09

C

20

20

U

U

U

U

20

20

1

0.1U_0402_10V6K

0.1U_0402_10V6K

C18

C18

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

2

DDR_DQS1P(4 )

DDR_DQS3P(4 )

DDR_DM1(4)

DDR_DM3(4)

DDR_DQS1N(4)

DDR_DQS3N(4)

DDR_RESET#(4,6,7)

DDR0_ODT1(4,6)

DDR0_CS1#(4,6)

DDR0_CKE1(4,6)

Compal Secret Data

Compal Secret Data

Compal Secret Data

YN2G@

YN2G@

H

H

S

S

A00005AV50

A00005AV50

S

S

IC D3 256M16/1600 H5TC4G6 3AFR-PBA ABO!

IC D3 256M16/1600 H5TC4G6 3AFR-PBA ABO!

H

H

YN4G@

YN4G@

S

S

A00006WZ40

A00006WZ40

S

S

IC D3 512M16/1600 H5TC8G6 3AMR-PBA ABO!

IC D3 512M16/1600 H5TC8G6 3AMR-PBA ABO!

1

C17

C17

2

Deciphered Date

Deciphered Date

Deciphered Date

0.1U_0402_10V6K

0.1U_0402_10V6K

DDR0_A3

DDR0_A4

DDR0_A5

DDR_BA0

DDR_BA1

DDR_BA2

DDR0_CLKP

DDR0_CLKN

DDR0_CKE0

DDR0_ODT0

DDR0_CS0#

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_DQS1P

DDR_DQS3P

DDR_DM1

DDR_DM3

DDR_DQS1N

DDR_DQS3N

DDR_RESET#

1

R9

R9

240_0402_1 %

240_0402_1 %

DDR0_ODT1

DDR0_CS1#

DDR0_CKE1

1

R11

R11

240_0402_1 %

240_0402_1 %

DDR_A0

DDR_A1

DDR_A2

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_A15

2

2

D

U

U

20

20

M8

VREFCA

H1

VREFDQ

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12

T3

A13

T7

A14

M7

A15/BA3

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE/CKE0

K1

ODT/ODT0

L2

CS/CS0

J3

RAS

K3

CAS

L3

WE

F3

DQSL

C7

DQSU

E7

DML

D3

DMU

G3

DQSL

B7

DQSU

T2

RESET

L8

ZQ/ZQ0

J1

NC/ODT1

L1

NC/CS1

J9

NC/CE1

L9

NCZQ1

96-BALL

96-BALL

SDRAM DDR3

SDRAM DDR3

H5TC4G63MFR-PBA 9 6P

H5TC4G63MFR-PBA 9 6P

SA00005AV50

SA00005AV50

@

@

D

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

E

19

19

U

U

U

U

20

20

E3

DDR_DQ8

F7

DDR_DQ9

F2

DDR_DQ10

F8

DDR_DQ11

H3

DDR_DQ12

H8

DDR_DQ13

G2

DDR_DQ14

H7

DDR_DQ15

D7

DDR_DQ24

C3

DDR_DQ25

C8

DDR_DQ26

C2

DDR_DQ27

A7

DDR_DQ28

A2

DDR_DQ29

B8

DDR_DQ30

A3

DDR_DQ31

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

Title

Title

Title

Size Doc ument Number Rev

Size Doc ument Number Rev

Size Doc ument Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

C24

C24

C34

C34

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

IN2G@

IN2G@

K

K

S

S

A00007X410

A00007X410

S

S

IC D3 256M16/1600 D25 16EC4BXGGB ABO!

IC D3 256M16/1600 D25 16EC4BXGGB ABO!

K

K

IN2G@

IN2G@

S

S

A00007X410

A00007X410

S

S

IC D3 256M16/1600 D25 16EC4BXGGB ABO!

IC D3 256M16/1600 D25 16EC4BXGGB ABO!

+VDDIO_DRAM

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

0.1U_0402_10V6K

1

2

1

2

0.1U_0402_10V6K

1

C25

C25

2

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

1

C35

C35

2

DDR3L CH0

DDR3L CH0

DDR3L CH0

1

C26

C26

2

+VDDIO_DRAM

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C36

C36

2

E

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C27

C27

2

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C37

C37

2

6 42Thursday, June 19, 201 4

6 42Thursday, June 19, 201 4

6 42Thursday, June 19, 201 4

C38

C38

of

of

of

0.1U_0402_10V6K

0.1U_0402_10V6K

C28

C28

1

2

1

0.1U_0402_10V6K

0.1U_0402_10V6K

1

2

2

0.1U_0402_10V6K

0.1U_0402_10V6K

3

4

0.1

0.1

0.1

1

2

3

+VDDIO_DRAM

4

MEM_1_VREFCA(7)

MEM_1_VREFDQ(7)

DDR1_ODT1(4,7)

DDR1_CS1#(4,7)

DDR1_CKE1(4,7)

1

R21

R21

5.49K_0402_1%

5.49K_0402_1%

2

1

R23

R23

5.49K_0402_1%

5.49K_0402_1%

2

A

2

56Mx16 DDR3 *4==>2048MB

512Mx16 DDR3 *4==>4096MB

D

DR_DQ[32..63](5)

D

DR_A[0..2](4,6)

DR1_A[5..3](4)

D

D

DDR_RESET#(4,6,7)

C39

C39

DDR_BA0(4,6)

DDR_BA1(4,6)

DDR_BA2(4,6)

DDR1_CLKP(4)

DDR1_CLKN(4)

DDR1_CKE0(4)

DDR_DQS6P(5)

DDR_DQS4P(5)

DDR_DM6(5)

DDR_DM4(5)

DDR_DQS6N(5)

DDR_DQS4N(5)

1

C40

C40

0

0

.1U_0402_10V6K

.1U_0402_10V6K

2

DDR1_ODT0(4)

DDR1_CS0#(4)

DDR_RAS#(4,6)

DDR_CAS#(4,6)

DDR_WE#(4,6)

1

R22

R22

5.49K_0402_1%

5.49K_0402_1%

2

1

R24

R24

5.49K_0402_1%

5.49K_0402_1%

2

A

DR_A[6..15](4,6)

1

0.1U_0402_10V6K

0.1U_0402_10V6K

2

DDR_A0

DDR_A1

DDR_A2

DDR1_A3

DDR1_A4

DDR1_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_A15

DDR_BA0

DDR_BA1

DDR_BA2

DDR1_CLKP

DDR1_CLKN

DDR1_CKE0

DDR1_ODT0

DDR1_CS0#

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_DQS6P

DDR_DQS4P

DDR_DM6

DDR_DM4

DDR_DQS6N

DDR_DQS4N

DDR_RESET#

1

2

R17

R17

240_0402_1%

240_0402_1%

DDR1_ODT1

DDR1_CS1#

DDR1_CKE1

1

2

R19

R19

240_0402_1%

240_0402_1%

MEM_1_VREFCA (7)

MEM_1_VREFDQ (7)

U

U

22

22

M8

VREFCA

H1

VREFDQ

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12

T3

A13

T7

A14

M7

A15/BA3

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE/CKE0

K1

ODT/ODT0

L2

CS/CS0

J3

RAS

K3

CAS

L3

WE

F3

DQSL

C7

DQSU

E7

DML

D3

DMU

G3

DQSL

B7

DQSU

T2

RESET

L8

ZQ/ZQ0

J1

NC/ODT1

L1

NC/CS1

J9

NC/CE1

L9

NCZQ1

96-BALL

96-BALL

SDRAM DDR3

SDRAM DDR3

H5TC4G63MFR-PBA 96P

H5TC4G63MFR-PBA 96P

SA00005AV50

SA00005AV50

@

@

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

+VDDIO_DRAM

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C50

C50

2

+VDDIO_DRAM

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C60

C60

2

E

1

2

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C51

C51

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C61

C61

2

7 42Thursday, June 19, 2014

7 42Thursday, June 19, 2014

7 42Thursday, June 19, 2014

E

1

1

C52

C52

2

2

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C62

C62

2

2

3

4

0.1

0.1

0.1

of

of

of

B

U

U

22

22

U

U

22

22

E3

DDR_DQ48

F7

DDR_DQ49

F2

DDR_DQ50

F8

DDR_DQ51

H3

DDR_DQ52

H8

DDR_DQ53

G2

DDR_DQ54

H7

DDR_DQ55

D7

DDR_DQ32

C3

DDR_DQ33

C8

DDR_DQ34

C2

DDR_DQ35

A7

DDR_DQ36

A2

DDR_DQ37

B8

DDR_DQ38

A3

DDR_DQ39

205mA 205mA

B2

D9

G7

K2

K8

C43

C43

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

C53

C53

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

B

YN2G@

YN2G@

H

H

S

S

A00005AV50

A00005AV50

S

S

IC D3 256M16/1600 H5TC4G63AFR-PBA ABO!

IC D3 256M16/1600 H5TC4G63AFR-PBA ABO!

H

H

YN4G@

YN4G@

A00006WZ40

A00006WZ40

S

S

S

S

IC D3 512M16/1600 H5TC8G63AMR-PBA ABO!

IC D3 512M16/1600 H5TC8G63AMR-PBA ABO!

+VDDIO_DRAM

0.1U_0402_10V6K

0.1U_0402_10V6K

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

1

1

C44

C44

2

2

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

1

1

C54

C54

2

2

1

C45

C45

2

+VDDIO_DRAM

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C55

C55

2

0.1U_0402_10V6K

0.1U_0402_10V6K

C46

C46

0.1U_0402_10V6K

0.1U_0402_10V6K

C56

C56

EMI, close to C50/C57/C28

+VDDIO_DRAM

1

C343

C343

2

Add C343/C344/C345 33P to +VDDIO_DRAM for EMI, 05/22

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

33P_0402_50V8K

33P_0402_50V8K

C344

C344

2

C

U

U

21

21

U

U

21

21

MEM_1_VREFCA(7)

MEM_1_VREFDQ(7)

0.1U_0402_10V6K

C47

C47

0.1U_0402_10V6K

1

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

2

1

33P_0402_50V8K

33P_0402_50V8K

2

C

0.1U_0402_10V6K

0.1U_0402_10V6K

1

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C57

C57

2

33P_0402_50V8K

33P_0402_50V8K

C345

C345

2013/11/20 2014/11/09

2013/11/20 2014/11/09

2013/11/20 2014/11/09

1

0.1U_0402_10V6K

0.1U_0402_10V6K

C42

C42

C41

C41

2

DDR_DQS7P(5)

DDR_DQS5P(5)

DDR_DM7(5)

DDR_DM5(5)

DDR_DQS7N(5)

DDR_DQS5N(5)

DDR_RESET#(4,6,7)

DDR1_ODT1(4,7)

DDR1_CS1#(4,7)

DDR1_CKE1(4,7)

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

YN2G@

YN2G@

H

H

S

S

A00005AV50

A00005AV50

S

S

IC D3 256M16/1600 H5TC4G63AFR-PBA ABO!

IC D3 256M16/1600 H5TC4G63AFR-PBA ABO!

H

H

YN4G@

YN4G@

A00006WZ40

A00006WZ40

S

S

S

S

IC D3 512M16/1600 H5TC8G63AMR-PBA ABO!

IC D3 512M16/1600 H5TC8G63AMR-PBA ABO!

0.1U_0402_10V6K

0.1U_0402_10V6K

DDR1_A3

DDR1_A4

DDR1_A5

DDR_DQS7P

DDR_DQS5P

DDR_DM7

DDR_DM5

DDR_DQS7N

DDR_DQS5N

DDR_RESET#

1

R18

R18

240_0402_1%

240_0402_1%

DDR1_ODT1

DDR1_CS1#

DDR1_CKE1

1

R20

R20

240_0402_1%

240_0402_1%

DDR_A0

DDR_A1

DDR_A2

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_A15

DDR_BA0

DDR_BA1

DDR_BA2

DDR1_CLKP

DDR1_CLKN

DDR1_CKE0

DDR1_ODT0

DDR1_CS0#

DDR_RAS#

DDR_CAS#

DDR_WE#

2

2

1

2

D

U

U

21

21

M8

VREFCA

H1

VREFDQ

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12

T3

A13

T7

A14

M7

A15/BA3

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE/CKE0

K1

ODT/ODT0

L2

CS/CS0

J3

RAS

K3

CAS

L3

WE

F3

DQSL

C7

DQSU

E7

DML

D3

DMU

G3

DQSL

B7

DQSU

T2

RESET

L8

ZQ/ZQ0

J1

NC/ODT1

L1

NC/CS1

J9

NC/CE1

L9

NCZQ1

96-BALL

96-BALL

SDRAM DDR3

SDRAM DDR3

H5TC4G63MFR-PBA 96P

H5TC4G63MFR-PBA 96P

SA00005AV50

SA00005AV50

@

@

D

U

U

22

22

U

U

21

21

E3

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Title

Title

Title

Size Doc ument Number Rev

Size Doc ument Number Rev

Size Doc ument Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

DDR_DQ56

F7

DDR_DQ57

F2

DDR_DQ58

F8

DDR_DQ59

H3

DDR_DQ60

H8

DDR_DQ61

G2

DDR_DQ62

H7

DDR_DQ63

D7

DDR_DQ40

C3

DDR_DQ41

C8

DDR_DQ42

C2

DDR_DQ43

A7

DDR_DQ44

A2

DDR_DQ45

B8

DDR_DQ46

A3

DDR_DQ47

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

IN2G@

IN2G@

K

K

S

S

A00007X410

A00007X410

S

S

IC D3 256M16/1600 D2516EC4BXGGB ABO!

IC D3 256M16/1600 D2516EC4BXGGB ABO!

K

K

IN2G@

IN2G@

A00007X410

A00007X410

S

S

S

S

IC D3 256M16/1600 D2516EC4BXGGB ABO!

IC D3 256M16/1600 D2516EC4BXGGB ABO!

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

1

C49

C49

C48

C48

2

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

1

C58

C58

C59

C59

2

DDR3L CH1

DDR3L CH1

DDR3L CH1

1

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

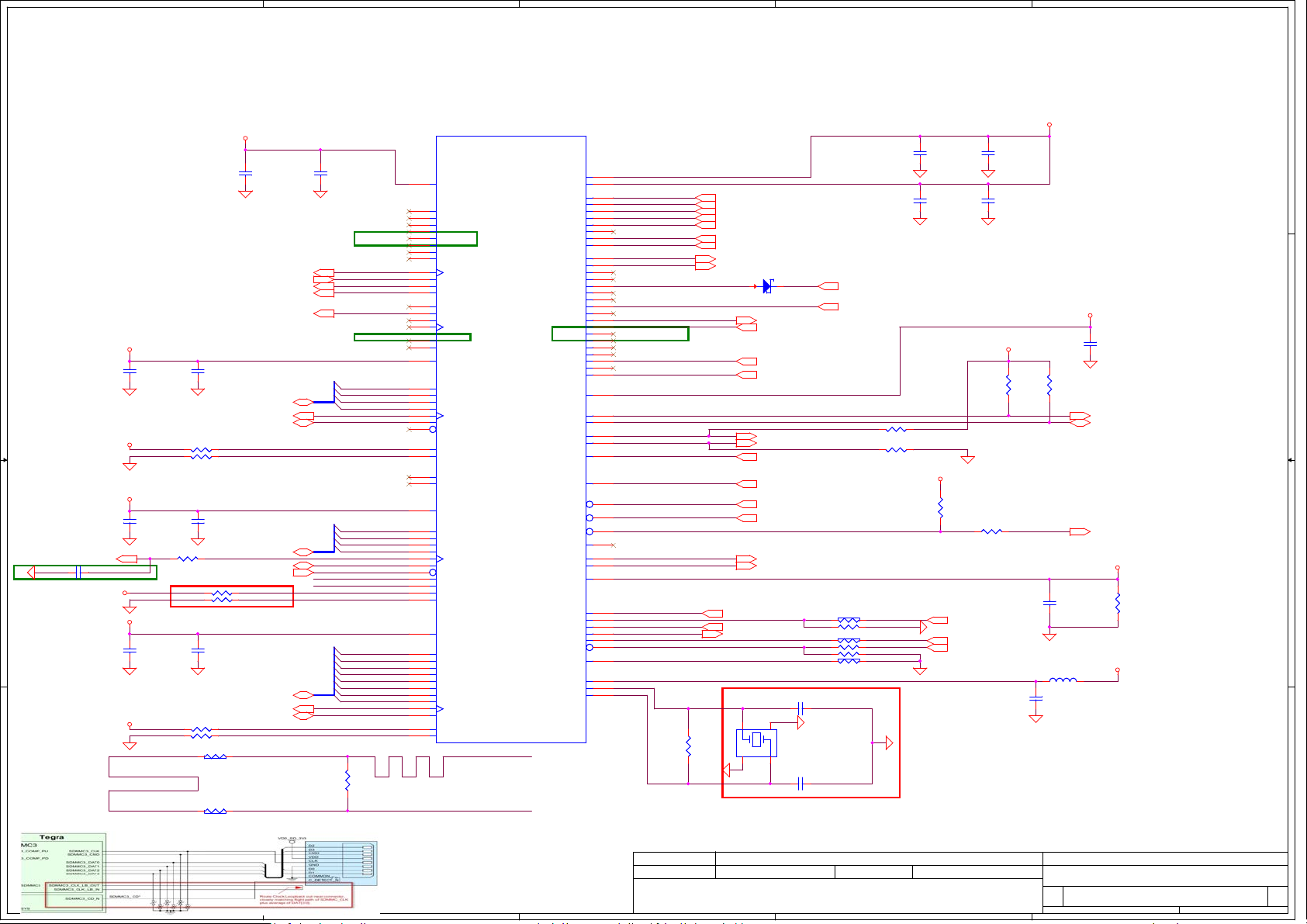

SDMMC3_CLK(27)

1

2

+VDDIO_SDMMC3

0.1U_0402_10V6K

0.1U_0402_10V6K

+1.8V_VDDIO_CPU

+1.8V_VDDIO_CPU

+VDDIO_SDMMC3

+1.8V_VDDIO_CPU

+1.8V_VDDIO_CPU

2

C327 22P_0402_50V8 J

C327 22P_0402_50V8 J

3

4

@

@

Add C327@ 22P, follow RF request, 01/14

A

1

C70

C70

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

2

1

C72

C72

2

1

C75

C75

2

SDMMC3_CLK_LB_IN_R

+

1.8V_VDDIO_CPU

1

C63

C63

0.1U_0402_10V6K

0.1U_0402_10V6K

2

KBC_SPI_MOSI(29)

KBC_SPI_MISO(29)

KBC_SPI_SCK(29)

KBC_SPI_CS(29)

EN_VDD_BL(15)

1

C71

C71

2

SDMMC1_DAT[3..0](20)

SDMMC1_CLK(20)

SDMMC1_CMD(20 )

R29 33.2_0402_1%

R29 33.2_0402_1%

1

R31 33.2_0402_1%

R31 33.2_0402_1%

1

R43 49.9_0402_1%

R43 49.9_0402_1%

R44 49.9_0402_1%

R44 49.9_0402_1%

2

1

2

1

C73 4.7U_0603 _6.3V6M

C73 4.7U_0603 _6.3V6M

2

R367

R367

0_0402_5%

0_0402_5%

R34 33.2_0402_1%

R34 33.2_0402_1%

R35 33.2_0402_1%

R35 33.2_0402_1%

C76

C76

1

1

SDMMC3_DAT[3..0](27)

2

SDMMC3_CMD(27 )

SDMMC3_CD(24,27)

1

2

1

2

Change R34/R35 from 49.9 to 33.2ohm, follow nV comment, 04/08

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

1

2

SDMMC4_DAT[7..0](25)

SDMMC4_CLK(25)

SDMMC4_CMD(25 )

2

2

R120 0_0402_5%

R120 0_0402_5%

1

2

R119 0_0402_5%

R119 0_0402_5%

1

2

1

C66

C66

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

2

Delete 3G interface, 12/19

SDMMC1_COMP_PU

SDMMC1_COMP_PD

SDMMC3_CLK_LB_OUT

SDMMC3_CLK_LB_IN

SDMMC3_COMP_PU

SDMMC3_COMP_PD

SDMMC4_COMP_PU

SDMMC4_COMP_PD

SDMMC1_DAT0

SDMMC1_DAT1

SDMMC1_DAT2

SDMMC1_DAT3

SDMMC3_DAT0

SDMMC3_DAT1

SDMMC3_DAT2

SDMMC3_DAT3

SDMMC4_DAT0

SDMMC4_DAT1

SDMMC4_DAT2

SDMMC4_DAT3

SDMMC4_DAT4

SDMMC4_DAT5

SDMMC4_DAT6

SDMMC4_DAT7

2

R75

R75

0_0402_5%

0_0402_5%

@

@

1

B

D580M_SDMMC_ULPI_JTAG

C

1A

1A

U

U

BGA

AC14

AF15

AH15

AD17

AJ15

AJ18

AH17

AK18

AL17

AK17

AL18

AG15

AL16

AF17

AE17

AE15

AJ17

AG17

AD15

P9

L2

L3

L1

J8

L7

L8

L5

J7

L6

K1

L4

E1

H2

H1

F1

G1

F5

F2

V24

F4

F3

E2

E5

F31

F29

F30

E28

H31

D31

E30

E29

F28

G31

E31

H30

H29

BGA

(1.8V-3.3V)

(1.8V-3.3V)

VDDIO_BB

ULPI_DATA0

ULPI_DATA1

ULPI_DATA2

ULPI_DATA3

ULPI_DATA4

ULPI_DATA5

ULPI_DATA6

ULPI_DATA7

ULPI_CLK

ULPI_DIR

ULPI_NXT

ULPI_STP

DAP3_DIN

DAP3_DOUT

DAP3_FS

DAP3_SCLK

GPIO_PV0

GPIO_PV1

(1.8V-3.3V)

(1.8V-3.3V)

VDDIO_SDMMC1

SDMMC1_DAT0

SDMMC1_DAT1

SDMMC1_DAT2

SDMMC1_DAT3

SDMMC1_CLK

SDMMC1_CMD

SDMMC1_WP_N

SDMMC1_COMP_PU

SDMMC1_COMP_PD

CLK2_OUT

CLK2_REQ

(1.8V-3.3V)

(1.8V-3.3V)

VDDIO_SDMMC3

SDMMC3_DAT0

SDMMC3_DAT1

SDMMC3_DAT2

SDMMC3_DAT3

SDMMC3_CLK

SDMMC3_CMD

SDMMC3_CD_N

SDMMC3_CLK_LB_OUT

SDMMC3_CLK_LB_IN

SDMMC3_COMP_PU

SDMMC3_COMP_PD

(1.2V-1.8V)

(1.2V-1.8V)

VDDIO_SDMMC4

SDMMC4_DAT0

SDMMC4_DAT1

SDMMC4_DAT2

SDMMC4_DAT3

SDMMC4_DAT4

SDMMC4_DAT5

SDMMC4_DAT6

SDMMC4_DAT7

SDMMC4_CLK

SDMMC4_CMD

SDMMC4_COMP_PU

SDMMC4_COMP_PD

SDMMC3_CLK_LB_OUT

CD580M

CD580M

SEC 1 OF 8

SEC 1 OF 8

SDMMC3_CLK_LB_IN

(1.8V-3.3V)

(1.8V-3.3V)

VDDIO_SYS

VDDIO_SYS_2

(0.9-1.1V)

(0.9-1.1V)

PWR_I2C_SCL

PWR_I2C_SDA

CORE_PWR_REQ

CPU_PWR_REQ

CLK_32K_IN

CLK_32K_OUT

PWR_INT_N

SYS_RESET_N

RESET_OUT_N

THERM_DP

THERM_DN

(1.8V)

(1.8V)

JTAG_RTCK

JTAG_TRST_N

TEST_MODE_EN

(1.8V - 3.3V)

(1.8V - 3.3V)

KB_COL0

KB_COL1

KB_COL2

KB_COL3

KB_COL4

KB_COL5

KB_COL6

KB_COL7

KB_ROW0

KB_ROW1

KB_ROW2

KB_ROW3

KB_ROW4

KB_ROW5

KB_ROW6

KB_ROW7

KB_ROW8

KB_ROW9

KB_ROW10

KB_ROW11

KB_ROW12

KB_ROW13

KB_ROW14

KB_ROW15

KB_ROW16

KB_ROW17

VDD_RTC

OWR

VPP_FUSE

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

AVDD_OSC

XTAL_IN

XTAL_OUT

V23

L10

AD30

AC28

AD28

AD31

AF28

AA27

AD29

AA25

W31

Y26

AF30

AC31

Y29

Y31

AB31

Y30

AA29

AA28

AA31

V28

Y27

AF29

AC30

Y25

AA26

AC29

AB12

J4

J3

Y28

V25

H3

J6

V30

AA30

Y24

AA7

U28

U29

R10

J2

H6

H5

J1

J5

H4

H7

D1

E3

E4

Delete 3G interface, 12/19Delete 3G interface, 12/19

JTAG_TCK_R

JTAG_TMS_R

JTAG_TRST#_R

TEST_MODE_EN

C

LID_CLOSED#

XTAL_IN

XTAL_OUT

ONKEY# (26)

HOLD_R (29)

SERVO_DBG_GPIO (24)

BD_ID_STRAP0 (26)

SDMMC3_WP# (27)

GOOG_DEV_MODE (24)

GOOG_RECOVERY_MODE (24)

EN_VDD_SD ( 27)

AP_WP# (18)

1

2

D1RB751V-40_SOD323-2

D1RB751V-40_SOD323-2

BR_UART1_TXD (24)

BR_UART1_RXD (24)

IGPU_PWRGD (36)

BD_ID_STRAP1 ( 26)

CORE_PWR_REQ (24,29,33 ,36)

CPU_PWR_REQ (24,33)

CLK_32KHZ_PMU (36)

CPU_OC_INT (36)

PMU_INT_L (36)

SYS_RESET# (21,24,25,3 0,36)

THERMD_P (21)

THERMD_N (21)

JTAG_RTCK (24)

JTAG_TDI (2 4)

JTAG_TDO (24)

1

2M_0402_5%

2M_0402_5%

2

1

R45

R45

4

Change C78/C79 to 8.2P, follow vendor suggestion, 04/09

R37 0_0402_5%

R37 0_0402_5%

R38 10K_0402_5%

R38 10K_0402_5%

R39 0_0402_5%

R39 0_0402_5%

R40 0_0402_5%@

R40 0_0402_5%@

R41 100K_0402_5%

R41 100K_0402_5%

R42 0_0402_5%

R42 0_0402_5%

C78

C78

8.2P_0402_50V8D

8.2P_0402_50V8D

1

2

2

Y1

Y1

12MHZ_7PF_FL120 0105

12MHZ_7PF_FL120 0105

3

C79

C79

1

2

8.2P_0402_50V8D

8.2P_0402_50V8D

1

2

1

1

1

1

LID_OPEN (24,29)

MIC_PRSNT# (23)

2

R28 100K_0402_5%@

R28 100K_0402_5%@

R30 100K_0402_5%@

R30 100K_0402_5%@

2

2

1

2

2

2

2

D

1

C64

C64

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

C67

C67

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

1

+1.8V_VDDIO_CPU

C65

C65

C68

C68

1

R32

R32

100K_0402_5%@

100K_0402_5%@

2

R33 0_0402_5%@

R33 0_0402_5%@

JTAG_TCK (24,29 )

JTAG_TMS (24,29)

JTAG_TRST# (24)

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

1

2

1

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M

2

+1.8V_VDDIO_CPU

R26

R26

1K_0402_5%

1K_0402_5%

1

1

2

2

+

1.8V_VDDIO_CPU

1

R27

R27

1K_0402_5%

1K_0402_5%

2

1

C74

C74

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

1

C77

C77

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

2

+1.00V_LP0_VDD_RTC

1

C69

C69

0.1U_0402_10V6K

0.1U_0402_10V6K

2

PWR_I2C_SCL (36)

PWR_I2C_SDA (36)

PMIC_WARM_RESET# (10,29,30)

+1.8V_RUN_VPP_FUSE

2

R36

R36

10K_0402_5%

10K_0402_5%

1

+1.8V_VDDIO_CPU

2

L1BLM15AX300SN1D_2P

L1BLM15AX300SN1D_2P

E

1

2

3

4

1.8V/ PU /ext PH 10K

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2013/11/20 2014/11/09

2013/11/20 2014/11/09

2013/11/20 2014/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SDMMC_ULPI_JTAG

SDMMC_ULPI_JTAG

SDMMC_ULPI_JTAG

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

Z3ENN M/B LA-B551P

E

0.1

0.1

0.1

of

8 42Thursday, June 19, 2014

of

8 42Thursday, June 19, 2014

of

8 42Thursday, June 19, 2014

1

2

3

+1.05V_RUN_AVDD_HDMI_PLL

SI2305CDS-T1-GE3_SOT23-3

SI2305CDS-T1-GE3_SOT23-3

Change Q2 P/N to SB923050030, 01/07

4

A

+

1.8V_VDDIO

+1.05V_RUN

+3.3V_RUN

+3.3V_LP0

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

Remove C96/C97 and put one test point, 12/23

+

1.8V_VDDIO_CPU

R

R

358

358

1

2

0_0805_5%

0_0805_5%

R

R

410

410

1

2

0_0805_5%

0_0805_5%

0612 modified.

+1.05V_RUN_CPU

R359

R359

1

2

0_0805_5%

0_0805_5%

R411

R411

1

2

0_0805_5%

0_0805_5%

0612 modified.

+3.3V_RUN_CPU

R360

R360

1

2

0_0603_5%

0_0603_5%

+3.3V_LP0_CPU

R361

R361

1

2

0.01_0603_1%

0.01_0603_1%

0612 modified.

+1.8V_VDDIO_CPU

1

C90

C90

0.1U_0402_10V6K

0.1U_0402_10V6K

2

TPM_I2C_SCL(21)

TPM_I2C_SDA(21)

R52 change to @, follow nV comment, 12/25

P-MOSFET TO POWER GATE AVDD_HDMI_PLL

1

1

D

D

Q2

Q2

A

2

G

G

2

1

D

D

Q4

Q4

@

@

DMG6968U-7_SOT23-3

DMG6968U-7_SOT23-3

S

S

3

3

S

S

1

R57

R57

1M_0402_5%

1M_0402_5%

2

R61 0_0402_5%@

2

G

G

SB00000Q800

SB00000Q800

VGTH(MAX)=0.9V

R61 0_0402_5%@

1

R55 0_0402_5%@

R55 0_0402_5%@

SB923050030

SB923050030

Change Q4@ to VGTH=0.9V, 01/08

1

C91

C91

2

T15 PAD @

T15 PAD @

Delete 3G interface, 12/19

1K_0402_1%

1K_0402_1%

+1.05V_RUN_CPU

1

2

B

A

K14

A

L13

A

L14

K9

A

A

L9

A

E9

D9

A

A

E11

A

D11

AK8

AL8

AJ9

AH9

AJ8

AH8

AF9

AG9

AK11

AL11

AD14

AE14

AL15

AK15

AG14

AF14

AJ14

AH14

AH12

AJ12

AE12

AD12

AL12

AK12

AF12

AG12

AJ11

AH11

AL10

AF11

AG11

AC11

AJ6

AL7

AK5

AK6

AH6

AH5

AL6

AJ5

AF8

AG8

AL5

AC15

AF18

AE18

AH18

AG18

AD18

HSIC_REXT

2

R52

R52

@

@

1

R60 0_0402_5%

R60 0_0402_5%

2

EN_VDD_HDMI (10,16,9)

B

1B

1B

U

U

BGA

BGA

(1.2V)

(1.2V)

VDD_DSI_CSI 1

A

VDD_DSI_CSI 2

A

A

VDD_DSI_CSI 3

SI_A_D0_N

C

C

SI_A_D0_P

C

SI_A_D1_N

SI_A_D1_P

C

C

SI_A_CLK_N

C

SI_A_CLK_P

CSI_B_D0_N

CSI_B_D0_P

CSI_B_D1_N

CSI_B_D1_P

CSI_E_CLK_N

CSI_E_CLK_P

CSI_E_D0_N

CSI_E_D0_P

DSI_A_D0_N

DSI_A_D0_P

DSI_A_D1_N

DSI_A_D1_P

DSI_A_D2_N

DSI_A_D2_P

DSI_A_D3_N

DSI_A_D3_P

DSI_A_CLK_N

DSI_A_CLK_P

DSI_B_D0_N

DSI_B_D0_P

DSI_B_D1_N

DSI_B_D1_P

DSI_B_D2_N

DSI_B_D2_P

DSI_B_D3_N

DSI_B_D3_P

DSI_B_CLK_N

DSI_B_CLK_P

CSI_DSI_TEST_OUT

CSI_DSI_RUP

CSI_DSI_RDN

(1.8V - 3.3V)

(1.8V - 3.3V)

VDDIO_CAM

GPIO_PCC1

GPIO_PCC2

GPIO_PBB0

GPIO_PBB3

GPIO_PBB4

GPIO_PBB5

GPIO_PBB6

GPIO_PBB7

CAM_I2C_SCL

CAM_I2C_SDA

CAM_MCLK

(1.2V)

(1.2V)

VDDIO_HSIC

HSIC1_DATA

HSIC_STROBE

HSIC_REXT

HSIC2_DATA

HSIC2_STROBE

+3.3V_AVDD_HDMI

GPIO_PH7 (10)

C

C

D580M

D580M

S

S

EC 2 OF 8

EC 2 OF 8

1

R56

R56

1M_0402_5%

1M_0402_5%

2

(3.3V)

(3.3V)

A

VDD_HDMI

A

A

VDD_HDMI

A

(1.05V.. 1.2V?)

(1.05V.. 1.2V?)

VDD_HDMI_PLL

A

HDMI_TXD0N

HDMI_TXD1N

HDMI_TXD2N

HDMI_PROBE

(1.05V)

(1.05V)

AVDD_LVDS0_IO

(1.05V)

(1.05V)

AVDD_PLL_UD2DPD

(1.8V)

(1.8V)

AVDD_LVDS0_PLL

LVDS0_TXD0N

LVDS0_TXD0P

LVDS0_TXD1N

LVDS0_TXD1P

LVDS0_TXD2N

LVDS0_TXD2P

LVDS0_TXD3N

LVDS0_TXD3P

LVDS0_TXD4N

LVDS0_TXD4P

LVDS0_PROBE

DP_AUX_CH0_P

DP_AUX_CH0_N

(1.8V)

(1.8V)

AVDD_PLL_UTMIP

(3.3V)

(3.3V)

USB_VBUS_EN0

USB_VBUS_EN1

AO3419L_SOT23-3

AO3419L_SOT23-3

SB000006R10

SB000006R10

S

S

3

Q1

Q1

HDMI_TXD0P

HDMI_TXD1P

HDMI_TXD2P

HDMI_TXCN

HDMI_TXCP

HDMI_CEC

HDMI_INT

HDMI_RSET

DDC_SCL

DDC_SDA

DP_HPD

LVDS0_RSET

AVDD_USB

USB0_DN

USB0_DP

USB1_DN

USB1_DP

USB2_DN

USB2_DP

USB0_VBUS

USB0_ID

USB_REXT

D

D

G

G

A

AD5

AD6

AD4

AD3

AD2

AD1

AF5

AF6

AD7

AC3

AF2

AE1

AC7

AC8

AJ1

AL4

AF1

AJ2

AJ3

AG3

AG4

AG5

AG6

AG1

AG2

AF3

AF4

AC2

AK3

AL3

AC6

AC5

AB15

AC12

AH20

AJ20

AF20

AG20

AE20

AD20

AB1

AC1

AL20

AK20

AL19

1

P-MOSFET TO PREVENT BACKDRIVE ON AVDD_HDMI

2

1

D

D

Q3

Q3

2

G

G

DMG6968U-7_SOT23-3

DMG6968U-7_SOT23-3

S

S

3

SB00000Q800

SB00000Q800

VGTH(MAX)=0.9V

Change Q3 to VGTH=0.9V, 01/08

C

3.3V_AVDD_HDMI

+

1

C

C

80

80

0.1U_0402_10V6K

0.1U_0402_10V6K

A9

A10

H1

HDMI_RSET

DDC_SCL

DDC_SDA

LVDS_RSET

USB0_VBUS

USB0_ID

USB_REXT

+3.3V_RUN_CPU

R58 0_0402_5%

R58 0_0402_5%

1

R59 0_0402_5%@

R59 0_0402_5%@

1

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

1

C

C

82

82

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

R46 1K_0402_1%

R46 1K_0402_1%

1

R47 33_0402_5%

R47 33_0402_5%

R48 33_0402_5%

R48 33_0402_5%

1

1

C86

C86

0.1U_0402_10V6K

0.1U_0402_10V6K

2

R49 1K_0402_1%

R49 1K_0402_1%

1

+1.8V_RUN_AVDD_PLL_UTMIP

USB0_D- (17)

USB0_D+ (1 7)

CAM_USB1_D- (14)

CAM_USB1_D+ (14)

USB2_D- (17)

USB2_D+ (1 7)

USB_VBUS_EN0 (1 7)

USB_VBUS_EN1 (1 7)

PAD@

PAD@

R54 1K_0402_1%

R54 1K_0402_1%

1

2

2

Issued Date

Issued Date

Issued Date

C

1

C

C

81

81

4.7U_0603_6.3V6M

4.7U_0603_6.3V6M