ZILOG Z86L88, Z86L86, Z86L81 Datasheet

FEATURES

PRELIMINARY

PRELIMINARY

CUSTOMER PROCUREMENT SPECIFICATION

Z86L88/L81/L86

INFRARED REMOTE CONTROLLERS

Z86L88/L81/L86

CP96LVO1201

ROM RAM* 28-pin

Part (KB) (Bytes) I/O DIP, SOIC

Z86L88 1 6 237 2 4 X

Z86L81 2 4 237 2 4 X

Z86L86 3 2 237 2 4 X

*General-Purpose

■ 2.0V to 3.9V Operating Range (8.0 MHz)

■ Three Standby Modes (Typical)

– STOP - 2 µA

– HALT - 0.8 mA

– Low-Voltage Standby (< VLV)

■ Expanded Register File Control Registers

■ Special Architecture to Automate Both Generation

and Reception of Complex Pulses or Signals:

– One Programmable 8-Bit Counter/Timer

with Two Capture Registers

– One Programmable 16-Bit Counter/Timer

with One Capture Register

– Programmable Input Glitch Filter

for Pulse Reception

■ Five Priority Interrupts

■ Low-Voltage Detection and Protection

■ Watch-Dog Timer (WDT)/Power-On Reset (POR)

■ Two Independent Comparators with Programmable

Interrupt Polarity

■ On-Chip Oscillator that Accepts a Crystal, Ceramic

Resonator, LC, or External Clock Drive

■ Mask Selectable 200 kOhms Pull-Ups on Ports 0, 2, 3

– All Eight Port 2 Bits at One Time or Not

– Pull-Ups Automatically Disabled Upon

Selecting Individual Pins as Outputs

■ Maskable 0.4 V

Through P03 for Direct Mouse/Trackball IR Sensor

Interface

■ Low-Voltage Standby Mode

Single Trip Point Inputs on P00

DD

GENERAL DESCRIPTION

The Z86L8X family of infrared (IR) consumer controller

processors are ROM-based members of the Z8® singlechip microcontroller family offering a unique register-toregister architecture that avoids accumulator bottlenecks

and offers fast execution of code.

Zilog's CMOS microcontrollers feature fast execution,

efficient use of memory, sophisticated interrupts, input/

output bit manipulation capabilities, automated pulse

generation/reception, and easy hardware/software system

expansion along with low-cost and low-power consumption.

CP96LVO1201 (6/96)

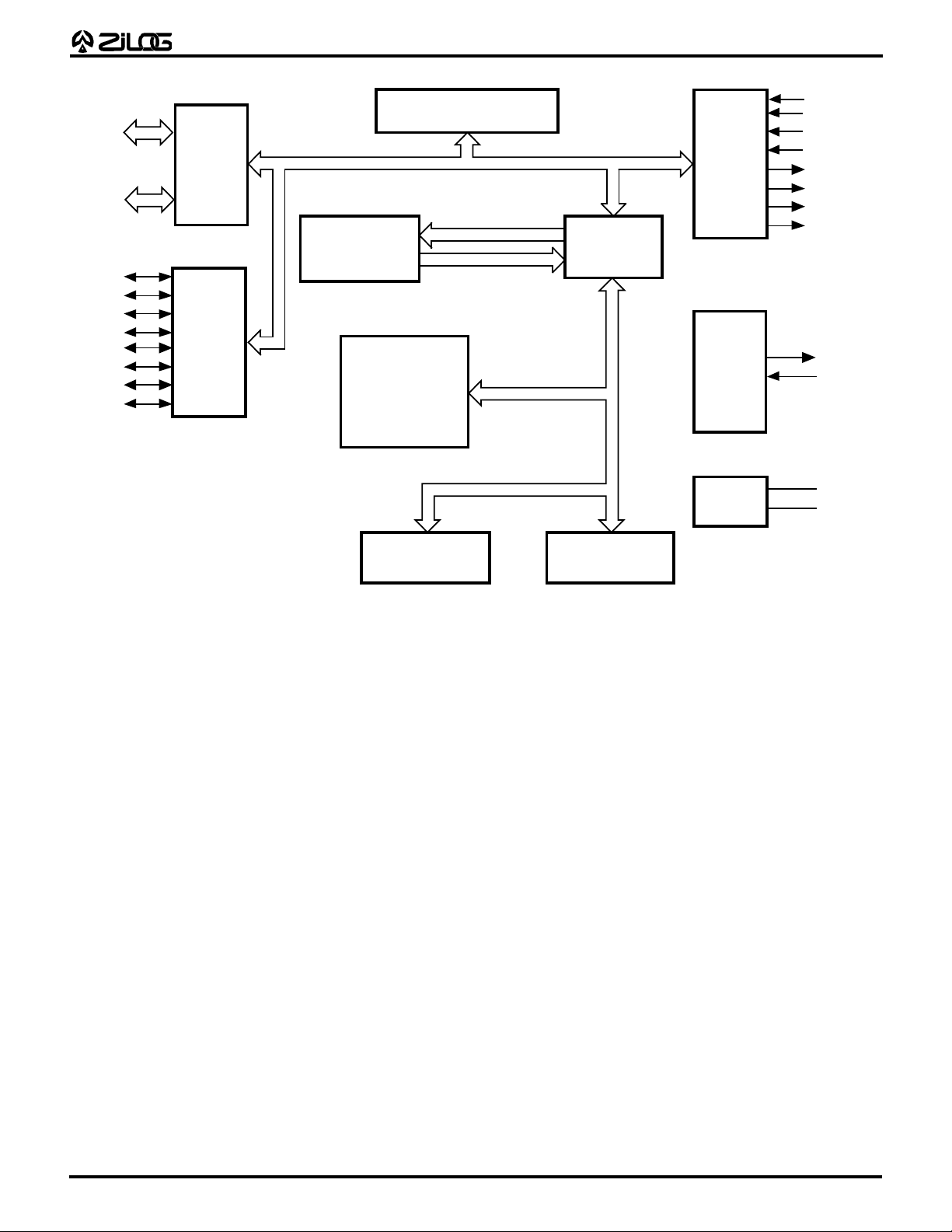

The Z86L8X family architecture is based on Zilog's 8-bit

microcontroller core with an Expanded Register File (ERF)

to allow access to register mapped peripherals, I/O circuits,

and powerful counter/timer circuitry. The Z86L8X offers a

flexible I/O scheme, an efficient register and address

space structure, and a number of ancillary features that

are useful in many consumer, automotive, computer

peripheral, and battery operated hand-held applications.

1

PRELIMINARY

GENERAL DESCRIPTION (Continued)

Z86L88/L81/L86

CP96LVO1201

For applications demanding powerful I/O capabilities, the

Z86L8X fulfills this with two package options in which 24

pins of dedicated input and output are grouped into three

ports. Each port consists of eight lines and is configurable

under software control to provide timing, status signals,

and parallel I/O.

There are three basic address spaces available to support

a wide range of configurations: Program Memory, Register

File, and Expanded Register File. (ERF). The Register File

is composed of 256 bytes of RAM. It includes four I/O port

registers, 15 control and status registers, and the rest are

general purpose registers. The ERF consists of two register groups (Banks D and F).

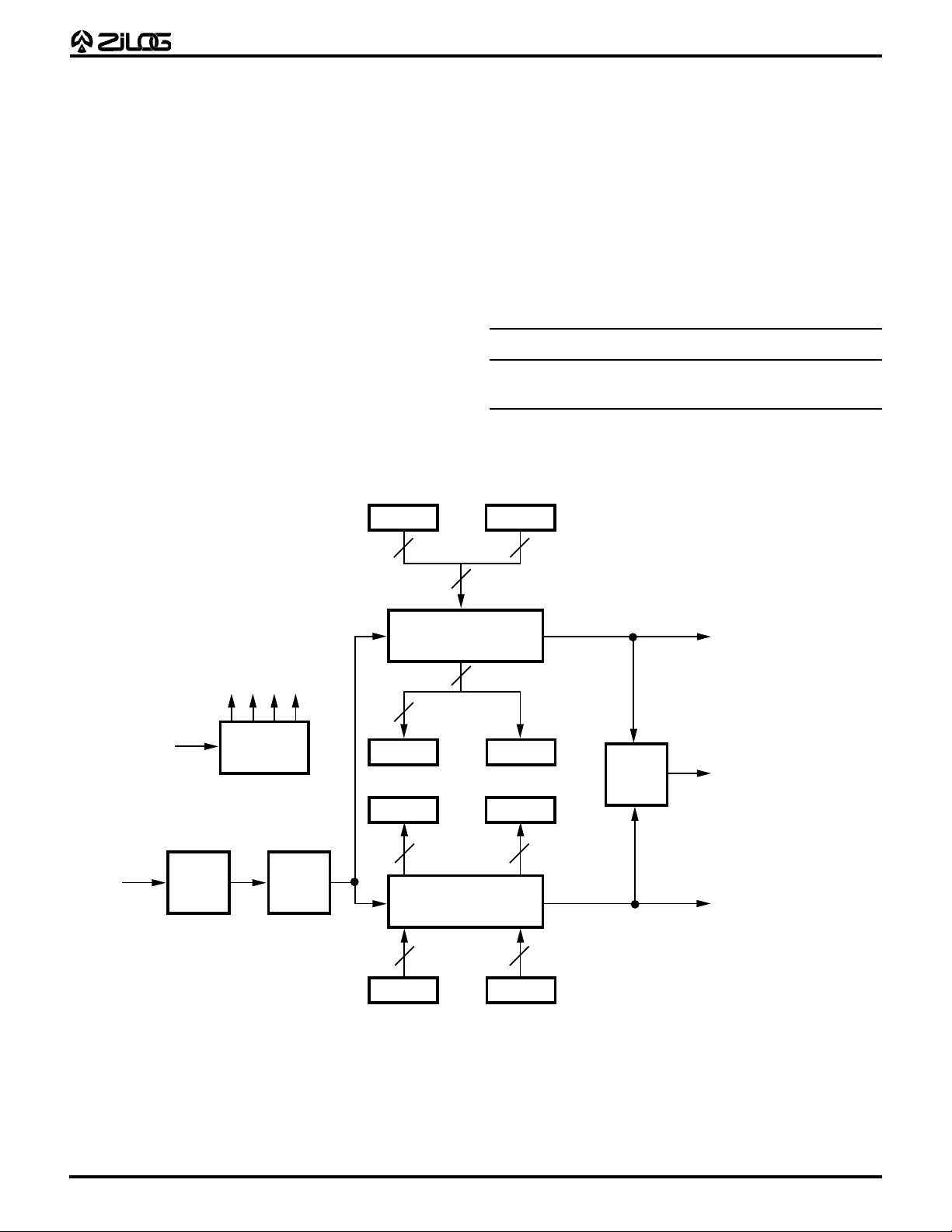

To unburden the program from coping with such real-time

problems as generating complex waveforms or receiving

HI16 LO16

8

and demodulating complex waveform/pulses, the Z86L8X

offers a new intelligent counter/timer architecture with 8-bit

and 16-bit counter/timers (Figure 1). Also included are a

large number of user-selectable modes, and two on-board

comparators to process analog signals with separate

reference voltages (Figure 2).

Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.,

B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

Connection Circuit Device

Power V

Ground GND V

8

CC

V

DD

SS

Input

SCLK

Glitch

Filter

1248

Clock

Divider

Edge

Detect

Circuit

16

16-Bit

T16

16

8

TC16H TC16L

HI8 LO8

8

8-Bit

T8

8

TC8H TC8L

Timer 16

And/Or

Logic

8

8

Timer 8/16

Timer 8

Figure 1. Counter/Timer Block Diagram

2

PRELIMINARY

Z86L88/L81/L86

CP96LVO1201

P00

P01

P02

P03

P04

P05

P06

P07

P20

P21

P22

P23

P24

P25

P26

P27

Port 0

Port 2

Register Bus

ROM

8K/4K x 8

Extended

Register

Counter/Timer 8

Register File

256 x 8-Bit

Internal Data Bus

File

8-Bit

Internal

Address Bus

Extended

Register Bus

Z8 Core

Counter/Timer 16

16-Bit

Port 3

Machine

Timing

&

Instruction

Control

Power

Pref1

P31

P32

P33

P34

P35

P36

P37

XTAL

VDD

VSS

Figure 2. Functional Block Diagram

3

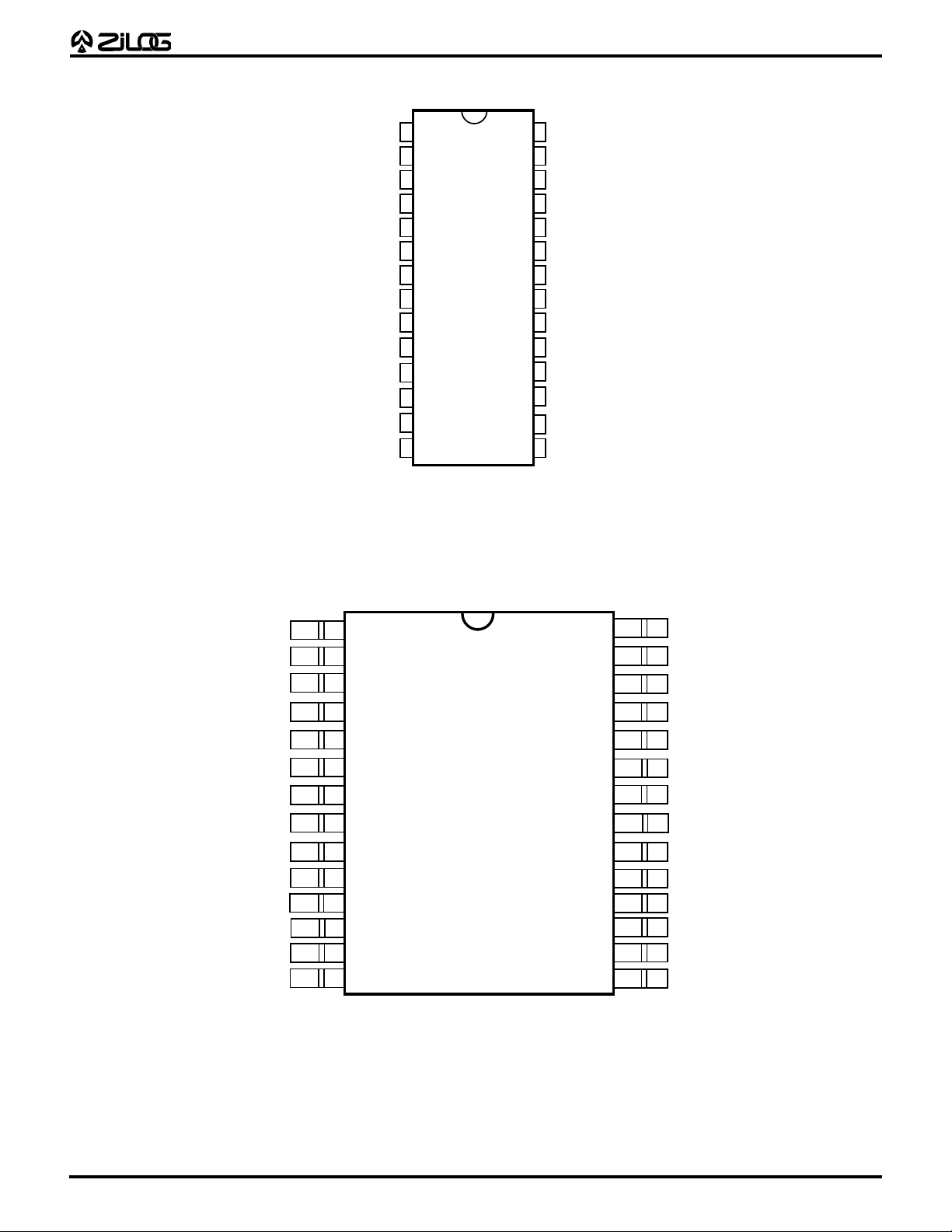

PIN DESCRIPTION

PRELIMINARY

Z86L88/L81/L86

CP96LVO1201

P25

P26

P27

P04

P05

P06

P07

VDD

XTAL2

XTAL1

P31

P32

P33

P34

1

2

3

4

5

6

7

8

9

10

11

12

13

Z86L88/

L81/L86

DIP

28

27

26

25

24

23

22

21

20

19

18

17

16

1514

Figure 3. 28-Pin DIP

Pin Assignments

P24

P23

P22

P21

P20

P03

VSS

P02

P01

P00

PREF1

P36

P37

P35

P25

P26

P27

P04

P05

P06

P07

VDD

XTAL2

XTAL1

P31

P32

P33

P34

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Z86L88/L81/L86

SOIC

Figure 4. 28-Pin SOIC

Pin Assignments

28

27

26

25

24

23

22

21

20

19

18

17

16

15

P24

P23

P22

P21

P20

P03

VSS

P02

P01

P00

PREF1

P36

P37

P35

4

Loading...

Loading...