ZILOG Z86E7216FSC, Z86E7316FSC, Z86E7316PSC, Z86E7316VSC, Z86E7216PSC Datasheet

...

1

P

RELIMINARY

P

RODUCT

S

PECIFICATION

FEATURES

ROM

Par t

Z86E73 32 256 31 3.0V to 5.5V

Z86E72 16 768 31 3.0V to 5.5V

Note: *General-Purpose

■

Low Power Consumption - 60 mW (Typical)

■

Two Standby Modes (Typical)

– STOP - 2 µ A

– HALT - 0.8 mA

■

Special Architecture to Automate Both Generation and

Reception of Complex Pulses or Signals:

– One Programmable 8-Bit Counter/Timer with Two

– One Programmable 16-Bit Counter/Timer with

– Programmable Input Glitch Filter for Pulse

(KB)

Capture Registers

One Capture Register

Reception

RAM*

(Bytes) I/O

Voltage

Range

Z86E72/73

OTP IR M

■

Five Priority Interrupts

– Three External

– Two Assigned to Counter/Timers

■

Two Independent Comparators with Programmable

Interrupt Polarity

■

On-Chip Oscillator that Accepts a Crystal, Ceramic

Resonator, LC, RC (mask option), or External Clock

Drive

■

Software Selectable 200 kOhms Pull-Ups on Ports 0 and

Port 2

– All Eight Port 2 Bits at One Time or Not Pull-Ups

Automatically Disabled Upon Selecting Individual

Pins as Outputs.

■

Software Mouse/Trackball Interface on P00 Through

P03

ICROCONTROLLERS

1

GENERAL DESCRIPTION

The Z86E7X family of IR (Infrared) CCP

troller Processor) are OTP-based members of the Z8

gle-chip microcontroller family with 256 or 768 bytes of

general-purpose RAM. The only differentiating factor between the E72/73 versions is the availability of RAM and

ROM. This EPROM Microcontroller family of OTP IR controllers also offer the use of external memory which enables this Z8 microcontroller to be used where code flexibility is required. Zilog's CMOS microcontrollers offer fast

execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, automated

pulse generation/reception, and easy hardware/software

system expansion along with cost-effective and low power

consumption.

DS96LVO1100

™

(Consumer Con-

®

P R E L I M I N A R Y

sin-

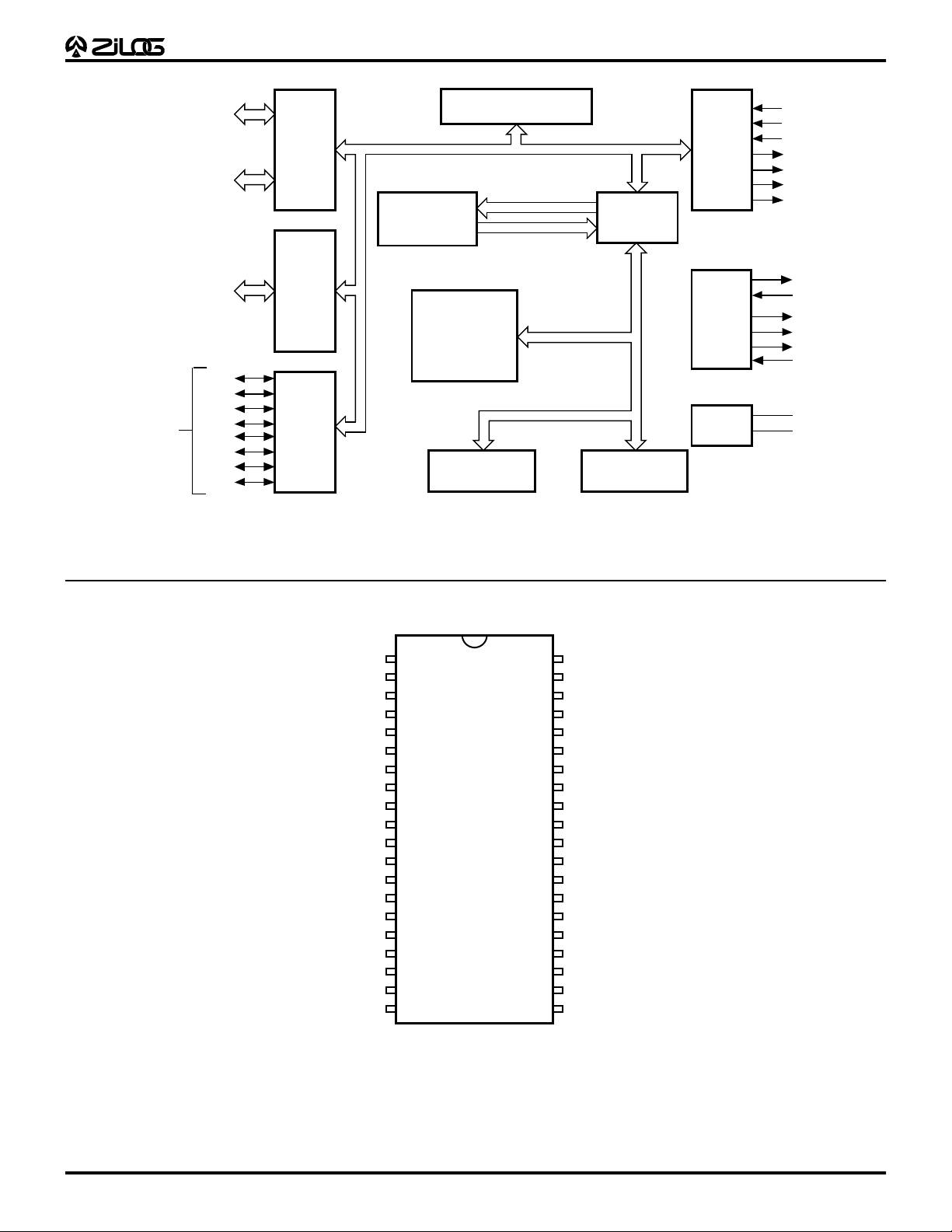

The Z86E7X architecture is based on Zilog's 8-bit microcontroller core with an Expanded Register File to allow access to register mapped peripherals, I/O circuits, and powerful counter/timer circuitry. The CCP offers a flexible I/O

scheme, an efficient register and address space structure,

and a number of ancillary features that are useful in many

consumer, automotive, computer peripheral, and battery

operated hand-held applications.

™

CCP

applications demand powerful I/O capabilities. The

Z86L7X family fulfills this with five package options in

which the E72/73/L74 versions provide 31 pins of dedicated input and output. These lines are grouped into four

ports. Each port consists of eight lines (Port 3 has seven

lines of I/O and one Pref comparator input) and is config-

1-1

Z86E72/E73

OTP IR Microcontrollers

GENERAL DESCRIPTION (Continued)

urable under software control to provide timing, status signals, parallel I/O with or without handshake, and an address/data bus for interfacing external memory.

There are five basic address spaces available to support a

wide range of configurations: Program Memory, Register

FIle, Expanded Register File, Extended Data RAM and External Memory. The register file is composed of 256 bytes

of RAM. It includes four I/O port registers, 16 control and

status registers and the rest are General Purpose registers. The Extended Data RAM adds 512 (E72) of usable

general-purpose registers. The Expanded Register File

consists of two additional register groups (F and D).

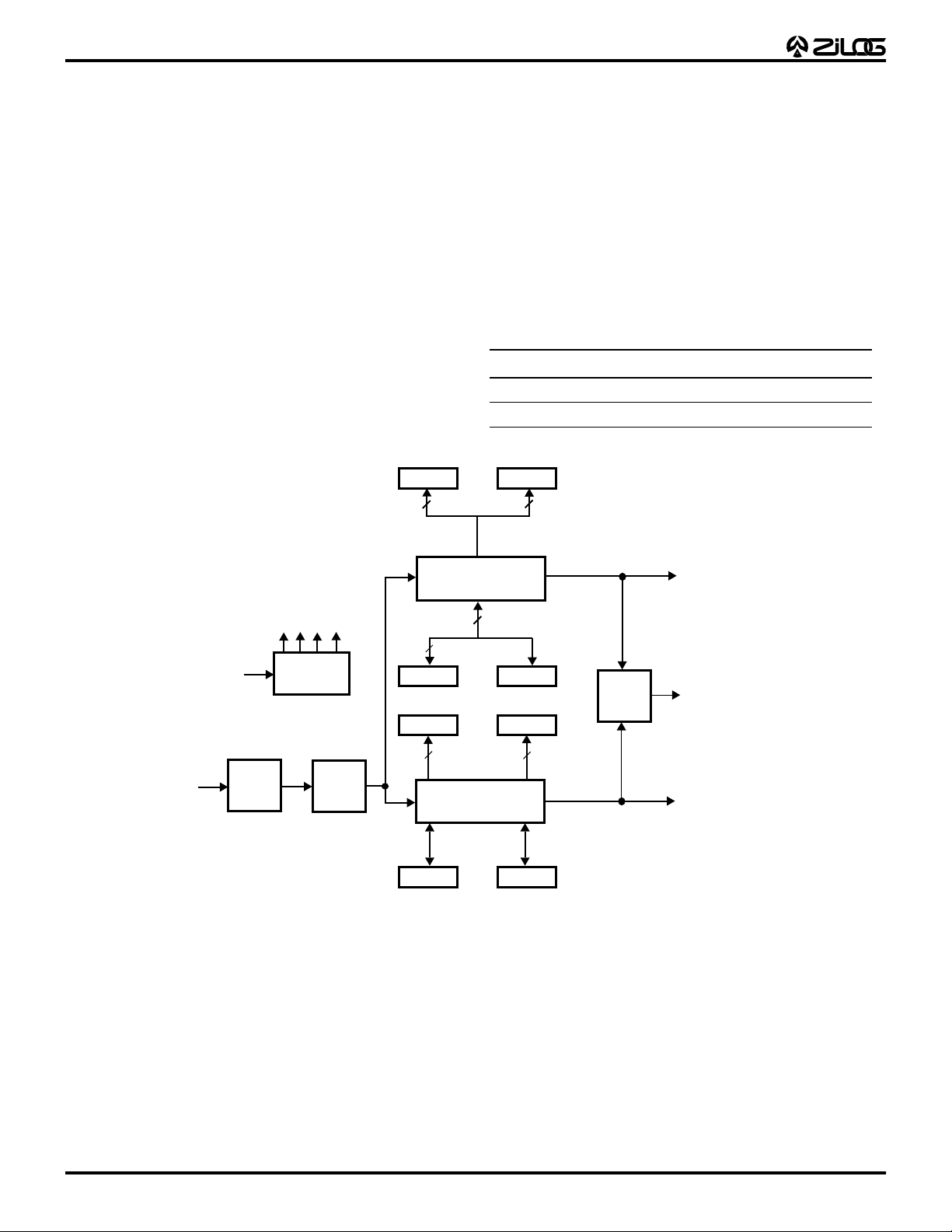

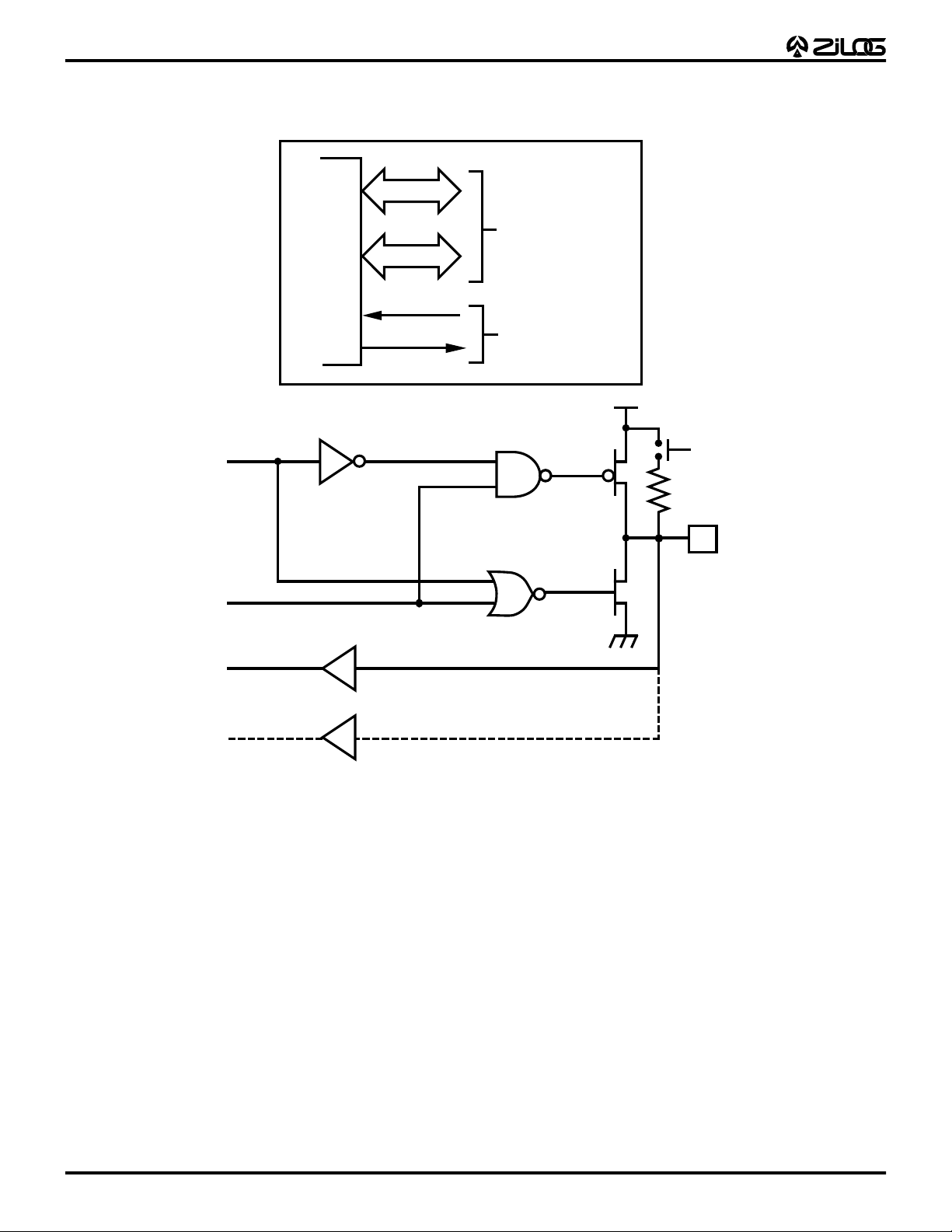

To unburden the program from coping with such real-time

problems as generating complex waveforms or receiving

and demodulating complex waveform/pulses, the Z86E7X

HI16

8

family offers a new intelligent counter/timer architecture

with 8-bit and 16-bit counter/timers (Figure 1). Also included are a large number of user-selectable modes, and two

on-board comparators to process analog signals with separate reference voltages (Figure 2).

Notes: All Signals with a preceding front slash, "/", are ac-

tive Low, e.g., B//W (WORD is active Low); /B/W (BYTE is

active Low, only).

Power connections follow conventional descriptions below:

Connection Circuit Device

16-Bit

T16

Power V

CC

Ground GND V

LO16

8

Timer 16

V

DD

SS

Input

SCLK

Glitch

Filter

2

48

1

Clock

Divider

8

TC16H

HI8 LO8

8

Edge

Detect

Circuit

TC8H

16

8

TC16L

8

8-Bit

T8

8

8

TC8L

Figure 1. Z86E7X Counter/Timer Block Diagram

And/Or

Logic

Timer 8/16

Timer 8

1-2

P R E L I M I N A R Y

DS96LVO1100

1

Z86E72/E73

OTP IR Microcontrollers

I/O Bit

Programmable

P00

P01

P02

P03

P04

P05

P06

P07

P10

P11

P12

P13

P14

P15

P16

P17

P20

P21

P22

P23

P24

P25

P26

P27

Register File

4

Port 0

4

8

Port 1

Port 2

Register Bus

ROM

16K/32K x 8

256 or 768 x 8-Bit

Address Bus

Internal Data Bus

Expanded

Register

File

Counter/Timer 8

8-Bit

Internal

Expanded

Register Bus

Counter/Timer 16

Port 3

Z8 Core

Machine

Timing

&

Instruction

Control

Power

16-Bit

P31

P32

P33

P34

P35

P36

P37

XTAL

/AS

/DS

R/W

/RESET

VDD

VSS

PIN DESCRIPTION

Figure 2. Z86E7X Functional Block Diagram

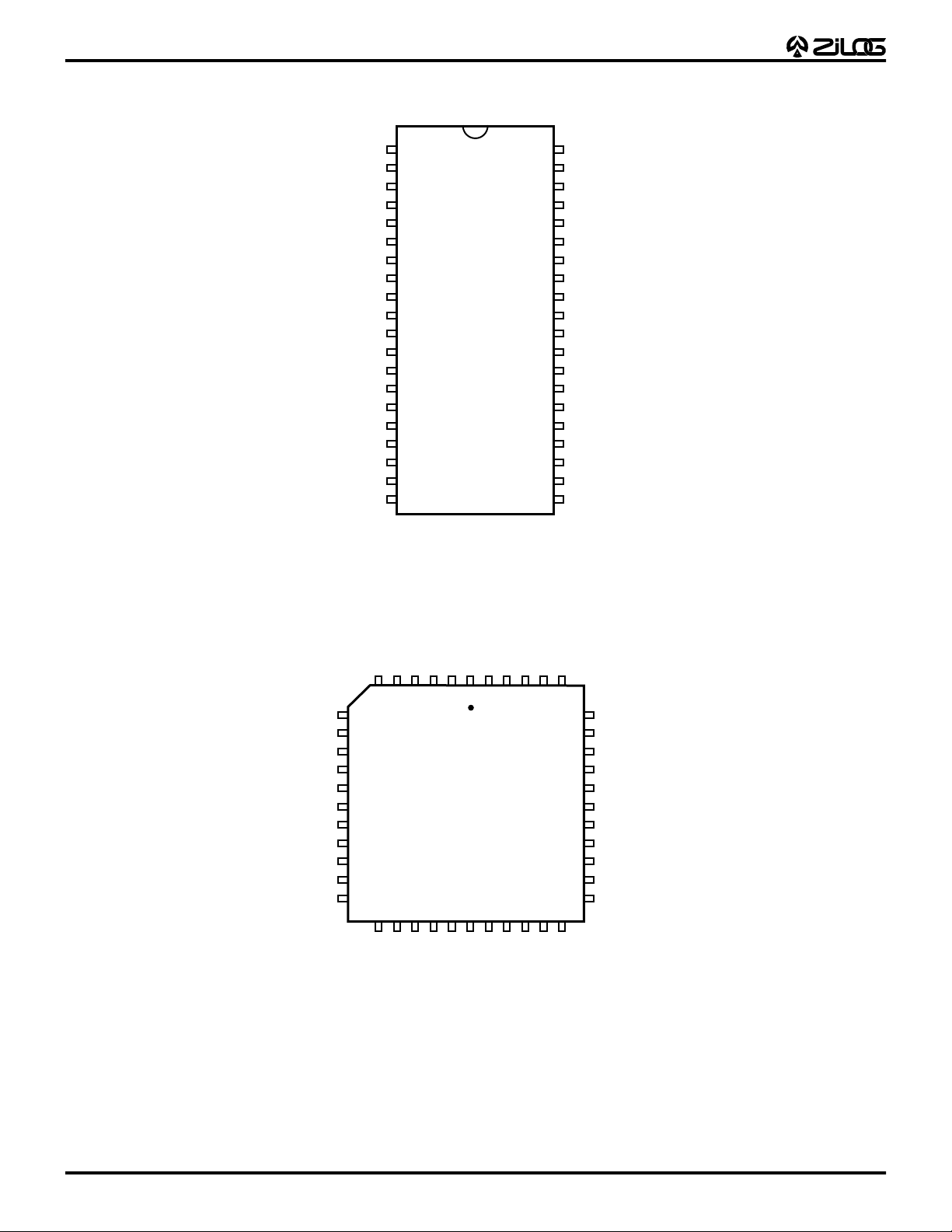

R//W

P25

P26

P27

P04

P05

P06

P14

P15

P07

VDD

P16

P17

XTAL2

XTAL1

P31

P32

P33

P34

/AS

1

2

3

4

5

6

7

8

Z86E72/73

9

10

DIP

11

12

13

14

15

16

17

18

19

20 21

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

/DS

P24

P23

P22

P21

P20

P03

P13

P12

VSS

P02

P11

P10

P01

P00

Pref1

P36

P37

P35

/RESET

DS96LVO1100

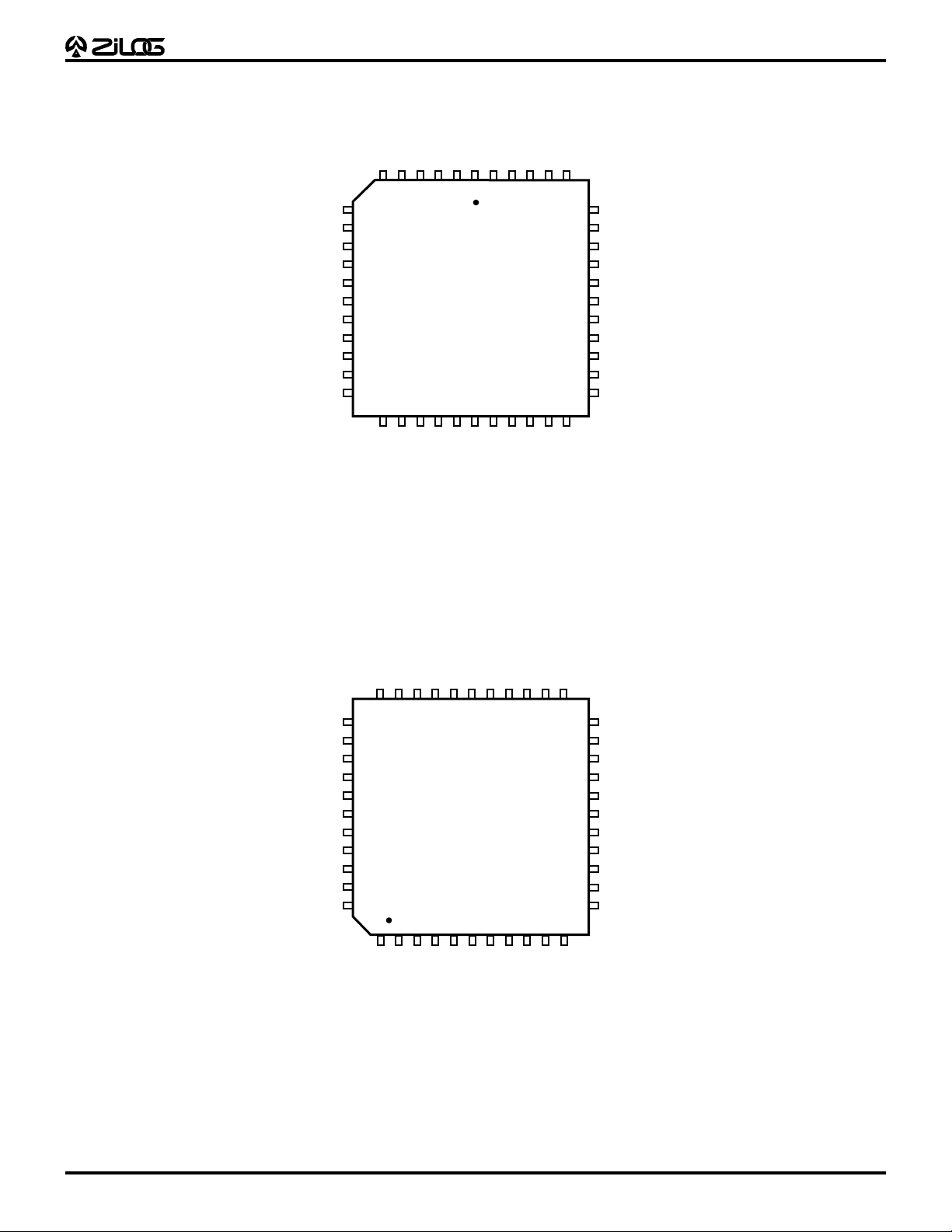

Figure 3. 40-Pin DIP Pin Assignments (Standard Mode)

P R E L I M I N A R Y

1-3

Z86E72/E73

OTP IR Microcontrollers

PIN DESCRIPTION (Continued)

NC

A13

A14

/PGM

A4

A5

A6

D4

D5

A7

VDD

D6

D7

NC

NC

/OE

EPM

VPP

NC

NC

1

2

3

4

5

6

7

8

9

Z86E72/73

10

11

12

13

14

15

16

17

18

19

20 21

DIP

40

39

38

37

36

35

34

33

31

30

29

28

27

26

25

24

23

22

32

NC

A12

A11

A10

A9

A8

A3

D3

D2

VSS

A2

D1

D0

A1

A0

/CE

NC

NC

NC

NC

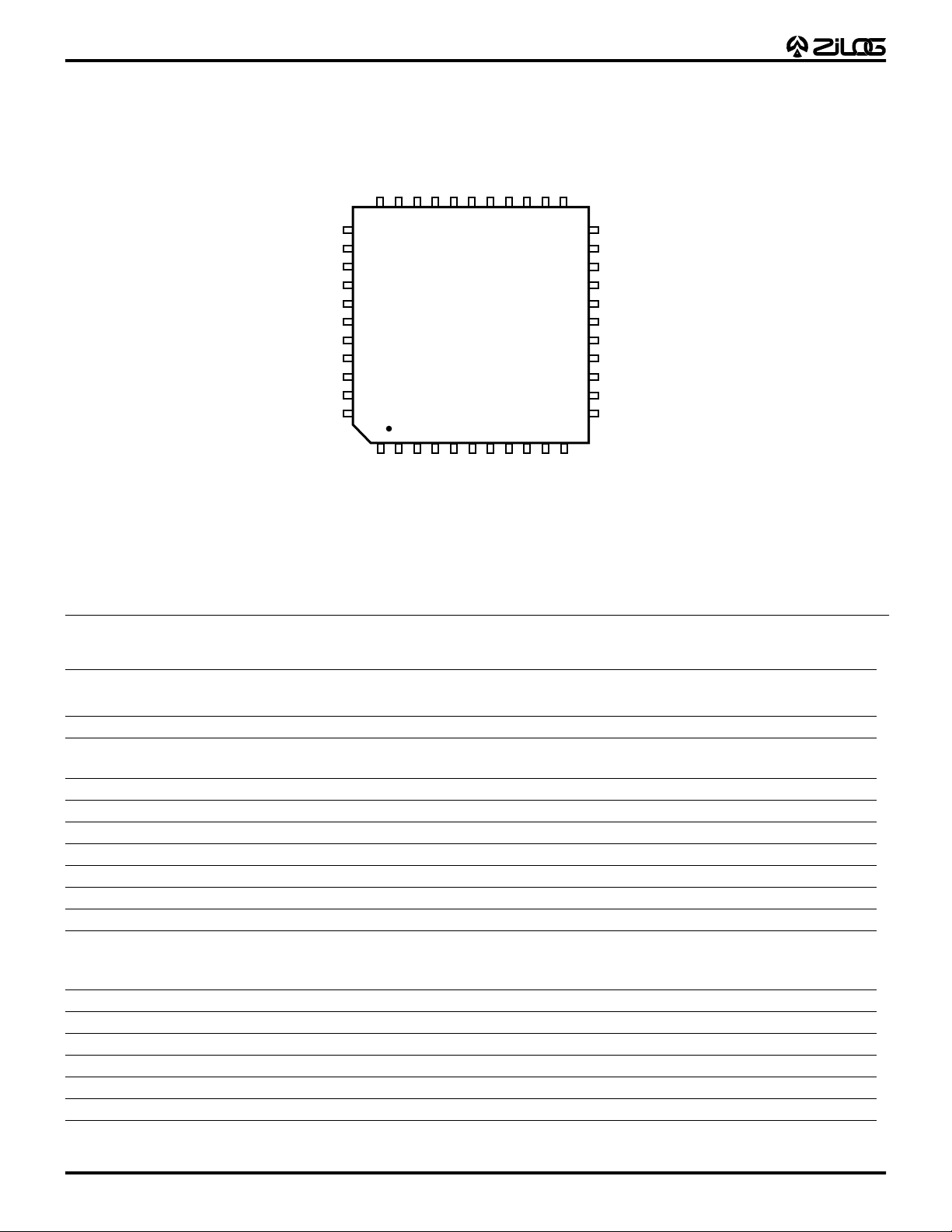

Figure 4. 40-Pin DIP Pin Assignments (EPROM Mode)

P20

P03

P13

P12

VSS

VSS

P02

P11

P10

P01

P00

VDD

VDD

42

P16

P17

406

2818

XTAL2

39

38

37

36

35

34

33

32

31

30

29

XTAL1

Pref1

P36

P37

P35

/RESET

VSS

/AS

P34

P33

P32

P31

P21

P22

P23

P24

/DS

R//RL

R//W

P25

P26

P27

P04

7

8

9

10

11

12

13

14

15

16

17

4

1

Z86E72/73

PLCC

20 22 24 26

P05

P06

P14

P15

P07

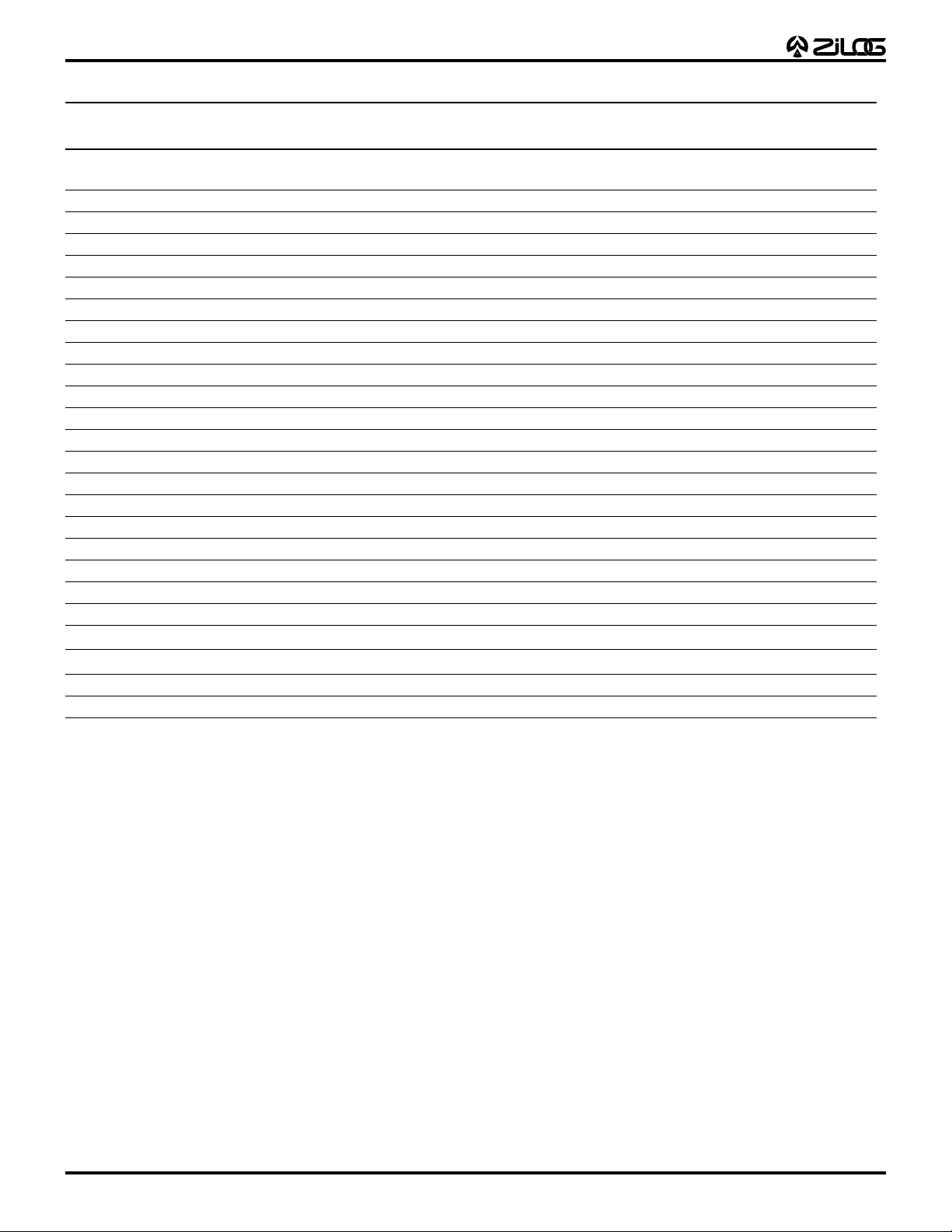

Figure 5. 44-Pin PLCC Pin Assignments (Standard Mode)

1-4

P R E L I M I N A R Y

DS96LVO1100

1

Z86E72/E73

OTP IR Microcontrollers

A9

A10

A11

A12

NC

NC

NC

A13

A14

/PGM

A4

A8A3D3D2VSS

4

7

8

9

10

11

12

13

14

15

16

17

20 22 24 26

P05

P06

P14

VSSA2D1D0A2

1

Z86E72/73

PLCC

P15

P07

VDD

VDD

42

P16

P17

406

2818

XTAL2

A0

39

38

37

36

35

34

33

32

31

30

29

XTAL1

/CE

NC

NC

NC

NC

SCC

NC

NC

VPP

EPM

/OE

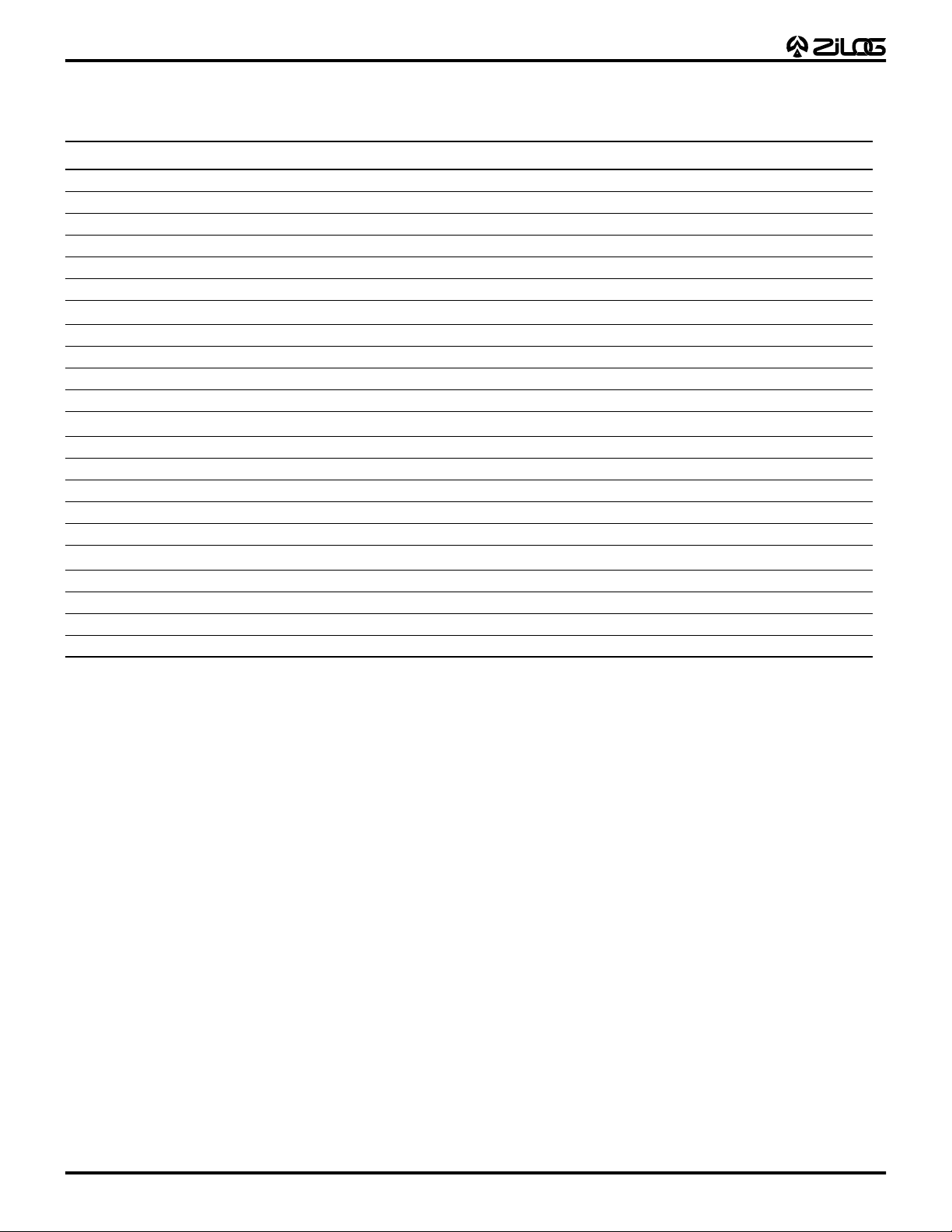

Figure 6. 44-Pin PLCC Pin Assignments (EPROM Mode)

P20

P03

P13

P12

VSS

VSS

P02

P11

P10

P01

P00

P21

P22

P23

P24

/DS

R//RL

R//W

P25

P26

P27

P04

34

35

36

37

38

39

40

41

42

43

44

1

P05

31

Z86E72/73

3

P06

P14

29

5

P15

QFP

P07

7

VDD

VDD

2527

9

P16

P17

2333

11

XTAL2

22

21

20

19

18

17

16

15

14

13

12

XTAL1

Pref1

P36

P37

P35

/RESET

VSS

/AS

P34

P33

P32

P31

Figure 7. 44-Pin QFP Pin Assignments (Standard Mode)

DS96LVO1100

P R E L I M I N A R Y

1-5

Z86E72/E73

OTP IR Microcontrollers

PIN DESCRIPTION (Continued)

A9

A10

A11

A12

N/C

N/C

N/C

A13

A14

/PGM

A4

A8A3D3D2VSS

31

33

34

35

36

37

38

39

40

41

42

43

44

1

3

A5

A6

D4

VSSA2D1D0A1

29 27 25

Z86E72/73

QFP

579

A7

D5

VDD

VDD

D6

D7

23

12

11

XTAL2

A0

22

21

20

19

18

17

16

15

14

13

XTAL1

/CE

N/C

N/C

N/C

N/C

VSS

N/C

N/C

VPP

EPM

/OE

Figure 8. 44-Pin QFP Pin Assignments (EPROM Mode)

Table 1. Pin Identification (Standard Mode)

40-Pin

DIP #

44-Pin

PLCC #

44-Pin

QFP # Symbol Direction Description

26 40 23 P00 Input/Output Port 0 is Nibble Programmable.

27 41 24 P01 Input/Output Port 0 can be configured as A15-A8

external program

30 44 27 P02 Input/Output

34 5 32 P03 Input/Output ROM Address Bus.

5 17 44 P04 Input/Output Port 0 can be configured as a

6 18 1 P05 Input/Output mouse/trackball input.

7 19 2 P06 Input/Output

10 22 5 P07 Input/Output

28 42 25 P10 Input/Output Port 1 is byte programmable.

29 43 26 P11 Input/Output Port 1 can be configured as multiplexed

A7-A0/D7-D0 external program ROM

Address/Data Bus

32 3 30 P12 Input/Output

33 4 31 P13 Input/Output

8 20 3 P14 Input/Output .

9 21 4 P15 Input/Output

12 25 8 P16 Input/Output

13 26 9 P17 Input/Output

1-6

P R E L I M I N A R Y

DS96LVO1100

Z86E72/E73

OTP IR Microcontrollers

Table 1. Pin Identification (Standard Mode)

40-Pin

DIP #

44-Pin

PLCC #

44-Pin

QFP # Symbol Direction Description

35 6 33 P20 Input/Output Port 2 pins are individually configurable

as input or output

36 7 34 P21 Input/Output

37 8 35 P22 Input/Output

38 9 36 P23 Input/Output

39 10 37 P24 Input/Output

2 14 41 P25 Input/Output

3 15 42 P26 Input/Output

4 16 43 P27 Input/Output

16 29 12 P31 Input IRQ2/Modulator input

17 30 13 P32 Input IRQ0

18 31 14 P33 Input IRQ1

19 32 15 P34 Output T8 output

22 36 19 P35 Output T16 output

24 38 21 P36 Output T8/T16 output

23 37 20 P37 Output

20 33 16 /AS Output Address Strobe

40 11 38 /DS Output Data Strobe

1 13 40 R//W Output Read/Write

21 35 18 /RESET Input Reset

15 28 11 XTAL1 Input Crystal, Oscillator Clock

14 27 10 XTAL2 Output Crystal, Oscillator Clock

11 23, 24 6, 7 V

31 1, 2, 34 17, 28, 29 V

DD

SS

Power Supply

Ground

25 39 22 Pref1 Input Comparator 1 Reference

NC 12 39 R//RL Input ROM//ROMless

1-7

P R E L I M I N A R Y

DS96LVO1100

Z86E72/E73

OTP IR Microcontrollers

PIN DESCRIPTION (Continued)

Table 2. Z86E72/73 40-Pin DIP Identification (EPROM Mode)

40-Pin # Symbol Function Direction

1 N/C Not Connected

2-3 A13-14 Address 13,14 Input

4 /PGM Program Mode Input

5-7 A4-A6 Address 4,5,6 Input

8-9 D4-D5 Data 4,5 Input/Output

10 A7 Address 7 Input

11 V

12-13 D6-D7 Data 6,7 Input/Output

14-15 N/C Not Connected

16 /OE Output Enable Input

17 EPM EPROM Prog.Mode Input

18 V

19-24 N/C Not Connected

25 /CE Chip Enable Input

26-27 A0-A1 Address 0,1 Input

28-29 D0-D1 Data 0, 1 Input/Output

30 A2 Address 2 Input

31 V

32-33 D2-D3 Data 2,3 Input/Output

34 A3 Address 3 Input

35-39 A8-A12 Address 8,9,10,11,12 Input

40 N/C Not Connected

DD

PP

SS

Power Supply

Prog. Voltage Input

Ground

1-8

P R E L I M I N A R Y

DS96LVO1100

1

OTP IR Microcontrollers

Table 3. Z86E72/73 44-Pin QFP/PLCC Pin Identification(EPROM Mode)

Z86E72/E73

44-Pin

QFP

1-2 18-19 A5-A6 Address 5,6 Input

3-4 20-21 D4-D5 Data 4,5 Input/Output

5 22 A7 Address 7 Input

6-7 23-24 V

8-9 25-26 D6-D7 Data 6,7 Input/Output

10 27 XTAL2 Crystal Oscillator Clock

11 28 XTAL1 Crystal Oscillator Clock

12 29 /OE Output Enable Input

13 30 EPM EPROM Prog. Mode Input

14 31 V

15-16 32-33 N/C Not Connected

17 34 V

18-21 35-38 N/C Not Connected

22 39 /CE Chip Select Input

23-24 40-41 A0-A1 Address 0,1 Input

25-26 42-43 D0-D1 Data 0,1 Input/Output

27 44 A2 Address 2 Input

28-29 1-2 V

30-31 3-4 D2-D3 Data 2, 3 Input/Output

32 5 A3 Address 3 Input

33-37 6-10 A8-A12 Address 8,9,10,11,12 Input

38-40 11-13 N/C Not Connected

41-42 14-15 A13-A14 Address 13,14 Input

43 16 /PGM Prog. Mode Input

44 17 A4 Address 4 Input

44-Pin

PLCC Symbol Function Direction

DD

PP

SS

SS

Power Supply

Prog. Voltage Input

Ground

Ground

DS96LVO1100

P R E L I M I N A R Y

1-9

Z86E72/E73

OTP IR Microcontrollers

ABSOLUTE MAXIMUM RATINGS

Symbol Description Min Max Units

V

T

Notes:

* Voltage on all pins with respect to GND.

† See Ordering Information.

Supply V oltage (*) –0.3 +7.0 V

CC

Storage Temp. –65 ° +150 ° C

STG

T

Oper. Ambient Temp. † C

A

STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test

conditions as noted. All voltages are referenced to GND.

Positive current flows into the referenced pin (Figure 13).

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at

any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period

may affect device reliability.

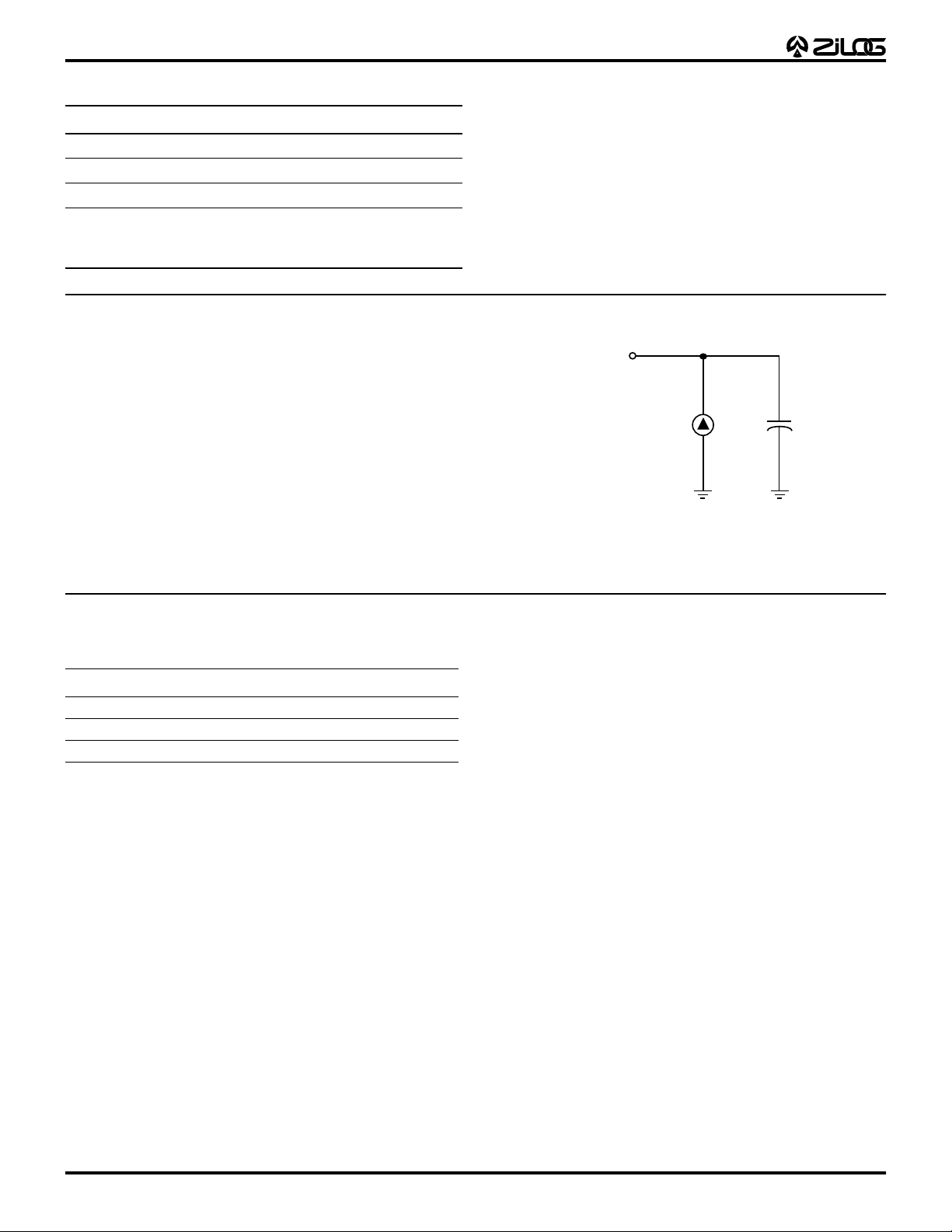

From Output

Under Test

150 pFI

Figure 9. Test Load Diagram

CAPACITANCE

T

= 25 ° C, V

A

Input capacitance 12 pF

Output capacitance 12 pF

I/O capacitance 12 pF

= GND = 0V, f = 1.0 MHz, unmeasured pins returned to GND.

CC

Parameter Max

1-10

P R E L I M I N A R Y

DS96LVO1100

1

DC CHARACTERISTICS

Preliminary

Z86E72/E73

OTP IR Microcontrollers

Sym. Parameter

Max Input Voltage 3.0V

V

Clock Input

CH

High V oltage

Clock Input

V

CL

Low V oltage

Input High Voltage 3.0V

V

IH

Input Low Voltage 3.0V

V

IL

V

V

Output High Voltage 3.0V

OH1

Output High Voltage

OH2

(P00,P01,P36, P37)

V

V

V

Output Low Voltage 3.0V

OL1

Output Low Voltage 3.0V

OL2*

Output Low Voltage

OL2

(P00, P01, P36,P37)

V

Reset Input

RH

High V oltage

Reset Input

V

Rl

Low V oltage

V

OFFSET

Comparator Input

Offset V oltage

I

Input Leakage 3.0V

IL

I

Output Leakage 3.0V

OL

I

Reset Input Current 3.0V

IR

I

Supply Current

CC

(WDT off)

V

CC

5.5V

3.0V

5.5V

3.0V

5.5V

5.5V

5.5V

5.5V

3.0V

5.5V

5.5V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

5.5V

5.5V

5.5V

3.0V

5.5V

= 0°C to +70°C

T

A

Typical

Min Max @ 25°C Units Conditions

0.9 V

CC

0.9 V

CC

VSS –0.3

V

–0.3

SS

0.7 V

CC

0.7 V

CC

VSS –0.3

V

–0.3

SS

VCC –0.4

V

–0.4

CC

VCC 0.7

V

0.7

CC

0.8 V

CC

0.8 V

CC

VSS –0.3

V

–0.3

SS

–1

–1

–1

–1

7

7

VCC + 0.3

V

+ 0.3

CC

0.2 V

CC

0.2 V

CC

VCC + 0.3

V

+ 0.3

CC

0.2 V

CC

0.2 V

CC

0.4

0.4

0.8

0.8

0.8

0.8

V

CC

V

CC

0.2 V

CC

0.2 V

CC

25

25

1

1

1

1

–230

–400

10

15

0.5 V

0.5 V

0.5 V

0.5 V

2.9

5.4

0.1

0.2

0.5

0.3

0.3

0.2

1.5

2.5

0.9

1.8

10

10

< 1

< 1

< 1

< 1

–50

–80

4

10

CC

CC

CC

CC

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

mV

mV

µA

µA

µA

µA

µA

µA

mA

mA

IIN 250 µA

I

250 µA

IN

Driven by External

Clock Generator

Driven by External

Clock Generator

= –0.5 mA

I

OH

I

= –0.5 mA

OH

= –7 mA

I

OH

I

= –7 mA

OH

IOL = 1.0 mA

I

= 4.0 mA

OL

IOL = 5.0 mA

I

= 7.0 mA

OL

IOL = 10 mA

I

= 10 mA

OL

VIN = 0V, V

VIN = 0V, V

VIN = 0V, V

VIN = 0V, V

@ 8.0 MHz

@ 8.0 MHz

CC

CC

CC

CC

DS96LVO1100

P R E L I M I N A R Y

1-11

Z86E72/E73

OTP IR Microcontrollers

DC CHARACTERISTICS (Continued)

Sym. Parameter

I

CC1

Standby Current

(WDT Off)

I

CC2

T

Standby Current 3.0V

Power-On Reset 3.0V

POR

Vram Static RAM Data

Retention V oltage

V

LV

(Vbo)

Notes:

Low Voltage

V

CC

Protection

I

CC1

Crystal/Resonator

3.0V

TA = 0°C to +70°C

V

CC

Min Max @ 25°C Units Conditions Notes

3

Typical

1

mAmAHALT Mode

VIN = 0V, V

CC

1,2

@ 8.0

MHz

5.5V

5

4

HALT Mode

V

= 0V, V

IN

CC

1,2

@ 8.0 MHz

3.0V

2

0.8

mAmAClock Divide-by-16 @

1,2

8.0 MHz

5.5V

4

2.5

Clock Divide-by-16 @

1,2

8.0 MHz

8

2

µAµASTOP Mode

VIN = OV, V

CC

3,5

WDT is not Running

STOP Mode

5.5V

10

3

VIN = 0V, V

CC

3,5

WDT is not Running

3.0V

5.5V

500

800

310

600

µAµASTOP Mode

VIN = 0V, V

3,5

CC

WDT is Running

5.5V

12

5

75

20

18

ms

7

ms

Vram 0.8 0.5 V 6

2.15 1.7 V 8 MHz max

Ext. CLK Freq.

Typ

3.0 mA

Max

5

Unit

mA

Frequency

8.0 MHz

4

External Clock Drive

1. All outputs unloaded, inputs at rail.

2. CL1 = CL2 = 100 pF

3. Same as note [4] except inputs at V

4. The V

5. Oscillator stopped.

6. Oscillator stops when VCC falls below Vlv limit

7. 32 kHz clock driver input.

* All Outputs excluding P00, P01, P36, and P37.

increases as the temperature decreases.

LV

0.3 mA

CC

5

.

mA

8.0 MHz

1-12 P R E L I M I N A R Y DS96LVO1100

1

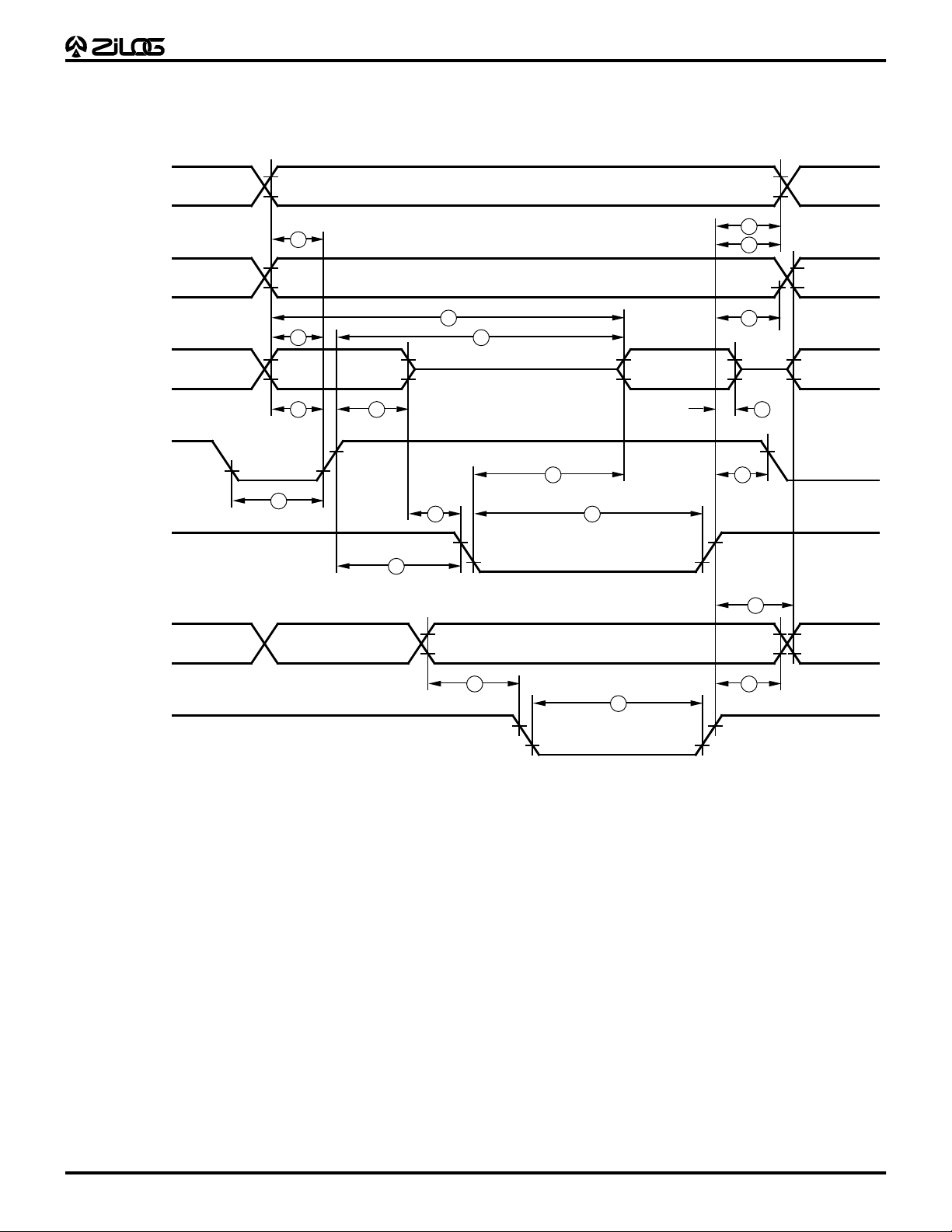

AC CHARACTERISTICS

External I/O or Memory Read and Write Timing

R//W

Z86E72/E73

OTP IR Microcontrollers

Port 0, /DM

Port 1

/AS

/DS

(Read)

Port 1

12

16

18

3

13

19

20

A7 - A0 D7 - D0 IN

21

8 11

4

5

17

6

9

10

D7 - D0 OUTA7 - A0

/DS

(Write)

14

7

Figure 10. External I/O or Memory Read/Write Timing

15

DS96LVO1100 P R E L I M I N A R Y 1-13

Z86E72/E73

OTP IR Microcontrollers

AC CHARACTERISTICS

Preliminary

External I/O or Memory Read and Write Timing Table

No. Symbol Parameter

1 TdA(AS) Address V alid to

/AS Rising Delay

2 TdAS(A) /AS Rising to Address Float Delay 3.0V

3 TdAS(DR) /AS Rising to Read Data Required Valid 3.0V

4 TwAS /AS Low Width 3.0V

5 Td Address Float to

/DS Falling

6 TwDSR /DS (Read) Low Width 3.0V

7 TwDSW /DS (Write) Low Width 3.0V

8 TdDSR(DR) /DS Falling to Read Data Required Valid 3.0V

9 ThDR(DS) Read Data to

/DS Rising Hold Time

10 TdDS(A) /DS Rising to Address Active Delay 3.0V

11 TdDS(AS) /DS Rising to /AS

Falling Delay

12 TdR/W(AS) R//W Valid to /AS

Rising Delay

13 TdDS(R/W) /DS Rising to

R//W Not Valid

14 TdDW(DSW) Write Data Valid to /DS Falling (Write)

Delay

15 TdDS(DW) /DS Rising to Write

Data Not Valid Delay

16 TdA(DR) Address Valid to Read Data Required

Valid

17 TdAS(DS) /AS Rising to

/DS Falling Delay

18 TdDM(AS) /DM Valid to /AS

Falling Delay

19 TdDS(DM) /DS Rise to

/DM Valid Delay

20 ThDS(A) /DS Rise to Address Valid Hold Time 3.0V

Notes:

1. When using extended memory timing add 2 TpC.

2. Timing numbers given are for minimum TpC.

Standard Test Load

All timing references use 0.9 V

for a logic 1 and 0.1 VCC for a logic 0.

CC

V

CC

3.0V

5.5V

5.5V

5.5V

5.5V

3.0V

5.5V

5.5V

5.5V

5.5V

3.0V

5.5V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

3.0V

5.5V

5.5V

TA = 0°C to +70°C

16 MHz

Min. Max. Units Notes

55

55

70

70

400

400

80

80

0

0

300

300

165

165

260

260

0

0

85

95

60

70

70

70

70

70

80

80

70

80

475

475

100

100

55

55

70

70

70

70

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

2

2

1,2

1,2

2

2

1,2

1,2

1,2

2

2

2

2

2

2

1,2

2

2

2

1-14 P R E L I M I N A R Y DS96LVO1100

1

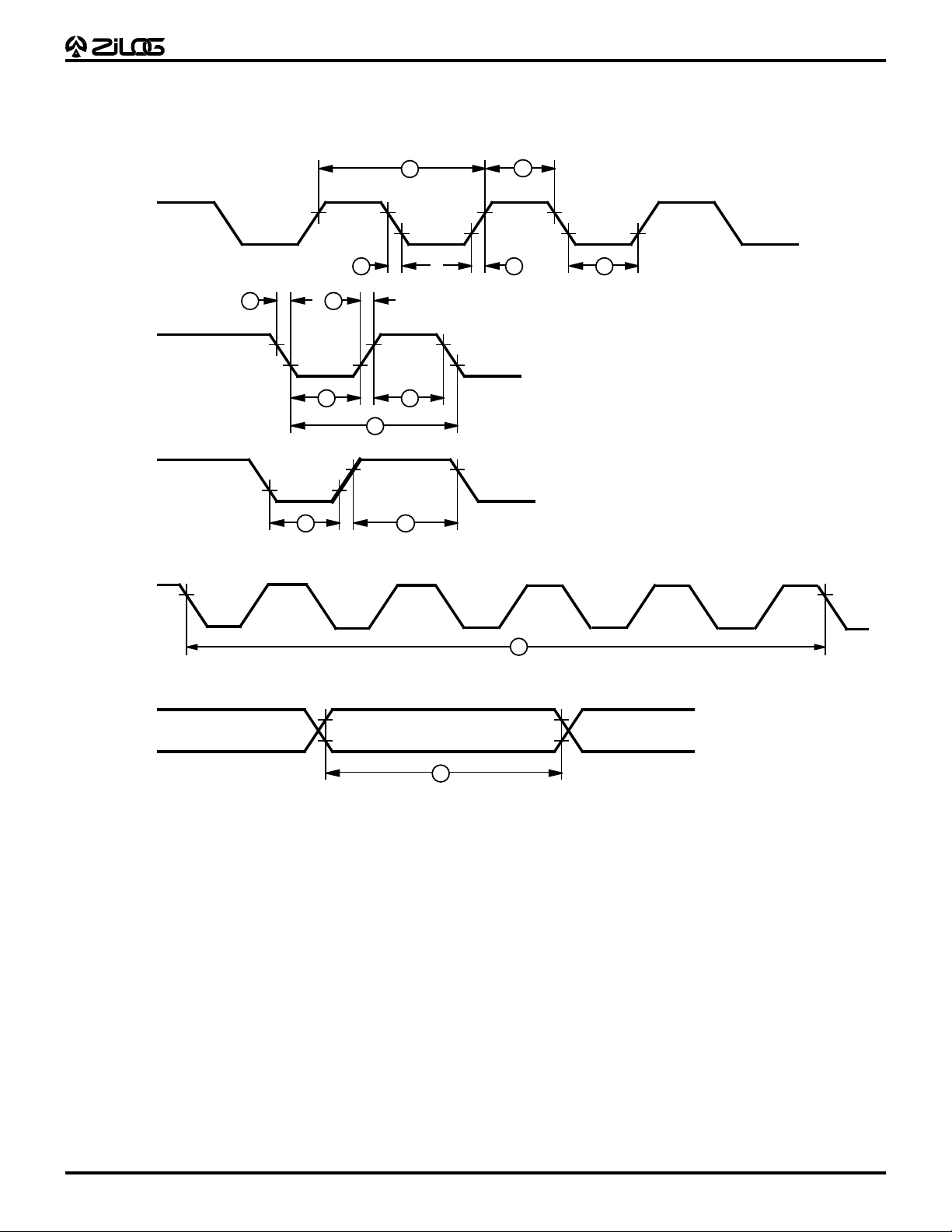

AC CHARACTERISTICS

Additional Timing Diagram

Z86E72/E73

OTP IR Microcontrollers

Clock

T

IN

IRQ

Clock

Setup

1

2 2 3

7 7

4

5

6

N

8

9

3

Stop

Mode

Recovery

Source

11

10

Figure 11. Additional Timing

DS96LVO1100 P R E L I M I N A R Y 1-15

Z86E72/E73

OTP IR Microcontrollers

AC CHARACTERISTICS

Preliminary

Additional Timing Table

No Symbol Parameter

1 TpC Input Clock Period 3.0V

2 TrC,TfC Clock Input Rise and Fall Times 3.0V

3 TwC Input Clock Width 3.0V

4 TwTinL Timer Input Low Width 3.0V

5 TwTinH Timer Input High Width 3.0V

6 TpTi Timer Input Period 3.0V

7 TrTin,TfTi Timer Input Rise and Fall Timers 3.0V

8A TwIL Interrupt Request Low Time 3.0V

8B TwIL Int. Request Low Time 4.5V

9 TwIH Interrupt Request Input High Time 4.5V

10 Twsm Stop-Mode Recovery Width Spec 3.0V

11 Tost Oscillator Start-up Time 3.0V

12 Twdt Watch-Dog Timer Delay Time

(5 ms)

(10 ms) 3.0V

(20 ms) 3.0V

(80 ms) 3.0V

Notes:

1. Timing Reference uses 0.9 V

2. Interrupt request through Port 3 (P33-P31).

3. Interrupt request through Port 3 (P30).

4. SMR – D5 = 0

5. Reg. WDTMR

6. Reg. SMR – D5 = 0

7. Reg. SMR – D5 = 1

for a logic 1 and 0.1 VCC for a logic 0.

CC

V

CC

5.5V

5.5V

5.5V

5.5V

5.5V

5.5V

5.5V

5.5V

5.5V

5.5V

5.5V

3.0V

5.5V

5.5V

3.0V

5.5V

5.5V

5.5V

5.5V

TA = 0°C to +70°C

Min Max Units Notes

121

121

37

37

100

70

DC

DC

25

25

ns

ns

ns

ns

ns

ns

ns

ns

3TpC

3TpC

8TpC

8TpC

100

70

100

70

3TpC

5TpC

5TpC

5TpC

12

12

ns

ns

ns

ns

ns

ns

1,2

1,2

1,3

1,3

1,2

1,2

5TpC

5TpC

5TpC

5TpC

12

5

25

10

50

20

225

80

75

20

150

40

300

80

1200

320

ms

ms

ms

ms

ms

ms

ms

ms

1

1

1

1

1

1

1

1

1

1

7

7

6

6

4

1-16 P R E L I M I N A R Y DS96LVO1100

1

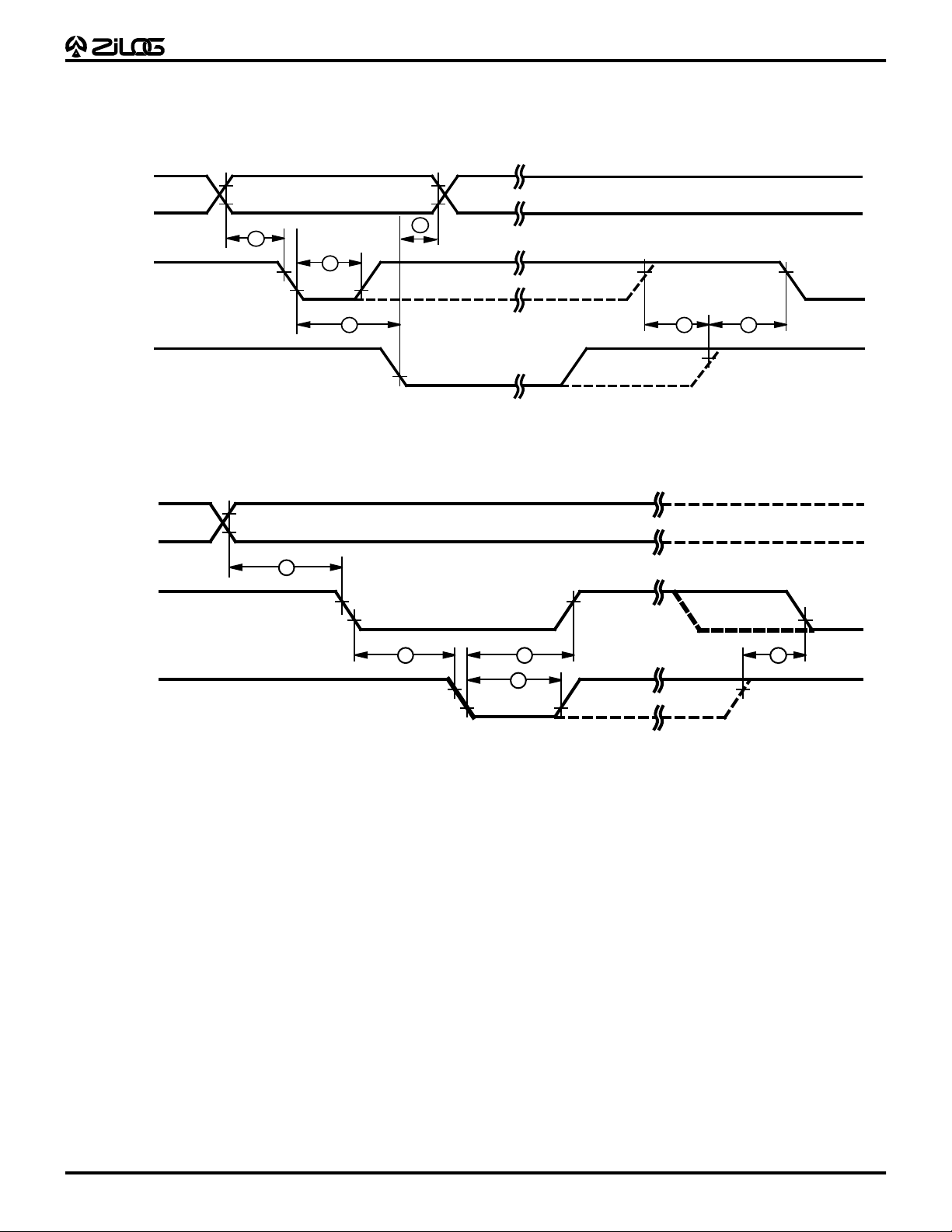

AC CHARACTERISTICS

Handshake Timing Diagrams

Z86E72/E73

OTP IR Microcontrollers

Data In

/DAV

(Input)

RDY

(Output)

Data Out

/DAV

(Output)

1

Data In Valid

3

7

Next Data In Valid

2

Delayed DAV

4

Figure 12. Input Handshake Timing

Data Out Valid

5 6

Delayed RDY

Next Data Out Valid

Delayed DAV

RDY

(Input)

8 9

10

Figure 13. Output Handshake Timing

11

Delayed RDY

DS96LVO1100 P R E L I M I N A R Y 1-17

Z86E72/E73

OTP IR Microcontrollers

AC CHARACTERISTICS

Preliminary

Handshake Timing Table

No Symbol Parameter

1 TsDI(DAV) Data In Setup Time 4.0V

2 ThDI(DAV) Data In Hold Time 4.0V

3 TwDAV Data Available Width 4.0V

4 TdDAVI(RDY) DAV Falling to RDY

Falling Delay

5 TdDAVId(RDY) DAV Rising to RDY

Falling Delay

6 TdRDYO(DAV) RDY Rising to DAV

Falling Delay

7 TdDO(DAV) Data Out to DAV

Falling Delay

8 TdDAV0(RDY) DAV Falling to RDY

Falling Delay

9 TdRDY0(DAV) RDY Falling to DAV

Rising Delay

10 TwRDY RDY Width 4.0V

11 TdRDY0d(DAV) RDY Rising to DAV

Falling Delay

V

CC

5.5V

5.5V

5.5V

4.0V

5.5V

4.0V

5.5V

4.0V

5.5V

4.0V

5.5V

4.0V

5.5V

4.0V

5.5V

5.5V

4.0V

5.5V

TA = 0°C to +70°C

16 MHz Data

Min Max Direction

0IN

IN

0

0

155

110

160

115

120

80

0

0

63

63

0

0

160

115

110

80

110

80

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

1-18 P R E L I M I N A R Y DS96LVO1100

1

PIN FUNCTIONS

Z86E72/E73

OTP IR Microcontrollers

/DS (Output, active Low). Data Strobe is activated once for

each external memory transfer. For a READ operation,

data must be available prior to the trailing edge of /DS. For

WRITE operations, the falling edge of /DS indicates that

output data is valid.

/AS (Output, active Low). Address Strobe is pulsed once

at the beginning of each machine cycle. Address output is

through Port 0/Port 1 for all external programs. Memory

address transfers are valid at the trailing edge of /AS. Under program control, /AS is placed in the high-impedance

state along with Ports 0 and 1, Data Strobe, and

Read/Write.

XTAL1 Crystal 1 (time-based input). This pin connects a

parallel-resonant crystal, ceramic resonator, LC, or RC

network or an external single-phase clock to the on-chip

oscillator input.

XTAL2 Crystal 2 (time-based output). This pin connects a

parallel-resonant, crystal, ceramic resonant, LC, or RC

network to the on-chip oscillator output.

R//W Read/Write (output, write Low). The R//W signal is

Low when the CCP is writing to the external program or

data memory.

R//RL (input). This pin, when connected to GND, disables

the internal ROM and forces the device to function as a

ROMless Z8. (Note that, when left unconnected or pulled

high to V

sion.)

, the part functions normally as a Z8 ROM ver-

CC

Port 0 (P07-P00). Port 0 is an 8-bit, bidirectional, CMOS

compatible port. These eight I/O lines are configured under software control as a nibble I/O port, or as an address

port for interfacing external memory. The output drivers

are push-pull. Port 0 is placed under handshake control. In

this configuration, Port 3, lines P32 and P35 are used as

the handshake control /DAV0 and RDY0. Handshake signal direction is dictated by the I/O direction to Port 0 of the

upper nibble P07-P04. The lower nibble must have the

same direction as the upper nibble.

For external memory references, Port 0 can provide address bits A11-A8 (lower nibble) or A15-A8 (lower and upper nibble) depending on the required address space. If

the address range requires 12 bits or less, the upper nibble

of Port 0 can be programmed independently as I/O while

the lower nibble is used for addressing. If one or both nibbles are needed for I/O operation, they must be configured

by writing to the Port 0 mode register. After a hardware reset, Port 0 is configured as an input port.

Port 0 is set in the high-impedance mode if selected as an

address output state along with Port 1 and the control signals /AS, /DS, and R//W (Figure 8).

A software option is available to program 0.4 VDD CMOS

trip inputs on P00-P03. This allows direct interface to

mouse/trackball IR sensors.

An optional 200 kOhm pull-up is available as a software

option of all Port 0 bits with nibble select.

These pull-ups are disabled when configured (bit by bit) as

an output.

DS96LVO1100 P R E L I M I N A R Y 1-19

Z86E72/E73

OTP IR Microcontrollers

PIN FUNCTIONS (Continued)

Z86LXX

MCU

4

Port 0 (I/O or A15 - A8)

4

Optional

Handshake Controls

/DAV0 and RDY0

(P32 and P35)

OEN

Out

In

In

0.4 VDD

Trip Point Buffer

* Note: On P00 and P07 only.

** POIM, DI, DO Mask Selectable.

*** Refer to the Z86C17 specification for

application information in utilizing these

inputs in a mouse or trackball application.

Mask

Option

200 kΩ

PAD

Figure 14. Port 0 Configuration

1-20 P R E L I M I N A R Y DS96LVO1100

Z86E72/E73

1

OTP IR Microcontrollers

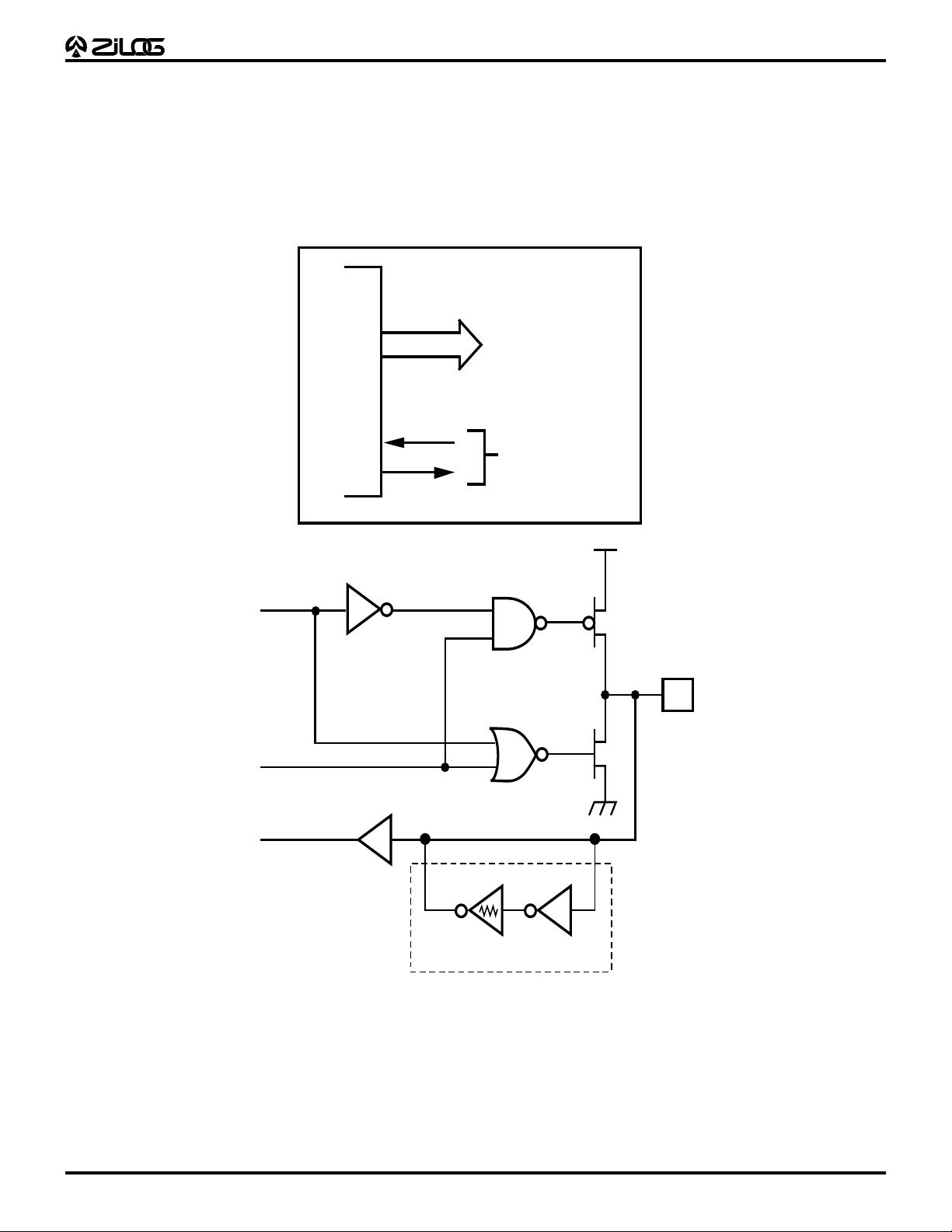

Port 1 (P17-P10). Port 1 is a multiplexed Address (A7-A0)

and Data (D7-D0), CMOS compatible port. Port 1 is dedicated to the Zilog ZBus®-compatible memory interface.

The operations of Port 1 are supported by the Address

Strobe (/AS) and Data Strobe (/DS) lines, and by the

Read/Write (R//W) and Data Memory (/DM) control lines.

Data memory read/write operations are done through this

8

Z86LXX

MCU

port (Figure 20). If more than 256 external locations are required, Port 0 outputs the additional lines.

Port 1 can be placed in the high-impedance state along

with Port 0, /AS, /DS, and R//W, allowing the Z86L7X to

share common resources in multiprocessor and DMA applications. Port1 can also be configured for standard port

output mode.

Port 1

(I/O or AD7 - AD0)

Optional

Handshake Controls

/DAV1 and RDY1

(P33 and P34)

OEN

Out

In

PAD

Auto Latch

R ≈ 500 KΩ

Figure 15. Port 1 Configuration

DS96LVO1100 P R E L I M I N A R Y 1-21

Z86E72/E73

OTP IR Microcontrollers

PIN FUNCTIONS (Continued)

Port 2 (P27-P20). Port 2 is an 8-bit, bidirectional, CMOS

compatible I/O port. These eight I/O lines can be independently configured under software control as inputs or outputs. Port 2 is always available for I/O operation. A software option is available to connect eight 200 kOhms

(±50%) pull-up resistors on this port. Bits programmed as

outputs are globally programmed as either push-pull or

open-drain. Port 2 may be placed under handshake control. In this configuration, Port 3 lines, P31 and P36 are

used as the handshake controls lines /DAV2 and RDY2.

Z86LXX

MCU

The handshake signal assignment for Port 3, lines P31

and P36 is dictated by the direction (input or output) assigned to Bit 7, Port 2 (Figure 10).

The CCP wakes up with the eight bits of Port 2 configured

as inputs with open-drain outputs.

Port 2 also has an 8-bit input OR and an AND gate which

can be used to wake up the part. P20 can be programmed

to access the edge selection circuitry (Figure 21).

Port 2 (I/O)

Optional

Handshake Controls

/DAV2 and RDY2

(P31 and P36)

(L72/E72 Only)

Open-Drain

OEN

Out

In

VCC

200 kΩ

Mask

Option

PAD

Figure 16. Port 2 Configuration

1-22 P R E L I M I N A R Y DS96LVO1100

Z86E72/E73

1

OTP IR Microcontrollers

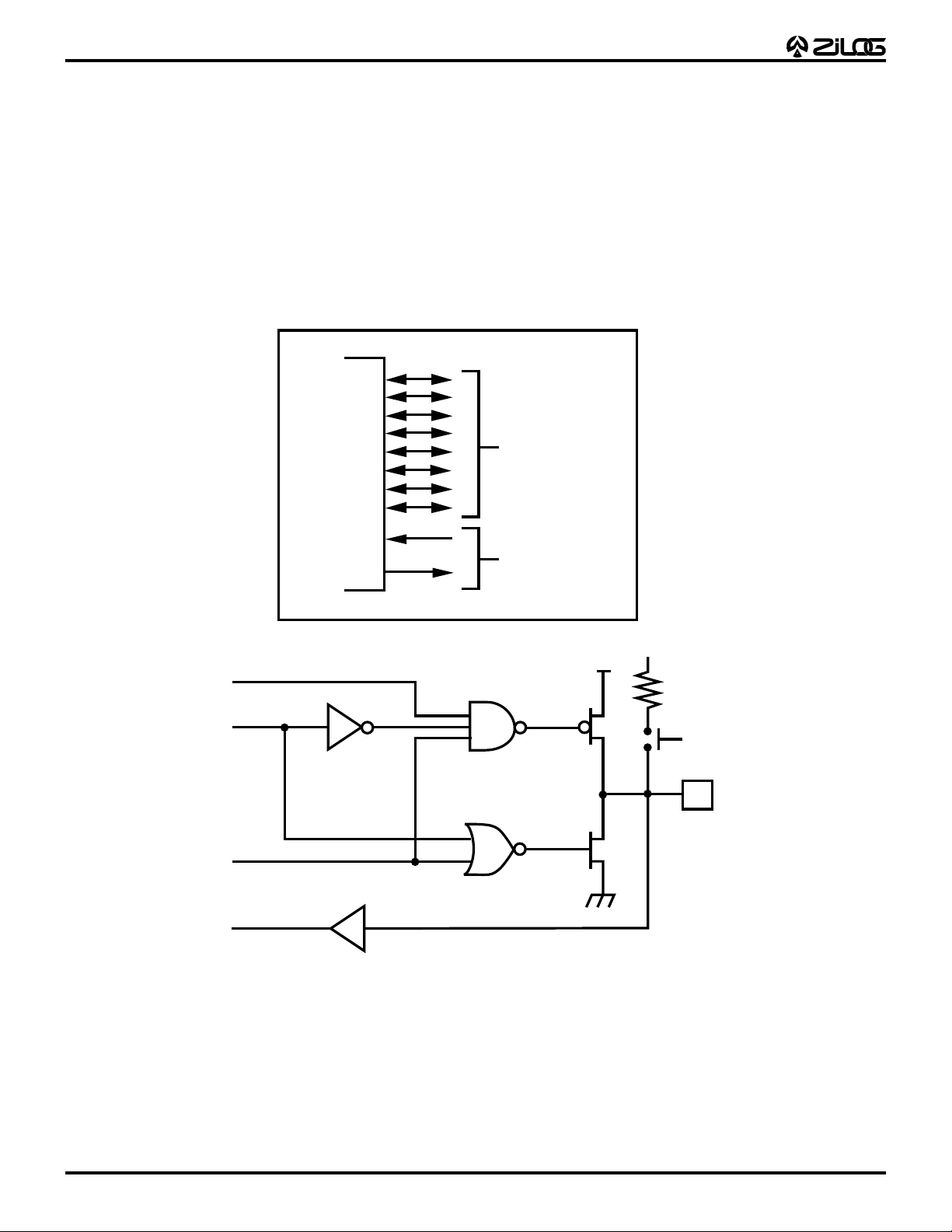

Port 3 (P37-P31). Port 3 is a 7-bit, CMOS compatible three

fixed input and four fixed output port. Port 3 consists of

three fixed input (P33-P31) and four fixed output (P37P34), and can be configured under software control for Input/Output, Interrupt, Port handshake, Data Memory functions and output from the counter/timers. P31, P32, and

P33 are standard CMOS inputs; outputs are push-pull.

Two on-board comparators process analog signals on P31

and P32 with reference to the voltage on Pref1 and P33.

The analog function is enabled by programming the Port 3

Mode Register (bit 1). P31 and P32 are programmable as

rising, falling, or both edge triggered interrupts (IRQ regis-

Counter/Timer

T8

P34 OUT

P31

PREF1

+

-

COMP1

P34 OUT

ter bits 6 and 7). Pref1 and P33 are the comparator reference voltage inputs. Access to the Counter Timer edge detection circuit is through P31 or P20 (see CTR1

description).

Port 3 provides the following control functions: handshake

for Ports 0, 1, and 2 (/DAV and RDY); three external interrupt request signals (IRQ2-IRQ0); Data Memory Select

(/DM) (Table 8).

Port 3 also provides output for each of the counter/timers

and the AND/OR Logic. Control is performed by programming bits D5-D4 of CTRI, bit 0 of CTR0 and bit 0 of CTR2.

P34

PAD

CTR0

0 Normal Control

D0

1 8-bit Timer output active

P37 OUT

P32

P33 (PREF2)

+

-

COMP2

PCON

0 = P34, P37 Standard Output

D0

1 = P34, P37 Comparator Output

Reset condition.

*

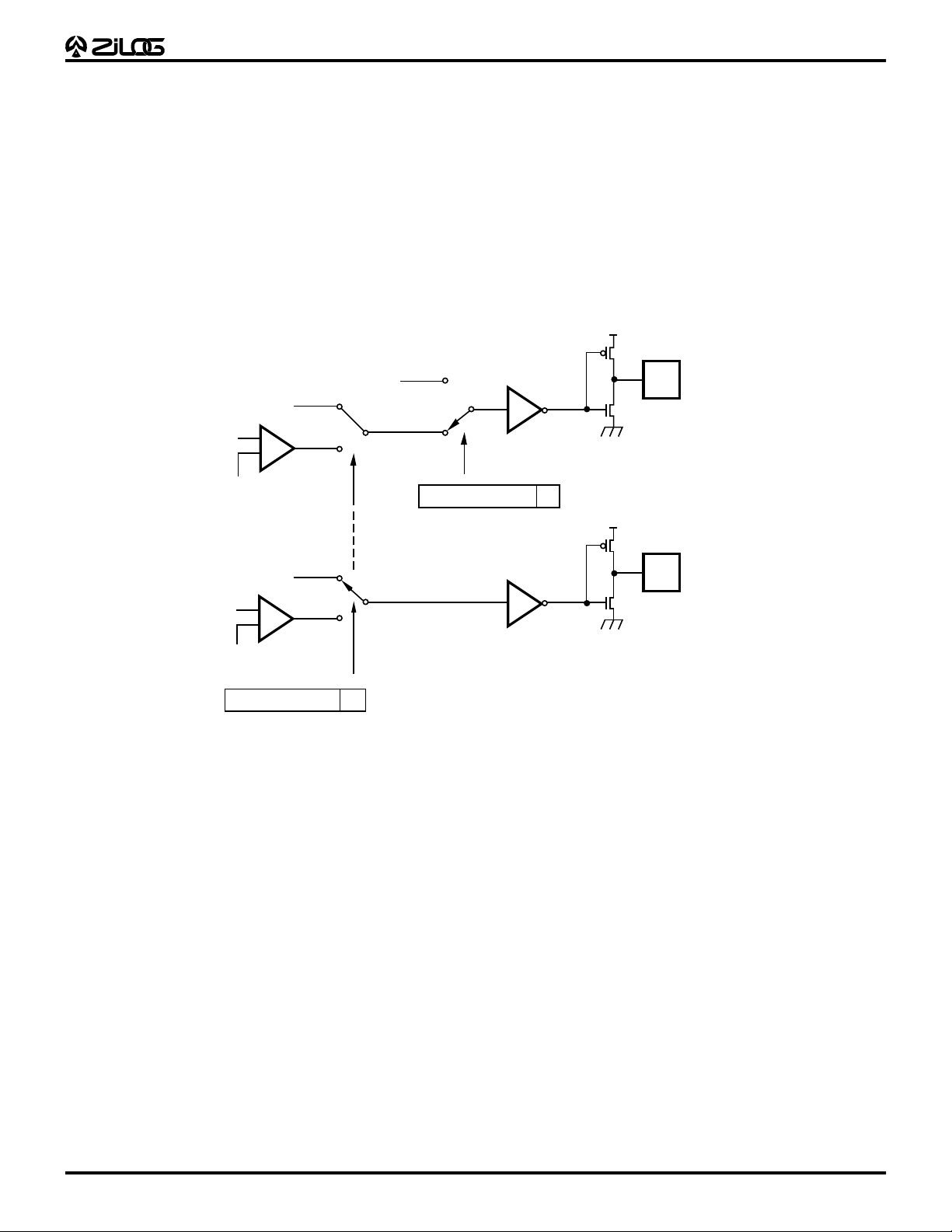

Figure 17. Port 3 Configuration

P37

PAD

*

DS96LVO1100 P R E L I M I N A R Y 1-23

Loading...

Loading...