Zetex ZXRD100ANQ16TA, ZXRD100ANQ16TC, ZXRD100APQ16TA, ZXRD100APQ16TC, ZXRD1033NQ16TA Datasheet

...

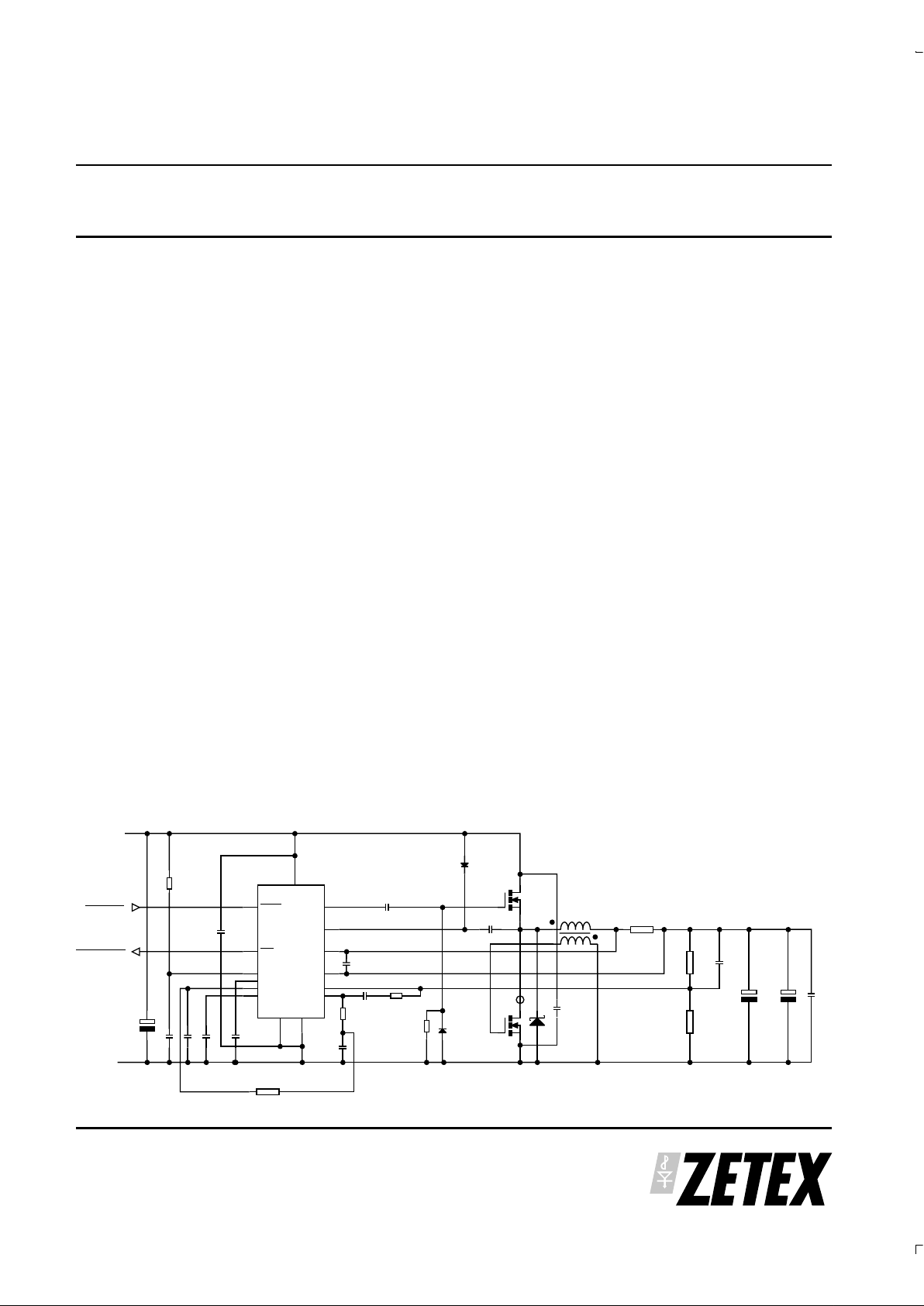

Very high efficiency SimpleSyncTM converter.

FEATURES

• > 95% Efficiency

• Fixed frequency (adjustable) PWM

• Voltage mode to ensure excellent stability &

transient response

• Low quiescent current in shutdown mode,15µA

• Low battery flag

• Output down to 2.0V

• Overload protection

• Demonstration boards available

• Synchronous or non-synchronous operation

• Cost effective solution

• N or P channel MOSFE Ts

• QSOP16 package

• Fixed 3.3, 5V and adjustable outputs

• Programmable soft st art

APPLICATIONS

• High efficiency 5 to 3.3V converters up to 4A

• Sub-notebook co mputers

• Embedded proc essor power supply

• Distribu ted power supply

• Portable instruments

• Local on card conversion

• GPS systems

DESCRIPTION

The ZXRD1000 series provides complete control and

protection functions for a high efficiency (> 95%) DC-DC

converter solution. The choice of external MOSFETs allow

the designer to size devices according to application. Th e

ZXRD1000 series uses advanced DC-DC converter

techniques to provide synchronous drive capability, using

innovative circuits that allow easy and cost effective

implementation of shoot through protection. The

ZXRD1000 series can be used with an all N channel

topology or a combination N & P channel topology.

Additional functionality includes shutdown control, a

user adjustable low battery flag and simple

adjustment of the fixed PWM switching frequency.

The controller is available with fixed outputs of 5V or

3.3V and an adjustable (2.0 to 12V) output.

4.5-10V

N1

ZXM64N02X

L1

15µH

C6

1µF

D1

ZHCS1000

C3

330pF

R3

3k

R1

100k

Fx

C1

1µF

0.01R

C7

22µF

D3

BAT54

C10

1µF

R4

10k

C8

2.2µF

68µF

C4

1µF

C5

1µF

x2

680µF

R6

10k

R5

6k

Cx2

0.01µF

CX1

0.022µF

RX

2k7

N2

ZXM64N02X

R2

680R

D2

BAT54

C11

1µF

C2

1µF

3.3V 4A

C9

1µF

120µF

V

CC

C

OUT

V

OUT

R

SENSE

13

Bootstrap

V

IN

GNDG

ND

PWR

LB

SET

Decoup

R

SENSE+

R

SENSE -

V

FB

C

T

LBF

SHDN

V

INT

Delay

Comp

V

DRIVE

2

1

7

8

16

15

34

6

5

10

14

11

9

C

IN

Low input flag

Shut Down

IC1

HIGH EFFICIENCY SIMPLESYNC PWM DC-DC CONTROLLERS

1

ZXRD1000 SERIES

ISSUE 4 - OCTOBER 2000

ABSOLUTE MAXIMUM RATINGS

Input without bootstrap (P suffix) 20V

Input with bootstrap(N suffix) 10V

Bootstrap voltage 20V

Shutdown pin V

IN

LB

SET

pin V

IN

R

SENSE

+, R

SENSE -

V

IN

Power dissipation 610mW (Note 4)

Operating temperature -40 to +85°C

Storage temperature -55 to +125°C

2

ELECTRICAL CHARACTERISTICS

TEST CONDITIONS (Unless otherwise stated) T

amb

=25°C

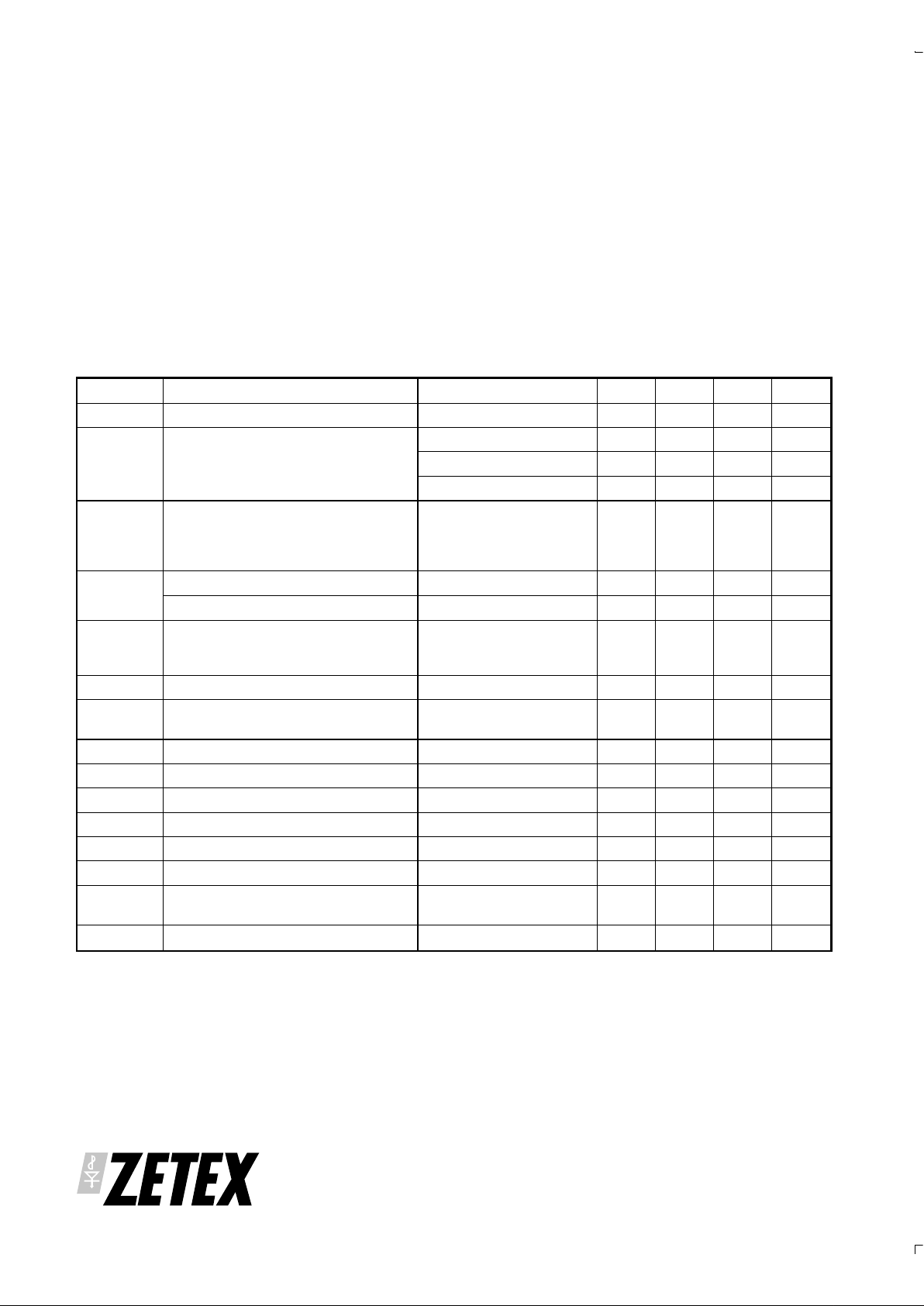

Symbol Parameter Conditions Min Typ Max Unit

V

IN(min)

Min. Operating Voltage No Output Device 4.5 V

V

FB

(Note 1)

Feedback Voltage V

IN

=5V,IFB=1mA 1.215 1.24 1.265 V

4.5<V

IN

<18V 1.213 1.24 1.267 V

50µA<I

FB

<1mA,VIN=5V

1.215 1.24 1.265 V

T

DRIVE

Gate Output Drive Capability CG=2200pF(Note 2)

C

G

=1000pF

V

IN

= 4.5 V to maximim

supply (Note 3)

60

35

ns

ns

I

CC

Supply Current VIN=5V 1620mA

Shutdown Current V

SHDN

= 0V;VIN=5V 15 50

µA

f

osc

(Note 5)

Operating frequency range

Frequency with timing capacitor C3=1300pF

C

3

=330pF

50

50

200

300 kHz

f

osc(tol)

Oscillator Tol.

±25

%

DC

MAX

Max Duty Cycl e N Channel

P Channel

15

0

94

100

%

%

V

RSENSE

R

SENSE

voltage differe ntial -40 to +85°C 50 mV

V

CMRSENSE

Common mode range of V

RSENSE

-40 to +85°C 2 V

IN

V

LBF

SET

Low Battery Flag set voltage 1.5 V

IN

V

LBF

OUT

Low Battery Flag output Active Low 0.2 0.4 V

LBF

HYST

Low Battery Fl ag Hyst eresis 10 20 50 mV

LBF

SINK

Low Battery Flag Sink Current -40 to +85°C 2 mA

V

SHDN

Shutdown Threshold Voltage Low(off)

High(on) 1.5

0.25 V

V

I

SHDN

Shutdown Pin Source Current 10

µA

ISSUE 4 - OCTOBER 2000

Note 1. V

FB

has a different function between fixed and adjustable controller options.

Note 2. 2200pF is the maximum recommended gate capacitance.

Note 3. Maximum supply for P phase controllers is 18V,maximum supply for N phase controllers is 10V.

Note 4. See V

IN

derating graph in Typical Characteristics.

Note 5. The maximum frequency in this application is 300kHz. For higher frequency operation contact Zetex

Applications Department.

ZXRD1000 SERIES

3

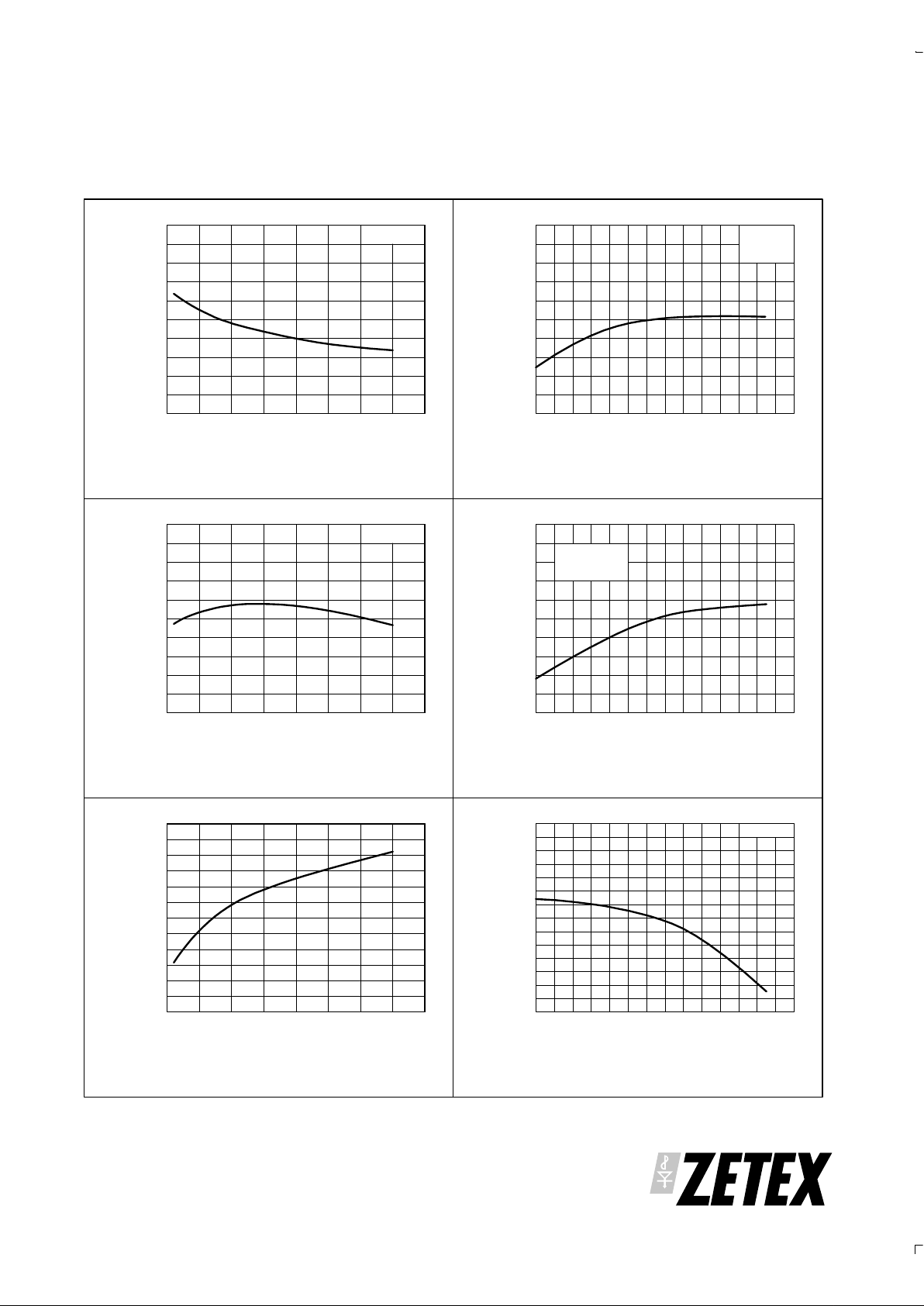

-40 -20 0 20 40 60 80 100

Temperatu re (°C)

1.23

1.235

1.24

1.245

1.25

V

FB

(V)

VFB v Temperatur e

VIN=5V

V

OUT

=3.3V

4681012141618

VIN (V)

1.236

1.238

1.24

1.244

VFB v VIN

V

FB

(V)

20

1.242

V

OUT

=3.3V

4681012141618

VIN (V)

0.99

1.00

1.01

Normalised LBSET v VIN

20

1.02

-40 -20 0 20 40 60 80 100

Temperatu re (°C)

0.995

1.000

1.005

Normalised LB

SET

Normalised LBSET v Temperature

VIN=5V

-40 -20 0 20 40 60 80 100

Temperatu re (°C)

190

195

200

205

210

FOSC v Temperature

VIN=5V

C3=330pF

4681012141618

VIN(V)

198

199

200

202

FOSC v VIN

F

OSC

(kHz)

20

201

197

C3=330pF

F

OSC

(kHz)

TYPICAL CHARACTERISTICS

Normalised LB

SET

ZXRD1000 SERIES

ISSUE 4 - OCTOBER 2000

4

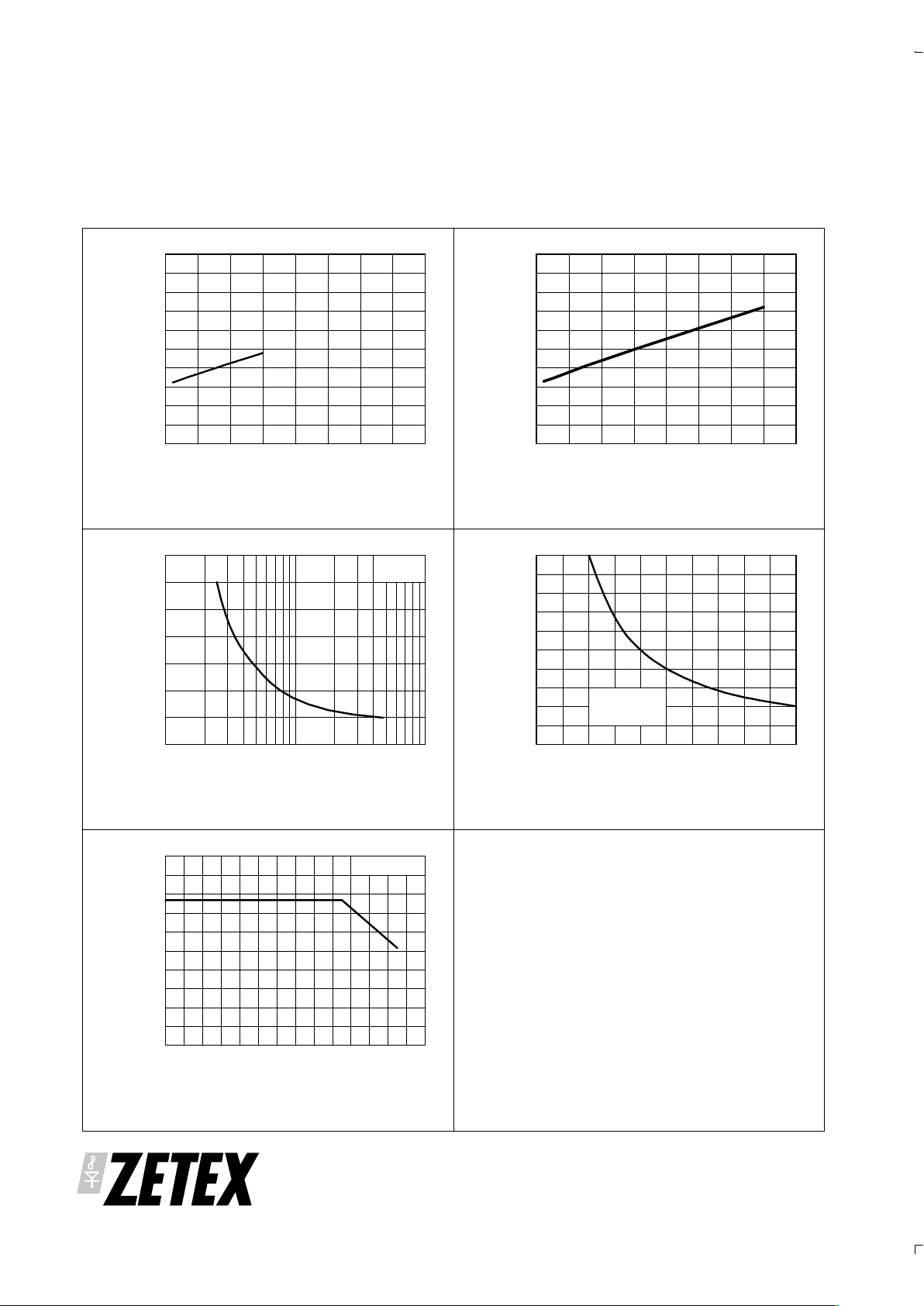

4 6 8 101214 1618

VIN(V)

10

15

20

25

30

Supply Current (mA)

204681012141618

VIN(V)

10

15

20

25

30

Supply Current v V

IN

N Phase Device

Supply Current (mA)

20

1nF 10nF

T iming Capacitance

200

300

F

OSC

v Capacitance

F

OSC

(kHz)

100

0

100pF

Vin=5V

10 20 30 40 50

RSENSE (m⍀)

2

3

4

Current Limit v R

SENSE

Current Li m i t (A )

5

1

0

0

VIN=5V

V

OUT=3.3V

-40 -20 0 20 40 60 80 100

Temperature (°C)

5

10

15

20

V

IN

(V)

VINDerating v Temperature

CG=2200pF

Supply Current v V

IN

P Phase Device

TYPICAL CHARACTERISTICS

ISSUE 4 - OCTOBER 2000

ZXRD1000 SERIES

DETAILED DESCRIPTION

The ZXRD1000 series can be configured to use either

N or P channel MOSFETs to suit most applications.

The most popular format, an all N channel

synchronous solution gives the optimum efficiency. A

feature of the ZXRD1000 series solution is the unique

method of generating th e synchronous dr ive, called

SimpleSync . Most solutions use an additional

output from the contro ller, inverted and delayed from

the main switch drive. The ZXRD1000 series solution

uses a simple overwind ing on the mai n choke (wou nd

on the same core at no real cost penalty) plus a small

ferrite bead . This means that the synchronous FET is

only enhanced when the main FET is turned off. This

reduces the ‘blanking period’ required for shootthrough protection, increasing efficien cy and allowing

smaller catch diodes to be used, making the controller

simpler and less costly by avoiding complex timing

circuitry. Included on chip are numerou s functions that

allow flexibility to suit most applications. The nominal

switching frequency (200kHz) can be adjusted by a

simple timing capacitor, C3. A low battery detect circuit

is also provided. Off the shelf components are availabl e

from major manufacturers such as Sumida to provide

either a single winding inductor for non-synchronous

applications or a coil with an over-winding for

synchronous applications. The combination of these

switching characteristics, innovative circuit design and

excellent user flexibility, make the ZXRD1000 series

DC-DC solutions some of the smallest and most cost

effective and electrically efficient currently available.

Using Zetex’s HDMOS low R

DS(on)

devices, ZXM64N02X

for the main and synchronous switch, efficiency can

peak at upto 95% and remains high over a wide range

of operating currents. Programm able soft start can also be

adjusted via the capacitor, C7, in the compens ation loop.

What is SimpleSyncTM?

Conventional Methods

In the conventional approach to the synchronous

DC-DC solution, much care has to be taken with the

timing constraints between the main and synchronous

switching devices. Not only is thi s dependent upon

individual MOSF ET gate thresh olds (whi ch vary fr om

device to device within data sheet limits and over

temperature), but it is also somewhat dependent up on

magnetics, layout and other parasitics. This normally

means that significant ‘dead time’ has to be factored

in to the design between the main and synchronous

devices being turned off and on respectively.

Incorrect application of dead time constraints can

potentially lead to catastrophic short circuit conditions

between V

IN

and GND. For some battery operated

systems this can not only damage MOSFETs, but also

the battery itself. To realise correct ‘dead time’

implementation takes complex circuitry and hence

implies additional cost.

The ZETEX Me thod

Zetex has taken a different approach to solving these

problems. By looking at the basic architecture of a

synchronou s converter, a n ovel approach u sing the

main circuit inductor was developed. By taking the

inverse waveform found at the input to the main

inductor of a non-synchronous solution, a

synchronous drive waveform can be generated that is

always relative to the main drive waveform and

inverted with a small delay. This waveform can be

used to drive the synchron ous switch which means no

complex circuitry in the IC need be used to allow for

shoot-through protection.

Implementation

Implementation was very easy and low cost. It simply

meant peeling off a strand of the main inductor

winding and isolating it to form a coupled secondary

winding. These are available as standard items

referred to in the applications ci rcuits parts list.The use

of a small, surface mount, inexpensive ’square loop ’

ferrite bead provides an excellent method of

eliminating shoot-through due to variation in gate

thresholds. The bead essentially acts as a high

impedance for the few nano seconds that

shoot-through would normally occur. It saturates very

quickly as the MOSFETs attain steady state operation,

reducing the bead impedance to virtually zero.

Benefits

The net result is an innovative solution that gives

additional benefits whilst lowering overall

implementation costs. It is also a technique that can

be simply omitted to make a non-synchronous

controller, saving further cost, at the expense of a few

efficiency points.

5

ZXRD1000 SERIES

ISSUE 4 - OCTOBER 2000

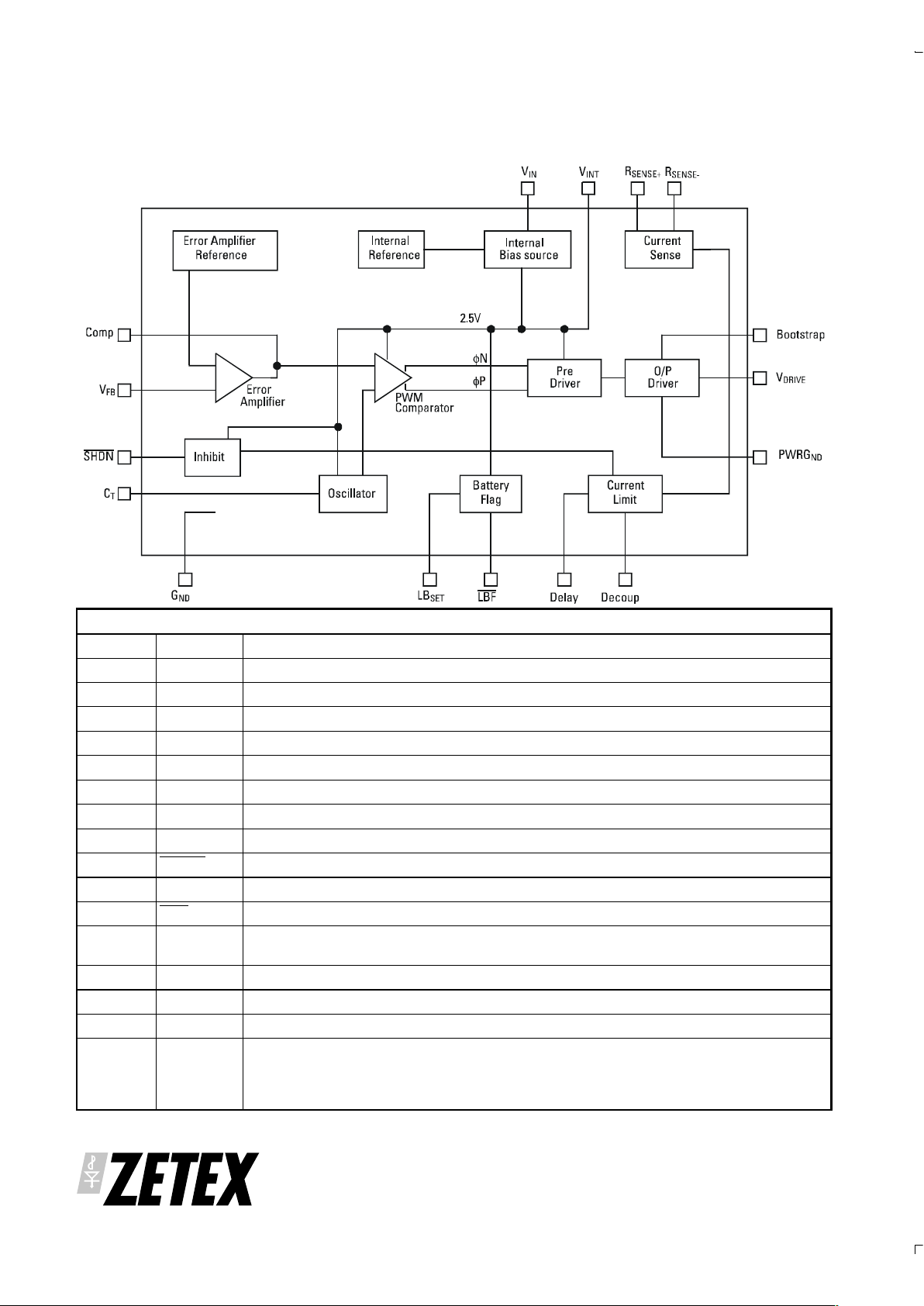

Functional Block Diagram

PIN DESCRIPTIONS ‡ See relevant Applications Section

Pin No. Name Description

1 Bootstrap Bootstrap circuit for generating gate drive

2V

DRIVE

Output to the gate drive circuit for main N/P channel switches

3PWRG

ND

Power ground

4G

ND

Signal ground

5C

T

Timing Capacitor sets oscillator frequency. ‡

6V

INT

Internal Bias Circuit. Decouple with 1µF ceramic capacitor

7R

SENSE+

Higher potential input to the current sense for current limit circuit

8R

SENSE-

Lower potential input to the current sense for current limit circuit

9

SHDN Shutdown control. Active low.

10 Dec oup Opt ional short ci rcuit and overloa d decoupling capaci tor for increased accurac y

11

LBF Low battery flag output. Active low, open collec tor output

12 LB

SET

Low battery flag set. Can be connected to VIN if unused, or threshold set

via potential divider. ‡

13 V

IN

Input Voltage

14 Delay External R and C to set the desired cycle time f or hiccup circuit. ‡

15 Comp Compensation pin to allow for stability components and soft start. ‡

16 V

FB

Feedback Voltage. This pin has a different function between fi xed and

adjustable controller options. The appropriate controller must be used for

the fixed or adjustable solution. Connect to V

OUT

for fixed output, or to

potential divider for adjustable output. ‡

6

ISSUE 4 - OCTOBER 2000

ZXRD1000 SERIES

Applications

Note: Component names refer to designators shown

in the application circuit diagrams.

Output Capa citors

Output capacitors are a critical choice in the overall

performance of the so lution. They are required to filter

the output and supply load tr ansient cur rent. They ar e

also affected by the switching frequency, ripple

current, di/dt and magnitude of tran sient load current.

ESR plays a key role in determining the value of

capacitor to be used. Combination of both high

frequency, low value ceramic capacitors and low ESR

bulk storage capacitors optimised for switching

applications provide the best response to load

transients and ripple requirements. Electrolytic

capacitors with low ESR are larger and more

expensive so the ultimate choice is always a

compromise between size, cost and performance.

Care must also be taken to ensure that for large

capacitors, the ESL of the leads does not become an

issue. Excellent low ESR tantalum or electrolytic

capacitors are available from Sanyo OS-CON, AVX,

Sprague and Nichicon.

The output capacitor will also affect loop stability,

transient performance. The capacitor ESR should

preferably be of a similar value to the sense resistor.

Parallel devices may be required.

I

RIPPLE(RMS)

=

0.29 V

OUT

(VIN−V

OUT

)

L f V

IN

where L= output filter inductance

f= switching frequency

For output v oltage ripple it is ne c e s sary to know th e

peak ripple current which is given by:

I

pk−pk

=

V

OUT

( VIN− V

OUT)

L f V

IN

Voltage ripple is then:V

RIPPLE

= I

pk

−

pk

∗ ESR

Input Capacitors

The input capacitor is chosen for its RMS current and

voltage rating. The use of low ESR electrolytic or

tantalum capacitors is recommended. Tantalum

capacitors should have their voltage rating at 2V

IN

(max), electrolytic at 1.4VIN(max). I

RMS

can be

approximated by:

I

RMS

= I

OUT

√

(V

OUT(VIN−VOUT

))

V

IN

Underspecification of this parameter can affect long

term reliability. An additonal ceramic capacitor should

be used to provide high frequency decoupli ng at V

IN.

Also note that the input capacitance ESR is effectively in

series with the input and hence contributes to efficiency

losses related to I

RMS

2

* ESR of the input capacitor.

MOSFET Selection

The ZXRD1000 family can be configured in circuits

where either N or P channel MOSFETs are employed

as the main switch. If an N channel device is used, the

corresponding N phase controller must be chosen.

Similarly, for P channel main switch a P phase

controller must be used. The ordering information has

a clear identifier to distinguish between N and P phase

controllers.

The MOSFET selection is subject to thermal and gate

drive considerations. Care also has to be taken to allow

for transition losses at high input voltages as well as

R

DS(ON)

losses for the main MOSFET. It is

recommended that a device with a drain source

breakdown of at least 1.2 times the maximum V

IN

should be used.

For optimum efficiency , two N channel low R

DS(on)

devices are required. MOSFETs should be selected

with the lowest R

DS(ON)

consistent with the output

current required. As a guide, for 3-4A output, <50mΩ

devices would be optimum, provided the devices are

low gate threshold and low gate charge. Typically look

for devices that will be fully enhanced with 2.7V V

GS

for 4-5A capability.

Zetex offers a range o f low R

DS(ON)

logic level MOSFETs

which are specifically designed with DC-DC power

conversion in mind. Packaging includes SOT23,

SOT23-6 and MSOP8 options. Ideal examples of

optimum devices would be Zetex ZXM64N03X and

ZXM64N02X (N channel). Contact your local Zetex office

or Zetex web page for further informatio n.

7

ZXRD1000 SERIES

ISSUE 4 - OCTOBER 2000

Applications (continued)

Inductor Selection

The inductor is one of the most critical com ponents in

the DC-DC circuit.There are numerous types o f devices

available from many suppliers. Zetex has opted to

specify off the shelf encapsulated surface mount

components, as these represent the best compro mise

in terms of cost, size, performance and shielding.

The SimpleSync

TM

technique uses a main inductor

with an overwinding for the gate drive which is

available as a standard part. However, for engineers

who wish to design their own custom magnetics, this

is a relatively simple and low cost construction

technique . It is simply form ed by terminatin g one of

the multiple strands of litz type wi re separately. It is

still wound on the same core as the main winding and

only has to handle enough current to charge the gate

of the synchronous MOSFET. The major benefit is

circuit simplification and hence lower co st of the control

IC. For non-synchronous operation, the overwinding is

not requir ed.

The choice of core type also plays a key role. For

optimum performance, a ’swinging choke’ is often

preferred. This is one which exhibits an increase in

inductance as load current decreases. This has the net

effect of reducing circulating current at lighter load

improving efficiency. There is normally a cost

premium for this added benefit. For this reason the

chokes specified are the more usual constant

inductance type.

Peak current of the inductor should be rated to

minimum 1.2I

OUT

(max) . To maximise efficiency, the

winding resistance of the main inductor should be less

than the main switch output on resistance.

Schottky Diode

Selection depends on whether a synchronous or

non-synchronous approach is taken. For the

ZXRD1000, the unique approach to the synchronous

drive means minimal dead time and hence a small

SOT23 1A DC rated device will suffice, such as the

ZHCS1000 from Zetex. The device i s o nly designed to

prevent the body diode of the synchronous MOSFET

from conducting during the initi a l s witching transi e nt

until the MOSFET takes over. The device should be

connected as close as possible to the source terminals

of the main MOSFET.

For non-synchr onous applications , the Schottky diod e

must be selected to allow for the worst case

conditions, when V

IN

is at its highest and V

OUT

is

lowest (short circuit conditions for example). Under

these conditions the device must handle peak current

at close to 100% duty cycle.

Frequency Adjustment

The nominal runn ing frequenc y of the contro ller is set

to 200kHz in the applications shown. This can be

adjusted over the range 50kHz to 300kHz by changing

the value of capacitor on the C

T

pin. A low cost

ceramic capacitor can be used.

Frequency = 60000/C3 (pF)

Frequency v temperature is given in the typical

characteristics.

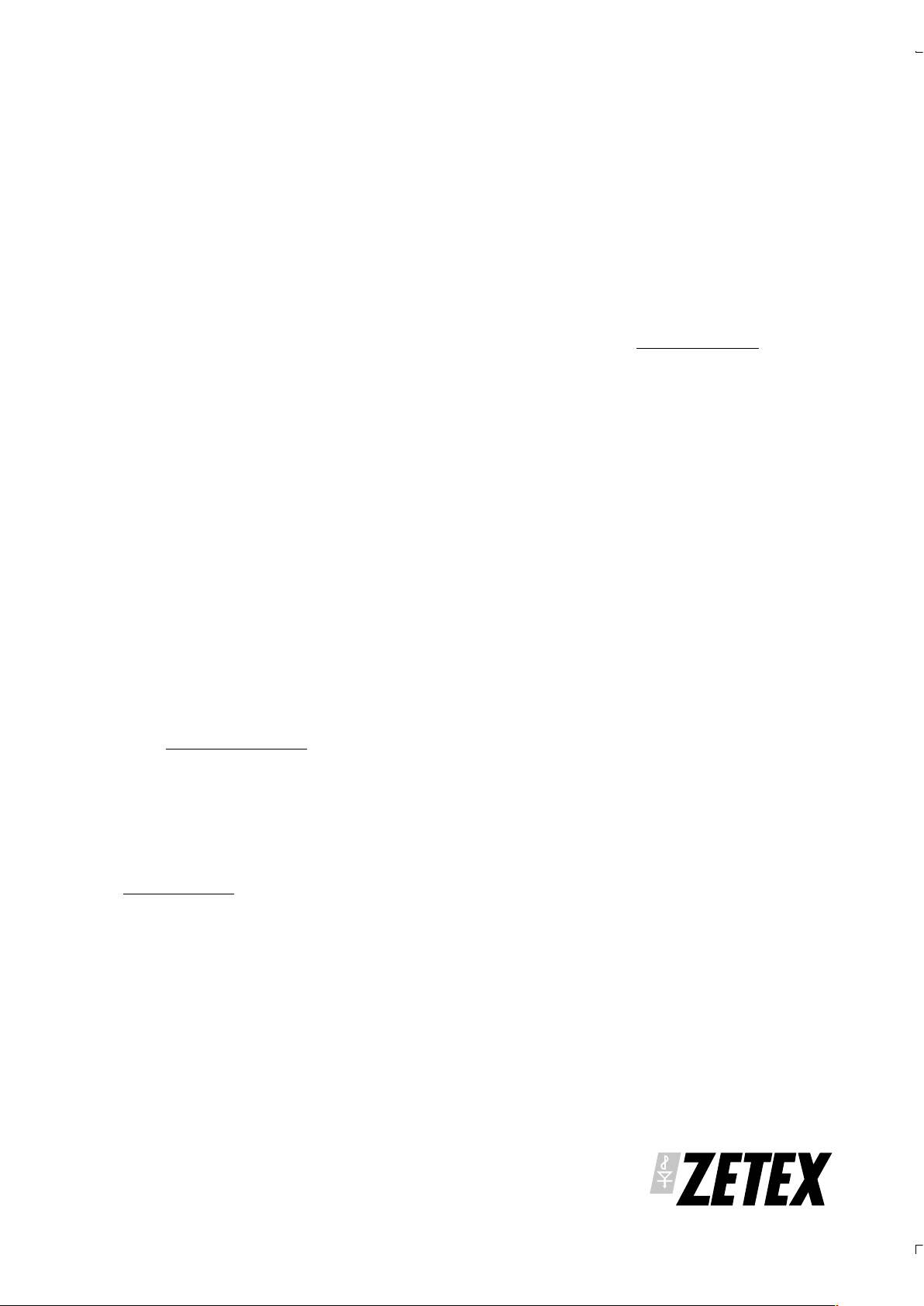

Output Voltage Adjustment

The ZXRD1000 is available as either a fixed 5V, 3.3V or

adjustable output. On fixed output versions, the V

FB

pin

should be connected to th e output. Adjustable operation

requires a resistive divider connected as follows:

The value of the output voltage is determined by the

equation

V

OUT

= VFB (1 +

R

A

R

B

)

V

FB

=1.24V

Note: The adjustable circuit is shown in the following

transient opti misation sect ion. It is also used in t he

evaluation PCB. In both t hese circuit s R

A

is assigned

the label R6 an d R

B

the label R5.

Values of resistor should be bet ween 1k and 20k to

guarantee operation. Output voltage can be adjusted in

the range 2V to 12V for non-synchronous ap plic ations.

For synchronous applications, the minimum V

OUT

is set

by the V

GS

threshold required for the synchronous

MOSFET, as the swing in the gate using the

SimpleSync

TM

technique is approximately V

OUT

.

8

ISSUE 4 - OCTOBER 2000

ZXRD1000 SERIES

Applications (continued)

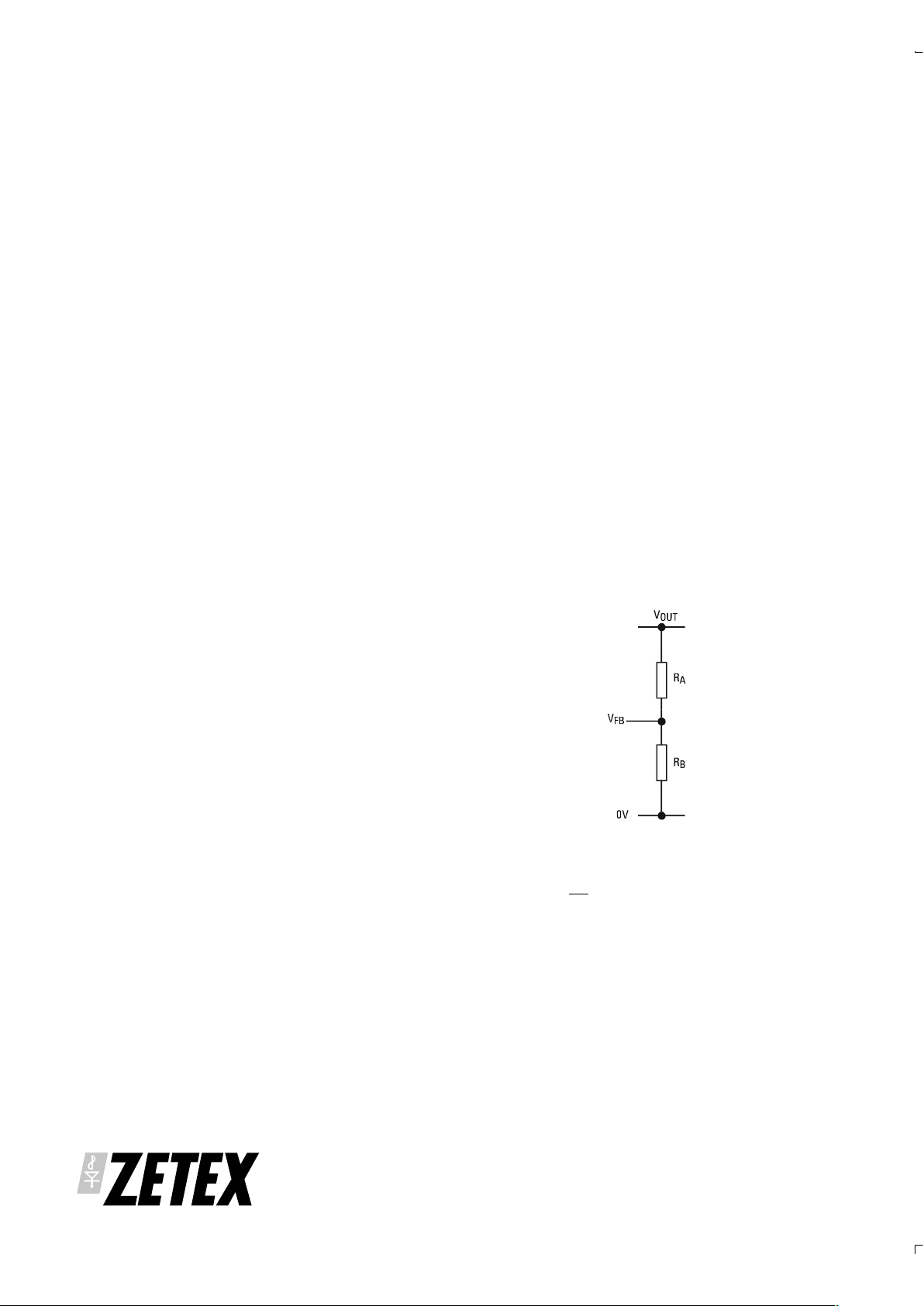

Low Battery Flag

The low battery flag threshold can be set by the user

to trip at a level determined by the equation:

V

LBSET

= 1.25

(

1 +

R

C

R

D

)

RD is recommended to be 10k where RC and RD are

connected as fo llows:

Hysteresis is typically 20mV at the LB

SET

pin.

Current Limit

A current limit is set by the low value resistor in the

output path, R

SENSE

. Since the resistor is only used for

overload current limit, it does not need to be accur ate

and can hence be a low cost device.

The value of the current limit is set by using the

equation:

I

LIM

(A) =

50(mV)

R

SENSE

(mΩ)

A graph of Current Limit v R

SENSE

is shown in the

typical characteristics. This should assist in the

selection of R

SENSE

appropriate to application.

If desired, R

SENSE

can also be on the input supply side.

When used on the i nput side R

SENSE

should be in series

with the upper output device (i.e. in series with the

drain or source in N and P channel solutions

respectively).Typically in this configuration R

SENSE

will

be 20m⍀.

Hiccup Time Constant

The hiccup circuit (at the ’delay’ pin) provides overload

protection for the sol ution. The threshold of the hic cup

mode is determined by the value of R

SENSE,

When

>50mV is developed across the sense resistor, the

hiccup circuit is triggered, inhibiting t he de vice.

It will stay in this state depending upon the time

constant of the resistor and capacitor connected at the

’delay’ pin. In order to keep the dissipation down

under overload conditions it is recommended the

circuit be off for approximately 100ms. If for other

application reasons this is too long an off period, this

can be reduced at least by 10:1, care needs to be taken

that any increased dissipation in the external MOSFET

is still acceptable. The resistor capacitor combin atio n

R1,C1 recommended in the applications circuits

provides a delay of 100ms.

Soft Start & Loop Stability

Soft start is determined by the time constant of the

capacitor and resistor C7 and R3. Typically a good

starting point is C7 = 22µF and R3 = 24k for fixed

voltage variants. For fully adjustable variants see

Optimising for Transient Response later in the

applicati on s sect i on. Th is ne tw or k als o hel ps pr ovi de

good loop stability.

Low Quiescent Shutdown

Shutdown control is provided via the SHDN pin,

putting the device in to a low quiescent sleep mode.

In some circumstances where rapid sequencing of V

CC

can occur (when VCC is turned off and back on) and V

CC

has a very rapid rise time (100-200ms) timing conflicts

can occur.

9

ZXRD1000 SERIES

ISSUE 4 - OCTOBER 2000

Loading...

Loading...