YAMAHA YSS915-M Datasheet

YAMAHA CORPORATION

YSS915

CATALOGUE No:LSI-4SS915A2

1999.09

YSS915

Karaoke Processor 2 for Video disc player

(KP2V2)

INTRODUCTION

YSS915 (KP2V2) is an LSI for processing Karaoke voice signals.

This LSI has an A/D converter (1 channel) for the microphone echo, and a memory for the microphone echo and

key control. These features allow achieving the functions needed for the Karaoke system by using only one LSI

chip. As for the microphone echoes, many other types of echoes are available in addition to ordinary ones so that

YSS915 is applicable to various uses.

In addition to these Karaoke programs, YSS915 is able to provide the Movie & Music programs, with which the

surround effect is applied to the movie and music sources for giving the users more enjoyment.

YSS915 is pin compatible with and register compatible with YSS903 (KP2V).

FEATURES

[

[ [

[ Fundamental Functions ]

Fundamental Functions ]Fundamental Functions ]

Fundamental Functions ]

1)

Karaoke program

•

Key Control (Control by 50 cents in +/- 600 cent range, +/- one octave, etc.)

•

Voice Cancel

Microphone Echo

•

Normal microphone echo (174 msec or less (fs = 44.1 kHz))

•

Stereo-Echo/ Reverb-Echo

•

Microphone Key Control (+/- 10 cents, +/- 20 cents, +/- 400 cents, +/- 700 cents and +/- 1 octave)

•

Microphone "YMERSION™"

Tone Control

•

Bass, Mid-tone, Treble (0 to +/- 10 dB at 2 dB steps)

Surround

•

"YMERSION™" (Yamaha's original wide surround technology)

2) Movie and music program

Surround

•

Initial reflection sound synthesizing system

•

Yamaha "YMERSION™"

Tone Control

•

Bass, Mid-tone, Treble (0 to +/- 10 dB at 2 dB steps)

[

[ [

[ I/O Interface ]

I/O Interface ]I/O Interface ]

I/O Interface ]

•

Digital signal inputs : 2 channels (16/18/20/24 bits)

•

Digital signal outputs : 2 channels (16/18/20/24 bits)

•

Analog signal input : 1 channel ( for the microphone )

•

Microprocessor interface : Serial four line system

•

Through-mode : Digital input is outputted without any processing

(Correspond with fs = 96 kHz 24 bit DVD format)

[

[ [

[

Others

Others Others

Others

]]]]

•

Pin/register upper compatible with YSS903 (KP2V)

•

Sampling frequency : 32, 37.8, 44.1, 48 kHz or correspond with 96 kHz through-mode.

•

Package : 28 pin SOP ( YSS915-M )

YSS915

2

Difference between YSS903 and YSS915

1.

No built-in DAC.

(Refer to the process flow chart in “OPERATIONS”.)

2.

Connectable directly with MSB justified data output ADC.

(Refer to “Format 4” of “4. Digital audio interface” in “ FUNCTIONS”.)

3.

Microphone interface terminals CDI and CDO can be connected on the board.

This feature allows to reduce the number of ports by one.

(Refer to “5. Microcomputer interface” in “ FUNCTIONS”.)

4.

Input fader has been added for the microphone echo.

This feature allows to apply fade-in/fade-out control to the microphone echo through designation with

one bit from the microcomputer.

(Refer to “1. Karaoke program” in “ OPERATIONS”, and “3) VCR ($02)” of “1. Functions” in

“REGISTERS”.)

5.

Zero level detection function has been added for digital audio output.

YSS915 outputs “0” at the pin “ZERO” when an audio input has been zero for a certain period.

This signal can be used to improve S/N ratio by muting the output of external DAC.

(Refer to “6. Others” in “ FUNCTIONS”.)

6.

An output port PO has been added for controlling peripheral devices.

The port “PO” can be used, as an example, to control the gain of audio output amplifier through this

LSI from the microcomputer.

(Refer to “6. Others” in “ FUNCTIONS”.)

7.

A mode with extended band width for microphone echo has been newly added.

Two types of cut-off frequency have been added for the low pass filter.

(Refer to “7) RVR ($06)” and “11) MDR ($1C)” of “1. Functions” in “REGISTERS”.)

8.

Internal DSP has been given the operation accuracy of 20 bits.

Internal multiplier-accumulator become 20bit*13bit=24bit therefore overall bit accuracy become

improved from 18bit(YSS903) to 20bit(YSS915).

In through-mode which internal DSP is not used for processing the accuracy of input data is

maintained to output.

YSS915

3

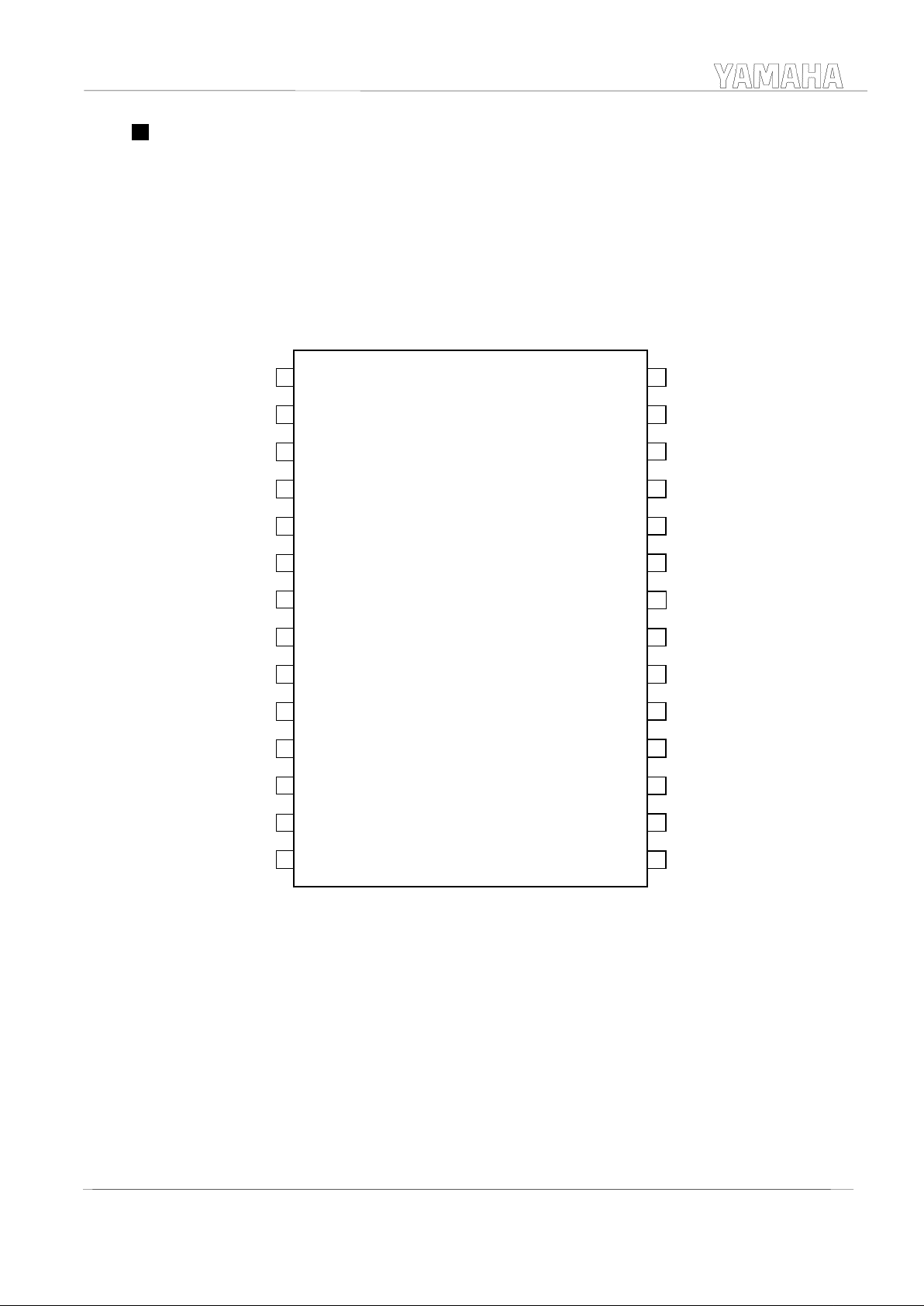

PIN CONFIGURATION

< 28pin SOP Top View >

/IC

/CS

CDI

/SCK

SDSY

DI

BCI

DO

L/R

AOL

VREF

AVSS

AVDD

XI

AOR

DVDD2

DVSS2

BCO

DEPI

DVSS1

DVDD1

ADC1

ADC2

MICIN

CDO

PLLC

P0

1

2

3

4

5

6

7

8

9

10

11

14

12

13

XISEL/ZERO

28

27

26

25

24

23

22

21

20

19

18

17

16

15

YSS915

4

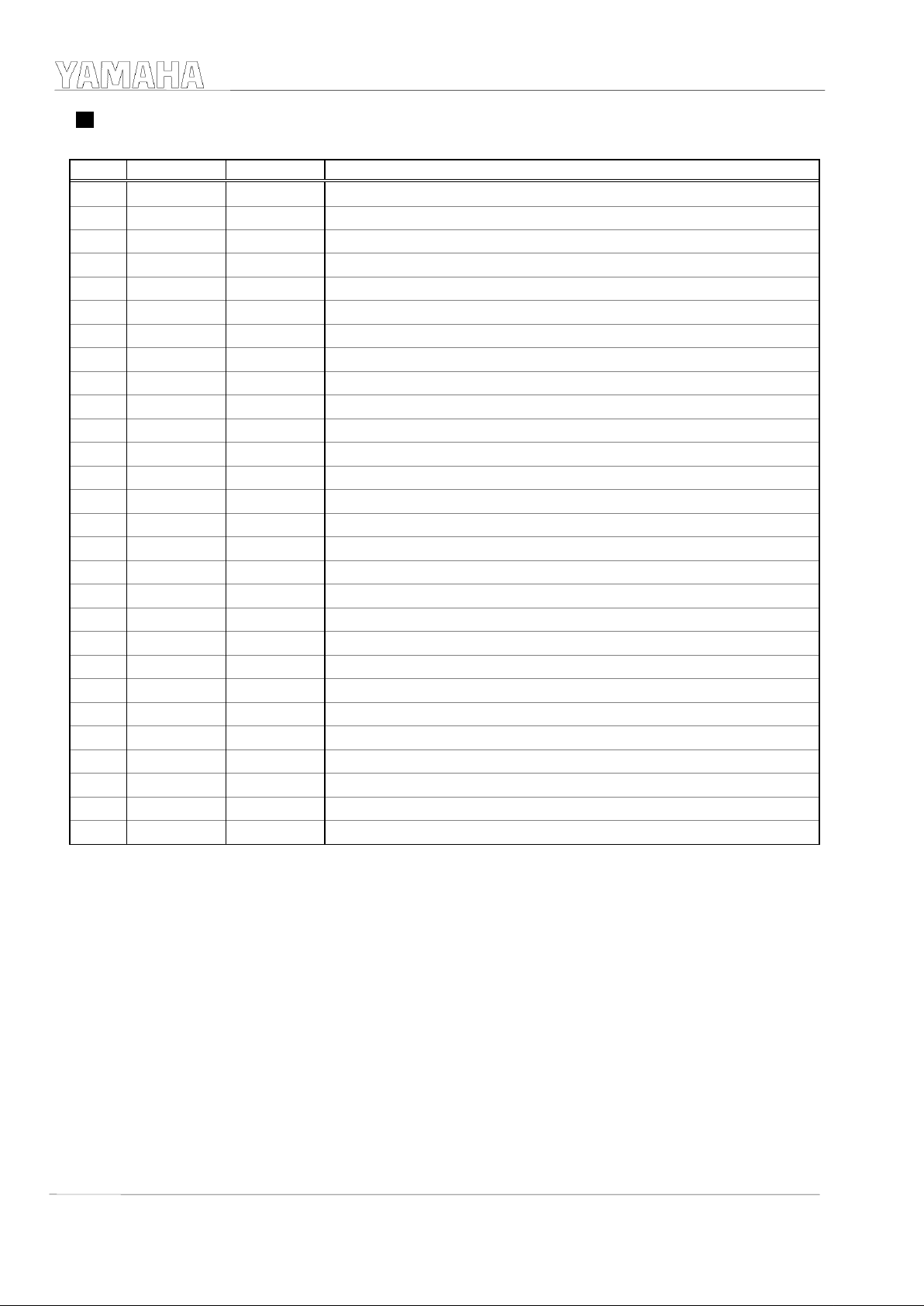

PIN FUNCTION

Notes ;

+ : Pull up

A : Analog terminal

No. Name I/O

(See Note1)

Function

1DI I+

Digital audio input Serial data

2 BCI I+

Digital audio input Bit clock

3DO O+

Digital audio output Serial data

4L/R O

Digital audio output Word clock

5 DVDD1 -

Power supply, +5 V (for digital system)

6 BCO O

Digital audio output Bit clock

7 DVSS1 -

Ground (for digital system)

8 AVDD -A

Power supply, +5 V (for analog system)

9 PLLC -A

Connecting resistor and capacitor for PLL

10 AVSS -A

Ground (for analog system)

11 ADC1 -A

Connecting capacitor for ADC

12 ADC2 -A

Connecting capacitor for ADC

13 VREF OA

Referential voltage output

14 MICIN IA

Analog input, analog voice sign al for m icrophone chan nel

15 AOL OA

Outputs analog voice signal for L channel

16 AOR OA

Outputs analog voice signal for R channel

17 XI I

External clock input

18 /IC I

Initial clear (Low active)

19 DVDD2 -

Power supply, +5 V (for digital system)

20 DEPI I

De-emphasis control (H : On, L : Off)

21 DVSS2 -

Ground (for digital system)

22 XISEL/ZERO I+/O

Switches master clock rate/ZERO output

23 P0 I+/O

Test input terminal /P0 output

24 /CS I

Microcomputer interface input Chip select

25 /SCK I

Microcomputer interface input Serial clock

26 CDI I

Microcomputer interface input Serial data

27 CDO O+

Microcomputer interface output Serial data

28 SDSY I+

Digital audio input Word clock

YSS915

5

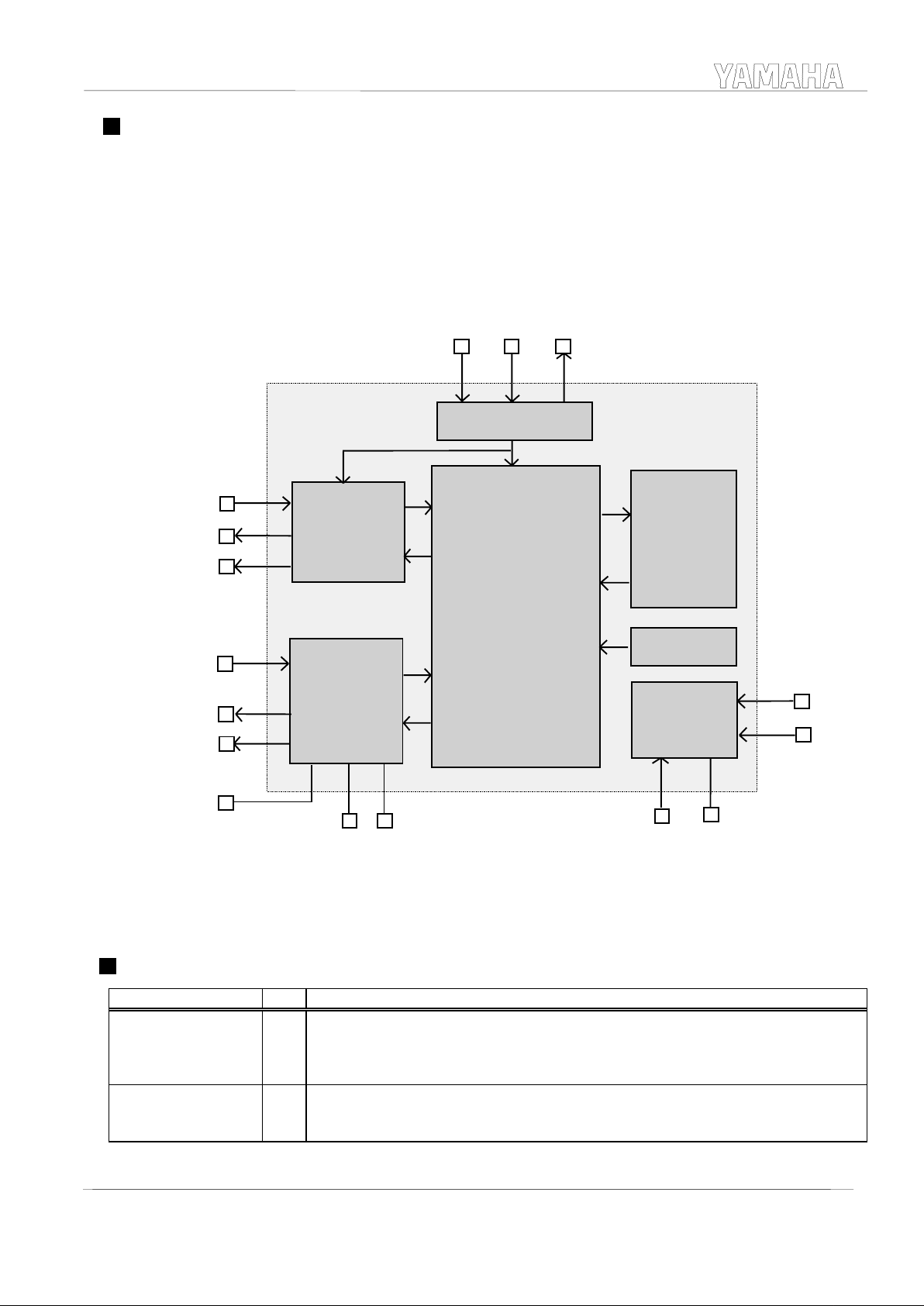

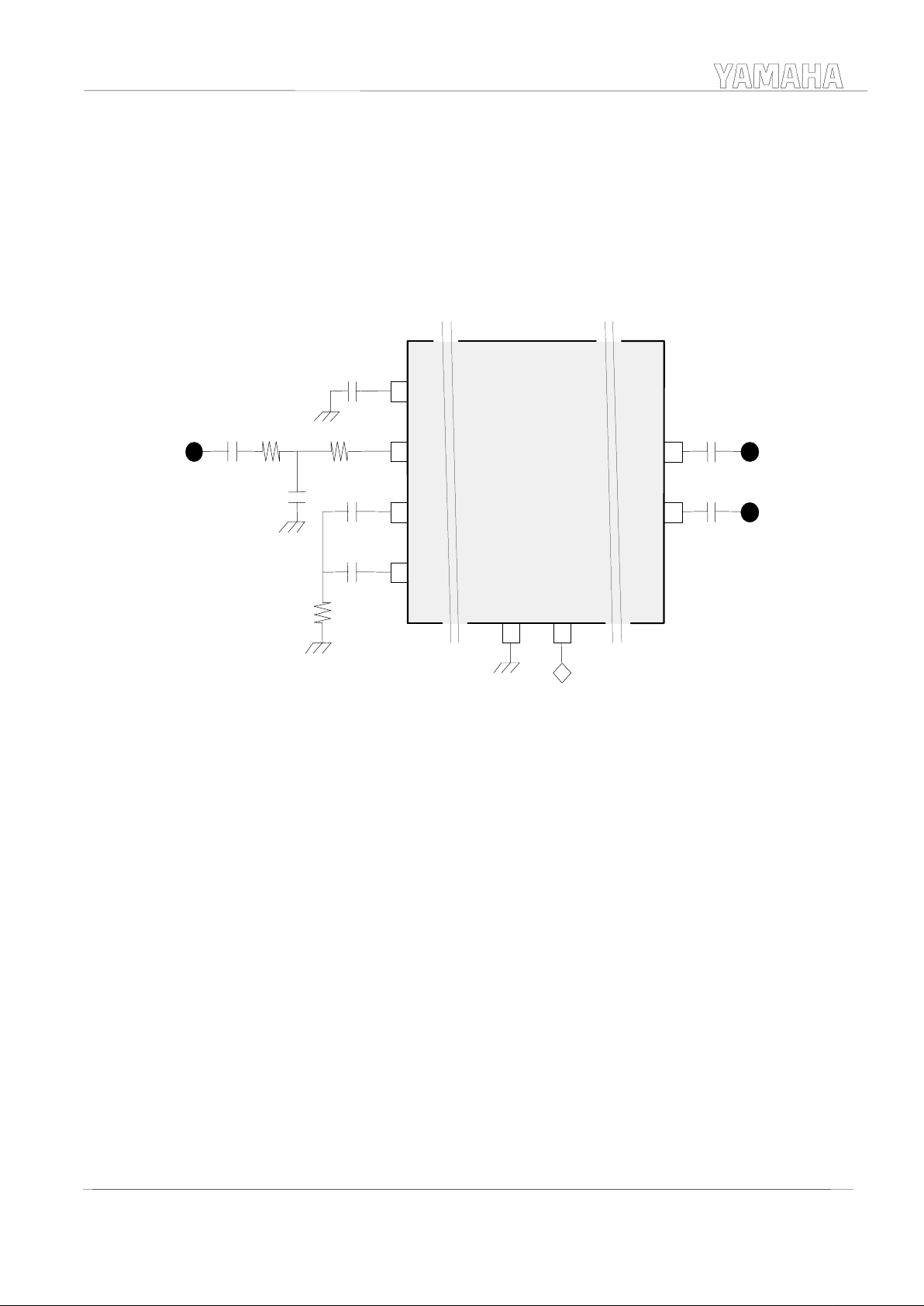

BLOCK DIAGRAM

This LSI has two input channels (L and R) and two output channels (L and R) for digital audio interface. It also has a

one bit Delta-Sigma type AD converter 1 channel (microphone) that performs Delta-Sigma modulation at its analog

block, and decimation/interpolation of 128 times at its DSP.

Karaoke audio signal is processed by DSP for processing Karaoke audio signal and RAM for delay.

For the details of Karaoke audio signal processing, please refer to "OPERATIONS".

The parameters of this LSI are set through CPU interface. For the details of the parameters, please refer to

"REGISTERS".

MODES

Name of mode Code Description

KP2

standard mode

N

The functions of KP2 (YSS216B) can be used. The registers are compatible, except that

the coefficient registers (addresses $27 and $30 to $33) of KP2 that controls the analog

audio input and analog microphone echo output cannot be used because YSS903 does not

have these ports.

KP2V

extended mode

E

Every function of this device can be used.

Analog block

DSP

for dela y

RAM

Digital I/O

Interface

CPU interface

Clock

generator

Program ROM

DEPI

CDI

/SCK

SDSY,DI,BCI

DO,L/R,BCO

AOL

AOR

XI

XISEL

VREF

/IC

CDO

P0

ADC1

MICIN

PLLC

ADC2

ZERO

KP2V2

/CS

YSS915

6

PIN FUNCTIONS

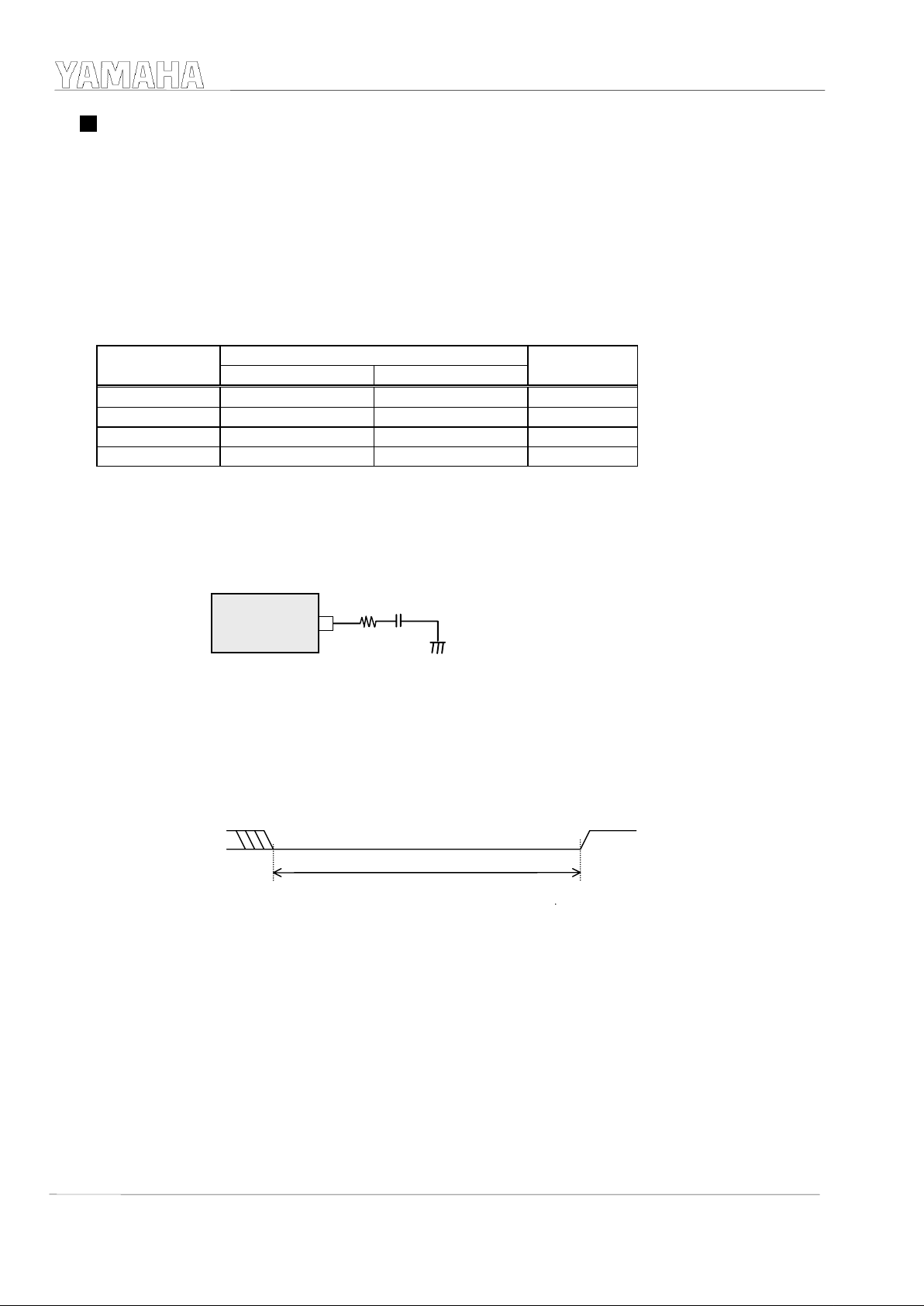

1. Clock signal

XI, XISEL, PLLC

Operation of this LSI requires input of clock with frequency of 384 fs (fs : sampling frequency) or 256 fs to the XI

terminal.

Keep the XISEL terminal open when using with the 384 fs clock.(XISEL pin is pulled up internally.)

Pull down XISEL terminal to the d i gital ground through 4.7 k ohm resistor when using with the 256 fs clock.

The sampling frequency can be selected in the range from 32 kHz to 48 kHz.

The sampling frequency is specified with OPR register ($00).(The sampling frequency of fs = 32 or 48 kHz can be

specified only KP2V Extended mode.)

In addition, the thing that input 3 7MHz in XI by a maximum is possible in only through-mode.

Connect a resistor and capacitor to PLLC terminal as shown below for adjustment of PLL in the LSI.

2. Initial clear

/IC

This LSI requires initial clear at power on. The initial clear is performed by inputting "L" to /IC terminal.

Note ;

N = KP2

standard mode

E = KP2V

extended mode

Sampling XI input frequency Available mode

frequency (fs) 384fs 256fs

(See Note.)

32.0 kHz

12.288 MHz 8.192 MHz

E

37.8 kHz

14.5152 MHz 9.6768 MHz

N,E

44.1 kHz

16.9344 MHz 11.2896 MHz

N,E

48.0 kHz

18.432 MHz 12.288 MHz

E

/IC

2msec min

PLLC

KP2

2

YSS915

7

3. Analog audio interface

MICIN, ADC1, ADC2, AOL, AOR, VREF

This LSI has a one channel (MIC input) of Delta-Sigma type A/D converter, thus requiring the external circuits as

described below.

The output of AOL and AOR can be used as a direct signal from the microphone because the volume of the signal is

controlled as analog signal which is outputted from AOL and AOR.

MIC

MICIN

ADC1

ADC2

VREF

AO

L

AOR

AVS S

A VDD

KP2V2

AOL

AOR

Analog input section Analog output section

Other section

YSS915

8

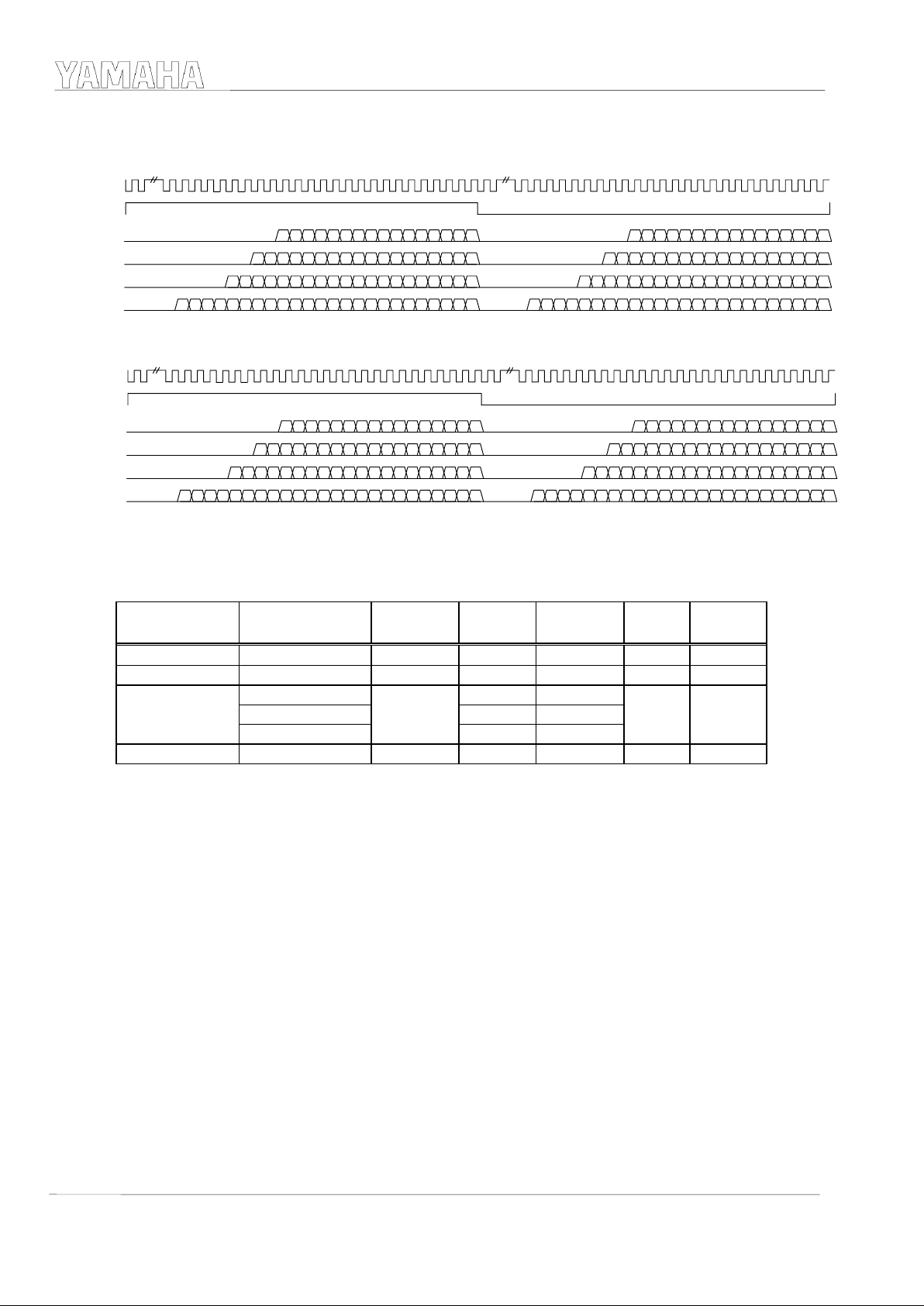

4. Digital audio interface

SDSY, BCI,DI, L/R,DO,BCO

-

1) Digital audio signal is inputted through BCI, SD SY and DI pins using the follo wing format.

-

2) Digital audio signal is outputted through BCO, L/R, and DO pins using the following format.

-

3) The digital audio interface is made compatible with the following format with OPR register ($00) and DAR register

($04).

N=KP2 standard mode

E=KP2V extended mode

Format1

Use this format when digital audio input is not used.

Format2

Use this format when digital audio input is used.

BCI is able to accept any frequency between including 96fs from 32fs, while BCO outputs only 64 fs.

BCI, SDSY and DI signals must be synchronized with XI clock.

Format3

Use this format when digital audio input is used.

BCI input signal is passed to the BCO output, being inverted.

SDSY input signal is passed to the L/R output, being delayed by 2.5 clocks of BCI.

BCI, SDSY and DI signals must be synchronized with XI clock.

Format BCI BCO OPR

[5]

DAR

[3:2]

MDR

[3]

Available

mode

Format1

- 64fs 1 * 0 N,E

Format2

32-96fs 64fs 0 0 0 N,E

64fs 0 1

Format3

48fs BCI 0 2 0 E

03

Format4

- 64fs 0 * 1 E

BCI

SDSY

0

1 2

3

4 5 6 7 8

9

101112131415

0 1 2 3 4 5 6 7 8 91011

1213

1415DI(16bit)

DI(18bit)

DI(20bit)

DI(24bit)

Lch Rch

0

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

1415

0

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

1415

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

141516

17

18

19

2021

22

23

16

17

18

19

16

17

16

17

18

19

2021

22

23

16

17

18

19

16

17

0

BCO

L/R

0

1 2

3

4 5 6 7 8

9

101112131415

0 1 2 3 4 5 6 7 8 91011

1213

1415DO(16bit)

DO(18bit)

DO(20bit)

DO(24bit)

Lch Rch

0

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

1415

0

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

1415

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

141516

17

18

19

2021

22

23

16

17

18

19

16

17

16

17

18

19

2021

22

23

16

17

18

19

16

17

0

YSS915

9

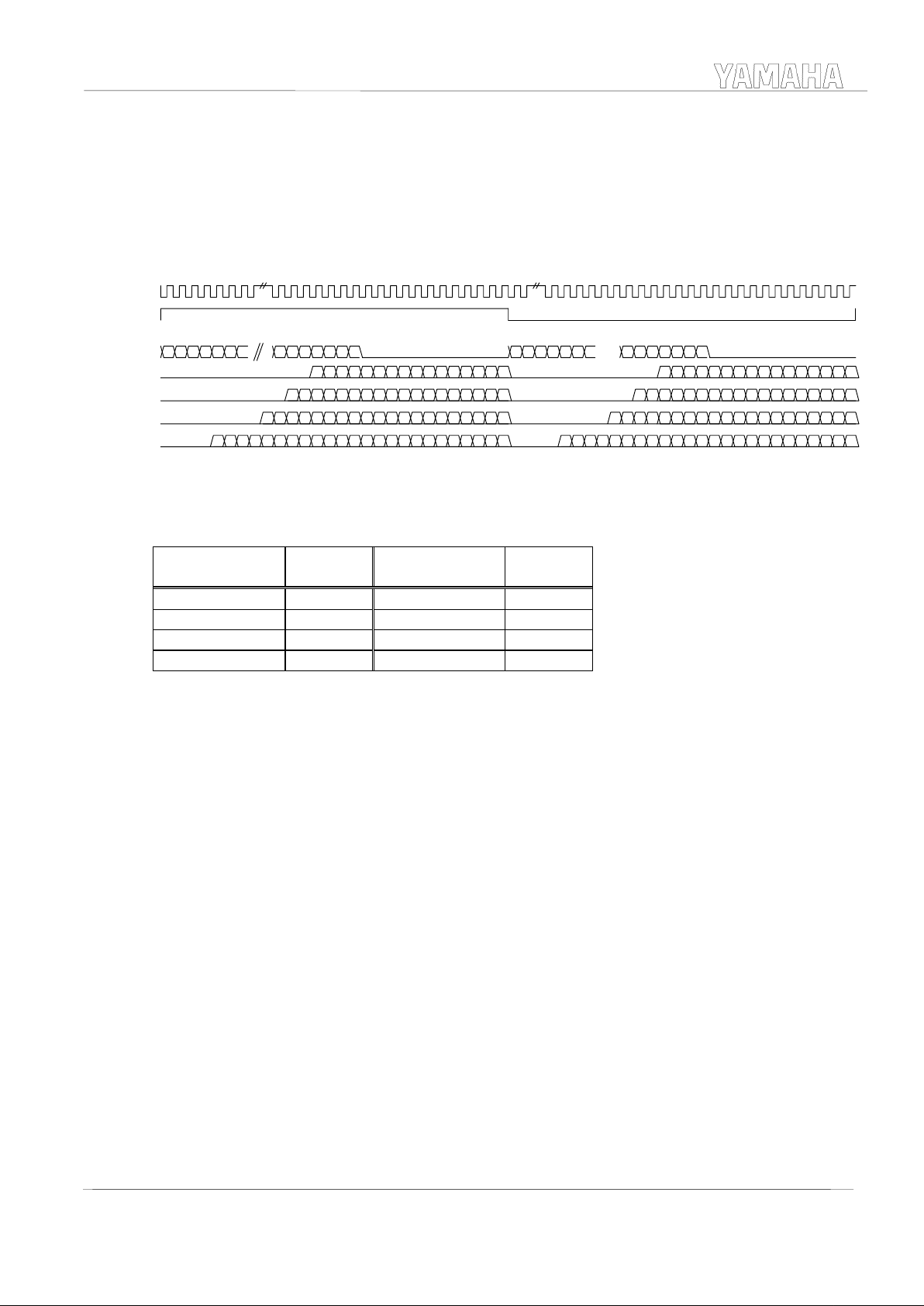

Format4

This format is used to interface with the A/D converter which outputs data MSB justified.

Connect BCO pin of this LSI to the bit clock input pin of the A/D converter, L/R pin to LR clock input pin of the

converter, and DI pin to data output pin of the converter.

BCO outputs 64 fs without regarding to the value of DAR[3:2].

Keep the pins BCI and SDSY open.

The format 4 is as described below.

-

4) Length of data word of the digital audio signal can be set by the DAR register ($04) to 16, 18, 20 or 24 bits (only in

KP2V extended mode). When the data word is 24 bit long, only upper 20 bits are used for p r ocessing internal signal.

Note ; In KP2 standard mode, both of the input and output word lengths are only 16 bits.

-

5) The through-mode can be selected by using DAR register ($04) (only in KP2V extended mode).

In the through-mode ;

BCI input signal is passed to the BCO output, being inverted.

SDSY input signal is passed to the L/R output, being delayed by 2.5 clocks of BCI.

DI input signal is passed to the DO output, being delayed by 2.5 clocks of BCI.

When the sampling frequency is in the range from 64 kHz to 96 kHz, the input signal can be passed through this

LSI without deteriorating, for example, the 24 bit data accuracy at the sampling frequency of 96 kHz.

The through-mode is enabled when the value of DAR[bit3:2] is “01”, “10” o r 11”.

Length of

inputted

word

DAR

[5:4]

Length of

outputted word

DAR

[1:0]

16bit 0 16bit 0

18bit 1 18bit 1

20bit 2 20bit 2

24bit 3 24bit 3

BCO

L/R

0

1 2

3

4 5 6 7 8

9

101112131415

0 1 2 3 4 5 6 7 8 91011

1213

1415DO(16bit)

DO(18bit)

DO(20bit)

DO(24bit)

Lch Rch

DI

MSB LSB

MSB LSB

01 31 0 1

0

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

1415

0

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

1415

0

1 2

3

4 5 6 7 8

9

101112131415 0 1 2 3 4 5 6 7 8 91011

1213

141516

17

18

19

2021

22

23

16

17

18

19

16

17

16

17

18

19

2021

22

23

16

17

18

19

16

17

YSS915

10

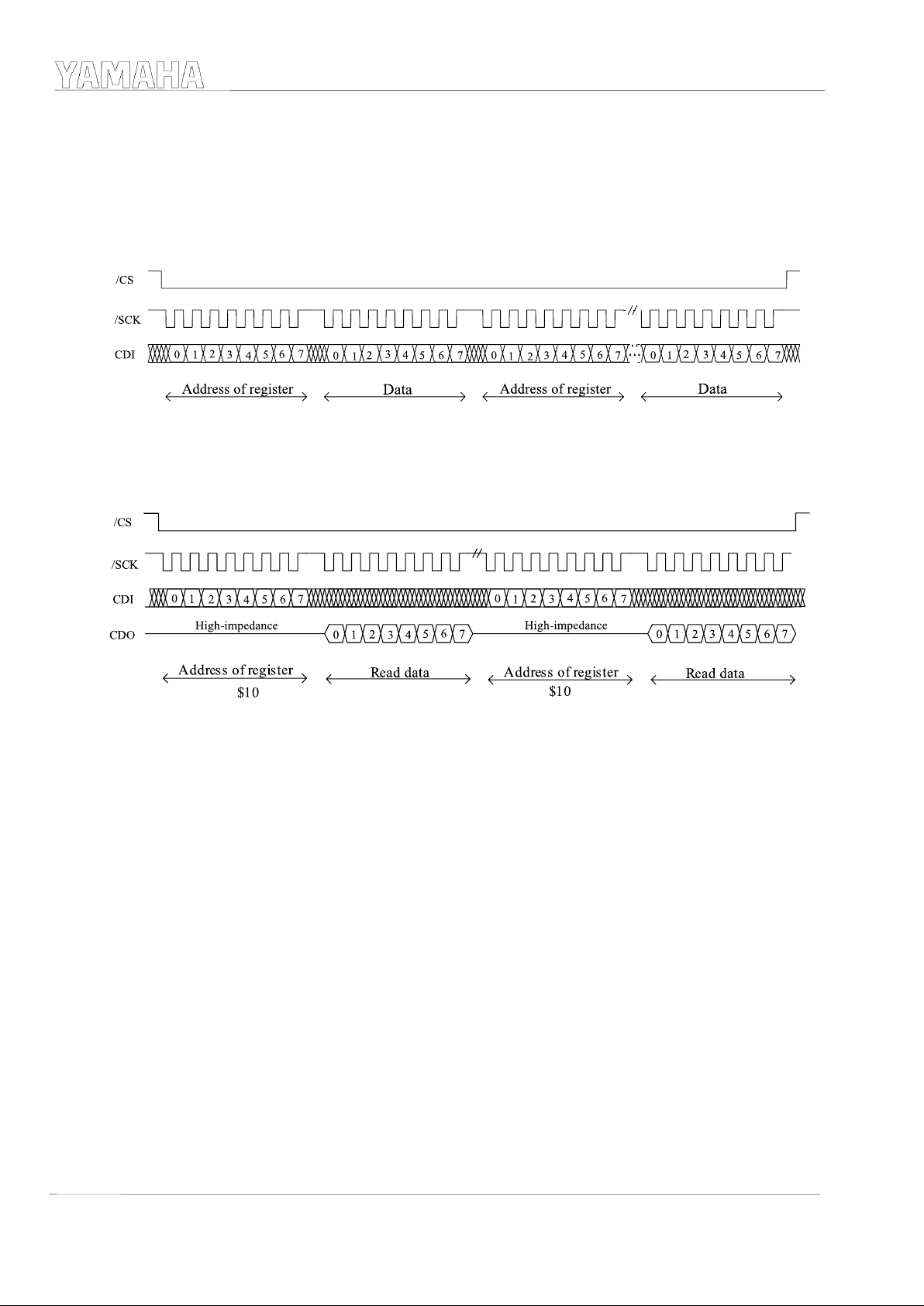

5. Microcomputer interface

/CS, /SCK, CDI, CDO, DEPI

These are 8 bit serial interface for writing data into or reading data from internal registers of this device.

Do not write or read data into or from this device in 200 msec from the initial clear moment (rise moment of /IC).

-

1)

Writing data

Set the address of an internal register into the first byte, and data into the second byte.

Use the following format.

-

2)

Reading data

(only in KP2V extended mode)

For reading data, only MLR register ($10) is provided.

Use the following format.

-

3)

DEPI

When DEPI is "H", de-emphasis is enabled regardless of the state of internal register.

When DEPI is "L", setting of OPR register ($00) is valid.

6. Others P0 ,ZERO

-

1)

P0

P0 pin outputs the value of the register PHC[0]($08). This value is outputted when OPR($00) has been set after the

initial clear. This pin is in High-impedance state until OPR($00) is set.

This function is valid when MDR[0]($1C) is ‘H’. When MDR[0]($1C) is ‘L’, this pin always outputs ‘L’ like

YSS903 does.

-

2)

ZERO

When both of the digital audio outputs, L and R, have been “zero(0)” for the period equivalent to 511 samplings, the zero

level detection function activates to make ZERO pin output ‘L’ . In other period, this pin is in ‘H’ state.

This value is outputted when OPR($00) has been set after the initial clear. This pin is in HZ state until OPR($00) is set.

This function is valid when MDR[1]($1C) is ‘H’. When MDR[1]($1C) is ‘L’, this pin always outputs ‘L’ like

YSS903 does.

Loading...

Loading...