Page 1

POWER AMPLIFIER

SERVICE MANUAL

SERVICE MANUAL

PX10

PX8

CONTENTS(目次)

SPECIFICATIONS(総合仕様) ....................................3

PANEL LAYOUT(パネルレイアウト) ..............................6

DIMENSIONS(寸法図) ............................................... 7

JACK AND PLUG LIST(端子とプラグ一覧) .................. 8

CIRCUIT BOARD LAYOUT(ユニットレイアウト) ..............9

DISASSEMBLY PROCEDURE(分解手順) ............... 10

LSI PIN DESCRIPTION(LSI端子機能表) ................. 18

CIRCUIT BOARDS(シート基板図) .............................21

INSPECTION(検査) ............................................ 32/61

MEASUREMENT(測定) ...................................... 53/82

UPDATING FIRMWARE(ファームウェアのアップデート)

DEVICE BACKUP(デバイスバックアップ) .................. 90

... 60/89

PX5

PX3

INITIALIZING THE PX AMPLIFIER

(PXアンプの初期化) .................................................. 92

FUNCTION LIST(機能一覧).......................................94

MESSAGE LIST(メッセ ージリスト)............................96/97

START-UP SEQUENCE(起動シーケンス) ........... 99/100

ENDING SEQUENCE(終了シーケンス) .............101/102

PARTS LIST

BLOCK DIAGRAM(ブロックダイアグラム )

LEVEL DIAGRAM(レベルダイアグラム)

WIRING(結線図)

CIRCUIT DIAGRAM(回路図)

PA

012180

HAMAMATSU, JAPAN

Copyright (c) Yamaha Corporation. All rights reserved. PDF ’16.10

Page 2

PX10/PX8/PX5/PX3

IMPORTANT NOTICE

This manual has been provided for the use of authorized Yamaha Retailers and their service personnel. It has been assumed that basic service procedures inherent to the industry, and more specifically Yamaha Products, are already known and understood by the users, and have

therefore not been restated.

WARNING : Failure to follow appropriate service and safety procedures when servicing this product may result in personal injury, de-

IMPORTANT : This presentation or sale of this manual to any individual or firm does not constitute authorization certification, recog-

The data provided is believed to be accurate and applicable to the unit(s) indicated on the cover. The research engineering, and service

departments of Yamaha are continually striving to improve Yamaha products. Modifications are, therefore, inevitable and changes in

specification are subject to change without notice or obligation to retrofit. Should any discrepancy appear to exist, please contact the

distributor’s Service Division.

WARNING : Static discharges can destroy expensive components. Discharge any static electricity your body may have accumulated by

struction of expensive components and failure of the product to perform as specified. For these reasons, we advise all

Yamaha product owners that all service required should be performed by an authorized Yamaha Retailer or the appointed

service representative.

nition of any applicable technical capabilities, or establish a principal-agent relationship of any form.

grounding yourself to the ground bus in the unit (heavy gauge black wires connect to this bus.)

IMPORTANT : Turn the unit OFF during disassembly and parts replacement. Recheck all work before you apply power to the unit.

WARNING: This product contains chemicals known to the State of California to cause cancer, or birth defects or other reproductive harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON WHAT SO EVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or expose eyes to solder/ flux

vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before handling food.

IMPORTANT NOTICE FOR THE UNITED KINGDOM

Connecting the Plug and Cord

WARNING: THIS APPARATUS MUST BE EARTHED IMPORTANT. The wires in this mains lead are coloured in accordance with

the following code:

GREEN-AND-YELLOW : EARTH

BLUE : NEUTRAL

BROWN : LIVE

As the colours of the wires in the mains lead of this apparatus may not correspond with the coloured markings identifying the

terminals in your plug proceed as follows:

The wire which is coloured GREEN-and-YELLOW must be connected to the terminal in the plug which is marked by the letter E

or by the safety earth symbol

The wire which is coloured BLUE must be connected to the terminal which is marked with the letter N or coloured BLACK.

The wire which is coloured BROWN must be connected to the terminal which is marked with the letter L or coloured RED.

or colored GREEN or GREEN-and-YELLOW.

(3 wires)

WARNING

Components having special characteristics are marked and must be replaced with parts having specification equal to those

originally installed.

印の部品は、安全を維持するために重要な部品です。交換する場合は、安全のために必ず指定の部品をご使用ください。

WARNING

Please keep the USB cap out of reach of children, to keep them from accidentally swallowing it.

USBキャップは、子供が誤って飲み込まないように、子供の手の届かないところに保管してください。

mark indicates a dangerous electrically live terminal. When connecting an external wire to

This

this terminal, it is necessary either to have “a person who have received appropriate guidance on

handling” make the connection or to use leads or a cord that have been manufactured in such a

way that the connection can be made simply and without problem.

マークは、危険活電部であることを示します。この端子への外部からの配線接続は、適正な取扱指導を

受けた者が行なうか、問題なく容易に接続できるように製作されたリ−ド線、またはコードを使用する

必要があります。

2

Page 3

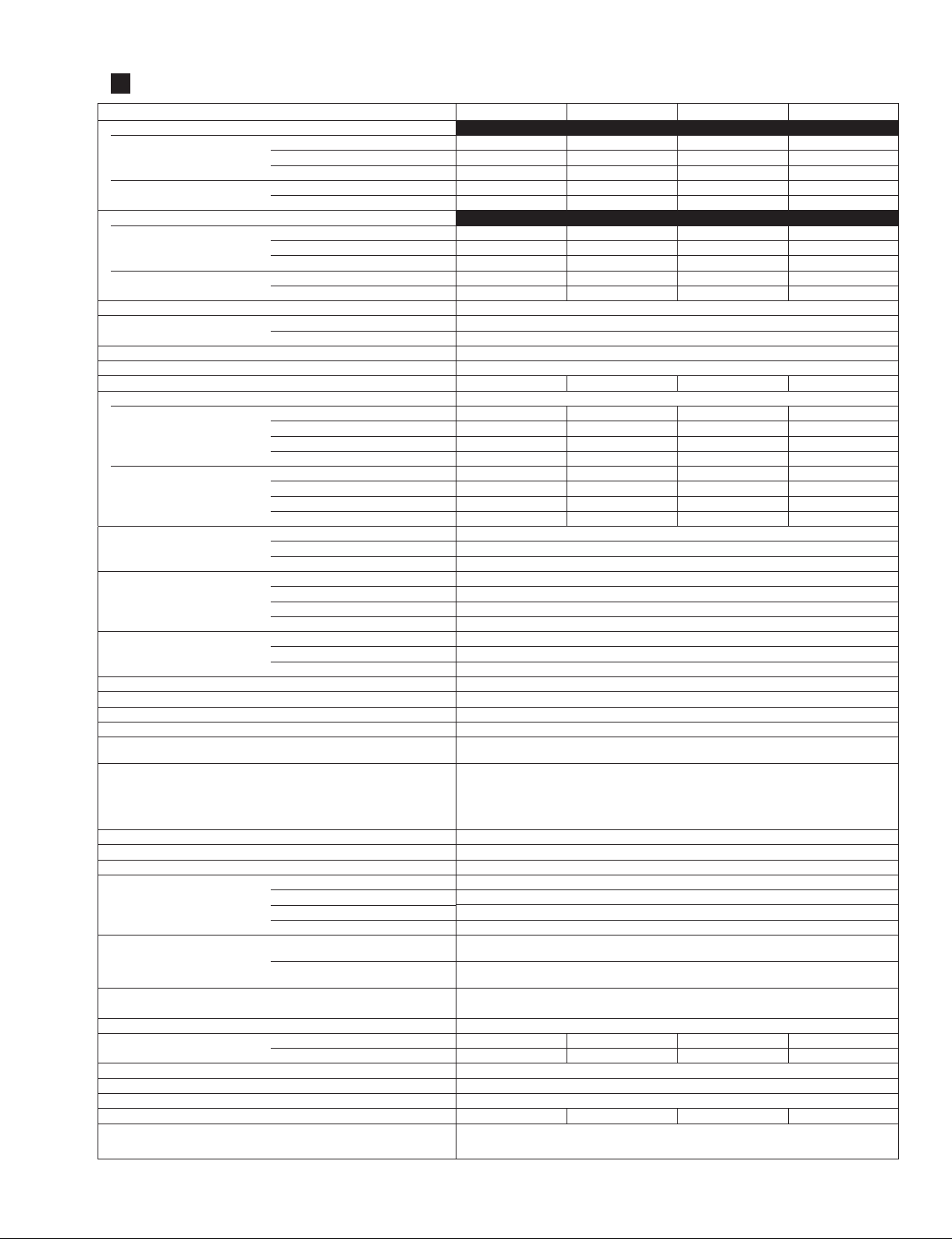

SPECIFICATIONS(総合仕様)

Output Power

1 kHz, non-clip, 20 msec burst,

both channels driven

1 kHz, non-clip, 20 msec burst

Output Power

1 kHz, non-clip, 20 msec burst,

both channels driven

1 kHz, non-clip, 20 msec burst

Amplifier Type (Output Circuitry)

THD+N

Frequency Response

Crosstalk

S/N Ratio

Voltage Gain/Sensitivity

8Ω, volume max.

8Ω, volume max.,

Power Boost mode

Load Protection

Amplifier Protection

Power Supply Protection

Cooling

Maximum Input Voltage

Input Impedance

Sampling Frequency

A/D, D/A Converters

Signal Processing

Latency

User Amplifier Preset

Factory Speaker Preset

Connectors

Controls

Indicators

AC Power Requirement

Power Consumption

Operating Temperature

Storage Temperature

Dimensions (W × H × D)

Net Weight

Included accessories

*1 Device operation has been confirmed within ±10% of the rated power supply voltage.

(出力)

(出力)

(全高調波歪率)

(周波数特性)

(クロストーク)

(S/N 比)

(負荷保護)

(アンプ保護)

(冷却)

(入力インピーダンス)

(サンプリング周波数)

(AD、DA コンバーター)

(信号処理)

(遅延)

(端子)

(操作子)

(インジケーター)

(消費電力)

(保存温度)

(質量)

8Ω 1000 W × 2 800 W × 2 500 W × 2 300 W × 2

4Ω 1200 W × 2 1050 W × 2 800 W × 2 500 W × 2

2Ω 700 W × 2 600 W × 2 500 W × 2 300 W × 2

8Ω/Power Boost Mode — — 800 W × 1 600 W × 1

4Ω/Power Boost Mode — — 1400 W × 1 1000 W × 1

8Ω 1000 W × 2 800 W × 2 500 W × 2 300 W × 2

4Ω 1200 W × 2 1050 W × 2 800 W × 2 500 W × 2

2Ω 700 W × 2 600 W × 2 500 W × 2 300 W × 2

8Ω/Power Boost Mode — — 800 W × 1 600 W × 1

4Ω/Power Boost Mode — — 1200 W × 1 1000 W × 1

(増幅方式(出力回路))

1 kHz, 10 W 0.1%

1 kHz, half power 0.3%

1 W, 8Ω, 20 Hz to 20 kHz ±1.0 dB

Half power, 8Ω, 1 kHz, vol. max., input 150Ω shunt

A-weighted, 8Ω, gain setting = +14 dBu

(電圧利得 / 感度)

(電源保護)

(最大入力電圧)

(ユーザーアンププリセット)

(出荷時スピーカープリセット)

(電源条件)

(使用温度)

(外形寸法)

(付属品)

Gain setting: 32 dB 32.0 dB/+9.3 dBu 32.0 dB/+8.3 dBu 32.0 dB/+6.3 dBu 32.0 dB/+4.1 dBu

Gain setting: 26 dB 26.0 dB/+15.3 dBu 26.0 dB/+14.3 dBu 26.0 dB/+12.3 dBu 26.0 dB/+10.1 dBu

Gain setting: +4 dBu 37.3 dB/+4 dBu 36.3 dB/+4 dBu 34.3 dB/+4 dBu 32.1 dB/+4 dBu

Gain setting: +14 dBu 27.3 dB/+14 dBu 26.3 dB/+14 dBu 24.3 dB/+14 dBu 22.1 dB/+14 dBu

Gain setting: 32 dB — — 34.0 dB/+6.3 dBu 35.0 dB/+4.1 dBu

Gain setting: 26 dB — — 28.0 dB/+12.3 dBu 29.0 dB/+10.1 dBu

Gain setting: +4 dBu — — 36.3 dB/+4 dBu 35.1 dB/+4 dBu

Gain setting: +14 dBu — — 26.3 dB/+14 dBu 25.1 dB/+14 dBu

POWER switch on/off Output mute

Output voltage protection Over voltage limiter, user configurable by wattage and speaker preset

DC-fault Power supply shutdown (NOT restored automatically)

Thermal Output limiter (Restored automatically) → Output mute (Restored automatically)

Over current Output mute (Restored automatically)

Over voltage Output limiter (Restored automatically)

Integrated Power Limit Output limiter (Restored automatically)

Thermal Output limiter (Restored automatically) → Power supply shutdown

Over voltage Power supply shutdown

Over current Power supply shutdown

Analog input to speakers 1.5 msec

Analog input XLR-3-31 × 2, 1/4" PHONE(TRS) × 2

Speakers Neutrik speakON NL4 × 2, binding post × 2 pairs, 1/4" PHONE(TS) × 2

AC IN AC inlet × 1 with AC cord clamp

USB

Front Panel

Display

1/8 MAX power, 4Ω, Pink noise at all channels

Idle, 4Ω 60 W 60 W 55 W 55 W

(定格電源電圧の± 10% の電圧で動作することを確認しています。)

PX10/PX8/PX5/PX3

PX10 PX8 PX5 PX3

Class D, balanced output circuit (BTL)

101 dB

HPF/LPF: cutoff frequency 20 Hz–20 kHz with polarity control

USB 2.0 Standard-A connector (female) for save/load, speaker preset update, firmware update with USB flash drive

POWER switch, 31 step volume knob × 2, rotary encoder and switches for GUI control

Operation lock feature (Full lock or Lock except volume and mute)

POWER × 1 (green), ALERT × 1 (red), USB × 1 (green), PROTECT × 2 (red), CLIP/LIMIT × 2 (red),

Depending on area of purchase; 100 V 50 Hz/60 Hz, 120 V 60 Hz, 220 V-240 V 50 Hz/60 Hz

310 W 280 W 230 W 160 W

7.4 kg (16.31 lbs) 7.2 kg (15.87 lbs) 6.9 kg (15.21 lbs) 6.9 kg (15.21 lbs)

• AC power cord • Owner’s Manual • Technical Specifications (English) • AC plug clamp • USB cap

(•電源コード•3芯−2芯変換プラグ•取扱説明書•TechnicalSpecifications(スペックシート、英文)

120 V 60 Hz, 220 V-240 V 50 Hz/60 Hz

100 V 50 Hz/60 Hz

(ClassD、バランス出力回路(BTL))

-60 dB

101 dB 100 dB 100 dB

16 step variable speed fan × 2, front to rear airflow

20 kΩ (Balance), 10 kΩ (Unbalance)

AD: 24-bit linear, 128 times over sampling

DA: 24-bit linear, 128 times over sampling

D-CONTOUR: FOH/MAIN, MONITOR, OFF

Speaker processor: 6 band PEQ + Limiter + Delay

Speaker presets for Yamaha passive speakers

128 × 64 pixel, mono color with brightness adjustment

SIGNAL × 2 (green),Auto LED off feature

480 × 88 × 388 mm (18.90 × 3.46 × 15.28 inch)

•電源コード誤脱防止クランプ•USBキャップ)

≦

+24 dBu

48 kHz

Input summing

Delay: 0–74msec

8 user amplifier presets

Auto display off feature

0°C to +40°C

-20°C to +60°C

*1

3

Page 4

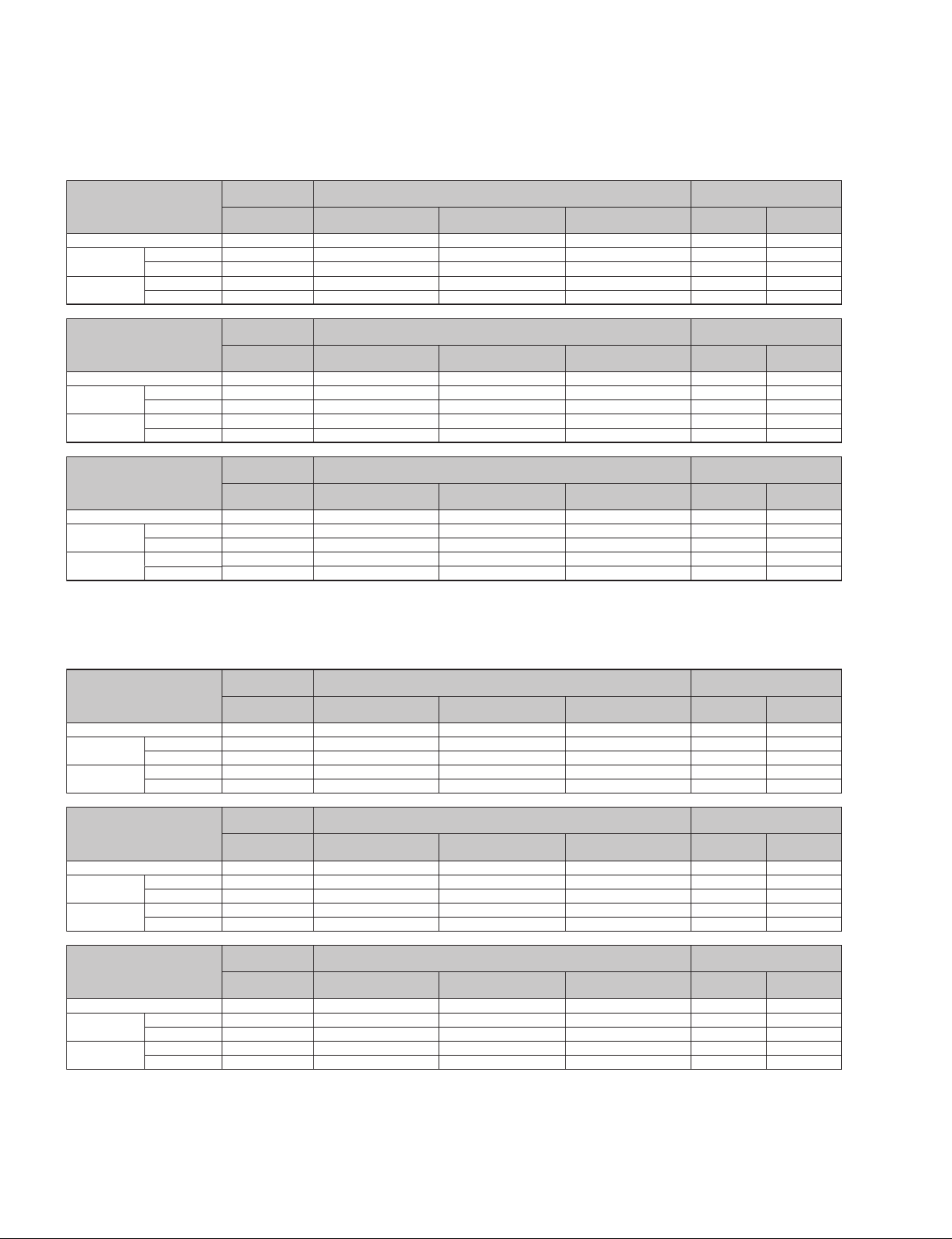

PX10/PX8/PX5/PX3

Current draw and thermal dissipation

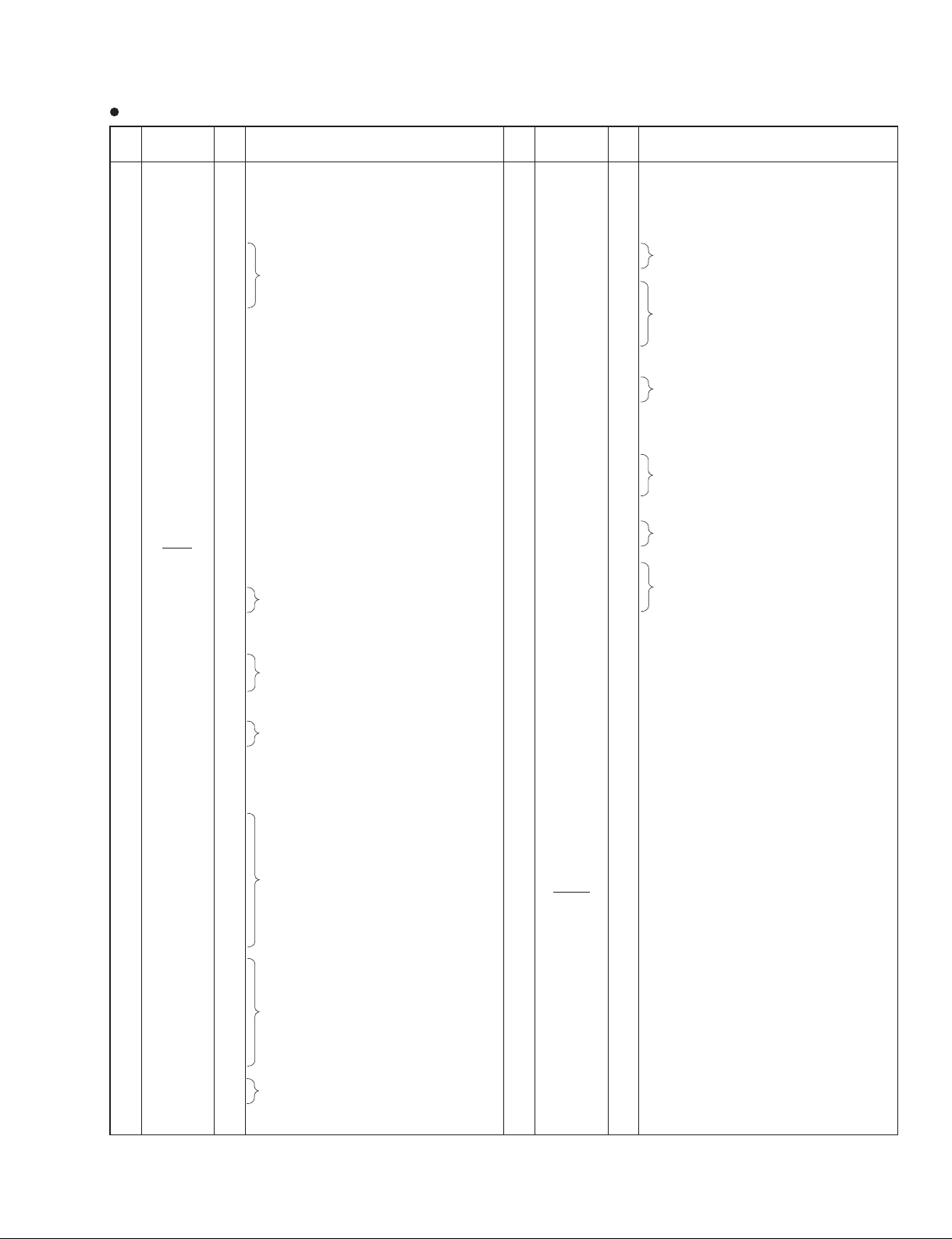

•

(消費電流と熱放散)

Testsignal:Pinknoise(bandwidthlimitedfrom22Hzto22kHz),1Btu=1,055.06J=0.252kcal,(W)×0.86=kcal

(テスト信号:ピンクノイズ(22Hz から 22kHz に帯域制限 )、1BTU=1,055.06J=0.252kcal、1W=0.86kcal)

●

PX10

Idle

(アイドル)

1/8 out

1/3 out

Idle

(アイドル)

1/8 out

1/3 out

Idle

(アイドル)

1/8 out

1/3 out

Line current (A)

100 V/50 Hz

8Ω/ch 2.6 213 125 88 300 76

4Ω/ch 3.1 261 150 111 379 95

8Ω/ch 5.6 472 333 139 474 120

4Ω/ch 7.2 608 400 208 710 179

110 V-120 V/60 Hz

8Ω/ch 2.2 213 125 88 300 76

4Ω/ch 2.7 263 150 113 386 97

8Ω/ch 4.6 466 333 133 454 114

4Ω/ch 5.9 597 400 197 672 169

220 V-240 V/50 Hz

8Ω/ch 1.4 219 125 94 321 81

4Ω/ch 1.6 271 150 121 413 104

8Ω/ch 2.7 471 333 138 471 119

4Ω/ch 3.3 602 400 202 689 174

(線電流)

100 V

0.8 57 0 57 195 49

Line current (A)

(線電流)

120 V

0.7 60 0 60 205 52

Line current (A)

(線電流)

230 V

0.5 62 0 62 212 53

Power consumption (In)

(消費電力)

Power consumption (In)

(消費電力)

Power consumption (In)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watts dissipated

(放散電力)

Watts dissipated

(放散電力)

Watts dissipated

(放散電力)

Thermal dissipation

(熱放散)

Btu/h kcal/h

Thermal dissipation

(熱放散)

Btu/h kcal/h

Thermal dissipation

(熱放散)

Btu/h kcal/h

●

PX8

Idle

1/8 out

1/3 out

Idle

1/8 out

1/3 out

Idle

1/8 out

1/3 out

(アイドル)

110 V-120 V/60 Hz

(アイドル)

220 V-240 V/50 Hz

(アイドル)

Line current (A)

100 V/50 Hz

8Ω/ch 2.2 178 100 78 266 67

4Ω/ch 2.9 237 131 106 362 91

8Ω/ch 4.6 386 267 119 406 102

4Ω/ch 6.4 543 350 193 659 166

8Ω/ch 1.9 182 100 82 280 71

4Ω/ch 2.5 237 131 106 362 91

8Ω/ch 3.8 385 267 118 403 101

4Ω/ch 5.4 542 350 192 655 165

8Ω/ch 1.2 184 100 84 287 72

4Ω/ch 1.5 242 131 111 379 95

8Ω/ch 2.2 385 267 118 403 101

4Ω/ch 3.0 544 350 194 662 167

(線電流)

100 V

0.8 57 0 57 195 49

Line current (A)

(線電流)

120 V

0.7 60 0 60 205 52

Line current (A)

(線電流)

230 V

0.5 62 0 62 212 53

Power consumption (In)

(消費電力)

Power consumption (In)

(消費電力)

Power consumption (In)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watts dissipated

(放散電力)

Watts dissipated

(放散電力)

Watts dissipated

(放散電力)

Thermal dissipation

Btu/h kcal/h

Thermal dissipation

Btu/h kcal/h

Thermal dissipation

Btu/h kcal/h

(熱放散)

(熱放散)

(熱放散)

4

Page 5

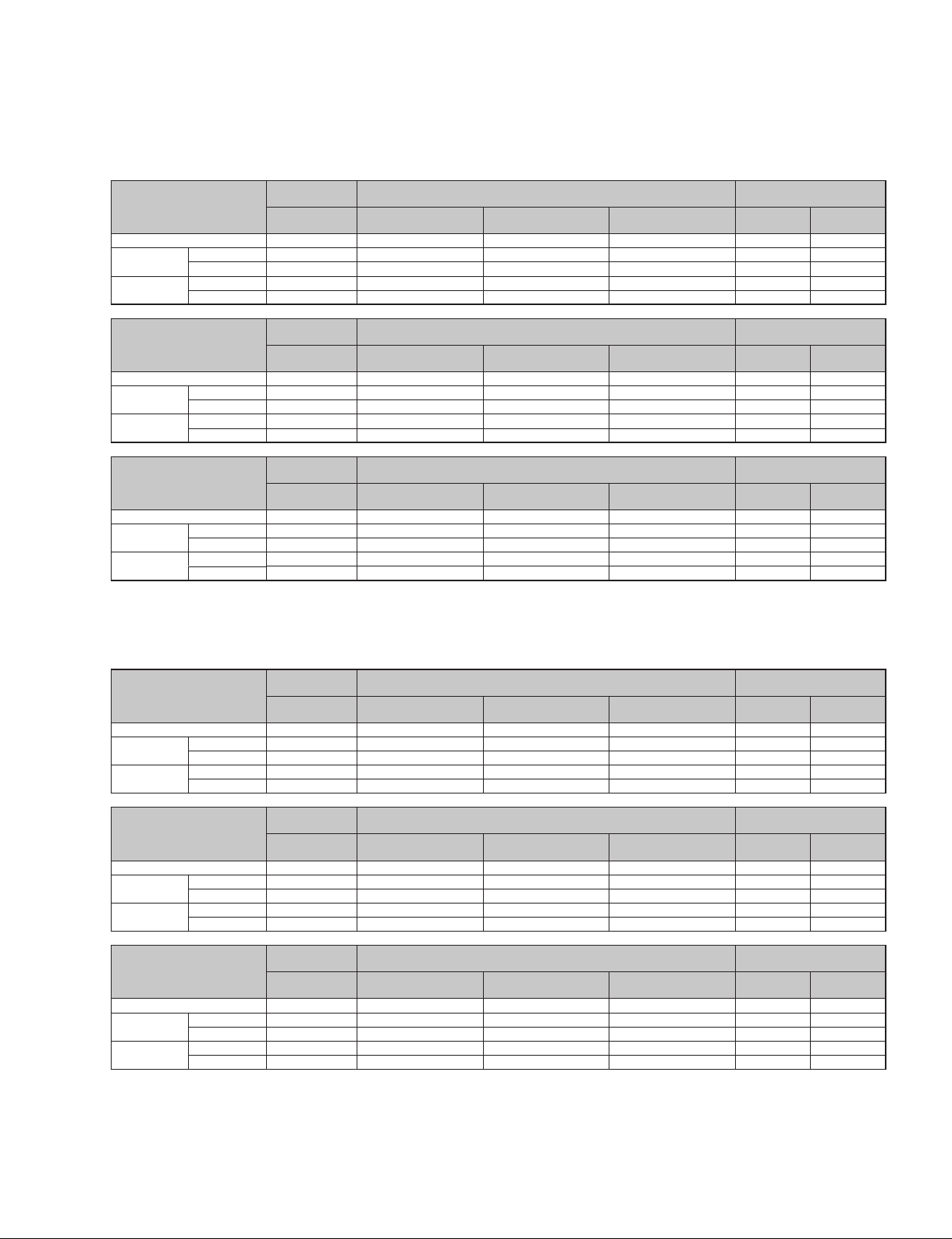

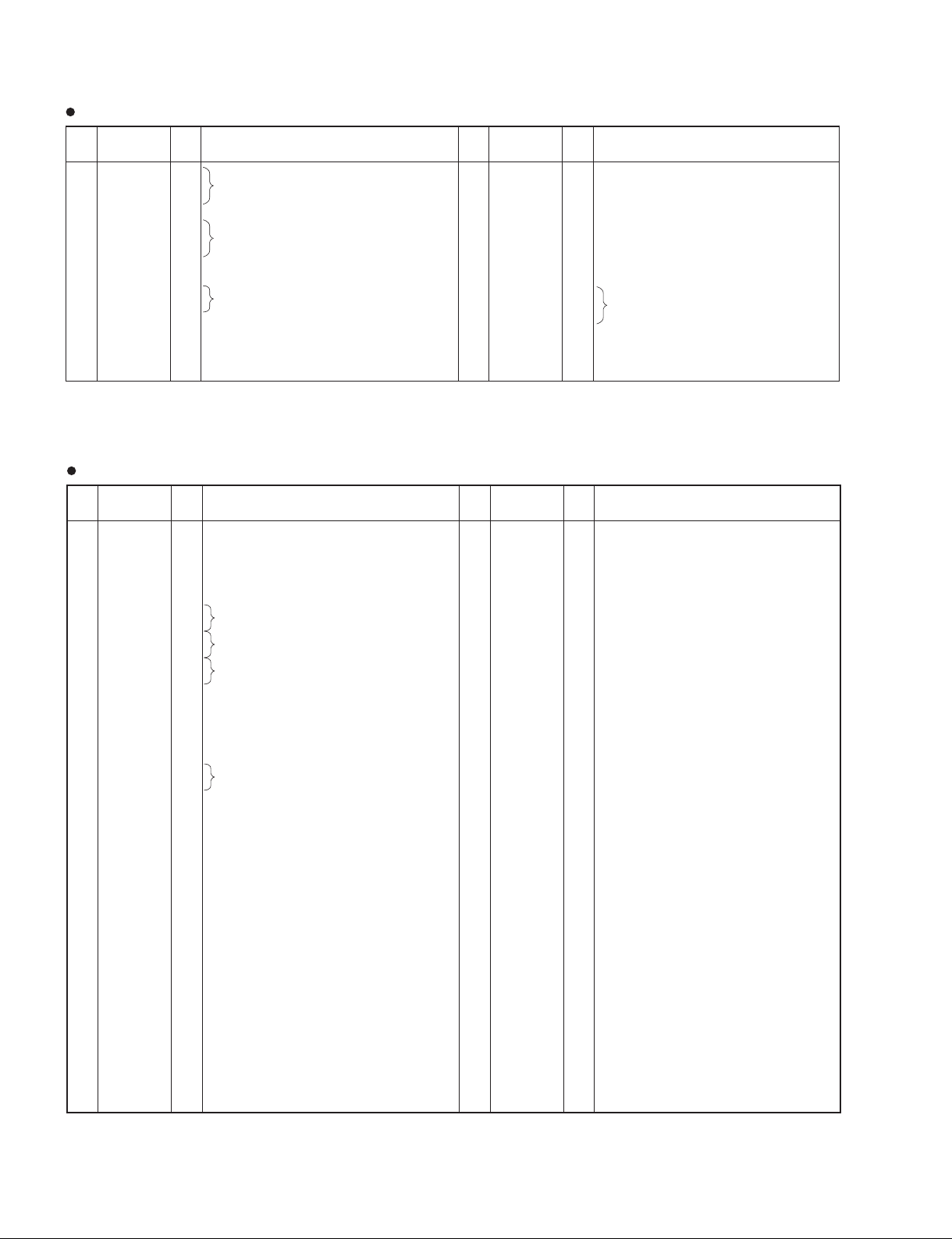

●

PX5

Idle

1/8 out

1/3 out

(アイドル)

PX10/PX8/PX5/PX3

Line current (A)

100 V/50 Hz

8Ω/ch 1.9 122 63 59 201 51

4Ω/ch 2.7 189 100 89 304 77

8Ω/ch 3.6 253 167 86 293 74

4Ω/ch 5.6 424 267 157 536 135

(線電流)

100 V

0.8 46 0 46 157 40

Power consumption (In)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watts dissipated

(放散電力)

Thermal dissipation

Btu/h kcal/h

(熱放散)

●

Idle

1/8 out

1/3 out

Idle

1/8 out

1/3 out

PX3

Idle

1/8 out

1/3 out

110 V-120 V/60 Hz

(アイドル)

220 V-240 V/50 Hz

(アイドル)

(アイドル)

Line current (A)

(線電流)

120 V

8Ω/ch 1.7 130 63 67 229 58

4Ω/ch 2.4 196 100 96 328 83

8Ω/ch 3.1 259 167 92 314 79

4Ω/ch 4.8 428 267 161 549 138

8Ω/ch 1.0 130 63 67 229 58

4Ω/ch 1.4 197 100 97 331 83

8Ω/ch 1.9 259 167 92 341 79

4Ω/ch 2.9 434 267 167 570 144

100 V/50 Hz

8Ω/ch 1.5 94 38 56 191 48

4Ω/ch 2.0 137 63 74 253 64

8Ω/ch 2.6 174 100 74 253 64

4Ω/ch 3.9 285 167 118 403 101

0.8 54 0 54 184 46

Line current (A)

(線電流)

230 V

0.5 57 0 57 195 49

Line current (A)

(線電流)

100 V

0.8 46 0 46 157 40

Power consumption (In)

(消費電力)

Power consumption (In)

(消費電力)

Power consumption (In)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watts dissipated

(放散電力)

Watts dissipated

(放散電力)

Watts dissipated

(放散電力)

Thermal dissipation

Btu/h kcal/h

Thermal dissipation

Btu/h kcal/h

Thermal dissipation

Btu/h kcal/h

(熱放散)

(熱放散)

(熱放散)

Idle

(アイドル)

1/8 out

1/3 out

Idle

(アイドル)

1/8 out

1/3 out

Line current (A)

110 V-120 V/60 Hz

8Ω/ch 1.3 100 38 62 212 53

4Ω/ch 1.8 140 63 77 263 66

8Ω/ch 2.3 183 100 83 283 71

4Ω/ch 3.4 291 167 124 423 107

220 V-240 V/50 Hz

8Ω/ch 0.8 101 38 63 215 54

4Ω/ch 1.1 142 63 79 270 68

8Ω/ch 1.4 181 100 81 276 70

4Ω/ch 2.1 293 167 126 430 108

(線電流)

120 V

0.8 54 0 54 184 46

Line current (A)

(線電流)

230 V

0.5 57 0 57 195 49

Power consumption (In)

(消費電力)

Power consumption (In)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watt (W)

(電力)

Power consumption (Out)

(消費電力)

Watts dissipated

(放散電力)

Watts dissipated

(放散電力)

Thermal dissipation

(熱放散)

Btu/h kcal/h

Thermal dissipation

(熱放散)

Btu/h kcal/h

5

Page 6

PX10/PX8/PX5/PX3

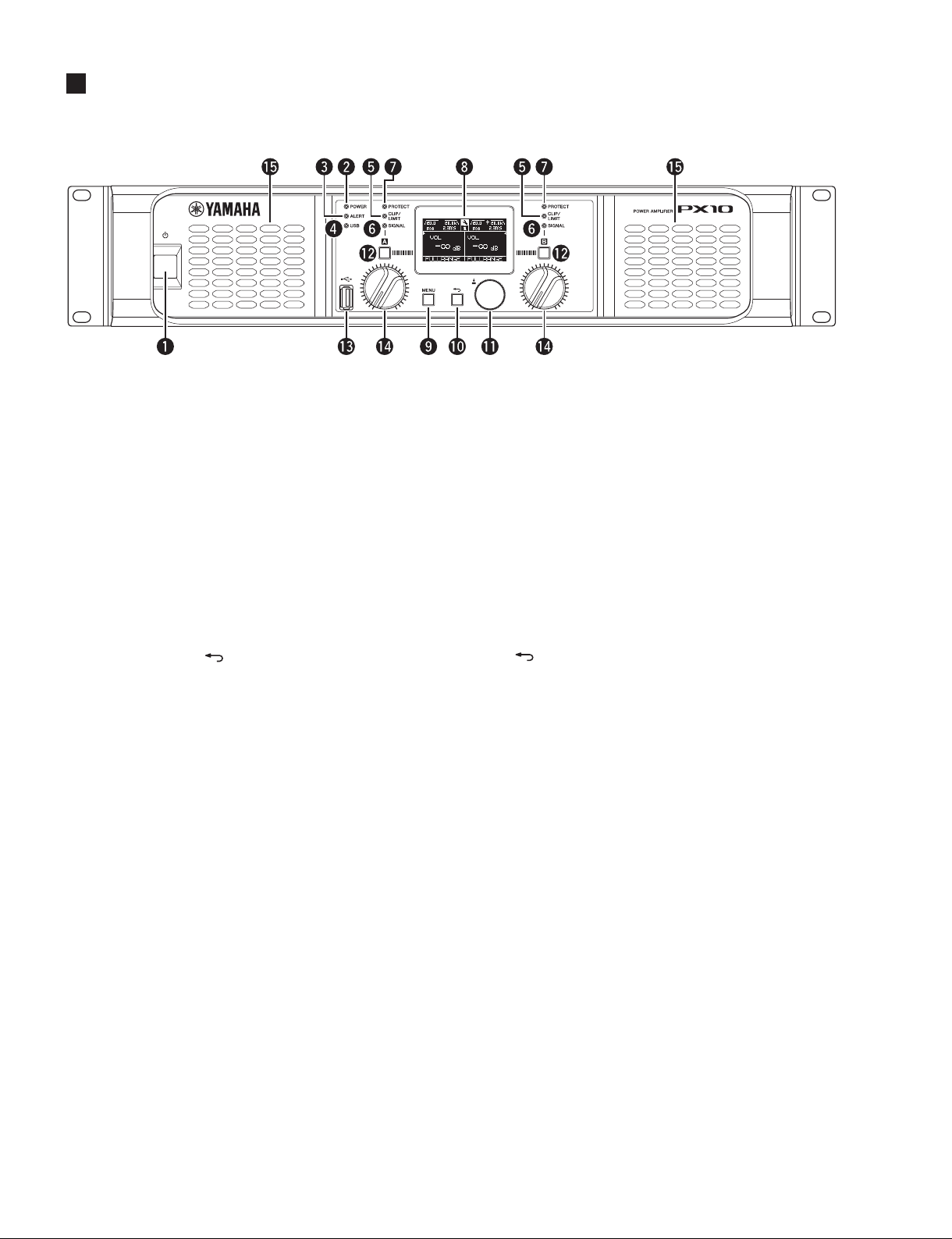

PANEL LAYOUT(パネルレイアウト)

• Front Panel

(フロントパネル)

q Power button

w [POWER] indicator

e [ALERT] indicator

r [USB] indicator

t [CLIP/LIMIT] indicators

y [SIGNAL] indicators

u [PROTECT] indicators

q 電源ボタン

w [POWER]インジケーター

e [ALERT]インジケーター

r [USB]インジケーター

t [CLIP/LIMIT]インジケーター

y [SIGNAL]インジケーター

u [PROTECT]インジケーター

i Display

o [MENU] key

!0 [

!1 Main knob

!2 [A]/[B] keys

!3 [USB] terminal

!4 Volume knobs

!5 Intake ports

] (Back) key

i ディスプレイ

o [MENU]キー

!0 [

!1 メインノブ

!2 [A]/[B]キー

!3 [USB] 端子

!4 ボリュームノブ

!5 吸気口

](バック)キー

6

Page 7

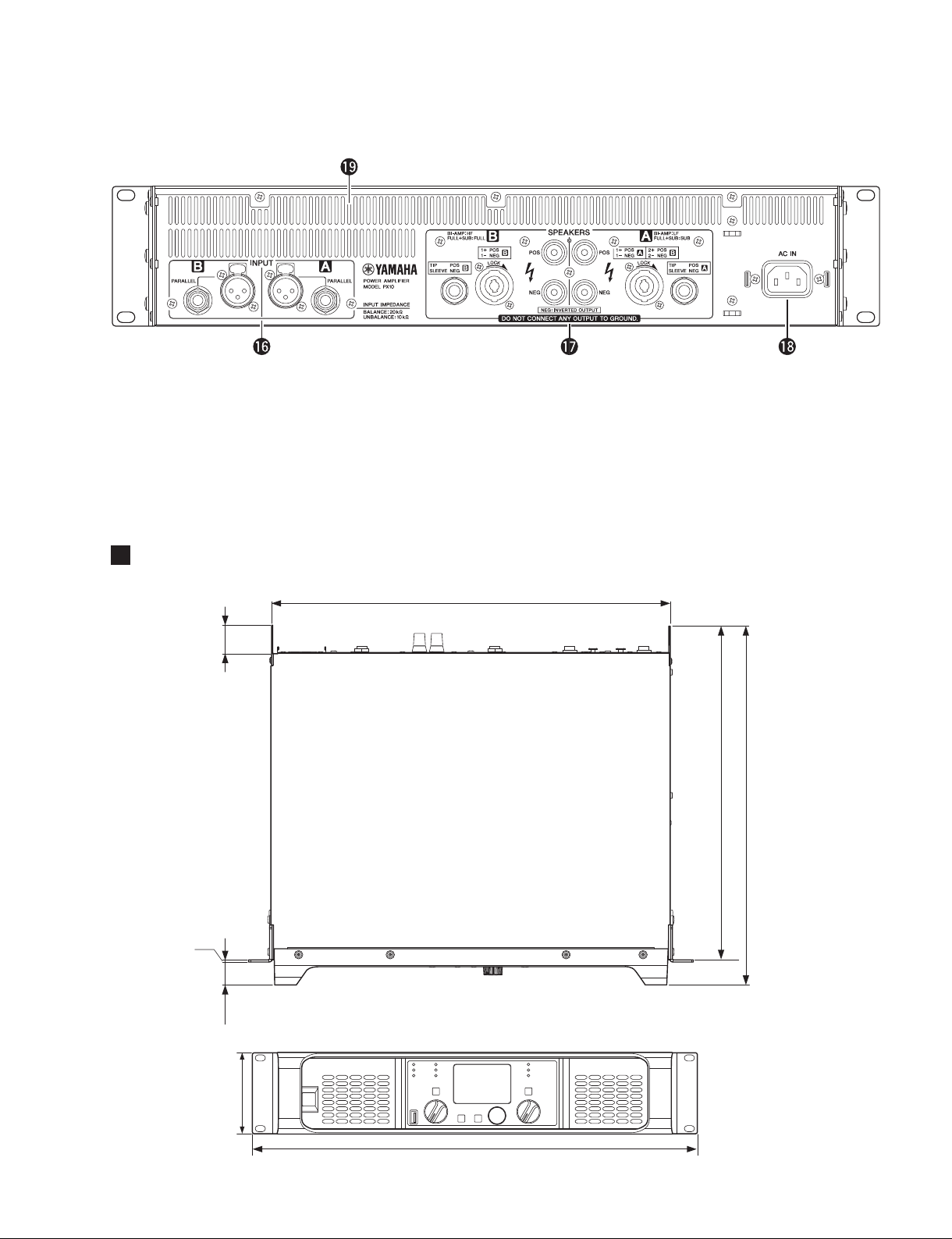

PX10/PX8/PX5/PX3

• Rear Panel

(リアパネル)

!6 [INPUT] A/B connectors

!7 [SPEAKERS] A/B terminals

!8 AC IN connector

!9 Exhaust ports

DIMENSIONS(寸法図)

!6 [INPUT]A/B端子

!7 [SPEAKERS]A/B端子

!8 ACIN端子

!9排気口

2.5

430

29

388

361 (Mounting Surface to Rear End)

24.5

88

480

unit(単位): mm

7

Page 8

PX10/PX8/PX5/PX3

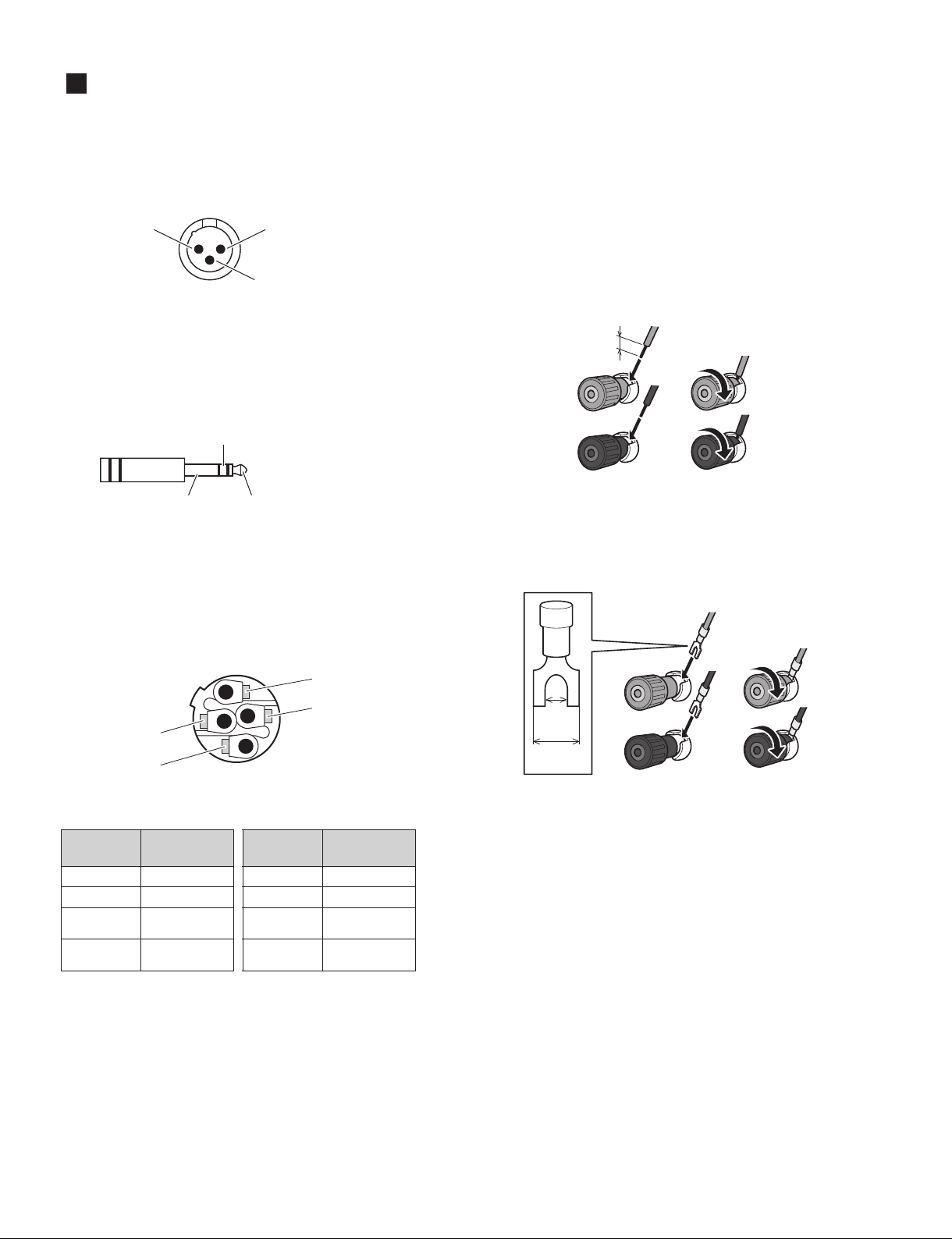

JACK AND PLUG LIST(端子とプラグ一覧)

• XLR jack

XLR type 3-31 jack.

(XLR端子)

(XLR型3-31タイプの端子です。)

The polarity is shown below (IEC60268).

(極性は次のとおりです(IEC60268)。)

Hot(ホット)

• Phone jack

21

3

(フォーン端子)

Ground(グラウンド)

Cold(コールド)

Balanced TRS phone jack.

(バランス型のTRSフォーン端子です。)

The polarity of the connections is shown below.

(接続する極性は次のとおりです。)

Ring (cold)(リング(コールド))

(スリーブ(グラウンド))

• SpeakON connector

Tip (hot)(チップ(ホット))Sleeve (ground)

(スピコン端子)

Insert the SpeakON cable plug (Neutrik NL4) into the

connector, and turn it to the right to lock it.

(スピコンケーブルプラグ(NeutrikNL4)を差し込み、

右に回してロックします。)

• Binding post connector

• Without plugs

Remove about 15 mm of insulation from the end of each

speaker cable, pass the bare wire through the holes in the

appropriate speaker terminals, and tighten the terminals to

securely clamp the wires. Make sure that the bare wire ends do

not jut out from the terminals and touch the chassis.

(スピーカーケーブルの先端の被覆を15mm外し、端子の穴に通

して締め付けます。このとき、芯線がシャーシに当たらないよう

にしてください。)

• Y-plugs

From above, insert the Y-plugs all the way into the opening, and

tighten the terminals.

(Y型プラグを上から奥まで差し込み、締め付けます。)

(プラグなしの場合)

15 mm

(Y型プラグの場合)

(バインディングポスト端子)

1+

1–

Channel A (Aチャンネル)

Neutrik NL4

1+ A+

1– A–

2+ B+

2– B–

PX amplifier

(PXアンプ)

2–

2+

Channel B (Bチャンネル)

Neutrik NL4

1+ B+

1– B–

2+

2–

PX amplifier

(PXアンプ)

not connected

(接続なし)

not connected

(接続なし)

0.25"

(6.3 mm)

≤0.51"

(12.9 mm)

8

Page 9

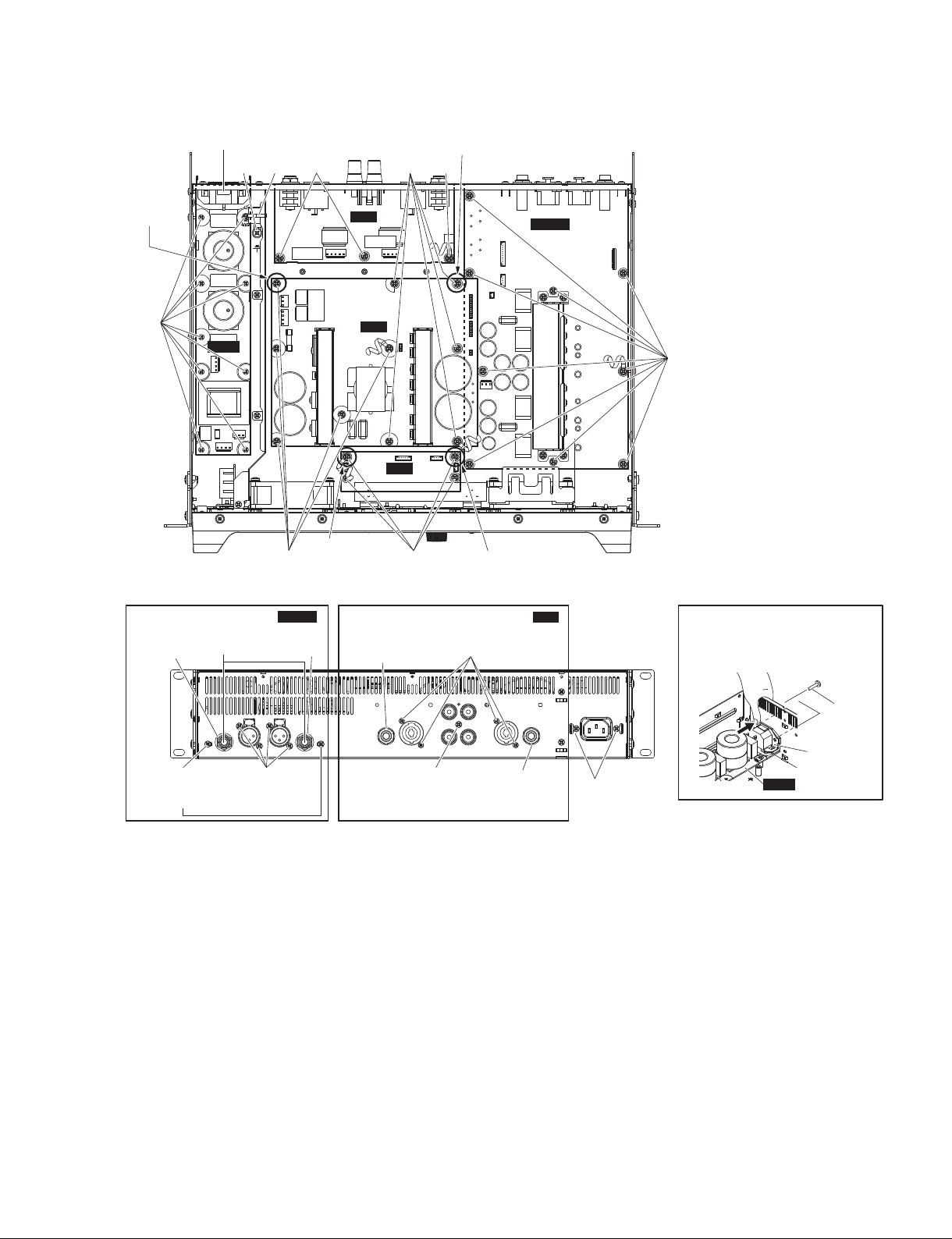

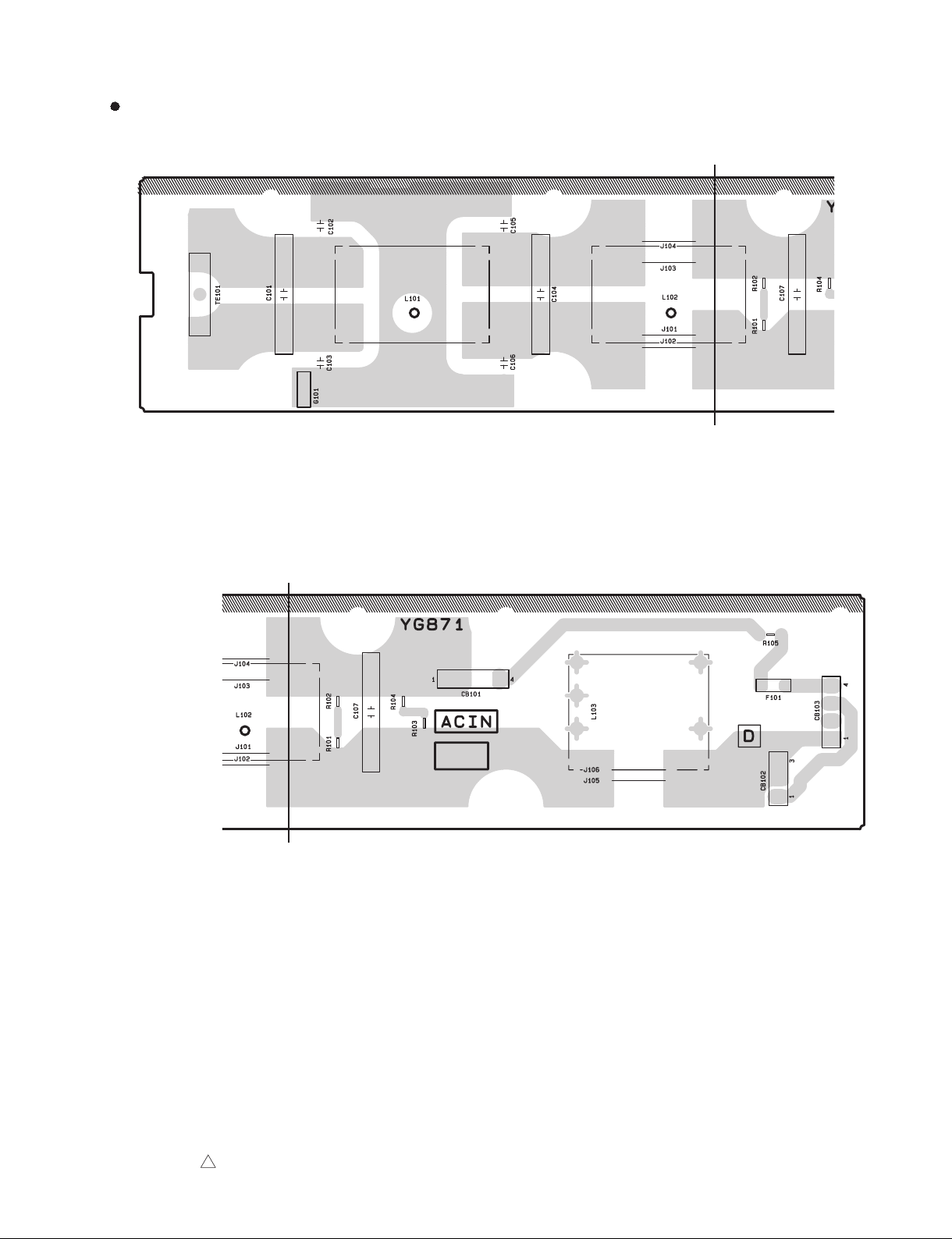

CIRCUIT BOARD LAYOUT(ユニットレイアウト)

PX10/PX8/PX5/PX3

• Top view

(上から見た図)

AC INLET

(ACインレット)

OUT

AUDIO

PS

ACIN

• Front view

PSW

DC FAN

(DCファン)

(前面から見た図)

PF

VOL

DC FAN

(DCファン)

FPN

USB ENC

9

Page 10

PX10/PX8/PX5/PX3

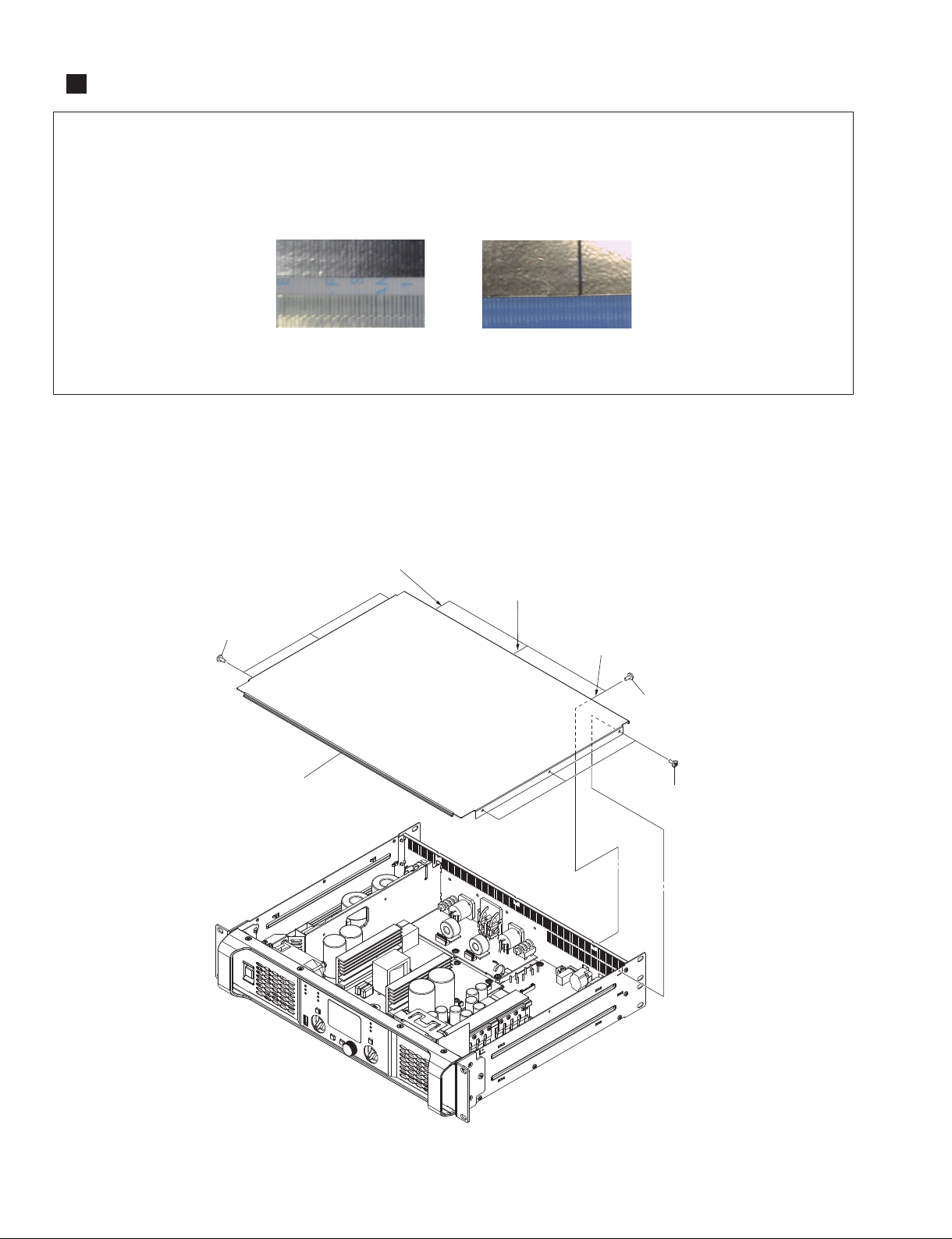

DISASSEMBLY PROCEDURE(分解手順)

Caution:

• Install the binding tie and the cord clamp in the same way

as they were before removal.

• Pay attention not to insert and install the FFC cable to the

connector inversely. (Photo A)

Front Side

(表面)

Photo A

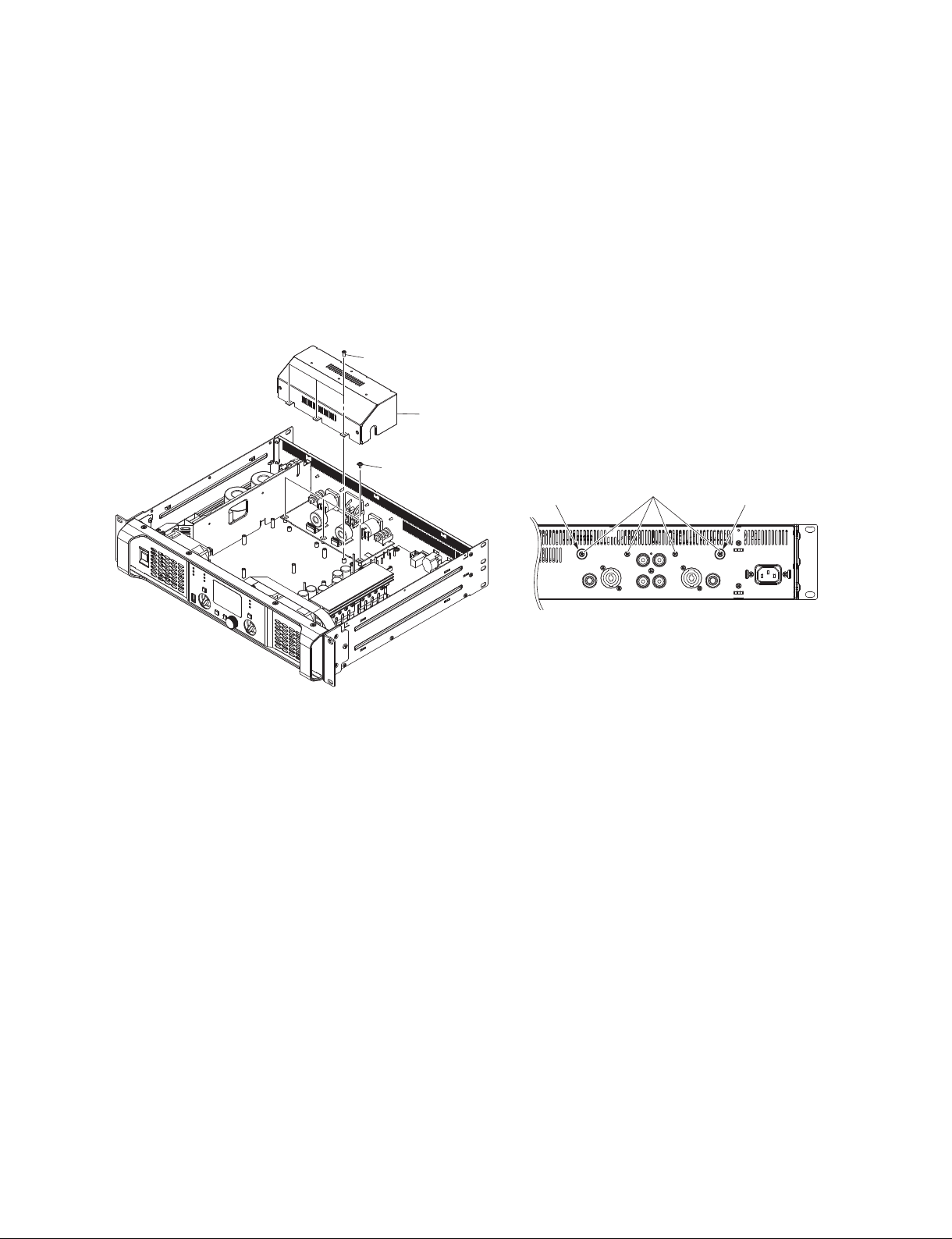

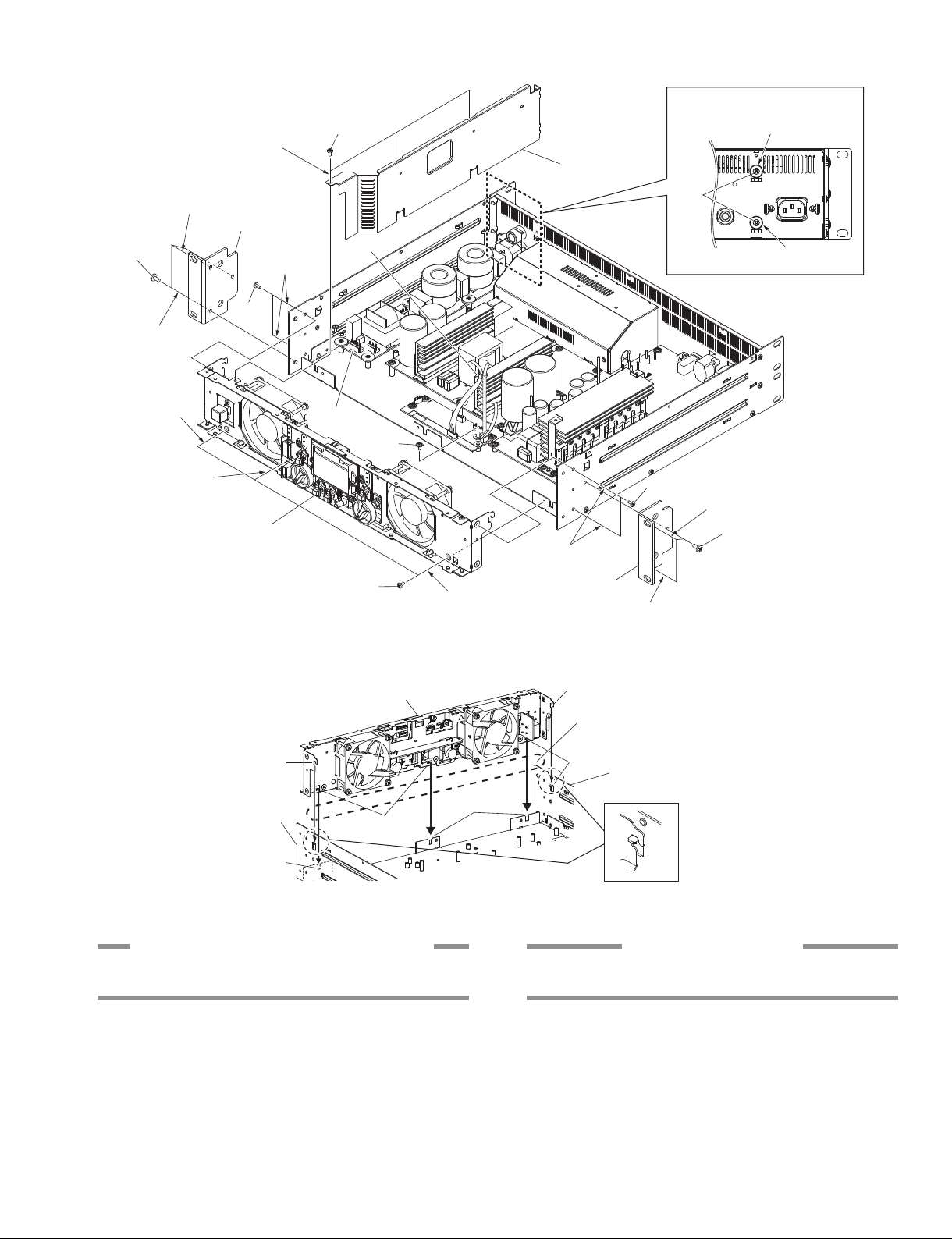

1. Top Panel (Time required: About 2 minutes)

1-1 Remove the nine (9) screws marked [1120]. The top panel

can then be removed. (Fig. 1)

* When installing the top panel, first tighten the priority

screws as shown in Fig. 1.

Priority screw (2nd)

(優先ネジ2)

注意事項

•インシュロックタイ、束線止めは、取り外す前と同じように取り

付けてください。

•FFCケーブルの表・裏を逆に差し込まないように注意して取り

付けてください。(写真A)

Back Side

(裏面)

(写真 A)

1. トップパネル

1-1 [1120]のネジ 9 本を外して、トップパネルを外します。

(図1)

※ トップパネルを取り付ける際は、優先ネジを図1に示す順

で締めてください。

Priority screw (1st)

(優先ネジ1)

(所要時間:約2 分)

[1120]

TOP PANEL

(トップパネル)

Priority screw (2nd)

(優先ネジ2)

[1120]

[1120]

10

Fig. 1

(図1)

Page 11

<Top view (上面)>

AC INLET

(ACインレット)

[860] [440] [440]

[350]

Priority screw (2nd)

(優先ネジ2)

[520]

PX10/PX8/PX5/PX3

Priority screw (1st)

(優先ネジ1)

[340]

<Rear view (背面)>

[670]

ACIN

HEXAGONAL NUT

(六角ナット)

Priority screw (3rd)

(優先ネジ3)

CB901

Priority screw (2nd)

[520]

AUDIO

[670]

OUT

CB902

PS

(優先ネジ2)

HEXAGONAL NUT

(六角ナット)

Priority screw (3rd)

(優先ネジ3)

PF

[470A]

Priority screw (1st)

(優先ネジ1)

Priority screw (2nd)

(優先ネジ2)

[430]

AUDIO

OUT

[630]

Tighten the screws marked [330] with

holding the inlet angle.

(インレット金 具を押さえながら[330]のネジを

締めてください 。)

[640]

Priority screw (2nd)

(優先ネジ2)

[620]

Priority screw (1st)

(優先ネジ1)

[420]

Priority screw (1st)

(優先ネジ1)

Fig. 2

2.

ACIN Circuit Board (Time required: About 4 minutes)

2-1 Remove the top panel. (See procedure 1.)

2-2 Remove the cable tie marked [860]. (Fig. 2)

2-3 Remove the two (2) screws marked [330], the nine (9)

screws marked [340] and the screw marked [350]. The

ACIN circuit board can then be removed.(Fig. 2)

* When installing the ACIN circuit board, first tighten the

screws marked [330] with holding the inlet angle.

(Fig. 2)

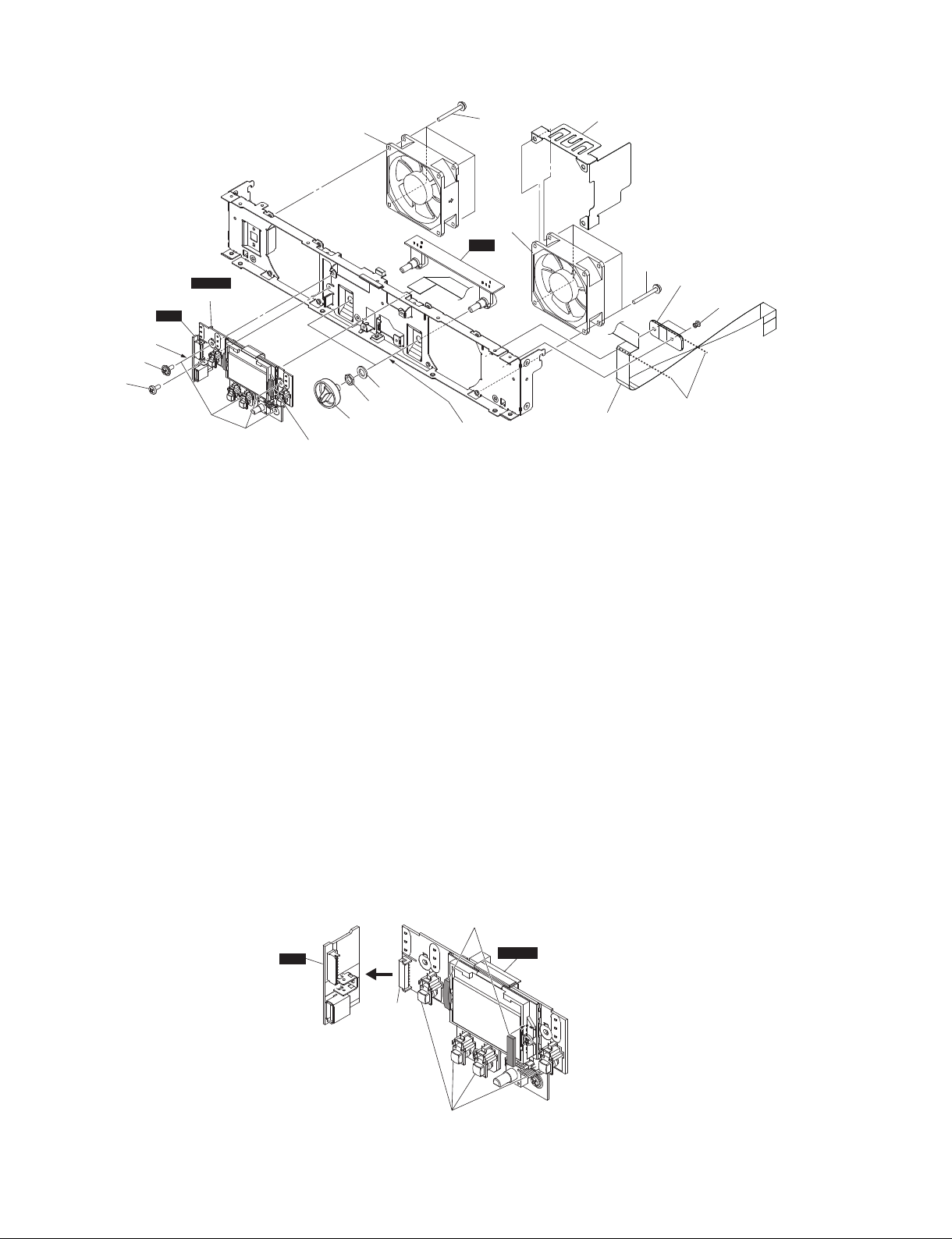

3.

PS Circuit Board (Time required: About 6 minutes)

3-1 Remove the top panel. (See procedure 1.)

3-2 Remove the ten (10) screws marked [520]. The PS circuit

board can then be removed.(Fig. 2)

* When installing the PS circuit board, first tighten the

priority screws as shown in Fig. 2.

HEXAGONAL NUT

(六角ナット)

Priority screw (3rd)

(優先ネジ3)

[330]

ACIN

(図2)

2. ACINシート

(所要時間:約4 分)

2-1 トップパネルを外します。(1項参照)

2-2 [860]のインシュロックタイを外します。(図2)

2-3 [330]のネジ2 本と[340]のネジ 9 本、[350]のネジ1本を

外して、ACINシート外します。(図2)

※ ACINシー トを取り付ける際は、先に[330]のネジをイン

レット金具を押さえながら締めてください。(図2)

3. PSシート

(所要時間:約6 分)

3-1 トップパネルを外します。(1項参照)

3-2 [520]のネジ10 本を外して、PSシート外します。

(図2)

※ PSシートを取り付ける際は、優先ネジを図2に示す順で締

めてください。

[330]

INLET ANGLE

(インレット金具)

11

Page 12

PX10/PX8/PX5/PX3

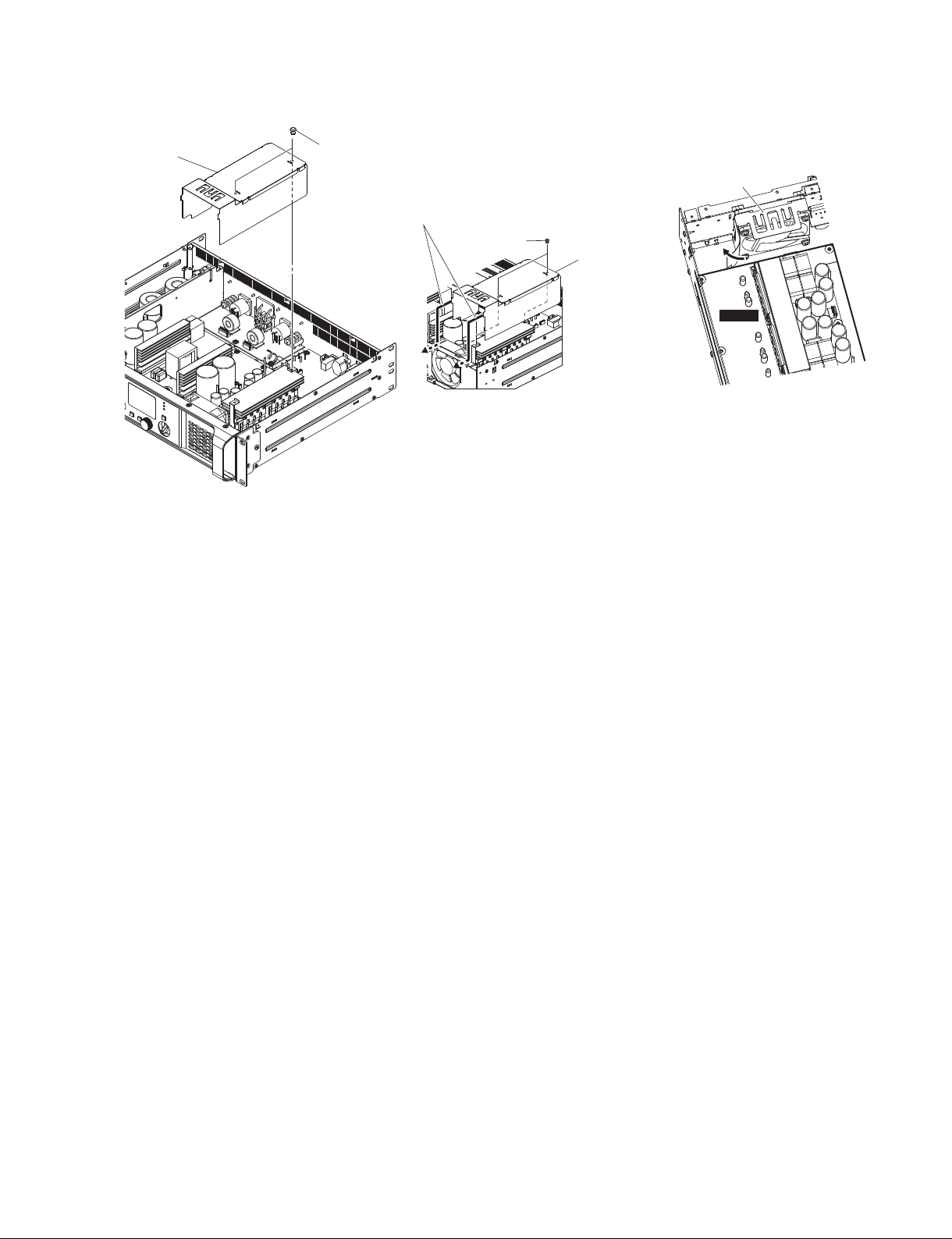

4.

OUT Circuit Board (Time required: About 8 minutes)

4-1 Remove the top panel. (See procedure 1.)

4-2 Remove the seven (7) screws marked [830]. The shield out

can then be removed. (Fig. 3)

* When installing the shield OUT, first tighten the priority

screws as shown in Fig. 3.

4-3 Remove the three (3) screws marked [440]. (Fig. 2, 3)

4-4 Remove the screw marked [420], the four (4) screws

marked [430] and the two (2) hexagonal nuts. The OUT

circuit board can then be removed. (Fig. 2)

* When installing the OUT circuit board, first tighten the

priority screws as shown in Fig. 2.

[830]

[440]

SHIELD OUT

(シールドOUT)

4. OUTシート

(所要時間:約8 分)

4-1 トップパネルを外します。(1項参照)

4-2 [830]のネジ7 本を外して、シールド OUTを外します。

(図3)

※ シールドOUTを取り付ける際は、優先ネジを図3に示す順

で締めてください。

4-3 [440]のネジ3 本を外します。(図2、3)

4-4 [420]のネジ1 本と[430]のネジ 4 本、六角ナット2 個を外

して、OUTシートを外します。(図2)

※ OUTシートを取り付ける際は、優先ネジを図2に示す順で

締めてください。

<Rear view (背面)>

Priority screw (1st)

(優先ネジ1)

[830]

Priority screw (2nd)

(優先ネジ2)

5. AUDIO

Circuit Board

(Time required: About 8 minutes)

5-1 Remove the top panel. (See procedure 1.)

5-2 Remove the shield out. (See procedure 4-2.)

5-3 Remove the connectors of the CB901 and CB902 from

OUT circuit board. (Fig. 2)

5-4 Remove the PS circuit board. (See procedure 3.)

5-5 PX10/PX8 only

Remove the two (2) plastic rivets marked [850]. The duct

amp can then be removed. (Fig. 4)

* When installing the duct amp, fit the tabs of duct amp

into the slots of sub chassis. (Fig. 4)

5-6 Remove the nine (9) screws marked [630]. (Fig. 2)

5-7 Remove the four (4) screws marked [620], the two (2)

screws marked [640], the two (2) hexagonal nuts, the two

(2) washers and the two (2) plastic washers marked [670].

The AUDIO circuit board can then be removed. (Fig. 2)

* When installing the AUDIO circuit board, first tighten

the priority screws as shown in Fig. 2.

* PX5/PX3 only : When installing the AUDIO circuit board,

AUDIO circuit board with bending FFC guard as shown

in Fig. 4.

Fig. 3

(図3)

5. AUDIOシート

(所要時間:約8 分)

5-1 トップパネルを外します。(1項参照)

5-2 シールドOUTを外します。(4-2 項参照)

5-3 OUTシートからCB901とCB902のコネクタを 外し

ます。(図2)

5-4 PSシートを外します。(3項参照)

5-5 PX10/PX8のみ

[850]のプラスチックリベット2個を外して、ダクト

AMPを外します。(図4)

※ ダクトAMPを取り付ける際は、ダクトAMPのタブをサブ

シャーシの長孔に挿し入れます。(図4)

5-6 [630]のネジ9 本を外します。(図2)

5-7 [620]のネジ 4 本と[640]のネジ 2 本、六角ナット2個と

ワッシャー 2個、[670]のプラワッシャー 2個を外して、

AUDIOシートを外します。(図2)

※ AUDIOシートを取り付ける際は、優先ネジを図2に示す順

で締めてください。

※ PX5/PX3 のみ:AUDIOシートを取り付ける際は、FFCガー

ドを曲げながらAUDIOシー トを取り付けてください。

(図4)

12

Page 13

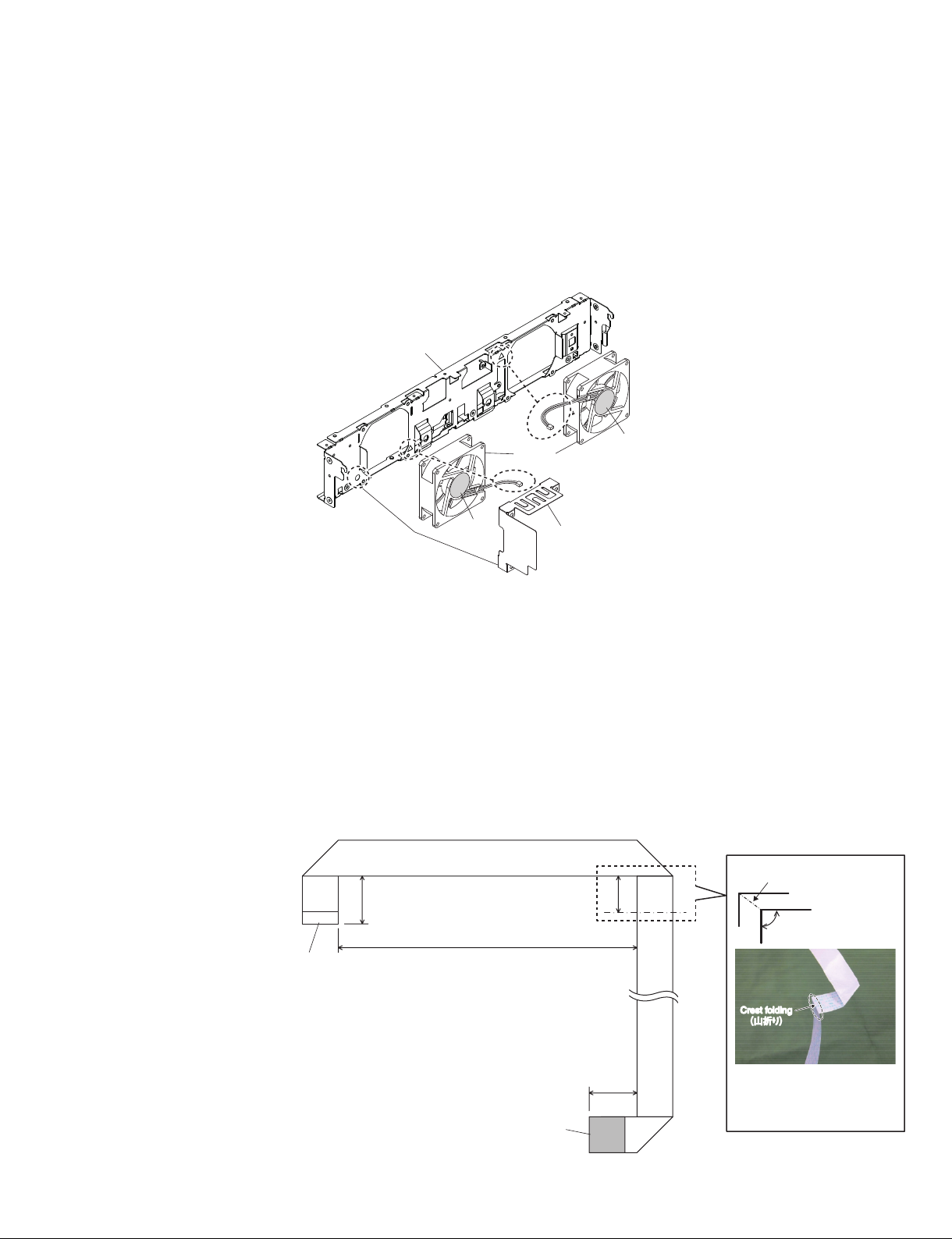

r1919 r1919

Set AUDIO circuit board with bending FFC guard.

DUCT AMP

(ダクトAMP)

[850]

Fit the tabs of duct amp into the slots of sub chassis.

(ダクトAMPのタブをサブシャーシの長孔に挿し入れます。)

[850]

Fig. 4

(図4)

DUCT AMP

(ダクトAMP)

(FFCガードを曲げながらAUDIOシートを 取り付 け てください 。)

PX10/PX8/PX5/PX3

FFC GUARD

(FFCガード)

AUDIO

6. PF

Circuit Board

(Time required: About 3 minutes)

6-1 Remove the top panel. (See procedure 1.)

6-2 Remove the four (4) screws marked [470A]. The PF circuit

board can then be removed. (Fig. 2)

* When installing the PF circuit board, first tighten the

priority screws as shown in Fig. 2.

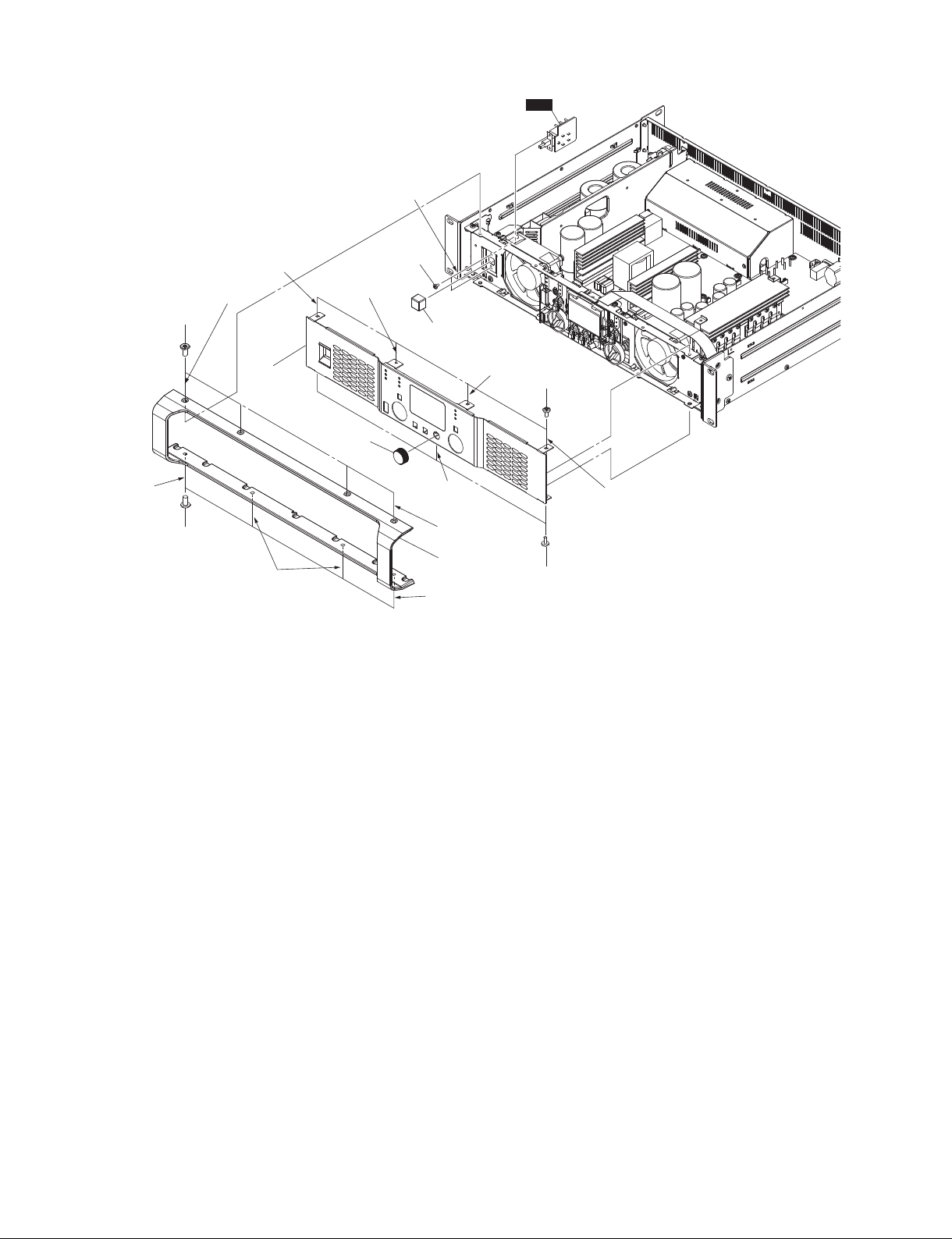

7. Front Panel Assembly

(Time required: About 4 minutes)

7-1 Remove the top panel. (See procedure 1.)

7-2 Remove the eight (8) screws marked [960]. The front

frame can then be removed. (Fig. 5)

7-3 Remove the seven (7) screws marked [940] and the knob

ENCDR. The front panel assembly can then be removed.

(Fig. 5)

* When installing the front frame and front panel

assembly, first tighten the priority screws as shown in

Fig. 5.

8. PSW

Circuit Board

(Time required: About 4 minutes)

8-1 Remove the top panel. (See procedure 1.)

8-2 Remove the front panel assembly. (See procedure 7.)

8-3 Remove the two (2) screws marked [100] and power

switch knob. The PSW circuit board can then be removed.

(Fig. 5)

* When installing the PSW circuit board, first tighten the

priority screws as shown in Fig. 5.

6. PFシート

(所要時間:約3 分)

6-1 トップパネルを外します。(1項参照)

6-2 [470A]のネジ 4本を外して、PFシートを外します。

(図2)

※ PFシートを取り付ける際は、優先ネジを図2に示す順で締

めてください。

7. Fパネル Ass'y

(所要時間:約4 分)

7-1 トップパネルを外します。(1項参照)

7-2 [960]のネジ 8 本を外して、フロントフレームを外し

ます。(図5)

7-3 [940]の ネジ7本 と ノブ ENCDRを外して、Fパネル

Ass'yを外します。(図5)

※ フロントフレームとFパネルAss'yを取り付ける際は、優先

ネジを図5に示す順で締めてください。

8. PSWシート

(所要時間:約4 分)

8-1 トップパネルを外します。(1項参照)

8-2 FパネルAss'yを外します。(7 項参照)

8-3 [100]のネジ2 本とPSWノブを外して、PSWシートを

外します。(図5)

※ PSWシートを取り付ける際は、優先ネジを図5に示す順で

締めてください。

13

Page 14

PX10/PX8/PX5/PX3

Priority screw (1st)

(優先ネジ1)

PSW

Priority screw (2nd)

(優先ネジ2)

Priority screw (4th)

(優先ネジ4)

[960]

Priority screw (3rd)

(優先ネジ3)

FRONT PANEL

ASSEMBLY

(FパネルAssy)

Priority screw (1st)

(優先ネジ1)

KNOB ENCDR

(ノブENCDR)

[100]

POWER SWITCH KNOB

Priority screw (4th)

(優先ネジ4)

[960]

Priority screw (3rd)

(優先ネジ3)

Fig. 5

9. Front Panel Section

(Time required: About 8 minutes)

9-1 Remove the top panel. (See procedure 1.)

9-2 Remove the front panel assembly. (See procedure 7.)

9-3 Remove the connector of the CB103 from ACIN circuit

board. (Fig. 6)

9-4 Remove the cable tie marked [750]. (Fig. 6)

9-5 Remove the five (5) screws marked [720]. The shield

ACIN can then be removed. (Fig. 6)

* When installing the shield ACIN, first tighten the priority

screws as shown in Fig. 6.

9-6 Remove the six (6) screws marked [1020]. The right and

left rack angles can then be removed. (Fig. 6)

* When installing the rack angles, first tighten the priority

screws as shown in Fig. 6.

9-7 Remove the screw marked [470B]. (Fig. 6)

9-8 Remove the seven (7) screws marked [270]. The front

panel section can then be removed. (Fig. 6)

* When installing the front panel section, first tighten the

priority screws as shown in Fig. 6.

* When installing the front panel section, fit the claws

of side panels (L/R) into the notches of front panel

sectoin, fit the claw of front panel section into the notch

of bottom assembly. (Fig. 7)

(PSWノブ)

Priority screw (2nd)

(優先ネジ2)

Priority screw (4th)

(優先ネジ4)

FRONT FRAME

(フロントフレーム )

Priority screw (1st)

(優先ネジ1)

(図5)

[940]

Priority screw (3rd)

(優先ネジ3)

[940]

9. フロントパネル部

(所要時間:約8 分)

9-1 トップパネルを外します。(1項参照)

9-2 FパネルAss'yを外します。(7 項参照)

9-3 ACINシートからCB103のコネクタを外します。(図6)

9-4 [750]のインシュロックタイを外します。(図6)

9-5 [720]のネジ5本を外して、シールドACINを外します。

(図6)

※ シールドACINを取り付ける際は、優先ネジを図6に示す順

で締めてください。

9-6 [1020]のネジ 6 本を外して、左右のラック金具を外し

ます。(図6)

※ ラック金具を取り付ける際は、優先ネジを図6に示す順で

締めてください。

9-7 [470B]のネジ1 本を外します。(図6)

9-8 [270]のネジ 7本を外して、フロントパネル部を外し

ます。(図6)

※ フロントパネル部を取り付ける際は、優先ネジを図6に示

す順で締めてください。

※ フロントパネル部を取り付ける際は、切り欠きをサイドパ

ネル(L/R)のツメに挿し込み、ツメをボトム Ass'yの切り欠

きに挿し込みます。(図7)

14

Page 15

Priority screw (2nd)

(優先ネジ2)

Priority screw (3rd)

(優先ネジ3)

RACK ANGLE

(ラック金具)

[720]

SHIELD ACIN

(シールドACIN)

<Rear view (背面)>

Priority screw (1st)

(優先ネジ1)

[720]

PX10/PX8/PX5/PX3

[1020]

Priority screw (3rd)

(優先ネジ3)

[270]

Priority screw (1st)

(優先ネジ1)

Priority screw (2nd)

(優先ネジ2)

Priority screw (1st)

(優先ネジ1)

FRONT PANEL SECTION

(フロントパネル 部)

CB103

• Rear view of the Front panel section

FRONT PANEL SECTION

[750]

[470B]

[270]

Priority screw (2nd)

(優先ネジ2)

Fig. 6

(図6)

(フロントパネル部を裏から見た図)

(フロントパネル 部)

Priority screw (3rd)

(優先ネジ3)

RACK ANGLE

(ラック金具)

NOTCH(切り欠き)

Be careful not to let wire bundles get pinched here.

(間に束線を挟みこまないようにしてください 。)

[270]

Priority screw (2nd)

(優先ネジ2)

Priority screw (2nd)

(優先ネジ2)

Priority screw (1st)

(優先ネジ1)

[1020]

NOTCH

(切り欠き)

NOTCH

SIDE PANEL R

(サイドパネルR )

NOTCH

(切り欠き)

CLAW

(ツメ)

(切り欠き)

Disassembly of the Front panel section.

*

Before disassembly, remove the front panel section in advance.

(See procedure 9 on page 14.)

10. VOLCircuit Board

(Time required: About 8 minutes)

10-1 Remove the two (2) knobs marked [910]. (Fig. 8)

10-2 Remove the two (2) hexagonal nuts and the two (2) flat

washers marked [140]. The VOL circuit board can then be

removed. (Fig. 8)

* When installing the VOL circuit board, first tighten the

priority nut as shown in Fig. 8.

BOTTOM ASSEMBLY

(ボトムAssy)

Fig. 7

(図7)

10. VOLシート

10-1 [910]のノブVR2 個を外します。(図8)

10-2 六角ナット2個と[140]の平座金VR2個を外して、

※ VOLシートを取り付ける際は、優先ナットを図8に示す順

CLAW

(ツメ)

SIDE PANEL L

(サイドパネルL )

フロントパネル部の分解

※ あらかじめフロントパネル部を外しておきます。

(14ページの9項参照)

(所要時間:約8 分)

VOLシートを外します。(図8)

で締めてください。

15

Page 16

PX10/PX8/PX5/PX3

(with ENC circuit board)

USB

Priority screw (2nd)

(優先ネジ2)

[80]

[90]

FPN CS

DC FAN

(DCファン)

Priority screw (1st)

(優先ネジ1)

[140]

HEXAGONAL NUT

(六角ナット)

[910]

Priority nut (1st)

(優先ナット1)

Fig. 8

(図8)

[40]

DC FAN

(DCファン)

VOL

FFC GUARD : PX5/PX3 onry

(FFCガード:PX5/PX3のみ)

[40]

Attach the holder FFC so as to match

FFC CABLE

(FFCケーブル)

the bend of FFC cable.

(ホルダーFFCをFFCケーブルの曲げに

合わせて貼り付けます。)

HOLDER FFC

(ホルダーFFC)

[880]

11. FPN CS (with ENC Circuit Board), USB

Circuit Board

11-1 Remove the four (4) screws marked [80] and the screw

marked [90]. The FPN CS circuit board and USB circuit

board can then be removed. (Fig. 8)

11-2 Remove the USB circuit board from the connector on the

CB106 of FPN CS circuit board. (Fig. 9)

11-3 Remove the four (4) button-tact switches from FPN CS

circuit board. (Fig. 9)

* When installing the FPN CS circuit board, first tighten

the priority screws as shown in Fig. 8.

* The two (2) cushions are not parts of the FPN CS circuit

board. Install the new cushions when replacing the FPN

CS circuit board. (Fig. 9)

* Attach the cushion on FPN CS circuit board in accordance

with the dashed line so as to cover the screw as shown

in Fig. 9.

(Time required: About 9 minutes)

USB

CB106

11. FPNCS(ENCシート付)、USBシート

(所要時間:約9 分)

11-1 [80]のネジ 4 本 と[90]の ネジ 1 本を外して、FPN CS

シートとUSBシートを外します。(図8)

11-2 FPNCSシートのCB106 のコネクタからUSBシート

を外します。(図9)

11-3 FPNCSシートより、ボタンタクトスイッチ4 個を外

します。(図9)

※ FPNCSシートを取り付ける際は、優先ネジを図8 に示す順

で締めてください。

※ クッション 2 個は、FPNCSシートの構成部品ではありま

せん。FPN CSシートを交換する際は、新しいクッション

を取り付けてください。(図9)

※ クッションを図9 に示すように、破線を基準にして、ネジを

覆うようにFPNCSシートへ貼り付けてください。

CUSHION

(クッション)

(with ENC circuit board)

FPN CS

16

BUTTON-TACT SWITCH

(ボタンタクトスイッチ )

Fig. 9

(図9)

Page 17

PX10/PX8/PX5/PX3

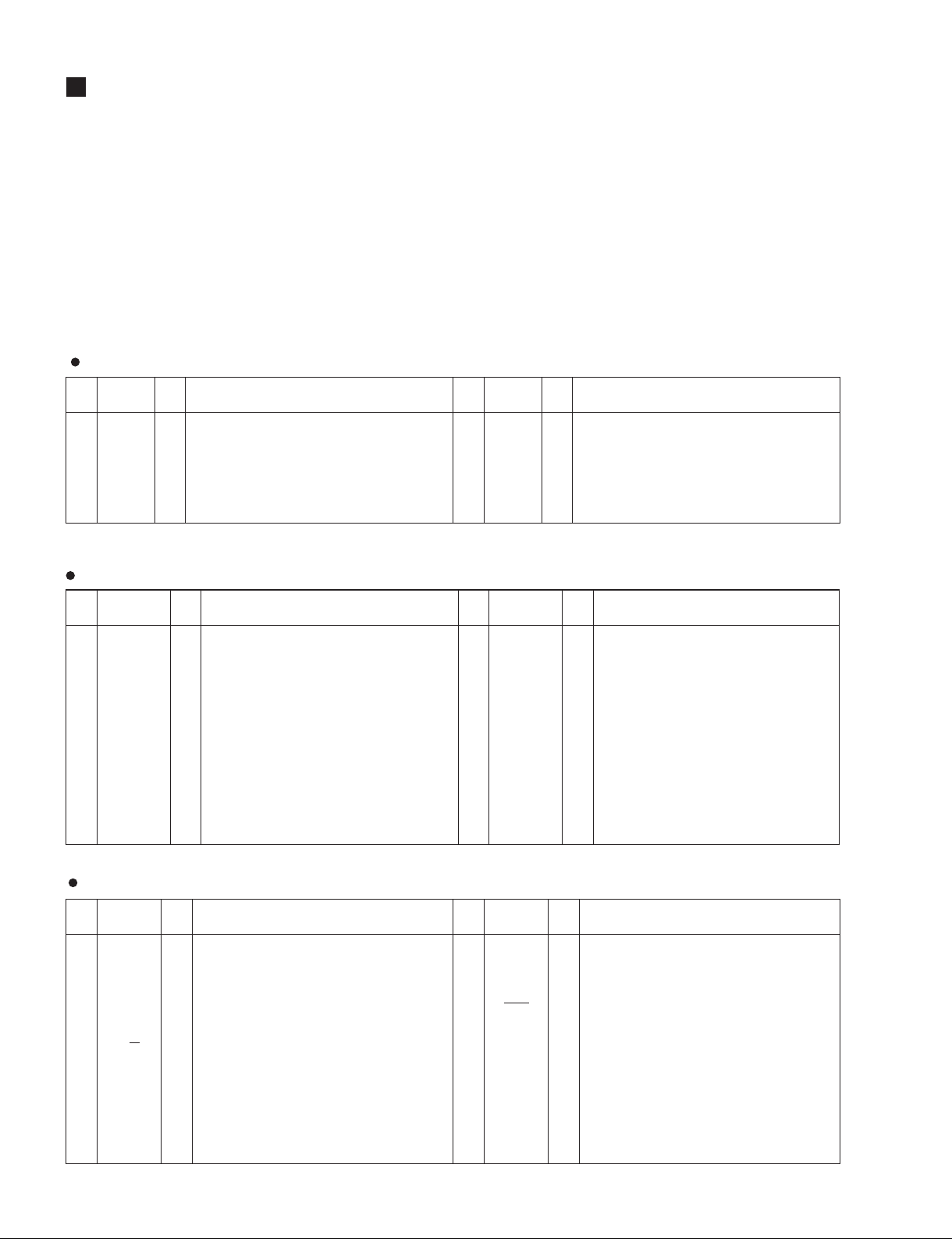

12. DC FAN (Time required: About 9 minutes)

12-1 Remove the eight (8) screws marked [40]. The DC fans

can then be removed. (Fig. 8)

* Remove the along with the FFC guard is the PX5 / PX3.

* When installing the DC fan, align the wire bundle of DC

fan in the “△” mark on sub chassis. (Fig. 10)

* When installing the DC fan, install DC fan so that label

surface can be secn. (Fig. 10)

* PX5/PX3 only : FFC in attach FFC guard to the side of

sub chassis having the “○” mark. (Fig. 10)

SUB CHASSIS

(サブシャーシ)

LABEL

(ラベル)

12. DCファン

(所要時間:約9 分)

12-1 [40]のネジ8 本を外して、左右のDCファンを外しま

す。(図8)

※ PX5/PX3 は、FFCガードと共に外します。

※ DCファンを取り付ける際は、束線をサブシャーシの「△」刻

印の方向に合わせて取り付けてください。(図10)

※ DCファンを取り付ける際は、DCファンのラベル面が見え

るように取り付けてください。(図10)

※ PX5/PX3 のみ:FFCガードは「○」刻印がある側に取り付

けてください。(図10)

DC FAN

(DCファン)

FFC GUARD

(FFCガード)

LABEL

(ラベル)

Fig. 10

13. FFC Cable (Time required: About 8 minutes)

13-1 Remove the plastic rivet [880] and press from the front.

The holder FFC can then be removed. (Fig. 8)

13-2 Remove the FFC cable from the holder FFC. (Fig. 8)

* When installing the FFC cable, after bending the FFC

cable as shown in Fig. 11, it bends to crest folding in the

position of an alternate long and short dash line, and

then insert to the connector.

* Attach the holder FFC so as to match the bend of FFC

cable. (Fig. 8)

• The bending size of a FFC cable

(FFCケーブルの折り曲げ寸法)

20 ± 2

Terminal Side

(端子面)

140 ± 2

(図10)

13. FFCケーブル

(所要時間:約8 分)

13-1 [880]のプラスチックリベットを正面側から押して、

ホルダー FFCを外します。(図8)

13-2

ホルダー FFCからFFCケーブルを取り外します。(図8)

※ FFCケーブルを取り付ける際は、図11のように折り曲げた

後、一点鎖線の位置で山折りに折り曲げ、コネクタに挿入し

ます。

※ ホルダー FFCをFFCケーブルの曲げに合わせて貼り付け

ます。(図8)

Crest folding

(山折り)

15 ± 2

90°

Crest folding

Crest folding

(山折り)

(山折り)

Protection plate side

(保護板面)

Fig. 11

(図11)

20 ± 2

As shown in a figure, after bending,

it bends to crest folding in the position

of an alternate long and short dash line.

(図の様に折り曲げた後、一点鎖線の位置

で山折りに折り曲げます。)

17

Page 18

PX10/PX8/PX5/PX3

LSI PIN DESCRIPTION(LSI 端子機能表)

AK4382AVT (X0661A00) DAC (Digital to Analog Converter) ...............................................................18

LPC1820FBD144,551 (YF570B00) MCU (Microcontroller Unit) ..........................................................19

NJW1194V(TE1) (X8355A00) 2-CHANNEL ELECTRONIC VOLUME ............................................... 18

PCM1804DBR (X6872A01) ADC (Analog to Digital Converter) ...........................................................18

YDA177-VZ (YF978A00) DIGITAL POWER AMPLIFIER ....................................................................20

YSS952-QZE2A (YE441A00) DSP(SPR-2) (Digital Signal Processor) ................................................20

AK4382AVT (X0661A00) DAC (Digital to Analog Converter)

PIN

NAME I/O FUNCTION

NO.

1

MCLK

2

BICK

3

SDTI

4

LRCK

5

PDN

6

CSN

7

CCLK

8

CDTI

I

I

I

I

I

I

I

I

Master Clock

Audio Serial Data Clock

Audio Serial Date Input

L/R Clock

Power Down mode

Chip Select

Control Data Input

Control Data Input

PIN

NAME I/O FUNCTION

NO.

9

10

11

12

13

14

15

16

AOUTRAOUTR+

AOUTL-

AOUTL+

Vss

VDD

DZFR

DZFL

O

O

O

O

-

O

O

Rch Analog out(-)

Rch Analog out(+)

Lch Analog out(-)

Lch Analog out(+)

Ground

Power Supply

Rch Data Zero Input Detect

Lch Data Zero Input Detect

NJW1194V(TE1) (X8355A00) 2-CHANNEL ELECTRONIC VOLUME

PIN

NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

InA1

InA2

InA3

InA4

GND

DCCAP_A

GND

OutA

VDDOUT

DATA

CLOCK

LATCH

GND

Tone_Tr1a

Tone_Ba1a

Tone_Ba2a

I/O FUNCTIONNAME

I

Ach Input 1

I

Ach Input 2

I

Ach Input 3

I

Ach Input 4

-

Ground

-

Switching noise rejection capacitor (Ach)

-

Ground

O

Ach Output

O

Internal Digital Power Supply output

I

Control data signal input

I

Clock signal input

I

Latch signal input

-

Ground

-

Ach Treble Filter Terminal 1

-

Ach Bass Filter Terminal 1

-

Ach Bass Filter Terminal 2

PIN

NO.

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

Tone_Ba2b

Tone_Ba1b

Tone_Tr1b

GND

V -

V +

ADR0

ADR1

OutB

GND

DCCAP_B

GND

InB4

InB3

InB2

InB1

I/O FUNCTIONNAME

-

Bch Bass Filter Terminal 2

-

Bch Bass Filter Terminal 1

-

Bch Treble Filter Terminal 1

Ground

Power Supply (-)

Power Supply (+)

Chip address setting terminal 0

I

Chip address setting terminal 1

I

Bch Output

O

Ground

Switching noise rejection capacitor (Bch)

Ground

Bch Input 4

I

Bch Input 3

I

Bch Input 2

I

Bch Input 1

I

AUDIO: IC416

AUDIO: IC422

PCM1804DBR (X6872A01) ADC (Analog to Digital Converter)

18

PIN

NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

V

REFL

AGNDL

V

COML

INL+

V

V

INL–

FMT0

FMT1

S/M

OSR0

OSR1

OSR2

BYPAS

DGND

DD

V

DATA/DSDR

I/O FUNCTIONNAME

-

L-channel voltage reference output,

requires capacitors for decoupling to AGND

-

Analog ground for VREFL

-

L-channel analog common-mode voltage (2.5 V)

I

L-channel analog input, positive pin

I

L-channel analog input, negative pin

I

Audio data format 0

I

Audio data format 1

I

Slave/master mode selection

I

Oversampling ratio 0

I

Oversampling ratio 1

I

Oversampling ratio 2

I

HPF bypass control

-

Digital ground

-

Digital power supply +3.3 V

O

L-channel and R-channel audio data output in PCM

mode / R-channel audio data output in DSD mode

PIN

NO.

16

BCK/DSDL

17

LRCK/DSDBCK

18

SCKI

19

RST

20

OVFR

21

OVFL

22

23

AGND

24

VINR–

25

VINR+

26

VCOMR

27

AGNDR

28

V

V

CC

REFR

I/O FUNCTIONNAME

I/O

I/O

Bit clock input/output in PCM mode /

L-channel audio data output in DSD mode

Sampling clock input/output in PCM and

DSD modes

I

System clock input

I

Reset, power-down input, active-low

O

Overflow signal of R-channel in PCM mode

O

Overflow signal of L-channel in PCM mode

-

Analog power supply +5 V

-

Analog ground

I

R-channel analog input, negative pin

I

R-channel analog input, positive pin

-

R-channel analog common-mode voltage (2.5 V)

-

Analog ground for VREFR

-

R-channel voltage reference output,

requires capacitors for decoupling to AGND

AUDIO : IC417

Page 19

PX10/PX8/PX5/PX3

LPC1820FBD144, 551 (YF570B00) MCU

PIN

NO.

1

GPIO2 [0

2

ADC0_1

3

GPIO2

4

VSSIO

5

VDDIO

6

DAC

7

GPIO2

8

GPIO2 [2

9

GPIO2 [4

10

GPIO2 [5

11

GPIO2 [6

12

XTAL1

13

XTAL2

14

I2S1_TX_SCK

15

GPIO5 [12

16

USB0_VDDA3V3_DRIVER

17

USB0_VDDA3V3

18

USB0_DP

19

USB0_VSSA_TERM

20

USB0_DM

21

USB0_VBUS

22

USB0_ID

23

USB0_VSSA_REF

24

USB0_RREF

25

VDDREG

26

TDI

27

TCK

28

DBGEN

29

TRST

30

TMS

31

TDO

32

GPIO0

33

GPIO5 [13

34

I2S1_TX_SDA

35

GPIO5 [14

36

VDDIO

37

GPIO2

38

GPIO0 [4

39

GPIO2 [10

40

VSSIO

41

VDDIO

42

BOOT

43

BOOT [1

44

SSP1_MISO

45

SSP1_SCK

46

GPIO2

47

SSP1_MOSI

48

SSP1_SSEL

49

GPIO1

50

GPIO1 [10

51

GPIO1 [1

52

GPIO1 [2

53

GPIO1 [3

54

GPIO2 [12

55

GPIO1 [4

56

GPIO1 [5

57

GPIO2 [13

58

GPIO2 [14

59

VDDREG

60

GPIO1

61

GPIO1 [7

62

GPIO0 [2

63

GPIO2 [15

64

GPIO0 [3

65

GPIO2 [7

66

GPIO0 [12

67

GPIO0 [13

68

CLKOUT

69

GPIO5

70

GPIO0 [15

71

VDDIO

72

GPIO4

[1]

[3]

[0]

[9]

[0]

[11]

[9]

[6]

[18]

[11]

I/O FUNCTIONNAME

]

I/O

General purpose digital input/output pin

I

ADC input channel 1

I/O

General purpose digital input/output pin

-

Ground

-

I/O power supply +3.3 V

I

ADC input channel 0

I/O

]

I/O

]

I/O

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

General purpose digital input/output pin

I/O

I/O

Input to the oscillator circuit and internal clock generator circuits

I

Output from the oscillator amplifier

O

Transmit Clock

I/O

General purpose digital input/output pin

I/O

Separate analog 3.3 V power supply for driver

USB 3.3 V separate power supply voltage

USB0 bidirectional D+ line

I/O

Dedicated analog ground for clean reference for termination resistors

USB0 bidirectional D- line

I/O

VBUS pin (power on USB cable)

I/O

Indicates to the transceiver whether connected as an

I

A-device (USB0_ID LOW) or B-device (USB0_ID HIGH)

Dedicated clean analog ground for generation of reference currents and voltages

-

12.0 kΩ (accuracy 1 %) on-board resistor to ground for current reference

Main regulator power supply +3.3 V

Test Data In for JTAG interface

I

Test Clock for JTAG interface

I

JTAG interface control signal

I

Test Reset for JTAG interface

I

Test Mode Select for JTAG interface

I

Test Data Out for JTAG interface

O

I/O

General purpose digital input/output pin

I/O

2

I

S1 transmit data

I/O

General purpose digital input/output pin

I/O

I/O power supply +3.3 V

-

I/O

General purpose digital input/output pin

I/O

I/O

Ground

I/O power supply +3.3 V

-

I/O

Boot pin

I/O

Master In Slave Out for SSP1

I/O

Serial clock for SSP1

I/O

General purpose digital input/output pin

I/O

Master Out Slave in for SSP1

I/O

Slave Select for SSP1

I/O

I/O

I/O

I/O

I/O

I/O

General purpose digital input/output pin

I/O

I/O

I/O

I/O

I/O

Main regulator power supply +3.3 V

-

I/O

I/O

I/O

I/O

General purpose digital input/output pin

I/O

I/O

I/O

I/O

Clock output pin

O

I/O

General purpose digital input/output pin

I/O

I/O power supply +3.3 V

General purpose digital input/output pin

I/O

(Microcontroller Unit)

PIN

NO.

73

I

2S0_RX_MCLK

74

I2S0_RX_WS

75

76

77

78

I2S0_RX_SDA

79

80

81

82

83

84

85

GPIO5 [15

86

GPIO5 [16

87

I2C1_SDA

88

89

90

91

92

93

I2C0_SDA

94

95

96

97

98

99

I2S0_TX_MCLK

100

101

102

103

104

GPIO0 [14

105

GPIO1 [11

106

GPIO1 [12

107

108

GPIO1

109

110

111

112

I2S0_TX_SCK

113

114

I2S0_TX_WS

115

GPIO3

116

I2S0_TX_SDA

117

GPIO3 [11

118

SPIFI_SCK

119

SPIFI_SIO3

120

TRACECLK

121

SPIFI_SIO2

122

SPIFI_MISO

123

SPIFI_MOSI

124

125

126

127

128

129

RTC_ALARM

130

WAKEUP0

131

132

TRACEDATA [0

133

TRACEDATA [1

134

TRACEDATA [2

135

136

137

138

139

140

TRACEDATA [3

141

142

143

144

U0_TXD

VSSIO

VDDIO

GPIO3 [2

GPIO3 [3

U0_RXD

GPIO3

GPIO0 [5

GPIO5 [2

I2C1_SCL

N.C.

N.C.

GPIO5

I2C0_SCL

VDDREG

GPIO5

GPIO0 [7

GPIO3 [5

BOOT [2

GPIO3 [6

GPIO3 [7

BOOT [3

GPIO2 [8

VDDIO

VSSIO

GPIO3

VDDIO

GPIO3 [9

SPIFI_CS

RTCX1

RTCX2

VBAT

RESET

VDDREG

VSSA

ADC0_7

VDDA

ADC0_4

ADC0_3

VDDIO

ADC0_6

ADC0_2

ADC0_5

[4]

[5]

[6]

[13]

[8]

[10]

I/O FUNCTIONNAME

O

I/O

O

-

-

I/O

]

I/O

]

I/O

I

I/O

]

I/O

]

I/O

]

I/O

]

I/O

I/O

I/O

-

I/O

I/O

I/O

I/O

]

I/O

]

I/O

]

-

O

]

I/O

]

I/O

]

I/O

]

I/O

]

I/O

]

I/O

]

I/O

I/O

I/O

I/O

]

I/O

I/O

I/O

I/O

]

I/O

O

I/O

O

I/O

I/O

I/O

I/O

I

O

I

O

I

-

]

O

]

O

]

O

I

I

I

]

O

I

I

I

FPN (PN) : IC103

2

S receive master clock

I

Receive Word Select

Transmitter output for USART0

Ground

I/O power supply +3.3 V

2

S Receive data

I

General purpose digital input/output pin

Receiver input for USART0

General purpose digital input/output pin

2

C1 data input/output

I

2

C1 clock input/output

I

Not connected

General purpose digital input/output pin

2

C clock input/output

I

2

C data input/output

I

Main regulator power supply +3.3 V

General purpose digital input/output pin

Boot pin

2

S transmit master clock

I

General purpose digital input/output pin

Boot pin

General purpose digital input/output pin

I/O power supply +3.3 V

General purpose digital input/output pin

Ground

General purpose digital input/output pin

I/O power supply +3.3 V

Transmit Clock

General purpose digital input/output pin

Transmit Word Select

General purpose digital input/output pin

2

S transmit data

I

General purpose digital input/output pin

Serial clock for SPIFI

I/O lane 3 for SPIFI

Trace clock

I/O lane 2 for SPIFI

Input 1 in SPIFI quad mode; SPIFI output IO1

Input 0 in SPIFI quad mode; SPIFI output IO0

SPIFI serial flash chip select

Input to the RTC 32 kHz ultra-low power oscillator circuit

Output from the RTC 32 kHz ultra-low power oscillator circuit

RTC power supply: 3.3 V on this pin supplies power to the RTC

External reset input

RTC controlled output

External wake-up input

Main regulator power supply +3.3 V

Trace data, bit 0

Trace data, bit 1

Trace data, bit 2

Analog ground

ADC input channel 7

Analog power supply +3.3 V and ADC reference voltage

ADC input channel 4

ADC input channel 3

Trace data, bit 3

I/O power supply +3.3 V

ADC input channel 6

ADC input channel 2

ADC input channel 5

19

Page 20

PX10/PX8/PX5/PX3

YSS952-QZE2A (YE441A00) DSP (SPR-2) (Digital Signal Processor)

PIN

NO.

10

11

12

13

14

15

16

1

2

3

4

5

6

7

8

9

GPIO5

GPIO4

GPIO3

DVSS

GPIO2

GPIO1

GPIO0

PLLVDD

IC_N

PLLVSS

PLLVSS

XIN

XOUT

IOVDD

SCL

SDA

I/O FUNCTIONNAME

I/O

I/O

General-purpose I/O pins

I/O

-

GND

I

I

General-purpose I/O pins

I

-

PLL power supply

I

Hardware reset pin

-

PLL GND

I

Clock input pin

O

Clock output pin

-

Control interface power supply

2

C control bus clock input pin

I

I

2

C control bus data I/O pin

I

I/O

PIN

NO.

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

OPEN

DVSS

IRQ_N

DVDD18

GPIO11

TESTb

DVSS

OPEN

DVSS

GPIO10

GPIO9

GPIO8

IOVDD

GPI07

DVDD18

GPI06

I/O FUNCTIONNAME

-

Leave this pin open

-

GND

O

Interrupt request output pin to the host controller

-

Core power supply

I/O

General-purpose I/O pins

I

Test pin

-

GND

-

Leave this pin open

-

GND

I/O

I/O

General-purpose I/O pins

I/O

-

Control interface power supply

I/O

General-purpose I/O pins

-

Core power supply

I/O

General-purpose I/O pins

YDA177-VZ (YF978A00) DIGITAL POWER AMPLIFIER

PIN

NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

DVSS

XTALVSS

XO

XI

XTALGND

CLKINS

FSSELA0

FSSELA1

FSSELB0

FSSELB1

ADDRESS0

ADDRESS1

ZERODET

TEST

MSSEL

DGND

CLKOUT

CLKINB

DVSS

DVSS

SDA

SCL

MUTEIA_N

MUTEIB_N

PROTA_N

PROTB_N

CLIPA_N

CLIPB_N

IOVDD33

CURLB

CURHB

AMPTEMPB

VSENSEB

ISENSEB

VINTB

IINTB

AVDDB

AINB

VOUTB

VGNDB

AVSSB

INPB

INMB

AGNDB

I/O FUNCTIONNAME

-

Digital block power supply DVSS(-5V)

-

XTAL power supply DVSS(-5V)

O

XTAL output

Is

XTAL input

-

GND for XTAL

I

System clock for slave mode

I

A channel carrier clock switching pin

I

I

B channel carrier clock switching pin

I

I

I2C slave address setting

I

I

Zero crossing sensing function enable / disable setting

I

Test mode setting terminal (Internal specification)

I

Device master / slave setting pin

-

Digital block power supply GND (0V)

O

Clock output

I

Clock input for B channel

Digital block power supply P(-5V)

-

Is/OD

I2C data

Is

I2C clock

AI

A channel mute external control terminal

AI

B channel mute external control terminal

OD

A channel protection signal

OD

B channel protection signal

OD

A channel clip sensing flag signal

OD

B channel clip sensing flag signal

-

External I2C host device power sensing P (3.3V)

AI

B channel Low-side OCP sensing signal

AI

B channel Hi-side OCP sensing signal

AI

B channel heatsink temperature sensing terminal (thermistor)

AI

B channel Output voltage sensing pin

AI

B channel output current sensing pin

AI

B channel Integral capacity connection for voltage monitor

AI

B channel Integral capacity connection for current monitor

-

B channel Analog block power supply AVDD(+5V)

AI

B channel input terminal

AO

B channel electronic volume output terminal

-

power supply for B channel electronic volume GND(0V)

-

B channel analog block power supply AVSS(-5V)

AI

B channel power amplifier input + terminal

AI

B channel power amplifier input - terminal

-

B channel analog block power supply GND(0V)

PIN

NO.

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

OFFTB

LFB

MUTEB_N

OUTB

OUTBX

VREF

MBMNT

OUTAX

OUTA

MUTEA_N

LFA

OFFTA

AGNDA

INMA

INPA

AVSSA

VGNDA

VOUTA

AINA

AVDDA

PBMNT

IINTA

VINTA

ISENSEA

VSENSEA

AMPENBL

AMPTEMPA

CURHA

CURLA

PSTEMP

VOLA

VOLB

DGND

RECOV

PLENBL

PARAMSET

I/O FUNCTIONNAME

AI

(*1 connect to GNDB through a 0Ω resistor.)

FRQQHFWWR966%WKURXJKDѥ)FDSDFLWRU

(Capacitor :No Mount)

AI

B channel Loop Filter capacitor connection terminal

O

B channel driver IC mute control terminal

O

B channel PWM output terminal

(Hi/Low by control for Hi-side signal)

O

B channel PWM output terminal

(Hi/Low by control for LoW-side signal)

AO

Analog intermediate voltage (AVSS/2)

AI

The final stage for the power supply (-200V) partial pressure signal

O

A channel PWM output terminal

(Hi/Low by control for LoW-side signal)

O

A channel PWM output terminal

(Hi/Low by control for Hi-side signal)

O

A channel driver IC mute control terminal

AI

A channel Loop Filter capacitor connection terminal

AI

(*1 connect to GNDA through a 0Ω resistor.)

FRQQHFWWR$966$WKURXJKDѥ)FDSDFLWRU

(Capacitor :No Mount)

-

A channel Analog block power supply GND(0V)

AI

A channel power amplifier input + terminal

AI

A channel power amplifier input - terminal

-

A channel analog block power supply AVSS(-5V)

-

A channel electronic volume connection terminal GND(0V)

AO

A channel electronic volume connection terminal

AI

A channel input terminal

-

A channel analog block power supply AVDD(+5V)

AI

The final stage for the power supply (+200V) partial pressure signal

AI

A channel Integral capacity for current monitor

AI

A channel Integral capacity connection for voltage monitor

AI

Output current sensing pin

AI

Output voltage sensing pin

I

Start up timer terminal

AI

A channel heatsink temperature sensing terminal (thermistor)

AI

A channel Hi-side OCP sensing signal

AI

A channel Low-side OCP sensing signal

AI

Primary power source temperature (POSISTOR signal)

AI

A channel volume terminal

AI

B channel volume terminal

-

Digital block power supply GND(0V)

I

Automatic return function enable / disable setting

I

POWER LIMIT function enable / disable setting

I

Parameter input switching pin

AUDIO: IC410

AUDIO:IC601

20

Page 21

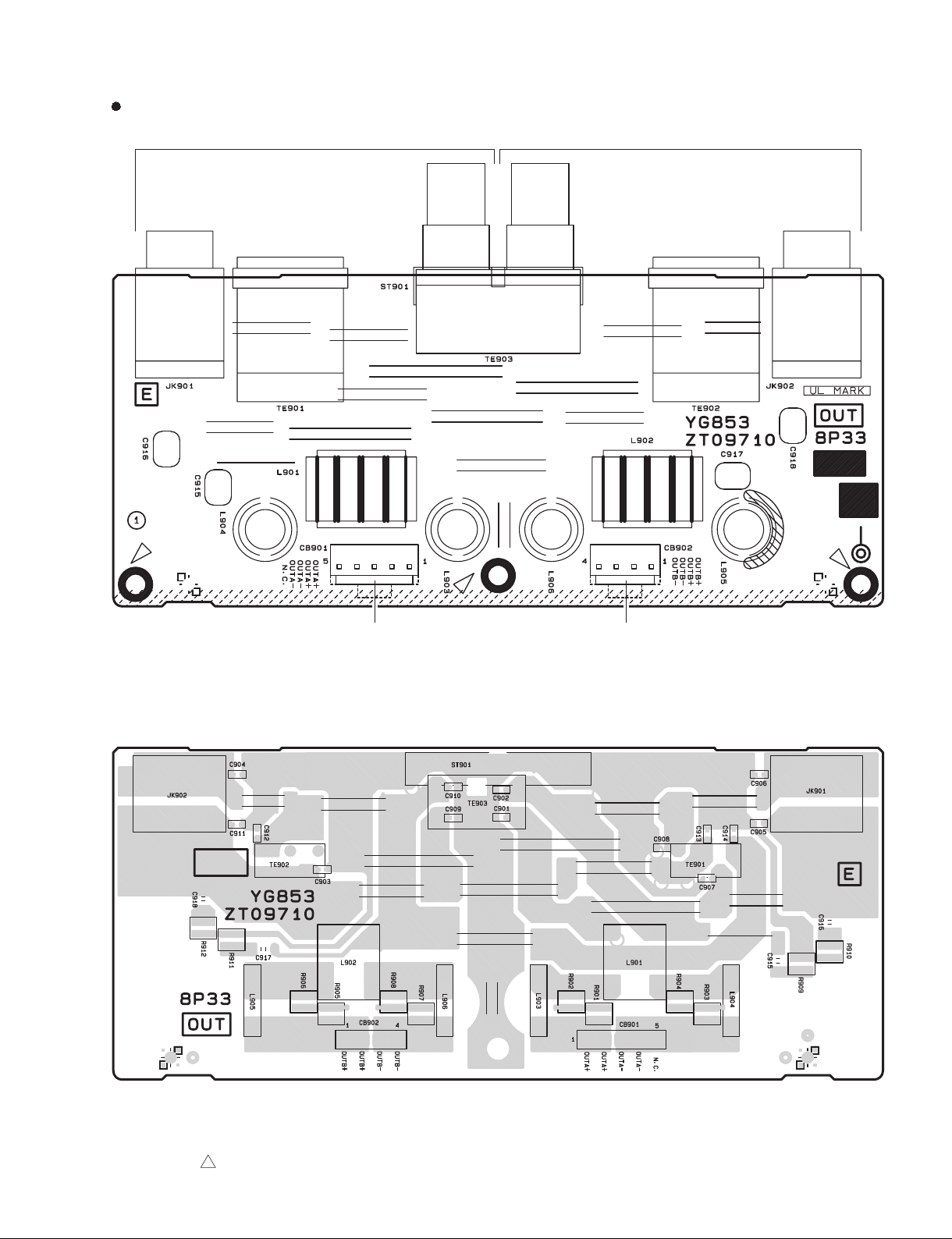

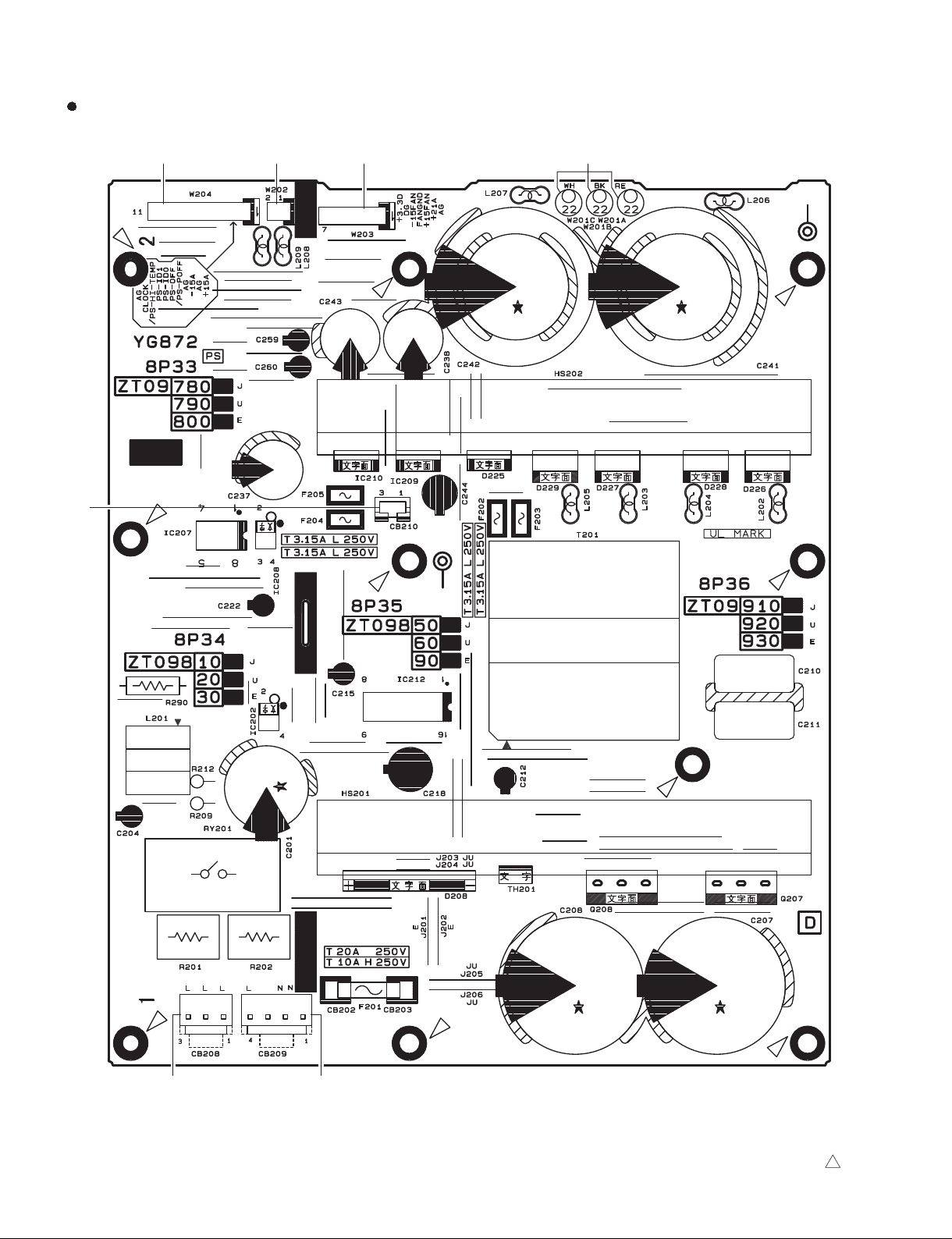

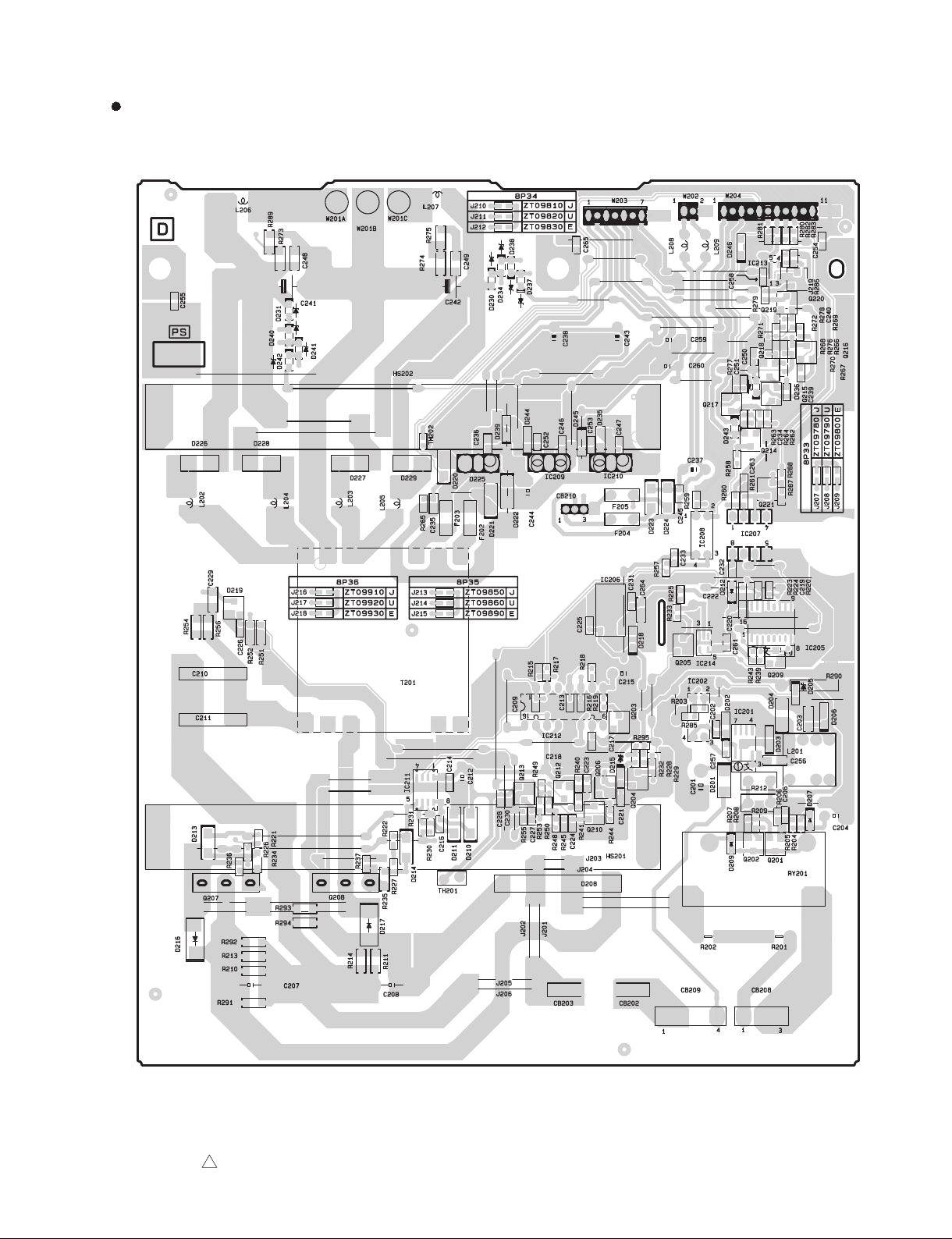

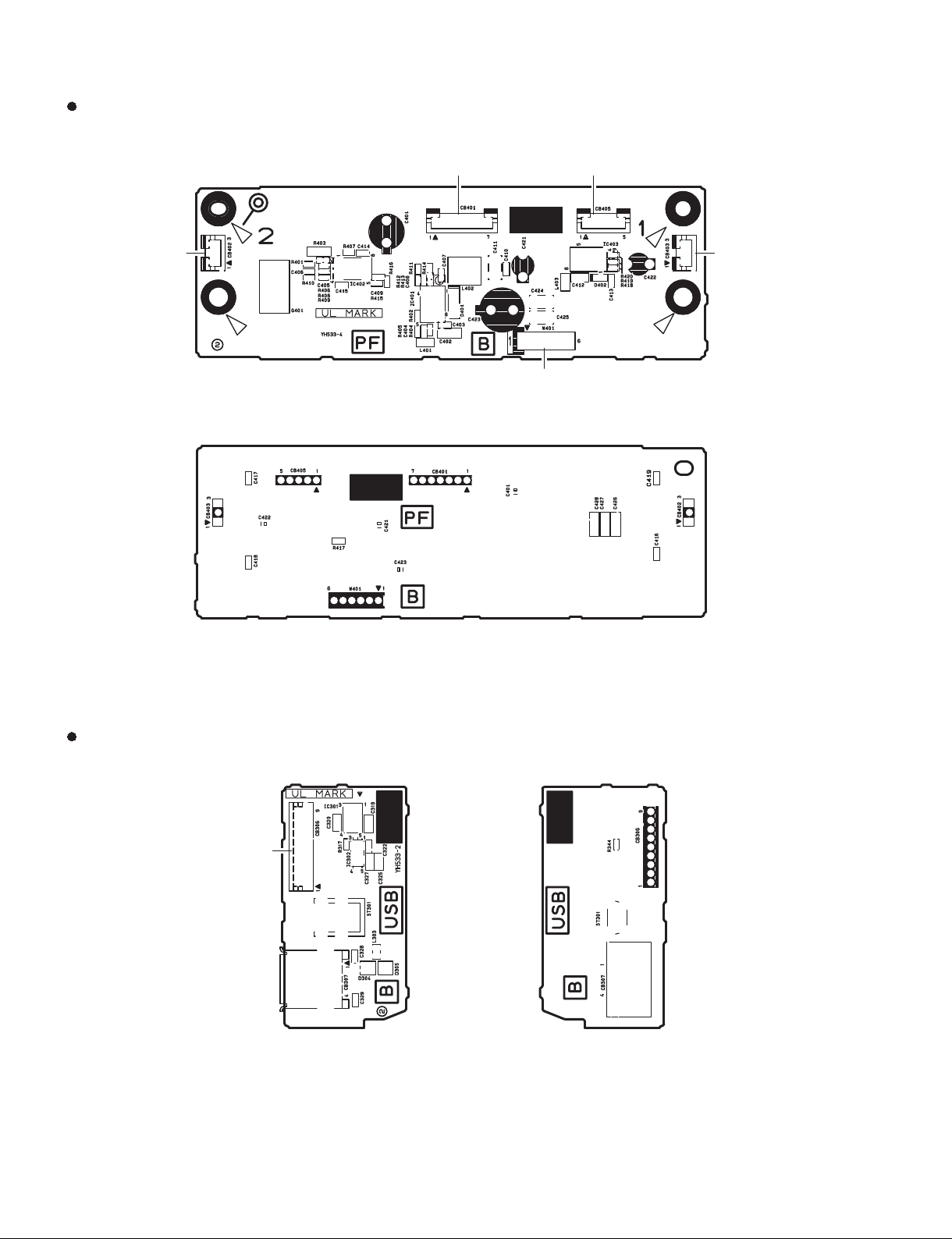

CIRCUIT BOARDS(シート基板図)

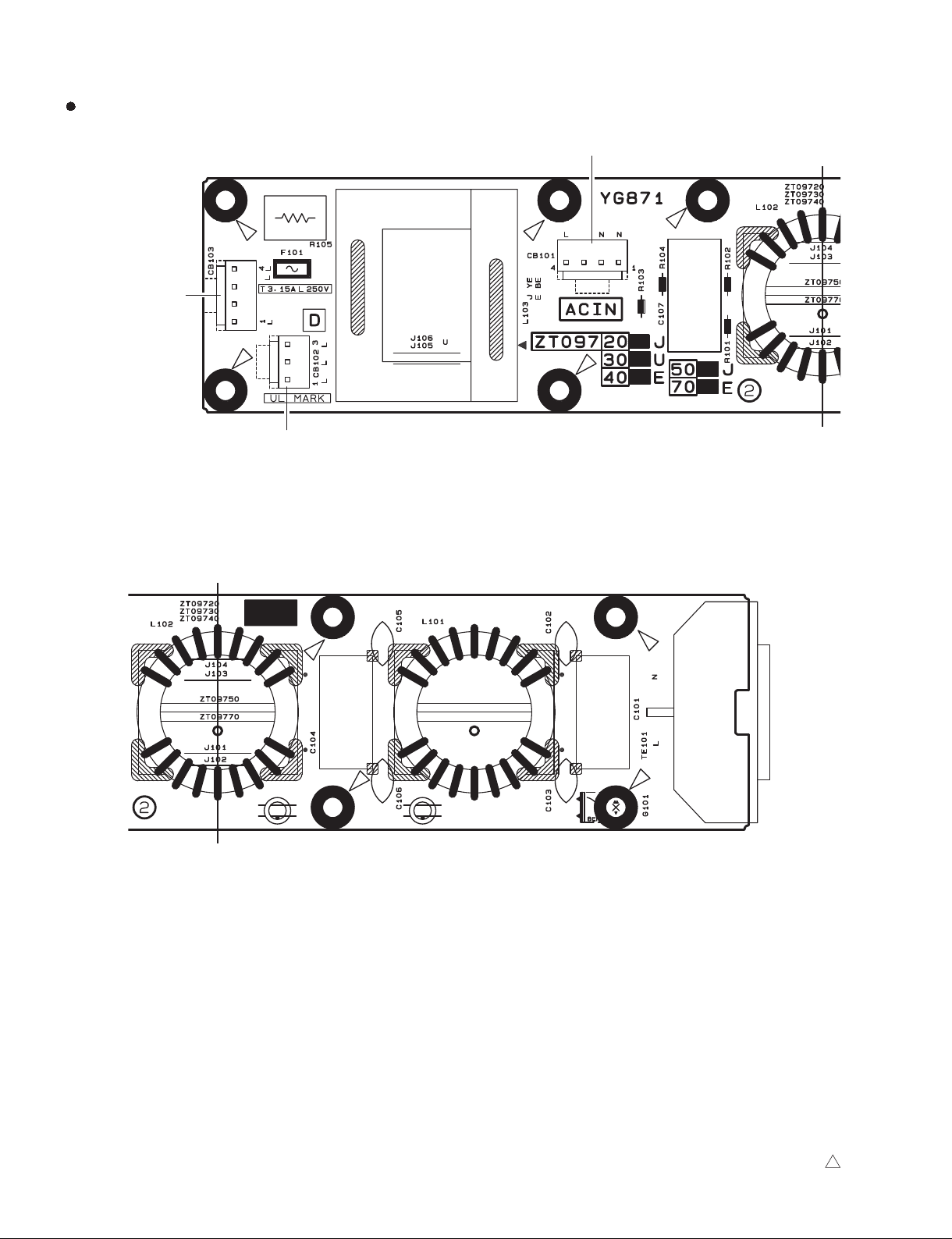

ACIN Circuit Board (YG871D0) ........................................ 22/23

AUDIO Circuit Board (YG852E0) ..................................... 24/25

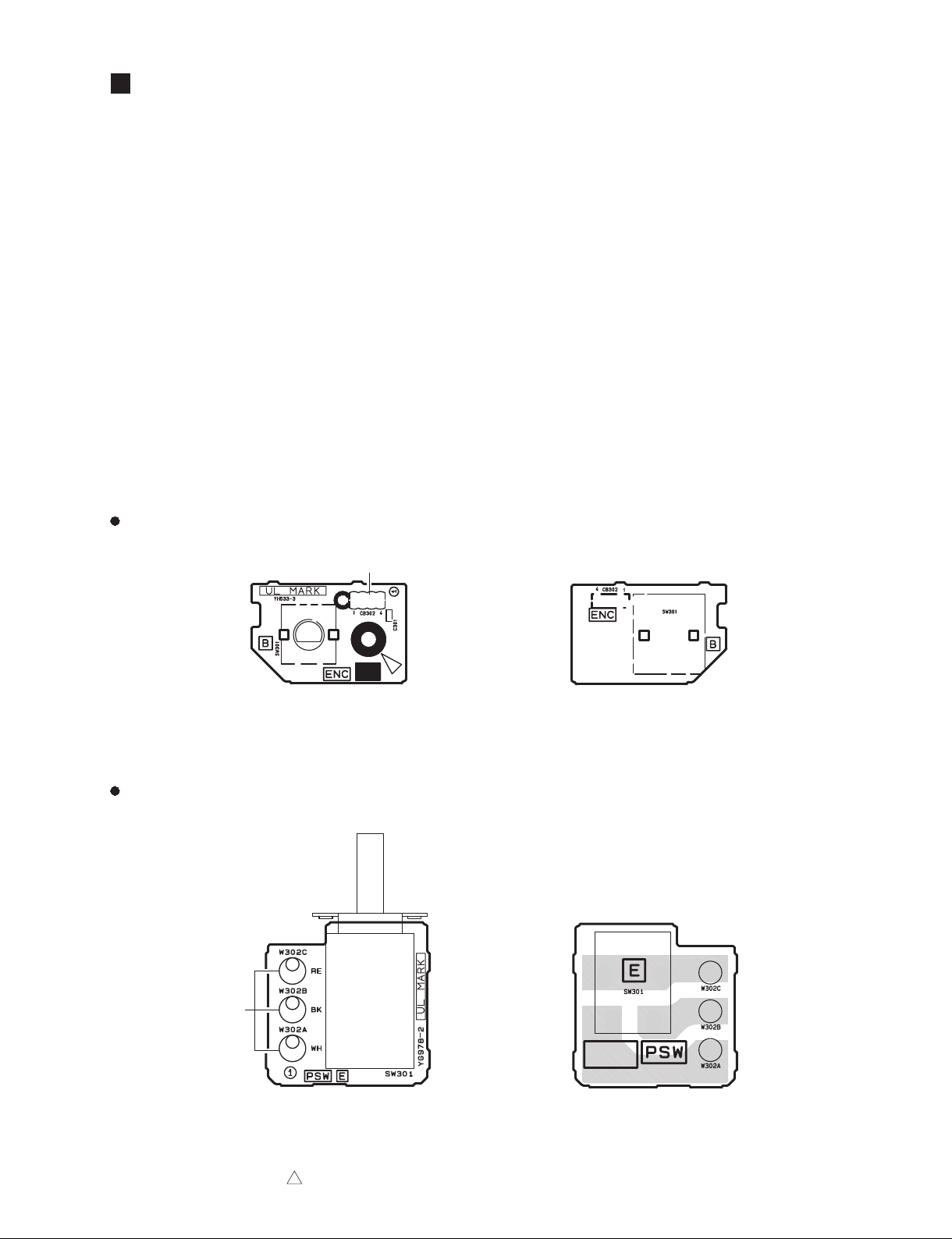

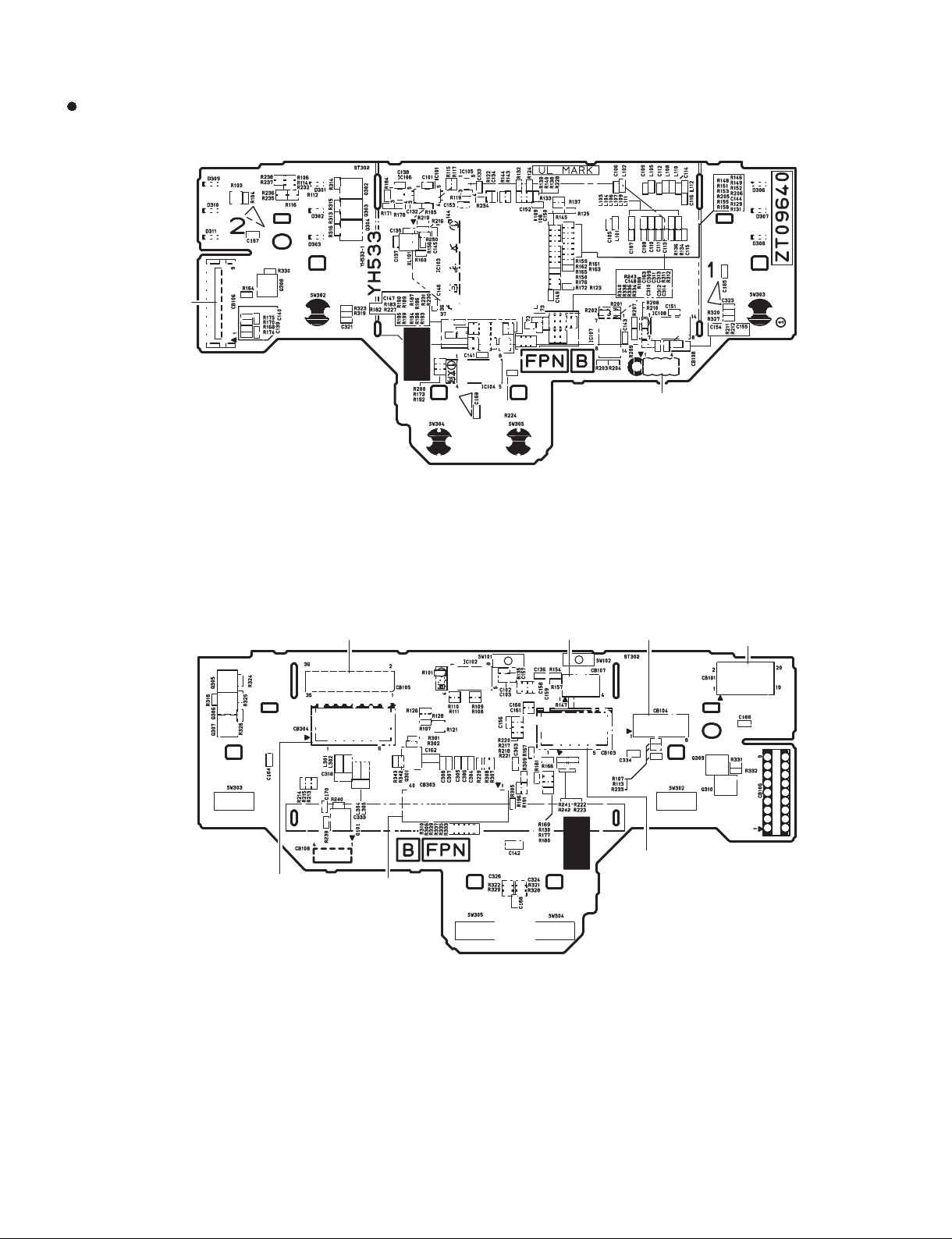

ENC (PN) Circuit Board (YH533B0) ...................................... 21

FPN (PN) Circuit Board (YH533B0)....................................... 26

OUT Circuit Board (YG853E0) .............................................. 27

PF (PN) Circuit Board (YH533B0) ......................................... 30

PS Circuit Board (YG872D0) ............................................ 28/29

PSW (SUB) Circuit Board (YG978E0) ................................... 21

USB (PN) Circuit Board (YH533B0) ...................................... 30

VOL (SUB) Circuit Board (YG978E0) .................................... 31

Note: See parts list for details of circuit board component parts.

注 : シートの部品詳細はパーツリストをご参照ください。

PX10/PX8/PX5/PX3

ENC (PN) Circuit Board

to FPN-CB108

Component side

PSW (SUB) Circuit Board

POWER SW

(部品側)

Pattern side

(パターン側)

to ACIN-CB103

ENC (PN) : 2NA-ZT09640

PSW (SUB) : 2NA-ZT09940

Component side

3

(部品側)

Pattern side

(パターン側)

21

Page 22

PX10/PX8/PX5/PX3

ACIN Circuit Board

to PSW-W302A/B/C

A

to PS-CB208

to PS-CB209

A

A’

A’

AC-INLET

Component side

2NA-ZT09720

(部品側)

2

22

Page 23

ACIN Circuit Board

PX10/PX8/PX5/PX3

B

B’

B’

B

Pattern side

(パターン側)

2NA-ZT09720

2

23

Page 24

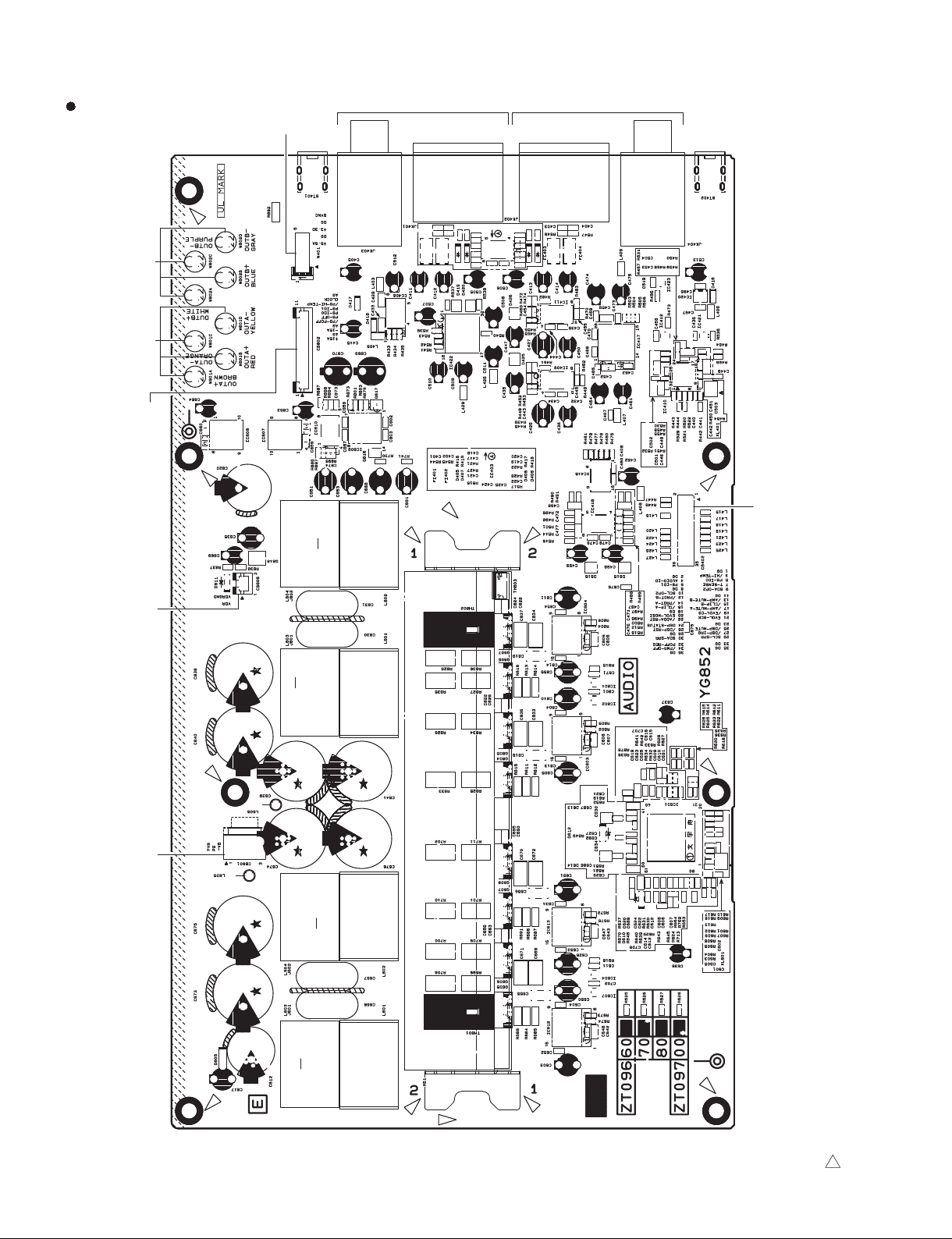

PX10/PX8/PX5/PX3

AUDIO Circuit Board

to OUT-CB901

to PS-W204to PS-W202to PS-W201A/B/C to OUT-CB902

Scale: 80/100

INPUT A INPUT B

to PF-CB405

to FPN-CB105

24

Component side

(部品側)

2NA-ZT09660

3

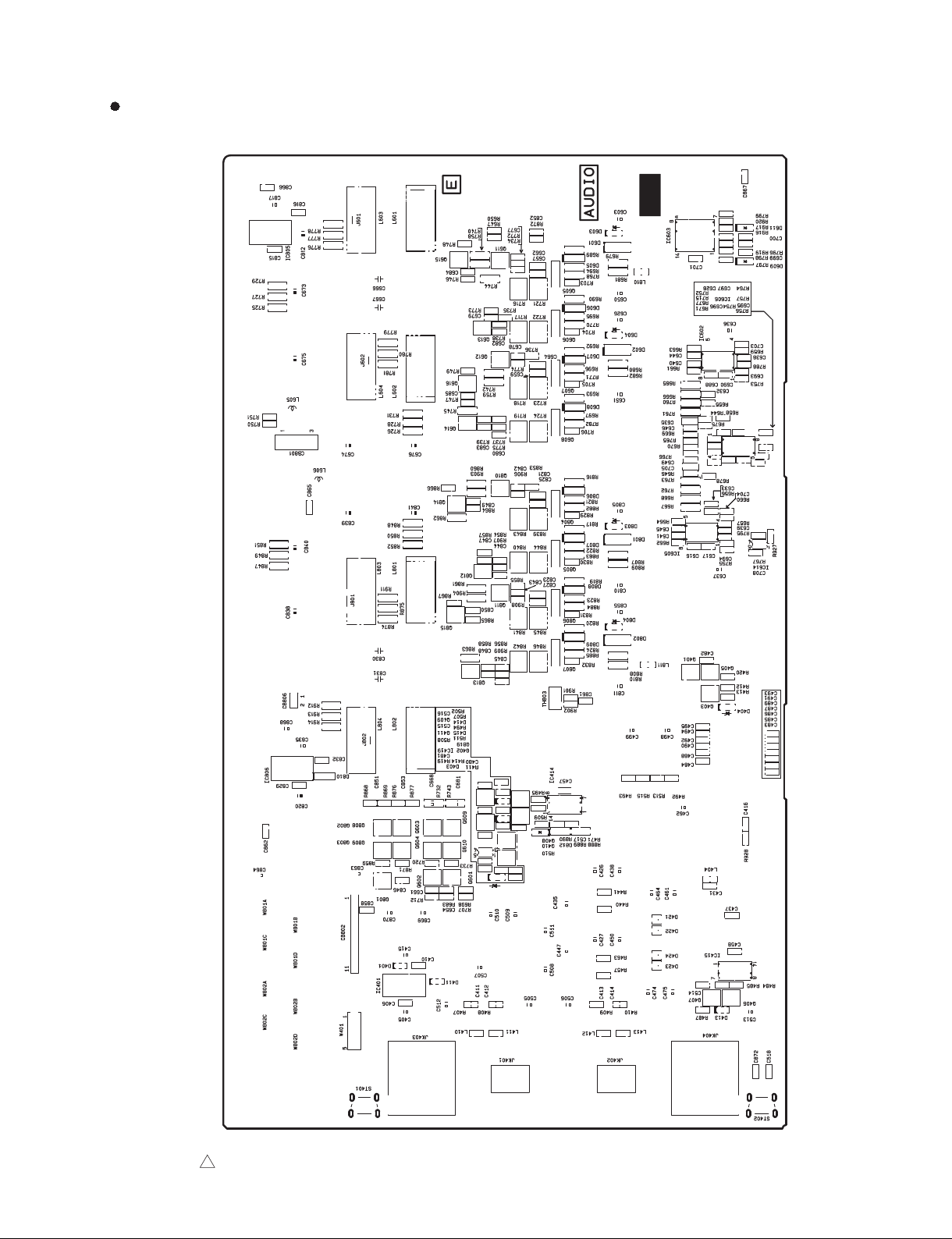

Page 25

AUDIO Circuit Board

PX10/PX8/PX5/PX3

Scale: 80/100

2NA-ZT09660

Pattern side

3

(パターン側)

25

Page 26

PX10/PX8/PX5/PX3

FPN (PN) Circuit Board

to USB-CB306

to ENC-CB302

to PF-W401

to AUDIO-CB402 N.C.

to DISPLAY

N.C.

to VOL-W301

Component side

not installed

(部品側)

26

Pattern side

2NA-ZT09640

(パターン側)

Page 27

OUT Circuit Board

SPEAKERS A SPEAKERS B

PX10/PX8/PX5/PX3

to AUDIO-W801A/B/C/D to AUDIO-W802A/B/C/D

Component side

(部品側)

2NA-ZT09710

Pattern side

1

(パターン側)

27

Page 28

PX10/PX8/PX5/PX3

PS Circuit Board

to AUDIO-CB802 to AUDIO-CB806 to AUDIO-CB801to PF-CB401

to POWER TRANSFORMER

28

to ACIN-CB102

to ACIN-CB101

Component side

2NA-ZT09780

(部品側)

2

Page 29

PS Circuit Board

PX10/PX8/PX5/PX3

2NA-ZT09780

Pattern side

2

(パターン側)

29

Page 30

PX10/PX8/PX5/PX3

PF (PN) Circuit Board

to PS-W203 to AUDIO-W401

to DC FAN

to FPN-CB304

to DC FAN

Component side

Pattern side

(パターン側)

(部品側)

USB (PN) Circuit Board

to FPN-CB106

30

Component side

(部品側)

Pattern side

(パターン側)

2NA-ZT09640

Page 31

VOL (SUB) Circuit Board

VOLUME A VOLUME B

PX10/PX8/PX5/PX3

to FPN-CB103

Component side

Pattern side

(パターン側)

(部品側)

2NA-ZT09940

3

31

Page 32

PX10/PX8/PX5/PX3

INSPECTION

1. Preparation

1-1. Equipment

•USB Memory

•Connect a FAT32 formatted USB2.0 memory

1-2. How to connect

Connection diagram

Insert a USB Memory in a PX's USB port.

3. List of inspection items

※○:inspect/×:not inspect

Inspection

No

category

01 USB USB Bus, USB0-ID Auto

02 Information Firmware version Measure

03 Statistics Browsing Visual

04 DP200 I2C Bus Auto

05 Temperature

Inspection item Judgment Service

VBUS Measure

/VBUS-FLG Measure

SERIES-ID Visual

AUDIO-ID Visual

AUDIO-ID Variable Semi-Auto

PS-ID0 Visual

PS-ID0 Variable Semi-Auto

PS-ID1 Visual

PS-ID1 Variable Semi-Auto

Clear Visual

OCPA Flag PROTA_N Auto

OCPB Flag PROTB_N Auto

VI-CALIB-A Auto

VI-CALIB-B Auto

V-SENSE-A (OUTVA) Auto

V-SENSE-B (OUTVB) Auto

I-SENSE-A (OUTIA) Auto

I-SENSE-B (OUTIB) Auto

/CLIP-A ON Auto

/CLIP-A OFF Auto

/CLIP-B ON Auto

/CLIP-B OFF Auto

AMP-A (OTP_PS Flag,PROT*_N)

AMP-B (T-SENSE) Auto

/HI-TEMP Auto

Auto

2. Modes for Activation

2-1. Service inspection mode

This activation mode is to perform Service inspection.

Turn on while pushing the [MENU]key, the [A]key and

the [B] key simultaneously.

[A] key [B] key

[ ] (Back) key[MENU] key Main knob

Inspection

No

category

○

×

×

○

○

○

×

○

×

○

×

○

○

○

×

×

○

○

○

○

○

○

×

×

×

×

×

○

×

06 SPI fl ash SPI Bus Auto

07 DSP I2C Bus Auto

08 Analog CFG1(+14dBu) Measure

09 LCD Parallel Bus Auto

10 FAN Turn Visual

11 LED In order Visual

12 Tact switch In order Semi-Auto

13 Rotary encoder Rotate Left Semi-Auto

Rotary potentiometer

14

15 Power off

Inspection item Judgment Service

/DSP-IRQ Auto

DSP-STATUS Auto

CFG2(+4dBu) Measure

CFG3(E-VOL=MUTE) Measure

CFG4(BOOST MODE) Measure

/DSP-MUTE ON Measure

/DSP-MUTE OFF Measure

Panel Visual

LCD-CONT (Contrast) Visual

LCD-BL (Backlight) Visual

Maximum speed Visual

Minimum speed Visual

Rotate Right Semi-Auto

VOL-ALT positive Semi-Auto

VOL-ALT negative Semi-Auto

Calibration 2 Semi-Auto

Confi rm & Save 2 Semi-Auto

/POFF-REQ /PWR-OFF(IRQ)

Visual

○

○

○

○

○

○

○

○

○

○

○

○

○

○

×

○

○

○

○

○

○

×

×

○

○

○

32

Page 33

4. Service inspection

4-1. How to connect

Refer to the “1-2. How to connect” (Page 32) of

Inspection section.

4-2. How to activate

Refer to the “2-1. Service inspection mode” (Page 32) of

Inspection section.

If powered on with service inspection mode successfully,

during Power On sequence, all LEDs light up simultaneously

for a few seconds.

4-3. The display for inspection

The PX device LCD. Category selection screen.

PX10/PX8/PX5/PX3

4-4. How to inspect

Controls Inspection category Inspection item After Execution

[MENU] key display category item display category item

[A] key select before category select before item display result before page

Switch

[B] key select next category select next item display result next page

Main knob fi x category (display item) execute item select next item

Main knob Left select before category select before item display result before page

Encoder

Main knob Right select next category select next item display result next page

Left end✽is a selecting cursor.

The automatic paging is supported.

33

Page 34

PX10/PX8/PX5/PX3

5. Inspection item

5-1. USB

5-1-1. USB Bus, USB0-ID

Contents The state of FAT32 fi le system currently recorded on

the USB memory is inspected.

Advance preparation

Confi rm the USB memory is inserted.

Service inspection screen

〈

〉

5-2. Information

5-2-1. Firmware version

Contents A version number inspects visual agreement.

Advance preparationNone.

Service inspection screen

〈

Inspect visually.

The fault location at the time of FAIL

Firmware is not upgraded correctly.

〉

The fault location at the time of FAIL

USB Bus (USB-DP, USB-DN, VBUS-EN, IC301, IC302),

USB0-ID

5-1-2. VBUS (PCB PN Assembly only)

This is not tested for service inspection of PX amplifi er.

5-1-3. /VBUS-FLG (PCB PN Assembly only)

This is not tested for service inspection of PX amplifi er.

5-2-2. SERIES-ID

Contents An SERIES-ID (from PCB PN) inspects visual

agreement.

Advance preparationNone.

Service inspection screen

〈

Inspect visually that it was displayed as “PX”.

The fault location at the time of FAIL

SERIES-ID0, SERIES-ID1, SERIES-ID2

〉

34

Page 35

PX10/PX8/PX5/PX3

5-2-3. AUDIO-ID

Contents An AUDIO-ID inspects automatically that it is in

agreement with an expected value.

Advance preparationNone.

Service inspection screen

〈

Inspect visually agreeing with the model name printed at the

panel.

The fault location at the time of FAIL

The classifi cation of PCB AUDIO connected is different.

Or, the circuit of the AUDIO-ID circumference is fault.

〉

5-2-6. PS-ID0 Variable (PCB PN Assembly only)

This is not tested for service inspection of PX amplifi er.

5-2-7. PS-ID1

Contents An PS-ID1(from PCB PS) inspects visually agreeing

with the destination of a PX amplifi er.

Advance preparationNone.

Service inspection screen

〈

Inspect visually agreeing with the destination of a PX amplifi er

using the following chart.

〉

5-2-4. AUDIO-ID Variable (PCB PN Assembly only)

This is not tested for service inspection of PX amplifi er.

5-2-5. PS-ID0

Contents An PS-ID0 (from PCB PS) inspects visually agreeing

with the model name printed at the panel.

Advance preparationNone.

Service inspection screen

〈

Inspect visually agreeing with the model name printed at the

panel.

〉

PS-ID1 destination

European model

British model

E

Korean model

Chinese model

U.S.A. model

U

Taiwan model

Brazilian model

J Japanese model

The fault location at the time of FAIL

The classifi cation of PCB PS connected is different.

Or, the circuit of the PS-ID1 circumference is fault.

5-2-8. PS-ID1 Variable (PCB PN Assembly only)

This is not tested for service inspection of PX amplifi er.

The fault location at the time of FAIL

The classifi cation of PCB PS connected is different.

Or, the circuit of the PS-ID0 circumference is fault.

35

Page 36

PX10/PX8/PX5/PX3

5-3. Statistics (Service only)

5-3-1. Browsing

Contents The operating condition statistic of amplifier is

inspected visually.

Refer to Statistics list.

Statistics list

Parameter Meaning

Power ON The number of times of turn on the power.

Encoder The number of times of rotation. Yes

Attenuator-A The number of times of rotation. Yes

Attenuator-B The number of times of rotation. Yes

Data Broken

/PS-HI-TEMP The number of /PS-HI-TEMP. Yes

Over Current

Low Temp

Low Mid Temp

High Mid Temp

High Temp

Total Op The operation total number of seconds.

Long Op

Flicker The number of power fl icker counts.

Run Away The number of run away counts.

The number of times of detecting data corruption.

The number of times that the excessive output exceeded the threshold.

The number of times of being a low temperature per unit time.

The number of times of being a lower-middle temperature per unit time.

The number of times of being a higher-middle temperature per unit time.

The number of times of being a high temperature per unit time.

The number of times that hours operated were 24 hours or more.

Clear Object

5-3-2. Clear

Contents After exchanging the following parts, a related

statistic is cleared manually.

Exchanged parts Item to clear

SW301 Rotary encoder The number of times of rotation

VR301 Rotary potentiometer The number of times of rotation

VR302 Rotary potentiometer The number of times of rotation

PCB PS The number of /PS-HI-TEMP

Advance preparationNone.

Note Don't clear accidentally.

Service inspection screen

〈

〉

Advance preparationNone.

Service inspection screen

〈

〉

Left end✽is a selecting cursor.

Left end✽is a selecting cursor.

Rotate the Main knob, confi rm the all parameters.

<Attention>

The purpose of this inspection is to obtain the hint of a fault cause.

This inspection does not pinpoint a fault location.

36

Page 37

5-4. DP200 (IC601)

5-4-1. I2C Bus

Contents Via I2C Bus which is a communication path with a

microcomputer, it inspects automatically using the

register of DP200.

Advance preparationNone.

Service inspection screen

〈

〉

PX10/PX8/PX5/PX3

5-4-4. V-SENSE (OUTVA,OUTVB)

Contents When the output voltage of amplifier without load

is normal, it inspects automatically that the value

of the OUTVA or OUTVB register of DP200 is

judgment within the range.

Advance preparation

1. Connect 8 ohms load resistances for PX amplifi er output

terminals.

2. Input 1kHz sine wave signal to PX amplifi er.

3. Adjust amplifi er outputs to 250W@8Ω.

Service inspection screen

〈

〉

Left end✽is a selecting cursor.

The fault location at the time of FAIL

I2C Bus(SCL-DP2, SCA-DP2)

5-4-2. OCPA Flag PROTA_N

This is not tested for service inspection of PX amplifi er.

5-4-3. OCPB Flag PROTB_N

This is not tested for service inspection of PX amplifi er.

Left end✽is a selecting cursor.

The fault location at the time of FAIL

VSENSEA, VSENSEB

37

Page 38

PX10/PX8/PX5/PX3

5-4-5. I-SENSE

Contents When the output current of amplifier with rated

Advance preparation

1. Connect 8 ohms load resistances for PX amplifi er output

terminals.

2. Input 1kHz sine wave signal to PX amplifi er.

3. Adjust amplifi er outputs to 250W@8Ω.

Service inspection screen

〈

(OUTIA,OUTIB)

load is normal, it inspects automatically that the

value of the OUTIA or OUTIB register of DP200 is

judgment within the range. Refer to the following

specifi cations about the normal current.

〉

5-4-9. /CLIP-B OFF

This is not tested for service inspection of PX amplifi er.

5-4-10. V-SENSE,I-SENSE Calibration

Contents This inspection is divided into every A and B, and is

performed.