Page 1

DSP UNIT

SERVICE MANUAL

PA

011509

CONTENTS

REVISED PAGE LIST ··························································· 2-1

SPECIFICATIONS································································· 3-1

PANEL LAYOUT···································································· 3-2

DIMENSIONS········································································ 3-4

CONNECTOR CIRCUIT DIAGRAM ········································· 4

DISASSEMBLY PROCEDURE················································· 6

LSI PIN DESCRIPTION·························································· 10

IC BLOCK DIAGRAM ····························································· 17

CIRCUIT BOARDS································································· 21

INSPECTION·········································································· 42

TEST PROGRAM··································································· 43

ERROR MESSAGES······························································ 57

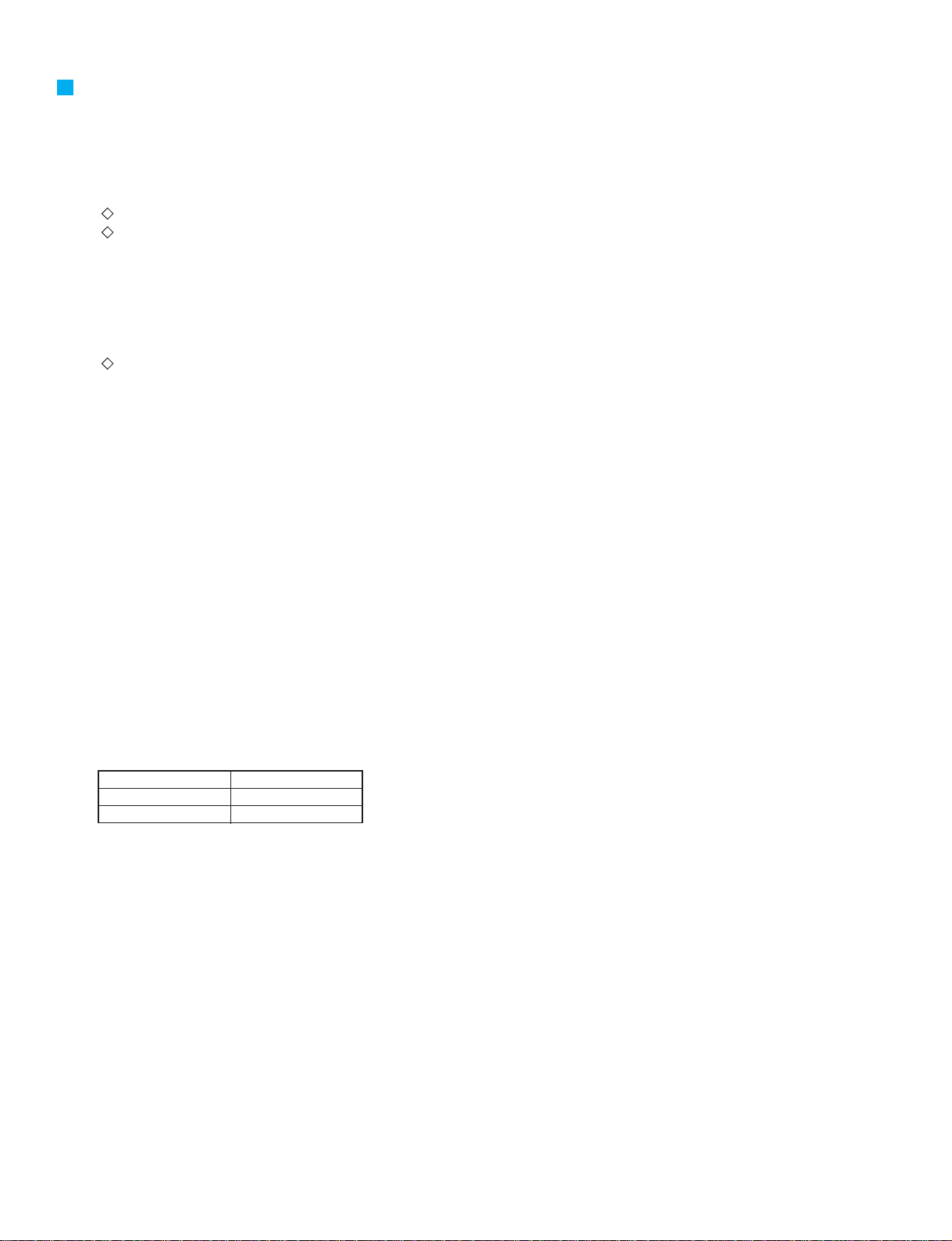

BLOCK DIAGRAM·································································· 58

PARTS LIST

CIRCUIT DIAGRAM

HAMAMATSU, JAPAN

0.27K-

****

Printed in Japan '00.09

Page 2

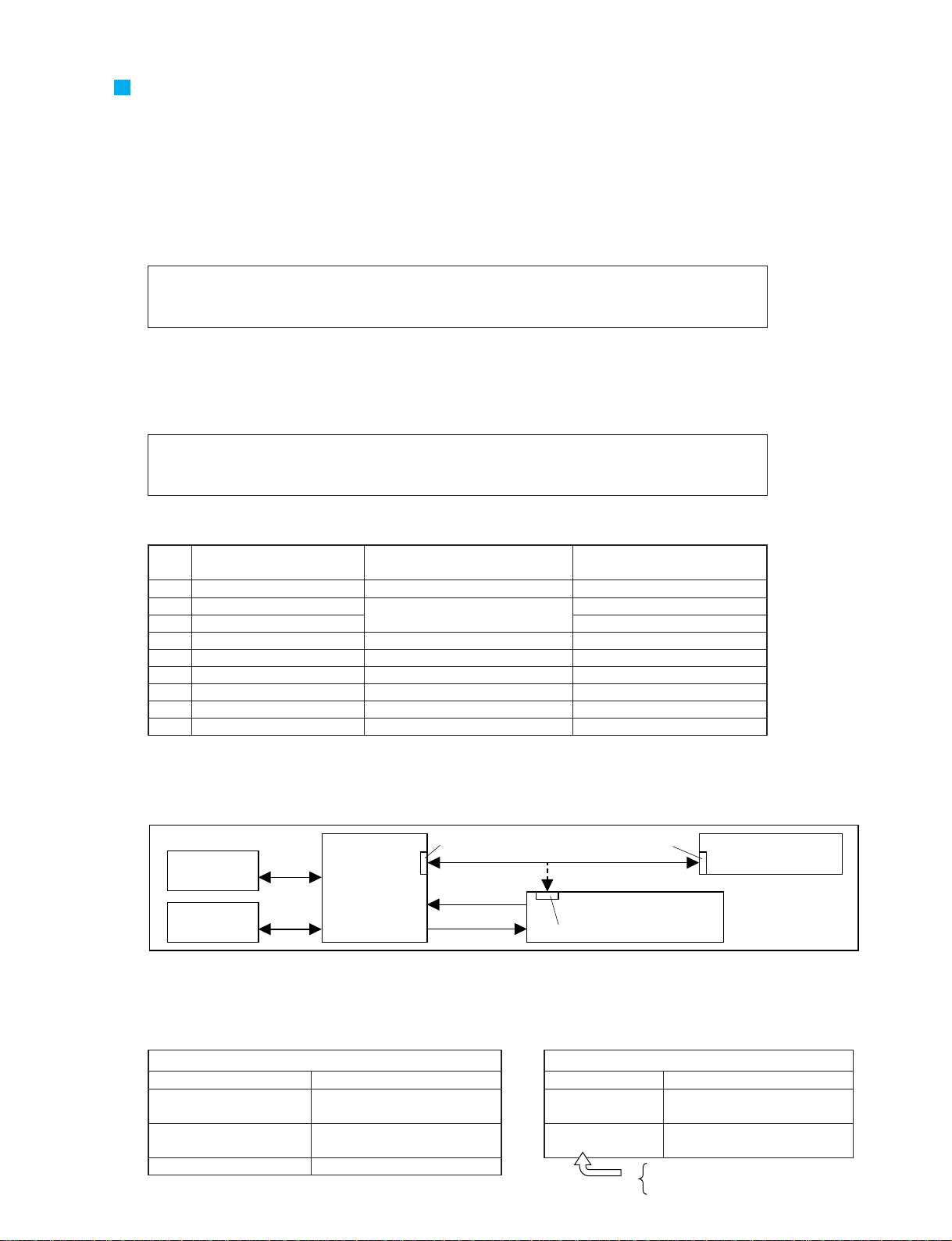

DSP1D

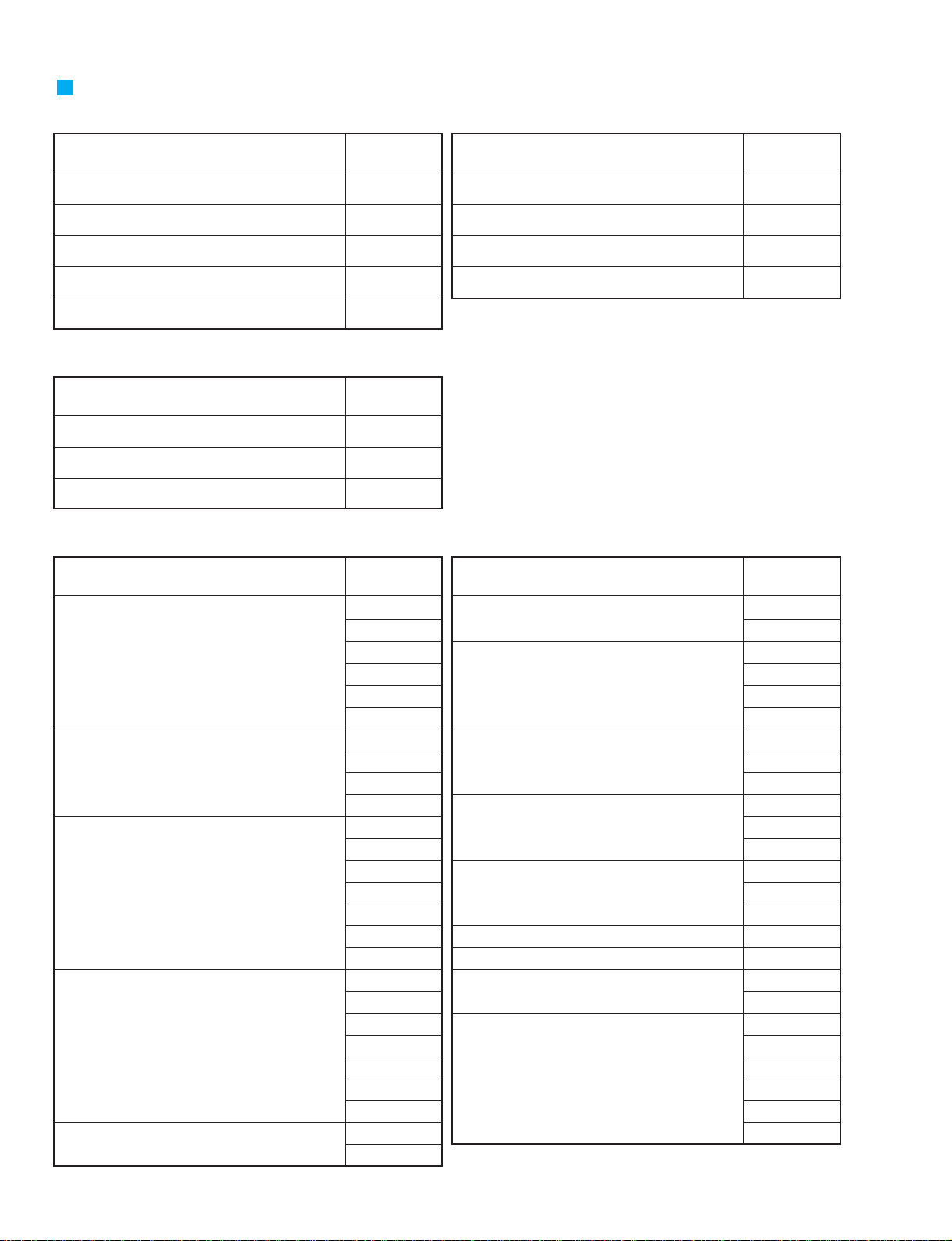

REVISED PAGE LIST

ITEM

SPECIFICATIONS

PANEL LAYOUT

DIMENSIONS

CONNECTOR CIRCUIT DIAGRAM

CIRCUIT BOARDS IFC1 Circuit Board

<

PARTS LIST>

ITEM

OVERALL ASSEMBLY

JK BOX ASSEMBLY

ELECTRICAL PARTS

<

CIRCUIT DIAGRAM>

ITEM

PAGE

3-1

3-2,3-3

3-4

4

35

PAGE

2~ 5

6

7~24

PAGE

ITEM

INSPECTION

TEST PROGRAM

ERROR MESSAGES

BLOCK DIAGRAM

ITEM

PAGE

42

43~56

57

58~93

PAGE

CIB CIRCUIT DIAGRAM 003

005

006

008

009

012

EDB CIRCUIT DIAGRAM 002

004

005

011

EMB CIRCUIT DIAGRAM 002

003

005

007

009

010

011

GDB CIRCUIT DIAGRAM 002

004

006

007

008

012

016

IDB CIRCUIT DIAGRAM 004

005

4

6

7

9

10

13

14

16

17

23

25

26

28

30

32

33

34

35

37

39

40

41

45

49

53

54

IDB CIRCUIT DIAGRAM 017

018

IFC1 CIRCUIT DIAGRAM 005

006

007

008

JK1 CIRCUIT DIAGRAM 002

003

004

JK2 CIRCUIT DIAGRAM 002

003

004

JK3 CIRCUIT DIAGRAM 002

003

005

JK4 CIRCUIT DIAGRAM 004

JK5 CIRCUIT DIAGRAM 2/2

JK6 CIRCUIT DIAGRAM 1/2

2/2

PDB CIRCUIT DIAGRAM 002

004

010

016

017

018

66

67

72

73

74

75

76

77

78

79

80

81

82

84

85

88

90

91

92

97

99

105

111

112

113

2-1

Page 3

DSP1D

IMPORTANT NOTICE

This manual has been provided for the use of authorized Yamaha Retailers and their service personnel. It has been assumed that

basic service procedures inherent to the industry, and more specifically Yamaha Products, are already known and understood by

the users, and have therefore not been restated.

WARNING: Failure to follow appropriate service and safety procedures when servicing this product may result in personal

injury, destruction of expensive components and failure of the product to perform as specified. For these

reasons, we advise all Yamaha product owners that all service required should be performed by an authorized

Yamaha Retailer or the appointed service representative.

IMPORTANT: This presentation or sale of this manual to any individual or firm does not constitute authorization, certification,

recognition of any applicable technical capabilities, or establish a principal-agent relationship of any form.

The data provided is belived to be accurate and applicable to the unit(s) indicated on the cover. The research engineering, and

service departments of Yamaha are continually striving to improve Yamaha products. Modifications are, therefore, inevitable and

changes in specification are subject to change without notice or obligation to retrofit. Should any discrepancy appear to exist,

please contact the distributor's Service Division.

WARNING: Static discharges can destroy expensive components. Discharge any static electricity your body may have

accumulated by grounding yourself to the ground bus in the unit (heavy gauge black wires connect to this bus).

IMPORTANT: Turn the unit OFF during disassembly and parts replacement. Recheck all work before you apply power to the

unit.

LITHIUM BATTERY HANDLING

This product uses a lithium battery for memory back-up.

WARNING: Lithium batteries are dangerous because they can be exploded by improper handling. Observe the following

precautions when handling or replacing lithium batteries.

Leave lithium battery replacement to qualified service personnel.

Always replace with batteries of the same type.

When installing on the PC board by soldering, solder using the connection terminals provided on the battery cells.

Never solder directly to the cells. Perform the soldering as quickly as possible.

Never reverse the battery polarities when installing.

Do not short the batteries.

Do not attempt to recharge these batteries.

Do not disassemble the batteries.

Never heat batteries or throw them into fire.

ADVARSEL!

Lithiumbatteri-Eksplosionsfare ved fejlagtig håndtering. Udskiftning må kun ske med batteri af samme fabrikat og type. Levér det

brugte batteri tilbage til leverandøren.

VARNING

Explosionsfara vid felaktigt batteribyte.

Använd samma batterityp eller en ekvivalent typ som rekommenderas av apparattillverkaren.

Kassera använt batteri enligt fabrikantens instruktion.

VAROITUS

Paristo voi räjähtää, jos se on virheellisesti asennettu.

Vaihda paristo ainoastaan laitevalmistajan suosittelemaan tyyppiin.

Hävitä käytetty paristo valmistajan ohjeiden mukaisesti.

The following information complies with Dutch Official Gazette 1995. 45; ESSENTIALS OF ORDER ON THE COLLECTION OF

BATTERIES.

• Please refer to the diassembly procedure for the removal of Back-up Battery.

• Leest u voor het verwijderen van de backup batterij deze beschrijving.

WARNING: CHEMICAL CONTENT NOTICE!

The solder used in the production of this product contains LEAD. In addition, other electrical/electronic and/or plastic (where

applicable) components may also contain traces of chemicals found by the California Health and Welfare Agency (and possibly

other entities) to cause cancer and/or birth defects or other reproductive harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON

WHAT SO EVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or expose eyes

to solder/flux vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before handling

food.

WARNING

Components having special characteristics are marked and must be replaced with parts having specification equal to those

originally installed.

2-2

Page 4

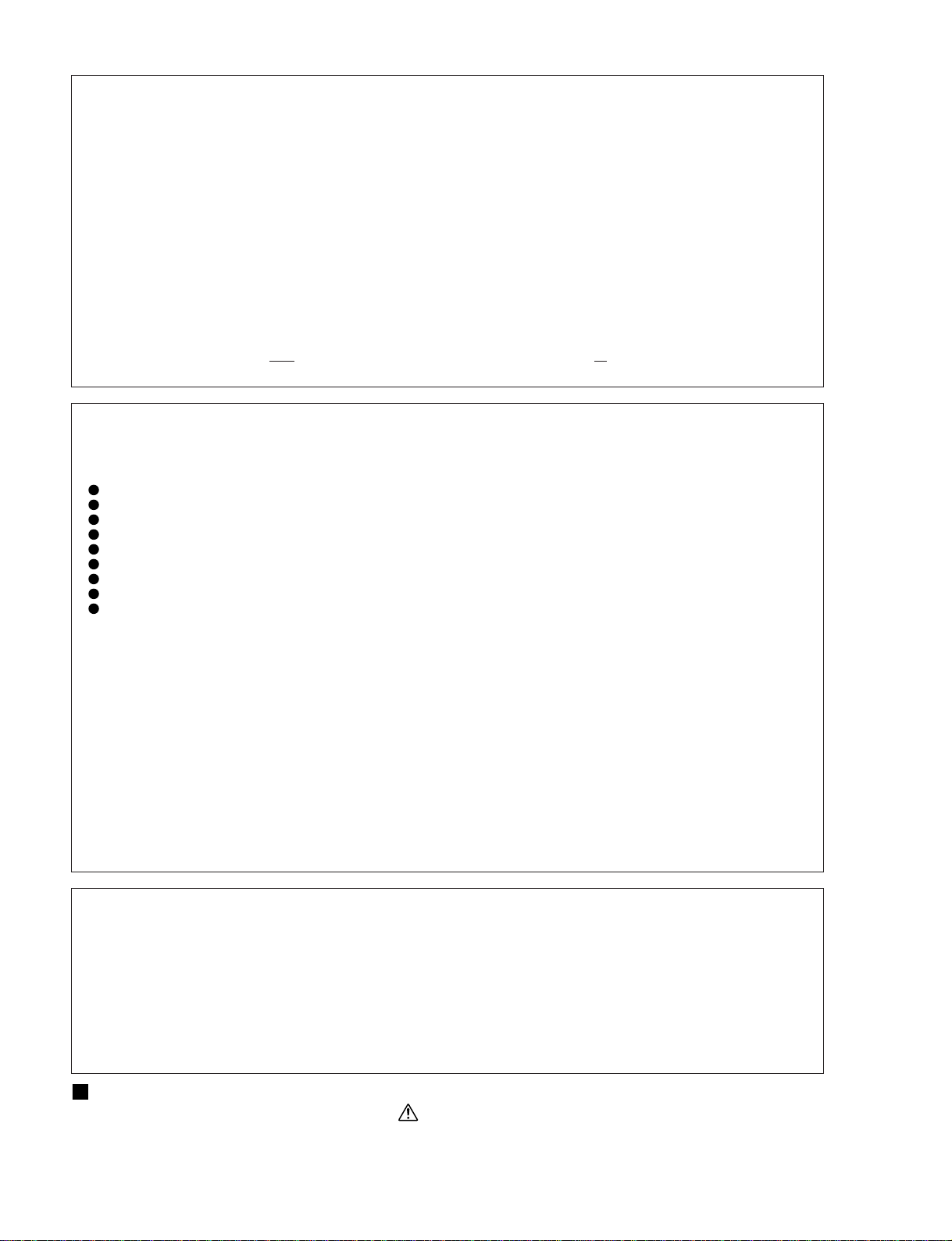

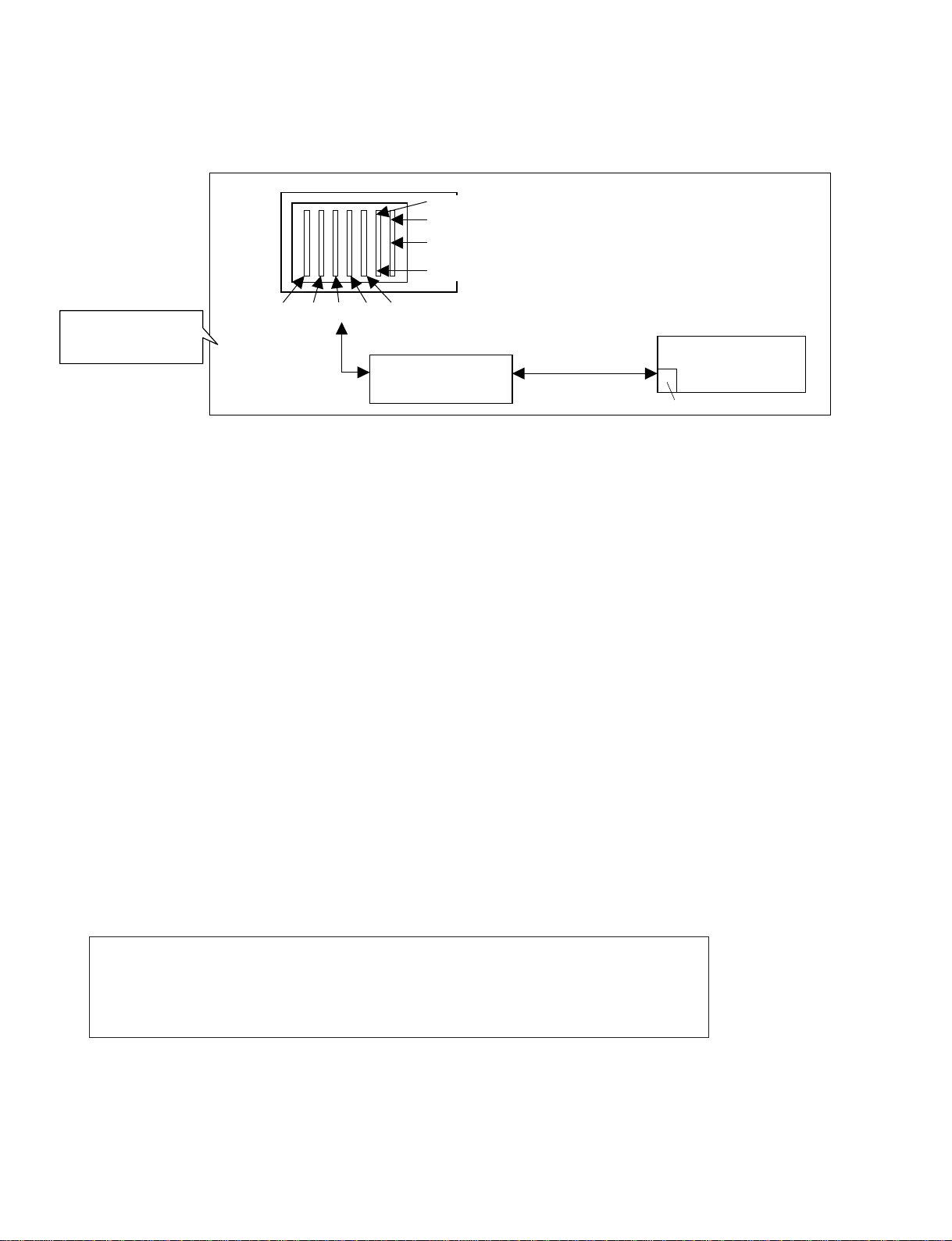

SPECIFICATIONS

DSP1D

Sampling frequency

Power supply

Power consumption

Dimensions (W x H x D)

Weight

Operating temperature

Fan circuit

Accessories

Digital I/Os

I/O connectors

DIGITAL I/O INPUT 1 –10

DIGITAL I/O OUTPUT 1 – 6

DIGITAL I/O CASCADE IN, OUT

DIGITAL I/O CONSOLE I/O 1, 2

CONTROL I/O CONSOLE 1 IN, OUT

CONTROL I/O CONSOLE 2 IN, OUT

REMOTE RS-422

GPI

TIME CODE IN

MIDI IN, OUT, THRU

PC CONTROL RS-232-C

PC CONTROL USB

WORD CLOCK IN

WORD CLOCK OUT

<External sync> 39.69 kHz – 50.88 kHz

<Internal sync> 44.1 kHz, 48 kHz

USA and Canada: 120 V, 60 Hz

Others: 230 V, 50 Hz

170 W

480 mm x 408.7 mm x 460.8 mm

33 kg

10 – 35˚C

always fixed

power cable 2.5 m x 1

Level

RS-422

RS-422

RS-422

RS-422

–0.225V — –1.825V/50 Ω

–0.225V — –1.825V/50 Ω

RS-422

C-MOS IN, Open collector OUT

1 pin: 150mA, 8pin total: 500mA

SMPTE format, Nominal –10 dB/10 kΩ

MIDI format

RS-232-C

0V — 3.3V

TTL/75 Ω (ON/OFF)

TTL/75 Ω

Type

D-sub, half-pitch, 68-pin connector (female) x 10

D-sub, half-pitch, 68-pin connector (female) x 6

D-sub, half-pitch, 68-pin connector (female) x 2

D-sub, half-pitch, 68-pin connector (female) x 2

BNC connector x 2

BNC connector x 2

D-sub, 9-pin connector (female)

D-sub, 25-pin connector (female)

XLR-3-31 type connector

5-pin DIN connector x 3

D-sub, 9-pin connector (male)

B type USB connector

BNC connector

BNC connector

Slots (for IDB1D board)

Unit

DPS1D

DPS1D-EX

* The DSP1D has an empty slot available for the IDB1D board.

INPUT 1-48 & ST IN 1-4 *

INPUT 1-96 & ST IN 1-8 (DSP1D + IDB1D for expansion)

Input channel

IMPORTANT NOTICE FOR THE UNITED KINGDOM

Connecting the Plug and Cord

IMPORTANT. The wires in this main lead are coloured in

accordance with the following code:

BLUE: NEUTRAL

BROWN: LIVE

As the colours of the wires in the main lead of this apparatus may not

correspond with the coloured markings identifying the terminals in

your plug, proceed as follows:

The BLUE wire must be connected to the terminal that is marked with

the letter N (or coloured BLACK).

The BROWN wire must be connected to the terminal that is marked

with the letter L (or coloured RED).

Be certain that neither core is connected to the earth terminal of the

three pin plug.

3-1

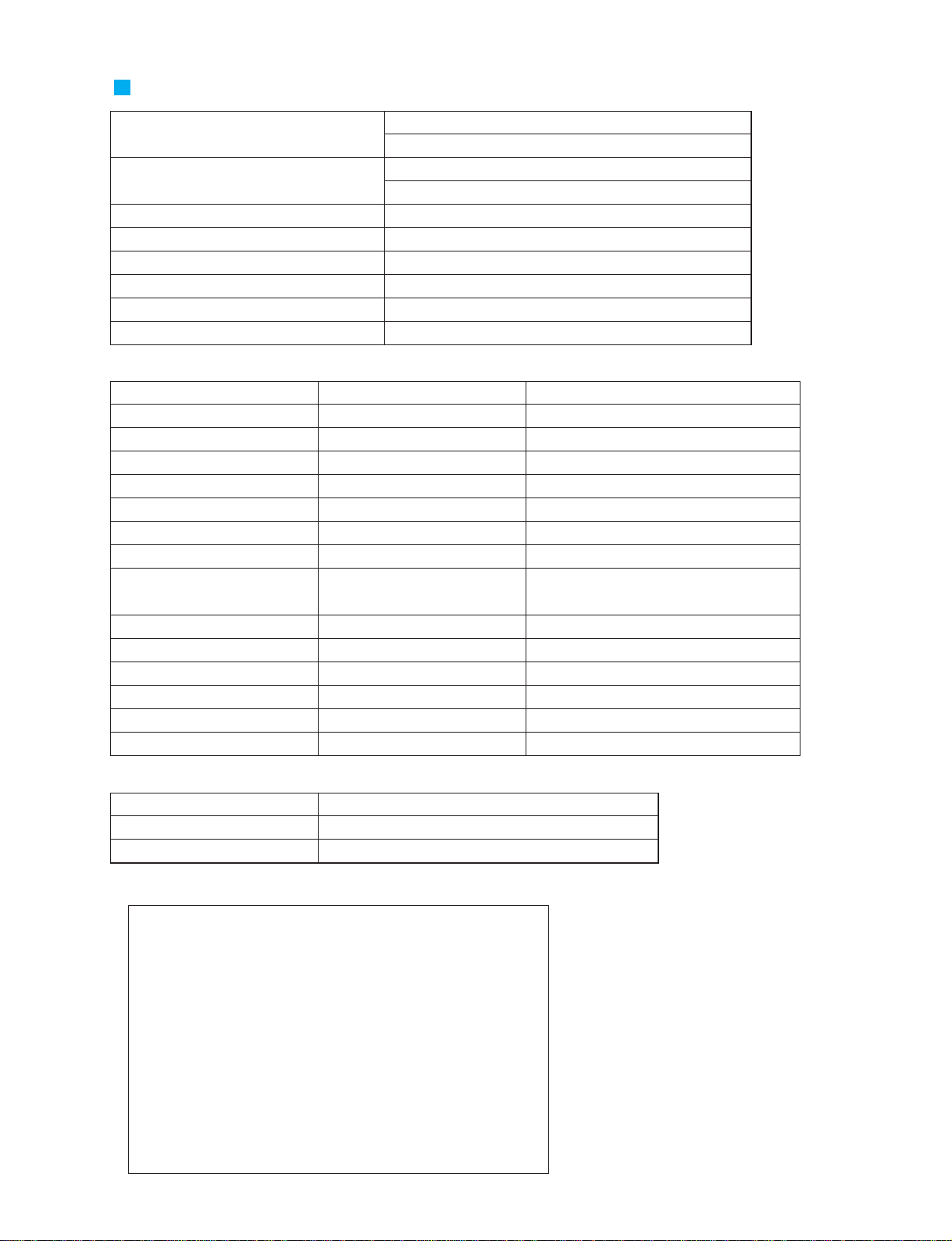

Page 5

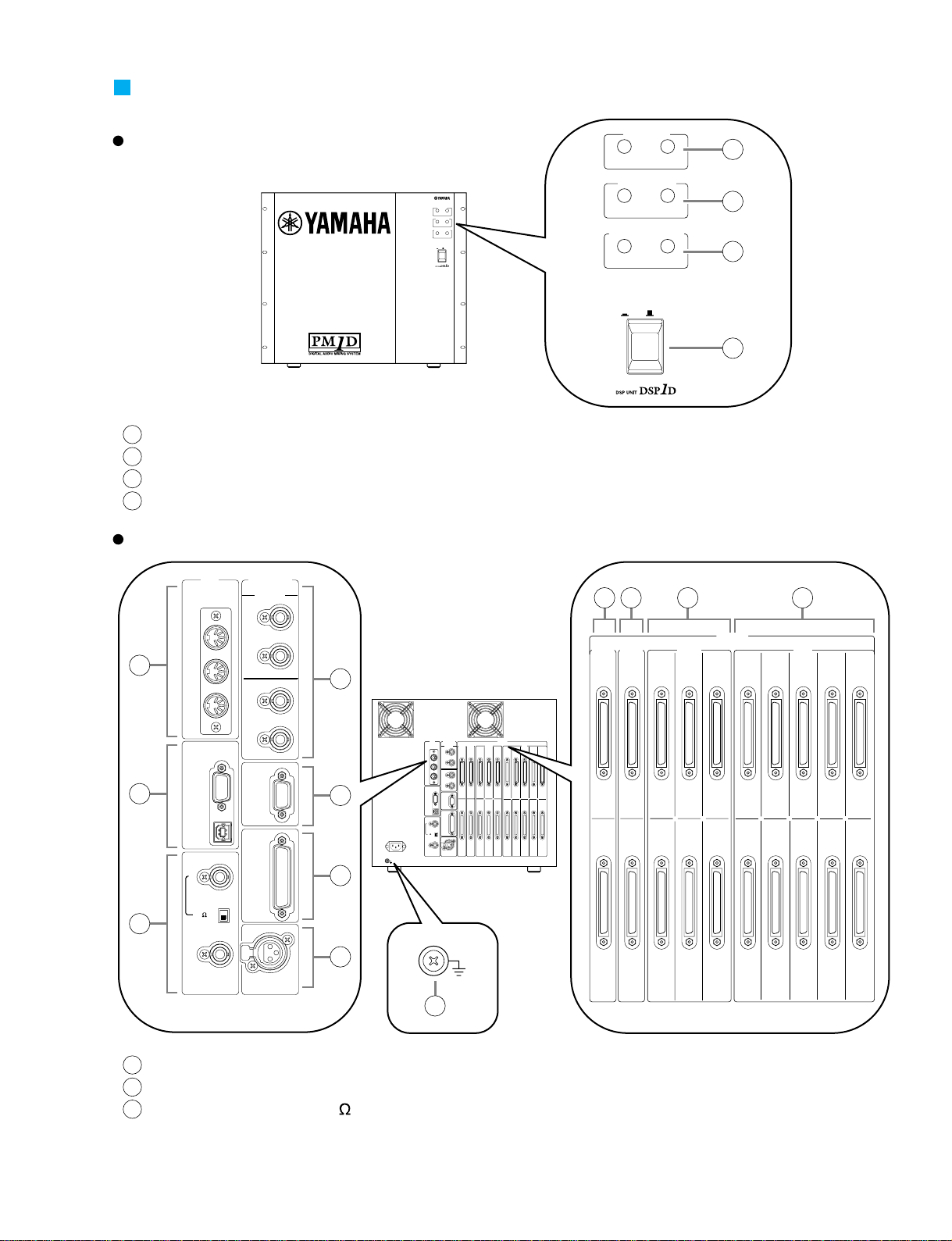

POWER

ON/ OFF

A B

ENGINE ID

1 2

CONTROL I/O

48CH 96CH

INPUT

CONFIGURATION

POWER

ON/ OFF

A B

ENGINE ID

1 2

CONTROL I/O

48CH 96CH

INPUT

CONFIGURATION

22

22

IN

OUT

IN

2

OUT

IN

1

1IN531 97531

2 OUT 6 4 2 10 8 6 4 2

OUT

THRU

PC

CONTROL

WORD CLOCK

TIME CODE IN

GPI

RS-422

REMOTE

IN

OUT

OFF

ON

RS-232-C

USB

75

MIDI

OUTPUT INPUT

CONTROL I/O

CONSOLE

CONSOLE

I/O

CASCADE

DIGITAL I/O

1 IN531 975 31

2 OUT 6 4 2 10 8 6 4 2

OUTPUT INPUT

CONSOLE

I/O

CASCADE

DIGITAL I/O

22

22

IN

OUT

IN

2

OUT

IN

1

OUT

THRU

PC

CONTROL

WORD CLOCK

TIME CODE IN

GPI

RS-422

REMOTE

IN

OUT

OFF

ON

RS-232-C

USB

75

MIDI CONTROL I/O

CONSOLE

1

2

3

4

5

6

7

8

9

10

11

16

12 13 14 15

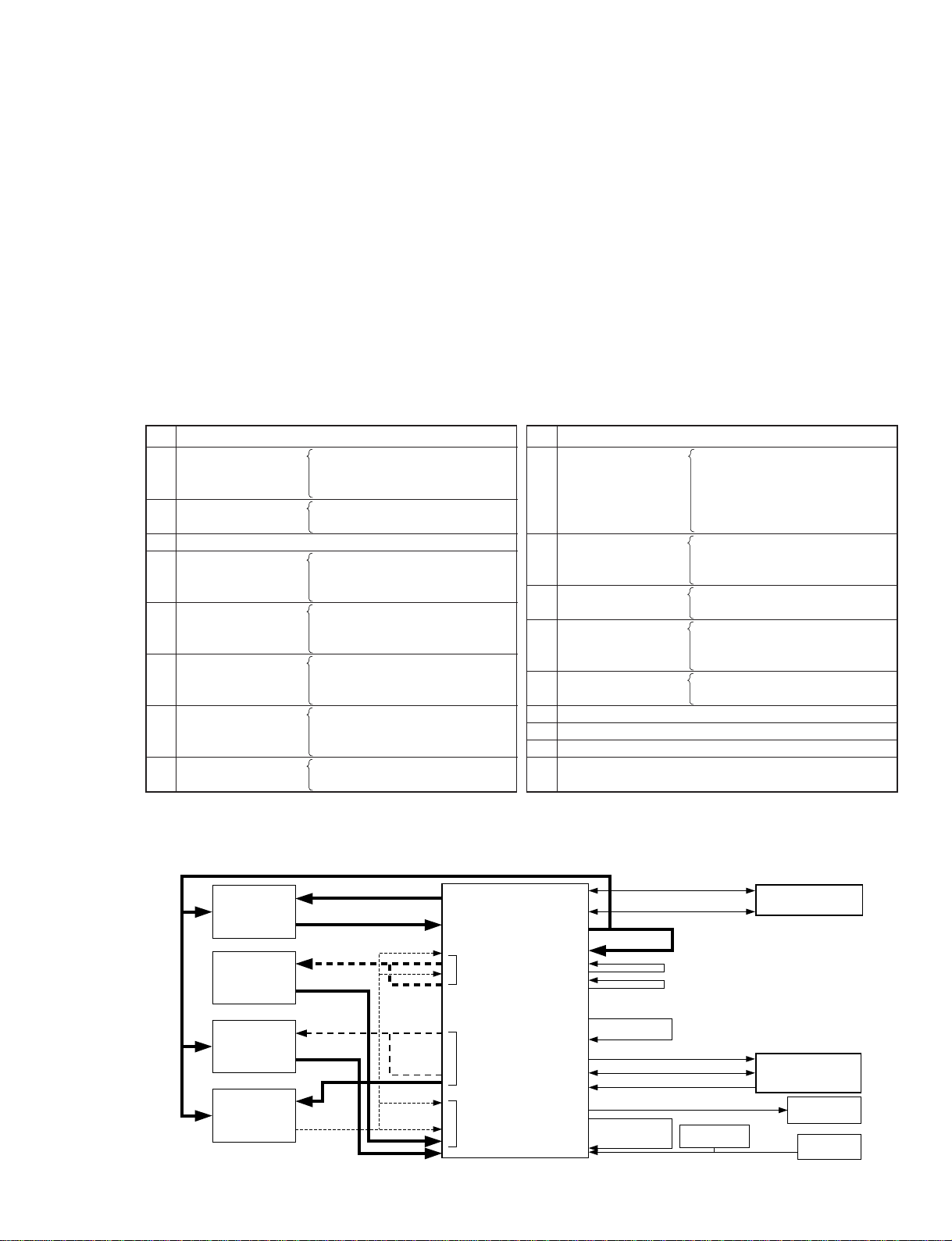

1

ENGINE ID A/B indicators

2

CONTROL I/O 1/2 indicators

3

INPUT CONFIGURATION 48CH/96CH indicators

4

POWER ON/OFF switch

5

MIDI IN/OUT/THRU connectors

6

PC CONTROL RS-232-C/USB ports

7

WORD CLOCK IN jack, 75 ON/OFF

switch, and WORD CLOCK OUT jack

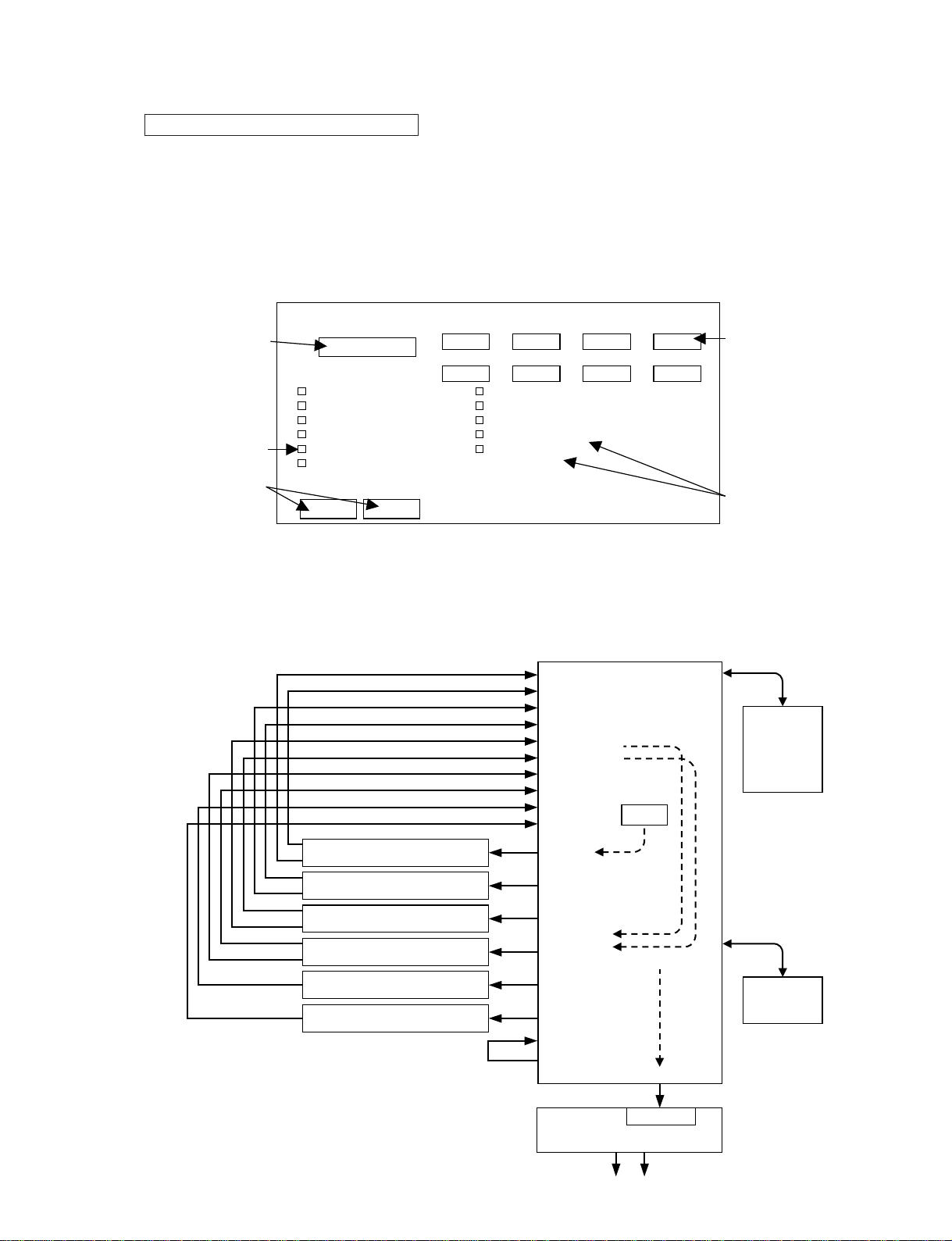

PANEL LAYOUT

Front Panel

Rear Panel

DSP1D

3-2

Page 6

8

CONSOLE 1, 2 IN/OUT jacks

9

REMOTE RS-422 connector

10

GPI connector

11

TIME CODE IN connector

12

CONSOLE I/O 1, 2 slots

13

CASCADE IN, OUT slots

14

OUTPUT 1–6 slot

15

INPUT 1–10 slot

16

Ground connector

DSP1D

3-3

Page 7

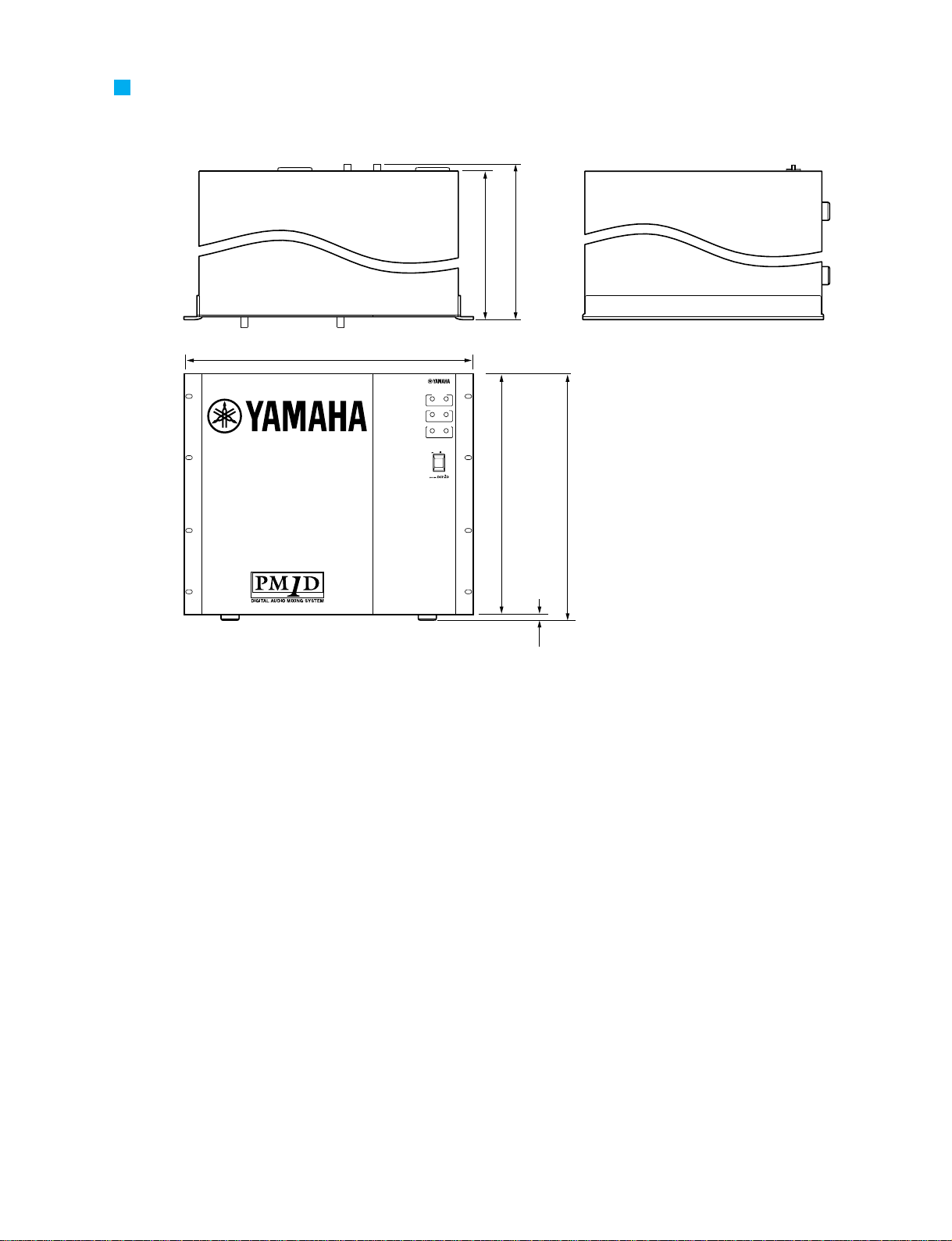

DIMENSIONS

POWER

ON/ OFF

A B

ENGINE ID

1 2

CONTROL I/O

48CH 96CH

INPUT

CONFIGURATION

460.8

450

480

399.2

408.7

9.5

DSP1D

Unit: mm

3-4

Page 8

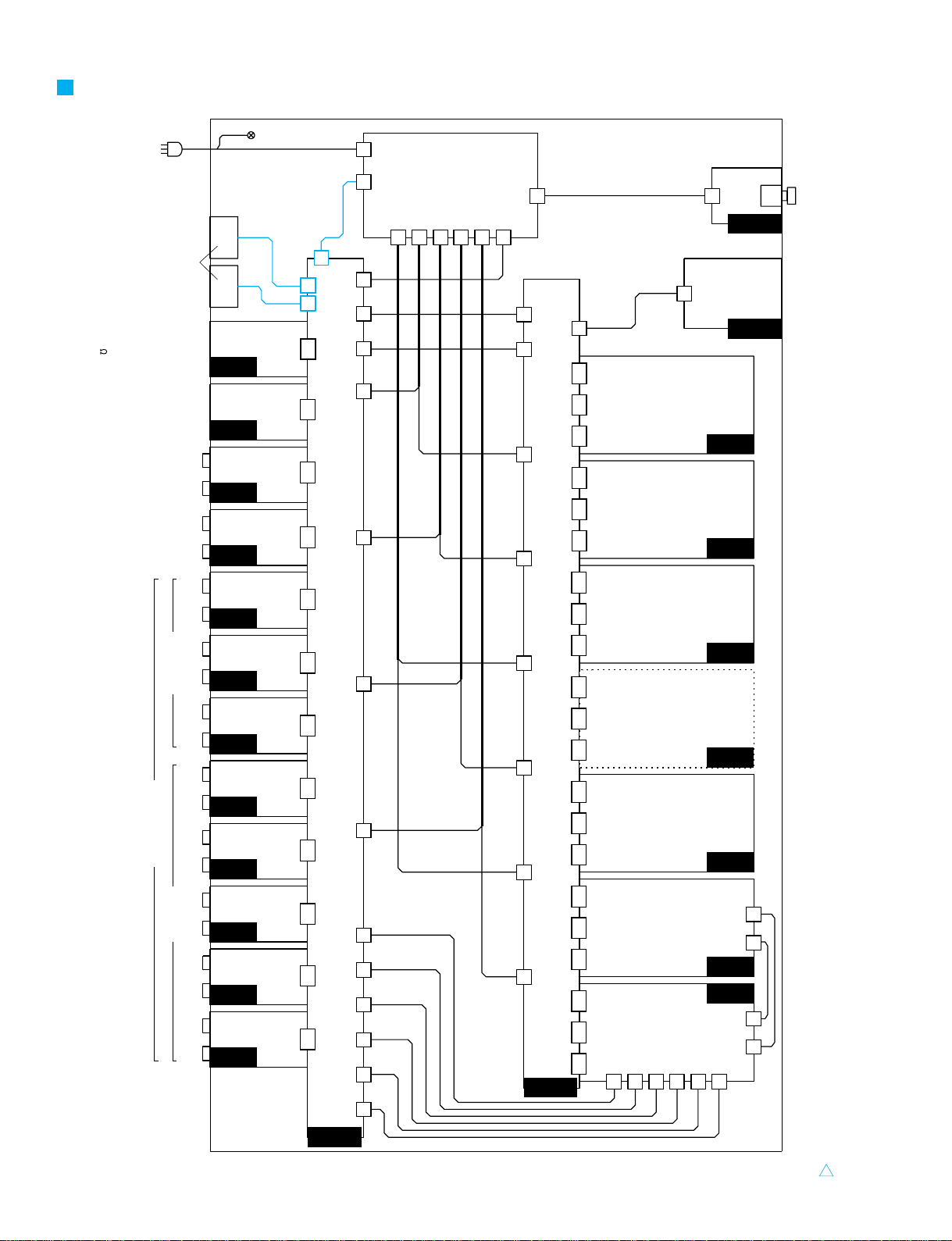

[1][2][3][5][6][7] [4][8][9][10][1][2][3][4][5][6][IN][OUT][1][2]

[INPUT][OUTPUT][CASCADE]

[CONSOLE I/O]

[CONTROL I/O]

[CONSOLE]

[1]

[2]

[REMOTE]

[GPI]

[TIME CODE IN]

[DIGITAL I/O]

[POWER]

[ON/OFF]

FOR DSP1D-EX

[IN]

[OUT]

[IN]

[OUT]

[RS-422]

[MIDI]

[PC CONTROL]

[WORD CLOCK]

[IN]

[OUT]

[THRU]

[RS-232-C]

[USB]

[IN][

75

]

[OUT]

[ON]

[OFF]

[CONTROL I/O]

[ENGINE ID]

[INPUT CONFIGURATION]

[A] [B]

[1] [2]

[48CH] [96CH]

POWER UNIT

FAN

8P

CN200

3P

CN1

CN809

3P

CN300

2P

CN8

10P

CN101

50P

CN802

50P

CN801

4P

CN604

4P

CN504

4P

CN404

4P

CN304

4P

CN204

4P

CN104

CIB

EMB

EDB

IDB

IDB

GDB

PDB

JK1

JK1

JK1

JK1

JK1

JK2

JK2

JK2

JK3

JK4

JK5

JK6

LED2

PSB2

MB11

IFC1

**

************

**

6P

CN9

8P

CN7

8P

CN6

8P

CN5

8P

CN4

9P

CN3

4P

CN10

8P

CN803

CN103

96P

CN703

CN102

96P

CN702

CN101

96P

CN701

CN103

96P

CN603

CN102

96P

CN602

CN101

96P

CN601

CN652

96P

CN503

CN651

96P

CN502

CN650

96P

CN501

CN3

96P

CN403

CN2

96P

CN402

CN1

96P

CN401

CN3

96P

CN303

CN2

96P

CN302

CN1

96P

CN301

CN904

96P

CN203

CN903

96P

CN202

CN902

96P

CN201

CN902

96P

CN103

CN901

96P

CN102

CN101

96P

CN102

CN102

96P

CN102

CN103

96P

CN102

CN104

96P

CN102

CN201

96P

CN102

CN202

96P

CN102

CN203

96P

CN102

CN301

96P

CN102

CN302

96P

CN102

CN303

96P

CN100

CN811

3P

CN810

96P

CN100

CN900

96P

CN101

CN100

96P

CN102

2P

FG

50P

CN901

50P

CN900

50P

CN950

14P

CN808

30P

CN801

30P

CN802

50P

CN807

50P

CN806

4P

CN105

4P

CN305

4P

CN505

4P

CN605

50P

CN804

50P

CN803

3P

CN405

50P

CN805

50P

CN952

50P

CN955

50P

CN954

50P

CN956

30P

CN951

30P

CN953

14P

CN957

KEC-92539-2

1

DSP1D

CONNECTOR CIRCUIT DIAGRAM

4

Page 9

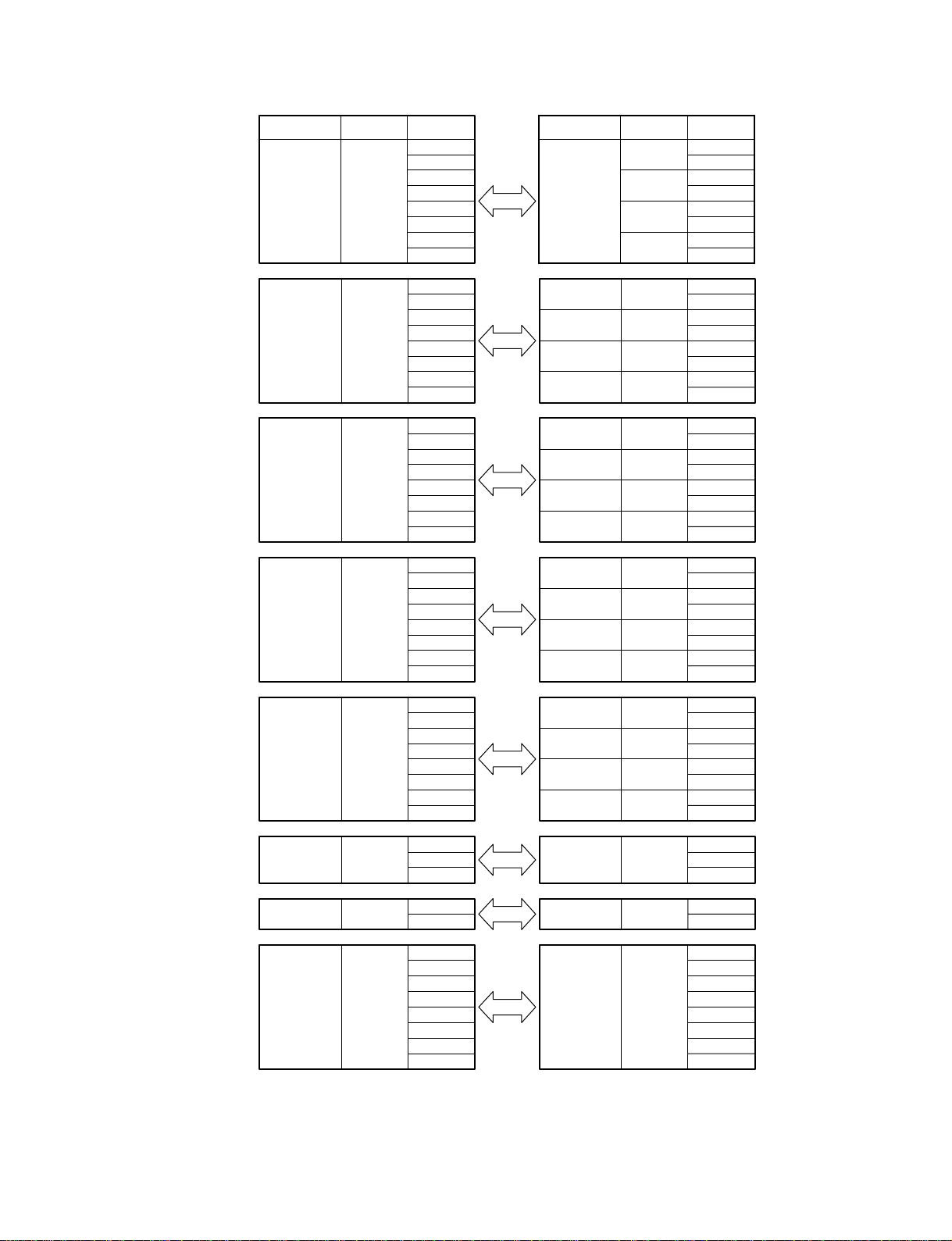

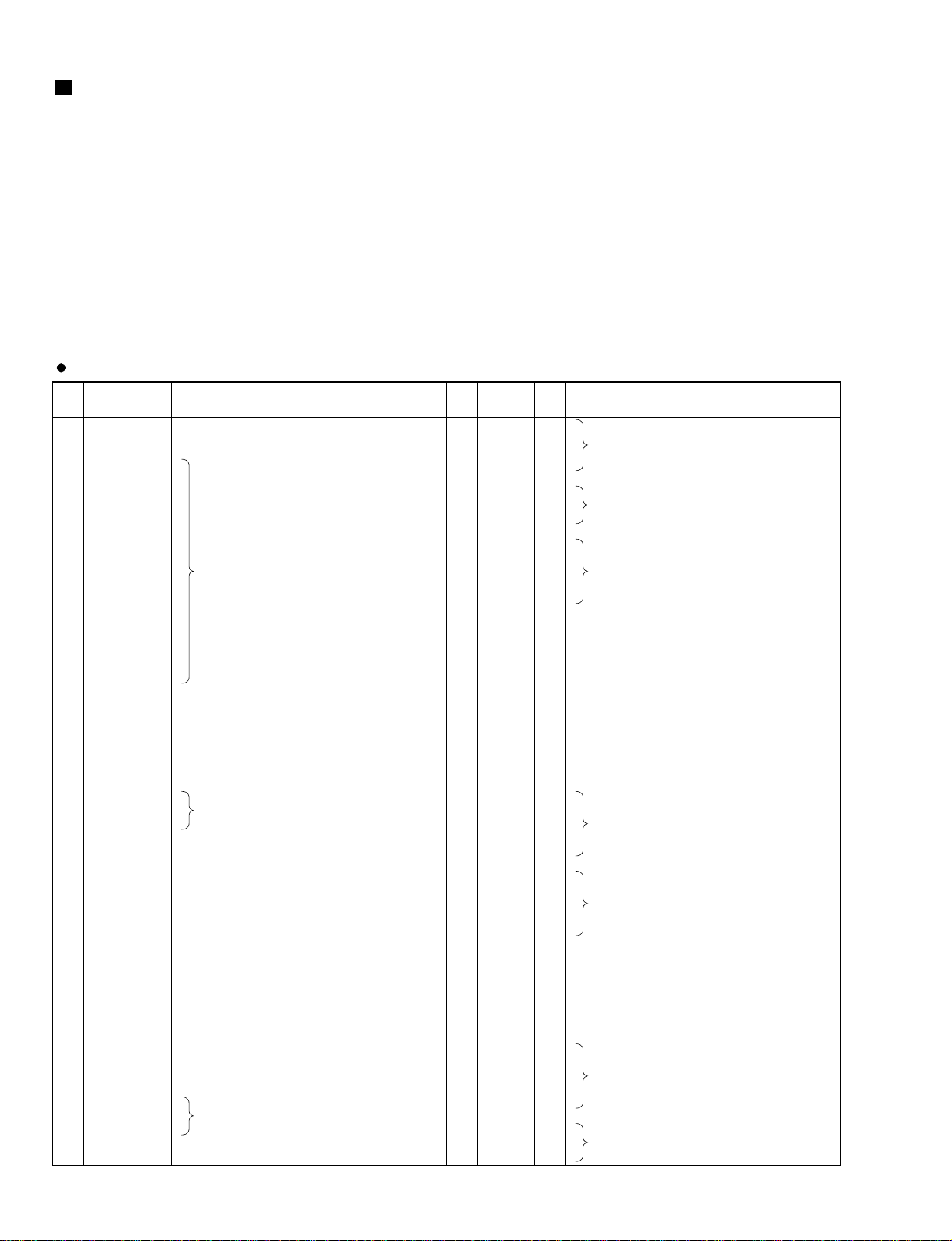

Circuit Board CN No. Pin No.

POWER UNIT

CN3

2

3

4

6

7

8

9

1 MB11 1

2

1

2

4

5

4

5

CN204

CN404

CN204

CN404

Circuit Board CN No. Pin No.

POWER UNIT

CN10 1

4

PSB2 CN200 1

3

POWER UNIT

CN4 1

3

2

4

5

6

7

8

MB11 CN604

IFC1 CN605

MB11 CN604

IFC1 CN605

1

2

1

2

3

4

3

4

POWER UNIT

CN5 1

3

2

4

5

6

7

8

MB11 CN504

IFC1 CN505

MB11 CN504

IFC1 CN505

1

2

1

2

3

4

3

4

POWER UNIT

CN6 1

3

2

4

5

6

7

8

MB11 CN304

IFC1 CN305

MB11 CN304

IFC1 CN305

1

2

1

2

3

4

3

4

POWER UNIT

CN7 1

3

2

4

5

6

7

8

MB11 CN104

IFC1 CN105

MB11 CN104

IFC1 CN105

1

2

1

2

3

4

3

4

LED2 CN101 1

3

2

4

5

6

7

8

MB11 CN803 1

2

3

4

5

6

7

8

POWER UNIT

CN9 1

6

5

IFC1 CN405 1

2

3

KEC-92539-3

DSP1D

5

Page 10

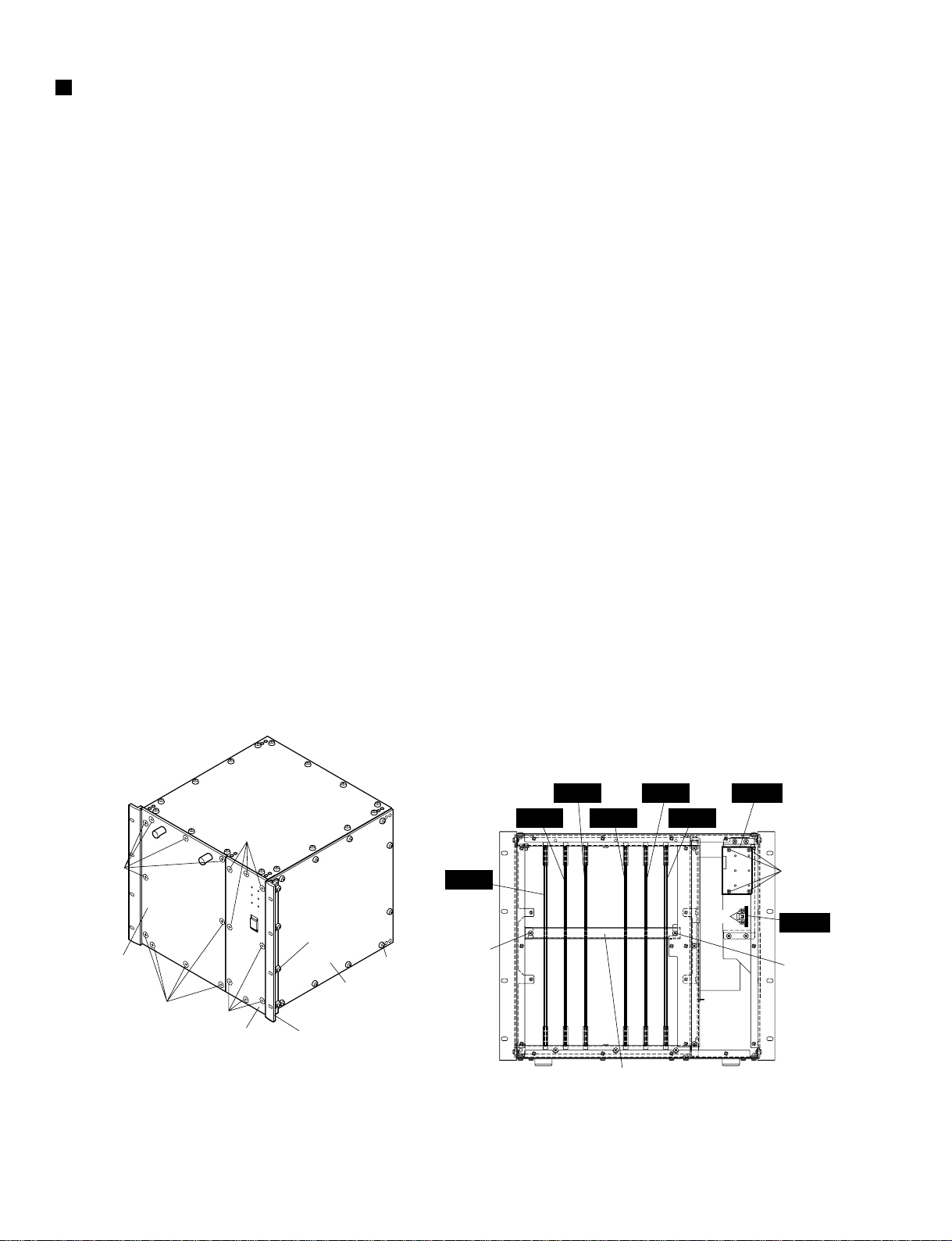

Fig. 1 Fig. 2

[750]

[750]

[960]B x 8

[940] x 10

[905]

[905]

Front cover

Front panel

Side panel-R

Reinforcement angle-A

Right frame

[750]: Oval Head Screw 3.0x6 MFZN2BL (VS153600)

[905]: Oval Head Screw 3.0x6 MFZN2BL (VS153600)

[940]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

[960B]: Oval Head Screw 3.0x6 MFZN2BL (VS153600)

[325]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230)

[330]: Bind Head Screw 3.0x8 MFZN2BL (VB659000)

[850]: Bind Head Screw A4.0x8 MFZN2BL (VP156800)

<Front View>

PDB

GDB

IDB

EDB

EMB

CIB

LED2

PSB2

[325]

[850]

[850]

[330]

DSP1D

6

DISASSEMBLY PROCEDURE

1. GDB, IDB, EDB, EMB and CIB Circuit Boards

1-1 Remove the ten (10) screws marked [905]. The front

cover can then be removed. (Fig. 1)

1-2 Remove the two (2) screws marked [850]. The

reinforcement angle-A can then be removed. (Fig. 2)

1-3 Remove the GDB, IDB, EDB, EMB and CIB circuit

boards by sliding forward. (Fig. 2)

2. PDB Circuit Board

2-1 Remove the front cover. (See procedure 1-1.)

2-2 Remove the reinforcement angle. (See procedure 1-2.)

2-3 Remove the eight (8) screws marked [960A]. The left

frame can then be removed. (Fig. 3)

2-4 Remove the twelve (12) screws marked [920]. The side

panel-L can then be removed. (Fig. 3)

2-5 Remove the PDB circuit board by sliding forward. (Fig. 2)

3. LED2 and PSB2 Circuit Boards

3-1 Remove the eight (8) screws marked [960B]. The right

frame can then be removed. (Fig. 1)

3-2 Remove the eight (8) screws marked [750]. The front

panel can then be removed. (Fig. 1)

3-3 Remove the four (4) screws marked [325]. The LED2

circuit board can then be removed. (Fig. 2)

3-4 Remove the two (2) screws marked [330]. The PSB2

circuit board can then be removed. (Fig. 2)

Page 11

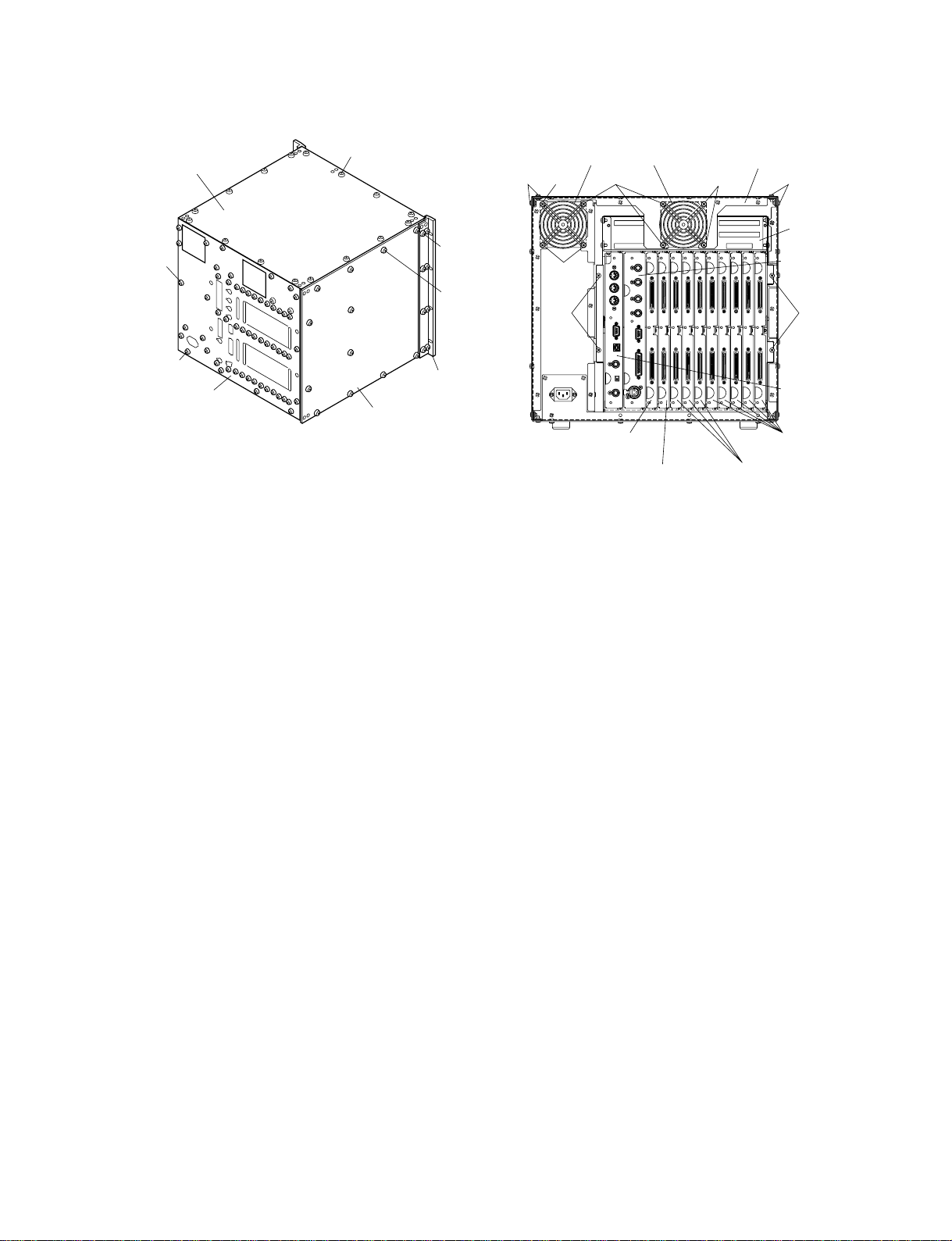

Fig. 3 Fig. 4

[870]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

[920]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

[960A]: Oval Head Screw 3.0x6 MFZN2BL (VS153600)

[980]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

[985]: Bind Head Screw A4.0x8 MFZN2BL (VP156800)

[480]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

[540]: Bind Head Tapping Screw-B A4.0x8 MFZN2BL (VC688800)

[590]: Bind Head Screw 4.0x35 MFZN2BL (VG605800)

Top cover

Rear panel

[870] x 16

[960A] x 8

[920] x 12

[540] [590]

[590]

[480]

[980] x 58

[985]

Side panel-L

Fan motor RR-TOP frame

JK box assembly

JK1 C.B. assembly

JK5 C.B. assembly

Left frame

<Rear View>

[540][590] [590]

[480]

JK4 C.B. assembly

JK2 C.B. assemblyJK3 C.B. assembly

JK6 C.B. assembly

4. Fan Motor

4-1 Remove the six-teen (16) screws marked [870]. The top

cover can then be removed. (Fig. 3)

4-2 Remove the four (4) screws each marked [590]. The fan

motor A or B can then be removed. (Fig. 4)

5. Power Supply Unit

5-1 Remove the top cover. (See procedure 4-1.)

5-2 Remove the right frame. (See procedure 3-1.)

5-3 Remove the ten (10) screws marked [940]. The side panel-

R can then be removed. (Fig. 1)

5-4 Remove the fifty-eight (58) screws marked [980] and the screw

marked [985]. The rear panel can then be removed. (Fig. 3)

5-5 Remove the eight (8) screws marked [540]. The RR-TOP

frame can then be removed. (Fig. 4)

5-6 Remove the fan motor B. (See procedure 4.)

5-7 Remove the three (3) screws marked [560]. The power

supply unit can then be removed by lifting up. (Fig. 5)

6. JK1-JK6 Circuit Board Assemblies

6-1 Remove the rear panel. (See procedure 5-4.)

6-2 Remove the JK1-JK6 circuit board assemblies by sliding

forward. (Fig. 4)

DSP1D

7

Page 12

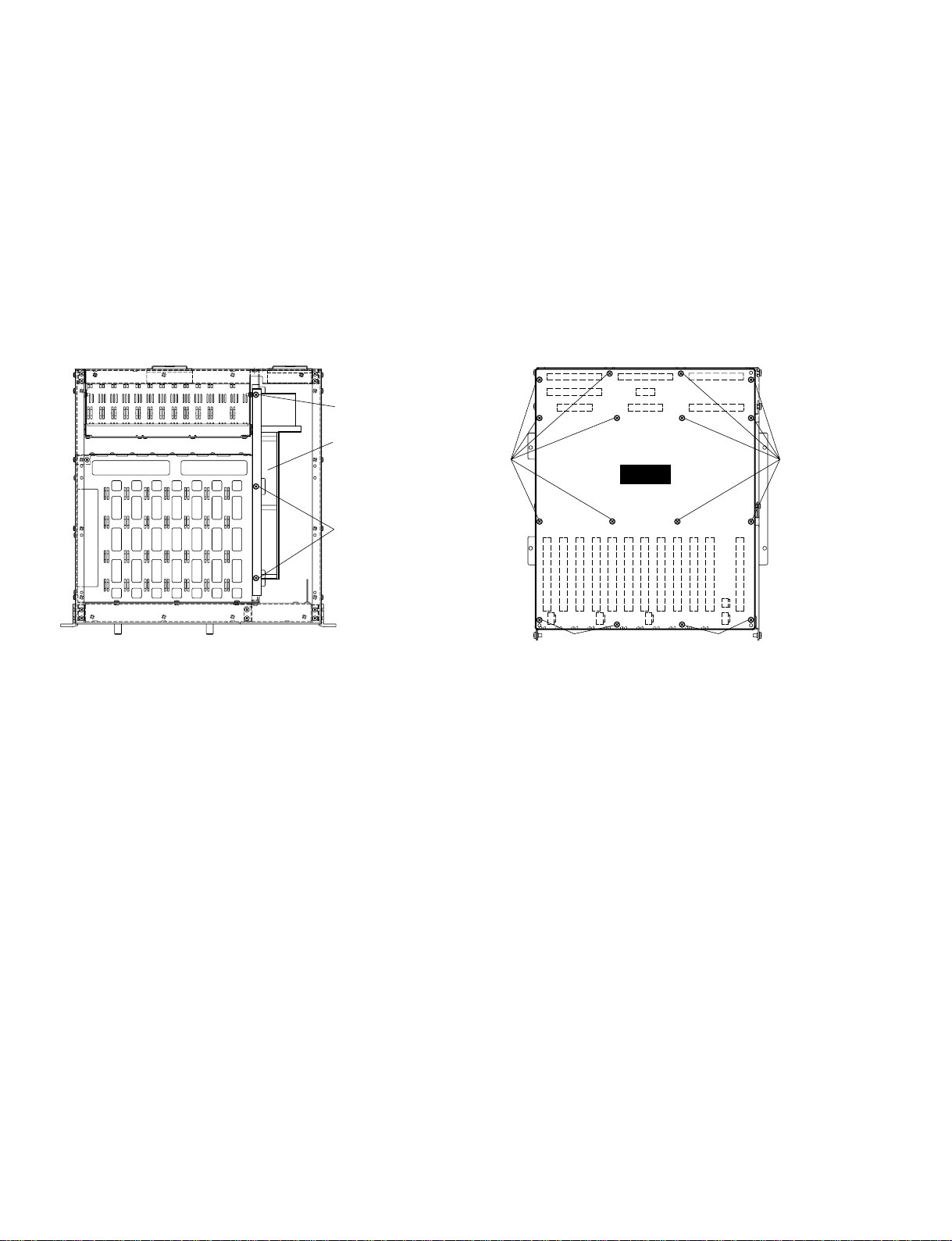

Fig. 5 Fig. 6

[560]: Bind Head Tapping Screw-B A4.0x12 MFZN2BL (VD831800) [110]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230)

<Top View> • JK Box Assembly

[560]

[110]

[110]

[560]

Power supply unit

[110]

[110]

IFC1

DSP1D

8

7. IFC Circuit Board

7-1 Remove the top cover. (See procedure 4-1.)

7-2 Remove the left frame and the side panel-L. (See procedure

2-2, 2-3.)

7-3 Remove the rear panel. (See procedure 5-4.)

7-4 Remove the RR-TOP frame. (See procedure 5-5.)

7-5 Remove the four (4) screws marked [480]. The JK box

assembly can then be removed. (Fig. 4)

7-6 Remove the six-teen (16) screws marked [110]. The IFC1

circuit board can then be removed. (Fig. 6)

8. MB11 Circuit Board

8-1 Remove the top cover. (See procedure 4-1.)

8-2 Remove the left frame and the side panel-L. (See procedure

2-2, 2-3.)

8-3 Remove the rear panel. (See procedure 5-4.)

8-4 Remove the RR-TOP frame. (See procedure 5-5.)

8-5 Remove the JK box assembly. (See procedure 7-5.)

8-6 Remove the eight-teen (18) screws marked [430] and the

two (2) screws marked [450]. The MB11 circuit board can

then be removed with the reinforcement angle-B. (Fig. 7)

8-7 Remove the six (6) screws marked [420]. The

reinforcement angle-B can then be removed from the

MB11 circuit board. (Fig. 8)

Page 13

Fig. 7 Fig. 8

[430]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230)

[450]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230) [420]: Bind Head Tapping Screw-B 3.0x6 MFZN2BL (EP600230)

<Rear View>

[450]

[430]

[430]

Reinforcement

angle-B

Reinforcement angle-B

[450]

[430]

[420]

MB11

MB11

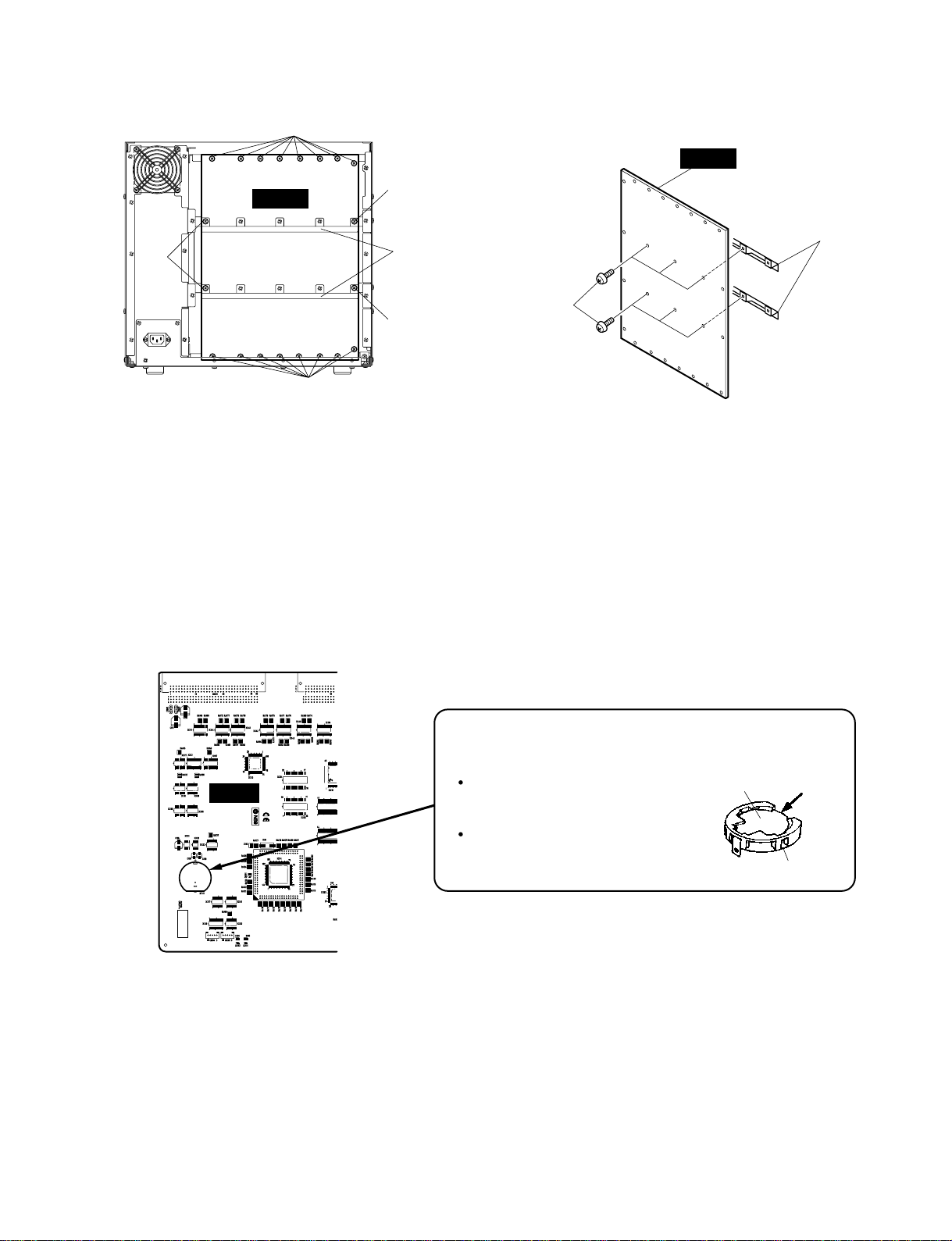

Fig. 9

Battery VN103500

VN103600(Battery holder for VN103500)

Notice for back-up battery removal

Push the battery as shown in figure,

then the battery will pop up.

Druk de batterij naar beneden zoals

aangeven in de tekening, de batterij

springt dan naar voren.

Battery

Battery holder

EMB

DSP1D

9

9. Replacement of the Lithium Battery

9-1 Remove the EMB circuit board. (See procedure 1.)

9-2 The lithium battery can be replacement on the EMB

circuit board. (Fig. 9)

* The lithium battery is not a part of the EMB circuit board.

When you replace the EMB circuit board, remove the

lithium battery and install it in the new circuit board.

Page 14

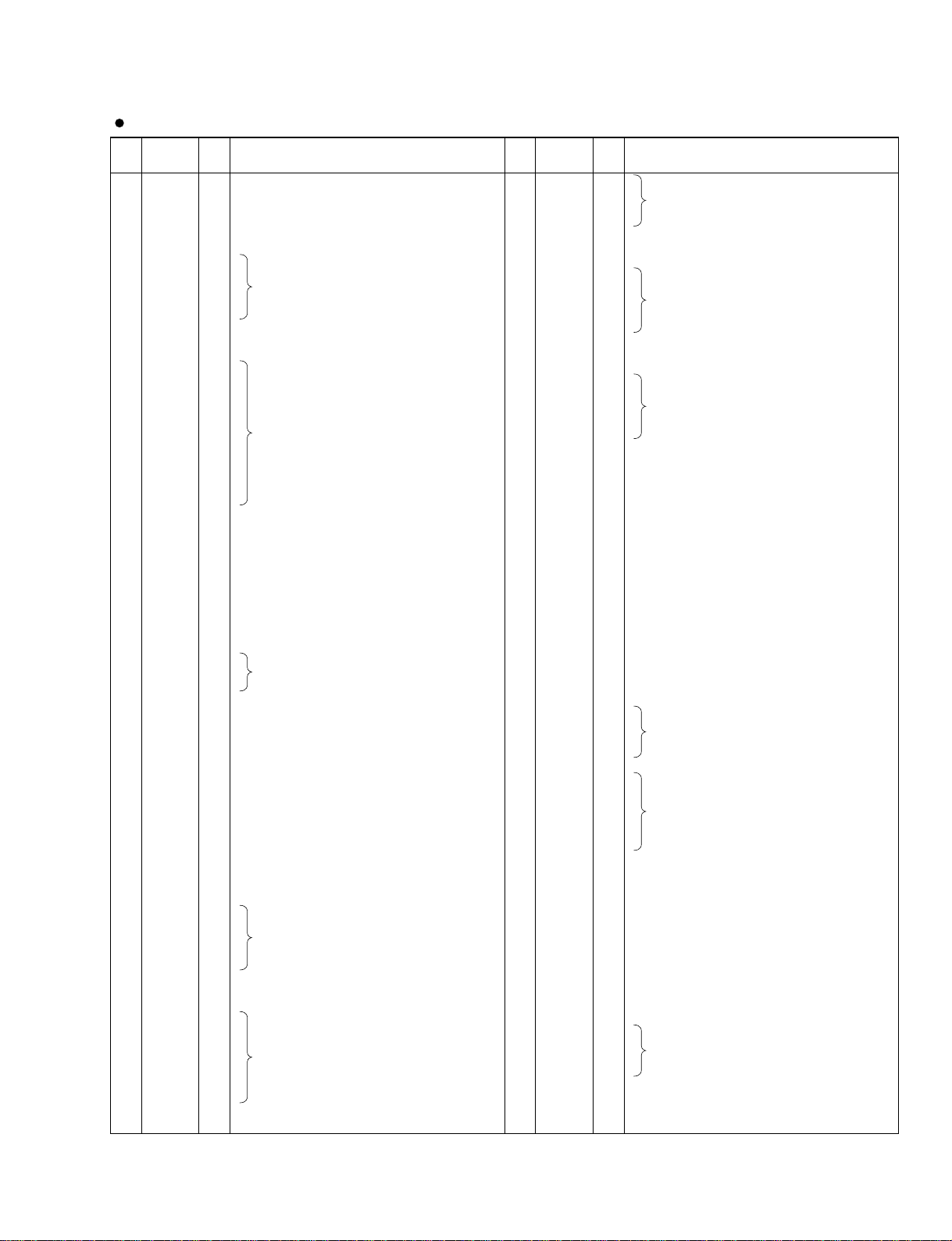

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

PE14

PE15

VSS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

VCC

A17

VSS

/RAS

/CASL

/CASH

VSS

RDWR / PB5

A18

A19

A20

PB9 /A21

VSS

/RD

/WDTOVF

/WRH

VCC

/WRL

VSS

/CS1

/CS0

PA9 / TCLKD

/IRQ2 / TCLKC

/CS3

/CS2

/IRQ1

TXD

RXD

/IRQ0

PA1 / TXD0

PA0 / RXD0

D15

D14

D13

VSS

D12

O

O

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

O

I

O

O

O

O

O

O

O

O

O

I

O

O

O

I

O

I

O

O

O

I

O

O

I

O

I

I

O

I

I/O

I/O

I/O

I

I/O

Port E

Port E

Ground

Address bus

Power supply

Address bus

Ground

Row address strobe

Column address strobe (low)

Column address strobe (high)

Ground

DRAM read/write / Port B

Address bus

Port B / Address bus

Ground

Read

Watch dog timer overflow

High write

Power supply

Low write

Ground

Chip select

Chip select

Port A / Timer clock

Interrupt request / Timer clock

Chip select

Chip select

Interrupt request

Data transmission

Data reception

Interrupt request

Port A / Data transmission

Port A / Data reception

Data bus

Ground

Data bus

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

D11

D10

D9

D8

VSS

D7

D6

D5

VCC

D4

D3

D2

D1

D0

VSS

XTAL

MD3

EXTAL

MD2

NMI

VCC

MD1

MD0

PLLVCC

PLLCAP

PLLVSS

PA15 / CK

/RES

PE0

PE1

PE2

PE3

PE4

VSS

AN0 / PF0

AN1 / PF1

AN2 / PF2

AN3 / PF3

AN4 / PF4

AN5 / PF5

AVSS

AN6 / PF6

AN7 / PF7

AVCC

VSS

PE5

VCC

PE6

PE7

PE8

PE9

PE10

VSS

PE11

PE12

PE13

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

I

I

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

I

O

O

O

O

O

I

O

O

O

Data bus

Ground

Data bus

Power supply

Data bus

Ground

Crystal oscillator

Mode control

Crystal oscillator

Mode control

Non-maskable interrupt request

Power supply

Mode control

Mode control

PLL Power supply

PLL capacitor

PLL Ground

Port A / Clock

Reset

Port E

Ground

Analog input / Port F

Analog ground

Analog input / Port F

Analog input / Port F

Power supply

Ground

Port E

Power supply

Port E

Ground

Port E

HD6477042AF28 (XY715A00) CPU

IC127

IC101

EMB:

PDB:

CIB:

GDB:

IC129,139

IC100

IC100

IC100

EDB:

IDB:

DSP1D

10

LSI PIN DESCRIPTION

HD6477042AF28 (XY715A00) CPU ···················································································· 10

HD6477043AF33 (XY716A00) CPU ···················································································· 11

YSS910-S (XV988A00) DSP6 (Digital Signal Processor)···················································· 12

YSS904-F (XV989A00) DSP5 (Digital Signal Processor) ···················································· 13

SGH609080F-47F (XU235A00) ATSC ················································································ 14

YM3436DK (XG948E0) DIR2 (Digital Format Interface Receiver)······································· 15

AM7992BPC (XW277A00) SIA (Serial Interface Adapter) ·················································· 15

ICS2008A (XV619A00) T.C. Reader/Generator································································· 16

PDIUSBD12PW (XW583A00) USB Interface ····································································· 16

Page 15

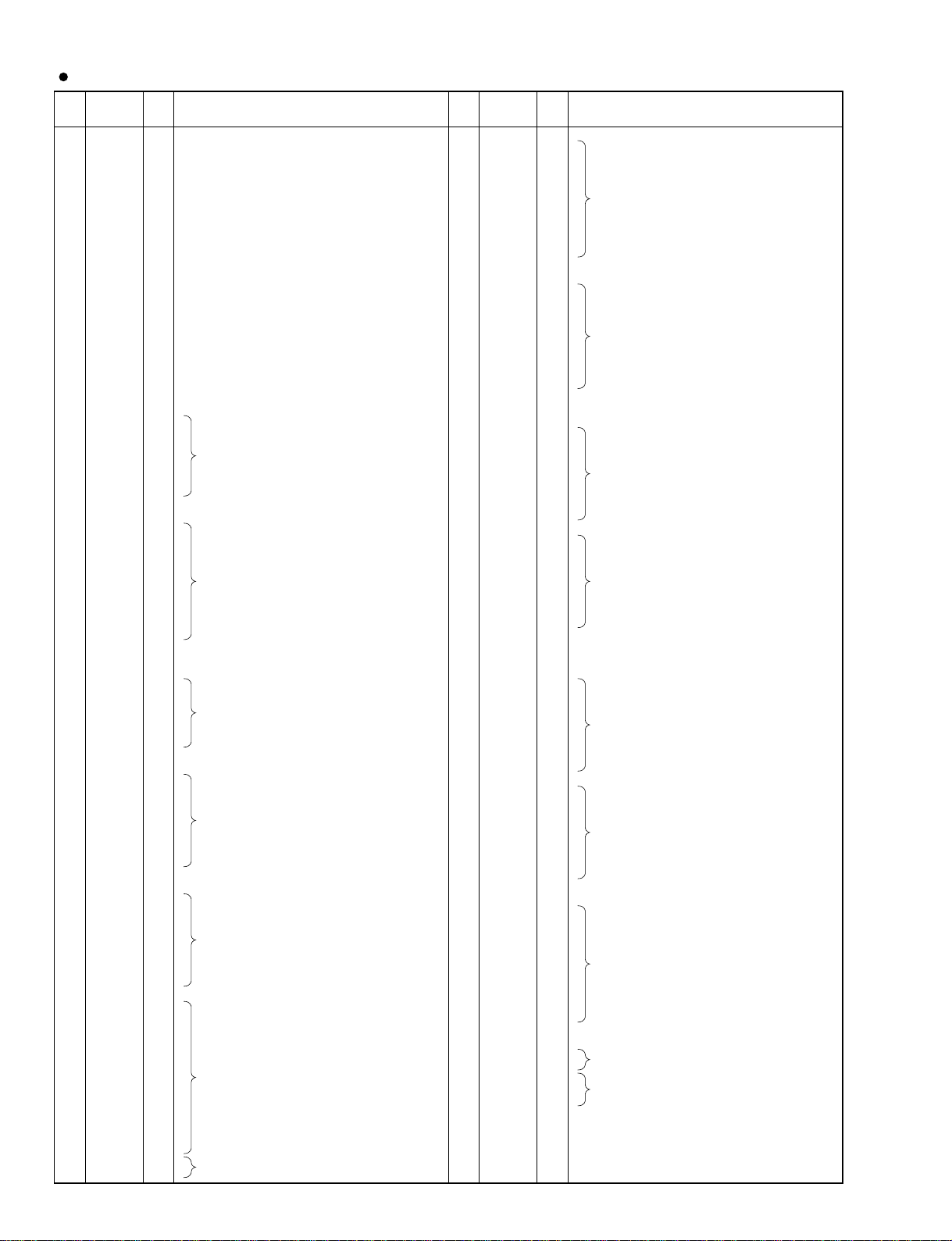

DSP1D

11

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

/WRHH

/DACK0/PE14

/WRHL

CASHH/PA21

DACK1/PE15

VSS

A0

A1

A2

A3

A4

VCC

A5

VSS

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

VCC

A17

VSS

/CASHL/PA20

PA19

/RAS/PB2

/CASL/PB3

PA18

/CASH/PB4

VSS

RDWR/PB5

A18

A19

A20

VCC

A21

VSS

/RD

/WDTOVF

D31

D30

/WRH

/WRL

/CS1

/CS0

/IRQ3/PA9

/IRQ2/PA8

/CS3

/CS2

VSS

D29

D28

D27

D26

D25

VSS

D24

VCC

D23

D22

D21

D20

D19

D18

D17

VSS

D16

O

O

O

I/O

O

I

O

O

O

O

O

I

O

I

O

O

O

O

O

O

O

O

O

O

O

I

O

I

I/O

I/O

O

O

I/O

O

I

O

O

O

O

I

O

I

O

O

I/O

I/O

O

O

O

O

I/O

I/O

O

O

I

I/O

I/O

I/O

I/O

I/O

I

I/O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

HH write

DAM transfer strobe/Port E

HL write

HH Column address strobe/Port A

DMA transfer strobe/Port E

Ground

Address bus

Power supply

Address bus

Ground

Address bus

Power supply

Address bus

Ground

HL Column address strobe/Port A

Port A

Row address strobe/Port B

Column address strobe (low) /Port B

Port A

Column address strobe (high) /Port B

Ground

DRAM read/write /Port B

Address bus

Power supply

Address bus

Ground

Read

Watch dog timer overflow

Data bus

Data bus

High write

Low write

Chip select

Chip select

Interrupt request/Port A

Interrupt request/Port A

Chip select

Chip select

Ground

Data bus

Ground

Data bus

Power supply

Data bus

Ground

Data bus

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

D15

D14

D13

D12

VCC

D11

VSS

D10

D9

D8

D7

D6

VCC

D5

VSS

D4

D3

D2

D1

D0

VSS

XTAL

MD3

EXTAL

MD2

NMI

VCC

PA16

PA17

MD1

MD0

PLLVCC

PLLCAP

PLLVSS

CK/PA15

/RES

/DREQ0/TIOC0A/PE0

PE1

/DREQ1/PE2

VCC

PE3

PE4

PE5

PE6

VSS

AN0 /PF0

AN1/ PF1

AN2 /PF2

AN3 /PF3

AN4 /PF4

AN5/PF5

AVSS

AN6/PF6

AN7/PF7

AVREF

AVCC

VSS

RxDO

TxDO

/IRQ0/SCK0

RxD1

TxD1

VCC

/IRQ1/SCK1

PE7

PE8

PE9

PE10

VSS

TIOC3D/PE11

PE12

PE13

I/O

I/O

I/O

I/O

I

I/O

I

I/O

I/O

I/O

I/O

I/O

I

I/O

I

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

-

I

I/O

I/O

I

I

I

I

I

I/O

I

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

I

I

I/O

I

I

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

Data bus

Power supply

Data bus

Ground

Data bus

Power supply

Data bus

Ground

Data bus

Ground

Crystal oscillator

Mode select

Crystal oscillator

Mode select

Non-maskable interrupt

Power supply

Port A

Port A

Mode select

Mode select

PLL Power supply

PLL capacitor

PLL Ground

Clock/Port A

Reset

DMA transfer request/MTU input capture/output compare (ch 0)/Port E

Port E

DMA transfer request/Port E

Power supply

Port E

Ground

Analog input/Port F

Analog ground

Analog input/ Port F

Analog input /Port F

Analog reference voltage

Analog power supply

Ground

Receive data

Transmit data

Interrupt request/Serial clock

Receive data

SCI

Power supply

Interrupt request/Serial clock

Port E

Ground

MTU input capture/output compare (ch 3)/Port E

Port E

Port E

HD6477043AF33 (XY716A00) CPU EMB: IC114

Page 16

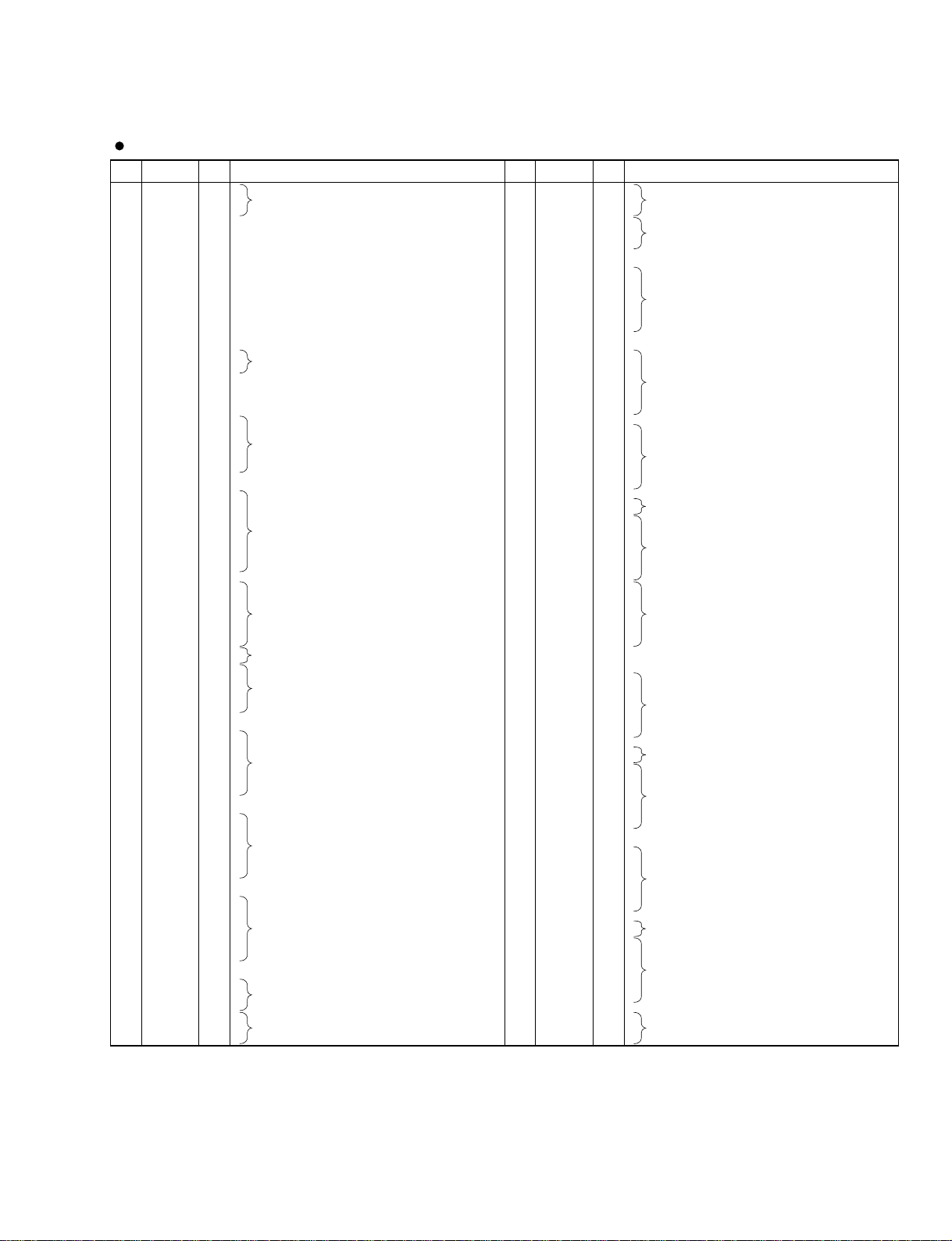

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

Vdd

Vss

XI

XO

Vdd

/SYNCI

/SYNCO

Vdd

CKI

CKO

CKSEL

Vss

MCKS

/SSYNC

/IC

/TEST

BTYP

/IRQ

TRIG

Vdd

Vss

/CS

/WR

/RD

CA7

CA6

CA5

CA4

CA3

CA2

CA1

Vss

Vdd

CD15

CD14

CD13

CD12

CD11

CD10

CD09

CD08

CD07

CD06

Vss

Vdd

Vdd

CD05

CD04

CD03

CD02

CD01

CD00

/WAIT

Vss

SI0

SI1

SI2

SI3

SI4

SI5

SI6

SI7

Vss

Vdd

SO0

SO1

SO2

SO3

SO4

SO5

SO6

SO7

Vss

DB00

DB01

DB02

DB03

DB04

DB05

DB06

DB07

DB08

DB09

DB10

DB11

DB12

Vdd

Vdd

I

O

I

O

I

O

I

I

I

I

I

I

O

I/O

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Power supply (3.3 V)

Ground

System master clock input (60 MHz or 30 MHz)

System master clock output (High or 30 MHz)

Power supply (5 V)

Sync. signal input

Sync. signal output

Power supply (5 V)

System clock input (30 MHz)

System clock output (30 MHz)

System master clock select (0: 60 MHz, 1: 30 MHz)

Ground

Serial I/O master clock input (128 x Fs)

Serial I/O Sync. signal output

Initial clear

Test mode setting (0: Test, 1: Normal)

Data bus type select (0: 8 bit, 1: 16 bit)

IRQ output

Trigger signal input/output

Power supply (5 V)

Ground

chip select signal input

Write signal input

Read signal input

Address bus of internal register

Ground

Power supply (3.3 V)

Data bus of internal register

Ground

Power supply (3.3 V)

Power supply (5 V)

Data bus of internal register

WAIT output

Ground

Serial data input

Ground

Power supply (5 V)

Serial data output

Ground

Parallel data bus

Power supply (5 V)

Power supply (3.3 V)

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

Vss

DB13

DB14

DB15

DB16

DB17

DB18

DB19

DB20

DB21

DB22

Vss

Vdd

DB23

DB24

DB25

DB26

DB27

DB28

DB29

DB30

DB31

TIMO/DBOB

Vss

Vdd

DA00

DA01

DA02

DA03

DA04

DA05

DA06

DA07

Vss

DA08

DA09

DA10

DA11

DA12

DA13

DA14

DA15

Vss

Vdd

(n.c)

Vdd

DA16

DA17

DA18

DA19

DA20

DA21

DA22

DA23

Vss

DA24

DA25

DA26

DA27

DA28

DA29

DA30

DA31

Vdd

Vss

A00

A01

A02

A03

A04

A05

A06

A07

A08

A09

Vss

Vdd

A10

A11

A12

A13

A14

A15/RAS

A16/CAS

A17/CE

/WE

/OE

Vdd

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

Ground

Parallel data bus

Ground

Power supply (3.3 V)

Parallel data bus

Timing signal output/ Parallel data bus output/ input

Ground

Power supply (5 V)

Memory data bus

Ground

Memory data bus

Ground

Power supply (3.3 V)

Not used

Power supply (5 V)

Memory data bus

Ground

Memory data bus

Power supply (5 V)

Ground

Memory address (SRAM, PSRAM, DRAM)

Ground

Power supply (3.3 V)

Memory address (SRAM, PSRAM, DRAM)

Memory address (SRAM, PSRAM)

Memory address (SRAM, PSRAM), /RAS (DRAM)

Memory address (SRAM, PSRAM), /CAS (DRAM)

Memory address (SRAM), /CE (PSRAM)

Memory write enable signal

Memory output enable signal

Power supply (5 V)

YSS910-S (XV988A00) DSP6 (Digital Signal Processor)

EDB:

GDB:

IDB:

PDB:

IC300,304,350,354,400,404,450,454,500,503,550,553

IC300,305,350,351,400,403,450,451,500,503,550,551,600

IC250,255,300,301,350,351,400,401,450,453,500,501,550,551,600,601

IC500,505,550,551,600,603,650,700,701

DSP1D

12

Page 17

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

NC

NC

NC

NC

Vdd

Vss

XI

XO

Vdd

/SYNCI

/SYNCO

Vdd

CKI

CKO

CKSEL

Vss

MCKD

/SSYNC

/IC

/TEST

NC

NC

NC

Vdd

Vss

/CS

/WR

/RD

CA7

CA6

CA5

CA4

CA3

CA2

CA1

Vss

Vdd

CD15

CD14

CD13

CD12

CD11

CD10

CD09

CD08

CD07

CD06

Vss

NC

NC

NC

NC

NC

NC

NC

NC

Vdd

Vdd

CD05

CD04

CD03

CD02

CD01

CD00

/WAIT

Vss

SIO00

SIO01

SIO02

SIO03

SIO04

SIO05

SIO06

SIO07

Vss

Vdd

SIO08

SIO09

SIO10

SIO11

SIO12

SIO13

SIO14

SIO15

Vss

Vdd

SIO16

SIO17

SIO18

SIO19

SIO20

SIO21

SIO22

SIO23

Vss

Vdd

SIO24

SIO25

SIO26

SIO27

NC

NC

NC

NC

I

O

O

I

O

I

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Not used

Ground

Power supply

System master clock input (60 MHz or 30 MHz)

System master clock output (High or 30 MHz)

Ground

Sync. signal input

Sync. signal output

Ground

System clock input (30 MHz)

System clock output (30 MHz)

System master clock select

Power supply

Serial clock input (256 fs)

Serial. signal input

Initial clear

Test mode setting (0: TEST, 1: Normal)

Not used

Ground

Power supply

Chip select

Write enable input

Read enable input

CPU address bus

Power supply

Ground

CPU data bus

Power supply

Not used

Ground

CPU data bus

Wait output

Power supply

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Not used

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

NC

NC

NC

NC

SIO28

SIO29

SIO30

SIO31

Vss

Vdd

SIO32

SIO33

SIO34

SIO35

SIO36

SIO37

SIO38

SIO39

Vss

Vdd

SIO40

SIO41

SIO42

SIO43

SIO44

SIO45

SIO46

SIO47

Vss

SIO48

SIO49

SIO50

SIO51

SIO52

SIO53

SIO54

SIO55

Vss

Vdd

Vdd

SIO56

SIO57

SIO58

SIO59

SIO60

SIO61

SIO62

SIO63

NC

NC

NC

NC

NC

NC

NC

NC

Vss

/POE

Vss

PIO00

PIO01

PIO02

PIO03

PIO04

PIO05

PIO06

PIO07

Vss

Vdd

Vdd

PIO08

PIO09

PIO10

PIO11

PIO12

PIO13

PIO14

PIO15

Vss

NC

PIO16

PIO17

PIO18

PIO19

PIO20

PIO21

PIO22

PIO23

Vss

Vdd

Vdd

PIO24

PIO25

PIO26

PIO27

PIO28

PIO29

PIO30

PIO31

Vss

NC

NC

NC

NC

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Not used

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Serial data bus

Power supply

Ground

Serial data bus

Not used

Power supply

Parallel data bus controll signal

Power supply

Parallel data bus

Power supply

Ground

Parallel data bus

Power supply

Not used

Parallel data bus

Power supply

Ground

Parallel data bus

Power supply

Not used

YSS904-F (XV989A00) DSP5 (Digital Signal Processor)

GDB:

IDB:

PDB:

IC250,251,650,651,750,751,800

IC650,651,700,701,750,751,800,801

IC250,251,300,301,350,351,400,401,450,750,751

DSP1D

13

Page 18

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

syncati

mccti

mcbti

VCC

GND

mcati

GND

siat0

siat1

siat2

siat3

ati

GND

ato

soat3

soat2

soat1

soat0

VCC

GND

mcato

GND

mcbto

mccto

syncato

clksel

ato-sel0

ato-sel1

bitsel2

bitsel1

bitsel0

VCC

GND

ext-sync2

ui0

ui1

ui2

ui3

si-sel0

si-sel1

I

I

I

I

I

I

I

I

I

O

O

O

O

O

I

I

I

I

I

I

I

Synch. word input terminal for ati,

siat3-0 input

64 fs clock input terminal for ati,

siat3-0 input

128 fs clock input terminal for ati,

siat3-0 input

Power supply (+5 V)

Ground

256 fs clock input terminal for ati,

siat3-0 input

Ground

Serial data input terminal

Optical input terminal

Ground

Optical output terminal

Serial data output terminal

Power supply (+5 V)

Ground

256 fs clock input terminal for ato,

soat3-0 output

Ground

128 fs clock input terminal for ato,

soat3-0 output

64 fs clock input terminal for ato,

soat3-0 output

Synch. word input terminal for ato,

soat3-0 output

Clock select terminal for ato,

soat 3-0 output

0: mcato,mcbto,mccto,syncato

1: mcai,mcbi,mcci,synci

Format select terminal for ato,

soat3-0 output

Format select terminal for ato,

soat3-0 output

Bit shift select terminal for the ato output

Power supply (+5 V)

Ground

Synch. detect output terminal 2

U-bit input terminal for optical output

input format select terminal for si3-0

input format select terminal for si3-0i

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

synci

mcci

mcbi

VCC

GND

mcai

GND

si0

si1

si2

si3

GND

so3

so2

so1

so0

VCC

GND

mcao

GND

mcbo

mcco

synco

so-sel1

so-sel0

uo3

uo2

uo1

uo0

ext-sync1

VCC

GND

clk

GND

/res

GND

wc-at

mute

ati-sel1

ati-sel0

I

I

I

I

I

I

I

I

O

O

O

O

I

I

I

I

I

I

O

O

O

O

O

I

I

O

I

I

I

Synch. word input terminal for si3-0 input

64 fs clock input terminal for si3-0 input

128 fs clock input terminal for si3-0 input

Power supply (+5 V)

Ground

256 fs clock input terminal for si3-0 input

Ground

Serial data input terminal

Ground

Serial data output terminal

Power supply (+5 V)

Ground

256 fs clock input terminal for so3-0 output

Ground

128 fs clock input terminal for so3-0 output

64 fs clock input terminal for so3-0 output

Synch. word input terminal for so3-0 output

Format select terminal for soat3-0 output

Format select terminal for soat3-0 output

U-bit output terminal for optical output

Synch. detect output terminal 1

Power supply (+5 V)

Ground

Clock input terminal for word clock extract

Ground

System reset input terminal

Ground

Word clock output terminal

Data mute input terminal

Input format select terminal for ati, siat3-0.

input format select terminal for ati, siat3-0.

SGH609080F-47F (XU235A00) ATSC

1

1

0

0

so sel1

1

0

1

0

so sel0

not enable to set

so0

so2, 0

so3-0

(8ch/line)

(4ch/line)

(2ch/line)

input format

1

1

0

0

ati sel1

1

0

1

0

ati sel0

ati

ati0

ati2, 0

ati3-0

(8ch/line)

(4ch/line)

(2ch/line)

input format

1

1

0

0

ato sel1

0: mcato,mcbto,mccto,syncato

1: mcai,mcbi,mcci,synci

1

0

1

0

ato sel0

ato

soat0

soat2, 0

soat3-0

(8ch/line)

(4ch/line)

(2ch/line)

output format

1

1

0

0

si sel1

1

0

1

0

si sel0

not enable to set

si0

si2, 0

si3-0

(8ch/line)

(4ch/line)

(2ch/line)

input format

IC100,101,113,114

IC109,110,118,119

JK2:

JK4:

JK1:

JK3:

IC109,110,119,120

IC111-114

DSP1D

14

Page 19

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

CLSN

RX

RENA

RCLK

TSEL

GND1

GND2

X1

X2

TX

TCLK

TENA

O

O

O

O

I/O

-

I

I

I

O

I

Collision (Output, TTL Active HIGH)

Receive Data

Receive Enable (Output, TTL Acvtive HIGH)

Receive Clock

Transmit Mode Select (Output, Open Collector;

Input, Sense Amplifier)

High Current Ground

Logic Ground

Biased Crystal Oscillator

Biased Crystal Oscillator

Transmit

Transmit Clock

Transmit Enable

13

14

15

16

17

18

19

20

21

22

23

24

Collision+

Collision-

Receive+

Receive-

/TEST

Vcc1

Vcc2

PF

RF

GND3

Transmit+

Transmit-

I

I

I

I

I

-

I

O

-

O

O

Collision

Collision

Receiver

Receiver

Test Control

High Current and Logic Supply

Voltage-Controlled Oscillator Supply

Receive Path Vco Phase-Locked Loop Filter

Frequency Setting Voltage-Controlled

Oscillator (Vco) Loop Filter (Output)

Voltage-Controlled Oscillator Ground

Transmit

Transmit

AM7992BPC (XW277A00) SIA (Serial Interface Adapter)

CIB: IC112-115

DSP1D

15

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

DAUX

HDLT

DOUT

VFL

OPT

SYNC

MCC

WC

MCB

MCA

SKSY

XI

XO

P256

LOCK

Vss

TC

DIM1

DIM0

DOM1

DOM0

KM1

I

O

O

O

O

O

O

O

O

O

I

I

O

O

O

O

I

I

I

I

I

Auxiliary input for audio data

Asynchronous buffer operation flag

Audio data output

Parity flag output

Fs x 1 Synchronous output signal for DAC

Fs x 1 Synchronous output signal for DSP

Fs x 64 Bit clock output

Fs x 1 Word clock output

Fs x 128 Bit clock output

Fs x 256 Bit clock output

Clock synchronization control input

Crystal oscillator connection or external

clock input

Crystal oscillator connection

VCO oscillating clock connection

PLL lock flag

Logic section power (GND)

PLL time constant switching output

Data input mode selection

Data input mode selection

Data output mode selection

Data output mode selection

Clock mode switching input 1

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

RSTN

Vdda

CTLN

PCO

(NC)

CTLP

Vssa

TSTN

KM2

KM0

FS1

FS0

CSM

EXTW

DDIN

LR

Vdd

ERR

EMP

CD0

CCK

CLD

I

I

O

I

I

I

I

O

O

I

I

I

O

O

O

O

I

I

System reset input

VCO section power (+5 V)

VCO control input N

PLL phase comparison output

VCO control input P

VCO section power (GND)

Test terminal. Open for normal use

Clock mode switching input 2

Clock mode switching input 0

Channel status sampling frequency

display output 1

Channel status sampling frequency

display output 0

Channel status output method selection

External synchronous auxiliary input

word clock

EIAJ (AES/EBU) data input

PLL word clock output

Logic section power (+5 V)

Data error flag output

Channel status emphasis control code

output

3-wire type microcomputer interface data

output

3-wire type microcomputer interface clock

input

3-wire type microcomputer interface load

input

YM3436DK (XG948E0) DIR2 (Digital Format Interface Receiver)

IC112,121

IC110,126

IC202

JK1:

JK3:

JK6

IFC1:

JK2:

JK4:

IC604-606

IC112,121

IC112,120

Page 20

DSP1D

16

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

INTR

RESET

FRAME

CLICK

LTCIN-

LTCIN+

LTCOUT

LFC

XTAL2

XTAL1

AVDD

AVSS

COUT

YOUT

C2

Y2

C1

Y1

STHRESH

CTHRESH

DTHRESH

RXD

O

I

I

I

I

I

O

I

O

I

-

O

O

I

I

I

I

I

I

I

I

Interrupt request

Master reset

Color frame A / B input

LTC SYNC input

SMPTE LTC input SMPTE LTC input +

SMPTE LTC output

External RC circuit

14.318 MHz crystal oscillator

14.318 MHz crystal oscillator

Analog power supply

Analog ground

C(Chroma) output

Y(Luma) output

C(Chroma) input

Y(Luma) input

C(Chroma) input

Y(Luma) input

SYNC threshold bypass input

Clamp threshold bypass input

Data threshold bypass input

UART receive data

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

CTS

TXD

RTS

LRCLK

VITCGATE

VITCOUT

A0

A1

/SMPTECS

/UARTSC

/IOR

VSS

VDD

/IOW

D0

D1

D2

D3

D4

D5

D6

D7

I

O

O

O

O

O

I

I

I

I

I

-

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Clear to send

UART transmit data

Ready to send

SMPTE LTC receive clock

VITE cord is for video overlay

SMPTE VITE output

Address bus

Address bus

SMPTE port chip select

UART chip select

Read enable

Digital ground

Digital power supply

Write enable

Data bus

ICS2008A (XV619A00) T.C. Reader/Generator CIB: IC136

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DATA0

DATA1

DATA2

DATA3

GND

DATA4

DATA5

DATA6

DATA7

ALE

CS_N

SUSPEND

CLKOUT

INT_N

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I/O

O

O

Bit 0 of bi-directional data.

Bit 1 of bi-directional data.

Bit 2 of bi-directional data.

Bit 3 of bi-directional data.

Ground

Bit 4 of bi-directional data.

Bit 5 of bi-directional data.

Bit 6 of bi-directional data.

Bit 7 of bi-directional data.

Address Latch Enable.

Chip Select (Active Low).

Device is in Suspend state.

Programmable Output Clock (slew-rate controlled)

interrupt (Active Low)

15

16

17

18

19

20

21

22

23

24

25

26

27

28

RD_N

WR_N

DMREQ

DMACK_N

EOT_N

RESET_N

GL_N

XTAL1

XTAL2

Vcc

D-

D+

Vout3.3

A0

I

I

O

I

I

I

O

I

O

-

-

-

I

Read Strobe (Active Low)

Write Strobe (Active Low)

DMA Request.

DMA Acknowledge (Active Low).

End of DMA Transfer (Active Low).

Reset (Active Low and asynchronous).

Built-in Power-On-Reset circuit

GoodLink LED indicator (Active Low)

Crystal Connection 1 (6 MHz)

Crystal Connection 2 (6 MHz)

Voltage supply (4.0-5.5 V)

USB D-data line

USB D+data line

3.3 V regulated output.

Address bit. A0=1 selects command

instruction; A0=0 selects the data phase.

PDIUSBD12PW (XW583A00) USB Interface JK6: IC105

Page 21

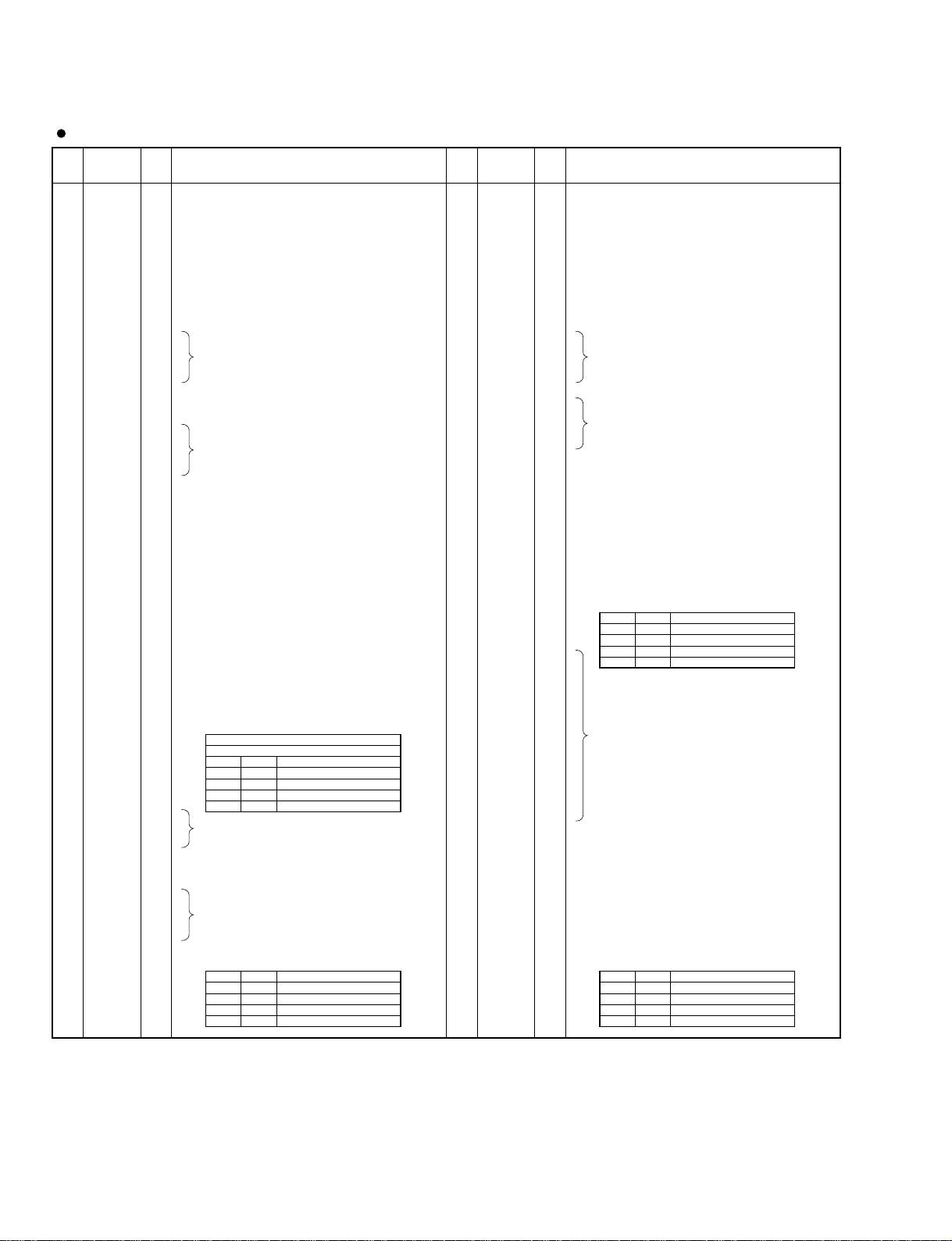

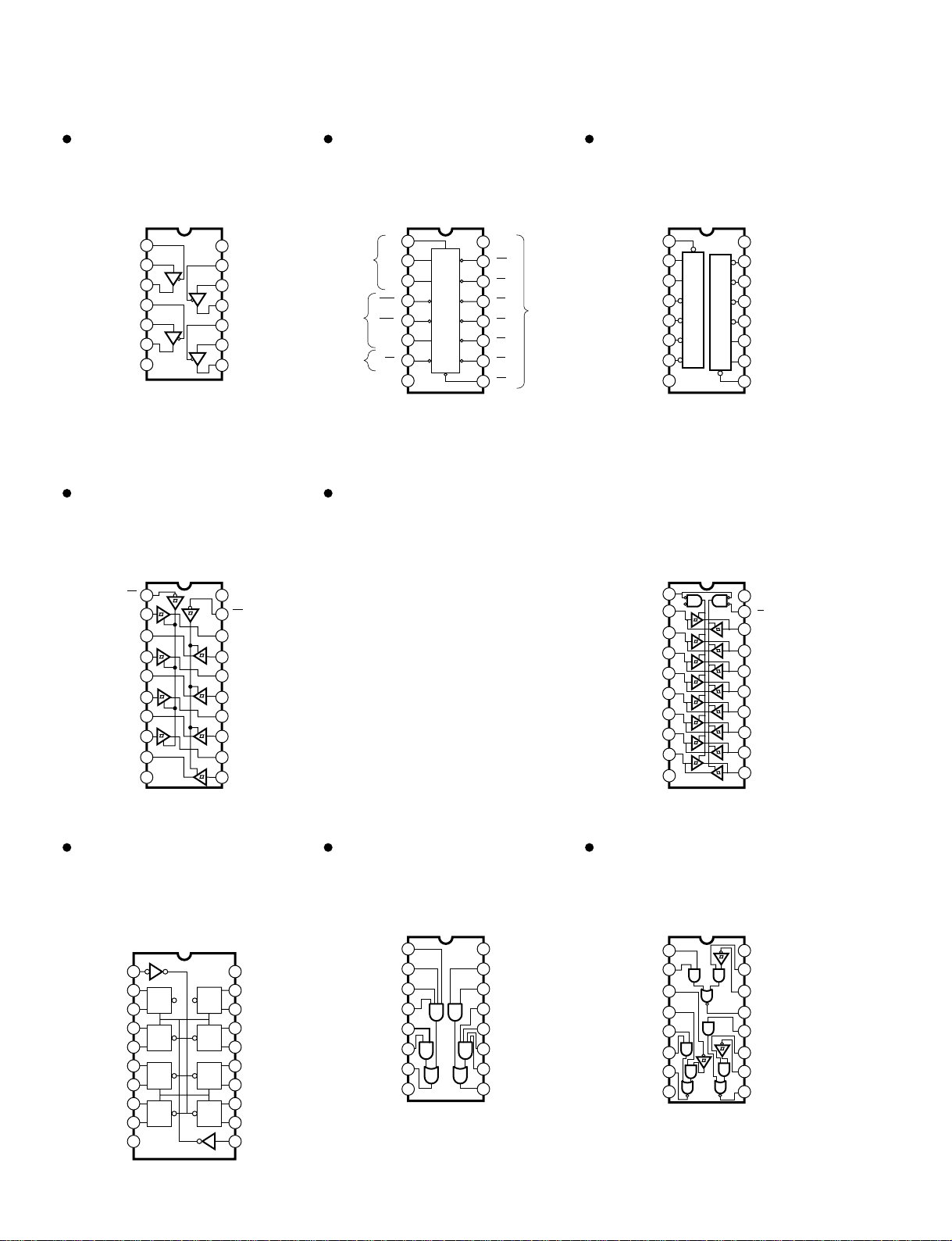

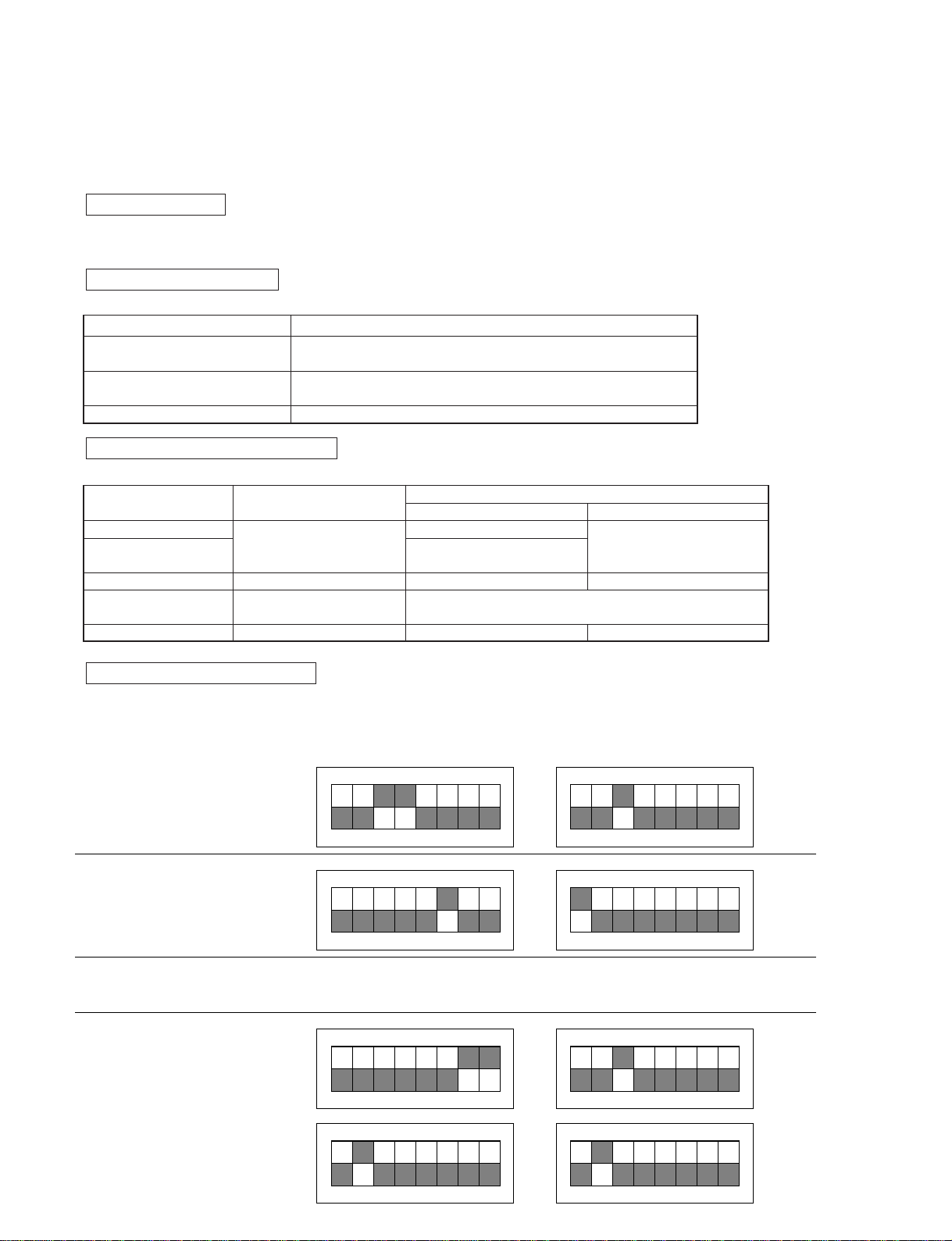

IC BLOCK DIAGRAM

HD74LV00AFPEL (IS000000)

Quad 2 Input NAND

EMB: IC101,105

HD74LV02AFPEL (IS00020)

Quad 2 Input NOR

CIB:

JK3:

HD74LV04AFPEL (IS000400)

HD74LV05AFPEL (IS000500)

SN74LS06NSR (XP985A00)

Hex Inverter

CIB:

EMB:

IDB:

JK1:

JK3:

JK5:

PDB:

HD74LV08AFPEL (IS000800)

Quad 2 Input AND

CIB:

EMB:

IDB:

JK1:

JK4:

HD74LV11AFPEL (IS001100)

Triple 3 Input AND

CIB:

EMB:

HD74LV14AFPEL (IS001400)

Hex Inverter

JK6: IC107

HD74HC30FPTL (XQ970A00)

8 Input NAND

EMB: IC106

HD74LV32AFPEL (IS003200)

Quad 2 Input OR

CIB:

GDB:

IDB:

JK2:

JK4:

HD74LV74AFPEL (IS007400)

Dual D-Type Flip-Flop

CIB: IC111

1

2

3

1A

1Y

42A

52B

62Y

7Vss

1B

14

13

12

VDD

4A

11 4Y

10 3B

9 3A

8 3Y

4B

1

2

3

1Y

1B

42Y

52A

62B

7Vss

1A

14

13

12

VDD

4A

11 4B

10 3Y

9 3A

8 3B

4Y

1

2

3

4

5

6

7

1A

1Y

2A

2Y

3A

3Y

Vss

14

13

12

11

10

9

8

VDD

6A

6Y

5A

5Y

4A

4Y

1

2

3

1A

1Y

42A

52B

62Y

7

VSS

1B

14

13

12

VDD

4A

11 4Y

10 3B

9 3A

8 3Y

4B

1

2

3

1A

2A

42B

52C

62Y

7

VSS

1B

14

13

12

VDD

1Y

11 3C

10 3B

9 3A

8 3Y

1C

1

2

3

4

5

6

7

1A

1Y

2A

2Y

3A

3Y

GND

14

13

12

11

10

9

8

VDD

6A

6Y

5A

5Y

4A

4Y

1

2

3

A

C

4D

5E

6F

7

GND

B

14

13

12

Vcc

H

11 G

10 NC

9 NC

8 Y

NC

1

2

3

1A

1Y

42A

52B

62Y

7GND

1B

14

13

12

Vcc

4A

11 4Y

10 3B

9 3A

8 3Y

4B

INPUTS OUTPUTS

PR CLR CLK D Q Q

L

H

H

L

H

Q

O

H

L

H

H

L

Q O

X

X

X

H

L

X

X

X

X

f

f

L

H

L

L

H

H

H

L

H

L

H

H

H

1

2

3

4

5

6

7

1CLR

1D

1CK

1PR

1Q

1Q

GND

14

13

12

11

10

9

8

VCC

2CLR

CLR

2D

D

2CK

CK

2PRPR

2Q

2Q

Q

Q

CLR

D

CK

PR

Q

Q

IC103,117,128,151

IC107,108,151

IC111,116

IC102,141

IC100,141

IC108

IC109,IC115

EDB:

GDB:

IFC1:

JK2:

JK4:

JK6:

IC109,IC110

IC109,IC110

IC601

IC109,141

IC102,121,141

IC100,IC108

JK1:

JK4:

IC100

IC100

IC104

IC108

IC131,141

IC116,117,129

IC114,115

IC140

IC140

JK2:

JK6:

IC140

IC207

JK3:

PDB:

IC140

IC102,103

EDB:

GDB:

IFC1:

IC106,107

IC106,107

IC602

IC134

IC108

IC112,113

IC126

IC125

JK1:

JK3:

PDB:

IC126

IC130

IC100,108

EDB:

GDB:

IC105

IC108

EMB: IC122

IC1102

IC132

DSP1D

17

Page 22

DSP1D

18

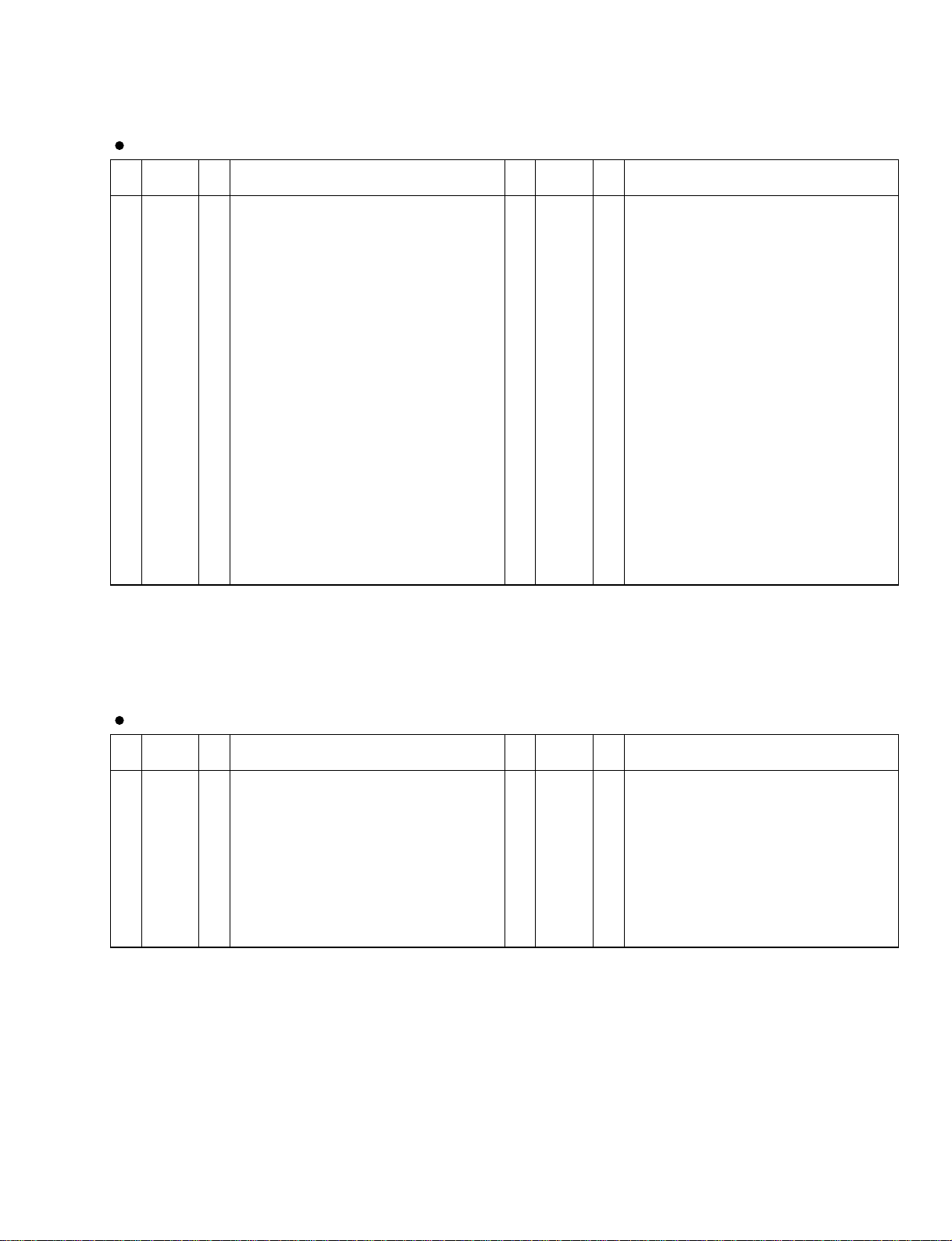

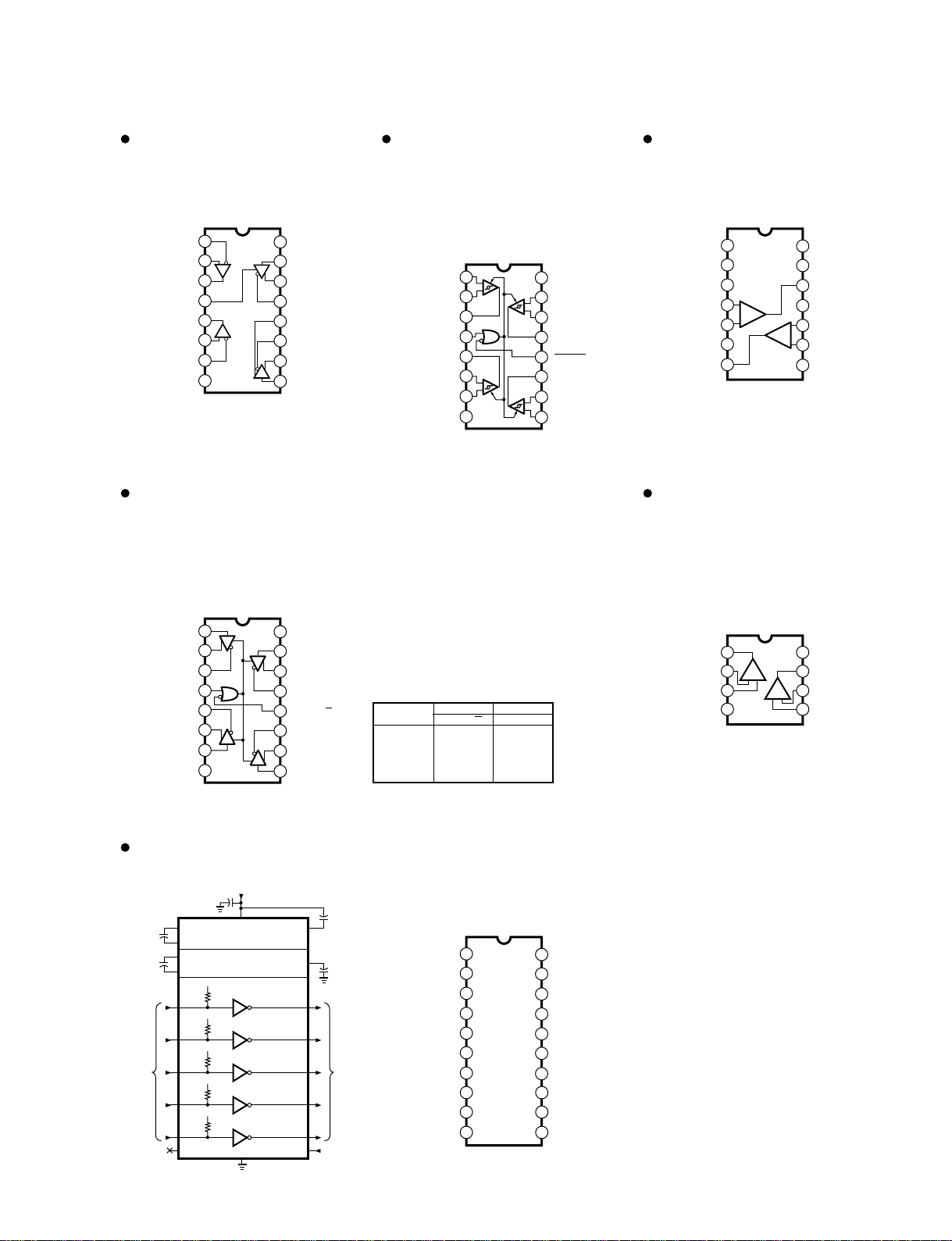

SN74HC125N (IR012550)

HD74LV125AFPEL (IS012500)

Quad 3-State Bus Buffer

CIB:

JK:

SN74LV138ANSR (IS013810)

3 to 8 Demultiplexer

CIB: IC152

SN74LV139ANSR (IS013910)

Dual 2 to 4 Demultiplexer

JK1:

JK3:

HD74LV244AFPEL (IS024400)

Octal 3-State Bus Buffer

IDB: IC855

HD74LV245AFPEL (IS024500)

TC74VHC245F (XT487A00)

TC74VHCT245AF (XV242A00)

TC74HC245AP (IR024500)

Octal 3-State Bus Transceiver

CIB:

EDB:

EMB:

GDB:

IDB:

IFC1:

JK1:

JK2:

JK3:

JK5:

JK4:

JK6:

PDB:

HD74LV273AFPEL (IS027300)

SN74HC273N (IR027350)

Octal D-Type Flir Flop

CIB:

JK2:

JK4:

SN75121NSR (XU816A00)

Dual Line Driver

JK6: IC200

SN75124NSR (XV930A00)

Triple Line Receiver

JK6: IC201

1

2

3

4

5

6

7

A

A

Select

Enable

Output

Output

B

B

C

C

G2A

G2A

G2B

G2B

G1

G1

Y7

Y7 Y5

Y4

Y3

Y2

Y1

Y0

Y6

16

15

14

13

12

11

10

Vcc

YO

Y1

Y2

Y3

Y4

Y5

8

GND

9

Y6

1

2

3

4

5

6

7

1G

1A

1B

1Y0

1Y1

1Y2

1Y3

A

G

B

Y0

Y1

Y2

Y3

16

15

14

13

12

11

10

Vcc

2G

2A

2B

2Y0

2Y1

2Y2

8

GND

9

2Y3

Y2

Y3

Y1

Y0

B

A

G

1

2

3

4

5

6

7

C1

A1

Y1

C2

A2

Y2

GND

14

13

12

11

10

9

8

Vcc

C4

A4

Y4

C3

A3

Y3

1G

1A1

2Y4

1A2

2Y3

1A3

2Y2

1A4

2Y1

1 20

2 19

3 18

4 17

5 16

6 15

7 14

8 13

9 12

10 11

VDD (Vcc)

2G

1Y1

2A4

1Y2

2A3

1Y3

2A2

1Y4

2A1

(GND) Vss

1

2

3

4

5

6

7

20

19

18

17

16

15

14

Vcc

G

B1

B2

B3

B4

B5

B6

B7

B8

8

9

10

12

11

GND

A8

A7

A6

A5

A4

A3

A2

A1

D1R

13

1A

1B

2R

2S

2A

2B

2Y

GND

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

Vcc

1S

1R

1Y

3A

3S

3R

3Y

Vcc

2F

2E

2A

2Y

GND

1Y

2C

2B

2D

1A

1B

1C

1D

1E

1F

8

1

2

3

4

5

6

7

9

16

15

14

13

12

11

10

IC148,150

IC107

EMB: IC149

IC125

IC131

IC125

IC124

JK2:

JK4:

IC105-110,120,121,130,135,137,140,145,146

IC101,250-253,255-260,306,307,600-606

IC120-104,109,112,115,128,134,137-147

IC102,220-229,303,304,850-871

IC220-232,253,254,850-854,856-863,900-913,IC102

IC504-507,509,608-610,701-717

IC122-124,128-133

IC122-124,128-134

IC115,116,127-129,132,134-138

IC103,104,105

IC122,123,127-134

IC103,104,103,204

IC105,103,110-112,200-202,204-206,503,504,

800-822,850-872,900-904

CLEAR

1Q

1D

2D

2Q

3Q

3D

4D

4Q

GND

VCC

8Q

8D

7D

7Q

6Q

6D

5D

5Q

CLOCK

1 20

2 19

3 18

4 17

5 16

6 15

7 14

8 13

9 12

10 11

Q

DCK

CL

D

Q

CK

CL

Q

DCK

CL

D

Q

CK

CL

D

Q

CK

CL

Q

DCK

CL

D

Q

CK

CL

Q

DCK

CL

IC124

IC127

IC126

EMB:

JK3:

JK5:

IC136

IC117-119,133

IC102

JK1: IC127

Page 23

DSP1D

19

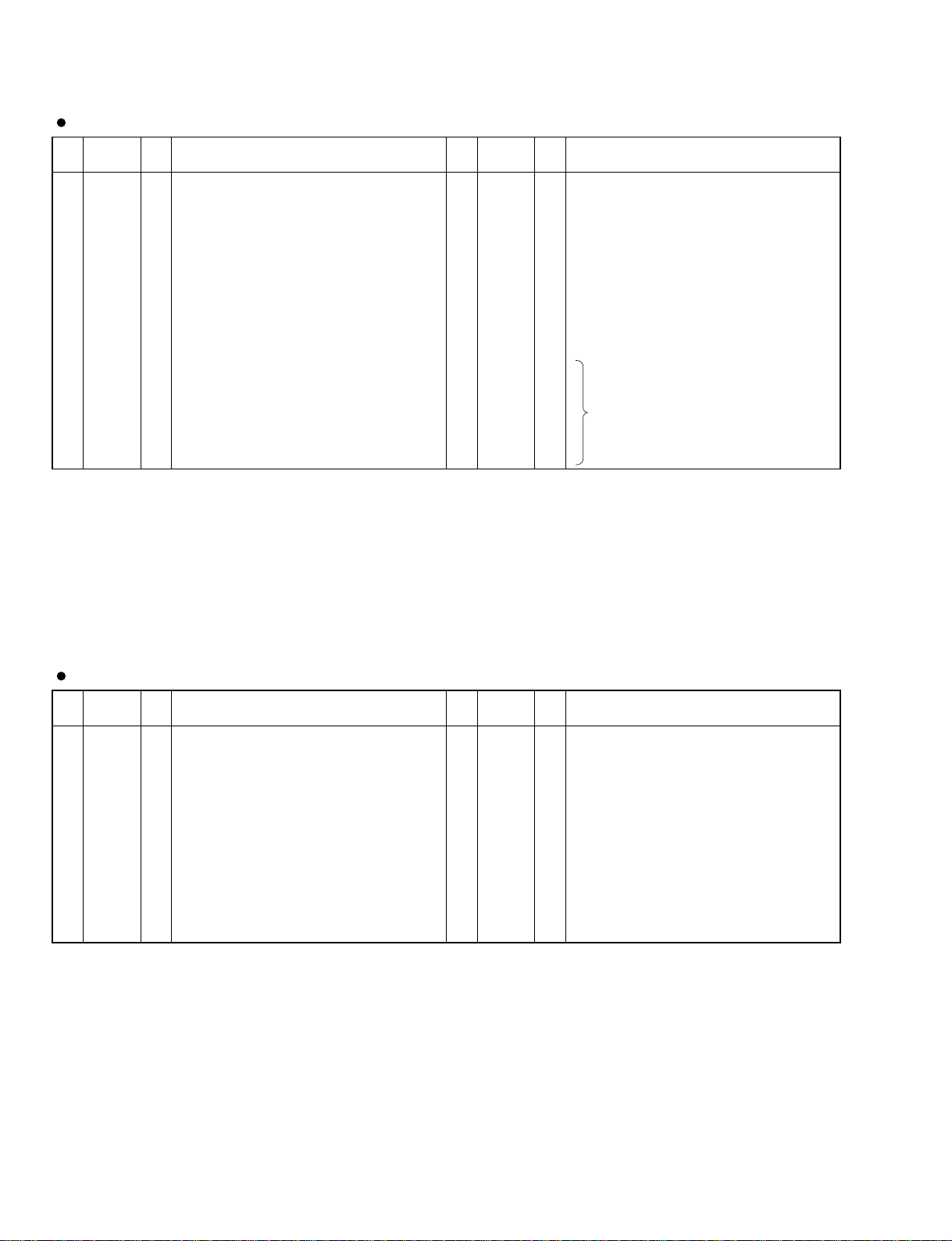

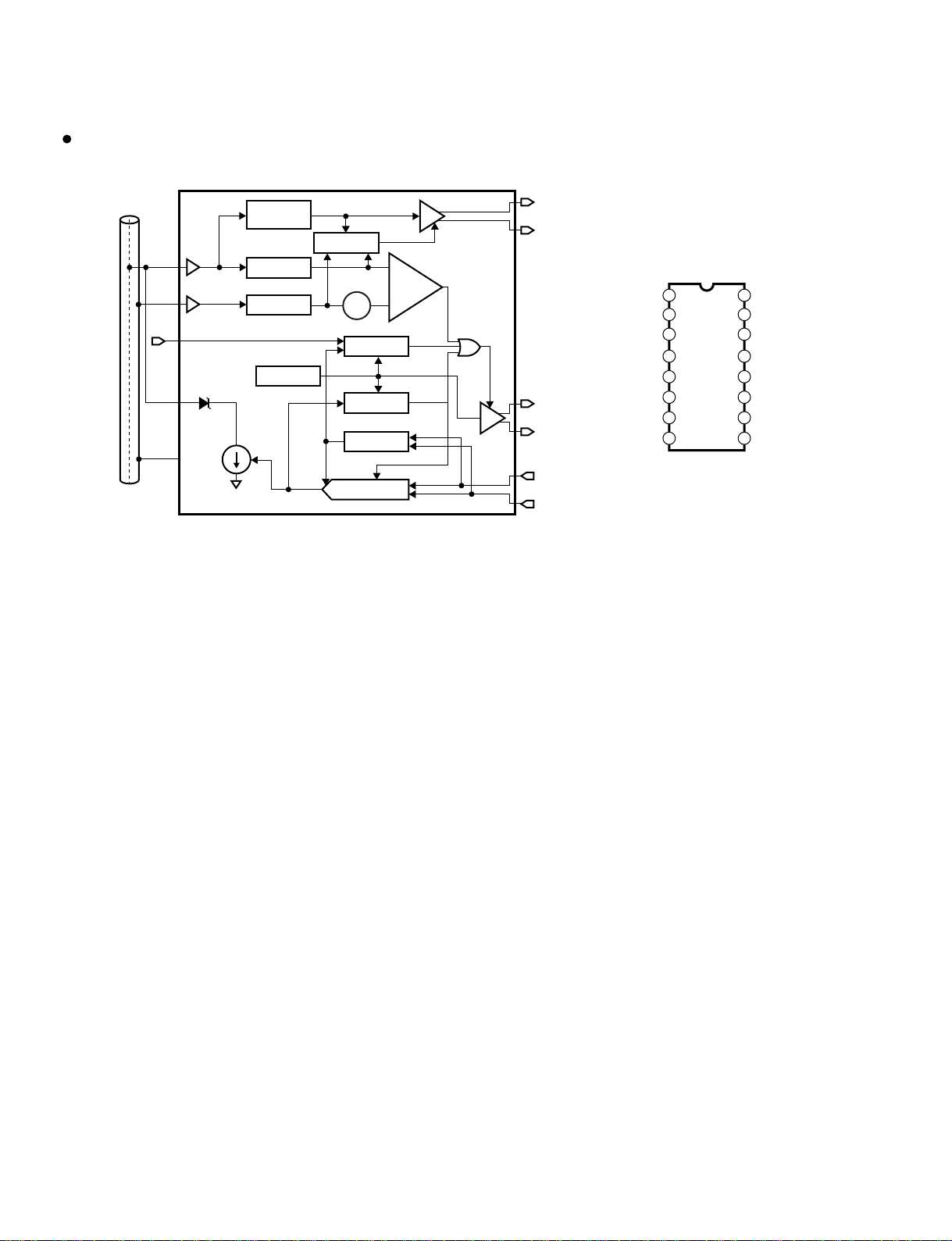

SN75C1168N (XU463A00)

Line Driver / Receiver

JK5: IC101

DS26C32ATMX (XU815A00)

Quad Differential Line Receiver

JK1:

JK2:

JK3:

JK4:

1

2

3

4

5

6

7

INPUT A

INPUT A

OUTPUT A

OUTPUT C

INPUT C

INPUT C

GND

ENABLE

16

15

14

13

12

11

Vcc

INPUT B

INPUT B

OUTPUT B

ENABLE

OUTPUT D

INPUT D

8

9

10

INPUT D

+

-

-

+

+

-

+

AM26LS31CNSR (XU996A00)

Quad Line Driver

JK1:

JK2:

JK3:

JK4:

1

2

3

4

5

6

7

1A

1Y

1Z

2Z

2Y

2A

GND

ENABLE G

16

15

14

13

12

11

Vcc

4A

4Y

4Z

ENABLE G

3Z

3Y

8

9

10

3A

H= high level

L= low level

X= irrelevant

Z= high impedance (off)

OUTPUTSENABLESINPUT

A

GGYZ

H

H

X

X

L

X

X

L

L

H

H

L

H

L

Z

L

H

L

H

Z

H

L

H

L

X

µPC319C (IG086700)

Voltage Comparator

JK5: IC100

NJM2082M (T1) (XN797A00)

NJM4560D (IG040000)

Dual Operational Amplifier

EMB:

JK5:

1

2