XICOR XM28C010PMHR-90, XM28C010PMHR-70, XM28C010PMHR-20, XM28C010PMHR-15, XM28C010PMHR-12 Datasheet

...

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 Megabit Puma Module |

XM28C010P |

32K x 32 Bit |

|

High Speed 5 Volt Byte Alterable Nonvolatile Memory Array

FEATURES

•High Speed, High Density Memory Module

—150ns, 120ns, 90ns and 70ns Access Times Available

—1 Megabit Memory in 1 square inch.

•Flexible Multiplane Architecture

—Four Separate Chip Selects

—32 Separate I/Os

•User Configurable I/Os—x8, x16, or x32

•User Configurable Page Size—64 Doublewords, 128 Words, or 256 Bytes

—Concurrent Read/Write Operations

•Able to Continue Reading During a Nonvolatile Write Cycle.

•5 Volt Byte or Page Alterable

—No Erase Before Write

•Software Data Protection

•Early End of Write Polling

—DATA Polling

—Toggle Bit Polling

•High Reliability

—Endurance: 100,000 Cycles

—Data Retention: 100 Years

DESCRIPTION

The XM28C010P is a high speed, high density CMOS byte alterable nonvolatile memory array constructed on a co-fired ceramic substrate using Xicor’s High Speed 32K x 8 components in 32-pad leadless chip carriers. The Substrate is a 66-pin ceramic pin grid array.

The module is configured with four separate chip enable and write enable inputs and 32 separate I/Os. This, along with the small footprint, provides the end user with a large degree of flexibility in board layout and memory configuration. In addition, with the large number of pins and the growth path being implemented, the module will be able to grow to 16 megabits.

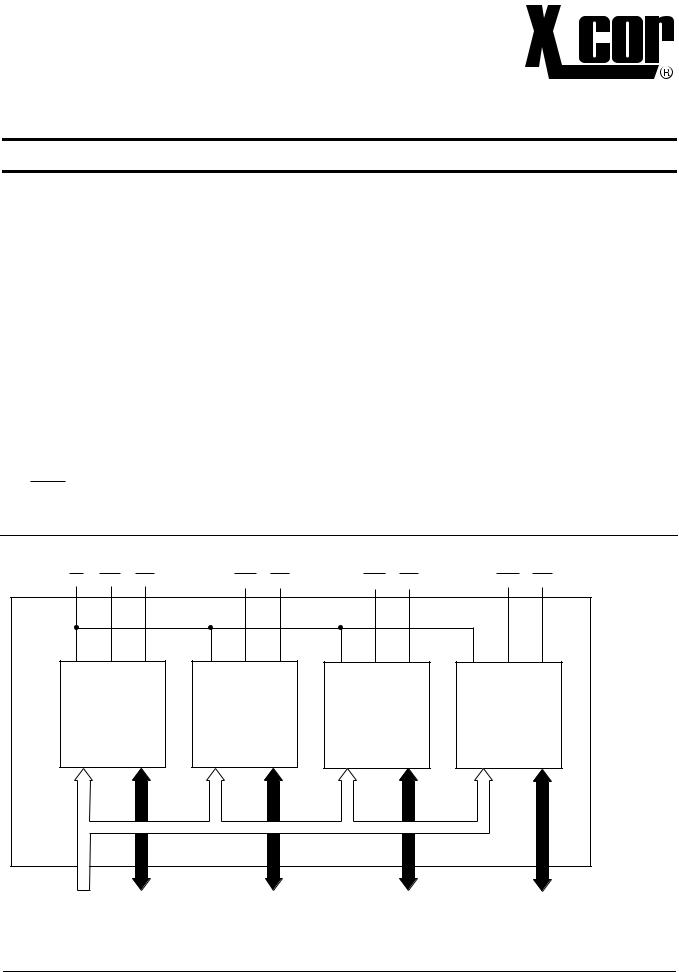

FUNCTIONAL DIAGRAM

OE |

WE1 |

CE1 |

WE2 |

CE2 |

WE3 |

CE3 |

WE4 |

CE4 |

|

|

|

32k x 8 |

|

32k x 8 |

|

32k x 8 |

|

32k x 8 |

|

|

|

A0–A15 |

I/O0–I/O7 |

I/O8–I/O15 |

I/O16–I/O23 |

I/O24–I/O31 |

6491 ILL F01 |

|||||

Xicor, 1995, 1996 Patents Pending |

1 |

Characteristics subject to change without notice |

6491-1.3 8/12/97 T0/C2/D0 NS

Loading...

Loading...