Page 1

5

4

3

2

1

D D

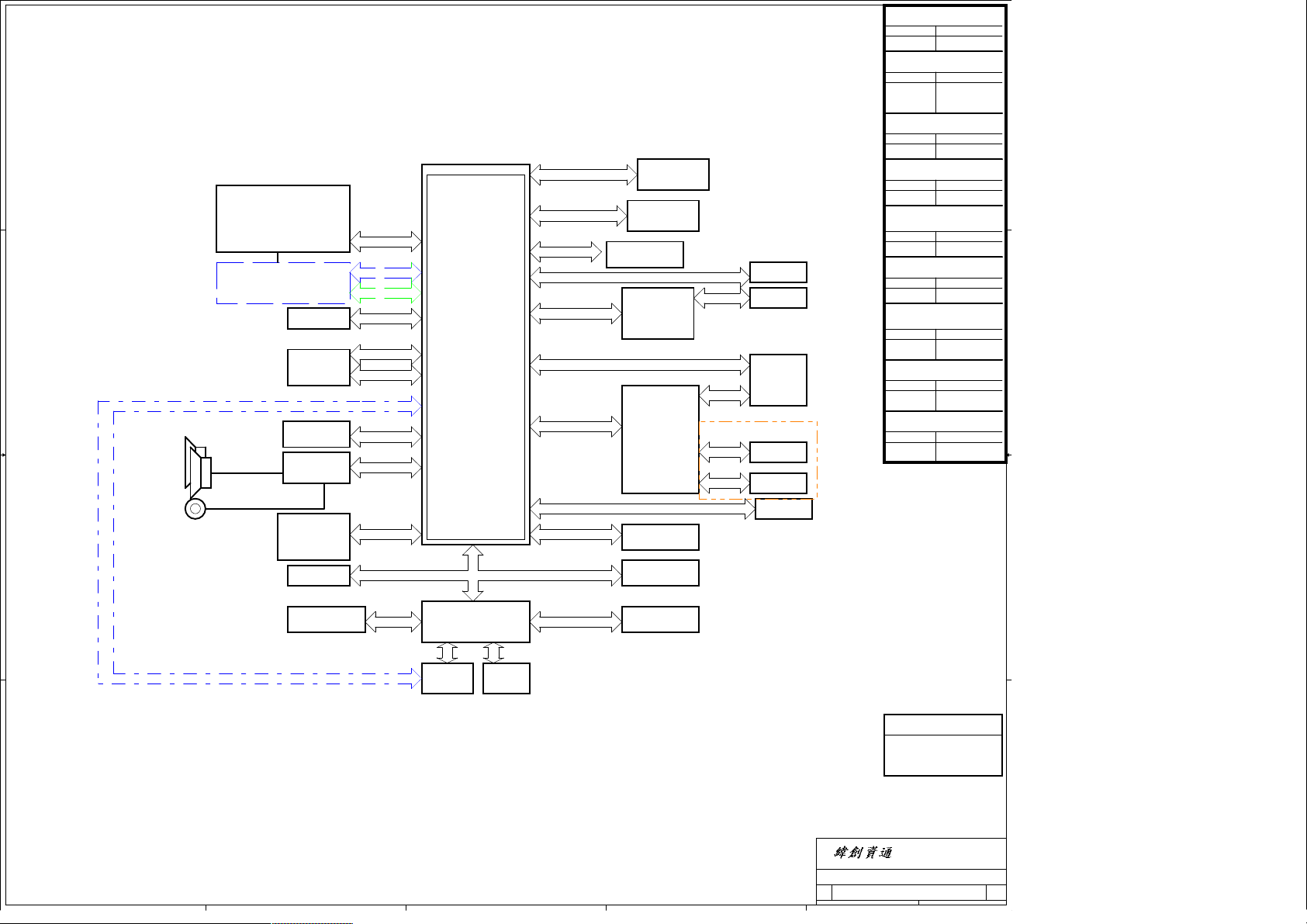

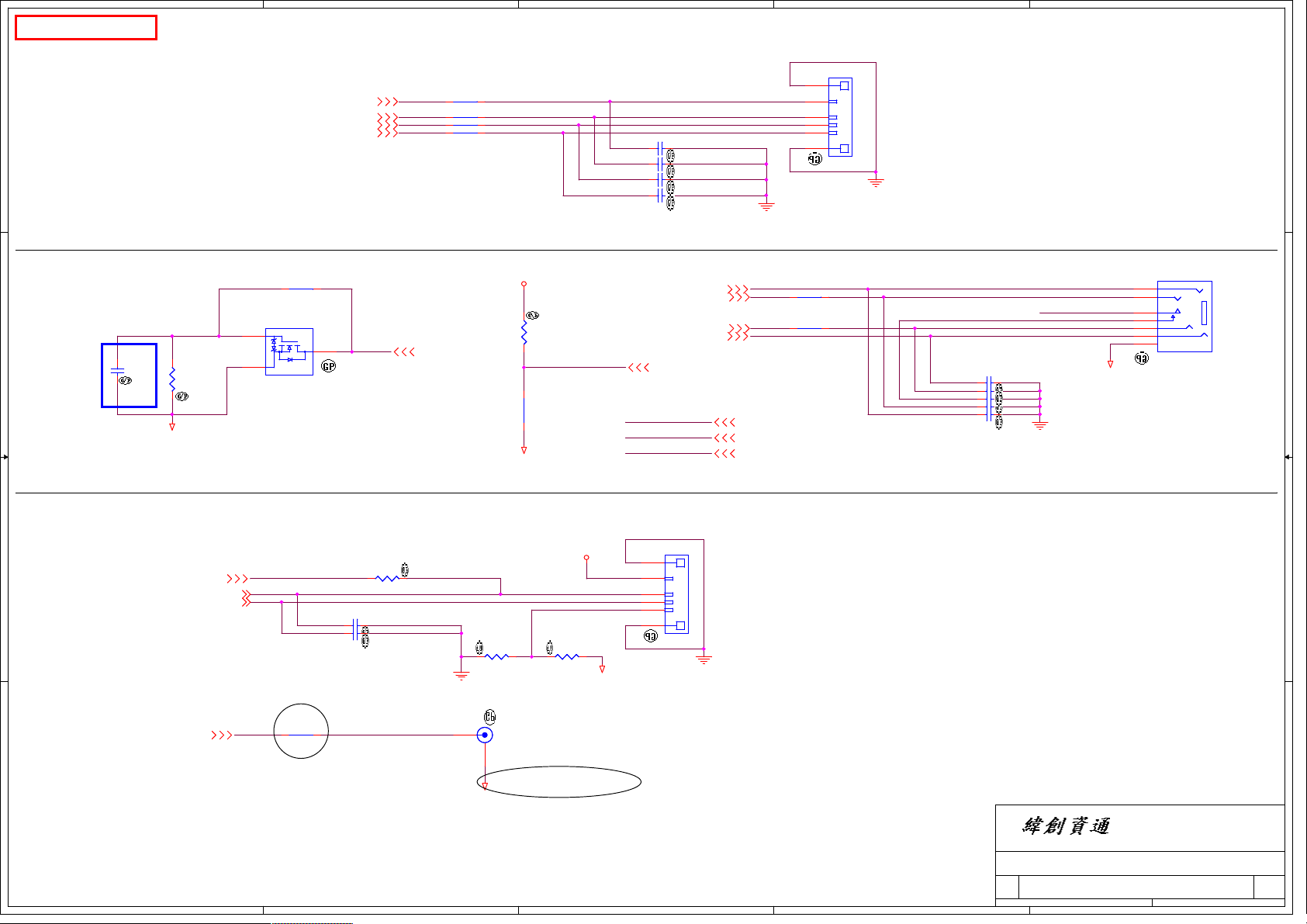

Schematics Document

C C

Domino_BA

B B

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

A A

5

4

3

2

application without get Wistron permission

<Variant Name>

<Variant Name>

<Variant Name>

stron Corporation

stron Corporation

stron Corporation

Wi

Wi

Wi

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Ti

tle

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

Date: Sheet

Date: Sheet

Date: Sheet

Co

Co

Co

Do

Do

Do

Taipei Hsien 221, Taiwan, R.O.C.

ver Page

ver Page

ver Page

mino

mino

mino

1

of

11

of

11

of

11

-1

-1

-1

02

02

02

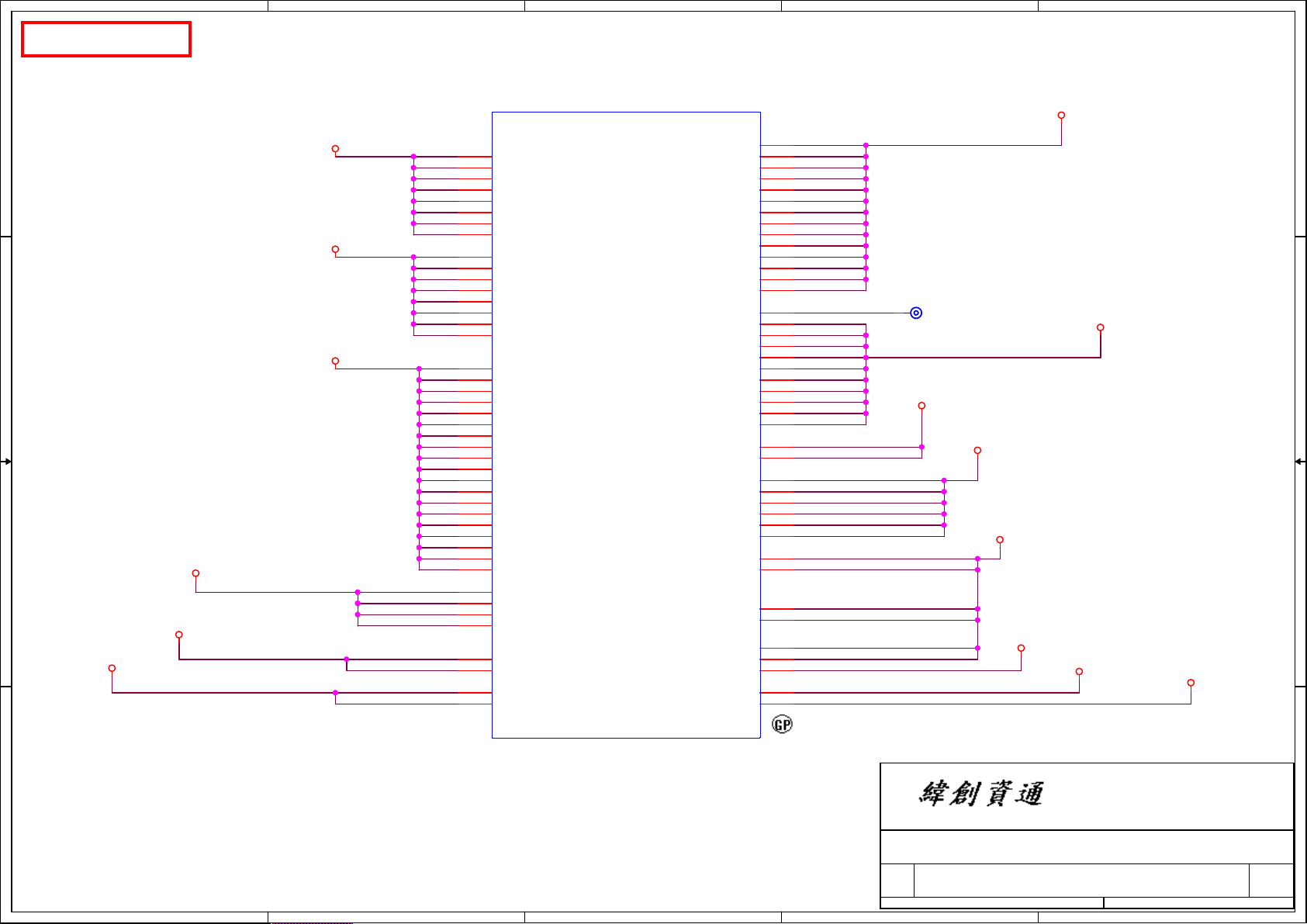

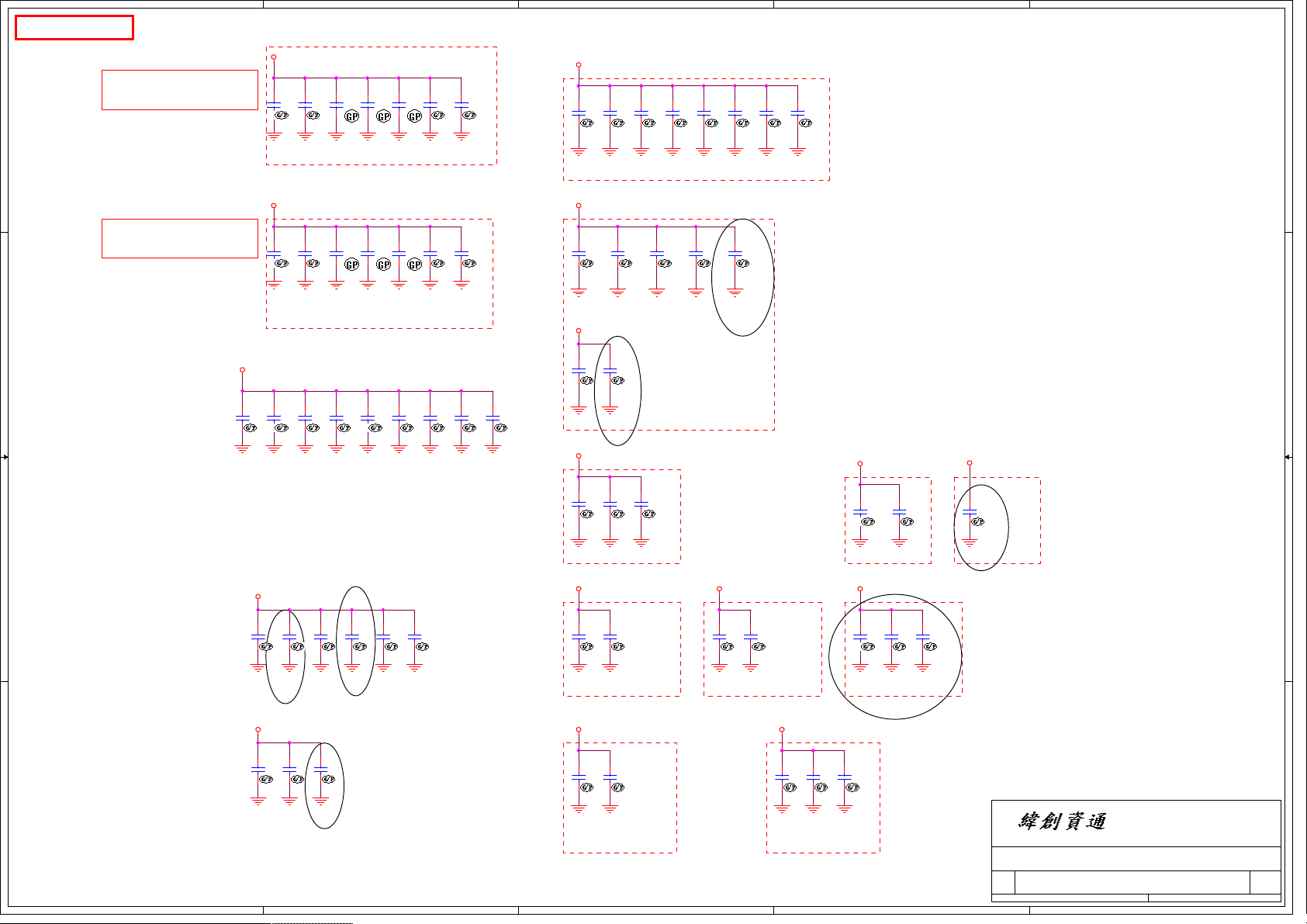

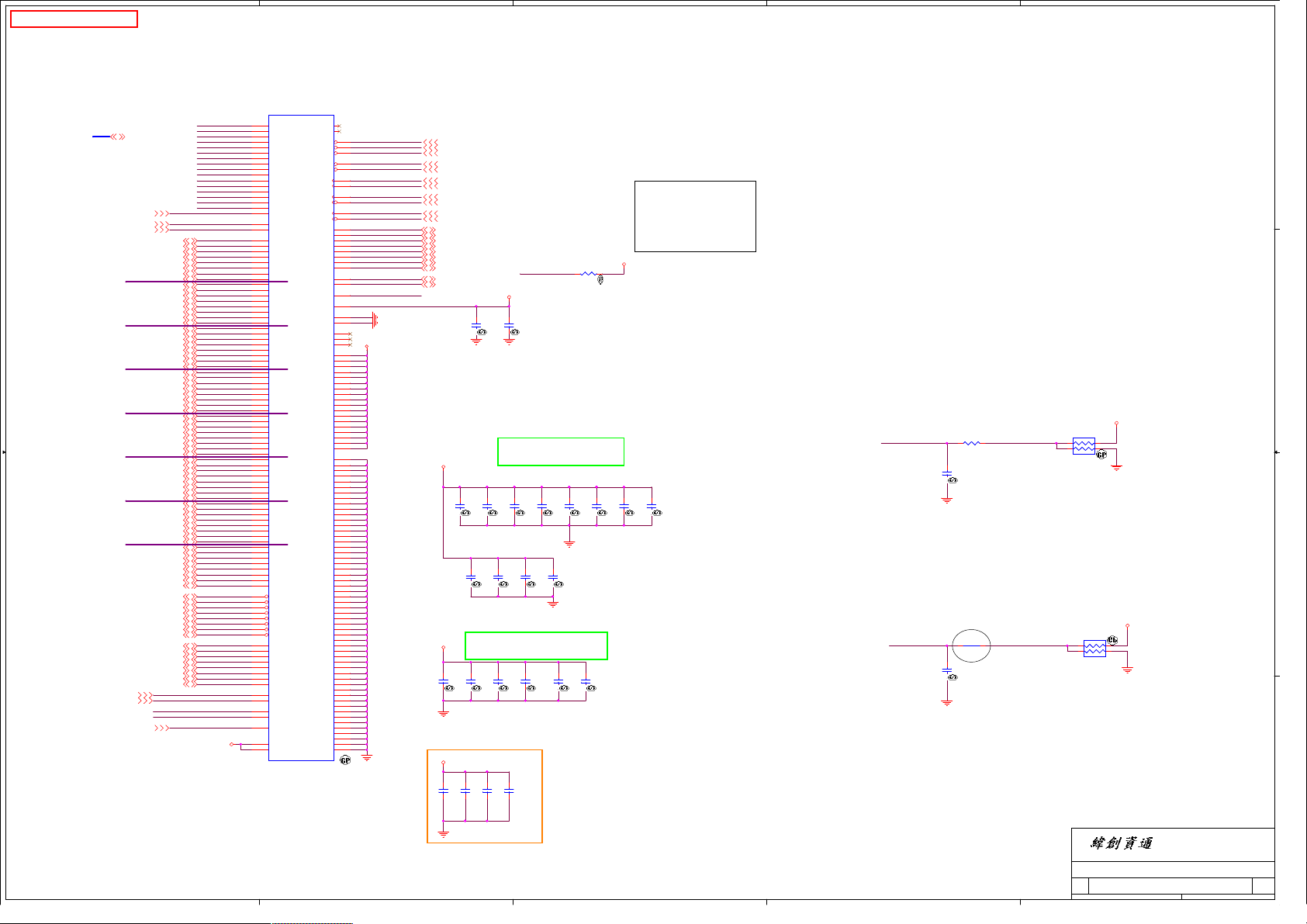

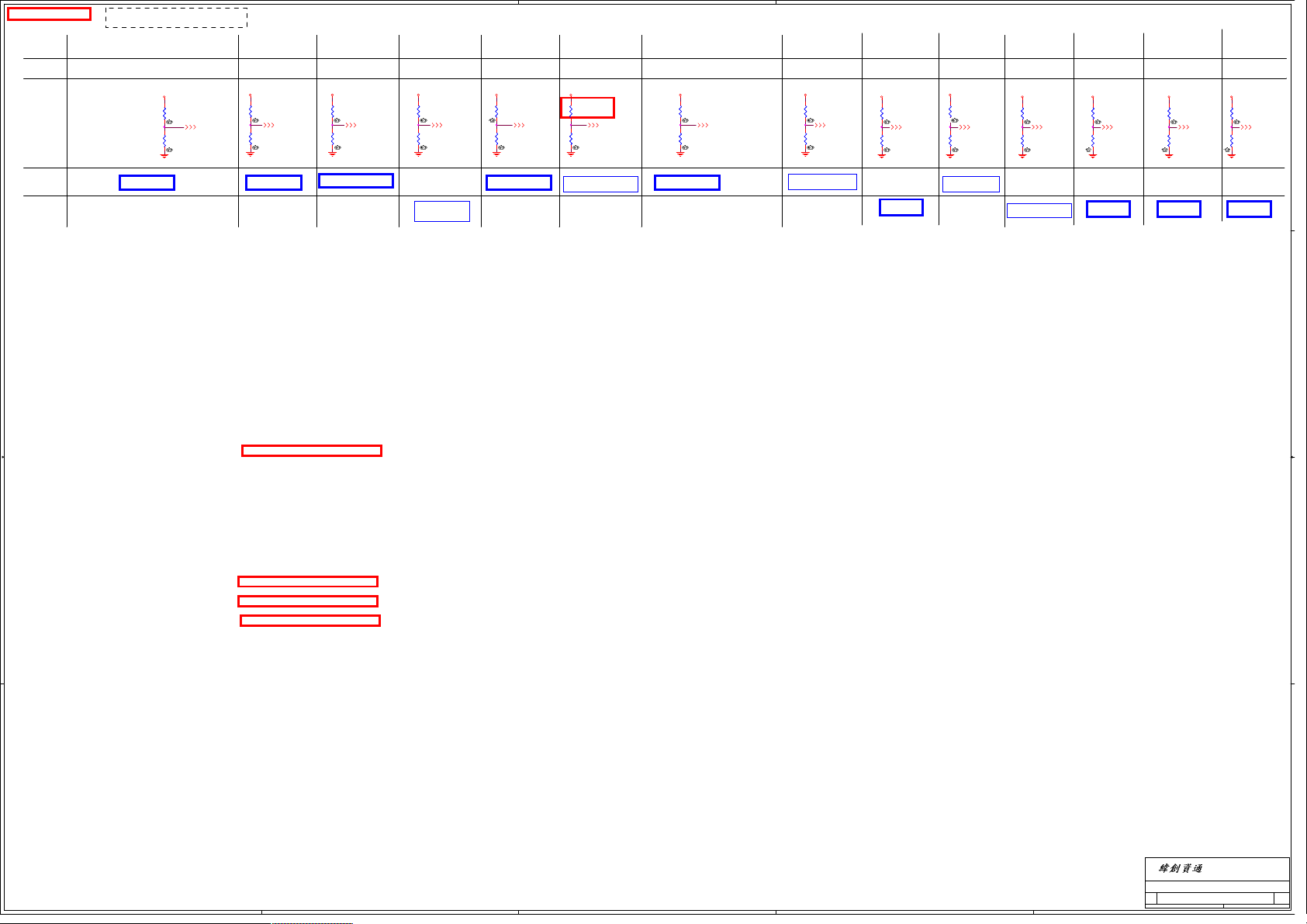

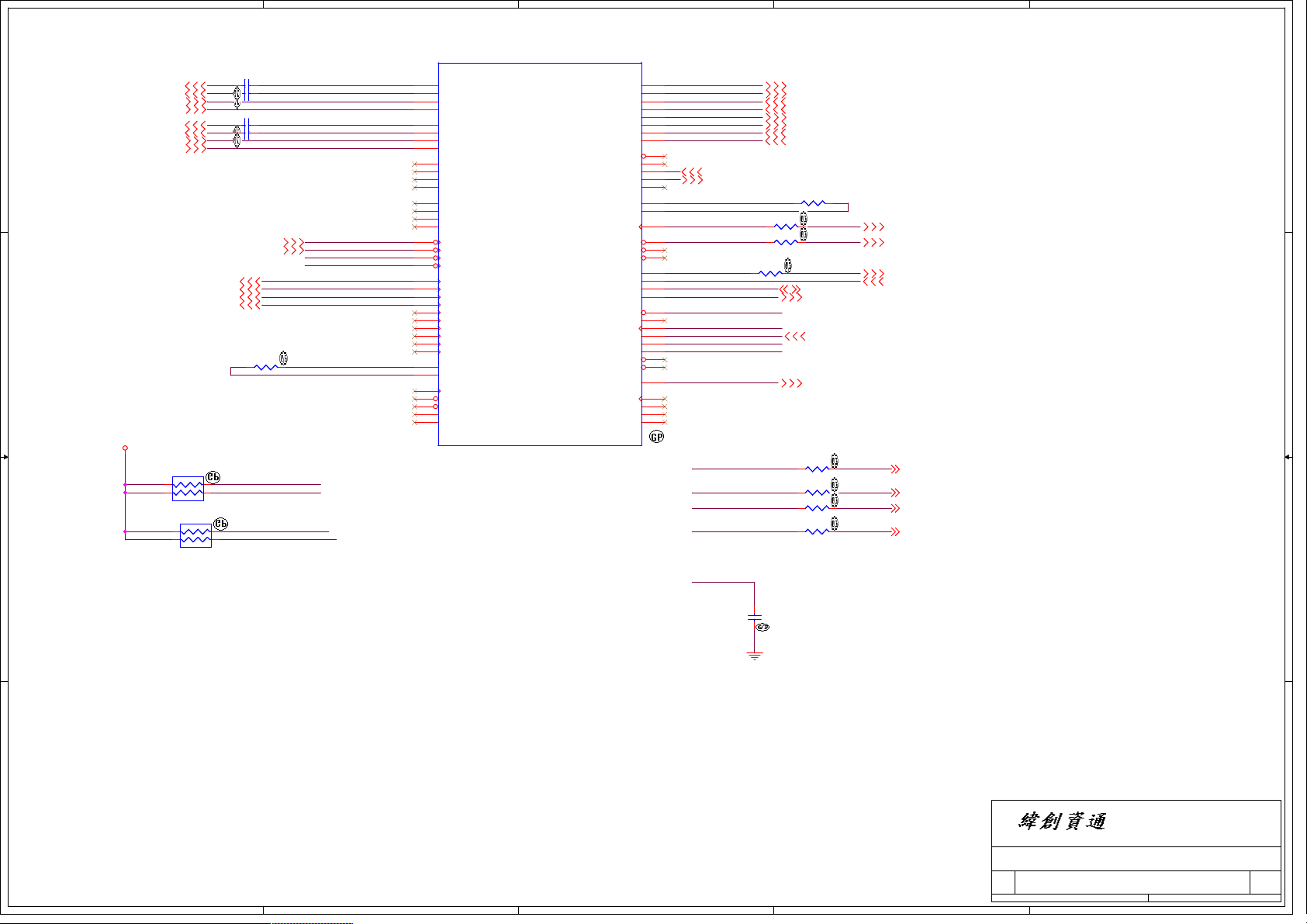

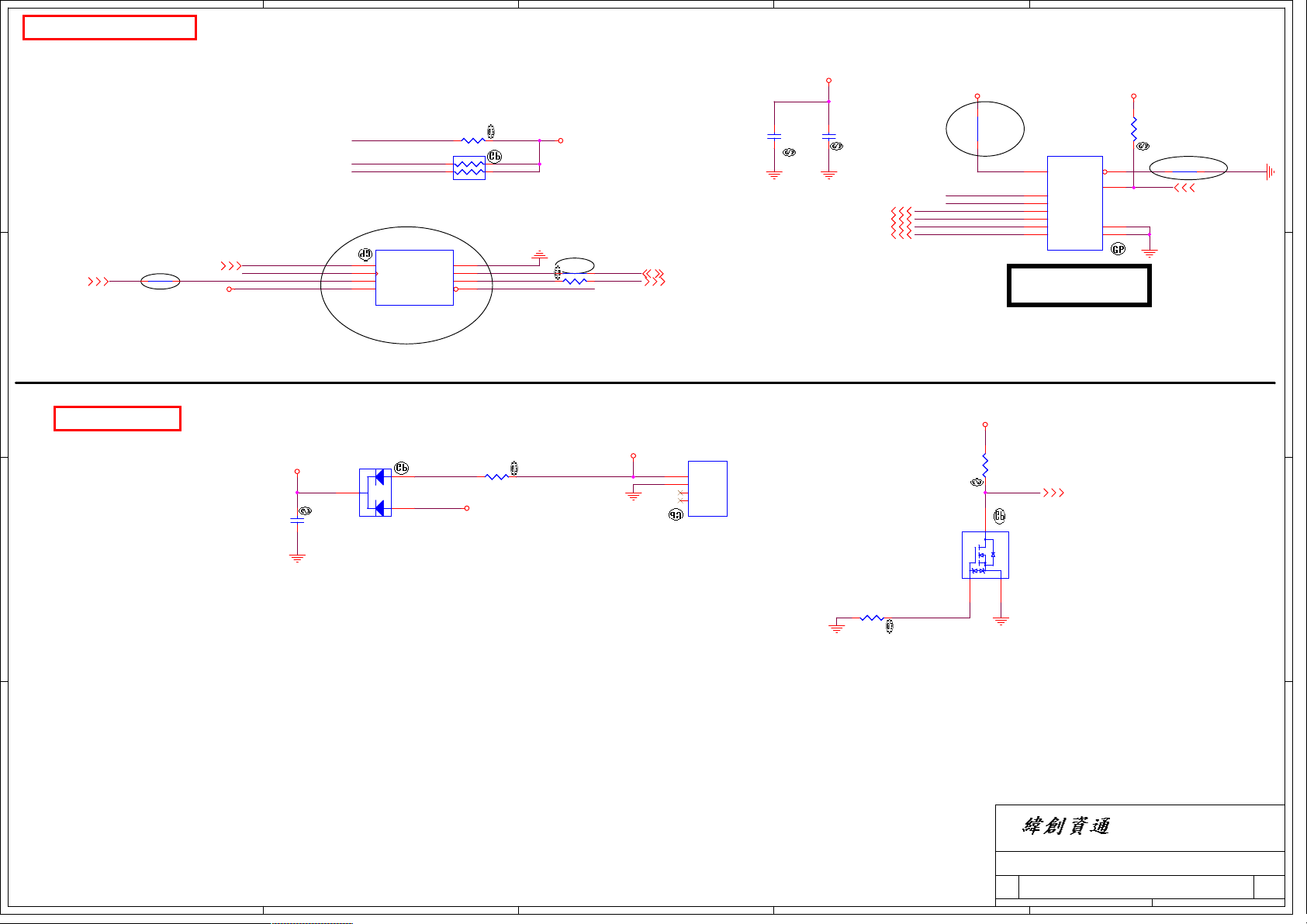

Page 2

5

Do

D D

D 15"

LC

15.6 WXGA (1366x768) Glare

To

uch Panel

C C

C for Precision Touchpad

I2

2CH

SPEAKER

ternal MIC

Ex

Headphone

B B

4

3

mino_BA Board Block Diagram

C

I2

3L/ 1.35V

DDR

DDR

3L 1333MHz Channel A

MC

eM

US

B2.0 x 1

Ie x 1

PC

PC

Ie x 1

US

B2.0 x 1

US

B2.0

TA PORT0

SA

LPC

BUS

HD

MI 1.4a

US

B3.0/2.0

ODD

HD

Audio Codec

ALC255

SPI Flash

MX

25U6473FM2I

-10G-GP

8M

B

TPM

In

tel CPU

P

eD

52

C x1

I2

B2.0x1

US

52

MI

HD

54

B2.0

US

US

B3.0

34

TA PORT1

SA

56

Audio

HD

27

I

SP

25

LPC

BUS

88

Br

aswell

A15

FCBG

ckage

Pa

25*27

US

B 3.0 (4)/2.0 (5)/HSIC ports (2)

ETHERNET (10/100/1000Mb)

High Definition Audio

LPC I/F

5,7,8,9,10,

11,12,15,16,18,19,21

G

Sensor

BMA250E

DDR

3L-1333

Slot 1

8G

MC

eM

N

LA

altek

Re

RTL8111H

USB 2.0 HUB

2.0 por

ts(4)

GL850G

HD

D

SA

TA2.0 (3G b/s, 300MB/s )

LPC

debug port

2

oject code : 4PD053010001

Pr

PCB P/N : 14285

Revision : -1

70

12

57

30

US

B2.0 x 1

B2.0 x 1

US

US

B2.0 x 1

35

56

65

B2.0

US

RJ

45

Mini-Card

WLAN & BT

comb module

US

B2.0

all Board

sm

Ca

rd reader

mera

Ca

1

CHARGER

HPA02224

INPUTS

DCBATOUT

SYSTEM DC/DC

RT6575D

INPUTS

5V_S5

DCBATOUT

3D3V_S5

CPU DC/DC

NCP81201MNTXG

INPUTS

DCBATOUT

CPU DC/DC

NCP81201MNTXG

INPUTS

DCBATOUT

SYSTEM DC/DC

TPS51716

INPUTS

DCBATOUT

SYSTEM DC/DC

34

31

58

63

63

52

TPS51716

INPUTS

1D35V_CPU_VDDQ_S3

DCBATOUT

SYSTEM LDO

S-1339D15

INPUTS

3D3V_S5

SYSTEM LDO

RT9043GB

INPUTS

1D8V_S5

SYSTEM DC/DC

RT8068AZQWID

INPUTS

3D3V_S5

OUTPUTS

BT+

OUTPUTS

46-47

OUTPUTS

1V_CPU_CORE

48

OUTPUTS

GFX_CORE

OUTPUTS

1D05V_S5

OUTPUTS

OUTPUTS

1D5V_S0

OUTPUTS

1D24V_S5

OUTPUTS

1D8V_S5

44

45

50

49

51

51

51

To

uch PAD

PS2

KBC

CE985PB

NP

Ch

Bus

SM

24

t.

In

KB

6262

HP

arger

A02224R

44

Th

ermal

_IN1 / 2

VD

I2C for Precisio n Touchpad

D

VI

26

PCB LAYER

L4:Signal

L1:Top

L5:GND

L2:VCC

L6:Bottom

L3:Signal

A A

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

Wi

Wi

Wi

stron Corporation

stron Corporation

stron Corporation

, 88, Sec.1, Hsin Tai Wu Rd., Hsich ih,

, 88, Sec.1, Hsin Tai Wu Rd., Hsich ih,

, 88, Sec.1, Hsin Tai Wu Rd., Hsich ih,

21F

21F

21F

Taipei Hs ien 221, Taiwan, R.O.C.

Taipei Hs ien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Cu

Cu

Cu

stom

stom

stom

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Taipei Hs ien 221, Taiwan, R.O.C.

ock Diagram

ock Diagram

ock Diagram

Bl

Bl

Bl

Do

Do

Do

mino

mino

mino

1

-1

-1

2102

2102

2102

-1

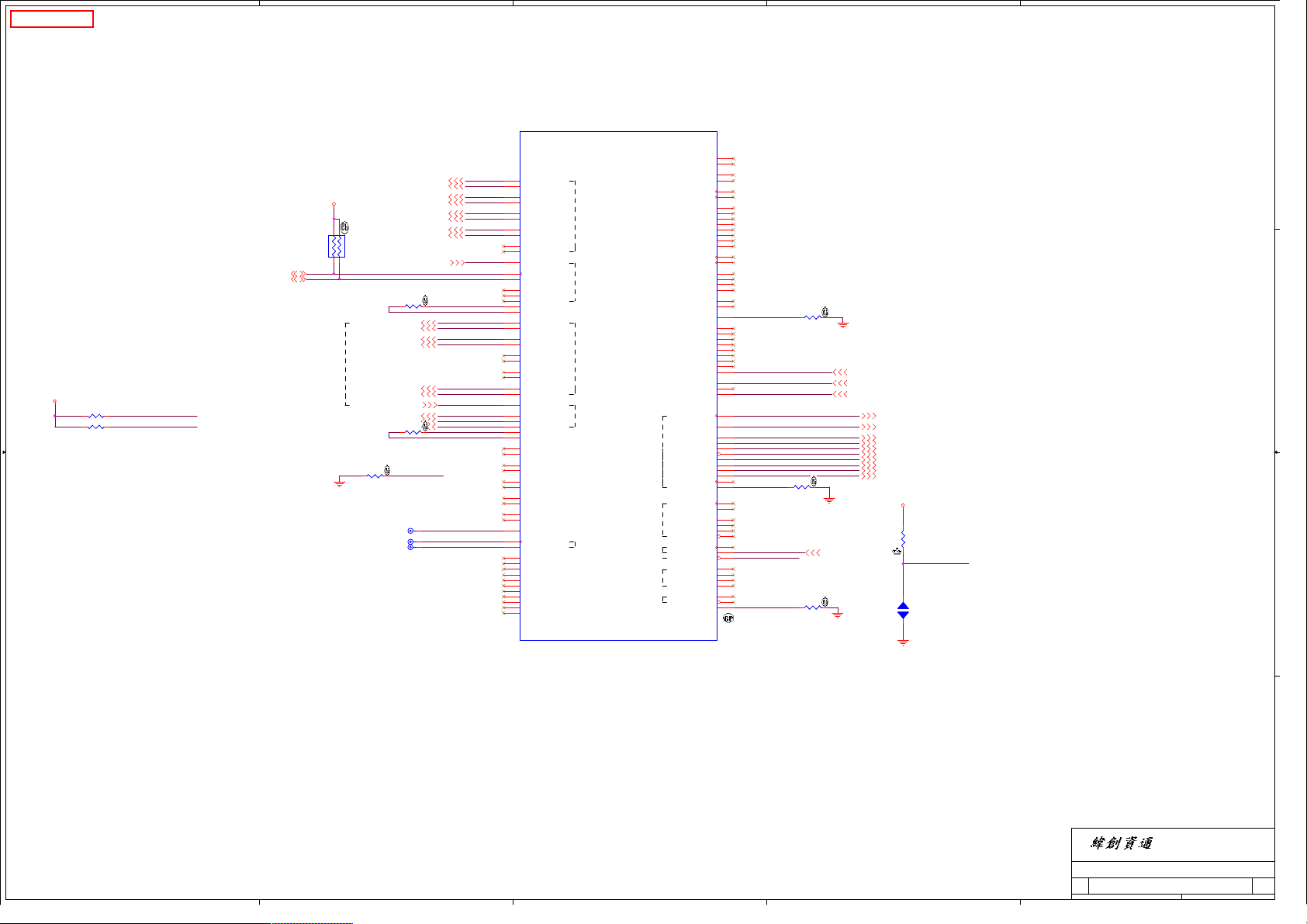

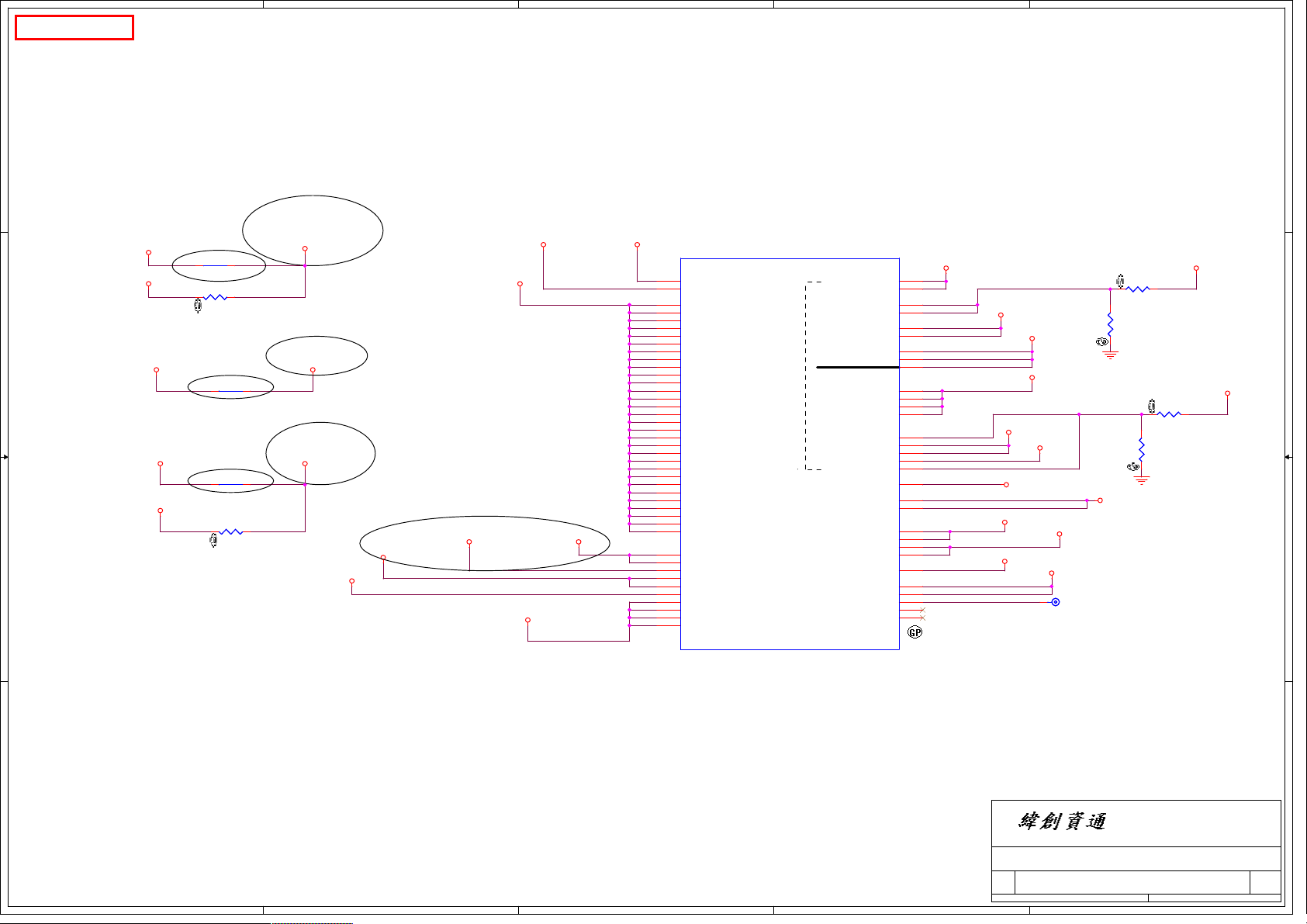

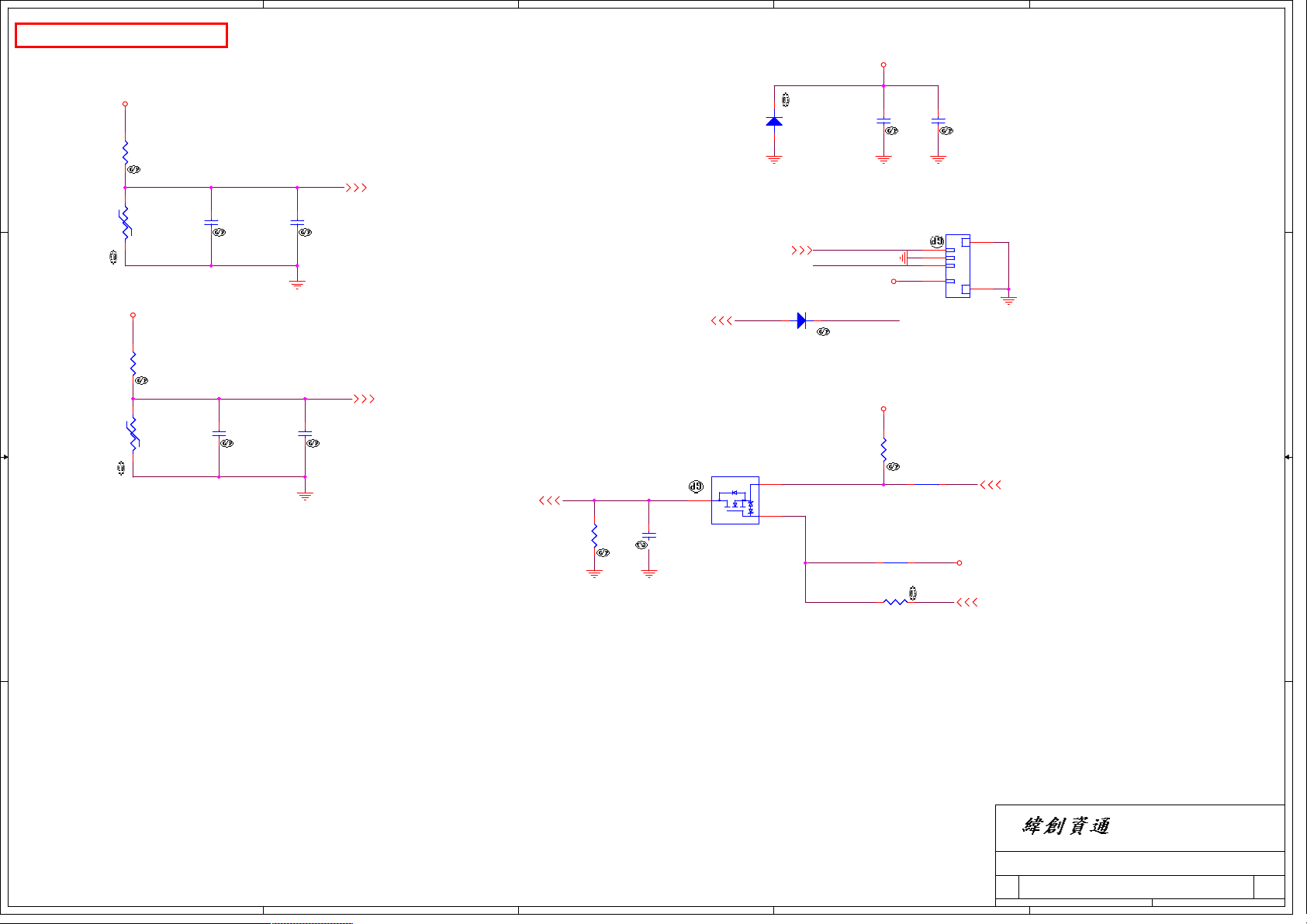

Page 3

5

4

3

2

1

SSID = CPU

D D

C C

Blanking

B B

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

<Variant Name>

<Variant Name>

<Variant Name>

A A

Title

Title

Ti

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

application without get Wistron permission

tron Corporation

tron Corporation

tron Corporation

Wis

Wis

Wis

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F,

21F,

21F,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

eserved)

eserved)

eserved)

(R

(R

(R

mino

mino

mino

Do

Do

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

2

Do

-1

-1

-1

02

02

31

31

31

of

of

of

1

02

Page 4

5

4

3

2

1

SSID = CPU

D D

C C

Blanking

B B

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

<Variant Name>

<Variant Name>

<Variant Name>

A A

Title

Title

Ti

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

application without get Wistron permission

tron Corporation

tron Corporation

tron Corporation

Wis

Wis

Wis

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F,

21F,

21F,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

eserved)

eserved)

eserved)

(R

(R

(R

mino

mino

mino

Do

Do

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

2

Do

-1

-1

-1

02

02

41

41

41

of

of

of

1

02

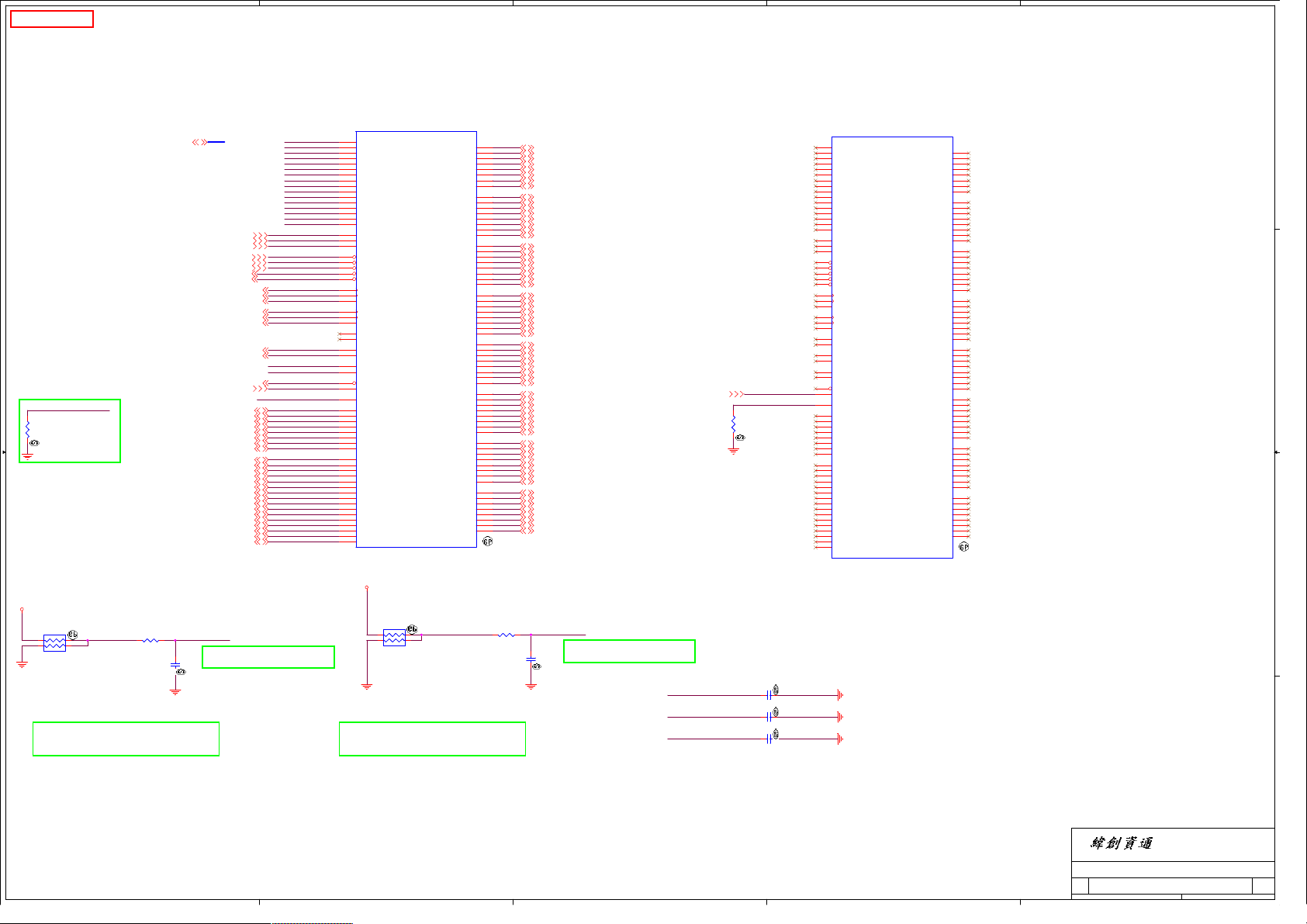

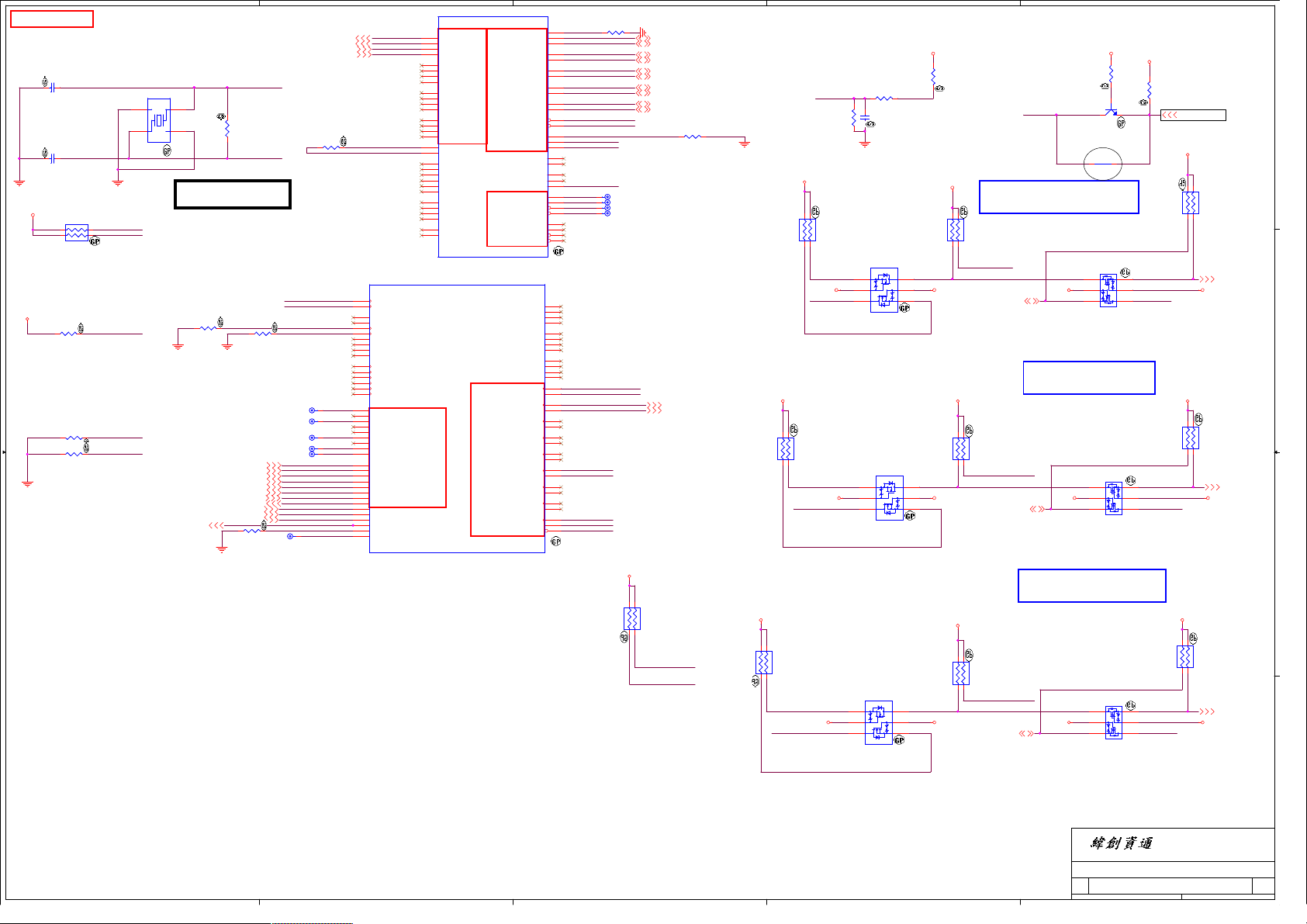

Page 5

SSID = CPU

5

4

3

2

1

D D

M_

SM

_RCOMP_0

A_A15

A_A14

M_

A_A13

M_

M_

A_A12

A_A11

M_

M_

A_A10

A_A9

M_

M_

A_A8

A_A7

M_

A_A6

M_

M_

A_A5

M_

A_A4

M_

A_A3

A_A2

M_

M_A_A1

A_A0

M_

V_SM_VREF_CNT

M_

VREF_DQ_DIM0

M_

A_A[15:0]12

A_BS212

M_

M_

A_BS112

M_

A_BS012

A_CAS#12

M_

M_

A_RAS#12

A_WE#12

M_

A_CS#112

M_

M_

A_CS#012

M_

A_CLK112

M_

A_CLK#112

M_

A_CKE112

A_CLK012

M_

M_

A_CLK#012

A_CKE012

M_

C C

SM

_RCOMP_0

12

R504

R504

182R2F-GP

182R2F-GP

Layout Note: Close CPU

B B

1D35V_CPU_VDDQ _S3

DY

DY

01

01

RN5

RN5

2 3

1

SRN4K7J-8-GP

SRN4K7J-8-GP

PLACE TWO 4.7K RESISTORS CLOSE TO CPU TO

CPU PINS ON M_VREF ROUTE THE VREF POWER

SIGNALS WITH THICK TRACES

M_OCAVREF_R

DRA

4

DY

DY

R506

R506

0R2J-2-GP

0R2J-2-GP

12

12

DY

DY

A_DIM0_ODT012

M_

M_

A_DIM0_ODT112

SM

_DRAMRST#12

_DRAM_PWROK36,86

DDR3

A_DM712

M_

M_

A_DM612

M_

A_DM512

M_

A_DM412

M_

A_DM312

A_DM212

M_

M_

A_DM112

A_DM012

M_

M_

A_DQS_DP712

M_A_DQS_DN712

A_DQS_DP612

M_

A_DQS_DN612

M_

M_

A_DQS_DP512

A_DQS_DN512

M_

A_DQS_DP412

M_

A_DQS_DN412

M_

A_DQS_DP312

M_

A_DQS_DN312

M_

M_

A_DQS_DP212

A_DQS_DN212

M_

A_DQS_DP112

M_

M_

A_DQS_DN112

M_

A_DQS_DP012

M_

A_DQS_DN012

SM_VREF_CNT

V_

NOTE:

01

01

C5

C5

SC

SC

PLACE 0.1U CAP CLOSE TO CPU

D1U16V2KX-L-GP

D1U16V2KX-L-GP

U1A

U1A

CP

CP

BD49

DDR3

_M0_MA_15

BD47

DDR3_M0_MA_14

BF44

DDR3

BF48

DDR3

BB49

DDR3

BJ45

DDR3

BE52

DDR3

BD44

DDR3

BE46

DDR3

BB46

DDR3

BH48

DDR3

BD42

DDR3

BH47

DDR3

BJ48

DDR3

BC42

DDR3

BB47

DDR3

BF52

DDR3

AY40

DDR3

BH46

DDR3

BG45

DDR3

BA40

DDR3

BH44

DDR3

AU38

DDR3

AY38

DDR3

BD38

DDR3

BF38

DDR3

AY42

DDR3

BD40

DDR3

BF40

DDR3

BB44

DDR3

AT30

RS

AU30

RS

AV36

DDR3

BA38

DDR3_M0_ODT_1

AT28

DDR3

AU28

DDR3

BA42

DDR3

AV28

DDR3

BA28

DDR3

BH30

DDR3

BD32

DDR3

AY36

DDR3

BG41

DDR3

BA53

DDR3

AP44

DDR3

AT48

DDR3

AP52

DDR3

BH32

DDR3

BG31

DDR3

BC30

DDR3

BC32

DDR3

AT32

DDR3_M0_DQS_5

AT34

DDR3_M0_DQSB_5

BH40

DDR3

BG39

DDR3_M0_DQSB_4

AY52

DDR3_M0_DQS_3

BA51

DDR3

AT42

DDR3

AT41

DDR3

AV47

DDR3

AV48

DDR3

AM52

DDR3

AM51

DDR3

BRASW

BRASW

071.BRASW.000U

071.BRASW.000U

1D

35V_CPU_VDDQ_S3

PLACE TWO 4.7K RESISTORS CLOSE TO CPU TO

CPU PINS ON M_VREF ROUTE THE VREF POWER

SIGNALS WITH THICK TRACES

_M0_MA_13

_M0_MA_12

_M0_MA_11

_M0_MA_10

_M0_MA_9

_M0_MA_8

_M0_MA_7

_M0_MA_6

_M0_MA_5

_M0_MA_4

_M0_MA_3

_M0_MA_2

_M0_MA_1

_M0_MA_0

_M0_BS_2

_M0_BS_1

_M0_BS_0

_M0_CAS#

_M0_RAS#

_M0_WE#

_M0_CS1#

_M0_CS0#

_M0_CK_1

_M0_CK_1#

_M0_CKE_1

_M0_CK_0

_M0_CK_0#

_M0_CKE_0

VD#AT30

VD#AU30

_M0_ODT_0

_M0_OCAVREF

_M0_ODQVREF

_M0_DRAMRST#

_DRAM_PWROK

_M0_RCOMPPD

_M0_DM_7

_M0_DM_6

_M0_DM_5

_M0_DM_4

_M0_DM_3

_M0_DM_2

_M0_DM_1

_M0_DM_0

_M0_DQS_7

_M0_DQSB_7

_M0_DQS_6

_M0_DQSB_6

_M0_DQS_4

_M0_DQSB_3

_M0_DQS_2

_M0_DQSB_2

_M0_DQS_1

_M0_DQSB_1

_M0_DQS_0

_M0_DQSB_0

ELL-GP

ELL-GP

RN5

RN5

2 3

1

SRN4K7J-8-GP

SRN4K7J-8-GP

DDR0

DDR0

DY

DY

02

02

BRASWELL

BRASWELL

4

1 OF 13

1 OF 13

DDR3_M0_DQ_63

DDR3

_M0_DQ_62

_M0_DQ_61

DDR3

_M0_DQ_60

DDR3

DDR3

_M0_DQ_59

DDR3

_M0_DQ_58

DDR3

_M0_DQ_57

_M0_DQ_56

DDR3

_M0_DQ_55

DDR3

DDR3

_M0_DQ_54

DDR3

_M0_DQ_53

DDR3

_M0_DQ_52

DDR3

_M0_DQ_51

_M0_DQ_50

DDR3

DDR3

_M0_DQ_49

_M0_DQ_48

DDR3

DDR3

_M0_DQ_47

DDR3_M0_DQ_46

_M0_DQ_45

DDR3

_M0_DQ_44

DDR3

DDR3

_M0_DQ_43

DDR3

_M0_DQ_42

DDR3

_M0_DQ_41

_M0_DQ_40

DDR3

DDR3

_M0_DQ_39

_M0_DQ_38

DDR3

DDR3

_M0_DQ_37

_M0_DQ_36

DDR3

DDR3

_M0_DQ_35

_M0_DQ_34

DDR3

_M0_DQ_33

DDR3

DDR3

_M0_DQ_32

DDR3

_M0_DQ_31

_M0_DQ_30

DDR3

DDR3_M0_DQ_29

_M0_DQ_28

DDR3

DDR3

_M0_DQ_27

DDR3

_M0_DQ_26

DDR3_M0_DQ_25

DDR3

_M0_DQ_24

DDR3

_M0_DQ_23

DDR3

_M0_DQ_22

DDR3

_M0_DQ_21

DDR3

_M0_DQ_20

_M0_DQ_19

DDR3

DDR3

_M0_DQ_18

_M0_DQ_17

DDR3

DDR3

_M0_DQ_16

DDR3

_M0_DQ_15

_M0_DQ_14

DDR3

_M0_DQ_13

DDR3

DDR3

_M0_DQ_12

_M0_DQ_11

DDR3

DDR3

_M0_DQ_10

_M0_DQ_9

DDR3

DDR3_M0_DQ_8

_M0_DQ_7

DDR3

DDR3_M0_DQ_6

DDR3_M0_DQ_5

_M0_DQ_4

DDR3

_M0_DQ_3

DDR3

_M0_DQ_2

DDR3

_M0_DQ_1

DDR3

_M0_DQ_0

DDR3

M_ODQVREF_R

DRA

BG33

BH28

BJ29

BG28

BG32

BH34

BG29

BJ33

BD28

BF30

BA34

BD34

BD30

BA32

BC34

BF34

AV32

AV34

BD36

BF36

AU32

AU34

BA36

BC36

BH38

BH36

BJ41

BH42

BJ37

BG37

BG43

BG42

BB51

AW53

BC52

AW51

AV51

BC53

AV52

BD52

AV42

AP41

AV41

AT44

AP40

AT38

AP42

AT40

AV45

AY50

AT50

AP47

AV50

AY48

AT47

AP48

AP51

AR53

AK52

AL53

AR51

AT52

AL51

AK51

DY

DY

R5

R5

07

07

0R2J-2-GP

0R2J-2-GP

DY

DY

12

A_DQ63 12

M_

M_

A_DQ62 12

A_DQ61 12

M_

M_

A_DQ60 12

A_DQ59 12

M_

M_

A_DQ58 12

A_DQ57 12

M_

A_DQ56 12

M_

M_

A_DQ55 12

M_

A_DQ54 12

A_DQ53 12

M_

M_A_DQ52 12

A_DQ51 12

M_

M_

A_DQ50 12

M_

A_DQ49 12

M_A_DQ48 12

A_DQ47 12

M_

M_

A_DQ46 12

M_

A_DQ45 12

M_

A_DQ44 12

M_

A_DQ43 12

A_DQ42 12

M_

M_

A_DQ41 12

A_DQ40 12

M_

M_

A_DQ39 12

M_

A_DQ38 12

A_DQ37 12

M_

A_DQ36 12

M_

M_

A_DQ35 12

A_DQ34 12

M_

M_

A_DQ33 12

A_DQ32 12

M_

A_DQ31 12

M_

A_DQ30 12

M_

M_

A_DQ29 12

M_A_DQ28 12

M_

A_DQ27 12

A_DQ26 12

M_

A_DQ25 12

M_

M_

A_DQ24 12

M_

A_DQ23 12

A_DQ22 12

M_

M_

A_DQ21 12

A_DQ20 12

M_

M_

A_DQ19 12

M_

A_DQ18 12

M_

A_DQ17 12

M_

A_DQ16 12

M_

A_DQ15 12

A_DQ14 12

M_

M_

A_DQ13 12

M_

A_DQ12 12

M_A_DQ11 12

A_DQ10 12

M_

A_DQ9 12

M_

M_

A_DQ8 12

A_DQ7 12

M_

A_DQ6 12

M_

A_DQ5 12

M_

A_DQ4 12

M_

M_

A_DQ3 12

A_DQ2 12

M_

A_DQ1 12

M_

M_

A_DQ0 12

VREF_DQ_DIM0

M_

NOTE:

12

C502

C502

SC

SC

PLACE 0.1U CAP CLOSE TO CPU

D1U16V2KX-L-GP

D1U16V2KX-L-GP

_VCCA_PWRGD36

DDR3

SM

_DRAMRST#

DDR3_DRAM_PWROK

_VCCA_PWRGD

DDR3

12

DRA

R5

R5

08

08

182R2F-GP

182R2F-GP

DY

DY

DY

DY

DY

DY

M_RCOMP_1

1 2

1 2

1 2

502

502

EC

EC

SCD1U25V2KX-GP

SCD1U25V2KX-GP

EC

EC

503

503

SCD1U25V2KX-GP

SCD1U25V2KX-GP

EC

EC

504

504

SCD1U25V2KX-GP

SCD1U25V2KX-GP

CPU1

CPU1

BD5

DDR3_M1_MA_15

BD7

DDR3

BF10

DDR3

BF6

DDR3

BB5

DDR3

BJ9

DDR3

BE2

DDR3

BD10

DDR3

BE8

DDR3

BB8

DDR3

BH6

DDR3

BD12

DDR3

BH7

DDR3

BJ6

DDR3

BC12

DDR3

BB7

DDR3

BF2

DDR3

AY14

DDR3

BH8

DDR3_M1_BS_0

BG9

DDR3

BA14

DDR3

BH10

DDR3

AU16

DDR3

AY16

DDR3

BD16

DDR3

BF16

DDR3

AY12

DDR3

BD14

DDR3

BF14

DDR3

BB10

DDR3

AT24

RS

AU24

RS

AV18

DDR3_M1_ODT_0

BA16

DDR3

AT26

DDR3

AU26

DDR3_M1_ODQVREF

BA12

DDR3

AV26

DDR3

BA26

DDR3

BH24

DDR3

BD22

DDR3

AY18

DDR3

BG13

DDR3

BA1

DDR3

AP10

DDR3

AT6

DDR3

AP2

DDR3

BH22

DDR3

BG23

DDR3

BC24

DDR3

BC22

DDR3_M1_DQSB_6

AT22

DDR3_M1_DQS_5

AT20

DDR3

BH14

DDR3_M1_DQS_4

BG15

DDR3_M1_DQSB_4

AY2

DDR3

BA3

DDR3

AT12

DDR3

AT13

DDR3

AV7

DDR3

AV6

DDR3

AM2

DDR3

AM3

DDR3

BRASWELL-GP

BRASWELL-GP

B

B

_M1_MA_14

_M1_MA_13

_M1_MA_12

_M1_MA_11

_M1_MA_10

_M1_MA_9

_M1_MA_8

_M1_MA_7

_M1_MA_6

_M1_MA_5

_M1_MA_4

_M1_MA_3

_M1_MA_2

_M1_MA_1

_M1_MA_0

_M1_BS_2

_M1_BS_1

_M1_CAS#

_M1_RAS#

_M1_WE#

_M1_CS1#

_M1_CS0#

_M1_CK_1

_M1_CK_1#

_M1_CKE_1

_M1_CK_0

_M1_CK_0#

_M1_CKE_0

VD#AT24

VD#AU24

_M1_ODT_1

_M1_OCAVREF

_M1_DRAMRST#

_VCCA_PWROK

_M1_RCOMPPD

_M1_DM_7

_M1_DM_6

_M1_DM_5

_M1_DM_4

_M1_DM_3

_M1_DM_2

_M1_DM_1

_M1_DM_0

_M1_DQS_7

_M1_DQSB_7

_M1_DQS_6

_M1_DQSB_5

_M1_DQS_3

_M1_DQSB_3

_M1_DQS_2

_M1_DQSB_2

_M1_DQS_1

_M1_DQSB_1

_M1_DQS_0

_M1_DQSB_0

DDR1

DDR1

BRASWELL

BRASWELL

2 OF 13

2 OF 13

DDR3

_M1_DQ_63

_M1_DQ_62

DDR3

_M1_DQ_61

DDR3

DDR3

_M1_DQ_60

DDR3

_M1_DQ_59

DDR3

_M1_DQ_58

_M1_DQ_57

DDR3

DDR3

_M1_DQ_56

DDR3

_M1_DQ_55

DDR3

_M1_DQ_54

DDR3

_M1_DQ_53

DDR3

_M1_DQ_52

_M1_DQ_51

DDR3

DDR3

_M1_DQ_50

_M1_DQ_49

DDR3

DDR3

_M1_DQ_48

DDR3_M1_DQ_47

_M1_DQ_46

DDR3

_M1_DQ_45

DDR3

DDR3

_M1_DQ_44

DDR3

_M1_DQ_43

DDR3

_M1_DQ_42

_M1_DQ_41

DDR3

_M1_DQ_40

DDR3

_M1_DQ_39

DDR3

DDR3

_M1_DQ_38

_M1_DQ_37

DDR3

DDR3

_M1_DQ_36

_M1_DQ_35

DDR3

_M1_DQ_34

DDR3

DDR3

_M1_DQ_33

DDR3

_M1_DQ_32

_M1_DQ_31

DDR3

DDR3_M1_DQ_30

_M1_DQ_29

DDR3

DDR3

_M1_DQ_28

DDR3

_M1_DQ_27

DDR3_M1_DQ_26

DDR3

_M1_DQ_25

_M1_DQ_24

DDR3

DDR3

_M1_DQ_23

DDR3

_M1_DQ_22

DDR3

_M1_DQ_21

_M1_DQ_20

DDR3

DDR3

_M1_DQ_19

_M1_DQ_18

DDR3

DDR3

_M1_DQ_17

DDR3

_M1_DQ_16

_M1_DQ_15

DDR3

_M1_DQ_14

DDR3

DDR3

_M1_DQ_13

_M1_DQ_12

DDR3

DDR3

_M1_DQ_11

_M1_DQ_10

DDR3

DDR3_M1_DQ_9

DDR3_M1_DQ_8

DDR3_M1_DQ_7

DDR3_M1_DQ_6

_M1_DQ_5

DDR3

_M1_DQ_4

DDR3

_M1_DQ_3

DDR3

_M1_DQ_2

DDR3

_M1_DQ_1

DDR3

_M1_DQ_0

DDR3

BG21

BH26

BJ25

BG26

BG22

BH20

BG25

BJ21

BD26

BF24

BA20

BD20

BD24

BA22

BC20

BF20

AV22

AV20

BD18

BF18

AU22

AU20

BA18

BC18

BH16

BH18

BJ13

BH12

BJ17

BG17

BG11

BG12

BB3

AW1

BC2

AW3

AV3

BC1

AV2

BD2

AV12

AP13

AV13

AT10

AP14

AT16

AP12

AT14

AV9

AY4

AT4

AP7

AV4

AY6

AT7

AP6

AP3

AR1

AK2

AL1

AR3

AT2

AL3

AK3

A A

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

<Variant Name>

<Variant Name>

<Variant Name>

application without get Wistron permission

stron Corporation

stron Corporation

stron Corporation

Wi

Wi

Wi

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

21F

21F

21F

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A2

A2

A2

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

CPU

CPU

CPU

Do

Do

Do

mino

mino

mino

1

Taipei Hsien 221, Taiwan, R.O.C.

(DDR)

(DDR)

(DDR)

-1

-1

51

51

51

-1

02

02

02

Page 6

5

4

3

2

1

SSID = CPU

D D

C C

Blanking

B B

Wistron Confidential document, Anyone can not

<Variant Name>

<Variant Name>

<Variant Name>

A A

tle

Title

Title

Ti

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

tron Corporation

tron Corporation

tron Corporation

Wis

Wis

Wis

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F,

21F,

21F,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

U (CFG)

U (CFG)

U (CFG)

CP

CP

CP

mino

mino

mino

Do

Do

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

2

Do

61

61

61

-1

-1

-1

02

02

of

of

of

1

02

Page 7

5

4

3

2

1

SSID = CPU

1D

05V_S5

05V_S5

05V_S5

1D

1D

05V_S5

1D

05V_S5

U1H

U1H

CP

AF36

AG33

AG35

AG36

AG38

AJ33

AJ36

AJ38

AF30

AG27

AG29

AG30

AJ27

AJ29

AJ30

AF29

AD16

AD18

AD19

AF16

AF18

AF19

AF21

AF22

AJ19

AG16

AG18

AG19

AG21

AG22

AG24

AJ21

AJ22

AJ24

AK24

AK30

AK35

AK36

AM29

AK33

AJ35

AM19

AK21

CP

RE_VCC1_S0IX3

CO

RE_VCC1_S0IX7

CO

RE_VCC1_S0IX8

CO

RE_VCC1_S0IX9

CO

RE_VCC1_S0IX10

CO

CO

RE_VCC1_S0IX14

CO

RE_VCC1_S0IX15

CO

RE_VCC1_S0IX16

RE_VCC1_S0IX2

CO

RE_VCC1_S0IX4

CO

RE_VCC1_S0IX5

CO

RE_VCC1_S0IX6

CO

RE_VCC1_S0IX11

CO

CO

RE_VCC1_S0IX12

CO

RE_VCC1_S0IX13

CO

RE_VCC1_S0IX1

_VGG_S0IX1

DDI

_VGG_S0IX2

DDI

_VGG_S0IX3

DDI

_VGG_S0IX4

DDI

DDI

_VGG_S0IX5

DDI

_VGG_S0IX6

DDI

_VGG_S0IX7

DDI

_VGG_S0IX8

_VGG_S0IX15

DDI

_VGG_S0IX9

DDI

_VGG_S0IX10

DDI

_VGG_S0IX11

DDI

_VGG_S0IX12

DDI

DDI

_VGG_S0IX13

DDI

_VGG_S0IX14

DDI

_VGG_S0IX16

DDI

_VGG_S0IX17

_VGG_S0IX18

DDI

_VGG_S0IX19

DDI

RE_V1P15_S0IX1

CO

RE_V1P15_S0IX2

CO

CO

RE_V1P15_S0IX3

CO

RE_V1P15_S0IX4

SE_V1P15_S0IX2

FU

SE_V1P15_S0IX1

FU

_V1P15_S0IX2

DDI

_V1P15_S0IX1

DDI

BRASWELL-GP

BRASWELL-GP

BRASWELL

BRASWELL

UNCO

USB

USB

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

RE_V1P15_S0IX10

LKDDRPCIeSATA

LKDDRPCIeSATA

iC

iC

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

E_V1P05A_G31#V22

PCI

PCI

SAT

SAT

USB3

USB3

USBSSI

FU

FU

FUSE

FUSE

D D

C C

15V_S5

1D

1D

15V_S5

B B

Imax=0.7A (1D15V_S5)

1D

15V_S5

Imax=6.4A (merged VCC0+VCC1)

_CPU_CORE

1V

_CPU_CORE

1V

X_CORE

GF

Imax=11A

8 OF 13

8 OF 13

RE_VNN_S41

RE_VNN_S42

RE_VNN_S43

RE_VNN_S44

RE_VNN_S45

RE_VNN_S46

RE_VNN_S47

RE_VNN_S48

RE_VNN_S49

RE_VNN_S410

RE_VNN_S411

RE_VNN_S412

RE_VNN_S413

RE_VNN_S414

RSVD#

RE_V1P15_S0IX6

RE_V1P15_S0IX1

RE_V1P15_S0IX2

RE_V1P15_S0IX3

RE_V1P15_S0IX4

RE_V1P15_S0IX5

RE_V1P15_S0IX7

RE_V1P15_S0IX8

RE_V1P15_S0IX9

IC

IC

E_V1P05A_G32

A_V1P05A_G32

A_V1P05A_G31

SE3_V1P05A_G5

SE_V1P05A_G3

AA30

LK_GND_OFF2

LK_GND_OFF1

V1P05A_G31

V1P05A_G34

V1P05A_G32

V1P05A_G35

V1P05A_G36

V1P05A_G33

_V1P05A_G32

_V1P05A_G31

C_V1P05A_G3

AA18

AA19

AA21

AA22

AA24

AA25

AC18

AC19

AC21

AC22

AC24

AC25

AD25

AD27

AA30

V33

AA32

AA33

AA35

AA36

AC32

Y30

Y32

Y33

Y35

V19

V18

AM21

AM33

AM22

AN22

AN32

AM32

V22

V24

U24

U22

V27

U27

V29

N18

U19

RSVD#

AA30

Imax=1.9A (1D05V_S5)

TP

TP

701 TPAD14-OP-GP

701 TPAD14-OP-GP

1

1D

05V_S5

Wistron Confidential document, Anyone can not

<Variant Name>

<Variant Name>

<Variant Name>

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

1D

05V_S5

1D

05V_S5

1D

tron Corporation

tron Corporation

tron Corporation

Wis

Wis

Wis

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F,

21F,

A A

Title

Title

Title

U (VCC_CORE)

U (VCC_CORE)

U (VCC_CORE)

CP

CP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

2

CP

Do

Do

Do

21F,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

mino

mino

mino

-1

-1

71

71

71

of

of

of

1

-1

02

02

02

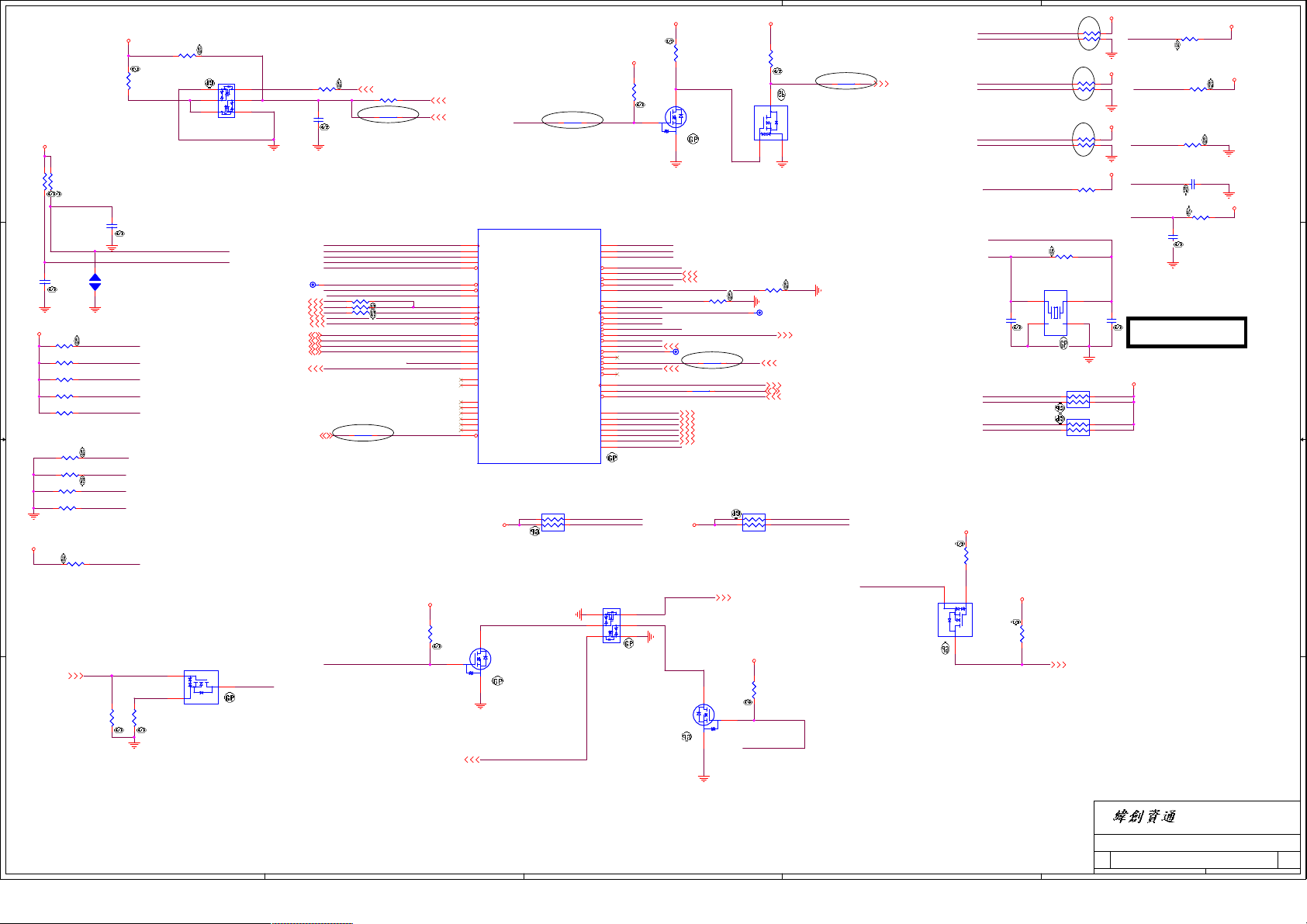

Page 8

SSID = CPU

5

4

3

2

1

D D

I_DATA_CPU_P254

HDM

I_DATA_CPU_N254

HDM

HDM

P_TX_CPU_P052

eD

eD

P_TX_CPU_N052

eDP_TX_CPU_P152

P_TX_CPU_N152

eD

eD

P_AUX_CPU_P52

eD

P_AUX_CPU_N52

eD

P_HPD_CPU_N52

eD

P_BLEN_CPU24

eD

P_BLCTRL_CPU52

eD

P_VDDEN_CPU52

R813

R813

1MR2J-L3-GP

1MR2J-L3-GP

HDM

HDMI_DATA_CPU_P054

HDM

HDM

HDMI_DATA_CPU_N354

R8

R8

02

02

402R2F-GP

402R2F-GP

1 2

1 2

R8

R8

01

01

402R2F-GP

402R2F-GP

eD

TP803TPAD14-OP-GP TP803TPAD14-OP-GP

801TPAD14-OP-GPTP801TPAD14-OP-GP

TP

TP802TPAD14-OP-GP TP802TPAD14-OP-GP

I_DATA_CPU_P154

I_DATA_CPU_N154

I_DATA_CPU_N054

I_DATA_CPU_P354

HDM

I_DET_CPU54

P_BLEN_CPU

1

1

1

DDI

0_PLLOBS_P

0_PLLOBS_N

DDI

P_BLEN_CPU

eD

eD

P_VDDEN_CPU

DDI

DDI

1_PLLOBS_P

1_PLLOBS_N

HV

UA

UA

_DDI2_HPD

RT1_TX

RT1_RX

8V_S5

1D

HDMI

4

RN8

RN8

03

03

SRN2K2J-1-GP

SRN2K2J-1-GP

CRB 2.2k

1

I_CLK_CPU54,86

HDM

HDM

I_DATA_CPU54

C C

1D

8V_S5

P_BLEN_CPU

03 100KR2J-1-GP

03 100KR2J-1-GP

R8

R8

1 2

DY

DY

R804 100KR2J-1-GP

R804 100KR2J-1-GP

1 2

DY

DY

B B

eD

eD

P_BLCTRL_CPU

2 3

EDP

1 2

D50

C51

H49

H50

F53

F52

G53

G52

H47

H46

W51

Y51

Y52

V52

V51

W53

F38

G38

J51

H51

K51

K52

L53

L51

M52

M51

M42

K42

R51

P51

P52

R53

F47

F49

F40

G40

J40

K40

F42

G42

D44

F44

D48

C49

U51

T51

T52

B53

A52

E52

D52

B50

B49

E53

C53

A51

A49

G44

C

C

CPU1

CPU1

DDI

0_TXP_0

0_TXN_0

DDI

0_TXP_1

DDI

DDI

0_TXN_1

DDI

0_TXP_2

DDI

0_TXN_2

DDI

0_TXP_3

0_TXN_3

DDI

DDI

0_AUXP

DDI0_AUXN

_DDI0_HPD

HV

HV

_DDI0_DDC_SCL

HV

_DDI0_DDC_SDA

EL0_BKLTEN

PAN

PAN

EL0_BKLTCTL

EL0_VDDEN

PAN

DDI

0_PLLOBS_P

0_PLLOBS_N

DDI

1_TXP_0

DDI

1_TXN_0

DDI

DDI

1_TXP_1

DDI

1_TXN_1

DDI1_TXP_2

1_TXN_2

DDI

DDI

1_TXP_3

DDI1_TXN_3

1_AUXP

DDI

DDI

1_AUXN

HV

_DDI1_HPD

EL1_BKLTEN

PAN

PAN

EL1_BKLTCTL

EL1_VDDEN

PAN

DDI

1_PLLOBS_P

DDI

1_PLLOBS_N

2_TXP_0

DDI

2_TXN_0

DDI

2_TXP_1

DDI

DDI

2_TXN_1

DDI2_TXP_2

DDI2_TXN_2

DDI2_TXP_3

DDI2_TXN_3

2_AUXP

DDI

2_AUXN

DDI

_DDI2_HPD

HV

_DDI2_DDC_SCL

HV

HV

_DDI2_DDC_SDA

VD#B53

RS

RS

VD#A52

RS

VD#E52

RS

VD#D52

RS

VD#B50

RS

VD#B49

RSVD#E53

RS

VD#C53

RSVD#A51

RSVD#A49

RSVD#G44

BRASWELL

BRASWELL

1.0V

0

0

DDI

DDI

1.8V

1.0V

DDI1

DDI1

1.8V

DDI2

DDI2

DDI2 do not support eDP

1.8V

NC's

NC's

1D8V_S5

MMC1

MMC1

SD

SD

1D8V_S5

SDMMC2

SDMMC2

3.3V

1.8V

3.3V

SDMMC3

SDMMC3

1.8V

3 OF 13

3 OF 13

VD#M44

RS

VD#K44

RS

RS

VD#K48

RS

VD#K47

MC

SI_1_CLKP

SI_1_CLKN

MC

MC

SI_1_DP_0

MC

SI_1_DN_0

MC

SI_1_DP_1

SI_1_DN_1

MC

MC

SI_1_DP_2

SI_1_DN_2

MC

MC

SI_1_DP_3

SI and Camera interface

SI and Camera interface

MC

SI_1_DN_3

MC

MC

SI_2_CLKP

MC

SI_2_CLKN

MC

MC

SI_2_DP_0

MC

SI_2_DN_0

SI_2_DP_1

MC

SI_2_DN_1

MC

VD#T50

RS

RS

VD#T48

MC

SI_COMP

_CAMERASB00

GP

GP

_CAMERASB01

GP

_CAMERASB02

GP

_CAMERASB03

_CAMERASB04

GP

GP_CAMERASB05

_CAMERASB06

GP

GP

_CAMERASB07

GP

_CAMERASB08

GP

_CAMERASB09

_CAMERASB10

GP

GP

_CAMERASB11

MMC1_CLK

SD

MMC1_CMD

SD

SD

MMC1_D0

SD

MMC1_D1

MMC1_D2

SD

MMC1_D3_CD#

SD

MMC

1_D4_SD_WE

MMC

MMC

MMC

MMC1_RCLK

SDMMC1_RCOMP

SDMMC2_CLK

MMC2_CMD

SD

MMC2_D0

SD

MMC2_D1

SD

MMC2_D2

SD

MMC2_D3_CD#

SD

SD

MMC3_CLK

SD

MMC3_CMD

MMC3_CD#

SD

SD

MMC3_D0

SD

MMC3_D1

SD

MMC3_D2

SD

MMC3_D3

SD

MMC3_1P8_EN

SDMMC3_PWR_EN#

SDMMC3_RCOMP

M44

K44

K48

K47

T44

T45

Y47

Y48

V45

V47

V50

V48

T41

T42

P50

P48

P47

P45

M48

M47

T50

T48

SI_COMP

MC

P44

AB41

AB45

AB44

AC53

AB51

AB52

AA51

AB40

Y44

Y42

Y41

V40

M7

P6

M6

M4

P9

P7

T6

T7

1_D5

T10

1_D6

T12

1_D7

T13

SDMMC1_RCOMP

P13

K10

K9

M12

M10

K7

K6

F2

D2

PSW

K3

J1

J3

H3

G2

K2

L3

MMC3_RCOMP

SD

P12

_CLR#

R8

R8

1 2

150R2F-1-GP

150R2F-1-GP

R8

R8

14

14

1 2

100R2F-L1-GP-U

100R2F-L1-GP-U

R8

R8

1 2

80D6R2F-L-GP

80D6R2F-L-GP

17

17

To XDP

GP

_CAMERASB08 15

GP

_CAMERASB09 15

_CAMERASB11 15

GP

MMC

1_CLK 57

MMC

1_CMD_CPU 57

1_D0_CPU 57

MMC

MMC

1_D1_CPU 57

1_D2_CPU 57

MMC

MMC

1_D3_CPU 57

MMC

1_D4_CPU 57

MMC1_D5_CPU 57

MMC

1_D6_CPU 57

1_D7_CPU 57

MMC

1D8V_S5

12

R818

R818

10KR2J-L-GP

RT

C_DET# 25

15

15

10KR2J-L-GP

21

G8

G8

01

01

GAP-OPEN

GAP-OPEN

PSW

_CLR#

BRASWELL-GP

BRASWELL-GP

A A

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

<Variant Name>

<Variant Name>

<Variant Name>

application without get Wistron permission

stron Corporation

stron Corporation

stron Corporation

Wi

Wi

Wi

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

21F

21F

21F

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A2

A2

A2

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU

CPU

CPU

(DDI/EDP/GPIO)

(DDI/EDP/GPIO)

(DDI/EDP/GPIO)

Do

Do

Do

mino

mino

mino

1

-1

-1

81

81

81

-1

02

02

02

Page 9

5

4

3

2

1

SSID = CPU

D D

CP

CP

U1L

U1K

U1K

CP

AN

BG30

BG27

BG24

BG20

BG19

BG18

BG16

BG14

BF42

BF32

BF28

BF27

BF26

BF22

BF12

BE35

BE19

C20

BD53

BG7

BD35

BD27

BD19

BD1

BC44

BC40

BC38

BC28

BC26

BC16

BC14

BC10

BB35

BB27

BB19

BA35

BA30

BA27

BA24

BA19

B36

B28

AY7

AY51

AY47

AY34

AY32

AY30

AY3

AN

AY45

21

30

CP

VSS5

VSS1

VSS1

VSS9

VSS9

VSS97

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS8

VSS8

VSS8

VSS8

VSS8

VSS1

VSS8

VSS1

VSS8

VSS8

VSS8

VSS80

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS60

VSS5

VSS5

VSS5

VSS5

VSS5

VSS5

VSS6

VSS5

BRASWELL-GP

BRASWELL-GP

CP

CP

U1J

U1J

AN3

VSS9

AN29

VSS9

AN25

VSS9

AN24

VSS9

AN16

VSS94

AN14

VSS9

AN12

VSS9

AN11

VSS9

AN1

VSS9

AM50

VSS8

AM42

VSS8

AM4

VSS8

AM38

VSS8

AM35

VSS8

AH44

VSS6

AM30

VSS8

AM27

VSS8

U25

VSS1

P10

VSS9

AM16

C C

B B

AD4

AK7

AK50

AK47

AK45

AK44

AK40

AK4

AK38

AK32

AK27

AK25

AM24

AK16

AJ53

AJ51

AJ25

AJ16

AH9

AH47

AH42

AH41

AH14

AH13

AH12

AH10

AG25

AF47

AJ3

AJ1

VSS8

VSS3

VSS8

VSS7

VSS78

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS8

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS59

VSS5

VSS5

VSS5

VSS5

VSS5

VSS5

VSS5

BRASWELL-GP

BRASWELL-GP

Po

Po

BRASWELL

BRASWELL

8

7

6

5

3

2

1

0

9

8

7

6

5

0

4

3

00

9

1

1

0

9

7

6

5

4

3

2

1

0

2

9

8

7

6

5

4

3

2

1

8

7

6

5

4

3

2

wer-VSS

wer-VSS

10 OF 13

10 OF 13

VSS5

VSS5

VSS4

VSS4

VSS47

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS2

VSS2

VSS28

VSS2

VSS2

VSS2

VSS2

VSS2

VSS2

VSS2

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS9

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

AF38

1

AF32

0

AF25

9

AF10

8

AE9

AE8

6

AE6

5

AE53

4

AE50

3

AE48

2

AE46

1

AE45

0

AE43

9

AE42

8

AE40

7

AE14

6

AE12

5

AE11

4

AE1

3

AD44

2

AD36

0

AC29

3

AD32

9

AD30

AD21

7

AC38

6

AC35

5

AC33

4

AC16

2

AB6

1

AB50

0

AB47

9

AB42

8

AB4

7

AB14

6

AB13

5

AB12

4

AB10

3

AA53

2

AA38

1

AA27

0

AA1

6

A47

A4

3

A3

9

A3

1

3

A2

A1

9

A1

5

A1

1

Po

Po

BRASWELL

BRASWELL

01

00

9

8

6

5

4

3

2

1

0

9

8

7

6

5

03

4

02

3

2

1

9

8

7

6

5

4

3

2

1

0

9

8

7

6

5

4

3

2

9

8

6

5

4

3

7

wer-VSS

wer-VSS

11 OF 13

11 OF 13

VSS6

VSS5

VSS5

VSS5

VSS4

VSS48

VSS4

VSS4

VSS4

VSS4

VSS3

VSS2

VSS4

VSS4

VSS4

VSS4

VSS4

VSS3

VSS3

VSS1

VSS3

VSS3

VSS3

VSS3

VSS33

VSS3

VSS3

VSS3

VSS2

VSS2

VSS2

VSS2

VSS2

VSS2

VSS2

VSS2

VSS2

VSS2

VSS1

VSS1

VSS1

VSS1

VSS1

VSS14

VSS1

VSS1

VSS1

VSS1

VSS9

VSS8

VSS7

AY9

1

AY28

2

AY26

1

AY24

0

AY22

9

AY20

AW35

7

AW27

6

AW19

5

13

AM

AK2

9

AK2

2

AV40

4

AV35

3

AV30

2

AV27

1

AV24

0

AV19

9

AV14

8

AJ

18

AU53

7

AU51

6

AU3

5

AU1

4

AT9

AT51

2

AT45

1

AT36

0

AT35

9

AT3

8

AT27

7

AT19

6

AT18

5

AP9

4

AP50

3

AP45

2

AP4

1

AN9

0

AN8

9

AN6

8

AN53

7

AN51

6

AN5

5

AN49

AN48

3

AN46

2

AN45

1

AN43

0

AN

42

AN

40

AN

38

U1L

AN

33

VSS2

P32

VSS9

P27

VSS9

P22

VSS9

P19

VSS9

AF

24

VSS1

N53

VSS95

N51

VSS9

N32

VSS9

N24

VSS9

N22

VSS9

M9

VSS9

K45

VSS7

M40

VSS8

M35

VSS8

M27

VSS8

AW

13

VSS3

M19

VSS8

M14

VSS8

L35

VSS8

L27

VSS8

L19

VSS8

L1

VSS7

K50

VSS7

T47

VSS100

K4

VSS7

K36

VSS7

K34

VSS7

K32

VSS7

K30

VSS7

K24

VSS7

K22

VSS7

K16

VSS6

K14

VSS6

K12

VSS6

J53

VSS6

M45

VSS8

J38

VSS6

J35

VSS6

J30

VSS6

J27

VSS6

J22

VSS6

J19

VSS5

J18

VSS58

H8

VSS5

E46

VSS4

H35

VSS5

H27

VSS5

H19

VSS5

M50

VSS8

V25

VSS1

BRASWELL-GP

BRASWELL-GP

Po

Po

BRASWELL

BRASWELL

9

8

7

6

4

3

2

1

0

7

7

6

5

4

3

2

1

0

9

8

6

5

4

3

2

1

0

9

8

7

6

8

4

3

2

1

0

9

7

0

6

5

4

9

01

wer-VSS

wer-VSS

12 OF 13

12 OF 13

VSS1

VSS5

VSS5

VSS5

VSS5

VSS4

VSS48

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS6

VSS29

VSS2

VSS2

VSS2

VSS2

VSS2

VSS2

VSS4

VSS2

VSS2

VSS2

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS11

VSS1

VSS9

VSS8

VSS7

VSS6

VSS5

Y24

02

G30

3

G28

2

G26

1

G22

0

G14

9

G12

F5

7

F35

6

F32

5

F27

4

F24

3

F19

2

E51

1

E35

9

E19

8

D42

7

D40

6

D38

5

D32

4

D27

3

D24

2

D16

1

D10

0

J42

5

C47

C39

8

C36

7

C30

6

C3

5

C28

4

C22

3

AW

BJ7

2

BJ47

1

BJ43

0

BJ39

9

BJ35

8

BJ31

7

BJ27

6

BJ23

5

BJ19

4

BJ15

3

BJ11

2

BG5

BG49

0

BG

BG

BG

BG

BG

B52 MAY NOT BE ABLE TO BREAK OUT IN ROUTING

41

40

38

36

35

34

901

901

TP

TP

TPAD14-OP-GP

TPAD14-OP-GP

TP

TP

902

902

TPAD14-OP-GP

TPAD14-OP-GP

CPU_

VSS16

1

nc b52

CPU_

VSS2

1

BH53

BH52

BH2

BH1

BG53

BG1

M24

BF

BF

BB5

BB4

BG47

F1

C1

B5

B2

A6

A5

A7

50

Y9

Y50

Y45

Y40

Y4

Y38

Y29

Y22

Y21

Y19

Y16

Y14

Y10

P4

L41

P36

CP

CP

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

2

VSS5

VSS4

VSS2

VSS1

VSSA

VSS3

VSS9

4

VSS8

0

VSS7

VSS6

VSS1

VSS7

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS60

VSS5

VSS5

VSS2

VSS1

VSS2

BRASWELL-GP

BRASWELL-GP

U1M

U1M

Po

Po

BRASWELL

BRASWELL

8

7

6

5

4

3

2

0

1

0

9

8

7

6

5

4

3

2

1

9

8

2

9

1

wer-VSS

wer-VSS

13 OF 13

13 OF 13

VSS5

VSS5

VSS5

VSS5

VSS5

VSS5

VSS5

VSS5

VSS4

VSS4

VSS4

VSS4

VSS4

VSS44

VSS4

VSS4

VSS4

VSS4

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS2

VSS2

VSS27

VSS2

VSS2

VSS2

VSS2

VSS2

W1

7

V44

6

V42

5

V41

4

V38

3

V32

2

V21

1

V16

0

U9

9

U8

8

U6

7

U53

6

U5

5

U49

U48

3

U46

2

U45

1

U43

0

U42

9

U40

8

U38

7

U33

5

U32

4

U30

3

U29

2

U21

1

U18

0

U36

6

U14

9

U12

8

U11

T9

6

P42

3

T14

5

R1

4

P35

0

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

<Variant Name>

<Variant Name>

A A

5

4

3

2

<Variant Name>

Wi

Wi

Wi

stron Corporation

stron Corporation

stron Corporation

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F,

21F,

21F,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

Date: Sheet

Date: Sheet

Date: Sheet

CP

CP

CP

Do

Do

Do

Taipei Hsien 221, Taiwan, R.O.C.

U (VSS)

U (VSS)

U (VSS)

mino

mino

mino

of

of

of

9102

9102

9102

1

-1

-1

-1

Page 10

5

4

3

2

1

SSID = CPU

1V

_CPU_CORE

AF36, AG33, AG35, AG36, AG38, AJ33, AJ36, AJ38

SC4D7U6D3V2MX-GP-U

SC4D7U6D3V2MX-GP-U

SC4D7U6D3V2MX-GP-U

SC4D7U6D3V2MX-GP-U

PC1

PC1

C1

PC1

PC1

SC10U6D3V3MX-L-GP

PLACE ALL THE CAPS

UNDER THE PKG SHADOW

D D

SC10U6D3V3MX-L-GP

12

042

042

C1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

027

027

12

048

048

12

12

SC4D7U6D3V2MX-GP-U

SC4D7U6D3V2MX-GP-U

C1

C1

030

030

12

DY

DY

PC1

PC1

C1

C1

029

029

12

DY

DY

PC1

PC1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

058

058

059

059

DY

DY

1D

05V_S5

AA18, AA19, AA21, AA22, AA24, AA25, AC18, AC19, AC21, AC22, AC24, AC25, AD25, AD27

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

024

024

12

12

SC1U10V2KX-1GP

C1

C1

C1

C1

025

025

001

001

12

12

SC1U10V2KX-1GP

SC10U6D3V3MX-L-GP

C1

C1

002

002

12

SC10U6D3V3MX-L-GP

C1

C1

PC1

PC1

008

008

12

12

009

009

PC1

PC1

010

010

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

PC1

PC1

12

011

011

_CPU_CORE

1V

AF30, AG27, AG29, AG30, AJ27, AJ29, AJ30, AF29

SC4D7U6D3V2MX-GP-U

SC4D7U6D3V2MX-GP-U

SC4D7U6D3V2MX-GP-U

C1

C1

032

032

PC1

PC1

045

045

SC4D7U6D3V2MX-GP-U

C1

C1

036

036

12

PC1

PC1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

12

062

062

DY

DY

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

039

039

049

049

12

12

12

DY

DY

12

DY

DY

PC1

PC1

PC1

PC1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

061

061

060

060

DY

DY

PC1

PC1

PC1

PC1

PC1

12

DY

DY

PC1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

064

064

065

065

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

063

063

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC4D7U6D3V2MX-GP-U

PC1

PC1

041

041

PC1

PC1

044

044

SC4D7U6D3V2MX-GP-U

C1

C1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

033

033

12

12

PC1

PC1

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

12

12

046

046

DY

DY

DY

DY

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

037

037

038

038

12

12

PC1

PC1

SC10U6D3V3MX-L-GP

PC1

PC1

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

031

031

15V_S5

12

SC10U6D3V3MX-L-GP

12

12

040

040

PC1

PC1

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

12

12

043

043

DY

DY

DY

DY

12/2

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1034

C1034

035

035

12

PLACE ALL THE CAPS

UNDER THE PKG SHADOW

C C

B B

GF

X_CORE

12

DY

DY

1D

05V_S5

1D

V33, AA32, AA33, AA35, AA36, AC32, Y30, Y32, Y33, Y35

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

20150313 SC

PC1

PC1

12

014

014

DY

DY

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

DY

DY

SC1U10V2KX-1GP

C1

C1

005

005

12

05V_S5

1D

C1

C1

C1

C1

003

003

004

12

004

12

V18, V19

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12/2

1D

05V_S5

1D

12

05V_S5

C1018

C1018

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

050

050

12

DY

DY

U19

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

023

023

022

022

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1020

C1020

C1

C1

021

021

12

12

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

006

006

007

007

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

057

057

056

056

12

DY

DY

1D

1D

12

05V_S5

12

05V_S5

AM21, AM33, AM22, AN22, AN32, AM32

SC1U10V2KX-1GP

SC1U10V2KX-1GP

PC1

PC1

C1

C1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

013

013

12

12

012

012

DY

DY

1D

05V_S5

V29 V22, V24, U24, U22, V27, U27

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

016

016

017

017

12

12

05V_S5

1D

N18

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

015

015

12

DY

DY

20150313 SC

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

019

019

DY

DY

DY

DY

DY

DY

DY

DY

DY

20150313 SC

1D15V_S5

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1047

C1047

12

A A

DY

DY

5

20150313 SC

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

026

026

028

028

12

12

DY

DY

DY

DY

DY

1D05V_S5 1D05V_S5

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

PC1

PC1

PC1

PC1

12

12

051

051

052

052

DY

DY

DY

DY

PLACE CLOSE TO PIN 1 OF RA

4

3

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

PC1054

PC1054

PC1055

PC1055

12

DY

DY

PC1

PC1

12

12

053

053

PLACE CLOSE TO PIN 1 OF RB

DY

DY

DY

DY

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

<Variant Name>

<Variant Name>

<Variant Name>

Wi

Wi

Wi

stron Corporation

stron Corporation

stron Corporation

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F,

21F,

21F,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

Date: Sheet

Date: Sheet

2

Date: Sheet

CP

CP

CP

Do

Do

Do

Taipei Hsien 221, Taiwan, R.O.C.

U (Power CAP1)

U (Power CAP1)

U (Power CAP1)

mino

mino

mino

10 102

10 102

10 102

1

-1

-1

of

of

of

-1

Page 11

5

4

3

2

1

SSID = CPU

1D

35V_CPU_VDDQ_S3

SC1U10V2KX-1GP

SC1U10V2KX-1GP

PC1

PC1

C1

C1

101

101

12

D D

Close to CPU

1D

35V_CPU_VDDQ_S3

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

118

118

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

143

143

12

Close to DDR

1D

24V_S5

1D

35V_CPU_VDDQ_S3

1D

24V_S5

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

PC1

PC1

C1

C1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

112

112

12

12

119

119

SC1U10V2KX-1GP

C1

C1

144

144

12

Close to DDRClose to CPU

1D

05V_S5

12

RT

C_AUX_S5

H10, G10

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

125

125

C1

C1

132

132

12

C5, B6

SC1U10V2KX-1GP

SC1U10V2KX-1GP

3D

3V_S5_PRIME

12

C1

C1

103

103

D4, E3

SC1U10V2KX-1GP

SC1U10V2KX-1GP

Place close to CPU V36, Y36 T40, P40

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

PC1

PC1

PC1

PC1

PC1

PC1

PC1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C C

24V_S5

1D

SC10U6D3V3MX-L-GP

12

120

120

122

122

PC1

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

SC10U6D3V3MX-L-GP

12

123

123

124

124

DY

DY

24V_S5

1D

M41 U35, V35

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

1D

12

DY

DY

24V_S5

C1

128

128

DY

DY

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

137

137

138

138

12

SC1U10V2KX-1GP

C1

C1

131

131

12

24V_S5

1D

Y27, Y25

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

134

134

12

24V_S5

1D

AF35, AD35, AD38, AC36 H44 P41

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

DY

DY

SC1U10V2KX-1GP

C1

C1

149

149

12

C1

C1

109

109

12

B B

20150313 SC

SC1U10V2KX-1GP

C1

C1

108

108

12

12

DY

DY

SC1U10V2KX-1GP

C1

C1

C1

C1

107

107

106

106

12

12

1D

8V_S5

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

114

114

DY

DY

1D

24V_S5

12

P38, V30, AC30

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

147

147

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

150

150

1D

12

DY

DY

24V_S5

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1117

C1117

116

116

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

129

129

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

148

148

12

DY

DY

3V_S5_PRIME

1D

8V_S5

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1105

C1105

104

104

12

12

3D

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

115

115

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

126

126

12

20150302 SC

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

127

127

12

3

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

<Variant Name>

<Variant Name>

<Variant Name>

Wi

Wi

Wi

stron Corporation

stron Corporation

stron Corporation

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F,

21F,

21F,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Friday, March 20, 2015

Friday, March 20, 2015

Friday, March 20, 2015

Date: Sheet

Date: Sheet

2

Date: Sheet

CP

CP

CP

Do

Do

Do

Taipei Hsien 221, Taiwan, R.O.C.

U (Power CAP2)

U (Power CAP2)

U (Power CAP2)

mino

mino

mino

11 102

11 102

11 102

1

-1

-1

of

of

of

-1

DY

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

111

111

DY

1D

8V_VCCCFIOAZA

12

4

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

102

102

DY

DY

1D

8V_S5

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

C1

C1

121

121

113

113

12

12

DY

DY

DY

A A

5

DY

20150313 SC

1D

8V_S5

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1130

C1130

12

DY

DY

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

110

110

12

DY

DY

3D

3V_1D8V_VCCPADCF1SI0

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1

C1

133

133

12

3D

3V_1D8V_VCCPADCF3SI0

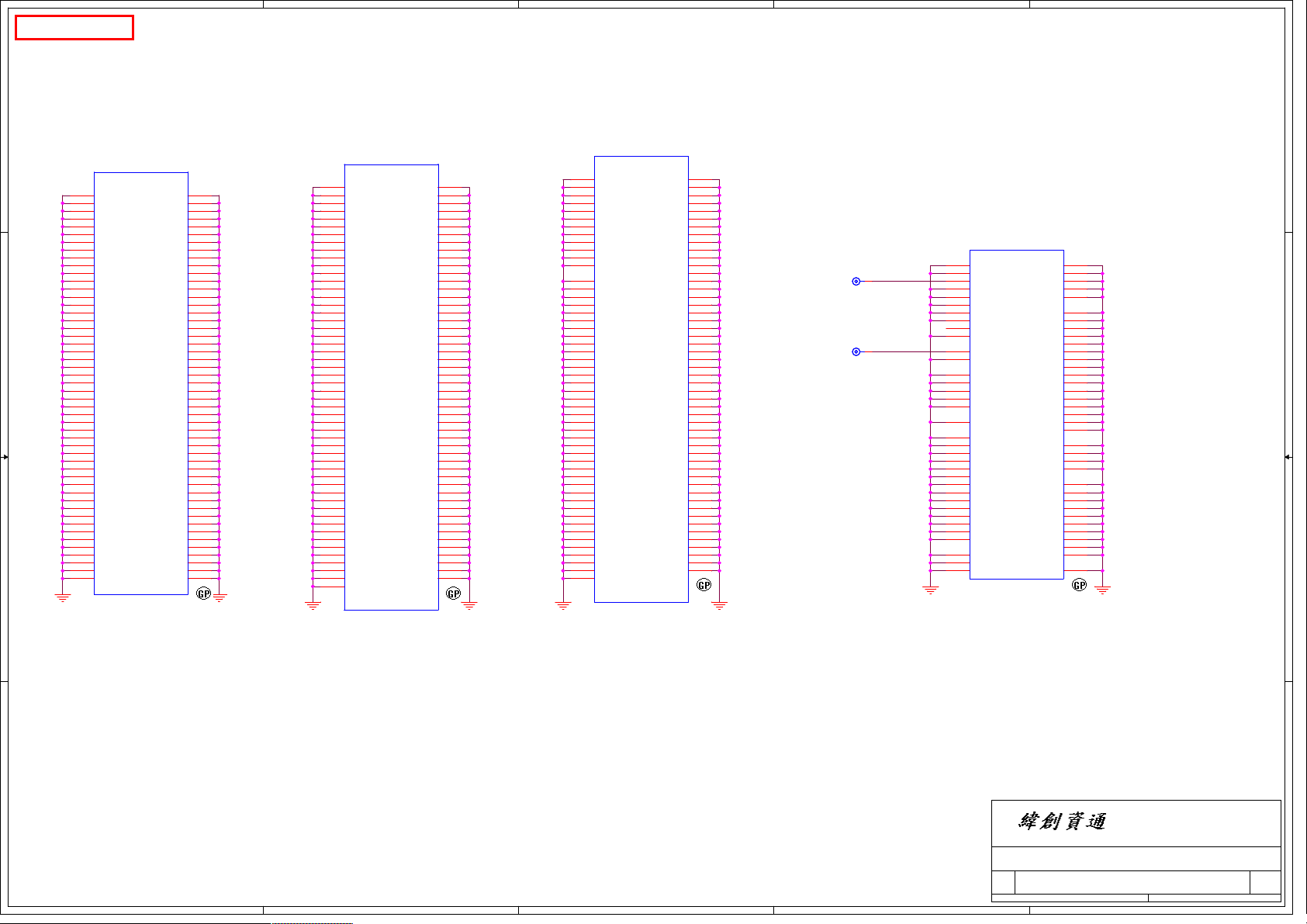

Page 12

5

4

3

2

1

SSID = MEMORY

P30

DM

DM

1

D D

A_A[15:0] 5

M_

M_

A_BS25

A_BS05

M_

M_A_BS15

M_

A_DQ15

A_DQ45

M_

M_

A_DQ25

M_

A_DQ35

M_

A_DQ05

M_

A_DQ55

A_DQ65

M_

M_

A_DQ75

A_DQ135

M_

M_

A_DQ95

M_

A_DQ105

M_

A_DQ145

A_DQ85

M_

A_DQ125

M_

M_

A_DQ115

A_DQ155

M_

M_

A_DQ225

A_DQ175

M_

C C

B B

M_A_DIM0_ODT05

M_

A_DIM0_ODT15

SM_DRAMRST#5

A A

M_A_DQ185

A_DQ235

M_

A_DQ195

M_

M_

A_DQ165

M_A_DQ205

M_

A_DQ215

A_DQ285

M_

A_DQ305

M_

M_

A_DQ245

M_

A_DQ265

M_

A_DQ275

A_DQ255

M_

M_

A_DQ315

A_DQ295

M_

M_

A_DQ325

M_

A_DQ375

M_

A_DQ345

M_

A_DQ385

A_DQ365

M_

M_

A_DQ335

A_DQ355

M_

M_

A_DQ395

M_

A_DQ405

M_A_DQ415

A_DQ425

M_

A_DQ465

M_

M_

A_DQ445

A_DQ455

M_

A_DQ435

M_

A_DQ475

M_

A_DQ485

M_

A_DQ525

M_

M_

A_DQ555

A_DQ515

M_

A_DQ535

M_

M_

A_DQ495

M_

A_DQ545

M_

A_DQ505

M_

A_DQ565

M_

A_DQ595

M_

A_DQ625

M_

A_DQ605

M_A_DQ585

M_A_DQ635

M_

A_DQ615

M_A_DQ575

A_DQS_DN05

M_

A_DQS_DN15

M_

M_A_DQS_DN25

A_DQS_DN35

M_

A_DQS_DN45

M_

A_DQS_DN55

M_

A_DQS_DN65

M_

A_DQS_DN75

M_

A_DQS_DP05

M_

M_

A_DQS_DP15

M_

A_DQS_DP25

M_

A_DQS_DP35

M_

A_DQS_DP45

M_

A_DQS_DP55

M_A_DQS_DP65

M_

A_DQS_DP75

VR

VREF_DQ

5

M_

A_DIM0_ODT0

M_A_DIM0_ODT1

EF_CA

675V_VREF_S0

0D

A_A0

M_

M_

A_A1

A_A2

M_

M_

A_A3

A_A4

M_

A_A5

M_

M_

A_A6

A_A7

M_

M_

A_A8

A_A9

M_

M_

A_A10

A_A11

M_

A_A12

M_

M_

A_A13

M_

A_A14

M_

A_A15

1

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A1

0/AP

84

1

A1

83

A1

2

119

3

A1

80

A1

4

78

A1

5

79

A1

6/BA2

109

BA0

108

BA1

5

DQ

0

7

DQ

1

15

DQ2

17

3

DQ

4

4

DQ

6

DQ

5

16

DQ

6

18

DQ

7

21

8

DQ

23

9

DQ

33

DQ

10

35

11

DQ

22

DQ

12

24

13

DQ

34

DQ

14

36

15

DQ

39

16

DQ

41

DQ

17

51

DQ

18

53

DQ

19

40

20

DQ

42

DQ21

50

22

DQ

52

DQ

23

57

DQ

24

59

DQ25

67

DQ

26

69

27

DQ

56

DQ

28

58

DQ

29

68

DQ

30

70

DQ

31

129

32

DQ

131

DQ

33

141

34

DQ

143

DQ

35

130

DQ

36

132

DQ

37

140

38

DQ

142

39

DQ

147

DQ

40

149

41

DQ

157

DQ

42

159

43

DQ

146

DQ44

148

DQ45

158

46

DQ

160

DQ47

163

DQ48

165

49

DQ

175

50

DQ

177

51

DQ

164

52

DQ

166

53

DQ

174

54

DQ

176

55

DQ

181

DQ

56

183

DQ

57

191

58

DQ

193

DQ

59

180

DQ

60

182

DQ

61

192

DQ

62

194

DQ

63

10

DQ

S0#

27

DQS1#

45

DQS2#

62

DQS3#

135

S4#

DQ

152

DQS5#

169

S6#

DQ

186

S7#

DQ

12

S0

DQ

29

S1

DQ

47

DQ

S2

64

S3

DQ

137

S4

DQ

154

DQ

S5

171

DQ

S6

188

DQ

S7

116

OD

T0

120

OD

T1

126

VREF_CA

1

VREF_DQ

30

RESET#

203

T1

VT

204

VTT2

SKT_DDR 204P SMD

SKT_DDR 204P SMD

DDR3-204P-263-GP-U

DDR3-204P-263-GP-U

d = 62.10024.M51

d = 62.10024.M51

2n

2n

62.10024.S61

62.10024.S61

4th = 62.10017.I21

4th = 62.10017.I21

3rd = 62.10024.Q71

3rd = 62.10024.Q71

NP1

NP1

NP2

2

NP

110

RA

S#

113

WE#

115

CA

S#

114

0#

CS

121

CS

1#

73

CK

E0

74

E1

CK

101

0

CK

103

CK

0#

102

CK

1

104

CK

1#

11

DM

0

28

1

DM

46

DM

2

63

DM

3

136

DM4

153

5

DM

170

6

DM

187

DM

7

200

SD

A

202

L

SC

EVEN

T#

VD

DSPD

SA0

SA1

NC#

1

NC#

2

NC#

/TEST

VDD1

D2

VD

VD

D3

VD

D4

VDD5

VD

D6

D7

VD

VD

D8

VD

D9

VD

D10

VD

D11

D12

VD

VD

D13

D14

VD

VD

D15

VD

D16

VD

D17

D18

VD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

198

199

197

201

77

122

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144