4 4

3 3

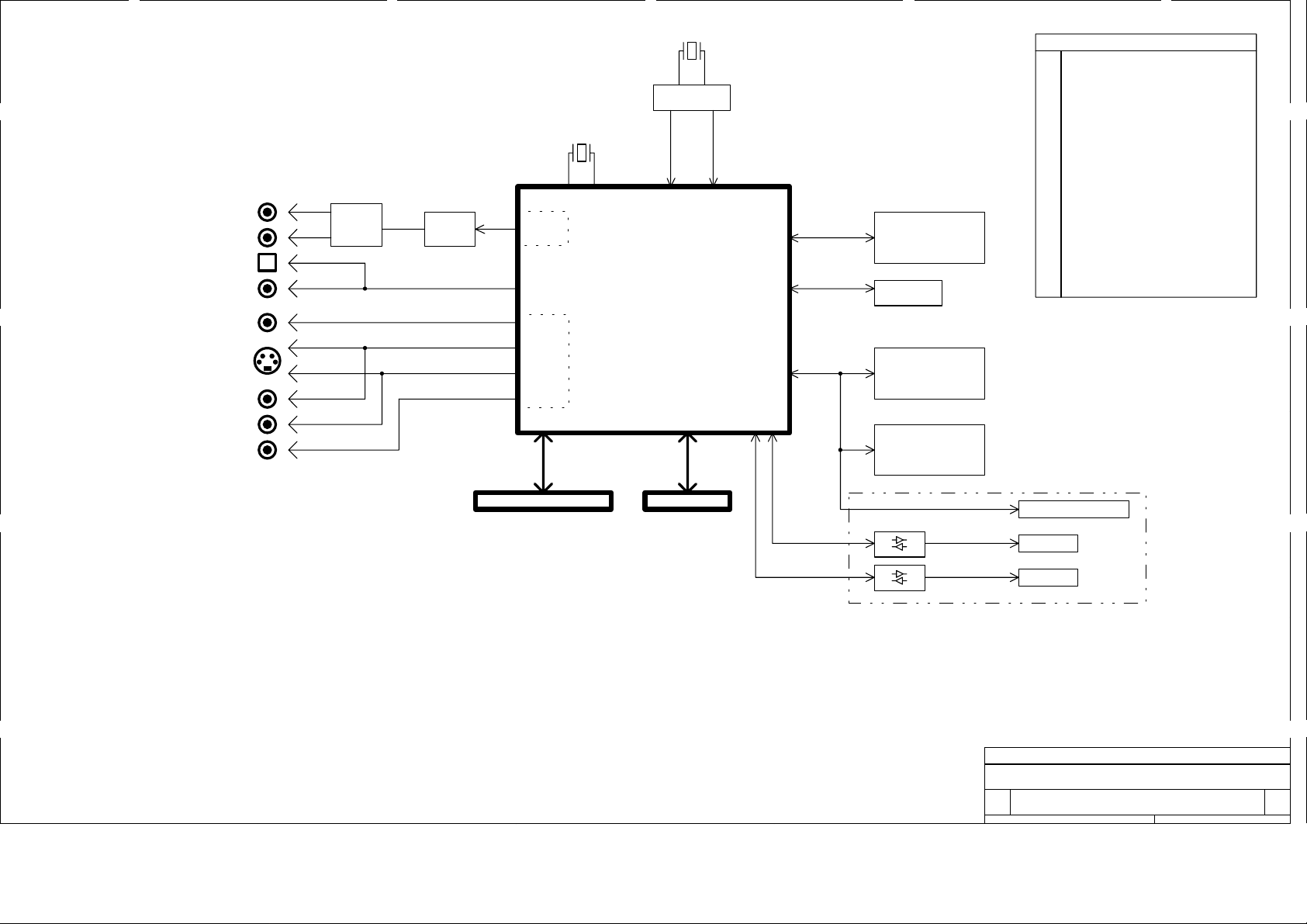

HDTV OUT

AUDIO

Digital

AUDIO

TV OUT

A

RightAnalog

Left

Optical

Coax.

Composite

S-Video

Component

Y

C

Y

Pr

Pb

Op-Amp

B

27MHz

DAC

Audio

OUT

S/PDIF

C

24.576MHz

96kHz

Clock

74AC04

RESET

D

SDRAM

2Mx32

EEPROM

E

Page Index

Block Diagram/Notes

0

Power, FIP input, Reset, 96kHz clock

1

2

EM8500 Main I/Os

3

EM8500 Power and decoupling

4

EM8500 Sys SDRAM + Flash

5

EM8500 MPEG SDRAM + UART

6

IDE / DVD LOADER

7

Video OUT

8

Audio OUT

9

(Debug) UARTs

10

(Debug) Flash Emulator

EM8500

Video

DACs

SDRAM

2Mx32

PWR: 3.3V/1.8V

FLASH

2MB

IDE Connector

F.I.Pannel

Emulator conn.

2 2

COM 1

COM 2

Debug Only

DVD Player - EM8500

1 1

REV 0.9

A

B

C

D

Title

DIVX PLAYER EM8500

Size Document Number Rev

<Doc> 0.9

B

111Saturday, March 29, 2003

Date: Sheet

of

E

A

B

C

D

E

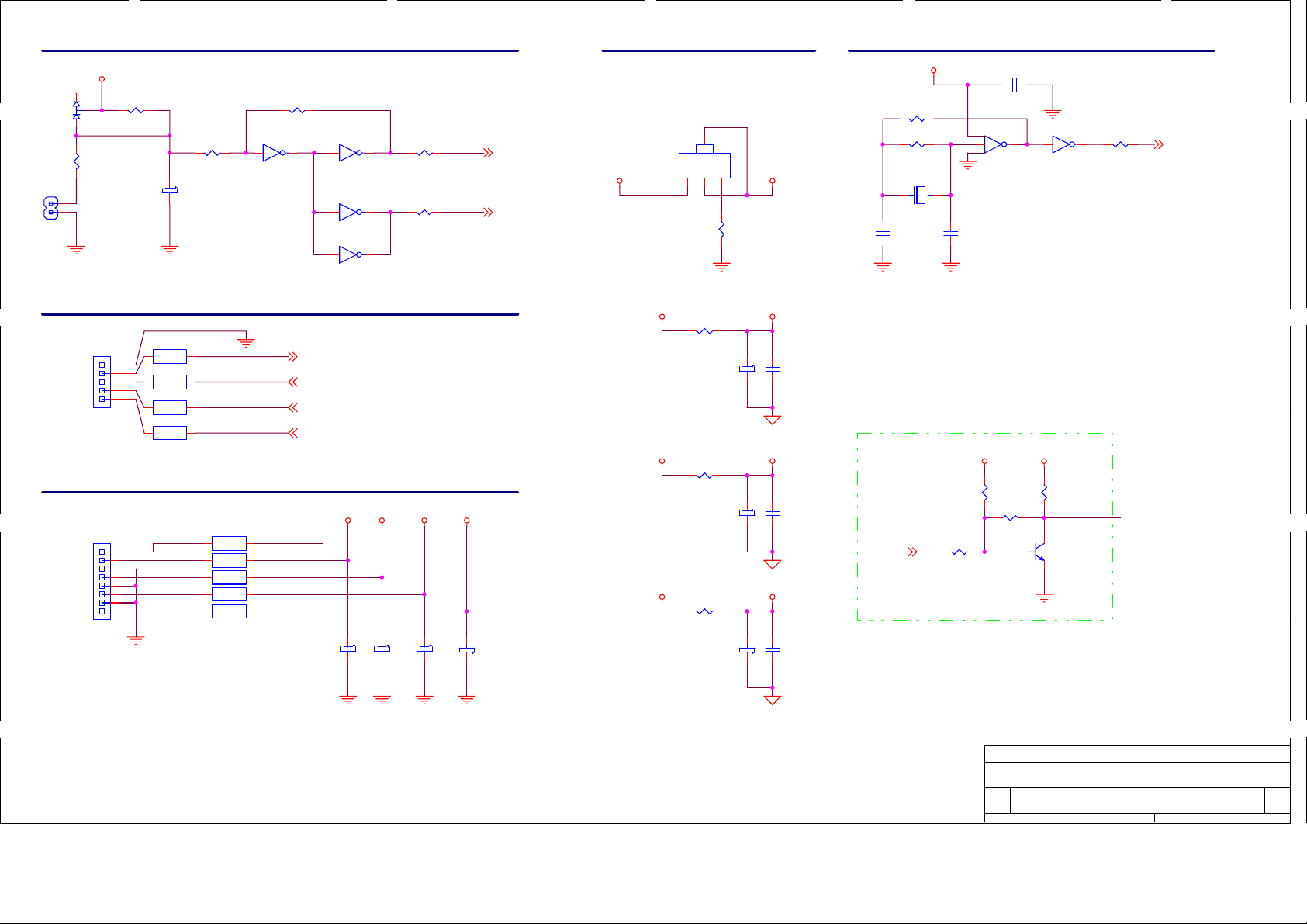

Reset

Vcc3V3

2

D12

4 4

J14

HDR1x2

3 3

3

Dual

1

R73

1K

NOT FITTING

1

2

Panel cn

J16

GND

IR

CLK

CS

DATA

HDR1x5

R7210K

R7110K

3 4

C10210uF/35V

L26

BEAD

1

2

L27

3

BEAD

4

5

L28

BEAD

L29

BEAD

U11B

74HC04

R7047K

9 8

5 6

11 10

J_FIP_IR

J_FIP_CLKO

J_FIP_FSTB

J_FIP_DATA

U11D

74HC04

U11C

74HC04

U11E

74HC04

22

R46

22

R47

RESET#

IDE_RESET#

Power Input

Neg12V

Vcc12V

C20647uF/25V

Vcc5VVcc3V3

C12647uF/25V

C20847uF/25V

C21047uF/25V

2 2

Stby

+3.3V

+5V

+12V

-12V

J10

HDR1x8

L19

1

2

3

4

5

6

7

8

BEAD

BEAD

BEAD

BEAD

BEAD

STANDBY

L20

L21

L22

L23

1.8V Regulator

AMS1117-1V8

VCC3v3

VIN

3

Vcc5V AUDP5V

22

Vcc12V AUDP12V

22

Neg12V AUDN12V

22

Z1

4

2

4

OUT

R91

R90

R92

1

R56

00

1 2

GND

Vcc1V8

C8110uF/35V

C8410uF/35V

C8210uF/35V

C830.1uF

C100.1uF

C90.1uF

24.576MHz

Vcc3V3

1 2

R76 220

1 2

R74 1M

X5

1 2

24.576MHz

12

C100

10pF

jump for power standby direct

STBY#

12

C101

10pF

R??

0R

1 2

R40 1k

C96 0.1uF

U11A

14

1 2

7

74HC04

R38

47k

1 2

1 2

Vcc5VVcc5V

12

1

U11F

13 12

74HC04

R39

10K

1 2

STANDBY

3

Q8

2

2N3904

1 2

R75 33

AUDCLK96

CONFIDENTIAL

1 1

Title

Clocks/Reset/Tooling

Size Document Number Rev

<Doc> 0.9

B

Saturday, March 29, 2003

Date: Sheet

A

B

C

D

E

of

211

A

B

C

D

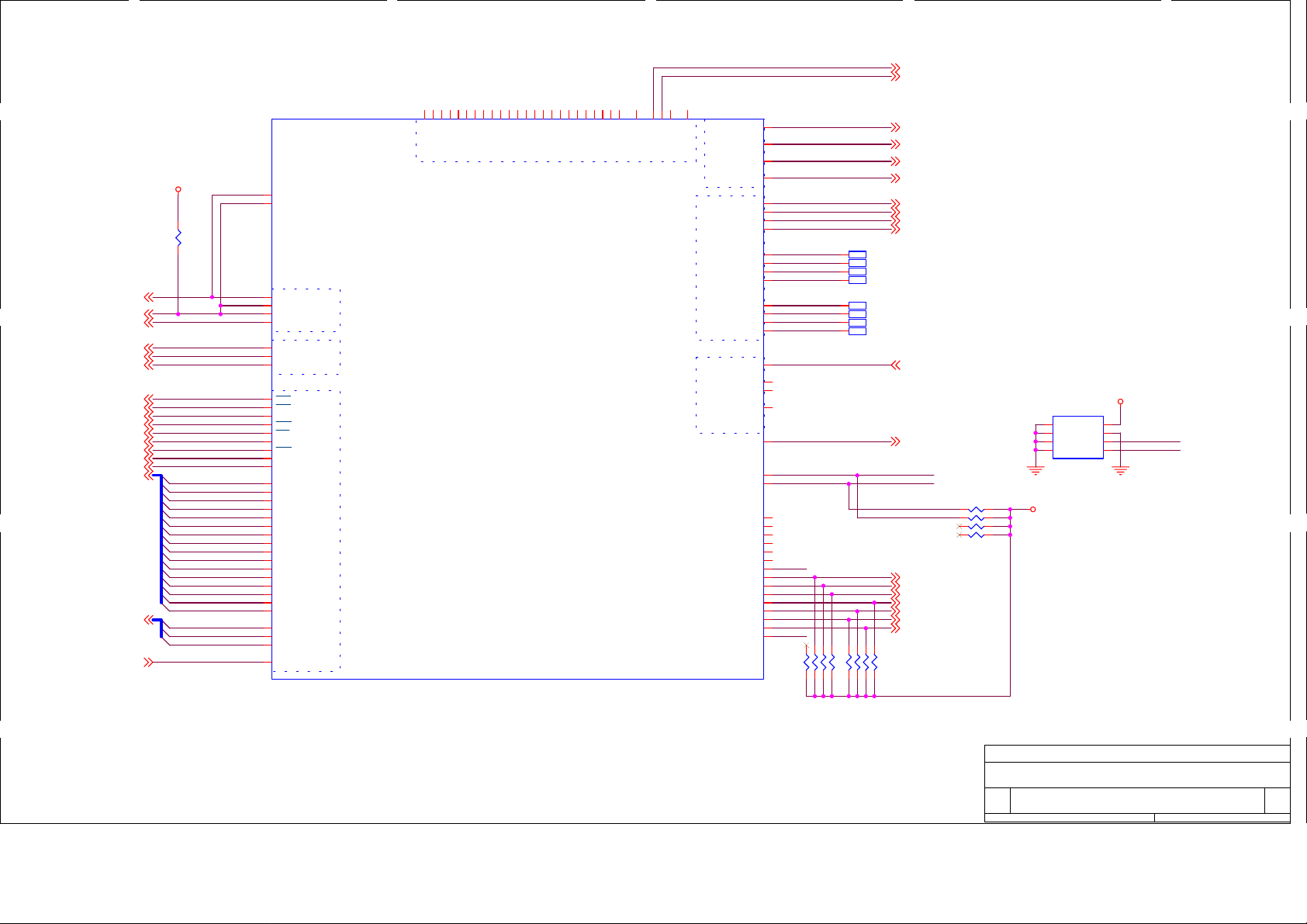

VSYNC

HSYNC

E

E2E3F4F5D3E4D2D1C2C1B1E5D4D6C3B2D7A2B3C4A1C5D9A3D5B4C6C7D8

P23

P22

P21

P20

P19

P18

P17

P16

P15

EM8500

P14

P13

P12

VIDEO OUT

P9P8P7P6P5P4P3P2P1

P11

P10

P0

PCLK

VVLD

VSYNC

HSYNC

TV OUT

AUDIO

OUT

I2S

IN-OUT

VCLK

CVBS

ACLK1

SCOUT1

SDOUT1

SFOUT1

ACLK2

SCOUT2

SDOUT2

SFOUT2

ACLK3

SCOUT3

SDOUT3

SFOUT3

SCIN

DAMCK

DADAT

DABCK

S/PDIF OUT

I2CM_SCLK

I2CM_SDATA

PIO_14

PIO_13

PIO_12

PIO_11

PIO_10

PIO_9

PIO_8

PIO_7

PIO_6

PIO_5

PIO_4

PIO_3

PIO_2

PIO_1

PIO_0

Y

U

V

J1

H3

G1

G5

K3

K2

M1

L2

K5

M5

J5

L5

N5

P6

R7

R5

K1

J4

G6

J3

U14

T14

D17

A16

B16

C16

D16

B15

FLASH_CRT

C15

D15

D13

A14

B14

A15

D14

C14

FLASH_CRT

E15

RP1

4x10K

O3P

O3N

O4P

O4N

O5P

O5N

O6P

O6N

1823

765

TV_CVBS

TV_Y/G/Y

TV_U/B/CVBS

TV_V/R/C

AMCLK

ASCLK

ADATA

ALRCK

T1

1

T2

1

T3

1

T4

1

T5

1

T6

1

T7

1

T8

1

AUDCLK96

Vcc3V3

24C0x

1

A0

2

A1

SPDIFOUT

I2CM_SCK

I2CM_SDA

RP3 4x10K

1 8

2

7

3

6

4

5

SCT-169

SCT-ENB

VGAEN#

STBY#

nSELYUV

MUTE

J_FIP_IR

4

1823

4

RP4

4x10K

765

3

A2

4 5

VSS SDA

Vcc3V3

8

VCC

7

WP

SCL

U2

I2CM_SCK

6

I2CM_SDA

V14

W13

W14

Y13

Y14

T15

U15

N16

Y20

R18

P16

R17

T18

V18

U18

V19

W18

Y17

V17

U17

V16

W16

W15

V15

Y15

Y16

U16

T16

T17

W17

R16

Y18

Y19

P18

W19

P17

A4

C8

U1A

PIO1_8

PIO1_7

FCLK

FDIN

FDOUT

FSTB

I2S_SCLK

I2S_SDATA

I2S_LRCLK

CS0

CS1

IRQ

IOW

IOR

DMAREQ

ACK

IORDY

NPCBLID

HD_0

HD_1

HD_2

HD_3

HD_4

HD_5

HD_6

HD_7

HD_8

HD_9

HD_10

HD_11

HD_12

HD_13

HD_14

HD_15

HA_0

HA_1

HA_2

DVD_CLKIN

FIP

I2S

IDE

4 4

Vcc3V3

R6710K

J_FIP_CLKO

3 3

2 2

J_FIP_DATA

J_FIP_FSTB

I2S_SCLK

I2S_SDATA

I2S_LRCLK

J_IDE_CS0#

J_IDE_CS1#

J_IDE_IRQ

J_IDE_DIOW#

J_IDE_DIOR#

J_IDE_DMARQ

J_IDE_DACK#

J_IDE_RDY

J_IDE_NPCBLID

J_IDE_PD[15..0]

J_IDE_PA[2..0]

J_IDE_DCLK

J_IDE_PD0

J_IDE_PD1

J_IDE_PD2

J_IDE_PD3

J_IDE_PD4

J_IDE_PD5

J_IDE_PD6

J_IDE_PD7

J_IDE_PD8

J_IDE_PD9

J_IDE_PD10

J_IDE_PD11

J_IDE_PD12

J_IDE_PD13

J_IDE_PD14

J_IDE_PD15

J_IDE_PA0

J_IDE_PA1

J_IDE_PA2

1 1

Title

EM8500 Decode

Size Document Number Rev

<Doc> 0.9

B

Saturday, March 29, 2003

Date: Sheet

A

B

C

D

311

E

of

Loading...

Loading...