www.vishay.com

TO-200AC (B-PUK)

PRODUCT SUMMARY

Package TO-200AC (B-PUK)

Diode variation Single SCR

I

T(AV)

V

DRM/VRRM

V

TM

I

GT

T

J

Phase Control Thyristors

(Hockey PUK Version), 560 A

FEATURES

• Center amplifying gate

• Metal case with ceramic insulator

• International standard case TO-200AC (B-PUK)

• Designed and qualified for industrial level

• Material categorization: For definitions of compliance

please see www.vishay.com/doc?99912

TYPICAL APPLICATIONS

• DC motor controls

• Controlled DC power supplies

• AC controllers

560 A

400 V to 2000 V

2.18 V

100 mA

-40 °C to 125 °C

VS-ST300CL Series

Vishay Semiconductors

MAJOR RATINGS AND CHARACTERISTICS

PARAMETER TEST CONDITIONS VALUES UNITS

I

T(AV)

I

T(RMS)

I

TSM

2

t

I

V

DRM/VRRM

t

q

T

J

ELECTRICAL SPECIFICATIONS

VOLTAGE RATINGS

TYPE NUMBER

VS-ST300C..L

Revision: 15-Apr-14

For technical questions within your region: DiodesAmericas@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

VOLTAGE

CODE

04 400 500

08 800 900

12 1200 1300

16 1600 1700

18 1800 1900

20 2000 2100

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

560 A

T

hs

T

hs

50 Hz 8000

60 Hz 8380

50 Hz 320

60 Hz 292

Typical 100 µs

V

DRM/VRRM

PEAK AND OFF-STATE VOLTAGE

, MAXIMUM REPETITIVE

NON-REPETITIVE PEAK VOLTAGE

V

1

, DiodesAsia@vishay.com, DiodesEurope@vishay.com

55 °C

1115 A

25 °C

kA2s

400 to 2000 V

-40 to 125 °C

V

, MAXIMUM

RSM

V

I

DRM/IRRM

AT T

MAXIMUM mA

Document Number: 94405

A

MAXIMUM

= TJ

J

50

VS-ST300CL Series

www.vishay.com

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL TEST CONDITIONS VALUES UNITS

Maximum average on-state current

at heatsink temperature

Maximum RMS on-state current I

T(RMS)

Maximum peak, one-cycle

non-repetitive surge current

Maximum I

Maximum I

2

t for fusing I2t

2

√t for fusing I2√t t = 0.1 to 10 ms, no voltage reapplied 3200 kA2√s

Low level value of threshold voltage V

High level value of threshold voltage V

Low level value of on-state slope resistance r

High level value of on-state slope resistance r

Maximum on-state voltage V

Maximum holding current I

Typical latching current I

I

T(AV)

I

TSM

T(TO)1

T(TO)2

t1

t2

TM

H

L

180° conduction, half sine wave

double side (single side) cooled

DC at 25 °C heatsink temperature double side cooled 1115

t = 10 ms

t = 8.3 ms 8380

t = 10 ms

t = 8.3 ms 7040

t = 10 ms

t = 8.3 ms 292

t = 10 ms

t = 8.3 ms 207

(16.7 % x π x I

(I > π x I

(16.7 % x π x I

(I > π x I

No voltage

reapplied

100 % V

reapplied

RRM

No voltage

reapplied

100 % V

reapplied

), TJ = TJ maximum 0.98

T(AV)

), TJ = TJ maximum 0.73

T(AV)

T(AV)

T(AV)

RRM

< I < π x I

< I < π x I

Ipk = 1635 A, TJ = TJ maximum, tp = 10 ms sine pulse 2.18 V

TJ = 25 °C, anode supply 12 V resistive load

Vishay Semiconductors

Sinusoidal half wave,

initial T

= TJ maximum

J

), TJ = TJ maximum 0.97

T(AV)

), TJ = TJ maximum 0.74

T(AV)

560 (275) A

55 (75) °C

8000

6730

320

226

kA2s

mΩ

600

1000

mA

A

V

SWITCHING

PARAMETER SYMBOL TEST CONDITIONS VALUES UNITS

Maximum non-repetitive rate of rise

of turned-on current

Typical delay time t

Typical turn-off time t

dI/dt

d

q

Gate drive 20 V, 20 Ω, t

T

= TJ maximum, anode voltage ≤ 80 % V

J

≤ 1 μs

r

DRM

Gate current 1 A, dIg/dt = 1 A/μs

V

= 0.67 % V

d

, TJ = 25 °C

DRM

ITM = 550 A, TJ = TJ maximum, dI/dt = 40 A/μs,

V

= 50 V, dV/dt = 20 V/μs, gate 0 V 100 Ω, tp = 500 μs

R

1000 A/µs

1.0

µs

100

BLOCKING

PARAMETER SYMBOL TEST CONDITIONS VALUES UNITS

Maximum critical rate of rise of

off-state voltage

Maximum peak reverse and

off-state leakage current

dV/dt T

I

RRM,

I

DRM

= TJ maximum linear to 80 % rated V

J

TJ = TJ maximum, rated V

DRM/VRRM

DRM

500 V/µs

applied 50 mA

Revision: 15-Apr-14

For technical questions within your region: DiodesAmericas@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

2

, DiodesAsia@vishay.com, DiodesEurope@vishay.com

Document Number: 94405

VS-ST300CL Series

www.vishay.com

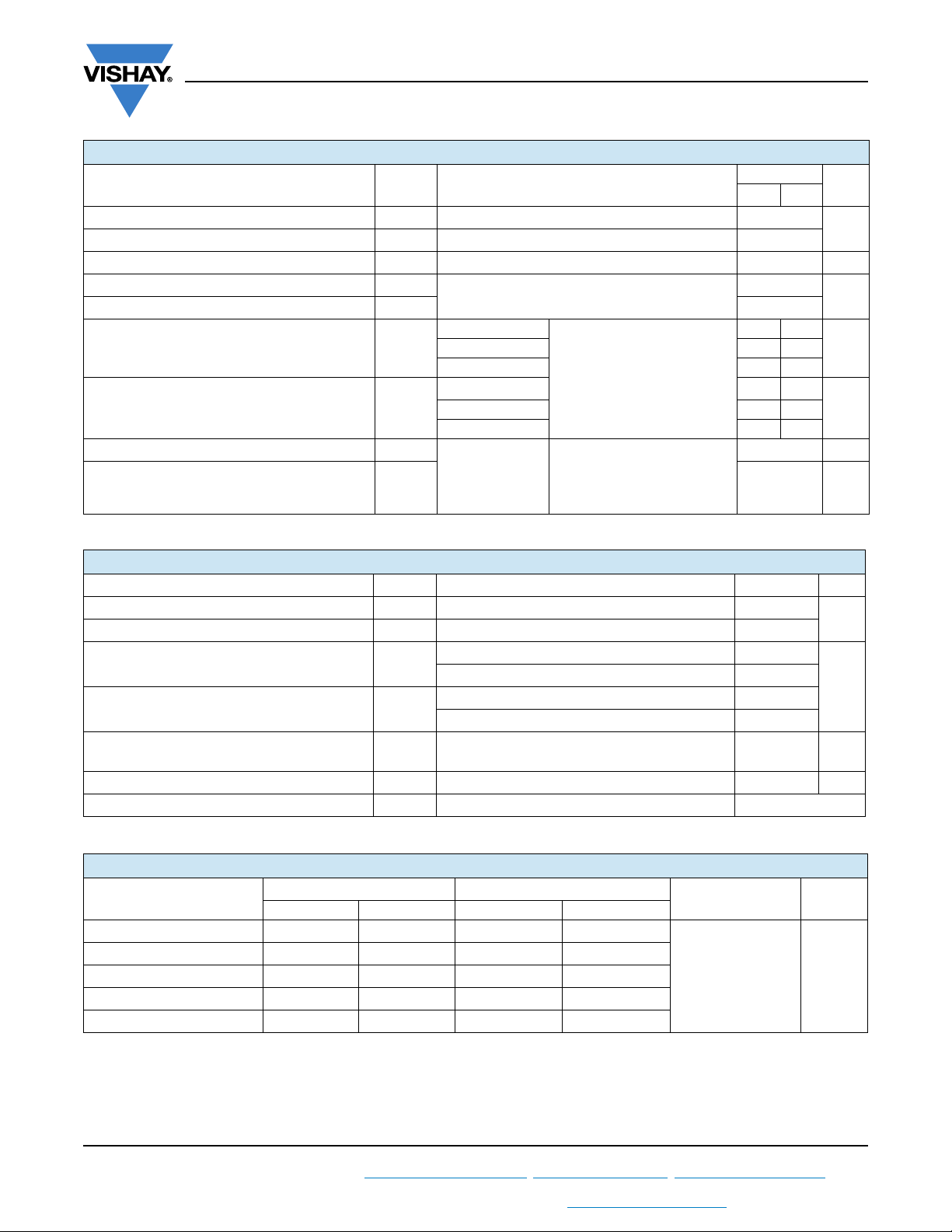

TRIGGERING

PARAMETER SYMBOL TEST CONDITIONS

Maximum peak gate power P

Maximum average gate power P

Maximum peak positive gate current I

Maximum peak positive gate voltage + V

Maximum peak negative gate voltage - V

DC gate current required to trigger I

DC gate voltage required to trigger V

DC gate current not to trigger I

DC gate voltage not to trigger V

G(AV)

GM

GT

GD

TJ = TJ maximum, tp ≤ 5 ms 10.0

GM

TJ = TJ maximum, f = 50 Hz, d% = 50 2.0

TJ = TJ maximum, tp ≤ 5 ms 3.0 A

GM

TJ = TJ maximum, tp ≤ 5 ms

GM

TJ = - 40 °C

= 25 °C 100 200

J

T

= 125 °C 50 -

J

TJ = - 40 °C 2.5 -

T

GT

= 25 °C 1.8 3.0

J

T

= 125 °C 1.1 -

J

Maximum required gate trigger/

current/voltage are the lowest

value which will trigger all units

12 V anode to cathode applied

Maximum gate current/

voltage not to trigger is the

TJ = TJ maximum

GD

maximum value which will not

trigger any unit with rated V

anode to cathode applied

Vishay Semiconductors

DRM

VALUES

TYP. MAX.

20

5.0

200 -

10.0 mA

0.25 V

UNITS

mAT

W

V

V

THERMAL AND MECHANICAL SPECIFICATIONS

PARAMETER SYMBOL TEST CONDITIONS VALUES UNITS

Maximum operating junction temperature range T

Maximum storage temperature range T

Maximum thermal resistance, junction to heatsink R

Maximum thermal resistance, case to heatsink R

J

Stg

thJ-hs

thC-hs

DC operation single side cooled 0.11

DC operation double side cooled 0.05

DC operation single side cooled 0.011

DC operation double side cooled 0.006

Mounting force, ± 10 %

Approximate weight 250 g

Case style See dimensions - link at the end of datasheet TO-200AC (B-PUK)

ΔR

CONDUCTION ANGLE

CONDUCTION

thJ-hs

SINUSOIDAL CONDUCTION RECTANGULAR CONDUCTION

SINGLE SIDE DOUBLE SIDE SINGLE SIDE DOUBLE SIDE

TEST CONDITIONS UNITS

180° 0.012 0.010 0.008 0.008

120° 0.014 0.015 0.014 0.014

90° 0.018 0.018 0.019 0.019

= TJ maximum K/W

T

J

60° 0.026 0.027 0.027 0.028

30° 0.045 0.046 0.046 0.046

Note

• The table above shows the increment of thermal resistance R

when devices operate at different conduction angles than DC

thJ-hs

-40 to 125

-40 to 150

9800

(1000)

°C

K/W

N

(kg)

Revision: 15-Apr-14

For technical questions within your region: DiodesAmericas@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

3

, DiodesAsia@vishay.com, DiodesEurope@vishay.com

Document Number: 94405

Loading...

Loading...