UNITRODE UCC1580-1, UCC1580-2, UCC1580-3, UCC1580-4, UCC2580-1 Technical data

...

查询UCC1580D-1供应商

Single Ended Active Clamp/Reset PWM

UCC1580-1,-2,-3,-4

UCC2580-1,-2,-3,-4

UCC3580-1,-2,-3,-4

FEATURES

Provides Auxiliary Switch Activation

•

Complementary to Main Power

Switch Drive

Programmable deadtime (Turn-on

•

Delay) Between Activation of Each

Switch

Voltage Mode Control with

•

Feedforward Operation

Programmable Limits for Both

•

Transformer Volt- Second Product

and PWM Duty Cycle

High Current Gate Driver for Both

•

Main and Auxiliary Outputs

Multiple Protection Features with

•

Latched Shutdown and Soft Restart

• Low Supply Current (100µA Startup,

1.5mA Operation)

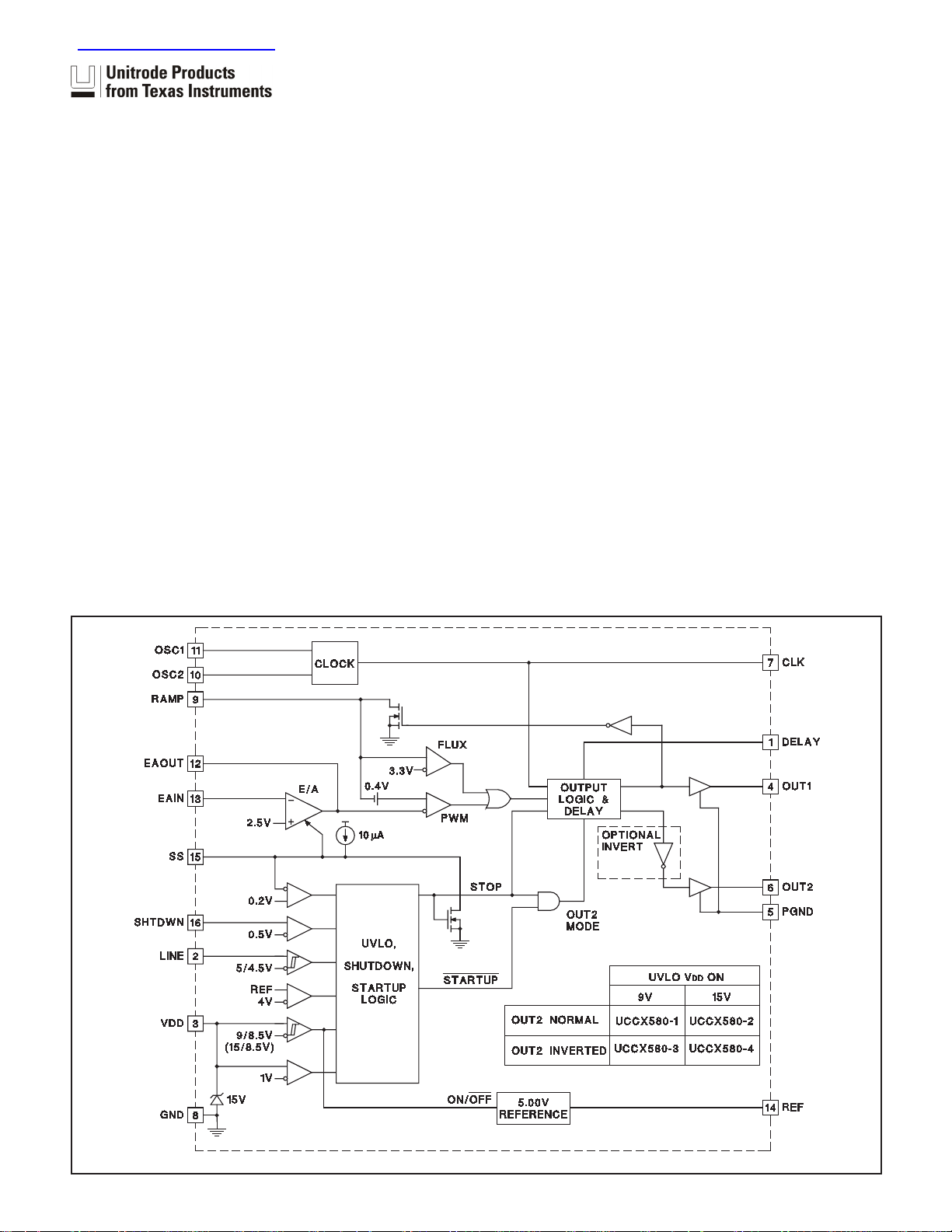

BLOCK DIAGRAM

DESCRIPTION

The UCC3580 family of PWM controllers is designed to implement a variety

of active clamp/reset and synchronous rectifier switching converter topolo

gies. While containing all the necessary functions for fixed frequency, high

performance pulse width modulation, the additional feature of this design is

the inclusion of an auxiliary switch driver which complements the main

power switch, and with a programmable deadtime or delay between each

transition. The active clamp/reset technique allows operation of single

ended converters beyond 50% duty cycle while reducing voltage stresses

on the switches, and allows a greater flux swing for the power transformer.

This approach also allows a reduction in switching losses by recovering en

ergy stored in parasitic elements such as leakage inductance and switch

capacitance.

The oscillator is programmed with two resistors and a capacitor to set

switching frequency and maximum duty cycle. A separate synchronized

ramp provides a voltage feedforward pulse width modulation and a pro

grammed maximum volt-second limit. The generated clock from the oscilla

tor contains both frequency and maximum duty cycle information.

(continued)

-

-

-

-

Pin Numbers refer to DIL-16 and SOIC-16 packages

SLUS292A - FEBRUARY 1999 - REVISED JANUARY 2002

UDG-95069-2

DESCRIPTION (cont.)

The main gate drive output (OUT1) is controlled by the

pulse width modulator. The second output (OUT2) is in

tended to activate an auxiliary switch during the off time

of the main switch, except that between each transition

there is deadtime where both switches are off, pro

grammed by a single external resistor. This design offers

two options for OUT2, normal and inverted. In the -1 and

-2 versions, OUT2 is normal and can be used to drive

PMOS FETs. In the -3 and -4 versions, OUT2 is inverted

and can be used to drive NMOS FETs. In all versions,

both the main and auxiliary switches are held off prior to

startup and when the PWM command goes to zero duty

cycle. During fault conditions, OUT1 is held off while

OUT2 operates at maximum duty cycle with a guaran

teed off time equal to the sum of the two deadtimes.

UCC1580-1,-2,-3,-4

UCC2580-1,-2,-3,-4

UCC3580-1,-2,-3,-4

Undervoltage lockout monitors supply voltage (VDD), the

-

precision reference (REF), input line voltage (LINE), and

the shutdown comparator (SHTDWN). If after any of

these four have sensed a fault condition, recovery to full

-

operation is initiated with a soft start. VDD thresholds, on

and off, are 15V and 8.5V for the -2 and -4 versions, 9V

and 8.5V for the -1 and -3 versions.

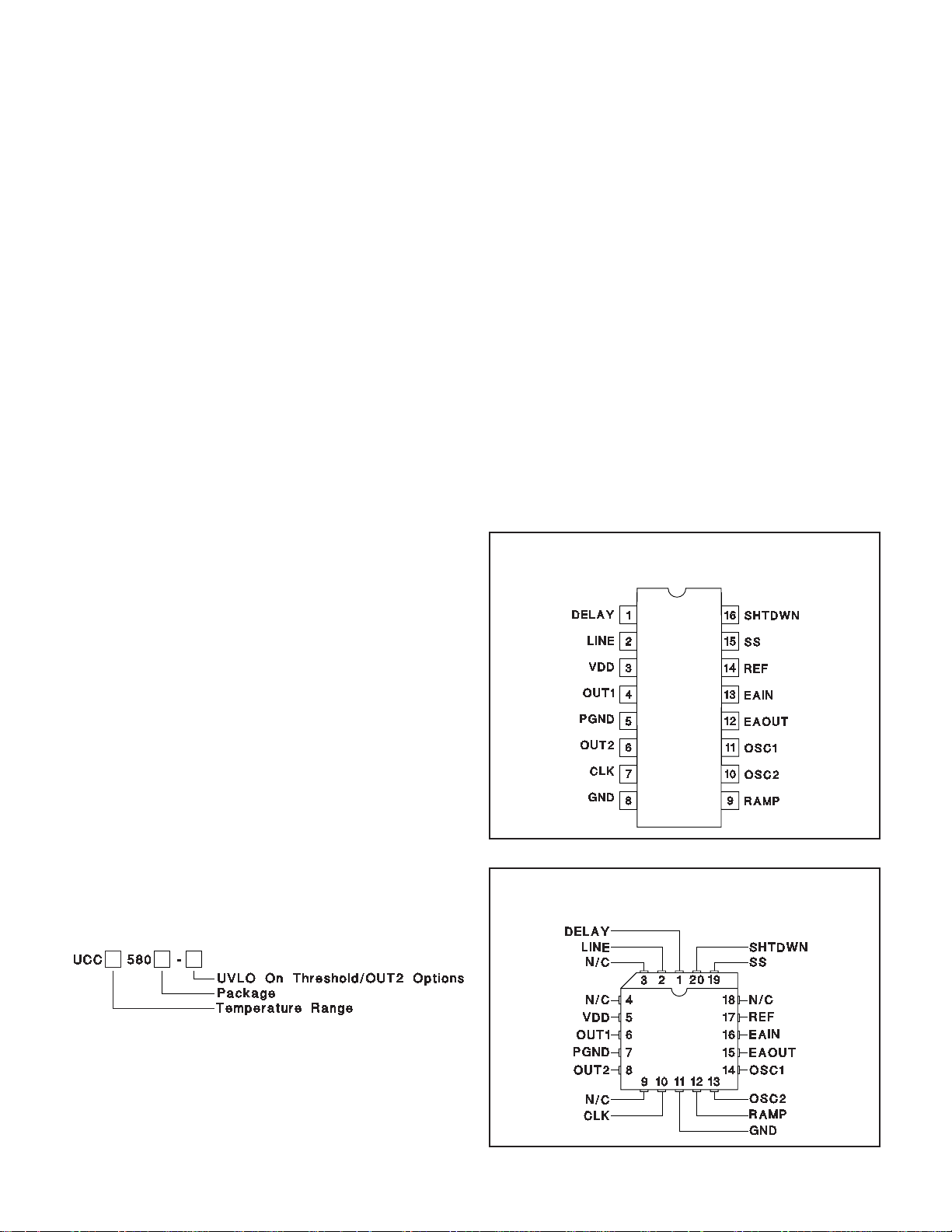

The UCC1580-x is specified for operation over the mili

tary temperature range of −55°C to 125°C. The

UCC2580-x is specified from −40°C to 85°C. The

UCC3580-x is specified from 0°C to 70°C. Package op

tions include 16-pin surface mount or dual in-line, and

20-pin plastic leadless chip carrier.

-

-

-

ABSOLUTE MAXIMUM RATINGS

VDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16V

I

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25mA

VDD

LINE, RAMP . . . . . . . . . . . . . . . . . . . . . . . . −0.3V to VDD + 1V

I

LINE,IRAMP

DELAY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.3V

I

DELAY

I

OUT1

I

OUT2

I

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −100mA to 100mA

CLK

OSC1, OSC2, SS, SHTDWN, EAIN . . . . . −0.3V to REF + 0.3V

I

EAOUT

I

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −30mA

REF

PGND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.2V to 0.2V

Storage Temperature . . . . . . . . . . . . . . . . . . . −65°C to +150°C

Junction Temperature. . . . . . . . . . . . . . . . . . . −55°C to +150°C

Lead Temperature (Soldering, 10 sec.) . . . . . . . . . . . . . +300°C

All voltages are with respect to ground unless otherwise stated.

Currents are positive into, negative out of the specified termi

nal. Consult Packaging Section of Databook for thermal limita

tions and considerations of packages.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −5mA

(tpw < 1µs and Duty Cycle < 10%) . . . . . . . −0.6A to 1.2A

(tpw < 1µs and Duty Cycle < 10%) . . . . . . . −0.4A to 0.4A

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −5mA to 5mA

ORDER INFORMATION

CONNECTION DIAGRAMS

DIL-16, SOIC-16 (Top View)

J, N, or D Packages

-

-

PLCC-20 (Top View)

Q Packages

2

UCC1580-1,-2,-3,-4

UCC2580-1,-2,-3,-4

UCC3580-1,-2,-3,-4

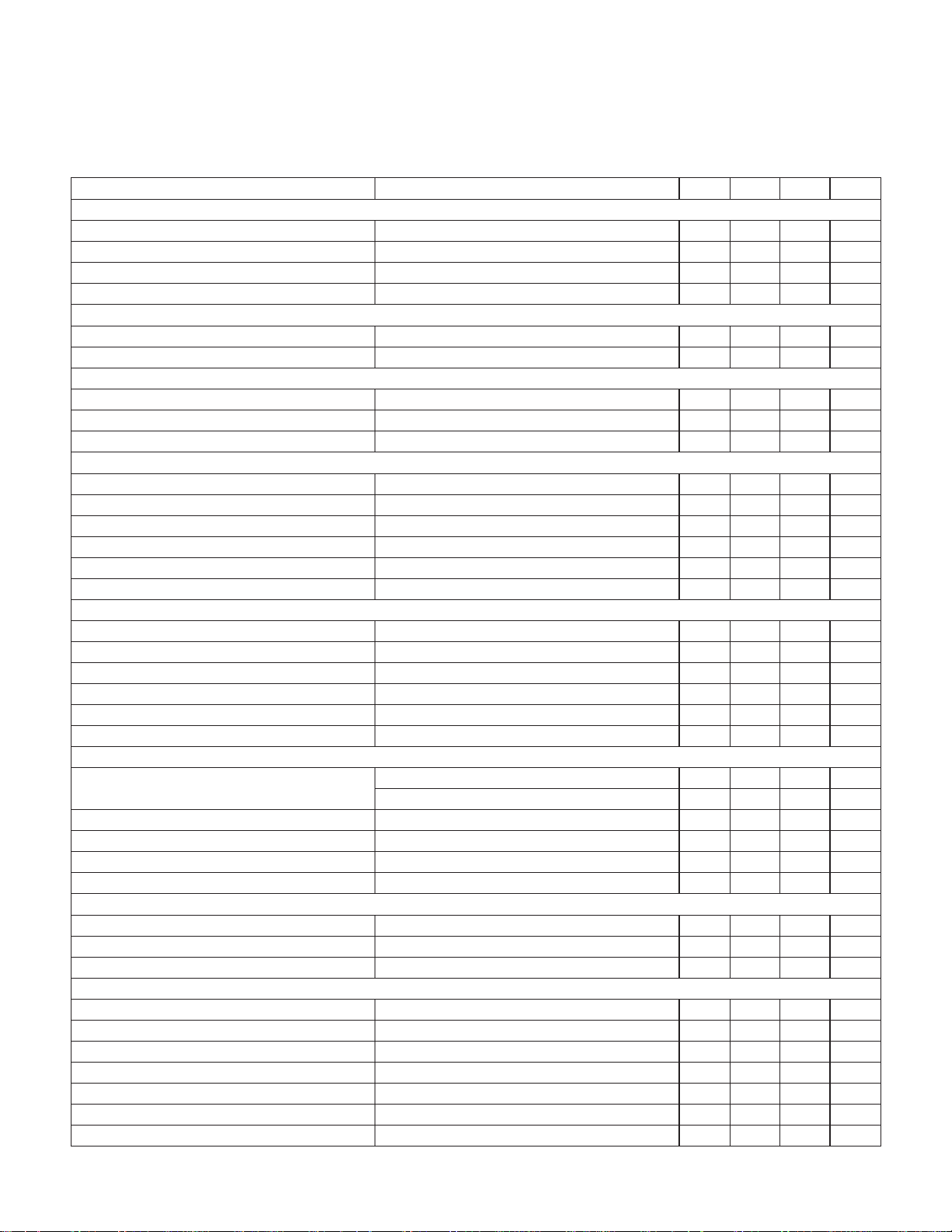

ELECTRICAL CHARACTERISTICS

= 12V, R1 = 18.2k, R2 = 4.41k, C

for the UCC2580, −55°C to 125°C for the UCC1580, T

= 100pF, R3 = 100k, C

T

Unless otherwise stated, all specifications are over the full temperature range, VDD

OUT1

A=TJ

= 0, C

.

= 0. TA= 0°C to 70°C for the UCC3580, −40°C to 85°C

OUT2

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Oscillator Section

Frequency 370 400 430 kHz

CLK Pulse Width 650 750 850 ns

I

CLK V

CLK V

OH

OL

= −3mA 4.3 4.7 V

CLK

I

= 3mA 0.3 0.5 V

CLK

Ramp Generator Section

I

Ramp V

OL

= 100µA 50 100 mV

RAMP

Flux Comparator Vth 3.16 3.33 3.50 V

Pulse Width Modulator Section

Minimum Duty Cycle OUT1, EAOUT = VOL 0 %

Maximum Duty Cycle OUT1, EAIN = 2.6V 63 66 69 %

PWM Comparator Offset 0.1 0.4 0.9 V

Error Amplifier Section

EAIN EAOUT = EAIN 2.44 2.5 2.56 V

I

EAIN

EAOUT, VOL EAIN = 2.6V, I

EAOUT, VOH EAIN = 2.4V, I

EAOUT = EAIN 150 400 nA

= 100µA 0.3 0.5 V

EAOUT

= −100µA 4 5 5.5 V

EAOUT

AVOL 70 80 dB

Gain Bandwidth Product f = 100kHz (Note 1) 2 6 MHz

Softstart/Shutdown Section

Start Duty Cycle EAIN = 2.4V 0 %

OL I

SS V

= 100µA 100 350 mV

SS

SS Restart Threshold 400 550 mV

I

SS

SHTDWN V

I

SHTDWN

TH

0.4 0.5 0.6 V

–20 –35 µA

50 150 nA

Undervoltage Lockout Section

VDD On UCC3580-2,-4 14 15 16 V

UCC3580-1,-3 8 9 10 V

VDD Off 7.5 8.5 9.5 V

LINE On 4.7 5 5.3 V

LINE Off 4.2 4.5 4.8 V

I

LINE

LINE = 6V 50 150 nA

Supply Section

VDD Clamp I

I

Start VDD < VDD On 160 250 µA

VDD

I

Operating No Load 2.5 3.5 mA

VDD

= 10mA 14 15 16 V

VDD

Output Drivers Section

OUT1 V

OUT1 V

OUT2 V

OUT2 V

High I

SAT

Low I

SAT

High I

SAT

Low I

SAT

OUT1 Fall Time C

OUT1 Rise Time C

OUT2 Fall Time C

= −50mA 0.4 1.0 V

OUT1

=100mA 0.4 1.0 V

OUT1

= −30mA 0.4 1.0 V

OUT2

= 30mA 0.4 1.0 V

OUT2

= 1nF, RS = 3Ω 20 50 ns

OUT1

= 1nF, RS = 3Ω 40 80 ns

OUT1

= 300pF, RS = 10Ω 20 50 ns

OUT2

3

Loading...

Loading...