TOSHIBA TC90A67F Technical data

東芝 CMOS デジタル集積回路 シリコン モノリシック

TC90A67F

ビデオデコーダ (PAL/NTSC) 内蔵1チップPIPコントローラ

TC90A67F は ADC、ビデオデコーダ (PAL/NTSC)、垂直フィル

タ、フィールドメモリ、DAC を内蔵した TV 用 PIP コントロール IC

です。子画面コンポジット信号、親画面 HD、VD タイミング信号を

入力すると、I

YUV もしくは RGB の信号形態で出力されます。

特

特 長長長長

特特

子画面用ビデオデコーダ部

子画面用ビデオデコーダ部

子画面用ビデオデコーダ部子画面用ビデオデコーダ部

· fH同期システムクロック(24 MHz)

· NTSC、PAL、M-PAL、N-PAL 対応 (SECAM 時は白黒)

· 入力信号方式自動判別

· 8 bit ADC 内蔵

· デジタルフィルタによる Y/C 分離回路内蔵

· ACC、カラーキラー回路内蔵

· 画質調整 (コントラスト、ブライトネス、カラー、TINT)

· 輝度信号用ピーキング回路内蔵

· V-CHIP 規格対応スライス回路内蔵

· 無信号判別回路内蔵

親システムクロック部

親システムクロック部

親システムクロック部親システムクロック部

· 外付け PLL 回路 (推奨 TI 性 TLC2933) (親ビデオデコーダから HD を入力)

PIP コントローラ

コントローラ

コントローラコントローラ

· 525-60 Hz、626-50 Hz 対応

· 垂直フィルタ用ラインメモリ内蔵

· フィールドメモリ (181 kbit) 内蔵

· 画面サイズ: 1 画面 PIP: 1/9、1/16、6 画面 PIP: 1/36 (デフォルト)

· 水平間引き: 1/3、1/4、1/6、1/8、垂直間引き: 1/3、1/4、1/5、1/6 (水平/垂直を独立に設定可)

· 表示位置可変

· YUV、RGB 用 8 bit DAC 3 ch 内蔵

· RGB マトリックス回路内蔵

その他

その他

その他その他

· 42 MHz 発振器

· I2C bus 対応

· パッケージ : QFP 80

· 電源電圧 : 3.3 V 単一

2

C バスで選択された表示モードに従った子画面信号が

質量: 1.6 g (標準)

TC90A67F

1

2002-02-08

TC90A67F

Yout

Rout

Bout

Ys

2002-02-08

X´tal

DAC YUV/RGB

Field

Memory

PIP

Control

DAC

DAC

42 MHz

Oscillator

Gene

VD-main

Gene

Main-

Timing

Gene

HD-main

42 MHz

VD

main

HD

main

Line

PDVCO

Vertical

Y signal

Filtering

Processing

LPF

ADC

Memory

Demo

Chroma

Gene

VD-sub

fsc

PLL

Clamp BPF ACC

fH PLL

Sync

Sepa

Sepa

V.Sync

C BUS

2

I

Slice

V-chip

2

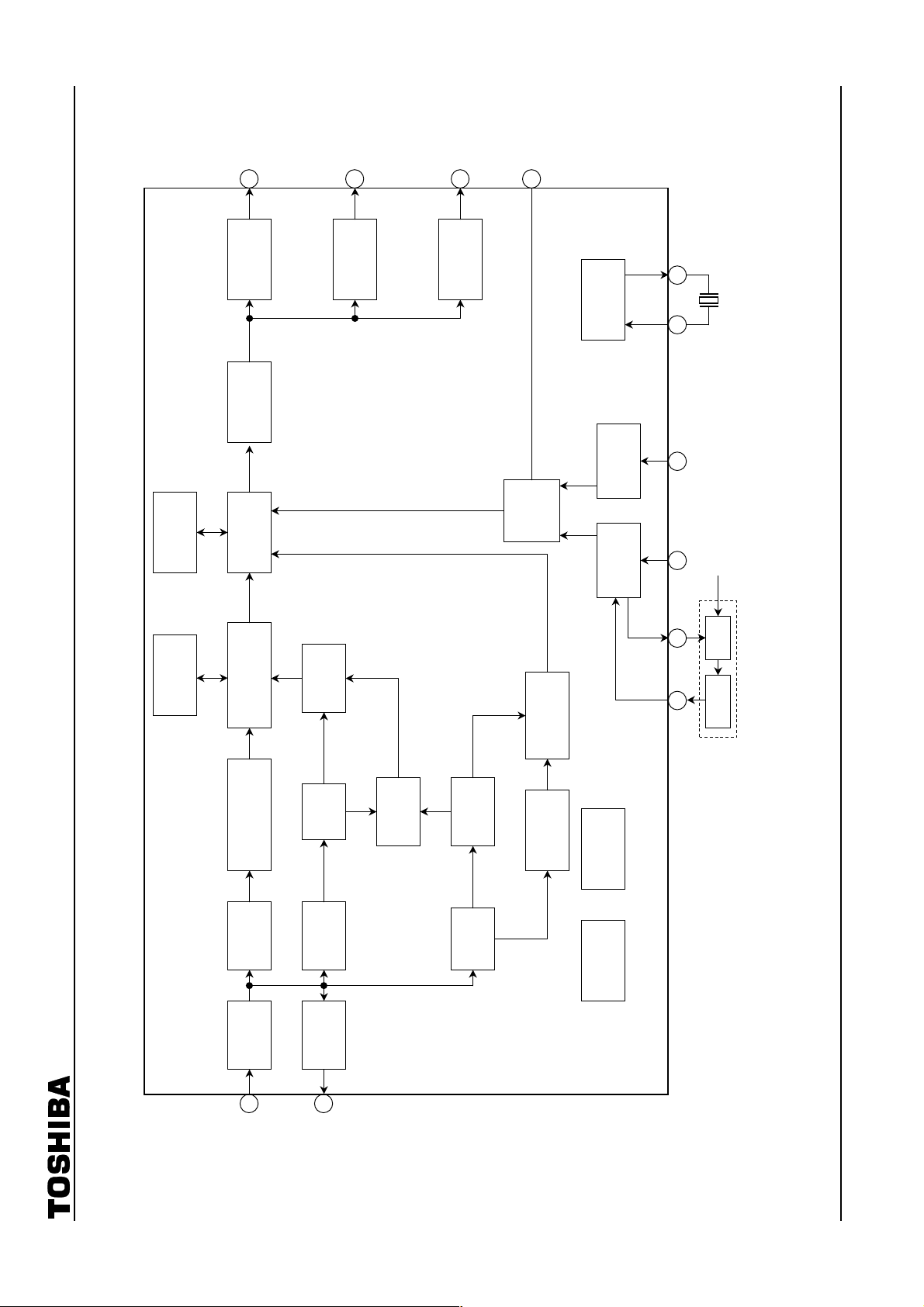

ブロック図

ブロック図ブロック図

ブロック図

CVI

CLMP

TC90A67F

A

R

2002-02-08

DD

SS

CSTD

CVREF

CFIELD

CHREF

40

39

NC

CKILL

VCHIP

RESET

DD

V

SDA

SCL

NC

PIPEN

YS

NC

SS

V

PVD

53 52 51 50 49 48 47 46 45 44 43 42 41

DD

V

NC

PHREF

CKPSEL

CKP

SS

V

PHD

NC

TESTM0

TESTM1

TESTM2

64 63 62 61 60 59 58 57 56 55 54

38

PFIELD

37

V

36

V

35

34

NC

33

TC90A67F

NC

32

(QFP80)

V

31

DD

NC

30

XO

29

XI

28

V

27

SS

TEST

26

V

25

DD

18 19 20 21 22 23 24

17

16 15 14131211109

1 8765432

SS

DD

SS

DD

SS

DD

SS

SS

V

NC

NC

NC

REF

NC

CVI

CKC

CKIN

V

REFL

REFH

CLMP

AV

AV

BIASD

AV

AV

V

AV

AV

V

BIAS

AV

CKCSEL

FILTE

3

CKOUT

65

66

67

68

69

70

SS

DD

V

V

TEST2

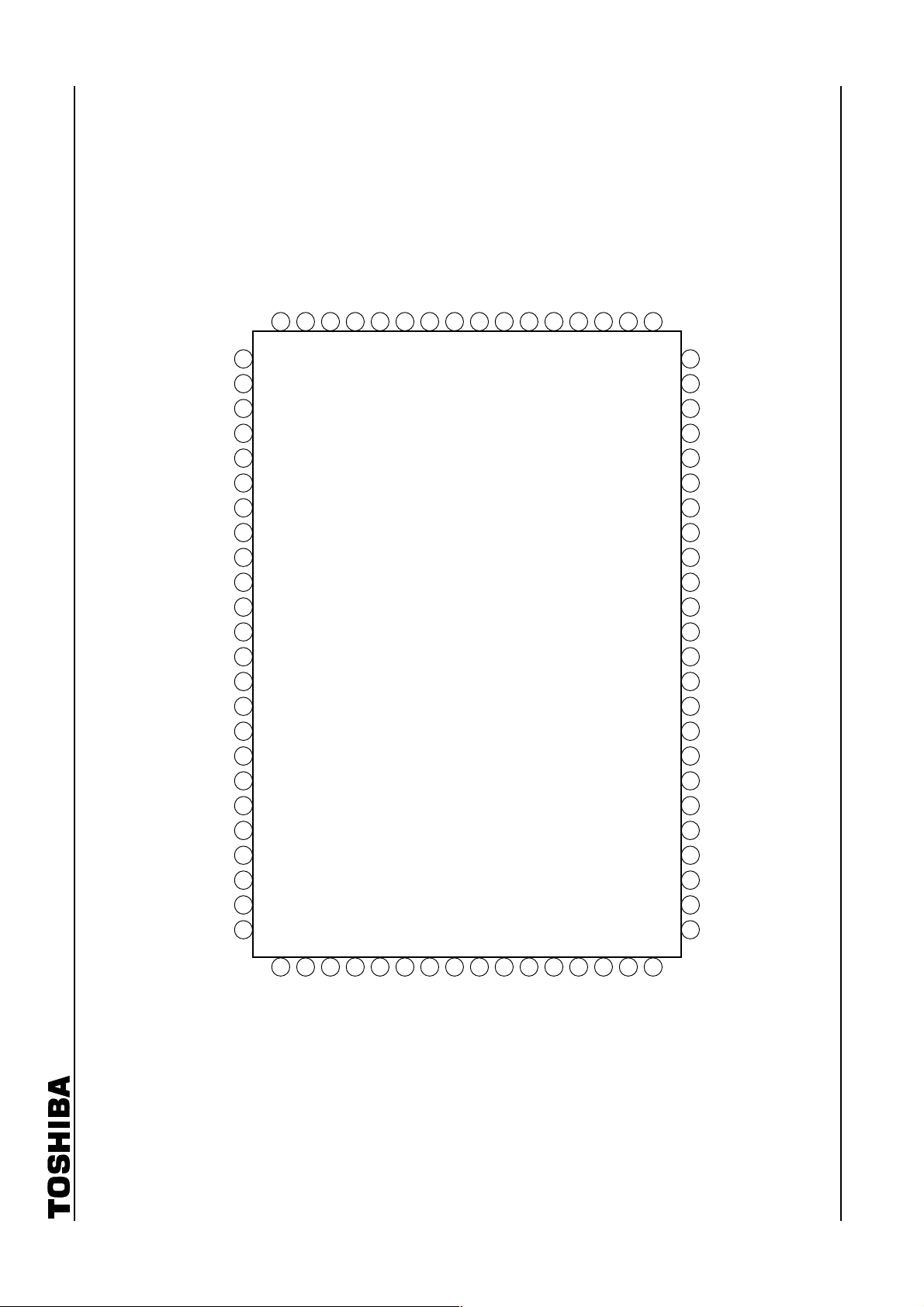

端子接続図

端子接続図端子接続図

端子接続図

NC

NC

REFD

V

71

BIAS2

72

NC

73

BIAS1

74

NC

75

DD

AV

76

BOUT

77

SS

AV

78

ROUT

79

DD

AV

80

YOUT

TC90A67F

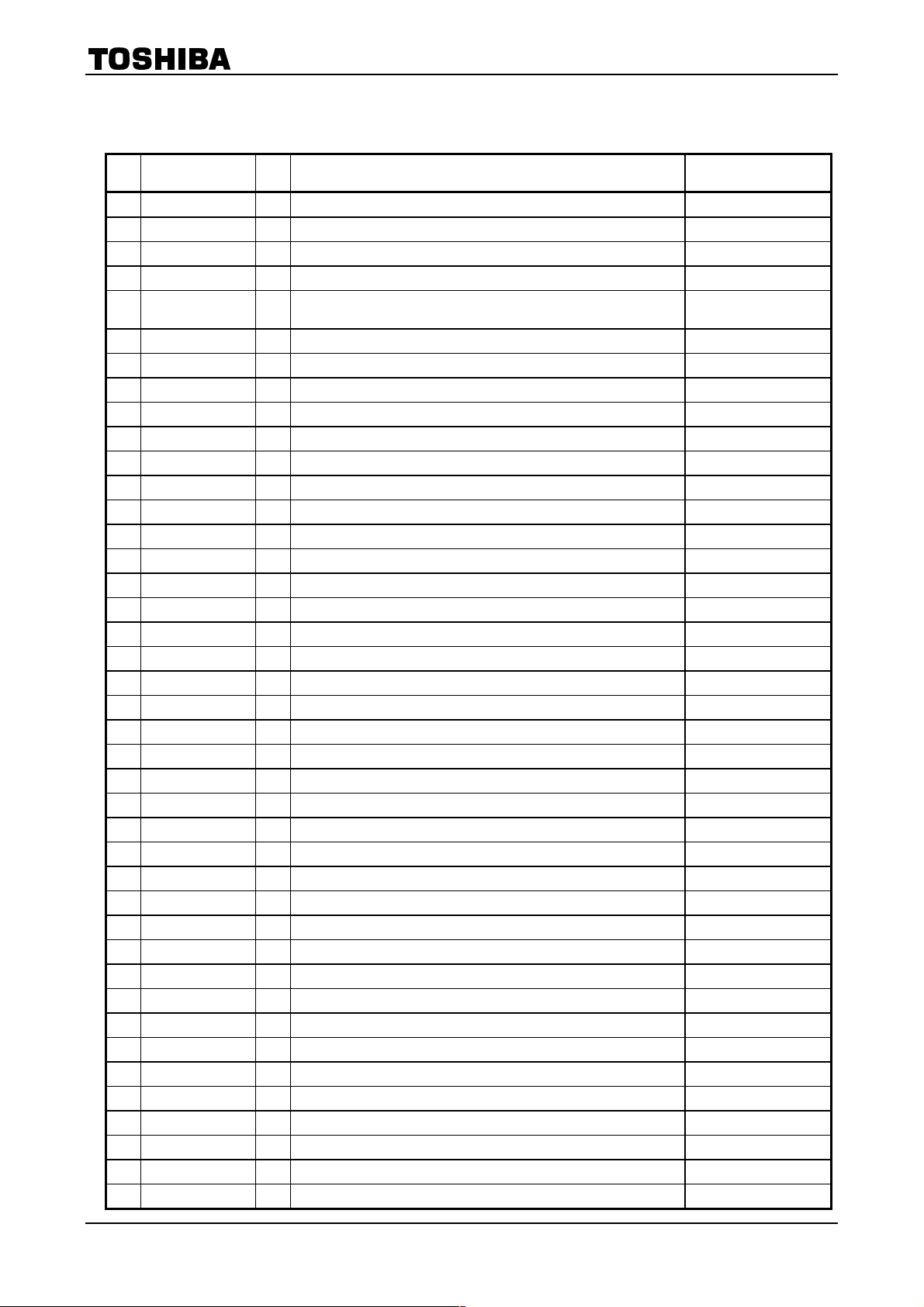

端子機能

端子機能

端子機能端子機能

QFP80-P-1420-0.80B

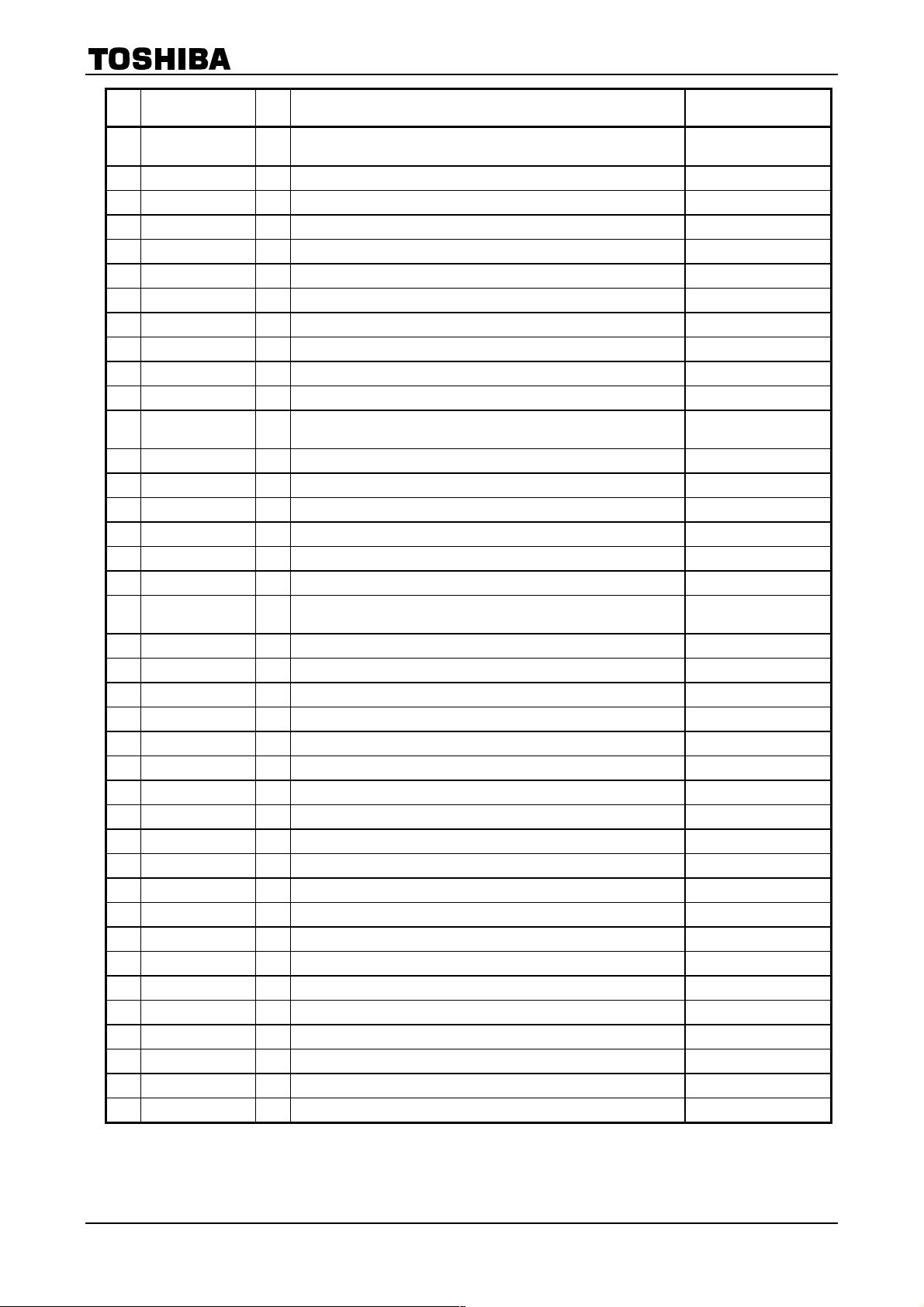

端子 名称 I/O 説明 動作条件

1 AVSS ¾ 映像 DAC 用 GND ¾

2 BIASA ¾ ADC 用バイアス端子 ¾

3 V

4 AVSS ¾ ADC 用 GND ¾

5 CVI I 映像入力端子

6 AVDD ¾ ADC用電源 ¾

7 V

8 AVSS ¾ 子画面 H-lock クロック再生用 DAC GND ¾

9 NC ¾¾ ¾

10 CKOUT O 子画面 H-lock クロック出力端子 6 MHz

11 AVDD O子画面 H-lock クロック再生用 DAC 電源 ¾

12 BIASD ¾ 子画面 H-lock クロック再生用 DAC バイアス端子 ¾

13 V

14 NC ¾¾ ¾

15 NC ¾¾ ¾

16 AVSS ¾ 8 逓倍 VCO GND ¾

17 FILTER O 8 逓倍 VCO 用フィルタ接続端子 ¾

18 AVDD ¾ 8逓倍 VCO VDD ¾

19 CKIN I 子 VCO 用 H-lock クロック入力端子 6 MHz

20 NC ¾¾ ¾

21 VSS ¾ デジタル GND ¾

22 CKC I 子画面用 H-lock クロック入力端子 24 MHz

23 CKCSEL I 子画面用内蔵 VCO/外付 VCO 切り替え端子 L: 内蔵、H: 外付け

24 CLMP O ペデスタルクランプ制御端子 ¾

25 VDD ¾ デジタル電源 ¾

26 TEST I テスト用入力端子 通常動作時 H 固定

27 VSS ¾ 42 MHz 水晶発振回路用 GND ¾

28 XI I 42 MHz 水晶発振用インバータ入力端子 ¾

29 XO O 42 MHz 水晶発振用インバータ出力端子 ¾

30 NC ¾¾ ¾

31 VDD ¾ 42 MHz水晶発振回路用電源 ¾

32 NC ¾¾ ¾

33 NC ¾¾ ¾

34 CSTD O 標準、非標準判定出力端子 ¾

35 VSS ¾ DRAM 用 GND ¾

36 VDD ¾ DRAM 用 VDD ¾

37 PFIELD O 親映像用フィールド判定信号出力端子 H: even, L: odd

38 CFIELD O 子映像用フィールド判定信号出力端子 H: even, L: odd

39 CVREF O 子垂直同期信号出力端子 ¾

40 CHREF O 子水平基準信号出力端子 ¾

41 NC ¾¾ ¾

¾ ADC 用ハイレベルリファレンス電圧端子 ノーマル時: 2.3 V

REFH

ダイナミックレンジ:

1.32 V

p-p

¾ ADC 用ローレベルリファレンス電圧端子 ノーマル時: 1.0 V

REFL

¾ 子画面 H-lock クロック再生用 DAC リファレンス電圧端子 ノーマル時: 1.8 V

REF

4

2002-02-08

TC90A67F

端子 名称 I/O 説明 動作条件

42 CKILL O カラーキラー判定出力端子

43 VCHIP I ライン判定信号出力端子 23rd-line: H

44 RESET I リセット端子 L: リセット

45 VDD ¾ デジタル電源 ¾

46 SDA I/O I2C バスデータ入力、アクノリッジ出力端子 5 V耐圧

47 SCL I I2C バスクロック入力端子 5 V 耐圧

48 NC ¾¾ ¾

49 PIPEN I PIPイネーブル端子 通常動作時 H 固定

50 YS O 親、子信号切り替え信号出力端子 子画面期間時 H

51 NC ¾¾ ¾

52 VSS Oデジタル GND ¾

53 PVD I 親垂直同期信号入力端子

54 VDD Oデジタル電源 ¾

55 NC ¾¾ ¾

56 PHREF O 親水平基準信号出力端子 ¾

57 CKPSEL I 親画面用 H-lock クロック入力切り替え端子 L: 24 MHz, H: 48 MHz

58 CKP I 親 H-lock クロック入力端子 ¾

59 VSS ¾ デジタル GND ¾

60 PHD I 親水平同期信号入力端子

61 NC ¾¾ ¾

62 TESTM0 I テスト用入力 通常動作時 H 固定

63 TESTM1 I テスト用入力 通常動作時 H 固定

64 TESTM2 I テスト用入力 通常動作時 H 固定

65 TEST2 I テスト用入力 通常動作時 H 固定

66 VDD ¾ デジタル電源 ¾

67 VSS ¾ デジタル GND ¾

68 NC ¾¾ ¾

69 NC ¾¾ ¾

70 V

71 BIAS2 ¾ 映像 DAC 用バイアス端子 2 ¾

72 NC ¾¾ ¾

73 BIAS1 ¾ 映像 DAC 用バイアス端子 1 ¾

74 NC ¾¾ ¾

75 AVDD ¾ 映像 DAC 用電源 ¾

76 BOUT O アナログ映像出力端子 (B-Y or B) ¾

77 AVSS ¾ 映像 DAC 用 GND ¾

78 ROUT O アナログ映像出力端子 (R-Y or R) ¾

79 AVDD ¾ 映像 DAC 用電源 ¾

80 YOUT O アナログ映像出力端子 (Y or G) ¾

I 映像 DAC 用基準電圧入力端子 ノーマル時: 1.8 V

REFD

H: color killer ON,

L: OFF

5 V 耐圧、

ノーマル時: 負極性

5 V 耐圧、

ノーマル時: 正極性

5

2002-02-08

システムブロック図

deo

sTC90A6

システムブロック図

システムブロック図システムブロック図

TC90A67F

PIP Mode

Main Vi

Chroma

Demo

Sync

Processor

H/V

PIP

Controller

Sub

V/C/J

RGB Text

Processor

YUV

Processor

YUVYUV

Y

7F

1 PIP MODE

Size: 1/9, 1/16

6 PIP MODE 1

Size: 1/36 ´ 6

6 PIP MODE 2

Size: 1/36 ´ 6

6

2002-02-08

TC90A67F

機能説明

機能説明

機能説明機能説明

本 IC は子画面用水平・垂直同期回路、子画面用色復調回路、親画面用水平・垂直タイミング発生回路、PIP コントロール

回路で構成されています。

子画面用色復調回路はデジタル回路で構成されており、M-NTSC、PAL 、M-PAL、N-PAL に対応できます。また、f

同期型デジタル PLL 回路によるシステムクロック (24 MHz) を採用することにより、子画面処理を容易に行うことがで

きます。親画面用水平・垂直タイミング回路はアナログ PLL 回路で f

ロックにしています。

PIP コントロール回路は水平間引きフィルタ、垂直間引きフィルタ、ラインメモリ、フィールドメモリから構成されてお

り、水平・垂直の間引き率などを変えることにより、さまざまな表示をすることができます。

1. ADC、クランプ

2. 親画面用水平・垂直同期再生回路

3. f

4. 水平間引き

、クランプ

、クランプ、クランプ

子画面映像は CVI 端子に入力し AD 変換を行い、デジタルデータに変換されます。ADC の D レンジは内部で

固定になっており、1.32 V

かけておりクランプ基準電圧は CLMP 端子から出力されます。よって、映像信号をコンデンサで AC カップリ

ングし、CLMP 端子から出力されている基準電圧に帰還抵抗を介して接続してください。ペデスタルレベルは約

1.32 V (64LSB) になります。

親画面用水平・垂直同期再生回路

親画面用水平・垂直同期再生回路親画面用水平・垂直同期再生回路

読み出し系クロック、タイミングを再生するために、親画面の HD、VD をそれぞれ PHD、PVD に入力して

ください。この PHD、PVD 端子は 5 V 耐圧になっています。極性は内部に反転回路があり、29hex: WVINV、

WHINV を 1 にすると内部で反転します。初期値では、HD: 正極性、VD: 負極性入力となります。

外部 VCO からのクロックは 2 種類選択でき (24 MHz、48 MHz)、切り替えは CKPSEL 端子 (57 ピン) で行

います。(CKPSEL = L: 24 MHz、CKPSEL = H: 48 MHz)

なお、内部分周比 (15hex: PHC で設定) を変化させると発振周波数を変えることができます。

同期システムクロック

同期システムクロック

同期システムクロック同期システムクロック

H

AD コンバータによりデジタル信号に変換されたデジタルビデオ信号より、水平同期分離、水平同期回路を通

じて PLL 回路を構成し、f

を LPF に通し、内蔵の VCO に入力することで 24 MHz のシステムクロックを発生します。ただし、発振周波

数は内部分周比 (20hex: CHLOADN、CHLOADP) を変化させることにより、可変することができます。(初期

値では、f

水平間引き

水平間引き水平間引き

PIP 処理を行う場合、輝度信号、復調後の色信号に対してそれぞれダウンサンプリングする必要があります。

水平の間引き率は 10hex: HWS で 4 状態を設定できます。

= 15.734 kHz 時 24.230 MHz、fH = 15.625 kHz 時 24.063 MHz となります。)

H

です。(top 電圧: 2.31 V、bottom 電圧: 0.99 V) 本 IC ではペデスタルクランプを

p-p

に位相同期した 6 MHz クロックをクロック用 DAC より出力します。このクロック

H

同期型クロック (24 MHz) を発生し、システムク

H

H

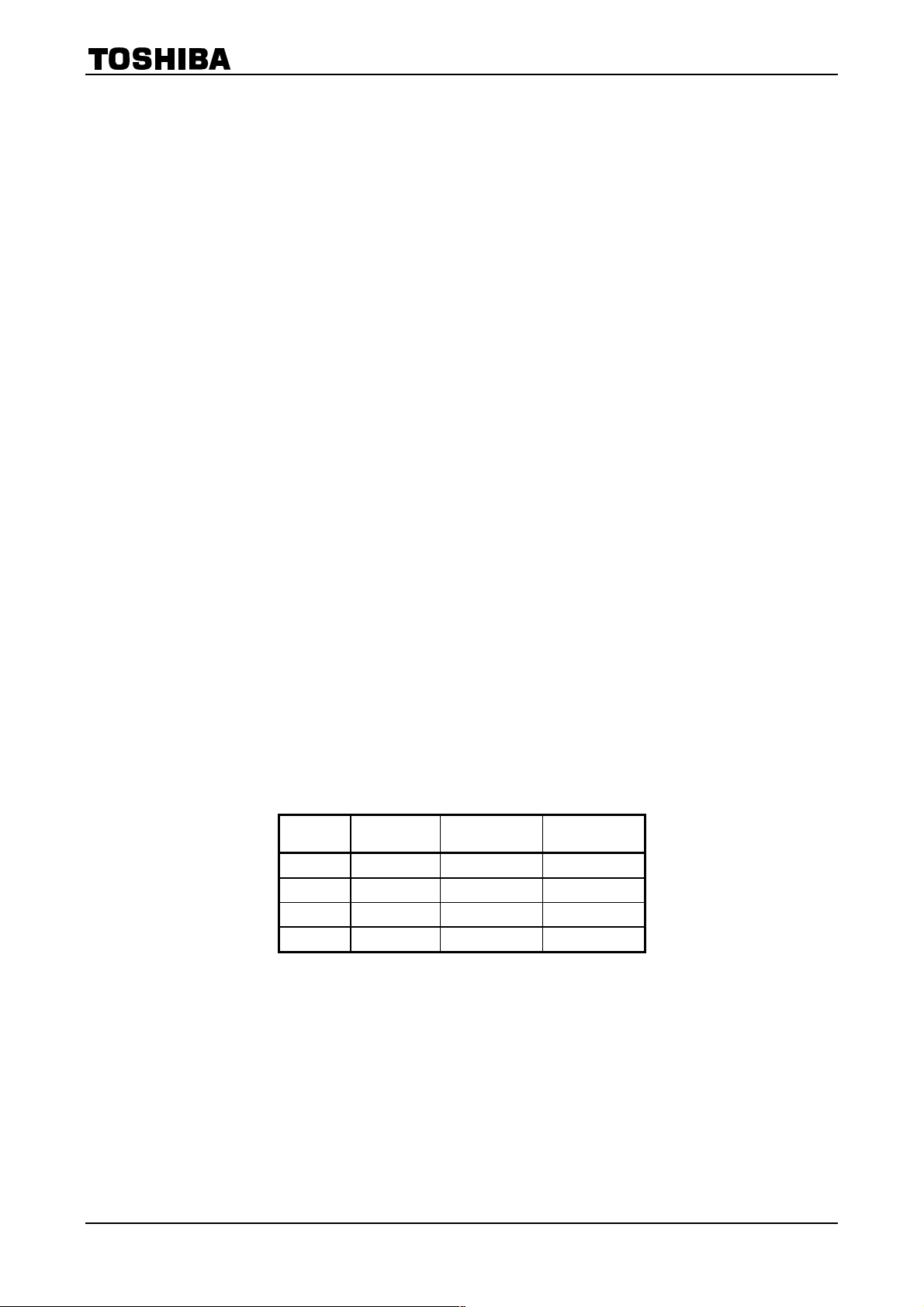

HWS [1:0] 水平間引き率 輝度信号レート 色差信号レート

00 1/3 4 MHz 1 MHz

01 1/4 3 MHz 0.75 MHz

10 1/6 2 MHz 0.5 MHz

11 1/8 1.5 MHz 0.375 MHz

水平のサンプル数は 1Ahex: HSPL で設定します。設定値としては 1 step 当たり輝度信号: 4 サンプル、復調

色信号: それぞれ 1 サンプルとなります。また、間引きに合わせて輝度、色信号に対し LPF が必要となります。

本 IC では間引き用 LPF を輝度信号 2 種類、色信号 6 種類変化させることができます。

7

2002-02-08

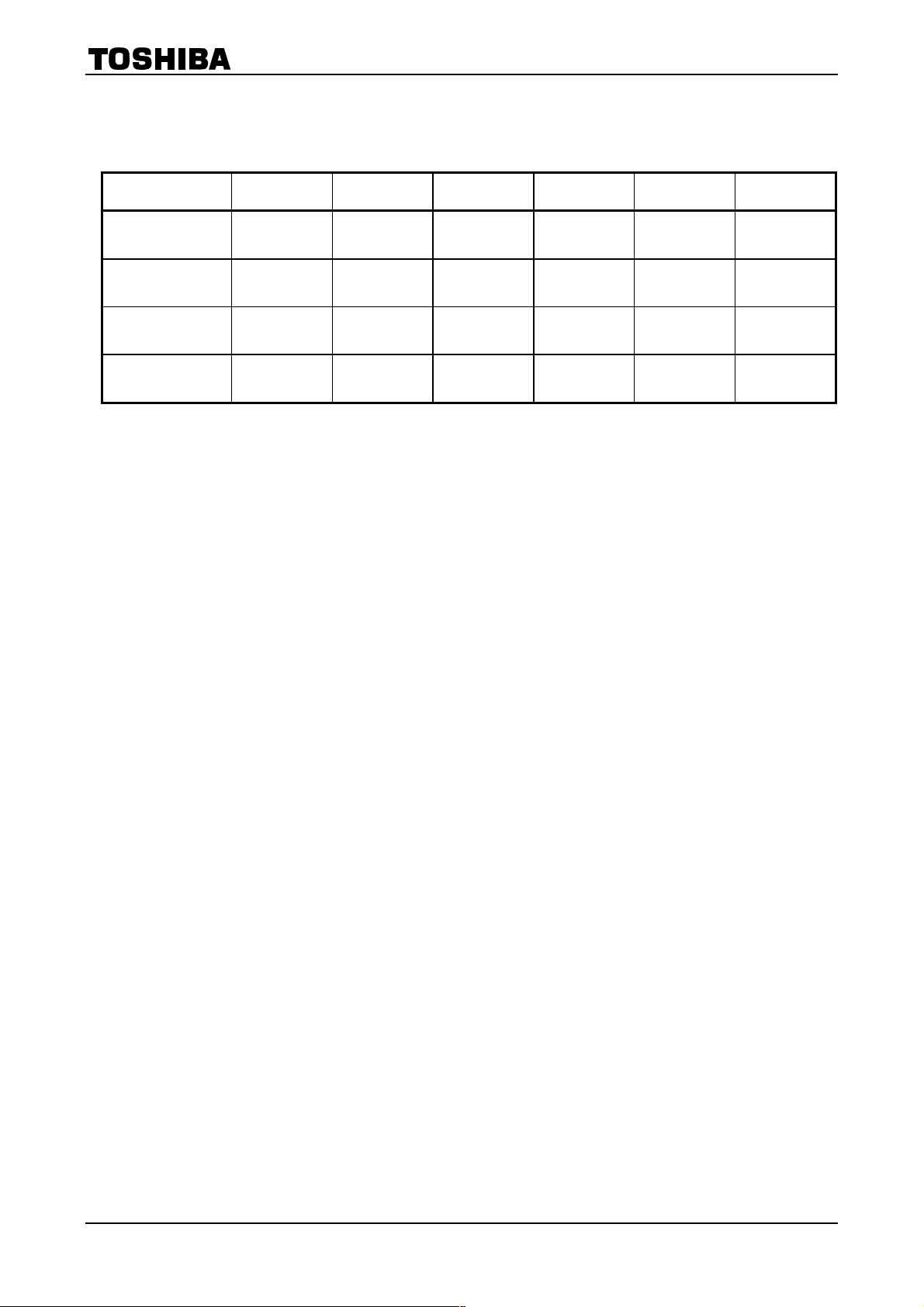

5. 垂直間引き

垂直間引き

垂直間引き垂直間引き

PIP 処理を行う場合、垂直方向に圧縮する必要があります。そこで、ラインメモリを用い、以下のような係数

により、垂直方向の間引きを行います。間引き率の設定は 10hex: VWS にて行います。

垂直間引き 1H 係数 2H 係数 3H 係数 4H 係数 5H 係数 6H 係数

TC90A67F

1/3 間引き

(VWS = 00)

1/4 間引き

(VWS = 01)

1/5 間引き

(VWS = 10)

1/6 間引き

(VWS = 11)

書き込みライン数は内部にて固定となっており、親信号の 50 Hz/60 Hz 検出結果により切り替わります。

なお、一画面分の表示ライン数は (書き込みライン数 -1) となります。

6. 書き込み

書き込み・読み出し

書き込み書き込み

書き込みの範囲設定は水平書き込みスタートポイント (16hex: CHS)、垂直書き込みスタートポイント (子画

面 f

V

また水平サンプル数は 1Ahex: HSPL で設定し、書き込みライン数は垂直間引き率により決定します。

読み出し位置の設定は水平読み出しスタートポイント (14hex: PHS)、垂直読み出しスタートポイント (親画

面 f

V

また水平表示サイズは 12hex: PHW で設定し、読み出しライン数は親画面 f

画面 f

7. 映像用

映像用 DAC

映像用映像用

本 IC では映像用として 3ch の 8 bit DAC を搭載しています。この DAC は 24 MHz で動作します。

出力 D レンジは V

8. ACC 制御

ACC 制御はカラーバースト信号の復調結果とコマンドで設定したリファレンスレベル (21hex: ACCPAL、

ACCNTSC) を比較することで行っています。

その比較値より小さい場合ゲインを上げ、大きい場合にはゲインを下げます。

9. 輝度信号ピーキング回路

輝度信号ピーキング回路

輝度信号ピーキング回路輝度信号ピーキング回路

間引きに伴う LPF の使用により、高域成分が除去され、PIP の映像としてぼやけた映像になります。

よってある帯域を持ち上げることにより鮮明な映像にすることができます。この回路の特性は 2 種類あり

(10hex: YPKGS で切り替え)、それぞれに対してゲインを 4 段階 (10hex: YPKGG) 選択できます。

10. コントラスト、色レベル調整

コントラスト、色レベル調整

コントラスト、色レベル調整コントラスト、色レベル調整

輝度信号に対してコントラスト、復調後色信号に対して色レベル調整が行えます。

コントラスト (1Ahex: CTRT 値) : +1.0dB (00000)~+3.5dB (11111)

色レベル (1Ahex: CVLV 値) : -6dB (10000)~0dB (00000)~+6dB (01111)

となります。初期値ではコントラスト+1dB、色レベル 0dB になっています。

・読み出し範囲設定

・読み出し・読み出し

= 60 Hz 時 16hex: CVSN、子画面 fV = 50 Hz 時 17hex: CVSP) にて書き込み開始位置を設定します。

= 60 Hz 時 14hex: PVSN、親画面 fV = 50 Hz 時 15hex: PVSP) にて読み出し開始位置を設定します。

= 50 Hz 時 13hex: PVWP で設定します。

V

制御

制御制御

1/4 1/2 1/4 ¾ ¾ ¾

1/8 3/8 3/8 1/8 ¾ ¾

1/16 1/4 3/8 1/4 1/16 ¾

1/16 3/16 1/4 1/4 3/16 1/16

範囲設定

範囲設定範囲設定

(top)-V

DD

(bottom) 端子電圧差で決まります。1.5 V

REFD

= 60 Hz 時 12hex: PVWN、親

V

(標準) で使用してください。

p-p

8

2002-02-08

Loading...

Loading...